# **Contribution to the Development of the LHCb Vertex Locator Readout Electronics**

## **Thèse de Doctorat**

présentée à la Faculté des Sciences

de l'Université de Lausanne

pour l'obtention du grade de docteur ès sciences

par

**Iouri Ermoline**

Ingenieur diplômé de l'LMI (Leningrad)

## **Jury**

Prof. Henri Masson, président du jury

Prof. Aurélio Bay, directeur de thèse

Dr. Paweł Jalocha, expert interne

Prof. Vladimir Obraztsov, expert externe

Lausanne, 2003

## Acknowledgements

I am grateful to many people I have been in contact and who helped me during my work on the subject described in this thesis.

Professor Aurelio Bay, the initiator and director, I would like to thank for his assistance and confidence.

Guido and Raymond, my Lausanne colleagues, were always ready to provide the practical help and participate in fruitful discussions. Special thanks to Erika for her permanent efforts to create a friendly atmosphere in the group and her distinguished linguistic achievements.

Among many of my LHCb colleagues I would like to mention Jorgen Christiansen, Paula Collins, Hans Dijkstra, Clara Gaspar, John Harvey, Richard Jacobsson, Beat Jost, Hans Muller, Tatsuya Nakada, Thomas Ruf, Ulrich Parzefall, Ulrich Straumann and Jacques Tinembart who helped me in direct and indirect ways during my work for the LHCb experiment.

# Abstract

The LHCb experiment is being built at the future LHC accelerator at CERN. It is a forward single-arm spectrometer dedicated to precision measurements of CP violation and rare decays in the b quark sector. Presently it is finishing its R&D and final design stage. The construction already started for the magnet and calorimeters.

In the Standard Model, CP violation arises via the complex phase of the  $3 \times 3$  CKM (Cabibbo-Kobayashi-Maskawa) quark mixing matrix. The LHCb experiment will test the unitarity of this matrix by measuring in several theoretically unrelated ways all angles and sides of the so-called "unitary triangle". This will allow to over-constrain the model and - hopefully - to exhibit inconsistencies which will be a signal of physics beyond the Standard Model.

The Vertex reconstruction is a fundamental requirement for the LHCb experiment. Displaced secondary vertices are a distinctive feature of b-hadron decays. This signature is used in the LHCb topology trigger. The Vertex Locator (VeLo) has to provide precise measurements of track coordinates close to the interaction region. These are used to reconstruct production and decay vertices of beauty-hadrons and to provide accurate measurements of their decay lifetimes.

The Vertex Locator electronics is an essential part of the data acquisition system and must conform to the overall LHCb electronics specification. The design of the electronics must maximize the signal to noise ratio in order to achieve the best tracking reconstruction performance in the detector. The electronics is being designed in parallel with the silicon detector development and went through several prototyping phases, which are described in this thesis.

## Résumé

L'expérience LHCb sera installée sur le futur accélérateur LHC du CERN. LHCb est un spectromètre à un bras consacré aux mesures de précision de la violation CP et à l'étude des désintégrations rares des particules qui contiennent un quark b. Actuellement LHCb se trouve dans la phase finale de recherche et développement et de conception. La construction a déjà commencé pour l'aimant et les calorimètres.

Dans le Modèle Standard, la violation CP est causée par une phase complexe dans la matrice  $3 \times 3$  CKM (Cabibbo-Kobayashi-Maskawa) de mélange des quarks. L'expérience LHCb compte utiliser les mesons B pour tester l'unitarité de cette matrice, en mesurant de diverses manières indépendantes tous les angles et côtés du "triangle d'unitarité". Cela permettra de surdéterminer le modèle et, peut-être, de mettre en évidence des incohérences qui seraient le signal de l'existence d'une physique au-delà du Modèle Standard.

La reconstruction du vertex de désintégration des particules est une condition fondamentale pour l'expérience LHCb. La présence d'un vertex secondaire déplacé est une signature de la désintégration de particules avec un quark b. Cette signature est utilisée dans le trigger topologique du LHCb. Le Vertex Locator (VeLo) doit fournir des mesures précises de coordonnées de passage des traces près de la région d'interaction. Ces points sont ensuite utilisés pour reconstruire les trajectoires des particules et l'identification des vertices secondaires et la mesure des temps de vie des hadrons avec quark b.

L'électronique du VeLo est une partie essentielle du système d'acquisition de données et doit se conformer aux spécifications de l'électronique de LHCb. La conception des circuits doit maximiser le rapport signal/bruit pour obtenir la meilleure performance de reconstruction des traces dans le détecteur. L'électronique, conçue en parallèle avec le développement du détecteur de silicium, a parcouru plusieurs phases de "prototyping" décrites dans cette thèse.

# Table of Contents

|                                                                 |    |

|-----------------------------------------------------------------|----|

| <b>1 Introduction</b>                                           | 1  |

| 1.1 Matter and antimatter                                       | 1  |

| 1.2 CERN and LHC                                                | 1  |

| 1.3 Overview of LHCb experiment                                 | 4  |

| <b>2 LHCb electronics, trigger and data acquisition</b>         | 9  |

| 2.1 Level-0 electronics                                         | 10 |

| 2.2 Level-1 electronics                                         | 12 |

| 2.3 Trigger system                                              | 13 |

| 2.4 Data acquisition system                                     | 15 |

| 2.5 Timing and Fast Control system                              | 17 |

| 2.6 Experiment Control System                                   | 19 |

| <b>3 VELO electronics development</b>                           | 21 |

| 3.1 VELO detector                                               | 21 |

| 3.1.1 VELO implementation                                       | 22 |

| 3.1.2 VELO experimental environment                             | 24 |

| 3.2 VELO Level-0 electronics                                    | 26 |

| 3.2.1 Level-0 chips                                             | 28 |

| 3.2.2 Level-0 electronics control                               | 30 |

| 3.2.2.1 Timing and Fast Control system interface                | 30 |

| 3.2.2.2 Experiment Control System interface                     | 31 |

| 3.2.2.3 Digital repeater card and overall timing/control layout | 33 |

| 3.2.3 Analog data link                                          | 34 |

| 3.2.3.1 Link requirements and implementation options            | 34 |

| 3.2.3.2 Analog link design (by R. Frei, UniL)                   | 36 |

| 3.3 VELO Level-1 electronics development                        | 42 |

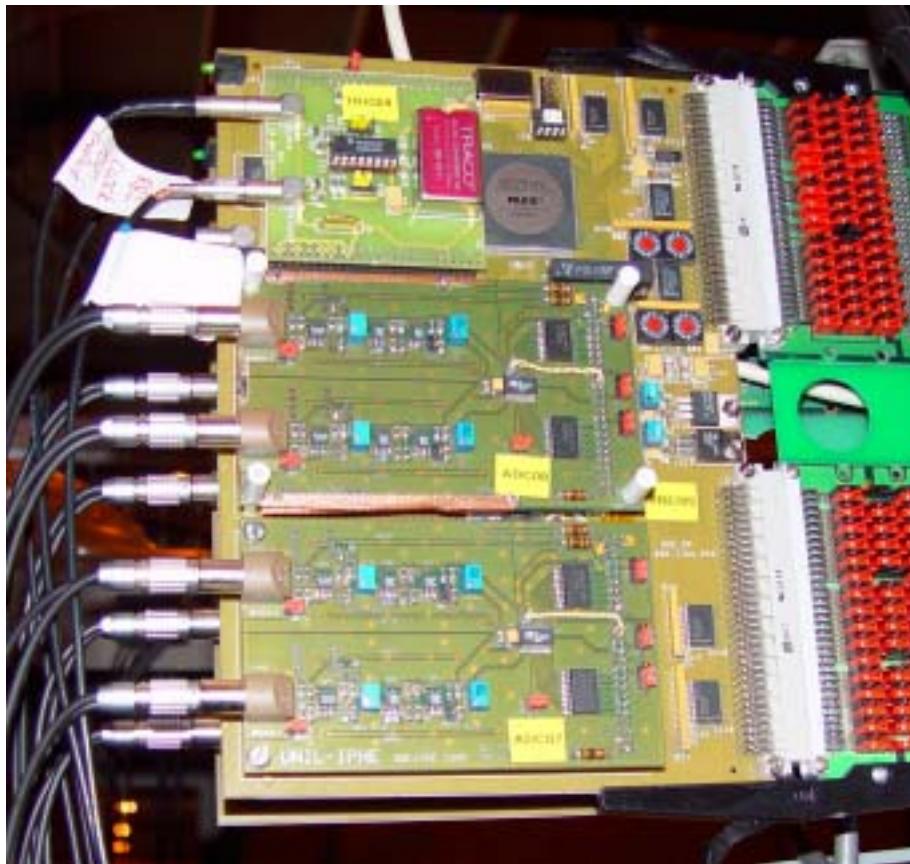

| 3.3.1 Level-1 electronics prototyping                           | 45 |

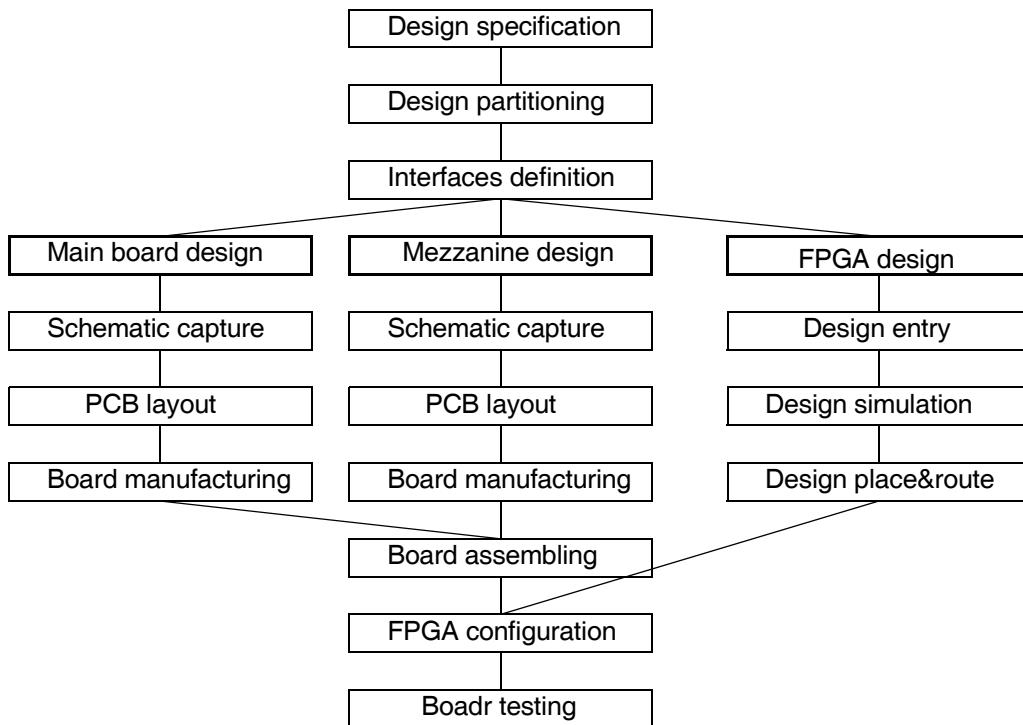

| 3.3.1.1 Design flow                                             | 46 |

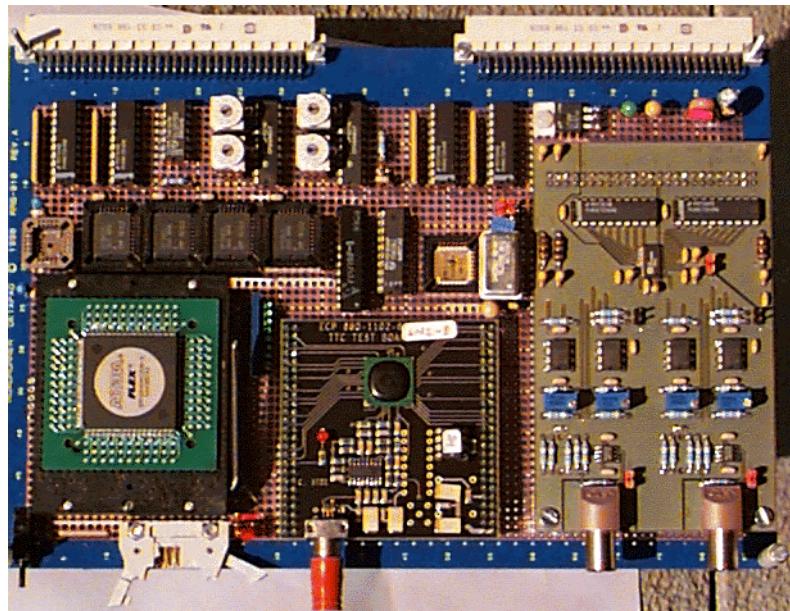

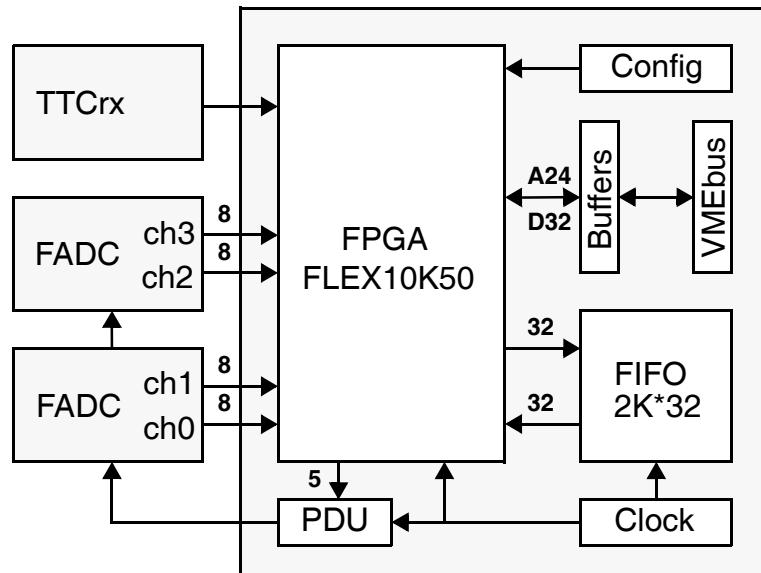

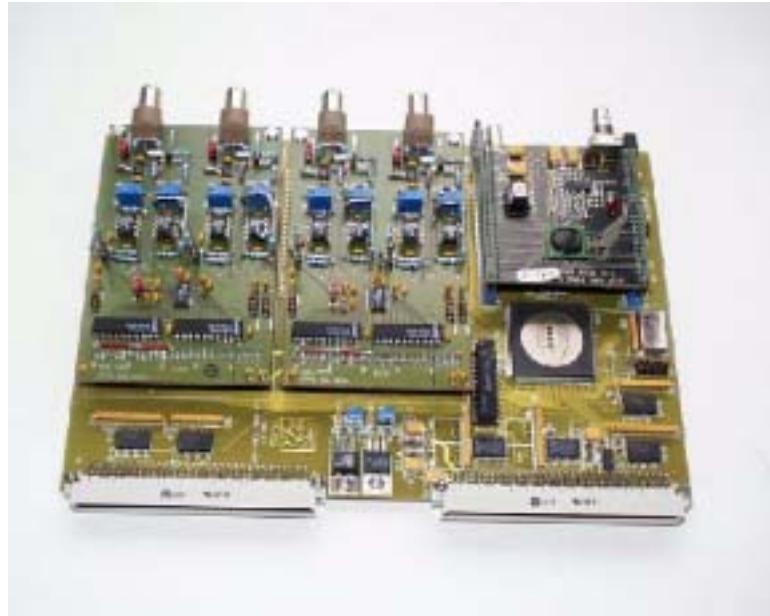

| 3.3.1.2 Level-1 electronics prototypes                          | 47 |

| 3.3.2 Tests on the Level-1 electronics prototype                | 55 |

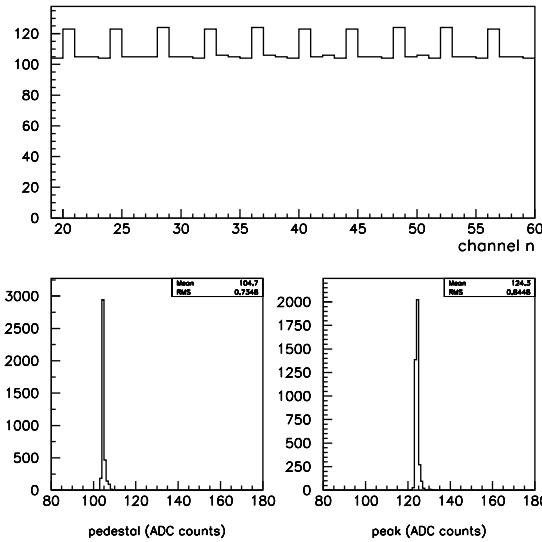

| 3.3.2.1 Test of the complete analog link                        | 55 |

| 3.3.2.2 Tests with the SCTA128 chip                             | 57 |

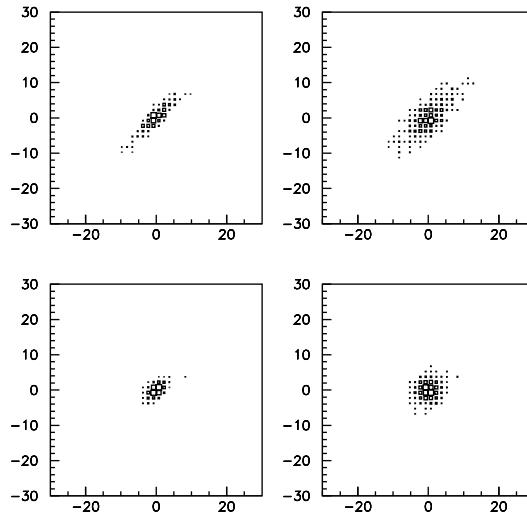

| 3.3.2.3 Test of the VELO silicon sensor prototype               | 60 |

| 3.3.2.4 Test of the complete readout chain                      | 63 |

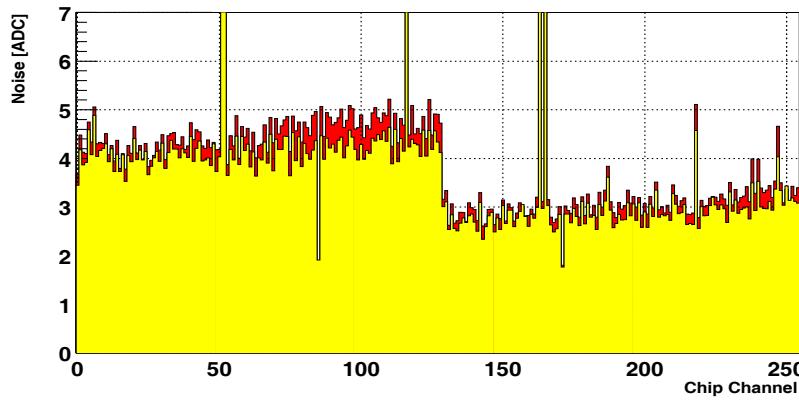

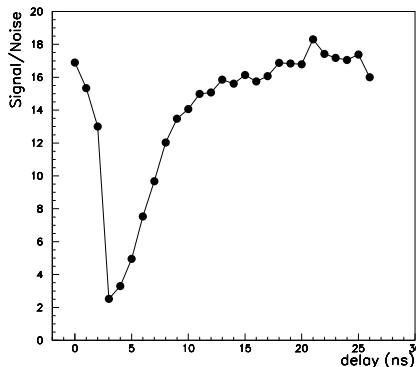

| 3.3.2.5 RB2 signal to noise study                               | 70 |

| <b>4 VELO Level-1 electronics integration</b>                   | 71 |

| 4.1 Timing and synchronisation                                  | 71 |

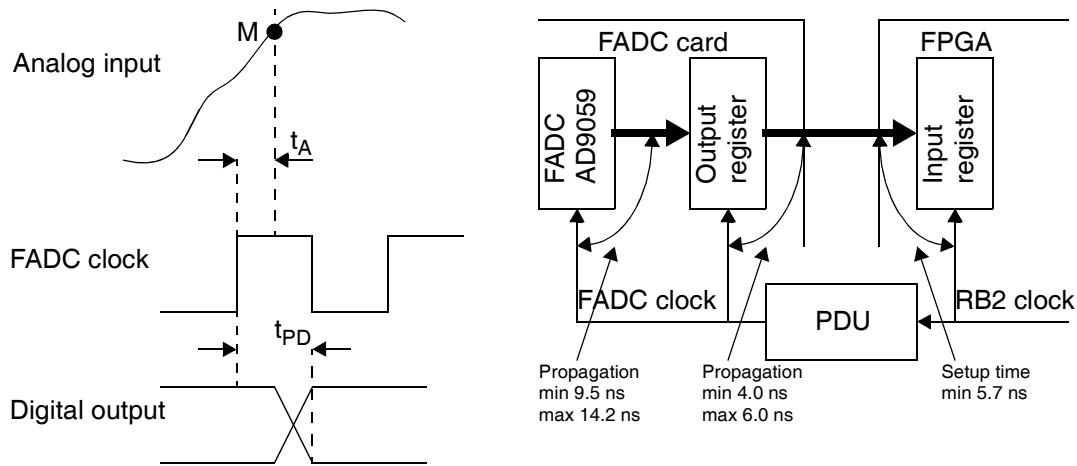

| 4.1.1 FADC clock adjustment                                     | 72 |

| 4.1.2 Event synchronisation                                     | 73 |

|                                                                    |           |

|--------------------------------------------------------------------|-----------|

| 4.1.3 Synchronisation error detection . . . . .                    | 73        |

| 4.1.4 System resets . . . . .                                      | 74        |

| 4.2 Level-1 trigger system interface . . . . .                     | 75        |

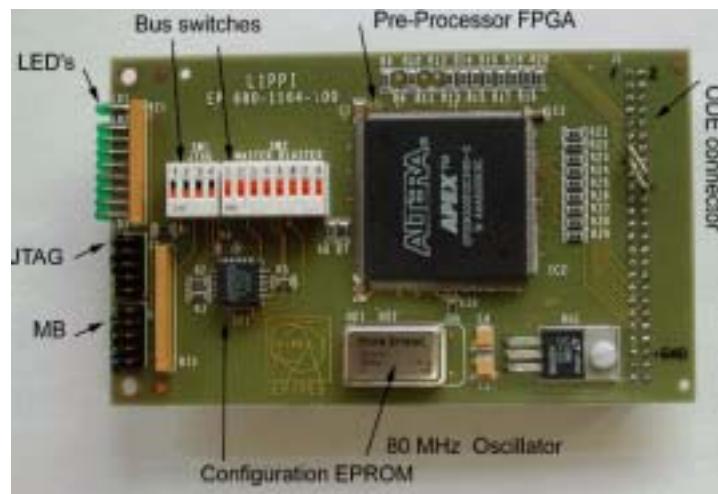

| 4.2.1 Level-1 trigger preprocessor (by G. Haefeli, UniL) . . . . . | 76        |

| 4.2.2 Electrical interface and data transfer protocol . . . . .    | 78        |

| 4.2.3 VELO - Level-1 trigger data format . . . . .                 | 78        |

| 4.3 DAQ interface . . . . .                                        | 81        |

| 4.4 ECS interface . . . . .                                        | 83        |

| <b>5 Perspectives and conclusions</b> . . . . .                    | <b>85</b> |

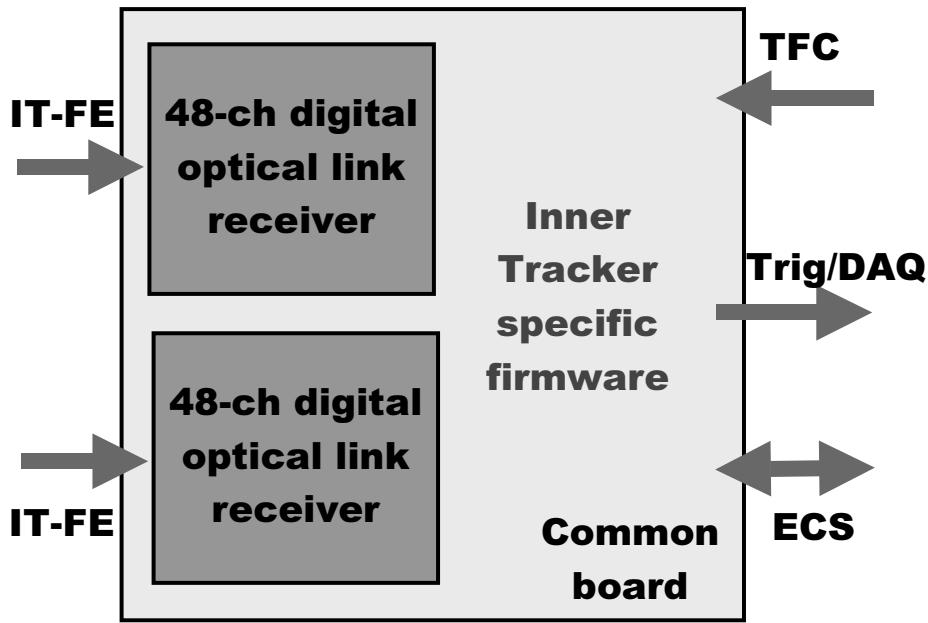

| 5.1 Common Level-1 board for several subdetectors . . . . .        | 86        |

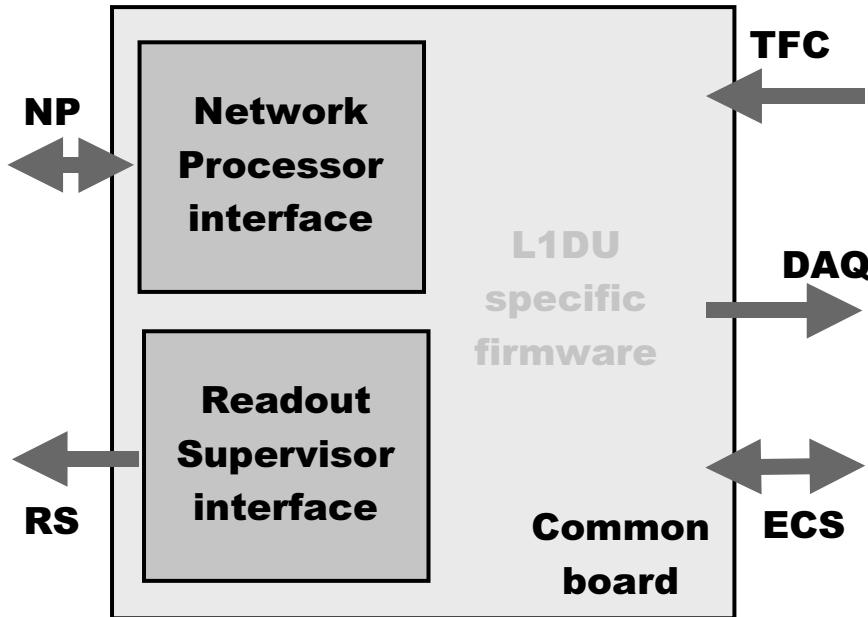

| 5.2 VELO Level-1 board as Level-1 Decision Unit . . . . .          | 88        |

| 5.3 Conclusions . . . . .                                          | 89        |

| <b>6 Bibliography</b> . . . . .                                    | <b>91</b> |

| <b>7 Acronyms</b> . . . . .                                        | <b>95</b> |

# 1 Introduction

## 1.1 Matter and antimatter

It is generally believed that our World is stable and made of matter. Where all antimatter disappeared after a Big Bang that created an equal mixture of matter and antimatter?

A possible explanation [1] is that an asymmetrical behaviour of particle and antiparticle, so called symmetry violation or CP (Charge conjugation / Parity) violation - the mysterious phenomena discovered in neutral kaon decays in 1964 [2], was at the origin of the slight matter-antimatter disequilibrium, necessary for the present dominance of matter over antimatter in the World.

The present Standard Model (SM) of the world of elementary particles can naturally generate CP violation. It was firmly established in neutral kaon decays and recently in the B-meson decays - the area, where a new generation of experiments opened a new phase of CP violation research. The SM, however, does not seem to be capable of generating a sufficient amount of CP violation to explain the observed dominance of matter. This calls for new sources of CP violation beyond the Standard Model which contribute or even fully accounts for the observed phenomena. CP violation is therefore a highly interesting place to look for evidence for new physics [3].

In the Standard Model, CP violation is described in the framework of the 3x3 complex unitary mass-mixing matrix (CKM matrix), which can be described by four independent parameters. These four parameters of the CKM matrix will be well determined with a small theoretical uncertainty within the framework of the Standard Model by ongoing experiments (BABAR, BELLE, CDF)

The Large Hadron Collider (LHC) at CERN is the new scientific instrument, a gigantic microscope to study invisible. It offers the opportunity to study CP violation with sufficient precision to isolate the contribution from a possible New Physics and to understand its nature.

## 1.2 CERN and LHC

CERN, the European Laboratory for Particle Physics near Geneva, created in 1954, provides the experimental facilities required to advance our knowledge of the universe, matter and the fundamental laws of the nature. The scientific research done at CERN not only contributes to particle physics but also to many other fields. These include vacuum technology, superconducting magnets, computing, cryogenics and electrical, electronics civil and mechanical engineering just to mention a few.

The Large Hadron Collider - the CERN next particle accelerator - allows to explore physics up to the TeV scale [4]. This is a 27 km circumference high luminosity proton-proton collider being built in the present LEP tunnel reusing CERN accelerator complex. It will accelerate two proton beams to the total energy of 14 TeV with a design luminosity of  $10^{34} \text{ cm}^{-2}\text{s}^{-1}$ .

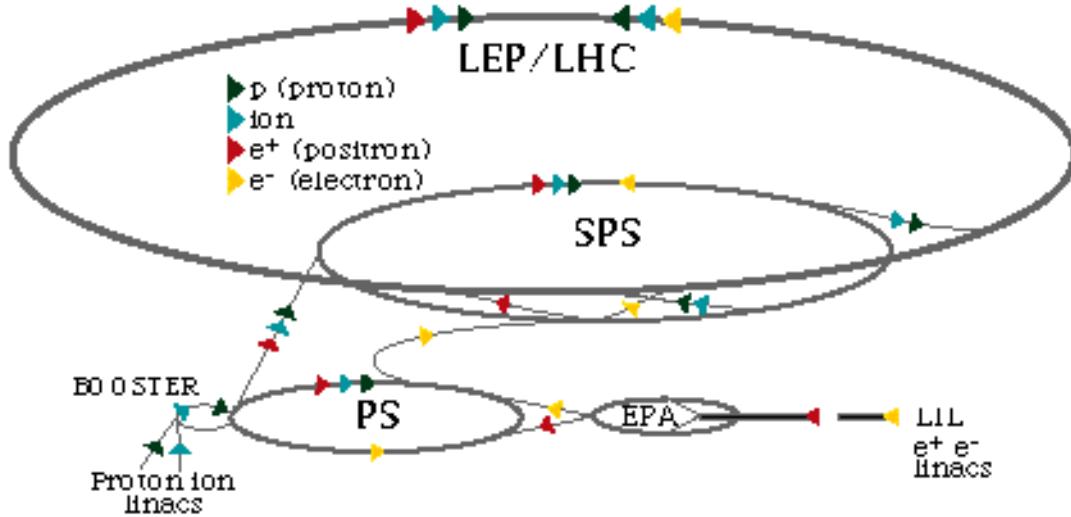

**Figure 1** The CERN accelerator complex.

The proton beams are accelerated in a linear accelerator at the Meyrin site (*Linac*) up to 50 MeV. Then two circular accelerators boost them to 1 GeV (*Booster*) and 26 GeV (*PS*) before they enter the Super Proton Synchrotron (*SPS*). There they reach an energy of 450 GeV and enter the LHC via two new tunnels. The final energy of 7 TeV is limited by the magnetic field in the super-conducting magnets.

Four experiments have been approved for the LHC accelerator and will be installed at the intersecting points of the LHC:

- The ALICE (A Large Ion Collider Experiment) Collaboration will build a dedicated heavy-ion detector to exploit the nucleus-nucleus interactions at LHC energies [7]. The aim is to study the physics of strongly interacting matter at extreme energy densities, where the formation of a new phase of matter, the quark-gluon plasma, is expected. The existence of such a phase and its properties are a key issue in QCD for the understanding of confinement and chiral-symmetry restoration. For this purpose, the collaboration intends to carry out a comprehensive study of the hadrons, electrons, muons and photons produced in the collision of heavy nuclei. The experiment is designed to cope with the highest particle multiplicities anticipated for Pb-Pb reactions.

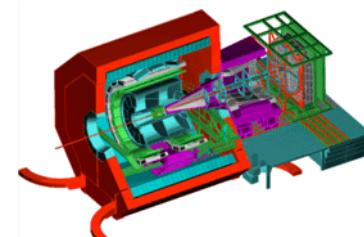

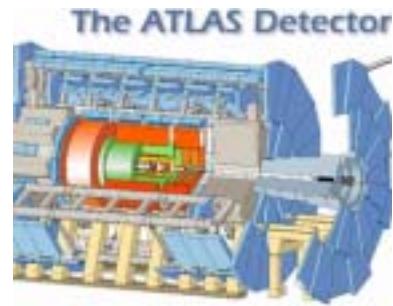

- The ATLAS (A Toroidal Lhc ApparatuS) Collaboration [6] proposes to build a general-purpose  $pp$  detector which is designed to exploit the full discovery potential of the LHC, among which the origin of mass at the electroweak scale. The detector optimization is therefore guided by physics issues such as sensitivity to the largest possible Higgs mass range. Other important goals are the searches for heavy W and Z-like objects, the super symmetric particles, the components of the fundamental fermions and detailed studies of the top quark. The primary goal is to operate at high luminosity, but the detector is conceived to assure performance in the full operational range of LHC. The investigation of CP violation in B-decays will be part of the addressed topics as well. ATLAS is planned to run also in heavy ion mode, searching for some rare processes.

- The CMS (Compact Muon Solenoid) detector has been designed to detect cleanly the various signatures for new physics by identifying and precisely measuring muons, electrons and photons over a large energy range and at high luminosity [5]. The key features that enable CMS detector to reach the challenges are an electromagnetic calorimeter with excellent energy resolution, efficient tracking at high luminosity for lepton momentum measurements, b-quark tagging and for electron and photon identification as well as tau and heavy-flavour vertexing, muon momentum measurement up to highest luminosity. CMS could be competitive as well for B-physics in some particular channels. The detector will also be used to detect low momentum muons produced in heavy ion collisions.

- The LHCb experiment is a forward detector which will study CP violation and other rare phenomena in the decays of Beauty particles [8]. At the LHC the produced B-mesons are correlated in rapidity and are typically forward, hence a forward spectrometer covering the angular region below 400 mrd would have all the decay product of the B-mesons in its acceptance for roughly (10-15)% of all Beauty events. LHC will operate at a luminosity much reduced compared with the maximum luminosity available to exploit only beam crossing with single interactions. Its main goal is to measure all angles of the unitary triangles in many different ways, over-constraining the CKM matrix including higher order terms and thereby searching for an inconsistency in the CKM picture that would reveal new physics. It will be described in more details in the following section.

### 1.3 Overview of LHCb experiment

#### Requirements

The production cross section of the  $b\bar{b}$  quark pairs at the LHC energy is estimated to be  $\sim 500 \mu b$ , larger than at any existing machines. The fraction of events with  $b$  quarks,  $\sigma_{b\bar{b}}/\sigma_{\text{inelastic}}$ , is about  $6 \times 10^{-3}$  which is similar to the fraction of charm events in the present fixed-target charm experiments. Thus, LHC appears to be a very promising place to perform high precision CP violation measurements in  $B$ -meson decays. At LHC,  $B_s$ ,  $\bar{B}_s$ ,  $B_c^\pm$  and  $b$ -baryons are abundantly produced, in addition to  $B^\pm$ ,  $B^0$  and  $\bar{B}^0$ .

The goal of  $B$  physics in the LHC era, is to determine the CKM parameters in a model-independent way and to isolate the effect of New Physics so that its characteristics could be identified. This calls for a high statistics experiment capable of studying CP violation with both  $B^0$  and  $B_s^0$  systems decaying into various final states, including those with only hadrons. In order to exploit the potential of LHC, experiments need to have the following capabilities:

- Trigger sensitive to both leptonic and hadronic final states.

- Particle identification system capable of identifying  $p$ ,  $K$ ,  $\pi$ ,  $\mu$  and  $e$  within the required momentum range.

- Vertex detector able to reconstruct primary and  $b$ -hadron vertices very precisely.

- Tracking system with good momentum resolution.

In addition, a capability of reconstructing  $\pi^0$  would enhance the potential of the experiment further. The LHCb spectrometer [9] is designed to fulfil these requirements. It is also important to note that the detector covers a region of phase space which is not looked at by the two general purpose detectors, ATLAS and CMS.

#### Apparatus

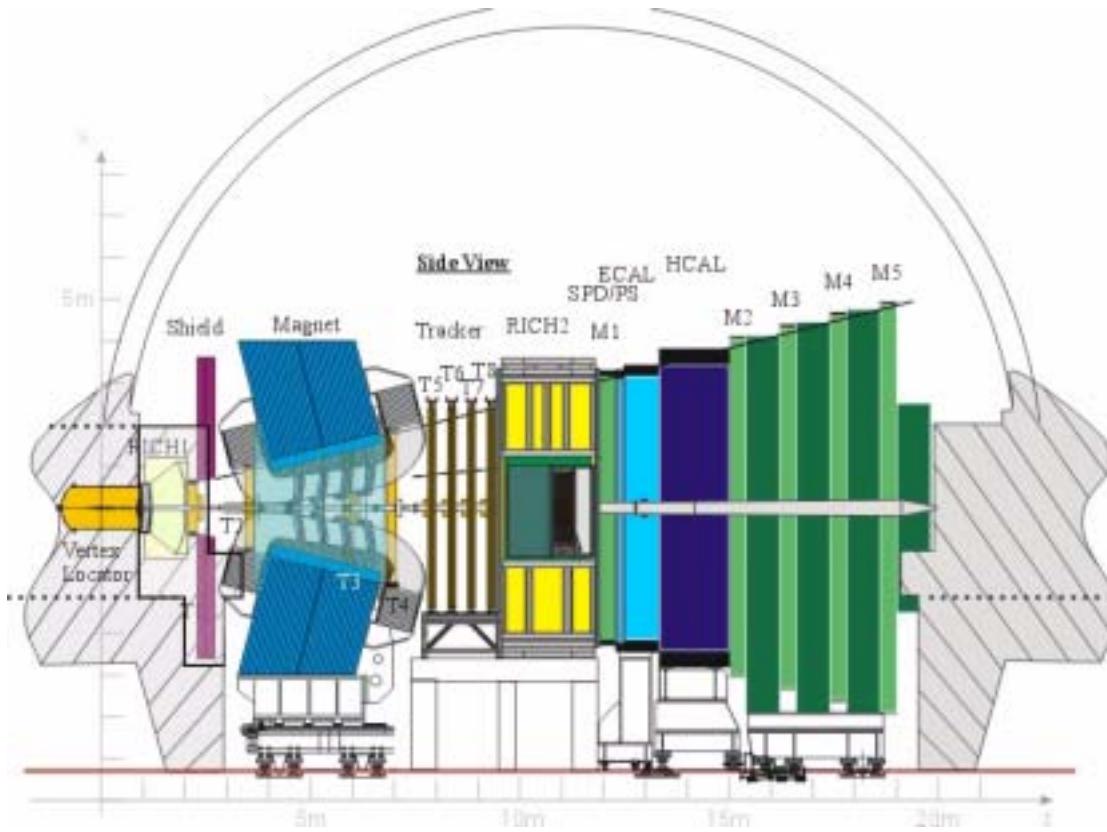

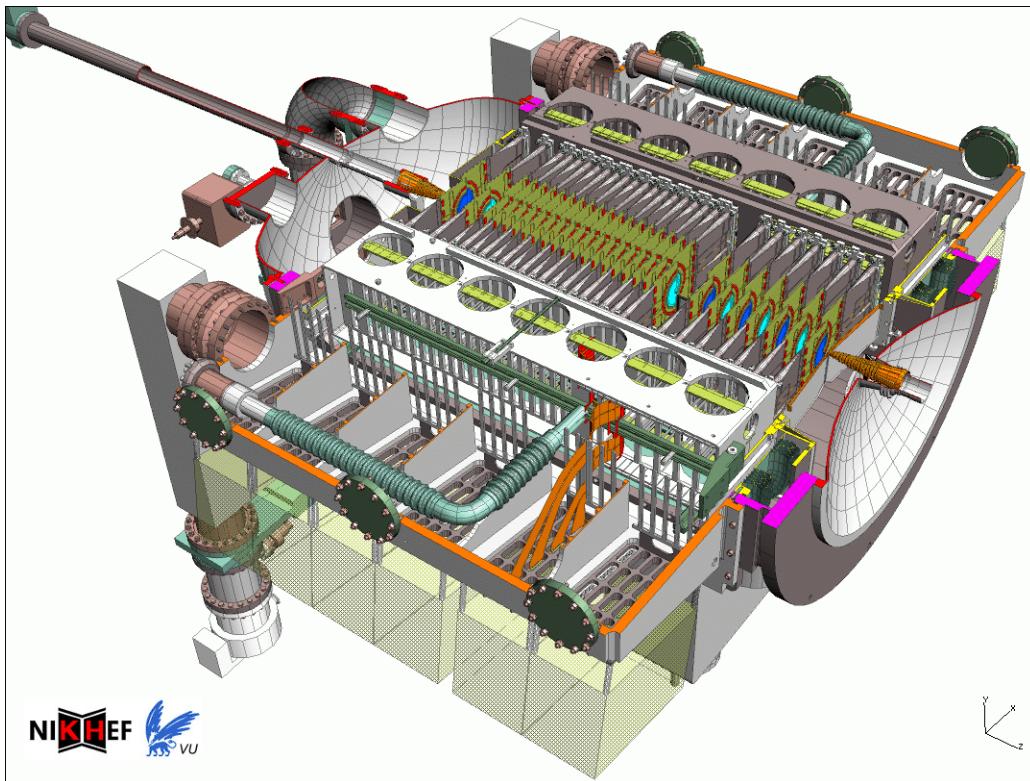

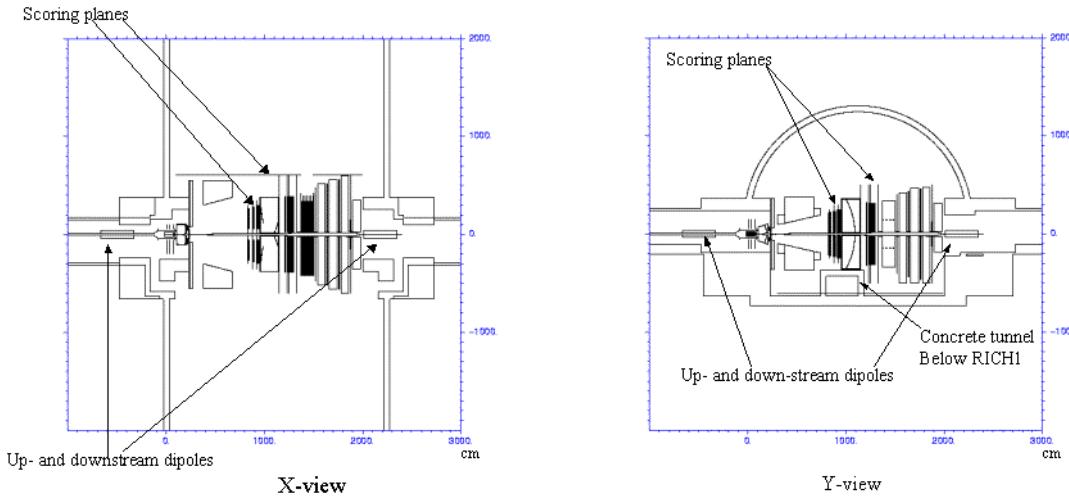

The layout of the LHCb detector<sup>1</sup> shown in Figure 2 resembles a typical fixed target spectrometer due to its forward geometry. LHCb consists of a vertex detector at the intersection point (placed in "Roman Pots"), a tracking system, Ring Imaging Cherenkov Counters with aerogel and gas radiators, a large-gap dipole magnet, a calorimeter system, and a muon system. An existing LEP experimental area is reused to install the detector. The interaction point is shifted by 11 m from the nominal point, the centre of the experimental hall, in order to accommodate the detector elements without extra excavation.

---

1. A redesign of some components of the LHCb is going on and will be finalised after the end of this thesis ("LHCb light"); unless otherwise specified, in this work the LHCb layout from the Technical Proposal [8] (LHCb TP) is described.

**Figure 2** The LHCb spectrometer in the experimental area.

The choice of the detector geometry is based on the fact that both the b- and  $\bar{b}$ -hadrons are predominantly produced in the same forward (or backward) cone at high energies. Further advantages of the forward geometry are:

- The b-hadrons produced in the forward direction are faster than those in the central region. Their average momentum is about 80 GeV/c, corresponding to a mean decay length of 7 mm. Therefore, a good decay time resolution can be obtained for reconstructed b-hadrons.

- The spectrometer can be built in an open geometry with an interaction region which is not surrounded by all the detector elements. This allows a vertex detector system to be built with sensors which can be extracted away from the beam during the injection using Roman Pot technique. During the data taking, the sensors are positioned close to the beam in order to achieve a good vertex resolution.

- In the forward region, momenta are mainly carried by the longitudinal components. Therefore, the threshold values for the  $p_T$  triggers can be set low for electrons, muons and hadrons without being constrained by the detector requirements. This makes the  $p_T$  triggers more efficient than in the central region.

- The momentum range required for particle identification is well matched to the Ring Imaging Cherenkov (RICH) technique. The required size for the RICH counters remains affordable.

- The open geometry allows easy installation, maintenance and possible upgrade.

### Beam Pipe

A large vacuum tank with a length of 1.7 m and a diameter of 1 m is placed around the interaction point to accommodate the vertex detector system with its retraction mechanics. It has a 2 mm thick Al forward exit window over the full detector acceptance. This part is followed by two conical sections: the first one is 1.4 m long with a 25 mrad opening angle, and the second part is 16 m long with a 10 mrad opening angle.

Except for bellows and flanges and the last 6.3 m of the 10 mrad cone, the beam pipe is made of Al-Be alloy in order to reduce the radiation length. This is essential for minimising the occupancies of the tracking and RICH systems, as well as for the detection of photons and electrons. Due to mechanical and safety reasons, flanges and bellows are made of Al. The beam pipe section in the region of the calorimeters and muon system is no longer important for the detection of electrons and photons. It is surrounded by shielding material, thus generating background particles is no longer an issue. Therefore, stainless steel is used for this section.

### Magnet

A dipole magnet with Al conductor provides a field integral of 4 Tm. The polarity of the field can be changed to reduce systematic errors in the CP-violation measurements that could result from a left-right asymmetry of the detector. The two pole faces form a wedge shape following the spectrometer acceptance, in order to reduce the power consumption to 42 MW. The yoke of the magnet weights 1.5 kt and consists of many iron plates assembled together. The magnet assembly will take place in the experimental area.

### Vertex Locator

A total of 27 stations of silicon microstrip detectors are placed perpendicular to the beam of which 25 stations are used as a vertex detector system (VErtex LOcator, VELO [10], 21 stations in the “LHCb light” layout). The remaining two stations are dedicated for detecting bunch crossings with more than one pp interaction as part of the Level-0 trigger (pile-up veto counter).

Stations are split into two halves, covering the left and right  $180^0$  sections. Each vertex detector station consists of two Si sensor planes with different strip layouts, one for  $r$  and the other for  $\phi$  measurements. There are about 200'000 strips in total with varying sizes so that the occupancy remains below 1% everywhere. The pile-up veto counter has only  $r$ -measuring sensors. The closest distance between the active silicon area and the beam is 8 mm.

In order to cope with high radiation dose expected at this position so close to the beam, n-on-n silicon sensors are taken as baseline. The silicon detectors are placed in Roman Pots with  $250\ \mu\text{m}$  thick aluminium foil, which acts as a shield against RF pickup of the circulating beam bunches. In order to avoid explosion, a secondary vacuum is maintained inside the Roman Pots.

During the injection and acceleration, the Roman Pot system will be moved away from the beam to avoid interference with the machine operation and accidental irradiation of the detectors.

### Tracking

Because of the high particle density close to the beam pipe, the LHCb tracking detector is split into inner and outer systems. The boundary between the two was chosen so that the occupancy of the outer tracker does not exceed 15% at the highest point.

The outer tracking system uses drift chambers based on a straw cells structure. Straws are made by winding the carbon-loaded Kapton foil. The diameter of the straw is 5 mm and drift-time is sampled over 50 ns, i.e. two bunch crossings.

The inner tracking system is made from single sided p-on-n Si strip detectors with a strip pitch of  $\sim 200\ \mu\text{m}$ . Since the sensitive regions of the Si sensor are further away from the beam (several centimetres) compared with the sensors of the Vertex Locator, the problem of radiation damage is less severe.

### RICH

The RICH system of the LHCb detector consists of two detectors with three different radiators in order to cover the required momentum range, 1-100 GeV/c. The first detector uses aerogel and  $\text{C}_4\text{F}_{10}$  gas as radiators. The second detector, design to identify high momentum particles, is placed after the magnet and uses  $\text{CF}_4$  as radiator. The Cherenkov light is detected with planes of Hybrid Photon Detectors (HPD's) placed outside the spectrometer acceptance.

### Calorimeters

The calorimeter system consists of a preshower detector followed by electromagnetic and hadronic calorimeters. The primary function of the calorimeter system is to provide single-particle energy information to the Level-0 trigger. It is also used in offline to reconstruct  $\pi^0$  from B meson decays. It serves as the initial part of the muon filter system. The cells of the Preshower detector are made as two scintillator plates sandwiching a 14 mm-thick lead plate. The cell size of the preshower detector is matched to the module size of the electromagnetic calorimeter.

The hadron calorimeter is based on a scintillating tile design similar to that used in the ATLAS experiment with a reduced energy resolution of  $\sim 80\%$ . It is 6.8 m tall, 8.4 m wide and 165.5 cm long corresponding to  $5.6\ \lambda_L$ . There are only two cell sizes for the hadron calorimeter modules;  $13 \times 13\ \text{cm}^2$  and  $26 \times 26\ \text{cm}^2$ .

For the electromagnetic part, a Shashlik calorimeter is used since a modest energy resolution of  $\sim 10\%$  is needed. It is 6.3 m tall, 7.8 m wide and 83.5 cm long corresponding to  $25 X_0$ . The cell size of a module changes from  $4 \times 4 \text{ cm}^2$  in the zone closest to the beam pipe, to  $6 \times 6 \text{ cm}^2$  in the intermediate zone, and to  $12 \times 12 \text{ cm}^2$  in the outer most zone, minimizing the number of modules without deteriorating the performance.

## Muon

The muon system consists of four layers of hadron absorbers and five muon stations. The first station is placed in front of the first absorber layer, which is the calorimeter system. The three other absorbers are made of iron plates, each of them 80 cm thick. Three muon stations are placed between the absorbers and the fifth muon station is placed behind the last absorber, shielded with  $20 \lambda_I$  of material. A smaller shielding plate behind the last station protects the chambers from the particles produced by the proton beam in the accelerator.

In the LHCb Technical Proposal Resistive Plate Chambers are used in the region where the charged particle rate is below  $1 \text{ kHz/cm}^2$ . In the region with a charged particle rate from  $1 \text{ kHz/cm}^2$  to  $100 \text{ kHz/cm}^2$ , Multi Wire Proportional Chambers (MWPC's) are used. In the small region of the first muon station close to the beam pipe, where the charged particle rate exceeds  $100 \text{ kHz/cm}^2$ , triple-GEM chambers or MWPC's with asymmetric gas gap are being considered.

## Trigger system

The LHCb trigger is based on four decision levels. Due to the large mass and the transverse momentum spectrum of the B-meson, its decay products have on average higher  $p_T$  than particles produced in most of the inelastic pp interactions (minimum-bias events). Decay products of the B-meson originate from vertices that are displaced from the primary interaction point by several millimetres. The early levels of the LHCb trigger exploit those two characteristics.

Level-0 trigger decision is based on high- $p_T$  hadrons or electrons found in the calorimeter system or muons found in the muon system. In addition, the pile-up veto counter detects bunch crossings with more than one pp interaction. Level-0 trigger provides a modest reduction of minimum-bias events by a factor of  $\sim 10$ .

At Level-1, data from the Vertex Locator are used to select events with multiple vertices. Level-1 trigger provides a reduction factor of  $\sim 25$  for minimum-bias events. After a positive decision of the Level-1, whole LHCb data are read out to an event buffer in the CPU farm.

At Level-2 and Level-3 (or High Level Triggers) a further enhancement of events with b-hadrons is achieved by combining data from different detector components and reconstructing the full event for the decay modes of interest.

## 2 LHCb electronics, trigger and data acquisition

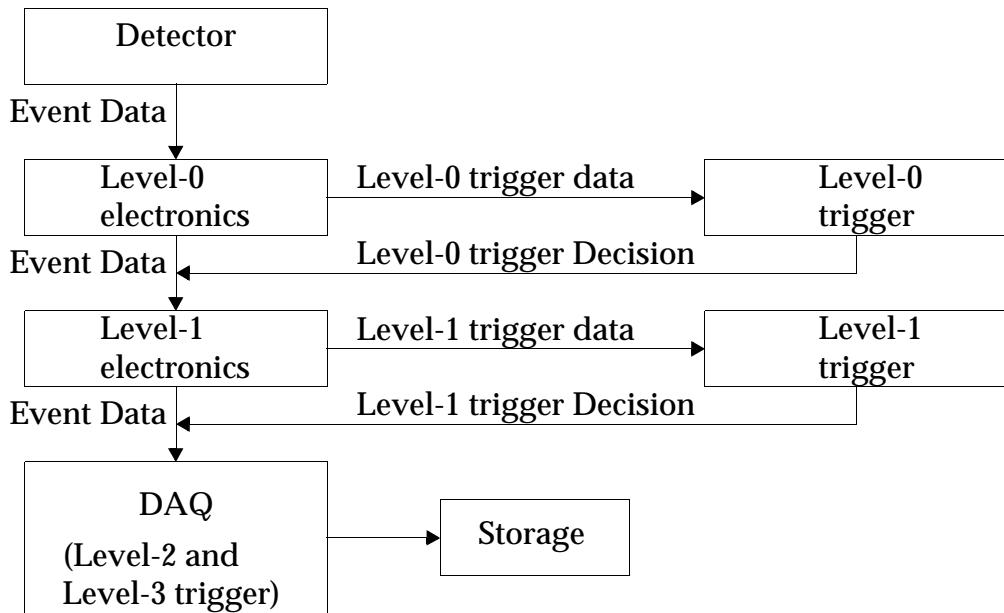

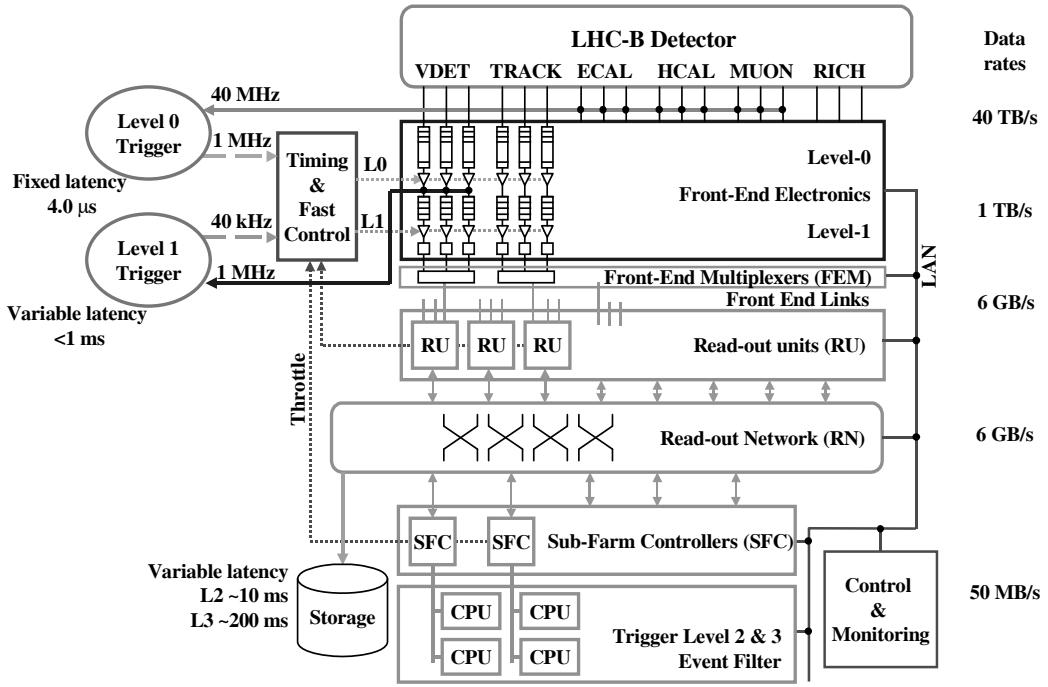

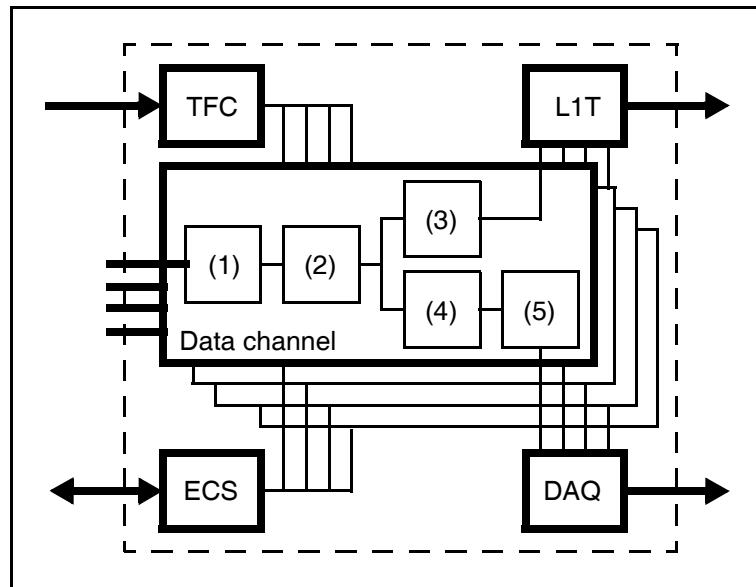

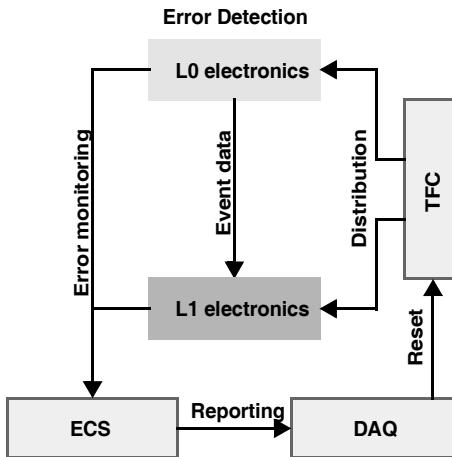

The LHCb electronics is divided in Level-0 and Level-1 electronics. The Level-0 electronics is located in the cavern on or near the detector while the most of the Level-1 electronics is located in the counting room as well as the trigger and the Data Acquisition (DAQ) systems. A simplified diagram of the LHCb electronics, trigger and DAQ systems is shown on Figure 3.

Figure 3 LHCb electronics, trigger and DAQ.

The Level-0 electronics of calorimeter and muon sub-detectors and the pile-up veto counter supplies data for the Level-0 trigger. During Level-0 trigger latency event data are kept in the pipelines of the Level-0 electronics. Data for events, accepted by the Level-0 trigger, are moved to the Level-1 electronics.

The Level-1 electronics of the Vertex Locator supplies data for the Level-1 trigger. During Level-1 trigger latency event data are kept in the Level-1 buffers of the Level-1 electronics. Upon positive trigger decision, data from the Level-1 electronics are collected by the DAQ system and made available for the Level-2 and Level-3 triggers. Finally selected events are stored for the off-line analysis.

The overall control of the LHCb electronics, trigger and DAQ system is performed by the TFC (Timing and Fast Control) system and the ECS (Experiment Control System) of the LHCb experiment.

In the following sections the individual parts of the LHCb electronics, trigger, DAQ and control systems will be described in more details.

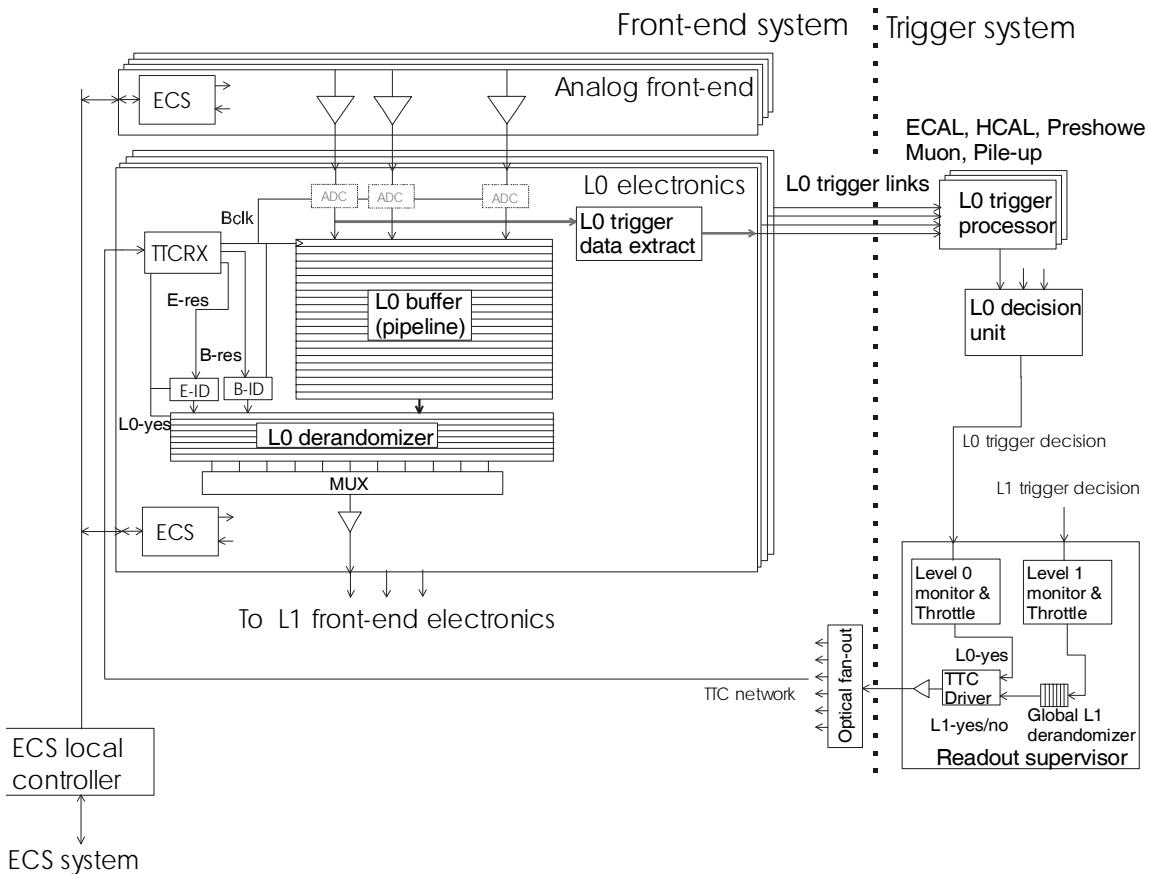

## 2.1 Level-0 electronics

The Level-0 electronics [11] must correctly capture and store detector signals, from particles generated by the bunch collisions of the LHC machine on a large number (~1 million) of electronic channels. The detector signals must be captured with sufficient time resolution, to determine the exact bunch crossing from which the particles originate. Captured data (analogue or digital) must be stored in the Level-0 electronics pipeline buffer, until the Level-0 trigger decision accepts or rejects data from a given bunch crossing. Accepted data must be extracted from the pipeline buffer and temporarily stored in the Level-0 derandomizer buffer, waiting to be transferred to the Level-1 electronics

**Figure 4** General architecture of the Level-0 electronics (from [11]).

A predictable behaviour of the Level-0 electronics system is of special importance in the LHCb experiment, because of the high bunch crossing rate (40 MHz) and the relatively high trigger rates. All electronics must be perfectly synchronised to the beam crossings, to insure correct capture of detector signals. The arrival of the Level-0 trigger-accept to the Level-0 electronics must also be in perfect synchronisation, to insure the extraction of correct event data from the Level-0 pipeline. Caused by the relative high Level-0 trigger accept rate, event data from the Level-0 pipeline must be temporarily stored in a derandomizer

buffer before being transferred to the Level-1 electronics. The size of this derandomizer buffer, and the speed of which data can be transferred to the Level-1 buffer, is a major bottleneck in the LHCb electronics that has a significant impact on the physics performance of the experiment. The Level-0 trigger accept rate must be limited centrally, based on an emulation of the Level-0 derandomizer buffers. For such a scheme to work in a reliable way for a large system, it is required that the Level-0 pipelines and the Level-0 derandomizers work in perfect synchronisation across the whole experiment. Otherwise one would have to reduce the Level-0 trigger rate significantly, to insure that no buffers overflow in any part of the electronics, or build a very large and fast signalling network which could throttle the Level-0 trigger, when any electronics buffer risk to overflow.

The LHCb TFC system, based on TTC (Timing and Trigger Control) system [12] is used for the distribution of all time critical signals. The use of a common system for this ensures that the control of the different sub-detector electronics implementations have a unified interface with a predictable behaviour. The Readout Supervisor, that receives trigger decisions from the trigger systems, drives the TFC system. The Readout Supervisor (RS) is responsible for preventing buffer overflows in the LHCb electronics and DAQ systems. During testing, debugging and special calibrations each sub-detector is driven from a separate Readout Supervisor via the partitioning system of the TFC. During normal physics running all sub-detectors are driven from one common central Readout Supervisor.

In the large and complex electronics system, consisting of several completely different implementations for different sub-detectors, it is also important to define a set of error checking and monitoring features. These kinds of functions are vital to insure that data collected from the experiment can be considered correct, with a sufficient confidence level, when working in a hostile environment (radiation). The control, monitoring, and verification of the LHCb electronics is performed by the LHCb ECS [13]. The global ECS system will communicate with the LHCb electronics via the ECS interfaces. The ECS interface to the electronics has been standardized, to insure a consistent control and monitoring system.

The Level-0 electronics is in general located very close to the detector, either inside the sub-detector itself or on its close periphery. Electronics located inside a sub-detector can only be accessed for service or repair during the long shutdown periods of the LHC machine once per year (may in exceptional cases be accessed to perform limited repairs). Electronics located outside the detector can be accessed on a regular basis for simple repairs and service. If standard commercial components are used in the Level-0 electronics, it must be located in places with low radiation levels (less than 10 krad total dose during 10 years) and the system must be verified to work correctly after realistic radiation doses. In locations with higher radiation levels special radiation hard/tolerant components must be used which have been qualified with appropriate procedures. Integrated circuits must be verified to be immune to single event latch-up (possibly destructive) in the given application.

The effects of Single Event Upsets (SEU) on the reliability of the electronics must be evaluated and the detection and recovery from such failures must be considered. The specific problems related to SEU effects on configuration data in FPGA's must be shown to be at an acceptable level. Especially the ECS interface of the Level-0 electronics must be shown to be immune to lockup states caused by SEU, as this interface is the only path available to recover normal functionality.

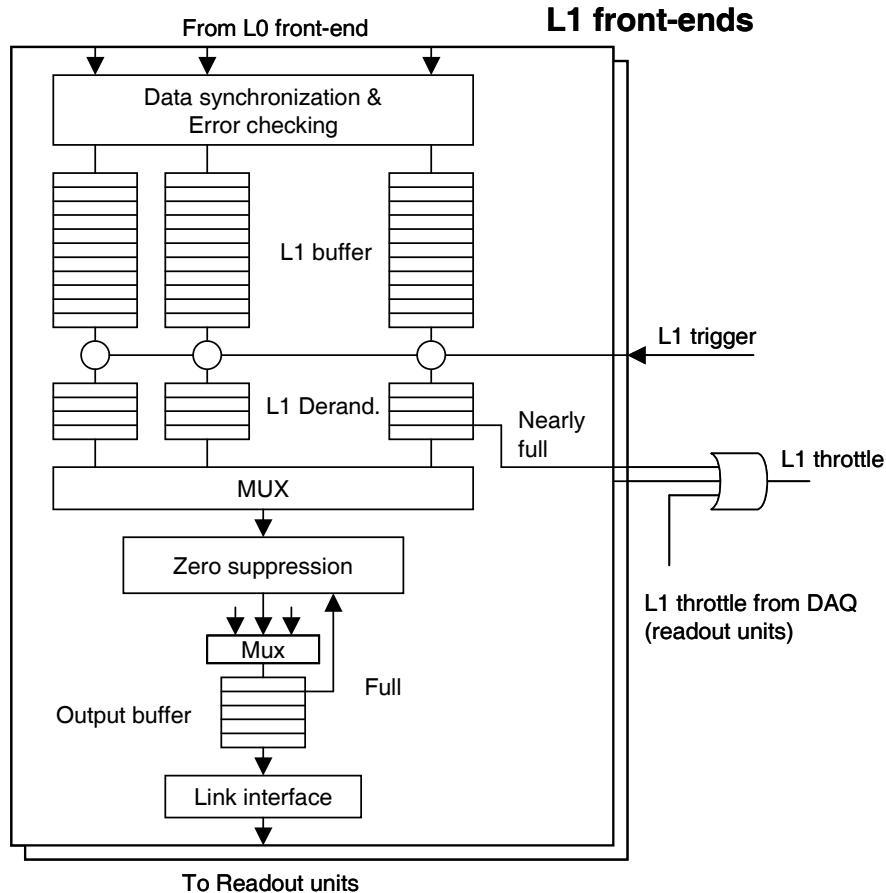

## 2.2 Level-1 electronics

The Level-1 electronics [14] is defined as the last stage of the sub-detector specific electronics, before data is sent to the common DAQ system. The general architecture of the Level-1 electronics is based on extensive simulation. The physical implementation of this architecture for different sub-detectors may look quite different, as long as it conforms to the defined requirements.

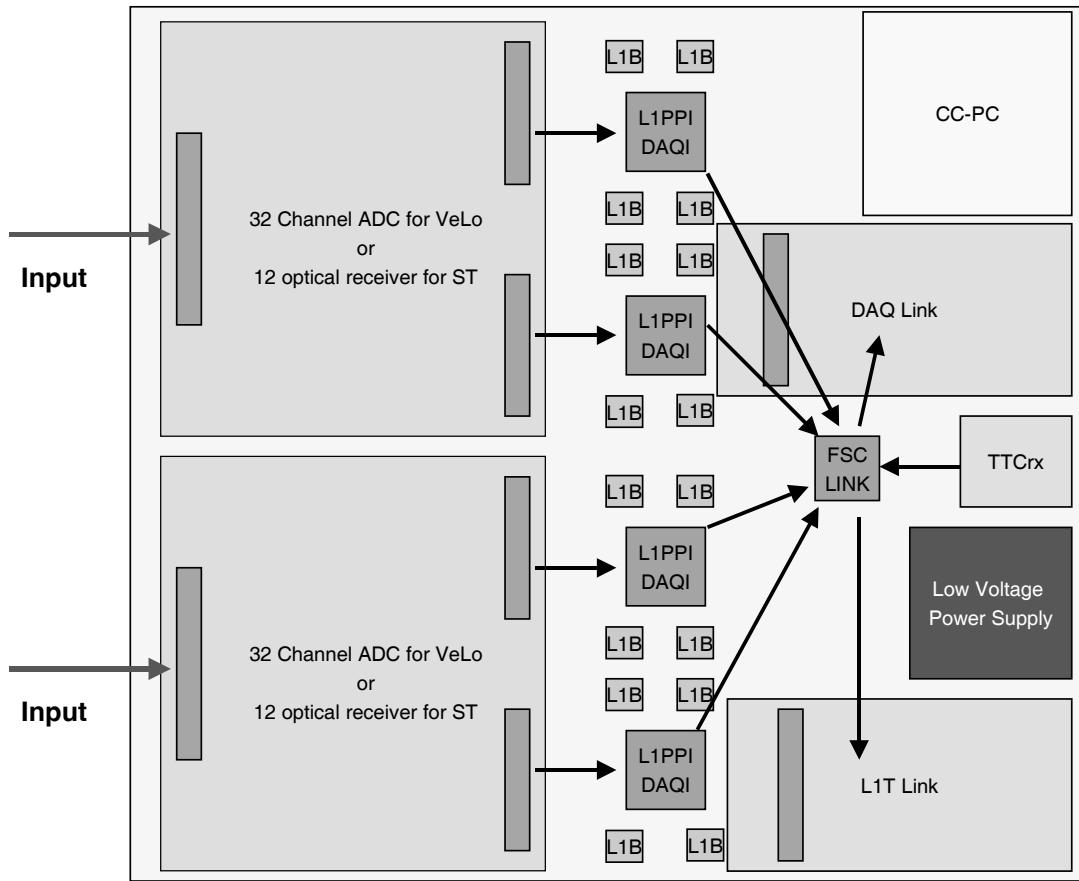

**Figure 5** General architecture of the Level-1 electronics (from [14]).

Event data, accepted by the Level-0 trigger, is received from the Level-0 electronics on a set of sub-detector specific links (or internal data buses in the case the Level-0 and Level-1 electronics are housed on same board). If data have not yet been digitised, it must be converted into a proper digital format, as sensitive analogue data cannot be stored reliably during the relatively long Level-1 trigger latency. The data is stored in the Level-1 buffers, waiting for the Level-1 trigger decision to be distributed to the Level-1 electronics via the TFC system. Events accepted by the Level-1 trigger must be extracted from the Level-1 buffer, derandomized in the Level-1 derandomizer, zero-suppressed and finally formatted to be sent to the DAQ system on standardized (optical) links. In the DAQ system, event data is not assumed to be preprocessed before it arrives in the CPU's of the Level-2/Level-3 trigger processor farm, therefore, all sub-detector specific processing of detector data must be performed in the Level-1 electronics.

Buffers overflow prevention in the Level-1 electronics is made as a combination of central control and a hardwired Level-1 throttle signal. The Level-1 buffer occupancy is controlled and monitored centrally in the Readout Supervisor based on a set of strictly defined parameters. The Level-1 derandomizer overflow after the Level-1 accept are prevented by a hardwired Level-1 throttle signal, as local Level-1 derandomizer occupancies can not be predicted centrally when event data have been zero-suppressed. The Level-1 derandomizer handles the delay of the Level-1 throttle signal, and following data buffers are assumed to back-propagate their full status to the Level-1 derandomizer.

The ECS interface is needed to configure and initialize the Level-1 electronics before data taking. It is also vital for efficient monitoring of the correct function of the Level-1 electronics modules during data taking. A high level of controllability and observability of the modules will be required to perform efficient testing and debugging of the electronics during commissioning and debugging. As the ECS interface is the only path to control and monitor the Level-0 electronics it must have high reliability and it must be insured that it cannot get into a deadlock state where the control of the module is lost. The ECS interface must be capable of recovering the normal function of a module without the need of powering off and powering on the module.

## 2.3 Trigger system

The 25 ns bunch spacing at LHC implies that the pipeline of the Level-0 electronics will have to be clocked at 40 MHz. However, some of the bunch crossings in LHCb will involve empty bunches, reducing the bunch crossing rate to an effective average value of 30 MHz.

At high luminosity, several proton-proton interactions are expected in a single bunch crossing. However, LHCb is planning to reach its physics goal using only events with single interactions. This is motivated by radiation damage, detector occupancy, pattern recognition flavour tagging and trigger issues. The detector

will therefore be operated at a modest luminosity of  $2 \times 10^{32} \text{ cm}^{-2}\text{s}^{-1}$ , (the beams will be defocused at the LHCb interaction point as the LHC machine gradually delivers its design luminosity of  $10^{34} \text{ cm}^{-2}\text{s}^{-1}$  to ATLAS and CMS). Under these conditions and assuming an inelastic cross section of 80 mb, 30% (10%) of the bunch crossings will have one (more than one) proton-proton interaction. In addition, a pile-up veto system is foreseen at the earliest trigger level to reject events with more than one interaction vertex, from the information provided by two dedicated silicon stations located upstream of the VELO detector. After this cut, the event rate is around 10 MHz with more than 90% single interactions.

The trigger scheme [15] will be implemented in four levels to selectively extract the B decays of interest while rejecting the non-b events. The lower level triggers (Level-0 and Level-1) will aim at rejecting non-b events. They will merely rely on two main features of the b-hadron decays: long lifetimes and significant transverse momentum release due to the high b-quark mass. The higher level triggers (Level 2 and 3) will consist of software algorithms running on farms of commercial computers and select specific  $b\bar{b}$  events channels.

### Level-0 Trigger

The first level of trigger, based on calorimeter and muon chamber information only, will reduce the event rate to 1 MHz by requiring a muon, an electron or a hadron with a transverse momentum ( $p_T$ ) or energy ( $E_T$ ) above some threshold, typically 1, 2.4 and 3.4 GeV respectively: tracks from b-hadron decays have indeed a harder  $p_T$  spectrum than tracks from non-b events. The fraction of the bandwidth attributed to the muon, electron and hadron triggers have been chosen to maximize the overall CP reach and will approximately be 20%, 10% and 60% respectively, the rest being allocated to other triggers (high  $E_T$  photon, dimuon, etc.). The Level-0 decision will take 4  $\mu\text{s}$  during which the data will be kept in the pipeline of the Level-0 electronics.

### Level-1 Trigger

The Level-1 trigger achieves a further reduction in rate by a factor of 25. It uses vertex detector information to identify secondary vertices produced by the b-hadron decays. Tracks are found from the hits in the VELO detector and a primary vertex is reconstructed. Secondary vertices are then formed with large impact parameter tracks. The Level-1 buffer will reside in the Level-1 electronics; its depth will allow for a maximum latency of the Level-1 trigger of 1.7 ms. After a Level-1 trigger accept, the zero-suppressed data are transferred to the data acquisition system and the full event data are available to the high level software triggers.

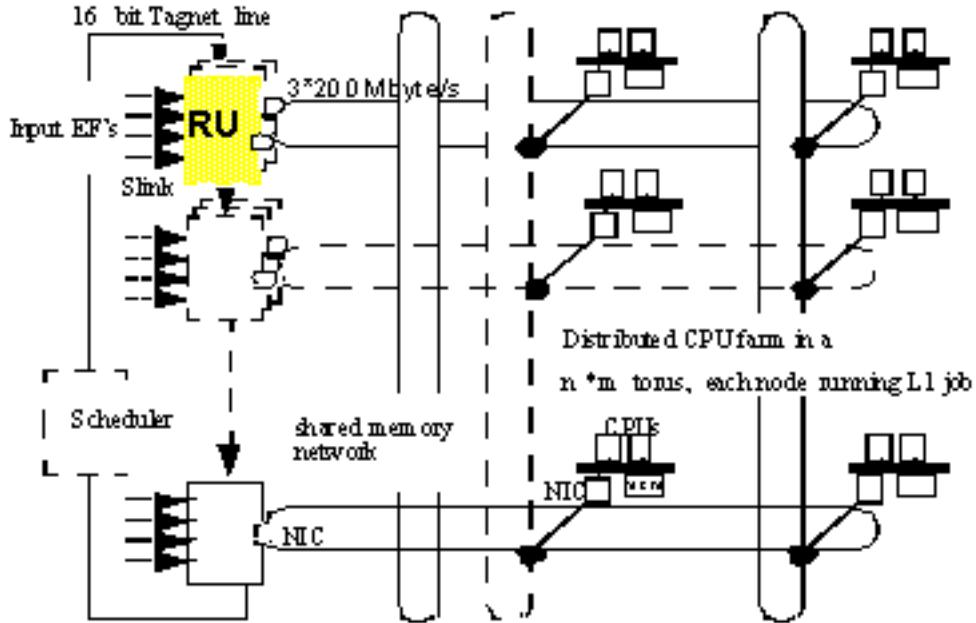

The overall layout of the Level-1 trigger system [16] is shown on Figure 6. It's a farm of processors connected by a low latency, shared memory network [17]. A two-dimensional torus network with distributed CPUs in the intersections is used. The torus is implemented as horizontal and vertical Scalable Coherent Interface (SCI) ringlets of 800 Mbyte/s bandwidth each [18]. The network congestion is avoided by destination address allocation and traffic scheduling.

Figure 6 Level-1 trigger system layout.

### High Level Triggers

Some secondary vertices found at Level-1 are fake due to low momentum tracks undergoing multiple scattering. The aim of the Level-2 trigger is to reconstruct large impact parameter tracks in the VELO and the first tracking chambers and use the momentum information to refine the secondary vertex requirement.

At Level-3, specific b-hadron decay modes will be reconstructed and selected with loose cuts using all available information. Approximately 200 events per second will be written to tape at a rate of 20 Mbytes/s.

## 2.4 Data acquisition system

The LHCb DAQ system [19] collects zero-suppressed data, belonging to one event, from the Level-1 electronics and assemble them in one CPU for execution of the high level trigger algorithms. It will have to cope with an average trigger rate of  $\sim 40$  kHz, after two levels of hardware triggers, and an average event size of  $\sim 150$  kB. Thus an event-building network which can sustain an average bandwidth of 6 GB/s is required. A powerful software trigger farm will have to be installed to reduce the rate from the 40 kHz to  $\sim 200$  Hz of events written to permanent storage.

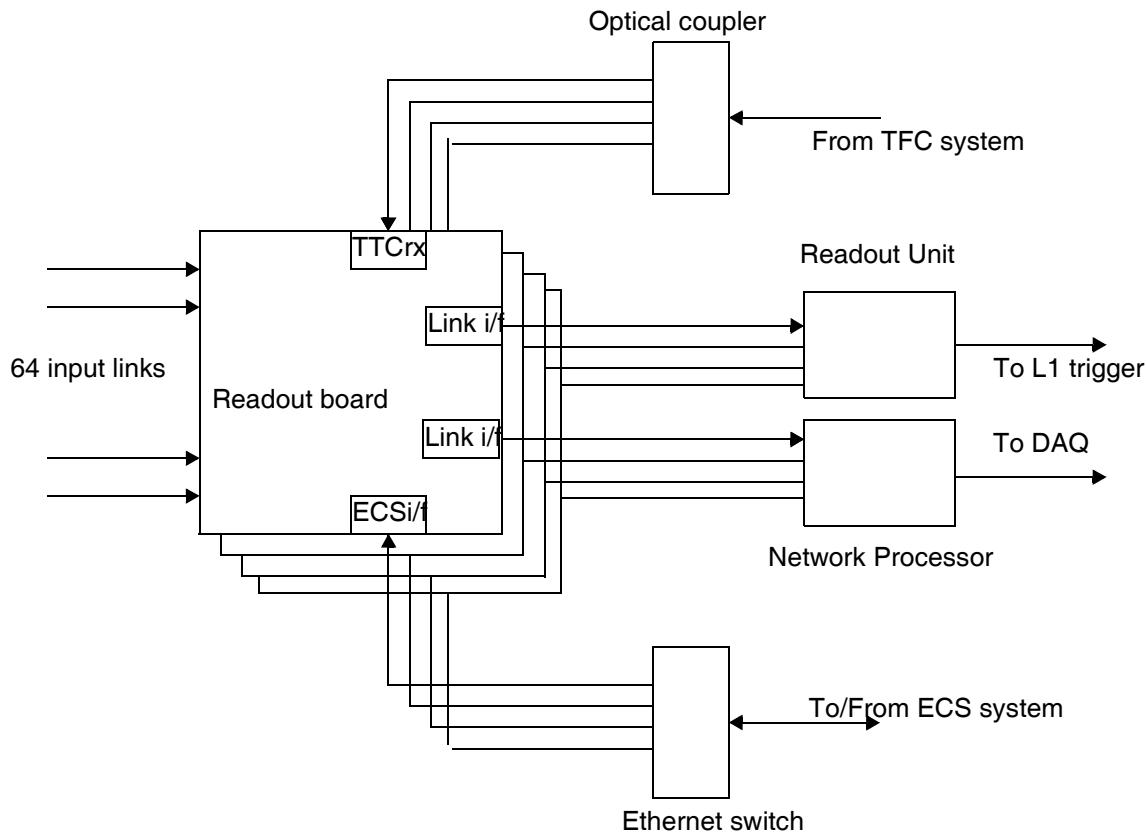

A overall architecture of LHCb electronics, trigger, DAQ and control systems is shown on Figure 7.

**Figure 7** Trigger and DAQ architecture (from [19]).

The main functional components of the LHCb DAQ system are:

- The Readout Units (RU) acting as a multiplexer of Level-0 links and as a interface to the Readout Network (RN). The same basic module is used as interface to the Readout Network and also as a Level-0 Multiplexer,

- The Readout Network (RN) which provides support for event-building, i.e. assembling all event fragments buffered in the RUs in one place,

- Sub-Farm Controllers (SFC) which act as an interface between the RN and the processor farm, which will run the higher-level triggers (Level-2 and Level-3),

- CPU farm to execute the higher level trigger algorithms (Level-2 and Level-3).

The purpose of the Level-0 Multiplexer (FEM) is to aggregate the data fragments originating from many Level-1 electronics boards and which have very low data rates into bigger fragments with the final aim of reducing the number of links into the Readout Network and/or making better use of the single link bandwidth. The functionality of the Readout Units is in the first instance the same as that for the FEMs (Multiplexing/Data Merging). In addition the RUs are connected to the Readout Network. The Readout Network can, for certain technologies, suspend the sending of data to it, and hence block the RUs. This can lead to congestion in the RUs, which in turn entails significant buffering requirements for the RUs. Another functionality of the RUs is related to network technology choices. If the technology of the links to the RUs is different from the technology of the Readout Network, the RUs must perform the necessary

'protocol translation' between the two technologies. In the terms of network language they act as a gateway between the two technologies. A third feature required of the RUs has to do with the event-building process. Unlike the FEMs the RUs can send their data to more than one destination through the Readout Network. The fragments of a given event-number, however, should arrive at only one destination. Hence the RUs have to support the destination assignment mechanism.

There are two main functional requirements imposed on the Readout Network (RN): to provide the connectivity between the RUs and the Sub-Farm Controllers, such that each RU can communicate to any Sub-Farm Controller and to provide the necessary bandwidth, such that all data arriving in the RUs can be sent to the Sub-Farm Controllers with only minimal packet loss.

The Sub-Farm Controllers (SFC) fulfils three functionalities. Firstly they perform the final event building, i.e. the concatenation of the event-fragments originating from the RUs to form a complete event. Secondly, they are supposed to isolate the Readout Network and its technology from the network technology within the sub-farm. Again, this is a gateway like function, as for the RUs, in network terms. Finally, the SFCs are supposed to exercise a load balancing function among the CPUs connected to each sub-farm. An event can spend a very long time in a CPU if it is accepted by the trigger algorithms and has to be reconstructed. A simple minded round-robin scheduling would lead to high buffer occupancies in the SFC and uneven load in the sub-farm nodes. The SFCs are also responsible for collecting the finally accepted and reconstructed data from the CPUs connected to them and to send these data to the storage controller also connected to the Readout Network.

The protocol applied for transferring the data from one stage to the next is a push protocol, which means that any module or stage that has data available for transfer will push them to the next higher stage immediately, under the condition that the output port is able to execute the transfer. There is no synchronisation or communication neither between components of the same level or between components of different levels. This protocol assumes that there is always enough buffer space available in the destination module to receive the data. Should buffer space get scarce traffic control has to be exercised. This is done through a throttle signal to the TFC system, specifically to the Readout Supervisor, which will inhibit the sending of new data from the Level-1 Electronics, by issuing Level-1 "No" decisions until the throttle signal is de-asserted.

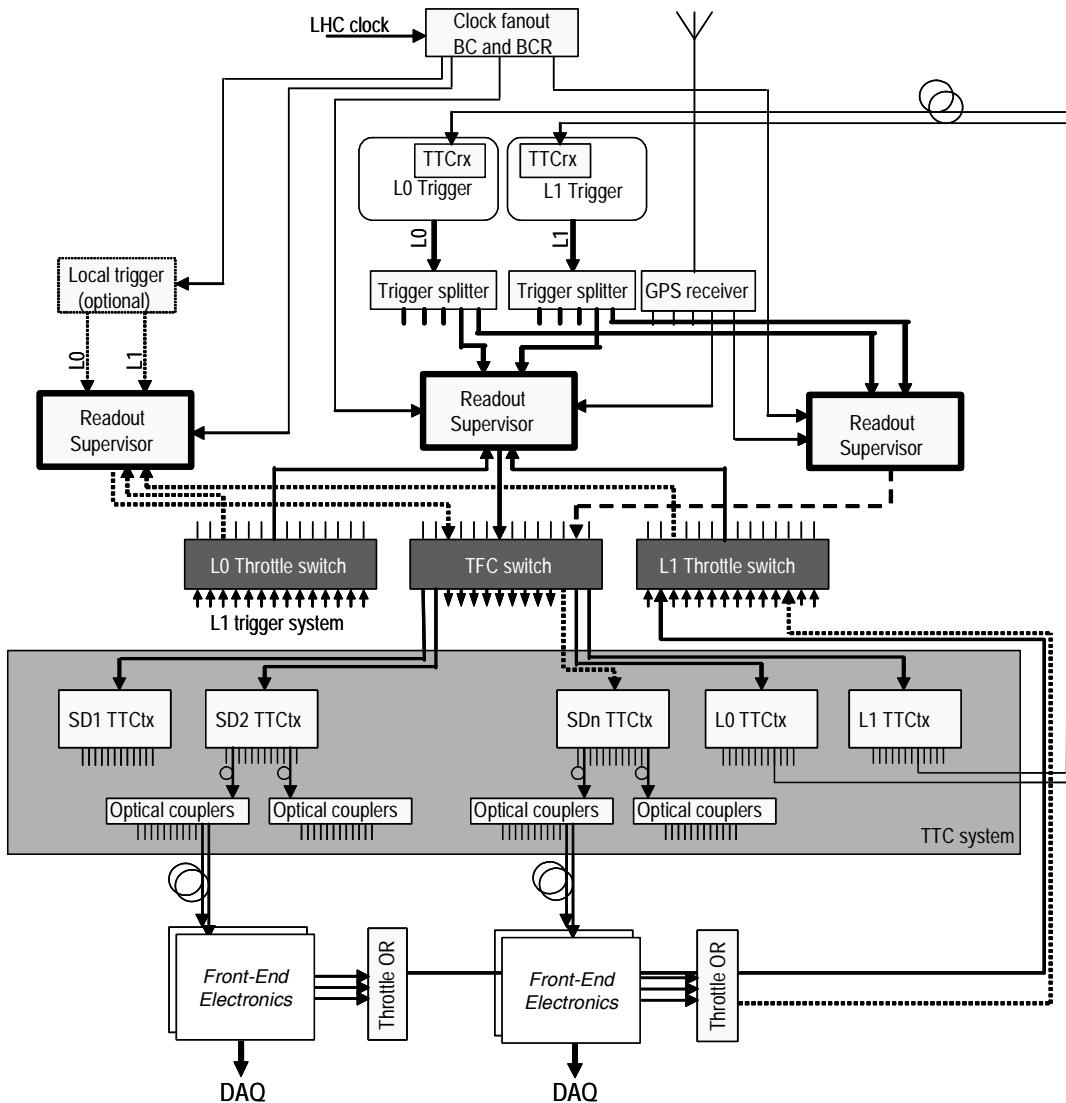

## 2.5 Timing and Fast Control system

The LHCb TFC system [20] distributes a common clock synchronous to the accelerator, the Level-0 and Level-1 decisions, resets and synchronization commands, bunch crossing number and event number to all components needing this information, such as Level-0/Level-1 electronics, trigger, etc.

Although the backbone of the timing, trigger and control distribution network is based on the CERN RD12 system (TTC), several components are specific to the LHCb experiment due to the fact that the LHCb trigger/DAQ system is different from that of the other experiments in several respects.

- The LHCb TFC system has to handle two levels of high-rate triggers: a Level-0 trigger with an accept rate of maximum 1.1 MHz and a Level-1 trigger with an accept rate of maximum 40-100 kHz.

- The TFC architecture has been designed with emphasis on partitioning. A partition is a configurable ensemble of parts of a sub-detector, an entire sub-detector or a combination of sub-detectors that can be run in parallel, independently and with a different timing, trigger and control configuration than any other partition.

Figure 8 TFC architecture (from [20]).

Furthermore, the aim has been to locate the entire TFC mastership of a partition in a single module. The trigger decision units are also considered as sub-detectors.

The TFC architecture is shown in Figure 8. It incorporates a pool of Readout Supervisors, one of which is interfaced to the central trigger decision units and is used for normal data taking. The other Readout Supervisors are reserves and can be invoked for tests, calibrations and debugging of individual sub-detectors.

The TFC Switch distributes the TFC information to the LHCb electronics and the Throttle Switches feed back hardware throttle signals from the Level-1 trigger system, the Level-1 derandomizers and components in the data-driven part of the DAQ system, to the appropriate Readout Supervisors. The Throttle ORs form a logical OR of the throttle signals from sets of LHCb electronics. A GPS system allows time-stamping the local event information sampled in the Readout Supervisor.

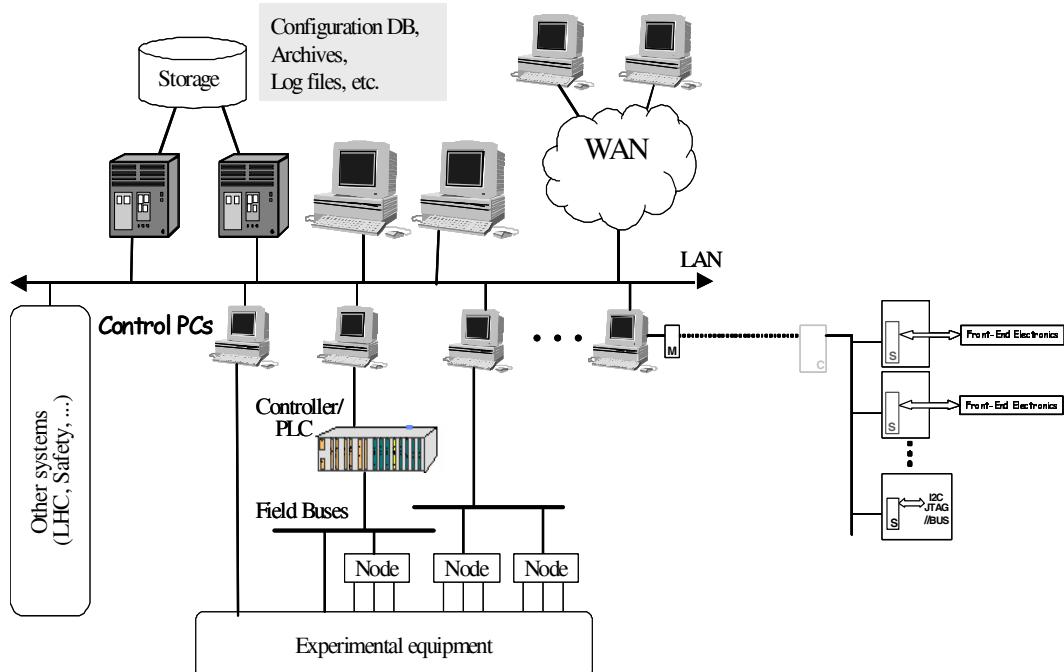

## 2.6 Experiment Control System

The LHCb Experiment Control System, shown on Figure 9, is in charge of the control and monitoring of all experimental equipment. As such, it has to provide interfaces to all types of devices in the experiment and a framework for the integration of these various devices into a coherent complete system.

Figure 9 ECS architecture (from [13]).

Each component of the system, be it a electronics board, a high voltage channel or a physics algorithm in the PC farm, will have to be initialized, configured and monitored for different activities or running modes.

The control framework was developed following the specification provided by the Joint Control Project at CERN and based on the PVSS II SCADA system. The framework offers tools to implement a hierarchical control system.

The ECS interface is needed to configure and initialize the LHCb electronics before data taking. It is also vital for efficient monitoring of the correct function of the LHCb electronics modules during data taking. To insure a homogenous ECS system it has been agreed to limit the number of different ECS interfaces to a minimum. Three different ECS interfaces have been identified as viable solutions. For applications in areas with no radiation (underground counting room and surface buildings) a commercial Ethernet interface based on a Credit-Card PC (CC-PC, [21]) has been found to be an attractive solution. The local intelligence of this CC-PC can be used for local monitoring and verification of the correct function of an electronics or DAQ module.

The CC-PC (Figure 10) contains and Intel Pentium compatible CPU, up to 64 MB of memory and outputs directly I2C, JTAG and the PCI bus, which can be easily converted into a simpler parallel bus. These CC-PCs will probably run Linux and will be booted remotely via the network.

**Figure 10** Credit-card PC.

In LHCb The CC-PCs will be used to provide the necessary local intelligence on an electronics board. They are connected to the central ECS via a conventional Ethernet and allow accessing the various components of the board.

## 3 VELO electronics development

### 3.1 VELO detector

Vertex reconstruction is a fundamental requirement for the LHCb experiment [10]. Displaced secondary vertices are a distinctive feature of b-hadron decays. The VErtex LLocator (VELO) has to provide precise measurements of track coordinates close to the interaction region. These are used to reconstruct production and decay vertices of beauty- and charm-hadrons, to provide an accurate measurement of their decay lifetimes, and to measure the impact parameter of particles used to tag their flavour. The VELO measurements are also a vital input to the Level-1 trigger, which enriches the b-decay content of the data. The VELO features a series of silicon stations placed along the beam direction. They are placed at a radial distance from the beam which is smaller than the aperture required by the LHC during injection and must therefore be retractable. This is achieved by mounting the detectors in a setup similar to Roman pot (Figure 11).

Figure 11 LHCb VELO detector.

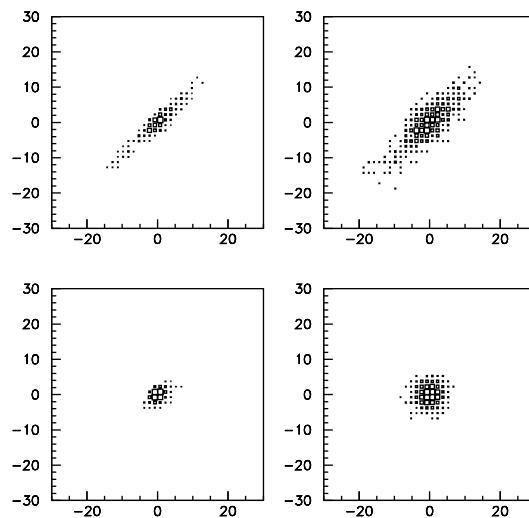

Special requirements emerge from the use of the VELO information in the Level-1 trigger. The Level-1 algorithm requires a fast and stand-alone three-dimensional pattern recognition to distinguish b-events from those minimum bias events which are accepted by the Level-0 trigger. B-hadrons that have all their decay products within the acceptance of the spectrometer are typically produced with a polar angle below 200 mrad. Hence, the projection of the impact parameter of the decay products to the primary vertex in the  $rz$ -plane is large, while in the plane perpendicular to the beam-axis ( $r\phi$ ) it is similar to that of tracks originating from the primary vertex. The Level-1 trigger exploits this by first reconstructing all tracks in the  $rz$ -projection, but reconstructing only tracks in three dimensions which have a significant  $rz$ -impact parameter. Hence, the strip pattern on the sensors has strips with constant radius for the  $rz$ -track reconstruction, combined with radial-strip sensors having a stereo angle of ( $10^\circ$ - $20^\circ$ ) to allow the two projections to be combined.

### 3.1.1 VELO implementation

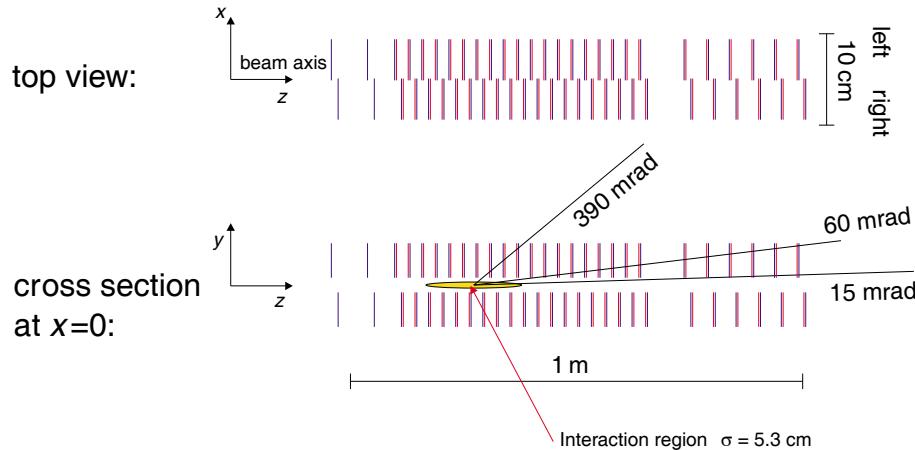

The VELO detector is composed of 25 (21 in “LHCb light”) parallel disk-shaped silicon strip detector stations as shown in Figure 12. To simplify the high impact parameter track search, the VELO is outside of the magnetic field (to have straight tracks) and measures the  $r$  and  $\phi$  coordinates. This geometry allows the identification of high impact parameter tracks using only the  $r$  coordinate.

**Figure 12** Arrangement of VELO sensors along beam axis.

The top figure shows the VELO setup seen from above, indicating the overlap between the left and right detector halves.

The bottom figure is a cross section of the setup at  $x = 0$  along the beam axis showing also the nominal position of the interaction area. The three lines indicate the maximum and minimum angular coverage of the VELO and the average angle of tracks in minimum bias events respectively.

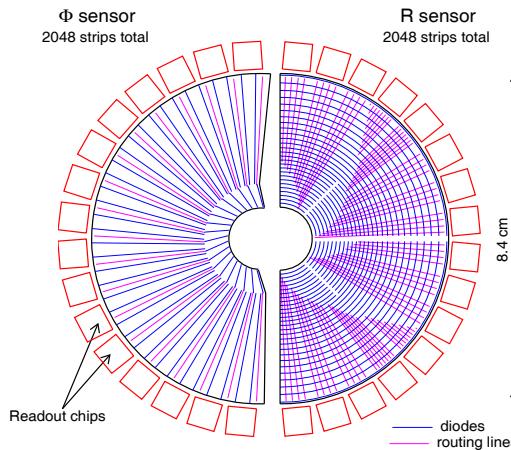

The silicon sensors have a circular shape, patterned with azimuthal ( $r$  measuring) or quasi-radial ( $\phi$  measuring) strips, and span  $182^\circ$ . These views have been chosen in order to optimize the stand-alone tracking performance for the Level-1 trigger. By using a double metal layer, it is possible to decouple the routing of the signals from the strip geometry and to move the electronics as far as possible out of the acceptance. The innermost radius of the sensitive area is 8 mm and the outermost radius is approximately 42 mm.

The concept of the strip layout is illustrated in Figure 13. The strips in the  $\phi$ -sensor are split into an inner and an outer region, chosen to equalize the occupancy in the two regions. The detectors are flipped from station to station, and the strips are tilted with a stereo angle, which is different in sign and magnitude for the inner and outer region. This results in a dog-leg shape, which minimizes the depth of the corrugations needed in the RF shield to accommodate the shape. The strips in the  $r$ -sensor are segmented into 4 (2) azimuthal sections in the inner (outer) regions. With this design it is possible to determine the primary vertex position in the plane perpendicular to the beam using the  $R$ -sensors alone, which is an important input to the Level-1 trigger. The pitch varies with radius, striking a balance between making the occupancy as uniform as possible, and ensuring that the first two points on the track are measured with the finest pitch available.

**Figure 13** Schematic view of a  $r$ - and  $\phi$ -measuring sensor.

The number of detector strips per sensor is kept as 2048. This leads to  $16 \times 128$  channels Level-0 chips (see 3.2.1) per sensor which fit at a maximum sensor radius.

The VELO module provides the mechanical infrastructure to support the sensors rigidly, stably and in a known position. It acts as the base on which the electronic components for the sensor can be mounted. It also allows the removal of heat from the Level-0 chips and sensors. The key components of the module are: 2 silicon sensors, the Level-0 chips, mounted on a hybrid and the module support

with the cooling pipes. The module is designed to allow the precision alignment of the sensors relative to the platform on which all modules are mounted. A large vacuum vessel, supported by a concrete stand, encloses the complete detector array and support frames.

### 3.1.2 VELO experimental environment

The design of the VELO system, including VELO electronics, is constrained by its proximity to the LHC beams and its integration into the LHCb experiment. In the design of the VELO, the following boundary conditions are imposed:

- The need for shielding against RF pick-up from the LHC beams, and the need to protect the LHC vacuum from outgassing of the detector modules, requires a protection to be placed around the detector modules.

- The space, available around the VELO detector and radiation levels in the VELO location constrain the VELO Level-0 and Level-1 electronics implementation.

- Cooling of the detector modules is required since the sensors are operated in a high radiation environment. Harsh radiation environment also lead to the silicon sensor efficiency degradation and the sensors have to be replaced every three year. To allow for a replacement of the sensors in case of radiation damage, access has to be rather simple.

- The number of analog channels in the VELO is limited to about 200K channels. In particular, this is due to the limited space for the vacuum feedthroughs on the VELO vacuum vessel.

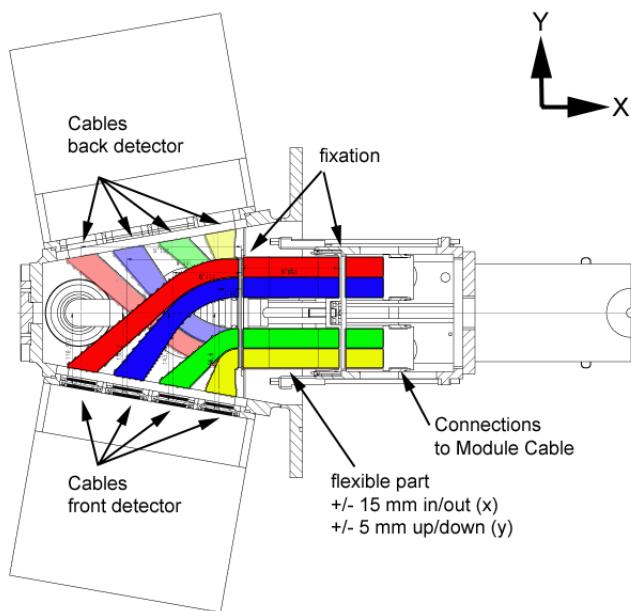

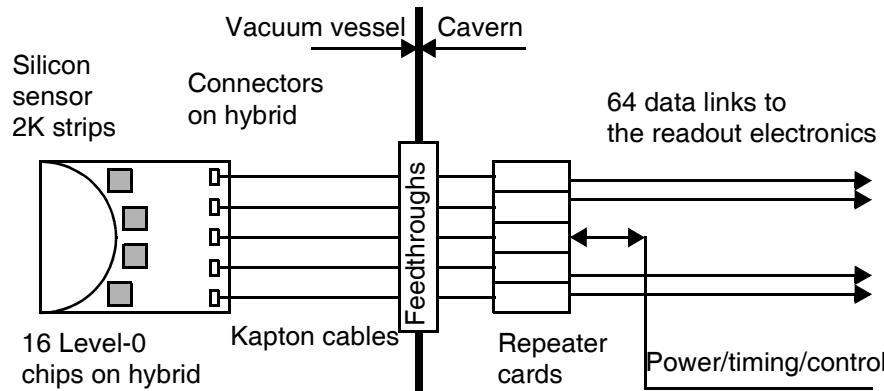

Figure 14 VELO cabling inside vacuum vessel.

Limited space around the vacuum vessel does not allow to place any Level-1 electronics close to the VELO detector. Radiation hard and flexible kapton flat cables transfer detector signals inside the vacuum vessel from the front-end chips on the VELO modules to the feedthroughs (Figure 14).

Outside of the vacuum vessel there are drivers for the signals from the front-end chips and receivers for the control signals. They are located on the repeater cards. Cables are traced from the VELO vicinity to the Level-1 electronics location.

Radiation levels in the LHCb cavern have been calculated with FLUKA99 [22]. The results are obtained for the experimental layout configuration shown in Figure 15.

**Figure 15** LHCb layout configuration for radiation levels study.

Material of all scoring volumes is silicon. In the cross-sections at  $X=0$  and  $X=200$  no special material is introduced. The dose is scored in the actual material of the detector present in each point of the scoring volume. The radiation level results have been divided into different categories to allow to use it to evaluate the possible effects on electronics. The three categories mentioned below is of particular use to define the radiation hardness requirements of electronics:

- Total ionizing dose is presented in units of Gy per collision.

- 1MeV neutron-equivalent fluence for silicon is used to define the level of damage to silicon lattice by hadrons (neutrons).

- High energy hadrons ( $E_k > 20\text{MeV}$ ): Used to evaluate rate of Single Event Upset (SEU) effects.

The presented radiation levels are without any safety factors for uncertainty of the Fluka simulation and the variability of radiation resistance of electronics. A total safety factor of the order of  $\sim 10$  must be used to define the requirements to electronics.

Results for the VELO detector area shows that radiation hard electronics must be used in the vicinity of the VELO both inside and outside of the vacuum vessel.

Location of the Level-1 electronics is constrained by the space available and the level of radiation in the experimental hall. Two possible locations are:

- In the experimental hall at the distance of about 10-15 m from the VELO vacuum vessel. Radiation level at this location may require radiation tolerant component for the Level-1 electronics (total dose effects are for most locations below 10 krad over the life time of the experiment, the effects of Single Event Upsets (SEU) must be considered seriously for complex electronics with large memory structures). However shorter cables may be used to transfer detector signals. Access to the electronics is also excluded during accelerator run and limited in time during the interruption (accessibility for an hour is expected to be granted with a 24 hour notice).

- In the underground counting room behind the massive concrete wall at the distance of about 40 m from the VELO. Radiation level in the counting room allows standard components to be used in the Level-1 electronics. This implementation requires longer cables which shall transport detector signals with losses under control. Access can be given at any time which simplifies maintenance during accelerator run.

In order to make a qualified decision about location of the Level-1 electronics for the VELO detector, several conditions have to be taken into account. They include, among others:

- feasibility to transfer detector signals over long cables without signal quality degradation at reasonable cost,

- qualification of the electronics components for the radiation levels and experience with the radiation tolerant electronics design techniques.

The positive result of the feasibility study of detector signals transfer gives a possibility to locate the VELO Level-1 electronics in the underground counting room and avoid the necessity of the radiation tolerant Level-1 electronics design and implementation. Otherwise a considerable efforts have to be put into qualification of the electronics components for the radiation levels and implementation of the Level-1 electronics using special radiation tolerant design techniques. Maintenance of the VELO Level-1 electronics also becomes more complicated.

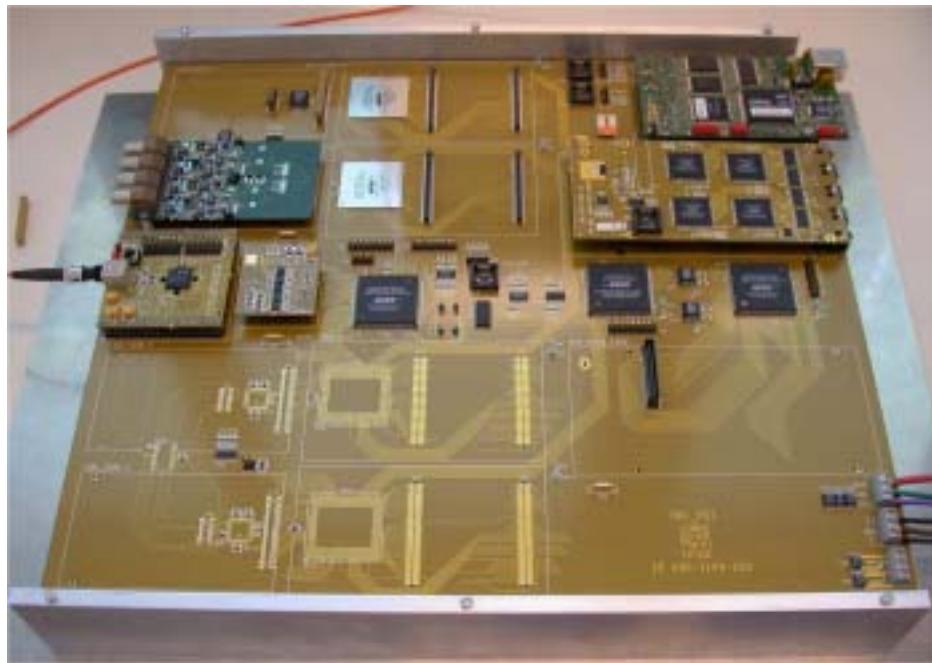

### 3.2 VELO Level-0 electronics

The VELO detector is located in the vacuum tank around LHCb interaction point. In the LHCb Technical Proposal it is divided in 25 stations, each station has 4 silicon sensors with 2K strips, 200K detector strips in total.

Each sensor is attached to the hybrid with 16 Level-0 chips, 1600 Level-0 chips in total. Detector strips are bonded to the pads on the Level-0 chips. Each Level-0 chip has 4 multiplexed analog outputs and timing/control interface.

**Figure 16** VELO Level-0 electronics layout.

Signals from connectors on the hybrid are transported via flexible kapton flat cables inside the vacuum vessel to the to the feedthroughs on the flanges of the vacuum vessel. Kapton cables are also used to distribute the low and high voltage power to the Level-0 chips on hybrids and to the silicon sensors.

Short cables between feedthroughs and connectors on the repeater cards isolates feedthroughs from mechanical stress during inserting and removal of the repeater cards.

“Digital” repeater cards (one card per hybrid, 100 cards in total) provide connection to the power supplies and to the timing and control systems. “Analog” repeater cards (4 cards per hybrid, 400 cards in total), located in the vicinity of the vacuum vessel contain drivers for the analog data links to the Level-1 electronics.

The analog data from the Level-0 chips has to be transmitted via electrical analog links (6400 links in total) to the read-out boards where they are converted to the digital data.

Therefore the main components of the VELO Level-0 electronics may be enumerated as following:

- 128-channel front-ens chips on the hybrid,

- Timing and control system interface for the VELO Level-0 electronics,

- Analog data links for the detector signals.

Following paragraphs describes in details individual components of the VELO Level-0 electronics.

### 3.2.1 Level-0 chips

VELO detector Level-0 electronics must conform to the overall LHCb Level-0 electronics and has to be radiation hard. Data from the VELO detector are used in the Level-1 trigger and in the data acquisition system.

Analog rather than binary front-end chip readout has been chosen since it provides a better hit resolution [23] and allows for better monitoring and control of effects due to the very non-uniform radiation damage to the silicon detectors. Detector readout lines are bonded to a front end chip which samples detector signals with the LHC bunch crossing frequency. The analog data have to be stored in the chip until a Level-0 trigger decision arrives and then are transferred to the VELO Level-1 electronics.

#### Requirements

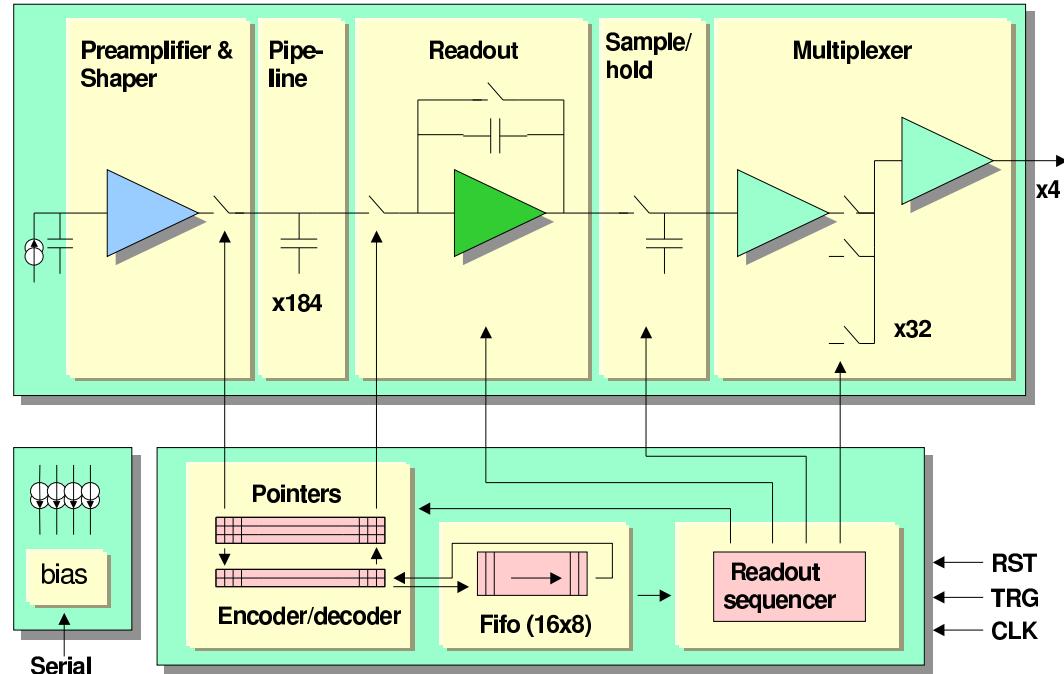

Requirements to the VELO Level-0 chip are specified in [24]. The dynamic range was chosen to correspond to 10 times the charge deposited by a minimum ionizing particle in 150  $\mu\text{m}$  silicon. The peaking time and sampling frequency is determined by the LHC bunch crossing rate of 40 MHz, the readout speed must match the Level-0 accept rate of 1 MHz. A signal to noise ratio (S/N)  $> 14$  is required for reliable operation of the silicon detector even after the irradiation. The radiation hardness must be such, that the chip withstand 5 years of operation at an estimated load of around 2 Mrad per year. The length of the pipeline is given by the 4  $\mu\text{s}$  latency of the Level-0 trigger decision plus the size of the derandomizing buffer, which has to be large enough to have negligible dead time at nominal operating conditions. A buffer depth of 16 events ensure that at readout speed of 900 ns per event and a Level-1 trigger rate of 1 MHz the remaining deadtime is below 1%.

The requirement about the tolerable signal left over after 25 ns (pulse spill-over) is derived from a study of the Level-1 trigger efficiency [23]. If the signals left over are too high, the Level-1 trigger starts to reconstruct tracks from the previous bunch crossing and assign them a large impact parameter. The output of the Level-1 trigger will then be saturated by fake b-events.

A single chip has 128 analog inputs. The data are brought off-chip at a clock frequency of 40 MHz, multiplexed to 4 lines. In addition every line transmits two samples of control information which code the pipeline location of the data that follows and thus allow to check the internal consistency of the data and the operation of the Level-0 electronics. With 34 bits of information per line and 40 MHz clock frequency the readout of one event is done in 850 ns. Additional functionalities of the chip are a programming via I<sup>2</sup>C-interface and internal pulse generation.

#### Level-0 chip design

Since a fast front-end readout chip satisfying the LHCb requirement was not available, it was decided to develop one within the collaboration.

Possible candidates to start from were the SCTA128 chip (built in the radiation hard silicon-on-insulator process [25]) developed for ATLAS and the HELIX chip (realized in a standard 0.8  $\mu\text{m}$  CMOS process with a radiation tolerant design) developed for the HERA-B experiment.

Both chips are based on the RD20 architecture [26] shown in Figure 17, which contains a low-noise charge-sensitive RC-CR preamplifier/shaper stage, an analog pipeline, a derandomizing buffer for triggered events and an output multiplexer.

In the meantime access became available to the 0.25  $\mu\text{m}$  CMOS technology, which can be made at least as radiation hard as the DMILL technology. To minimize the risk related to switching to a new technology, it was decided to pursue a dual approach:

- develop a new chip in 0.25  $\mu\text{m}$  CMOS technology (Beetle [27]),

- modify the existing SCTA128 chip such that it fulfils the requirements for the readout of LHCb (SCTA\_VEL0 [28]),

Figure 17 RD20 chip architecture.

R&D work towards the final Level-0 chip encompasses measurements with the existing SCTA128 chip, the predecessor of the SCTA\_VEL0, studies of test chips with components of the Beetle and results from the first prototype of the complete chip, the Beetle1.0.

### 3.2.2 Level-0 electronics control

Each silicon sensor of the VELO detector will be equipped with 16 analog Level-0 chips (Beetle or SCTA\_VEL0) residing on the hybrids inside the vacuum vessel. Radiation hard and flexible kapton flat cables transfer signals inside the vacuum vessel from/to the Level-0 chips to the feedthroughs. Outside of the vacuum vessel there are drivers for the analog signals from the Level-0 chips which are located on the “analog” repeater cards in the vicinity of the vacuum vessel.

For the proper operation, the Level-0 chips must be controlled by two LHCb systems - TFC and ECS. Receivers for the control signals are located on the separate repeater card (“digital”) in the vicinity of the vacuum vessel. “Digital” repeater cards also provides a connection to the low and high voltage power for the Level-0 chips on hybrids and for the silicon sensors.

All repeater cards are located on the flanges of the vacuum vessel using custom made mechanical support with short cables between feedthroughs and connectors on the repeater cards in order to isolate feedthroughs from mechanical stress during inserting and removal of the repeater cards.

#### 3.2.2.1 Timing and Fast Control system interface

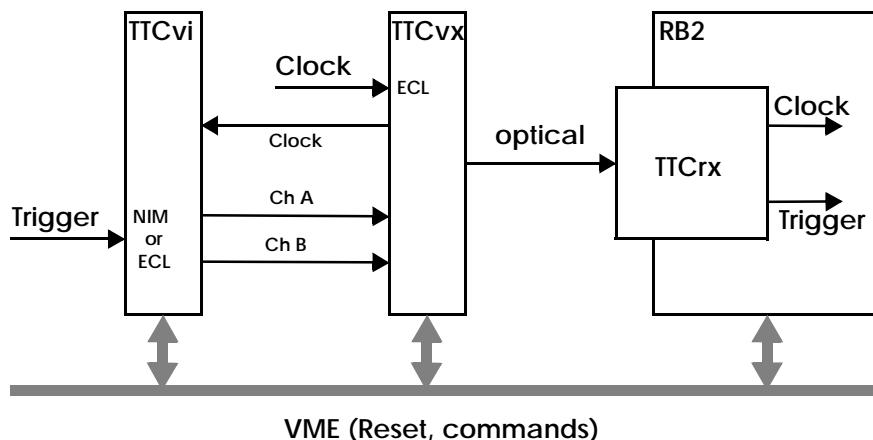

The TFC system is used for the distribution of all time critical signals to the Level-0 (a common clock synchronous to the accelerator, the Level-0 and Level-1 decisions, resets and synchronization commands, bunch crossing number and event number to all components needing this information, such as Level-0/Level-1 electronics, trigger, etc.) via optical distribution network tree (see Figure 8).

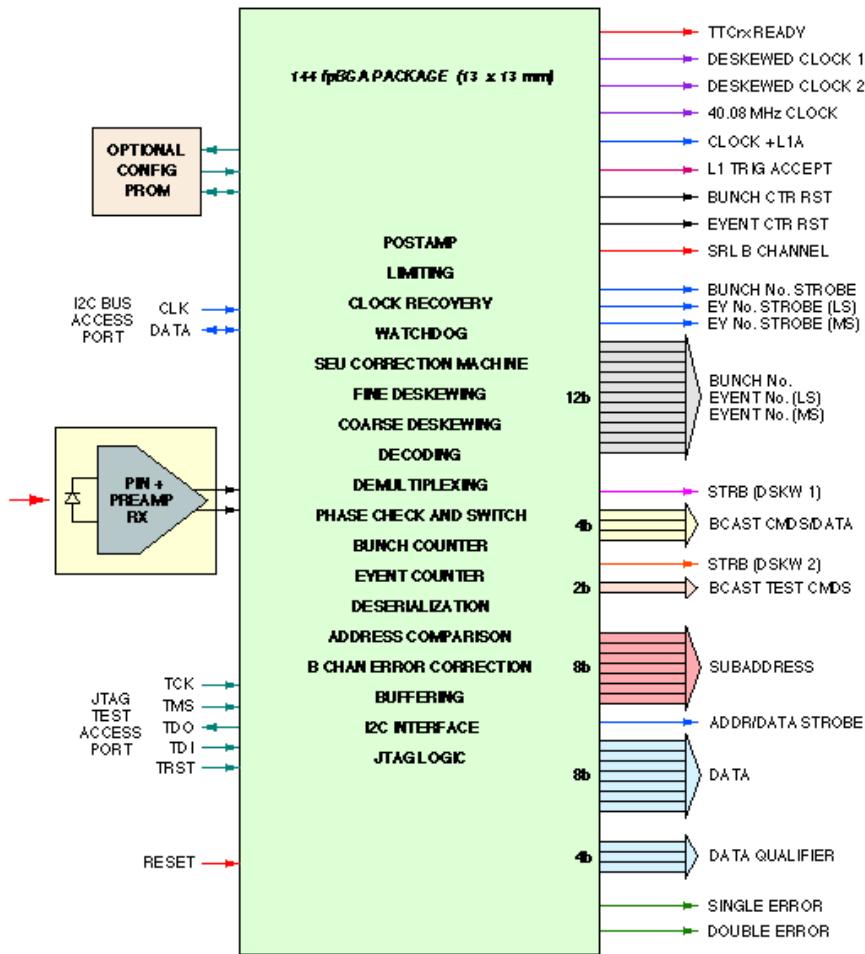

For their operation, Level-0 chips require three signals: 40 MHz clock, Level-0 decision and reset. They are delivered by the TTCrx receiver ASIC [29], developed by the CERN Microelectronics Group. It recovers 40.08 MHz LHC reference clock from the input optical signal and provides the Level-0 trigger decision (L1Accept output of the TTCrx chip), which can be delayed in steps of 25 ns (one clock cycle) up to 15 clock cycles. In the LHCb environment TTCrx 8-bit broadcast command is used to distribute reset to the Level-0 electronics.

Access to the internal registers of the TTCrx chip is provided by the I2C interface on the chip. The TTCrx chip contains a total of 20 user-accessible 8-bit registers.

TTCrx chip is located on the “digital” repeater card and is connected via optical fibre to the optical coupler (optical splitter). The TTCrx chip will be controlled in the same way as the Level-0 chips on the hybrid from the VELO Level-0 control system using I2C interface on the TTCrx chip.

Figure 18 TTCrx receiver ASIC.

### 3.2.2.2 Experiment Control System interface

The control, monitoring, and verification of the Level-0 electronics is performed by the ECS that communicates with the Level-0 electronics via the ECS interfaces. In LHCb the ECS interface to the Level-0 electronics has been standardized, to insure a consistent and well functioning control and monitoring system. The Serial Protocol for Experiment Control System (SPECS) derived from the SPAC bus (Serial Protocol for Argon Calorimeter [30]) has been chosen as the preferred solution for the interface between the Level-0 electronics and the ECS. The chosen system for programming and reading the registers of the Level-0 electronics provides interfaces to both I2C and JTAG which is important as two options exist for a VELO Level-0 chip: Beetle chip uses the I2C interface protocol and the SCTA\_VEL0 chip uses a reduced JTAG interface protocol. The last is identical on the hardware level to standard JTAG thus the modified protocol can be implemented in software.

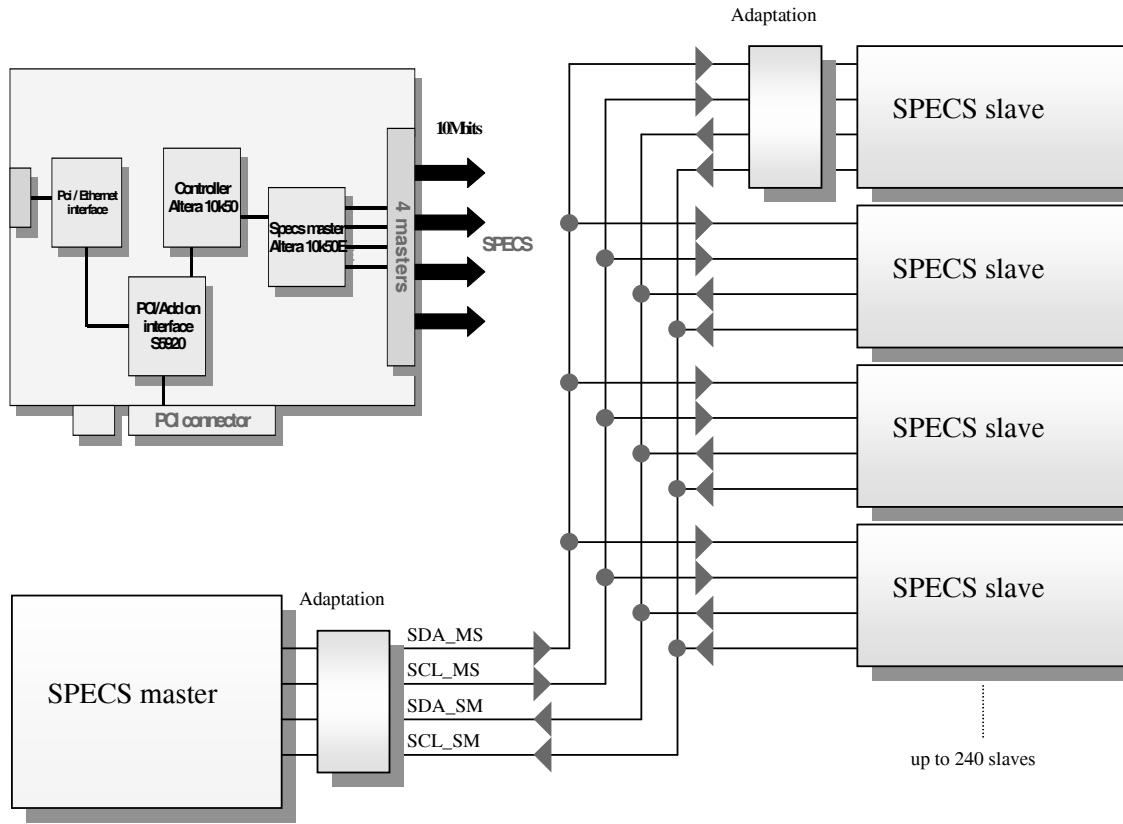

**Figure 19** SPECS bus.

SPECS is a one-master n-slaves bus (Figure 19) where the master is implemented in a PCI board located in a PC in the counting room. The SPECS master board provides up to 4 output SPECS buses. The SPECS bus is fast (100 Mbit/s) and works up to 100 m using cheap AWG26 Cat5 cables. Up to 240 slaves can be connected to one SPECS bus.

The slave boards are located in the cavern, close to the detector. The slave board acts as a SPECS to the Level-0 electronics transceivers and contain four SPECS slaves, each provides four differential I2C and JTAG buses either directly or via an active bus splitter. A total length of about 10 m can be realized for I2C and JTAG interfaces, hence the slave board may be located at a distance where the radiation dose is below 100 Rad/year and therefore may be radiation tolerant, for example, implemented in an Actel FPGA with SEU tolerant antifuse technology.

The number of Level-0 chips connected to a single bus is only limited by the 7 bit I2C/JTAG address scheme. For both I2C and JTAG, all chips on a hybrid will be connected to a single bus from SPECS slave. Thus the Velo Level-0 control system has to provide 100 I2C/JTAG buses, one for each hybrid.

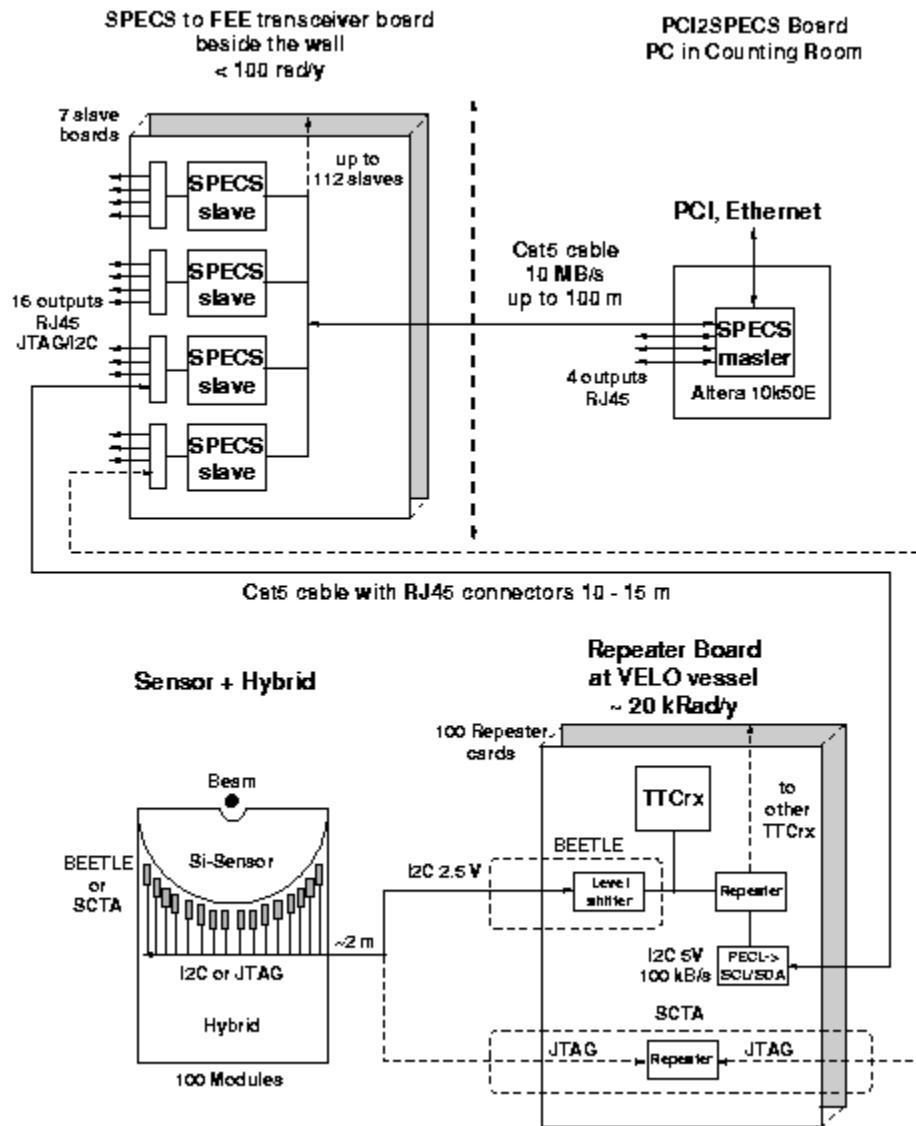

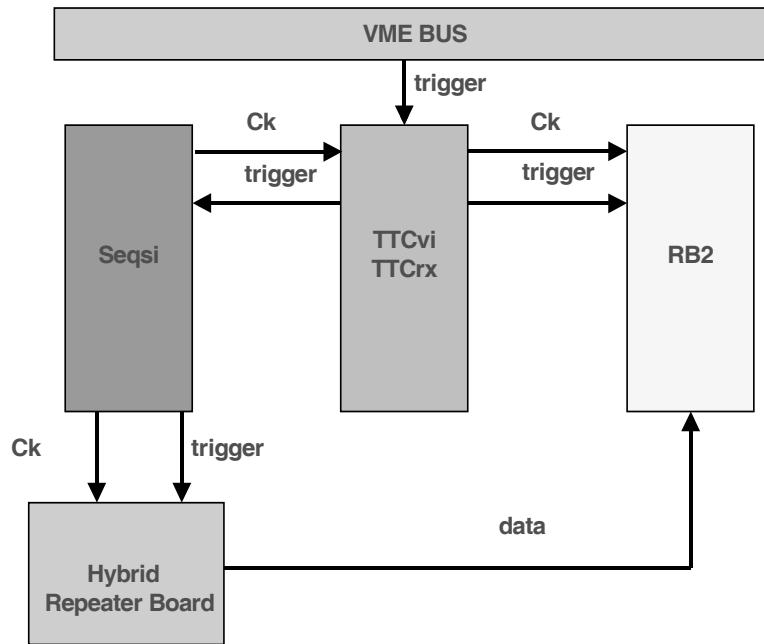

### 3.2.2.3 Digital repeater card and overall timing/control layout

The overall timing and control layout for the VELO Level-0 electronics is described in [31] and shown on Figure 20.

Figure 20 VELO Level-0 electronics control (from [31]).

One SPECS slave board provides up to 16 I2C/JTAG buses, therefore, 7 slave boards, located in a single crate, are sufficient to connect all 100 “digital” repeated cards to the SPECS bus. As the SPECS bus can be distributed in the crate via the backplane, only one link is needed to connect the crate to the SPECS master located in the counting room. “Digital” repeater cards (one card per hybrid, 100 cards in total), which are located on the flanges of the vacuum vessel, provide connection to the timing and control systems. Each “digital” repeater card contains:

- One TTCrx chip which receives timing and fast control signals via optical fibre from the TFC system. The output signals (40 MHz clock, reset and Level-0 decision) are converted to 2.5V LVDS signals and are transferred to the Level-0 chips on the hybrid. The TTCrx chip is controlled in the same way as the Level-0 chips on the hybrid via I2C interface.

- I2C/JTAG bus receivers which converts the differential I2C/JTAG signals to the standard 2 wire bidirectional bus. They are connected to the SPECS slave on the slave board, located at the distance of about 10-15 m from the vacuum vessel,

- power connectors for high and low voltage.

### 3.2.3 Analog data link

The front end chip samples detector signals with the LHC bunch crossing frequency of 40 MHz. The analog data have to be stored in the chip until a Level-0 trigger decision arrives and then are transferred to the VELO Level-1 electronics. A single chip has 128 analog inputs which are multiplexed to 4 lines at a clock frequency of 40 MHz. 32 samples of the analog data (charge released in the silicon and encoded as a voltage level) plus two samples of control information (constant voltage levels) are sequentially sent out of the Level-0 chip via kapton cable to the feedthroughs and then to the “analog” repeater card.

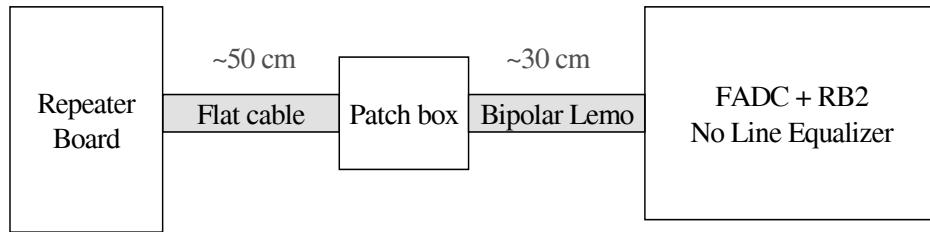

#### 3.2.3.1 Link requirements and implementation options

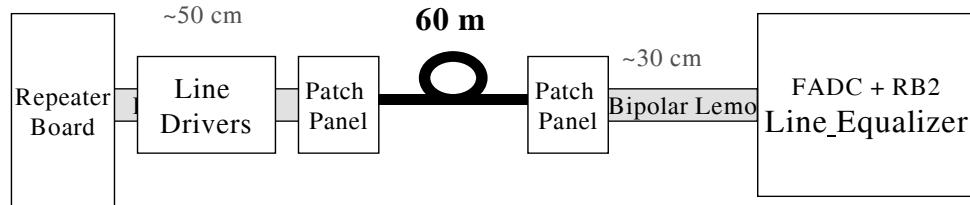

The analog data from the Level-0 chips has to be transmitted to the read-out boards. A preferred location of the VELO Level-1 electronics is in the underground counting room behind the massive concrete wall at the distance of about 40 m from the VELO detector where radiation level allows to use standard components.

The definition of the analog data link includes all link components starting from the link drivers on the “analog” repeater card, connectors, cables, receivers, up to the digital output of the link inside the Level-1 electronics. The requirements to the link between the Level-0 and the Level-1 electronics are:

- a minimal distortion of the analog data during transmission over long cable due to a sample-to-sample crosstalk (<5%) and a signal attenuation,

- a minimal degradation of the signal to noise (S/N) ratio at the receiving end of the link (10%),

- low sensitivity to the electromagnetic radiation (noise),

- 8-bit digital output data at the receiving end,

- link implementation matching the Level-1 electronics granularity - 32 or 64 analog links per Level-1 board (in order to avoid an extra cost overhead).

Several possible implementation options has been taken into consideration [32]. They are differ by their parameters and cost.

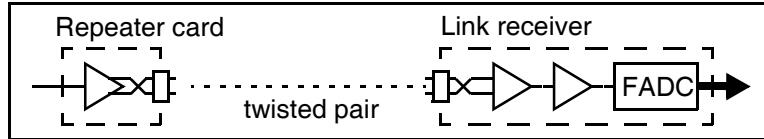

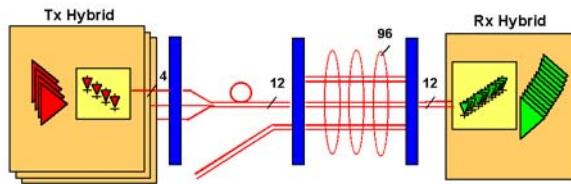

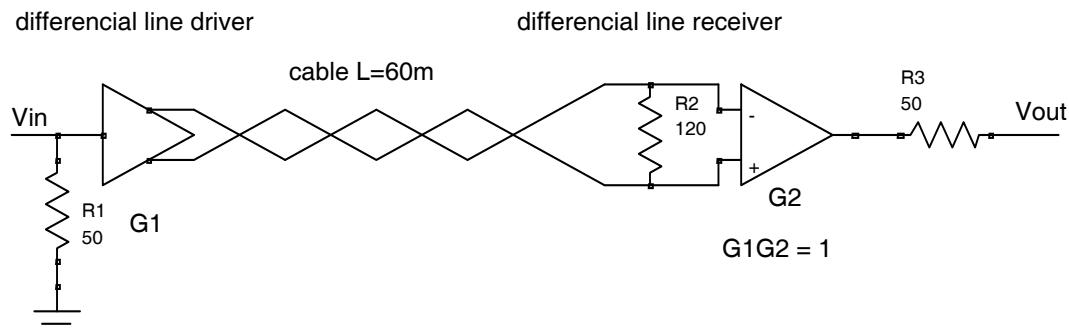

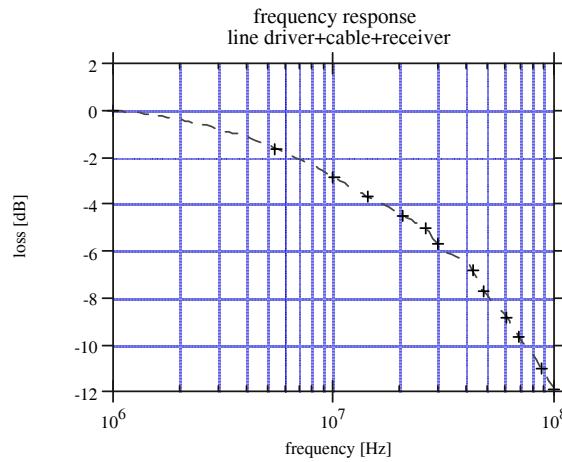

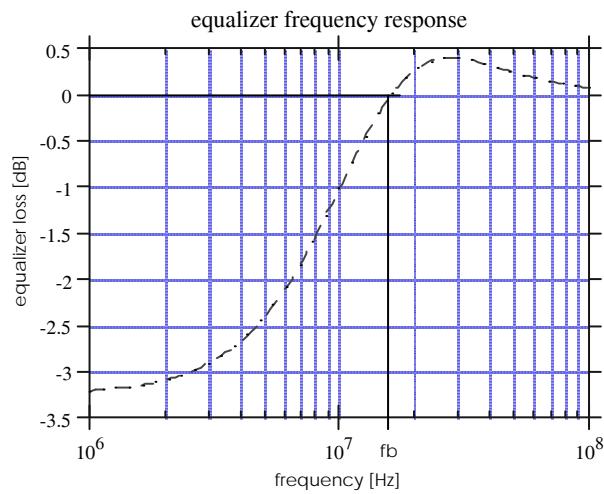

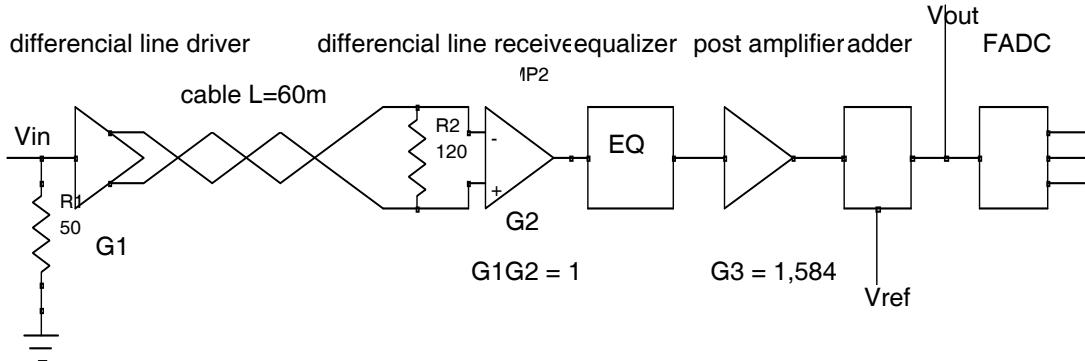

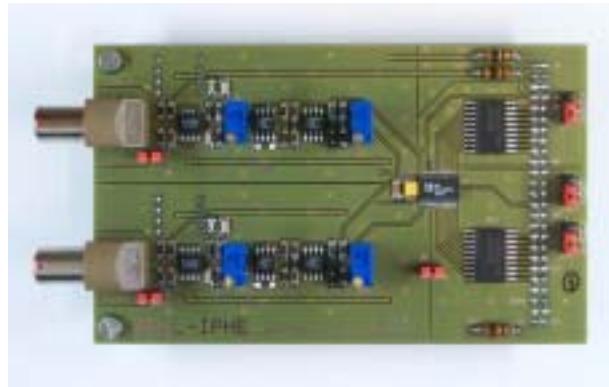

**An analog electrical link** is the simplest and cheapest one (Figure 21). It is based on the twisted pair cable for the data transmission. The analog data from the Level-0 chip are amplified by the radiation hard link driver on the “analog” repeater card in the vicinity of the detector and transmitted to the read-out board via multi-conductor shielded twisted pair cable.

Figure 21 Analog electrical link.

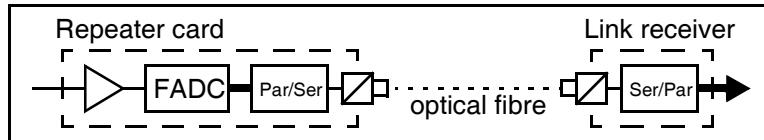

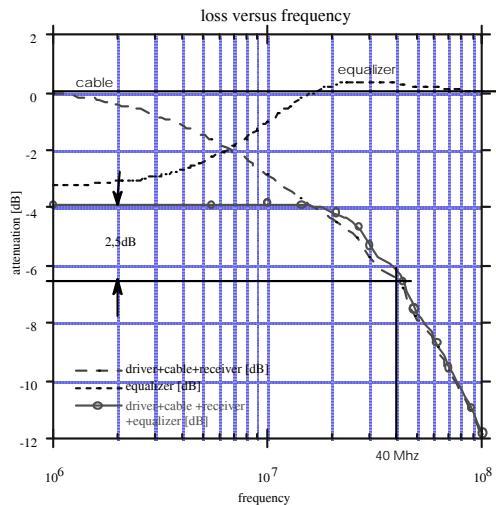

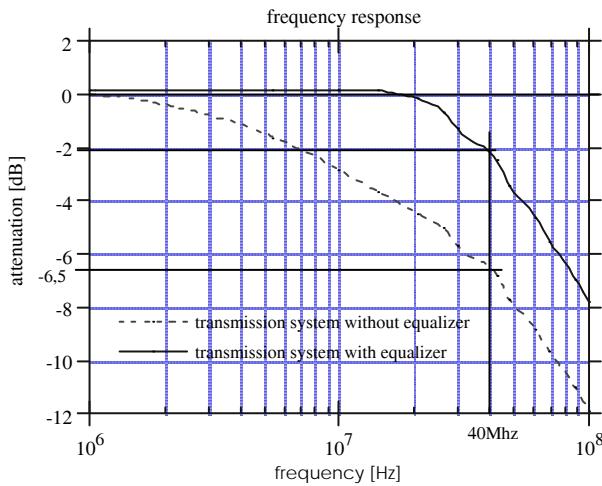

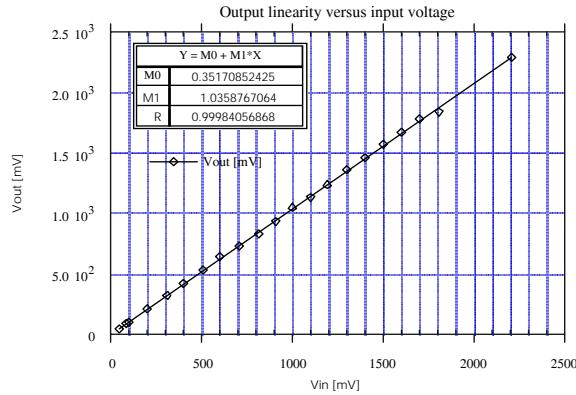

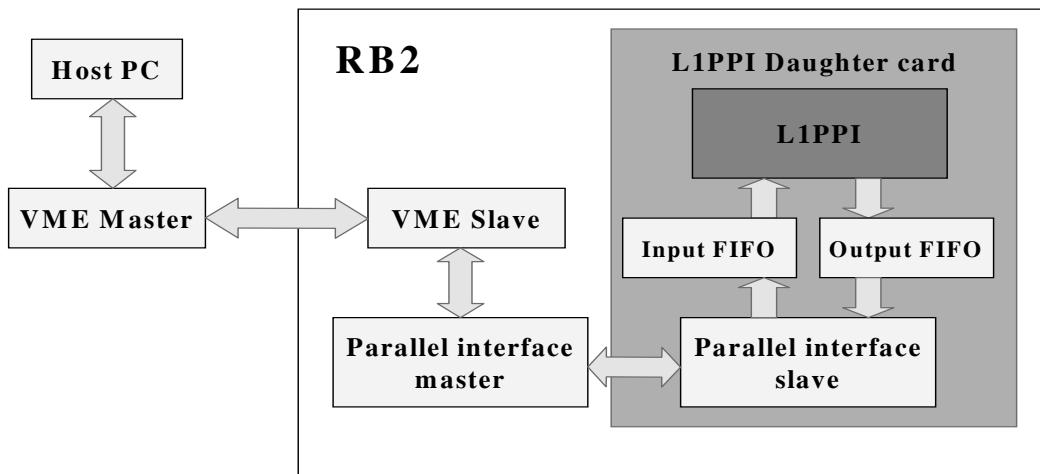

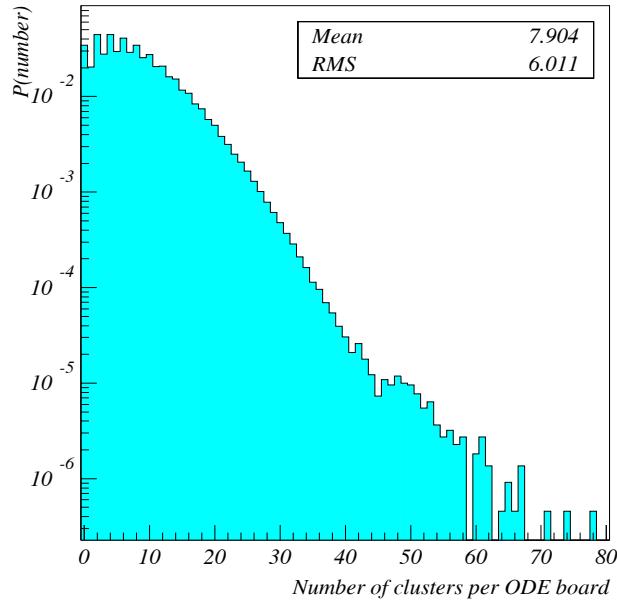

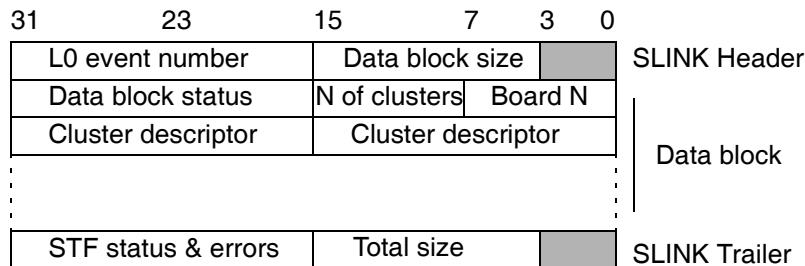

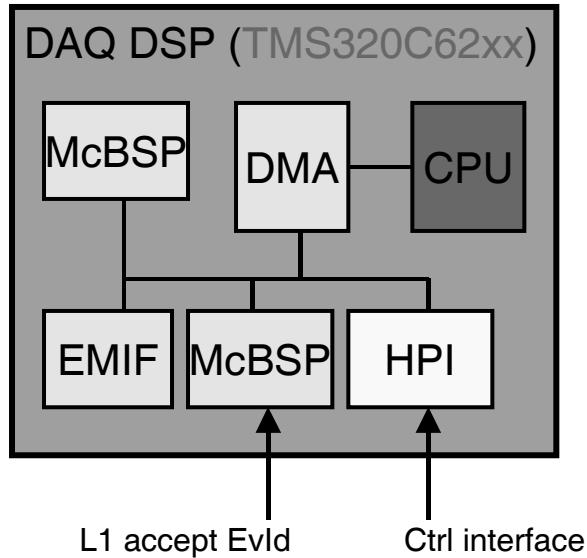

On the read-out board, after link receiver and amplifier, the analog signal is converted into 8-bit digit by FADC. This link provides required technical parameters at relatively low cost. It is also well matched to the Level-1 electronics granularity.