DD

EN-10001

SW9740

P00032111

# Real Time HEP Applications using T9000 Transputers, Links and Switches

Thesis submitted in accordance with the requirements of

the University of Liverpool

for the degree of Doctor of Philosophy

by

**Roger Heeley**

October 1996

## Acknowledgements

Firstly I would like to thank my joint supervisors Bob Dobinson and Erwin Gabathuler for giving me the opportunity to carry out the work presented within this thesis and for their support and guidance over the last three years.

I would also like to thank the European Union for my funding through the GPMIMD ESPRIT project (P5404), CERN for hosting this project and the CPLEAR collaboration for their support.

I would like to thank the four people I have worked most closely with for the last three years: Dave Francis, William Lu, Michael Ward and Jean Moonen. All of whom have played an important part in allowing me to carry out the work for this thesis.

Thanks also to Stuart Fisher who has worked extensively on benchmarking T9000s and carried out the work on the TransAlphas.

Our hardware group was crucial for the completion of the work within CPLEAR, I would like to thank Brian Martin, Minghua Zhu and Xinjah Liu. In addition to hardware support Minghua also carried out the memory benchmarks presented within chapter 2.

A thank you also to the GPMIMD industrial collaborators: Parsys, Telmat and SGS Thomson.

Last but obviously not least I would like to thank my family and friends. In particular, I would mention my parents, Suzanne, Tony and Julie, without whom this thesis would never have been started. Also a collective thanks to the Heeleys, Ousleys, Hardmans and Smiths (including pets).

# Abstract

Requirements for triggering systems in future generations of High Energy Physics (HEP) experiments in terms of computing power and communications performance are orders of magnitude greater than those of existing experiments. Point to point links and switches interconnecting microprocessors allow the construction of the required large systems scalable in terms of both computational and communications performance. There are relatively few "open" technologies currently available which allow a practical investigation of microprocessors interconnected by point to point links and switches. The IEEE 1355 standard including DS links is one such technology. This thesis presents the application of this technology to two HEP experiments: CPLEAR and a future generation experiment the Large Hadron Collider (LHC) at CERN.

The CPLEAR application involved the use of the T9000 in an on-line event filtering farm. The aims were to demonstrate the feasibility of replacing the existing off-line analysis system, demonstrate reliable operation of the technology and to obtain information for experiments at the LHC. The application of the technology to the LHC allows extrapolations to predict the capability of currently available technology to meet the requirements of future generation experiments. The work also identifies a set of factors which will be crucial in the performance of future HEP systems. The technology presented within this thesis may not be the technology to be used at the LHC, however, the conclusions of this thesis should provide valuable information for the construction and design of the future triggering systems.

# Table of Contents

|                                                                     |           |

|---------------------------------------------------------------------|-----------|

| <b>Chapter 1 Introduction .....</b>                                 | <b>1</b>  |

| 1.1 Motivation .....                                                | 1         |

| 1.2 Outline of thesis.....                                          | 2         |

| 1.3 Context of thesis.....                                          | 3         |

| 1.3.1 Authors work.....                                             | 3         |

| <b>Chapter 2 The T9000 Transputer and DS links.....</b>             | <b>5</b>  |

| 2.1 Transputers.....                                                | 5         |

| 2.2 Occam .....                                                     | 6         |

| 2.3 The T9000 Transputer.....                                       | 8         |

| 2.3.1 T9000 Architecture .....                                      | 10        |

| 2.3.2 DS Links .....                                                | 10        |

| 2.3.3 Virtual Channels and the Virtual Channel Processor (VCP)..... | 12        |

| 2.3.4 The Hardware Scheduler.....                                   | 14        |

| 2.3.5 Memory system.....                                            | 16        |

| 2.3.6 T9000 Known Hardware Bugs and Problems.....                   | 19        |

| 2.4 The C104 Packet Switch.....                                     | 19        |

| 2.4.1 Hardware Bugs.....                                            | 21        |

| 2.5 The T9000 Toolset Development System.....                       | 21        |

| 2.5.1 Problems with the Toolset.....                                | 24        |

| 2.6 Hosting T9000 Systems.....                                      | 24        |

| 2.7 The GPMIMD Machine.....                                         | 25        |

| 2.8 The TransAlpha Module.....                                      | 27        |

| 2.9 Conclusions.....                                                | 28        |

| <b>Chapter 3 Evaluation of Technology .....</b>                     | <b>31</b> |

| 3.1 Communication Benchmarks.....                                   | 31        |

| 3.1.1 Single Link Results.....                                      | 31        |

| 3.1.2 Dependence on memory bandwidth.....                           | 33        |

| 3.1.3 One to four physical links.....                               | 34        |

| 3.1.4 Dependence on clock speed.....                                | 35        |

| 3.1.5 Single Network GPMIMD Machine Results.....                    | 35        |

| 3.1.6 Multiple Network Results.....                                 | 38        |

|       |                                                    |    |

|-------|----------------------------------------------------|----|

| 3.2   | Interrupt Response and Context Switch Results..... | 40 |

| 3.2.1 | Timeslice operation.....                           | 40 |

| 3.2.2 | Timer generated interrupts.....                    | 40 |

| 3.2.3 | Interprocess communications.....                   | 40 |

| 3.3   | Supervisor/Control processor benchmarks.....       | 41 |

| 3.3.1 | Short Message Sends.....                           | 42 |

| 3.3.2 | Combined Communication and Computation.....        | 44 |

| 3.4   | Computation Benchmarks.....                        | 47 |

| 3.5   | Comparison to other platforms.....                 | 47 |

| 3.5.1 | VMEbus PowerPC systems running LynxOS.....         | 47 |

| 3.6   | Conclusions.....                                   | 49 |

## **Chapter 4 The Application of the T9000 to CPLEAR..... 53**

|       |                                                                 |    |

|-------|-----------------------------------------------------------------|----|

| 4.1   | Motivation.....                                                 | 53 |

| 4.1.1 | Value to CPLEAR.....                                            | 53 |

| 4.1.2 | Proof of existence and operation of the T9000 and C104.....     | 54 |

| 4.1.3 | Use of the T9000 for future generations of HEP experiments..... | 54 |

| 4.2   | The CPLEAR Experiment.....                                      | 54 |

| 4.2.1 | Physics Background.....                                         | 54 |

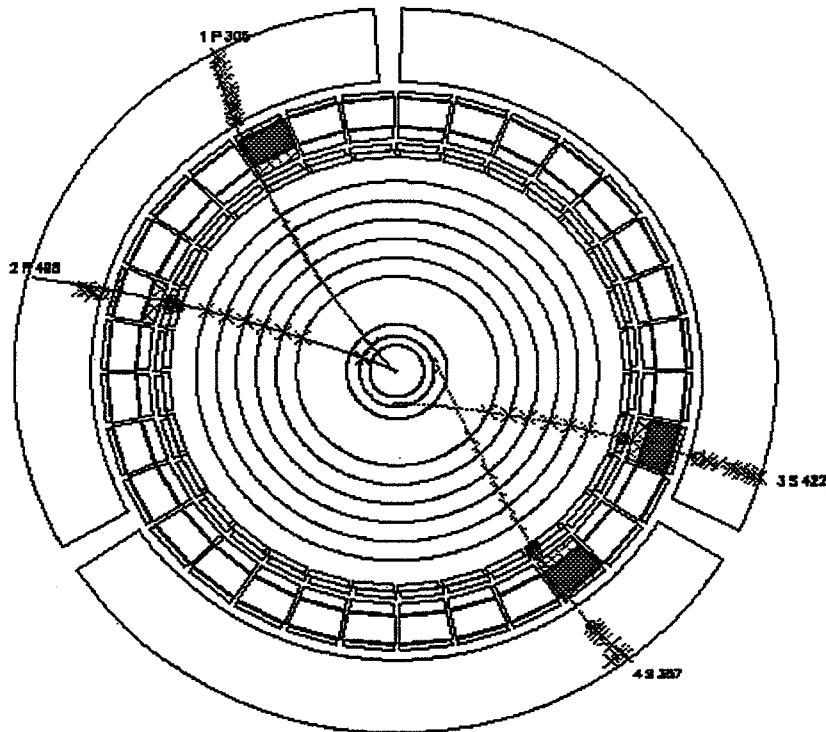

| 4.2.2 | Event Detection.....                                            | 55 |

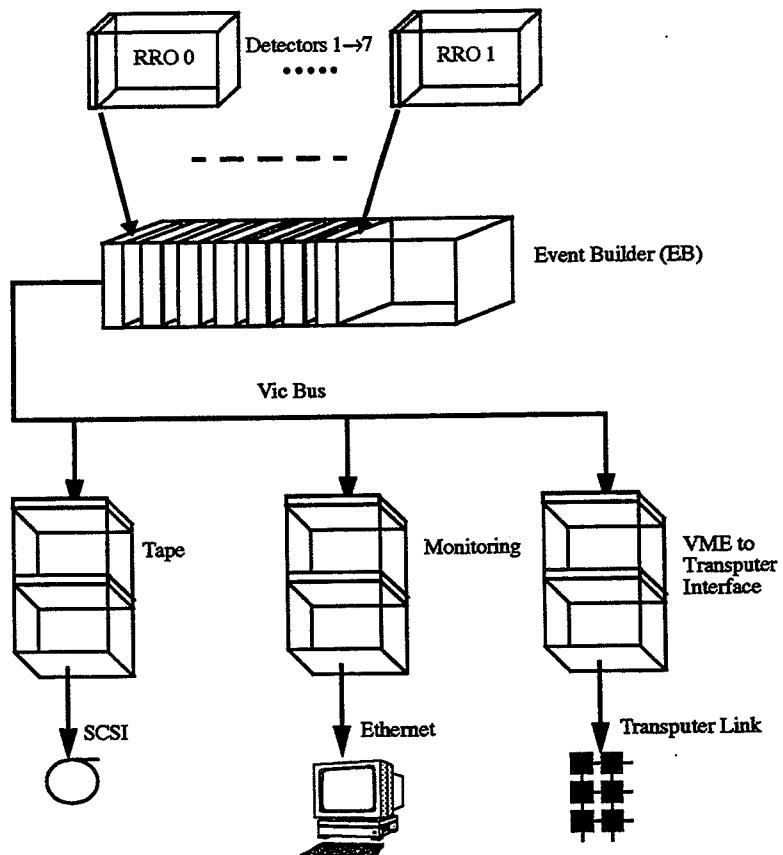

| 4.2.3 | Data Acquisition.....                                           | 56 |

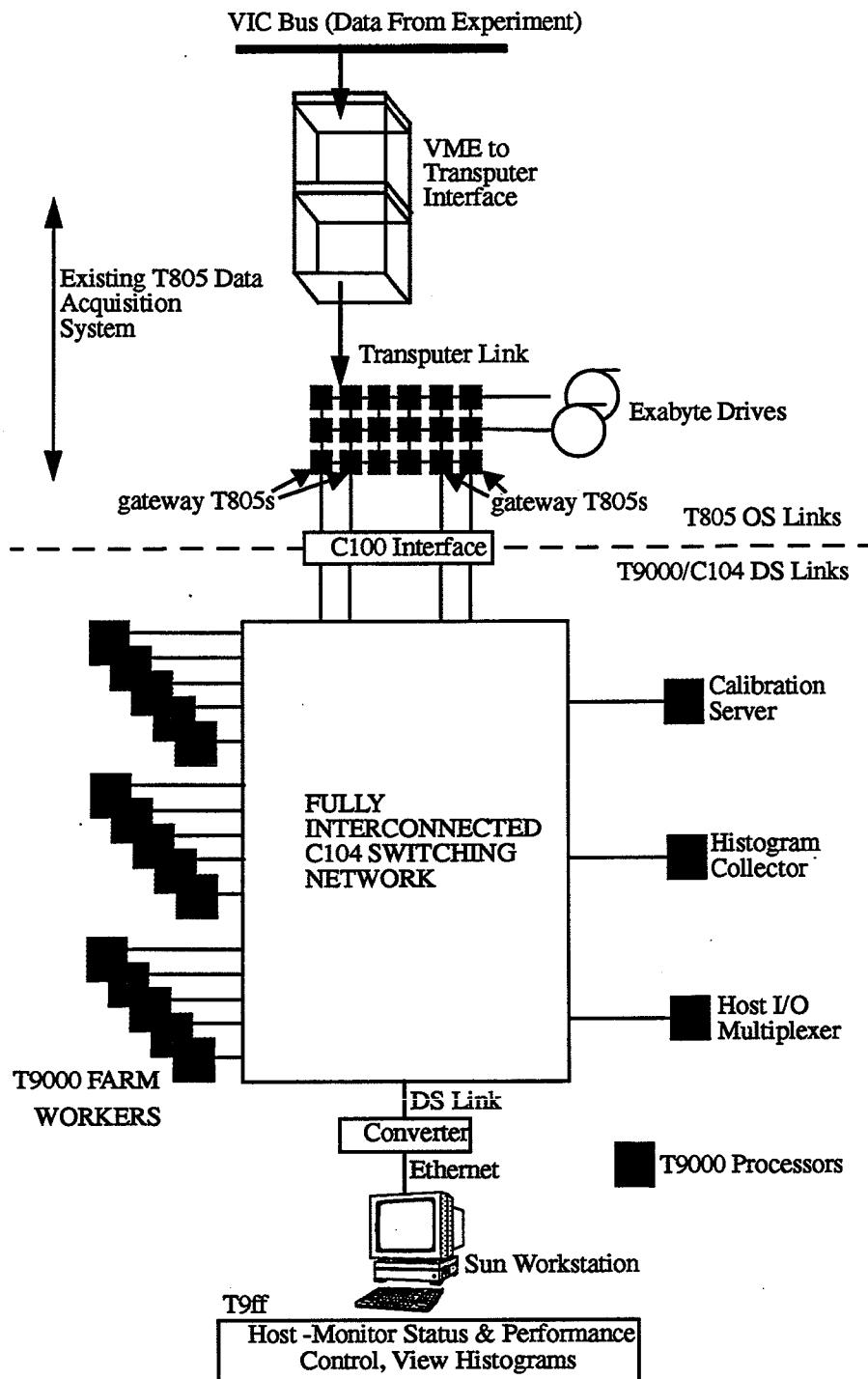

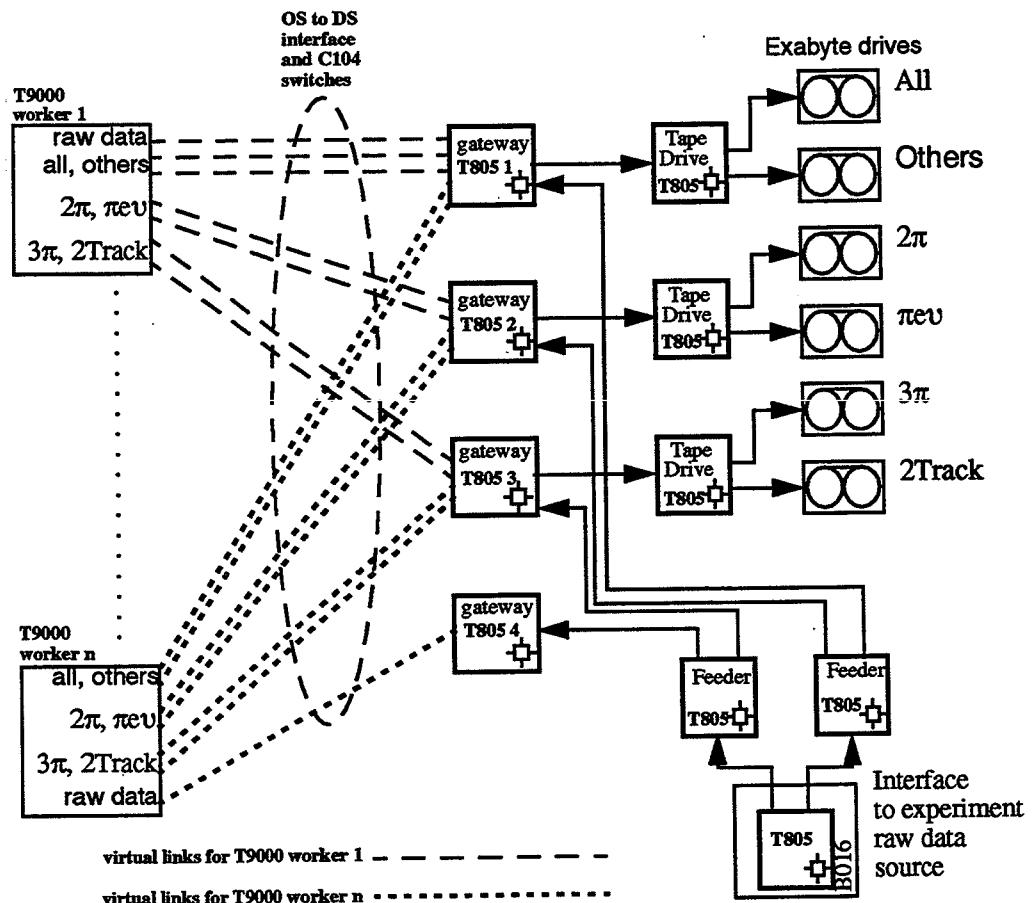

| 4.3   | T9000 Processor Farm System Overview.....                       | 57 |

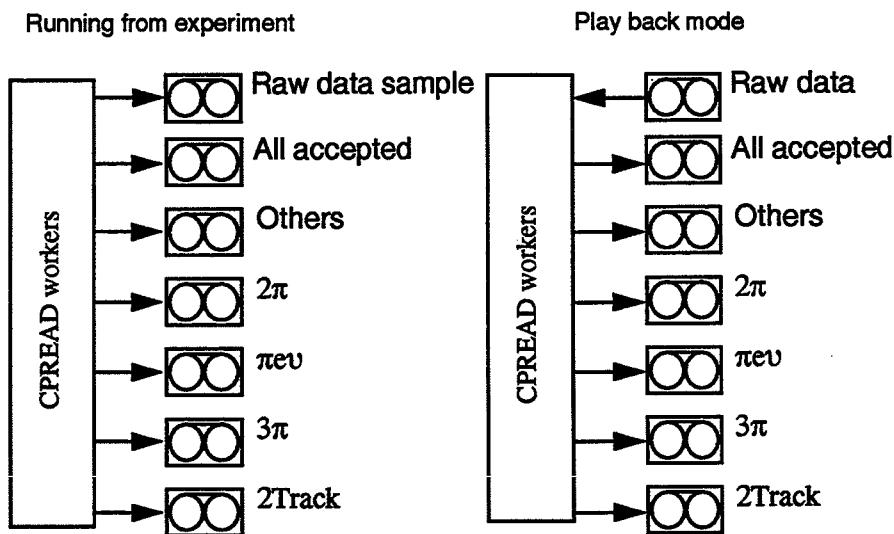

| 4.4   | Play-back mode.....                                             | 59 |

| 4.5   | Event types.....                                                | 60 |

| 4.6   | Porting of CPREAD.....                                          | 61 |

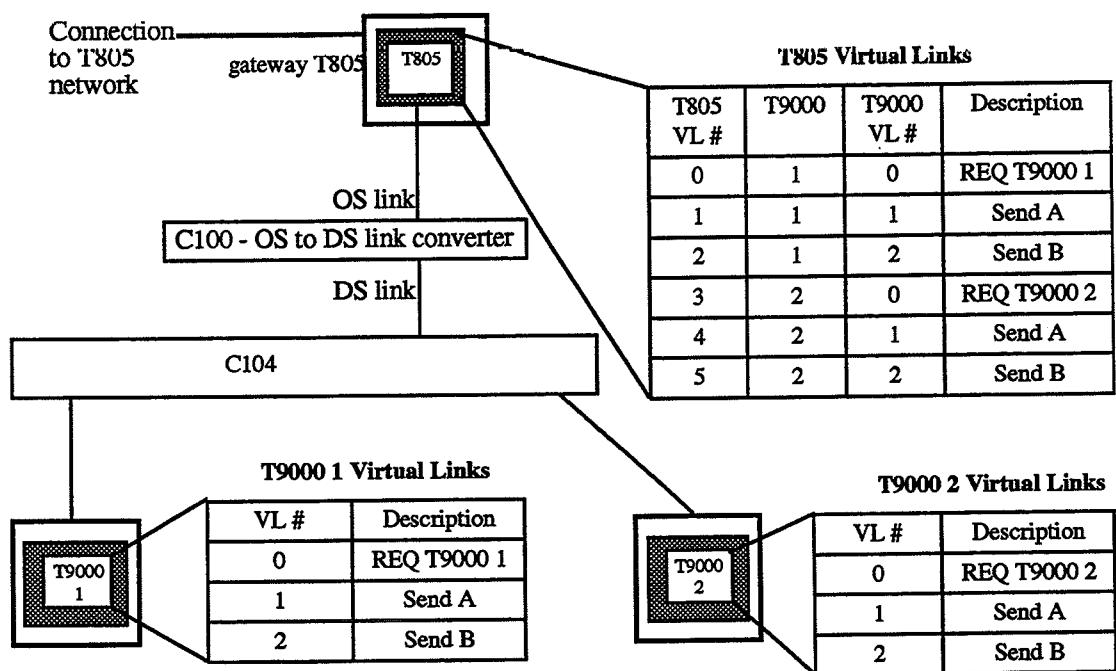

| 4.7   | T805 to T9000 Interface.....                                    | 61 |

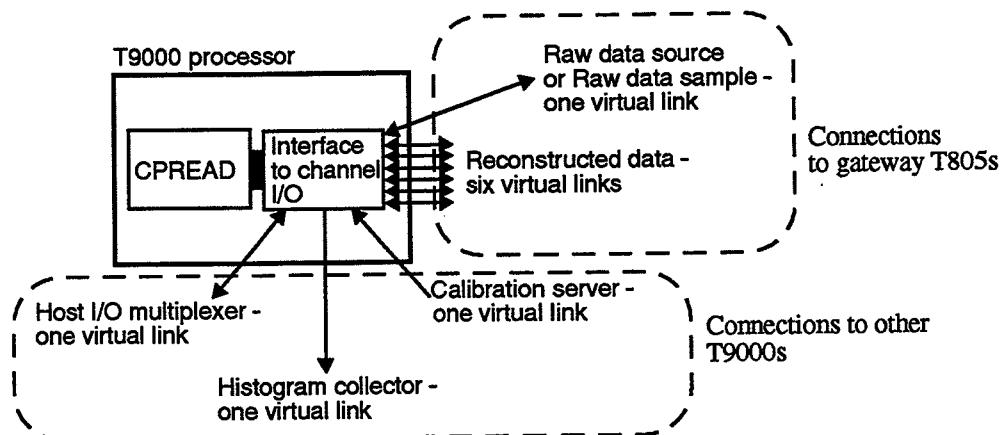

| 4.7.1 | Overview.....                                                   | 61 |

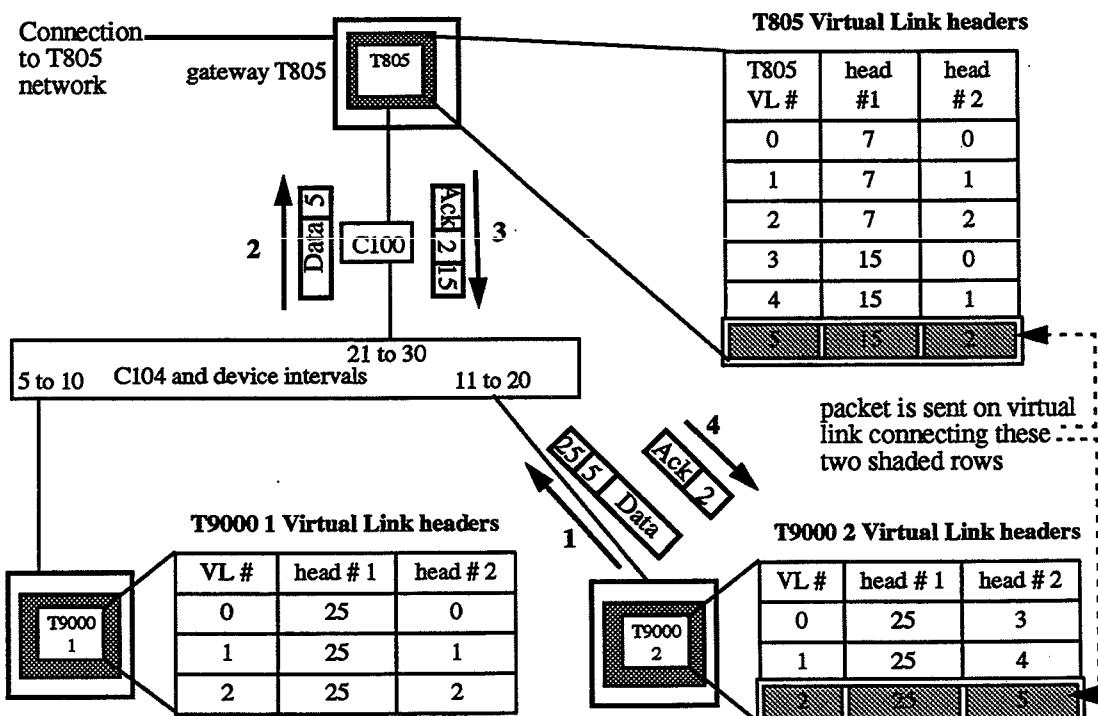

| 4.7.2 | An example T805 to T9000 interface.....                         | 64 |

| 4.7.3 | Extracting packet headers for the gateway T805.....             | 67 |

| 4.7.4 | Remaining problems.....                                         | 68 |

| 4.8   | On-line Monitoring.....                                         | 68 |

| 4.9   | History of Installations and associated problems.....           | 71 |

| 4.9.1 | CPLEAR run June 1994.....                                       | 71 |

| 4.9.2 | CPLEAR run September/October 1994.....                          | 72 |

| 4.9.3 | Practical problems and solutions.....                           | 75 |

| 4.10  | Results.....                                                    | 81 |

| 4.11  | Boosting computational power using TransAlpha modules.....      | 83 |

| 4.12  | Summary.....                                                    | 84 |

|                                                                |            |

|----------------------------------------------------------------|------------|

| <b>Chapter 5 DS link technology applied to the LHC .....</b>   | <b>87</b>  |

| 5.1    Introduction.....                                       | 87         |

| 5.2    Atlas.....                                              | 88         |

| 5.2.1    Overview.....                                         | 88         |

| 5.2.2    The level 2 trigger.....                              | 89         |

| 5.2.3    The level 3 trigger.....                              | 91         |

| 5.3    GPMIMD machine applied to level 2 and level 3.....      | 91         |

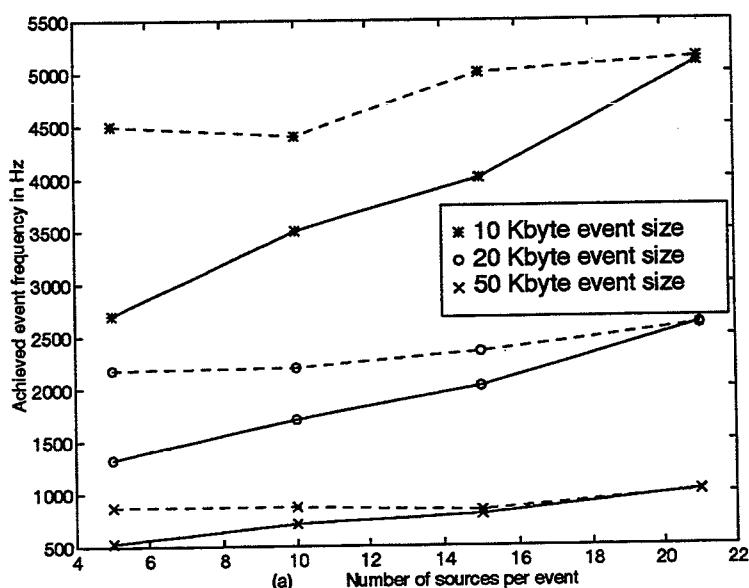

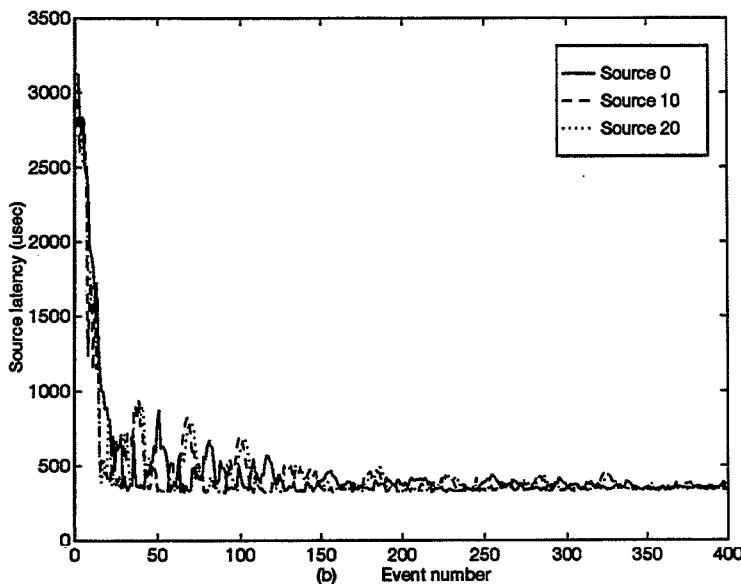

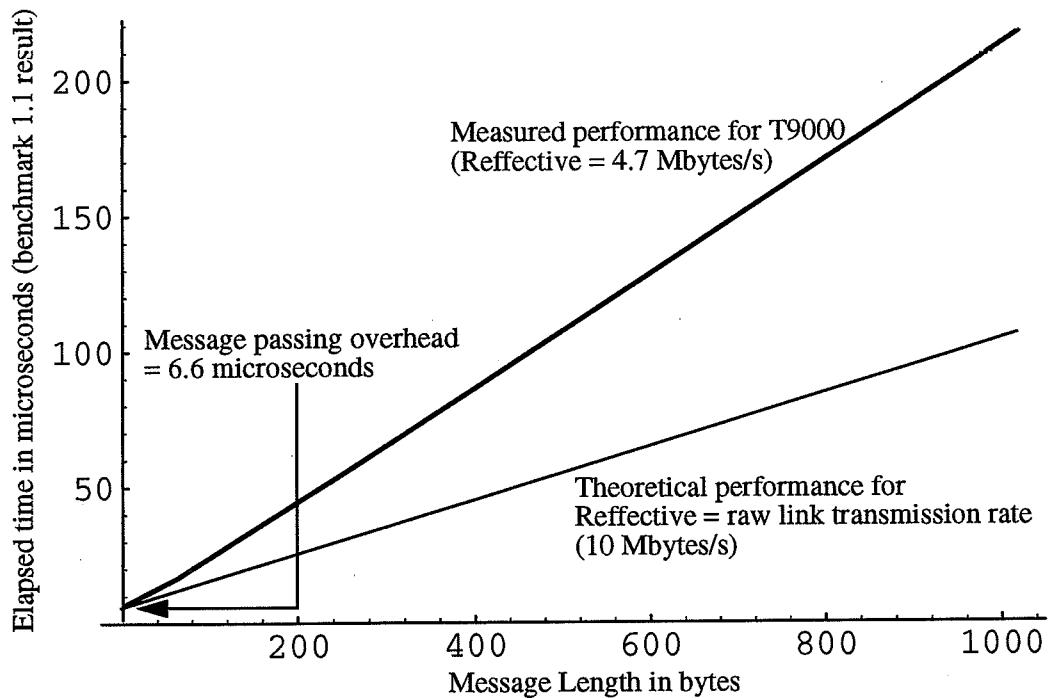

| 5.3.1    level 2 results.....                                  | 91         |

| 5.3.2    level 3 results.....                                  | 96         |

| 5.3.3    Extrapolation for level 2 to the SCT subdetector..... | 99         |

| 5.3.4    Extrapolation for level 3 to the SCT subdetector..... | 101        |

| 5.3.5    Conclusions.....                                      | 101        |

| 5.4    Comparison with other parallel platforms.....           | 102        |

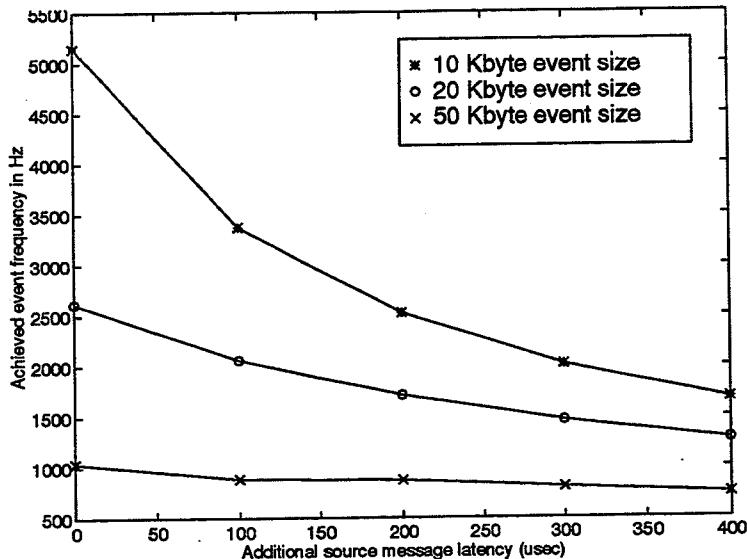

| 5.4.1    Benchmark 1.1 (one-way).....                          | 103        |

| 5.4.2    Benchmark 1.2 (two-way).....                          | 105        |

| 5.4.3    Benchmark 1.3 (all to all).....                       | 106        |

| 5.4.4    Benchmark 2.1 (push farm with supervisor).....        | 107        |

| 5.4.5    Summary of comparisons to other platforms.....        | 108        |

| 5.5    Conclusions.....                                        | 108        |

| 5.6    Future Work.....                                        | 111        |

| <b>Chapter 6 Concluding remarks .....</b>                      | <b>113</b> |

| 6.1    Original goals.....                                     | 113        |

| 6.2    Summary of results.....                                 | 113        |

| 6.3    Achievements.....                                       | 114        |

| 6.4    Future work.....                                        | 116        |

| 6.5    Final remarks.....                                      | 116        |

| <b>References .....</b>                                        | <b>117</b> |

# Chapter 1

## Introduction

### 1.1 Motivation

Requirements for triggering systems in future generations of High Energy Physics (HEP) experiments in terms of computing power and communications performance are orders of magnitude greater than those of existing experiments [1]. The experiments will increase in complexity, event rates, event sizes and the amount of computationally intensive analysis required in real-time. The only way to meet these continually increasing requirements is the use of large arrays of processors interworking via high speed interconnects. The computational and communications performance of such systems must scale to meet the dynamic requirements of the experiment.

Existing experiments largely base their trigger systems on standard (shared) buses such as CAMAC, VME and FASTBUS. This approach is being replaced by a migration to microprocessors communicating via high speed point to point links interconnected by switches. Point to point links and switches interconnecting microprocessors allow the construction of the required large systems scalable in terms of both computational and communications performance. Bus based systems are limited in scalability, they suffer from bottlenecks in the bus bandwidth and the limited interconnectivity available between multiple buses.

Table 1.1 contains a summary of existing HEP experiment requirements compared to the requirements of future generation experiments. The increases in reduction factors performed by the trigger are three orders of magnitude. These increases in rejection factors demand increased computational power available in real-time.

There are relatively few “open” technologies currently available which allow a practical investigation of microprocessors interconnected by point to point links and switches, and no clear winner in industry. In particular, few technologies are available to allow an investigation into their use in triggering and data acquisition in HEP. The IEEE 1355 standard [2] including DS links, the T9000 Transputer [3] and associated C104 packet switch [4] are technologies that have already been used to build substantial systems. A Transputer is a complete microcomputer with four integrated on-chip links allowing multiple processors to be interconnected. Using these links Transputers are directly connected or connected via switches.

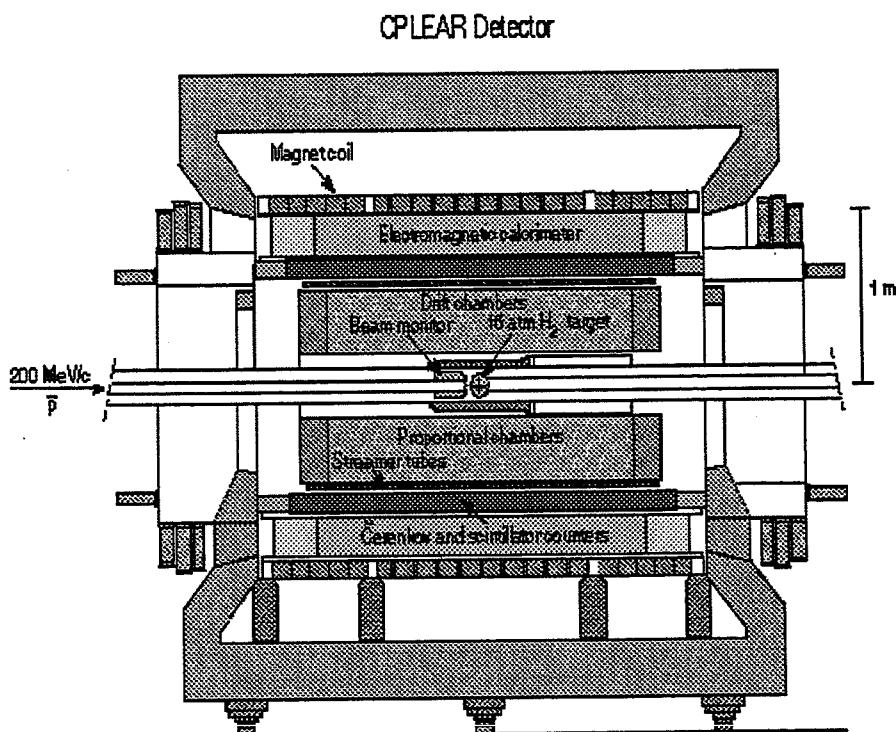

As part of the ESPRIT project, GPMIMD [5] a 64 node T9000 machine using C104 packet switches has been constructed. ESPRIT is the European Strategic Programme of Research and Development in Information Technology. This thesis presents the application of this technology to two HEP experiments: CPLEAR<sup>1</sup> and a future generation experiment the

---

1. CP violation at the Low Energy Anti-proton Ring [6].

Large Hadron Collider (LHC) at CERN<sup>2</sup>. For the LHC, I will investigate the application of the technology to the Atlas detector [7].

TABLE 1.1 Comparison between existing and future generation HEP experiments

|                    | CPLEAR             | A typical LEP <sup>a</sup> experiment | A typical LHC experiment - to be constructed in 2005 |

|--------------------|--------------------|---------------------------------------|------------------------------------------------------|

| Raw Event Rate     | $10^6$ Hz          | $5 \times 10^4$                       | $10^9$ Hz                                            |

| Trigger Reduction  | $4 \times 10^{-4}$ | $\sim 10^{-4}$                        | $10^{-7}$                                            |

| Number of Channels | $3 \times 10^4$    | $<10^6$                               | $>10^7$                                              |

| Event Size         | $\sim 2$ Kbytes    | $\sim 300$ Kbytes                     | $\sim 1$ Mbyte                                       |

| Final Data Rate    | $\sim 1$ Mbyte/s   | $\sim 1$ Mbyte/s                      | 10-100 Mbyte/s                                       |

a. Large Electron Positron collider at CERN.

The CPLEAR application involved the use of the T9000 in an on-line event filtering farm. The aims were to demonstrate the feasibility of replacing the existing off-line analysis system, demonstrate reliable operation of the technology and to obtain information for experiments at the LHC. The T9000s and C104s used for the CPLEAR application were prototypes, when the work was carried out, little or no experience existed in building large systems with these components.

The application of the technology to the LHC allows extrapolations to predict the capability of currently available technology to meet the requirements of future generation experiments. The work should also identify a set of factors which will be crucial in the performance of future HEP systems. The technology presented within this thesis may not be the technology to be used at the LHC, however, the conclusions of this thesis should provide valuable information for the construction and design of the future triggering systems.

## 1.2 Outline of thesis

This introduction chapter gives the general motivation for the thesis, an outline of the thesis and the background in which the work was carried out. Chapter 2 presents the technology of Transputers, links and switches along with supporting concepts and an introduction to parallel processing.

Chapter 3 describes an evaluation of the technology, which identifies a set of critical factors that dictate the performance of multi-processor systems. Included in the evaluation are communications, interrupt response, context switching and computational performance. In addition the performance of the T9000 is compared to other platforms.

Chapter 4 contains the application of the T9000 to the CPLEAR experiment operating as an on-line event filtering farm. Results are presented, problems discussed and projections are made to demonstrate the feasibility of using the technology to build processor farms in CPLEAR. Chapter 5 outlines the application of DS link technology to the LHC, a continuation of the CPLEAR application. Results are presented and discussed, the work has resulted in a set of factors affecting the performance of DS links applied to triggering at the LHC.

---

2. The European Laboratory for Particle Physics Research.

---

The factors are of relevance to any future system based on switching networks and point to point links. Some of these factors have been investigated, and those which have not are presented as future work. The final chapter, chapter 6, is a summary of the conclusions presented throughout the thesis.

### 1.3 Context of thesis

The work presented within this thesis was carried out at CERN within the ESPRIT project GPMIMD, a collaboration between fourteen European industrial partners. An objective of the project was the construction of a parallel scalable computer using the T9000 and C104. The role of CERN within this project included the mounting of HEP applications onto this machine. These applications are only a small part of the project, however, the successful operation of the technology in the demanding environment of an HEP experiment and the availability of substantial demonstration systems was a crucial aspect of the project. This was recognised as such by our industrial partners and the external project reviewers appointed by the European Union. Work carried out within this project has lead to the basis of work for this thesis.

#### 1.3.1 Authors work

The benchmarking and technology evaluation presented within chapter 3 is the authors own work. This includes the writing of benchmarks to assess communications, interrupt response and context switch performance. Any results from other sources used for comparison are clearly referenced at the point they are presented.

Chapter 4 is entirely the authors own work. This includes the design and implementation of the T9000 system and the integration with the existing CPLEAR data acquisition system. All extrapolations and conclusions are the authors own work. Clear references are given where existing systems or software produced by other persons are used.

In chapter 5 all extrapolations, interpretation of results and conclusions are the authors own work. Some results were produced in collaboration with another member of the group.

Chapter 6 is entirely the work of the author.

---

## Introduction

---

# Chapter 2

## The T9000 Transputer and DS links: hardware and software

In this chapter the relevant technologies used are presented, including supporting concepts and a general introduction to parallel processing using Transputers.

The requirement for processing performance in HEP data acquisition, and more generally real-time embedded systems, is continuously increasing as systems become more complex. The only way to satisfy these requirements in the long term is the use of multiple processors which provide efficient support for multiprocessing. Crucial issues will be the inter-processor communication performance, efficient support for concurrent communication and computation, fast interrupt response times and context switch times. The T9000 Transputer has been specifically designed to provide high performance in all of these areas.

Of equal importance is the software development environment and host system software. Multiprocessing systems require complex real-time monitoring and fault tolerance control systems. The T9000 provides dedicated control links for configuration, monitoring and control.

The Transputer model of concurrent programming is presented, followed by details of Transputer and switch implementations, i.e. the T9000 and C104. The software development environment and host system software for the T9000 is presented and a critique given. The TransAlpha module is presented which combines the T9000 with a DEC Alpha processor to boost its computational power.

### 2.1 Transputers

A Transputer is a complete microcomputer on a single VLSI chip. Each Transputer has a number of communication links, allowing them to be interconnected. These links allow concurrent programming in multi-processor Transputer networks. The Transputer instruction set contains single instructions to send and receive messages through these links, minimizing delays in inter-Transputer communication. Transputers can be directly connected, to form specialised networks, or can be interconnected via switches.

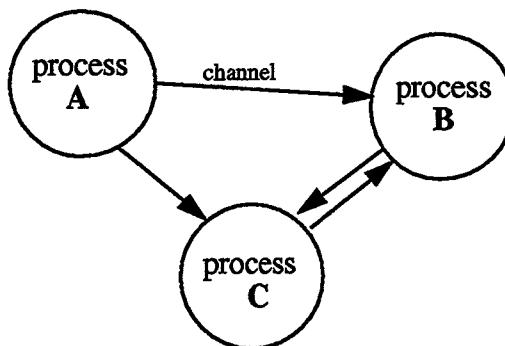

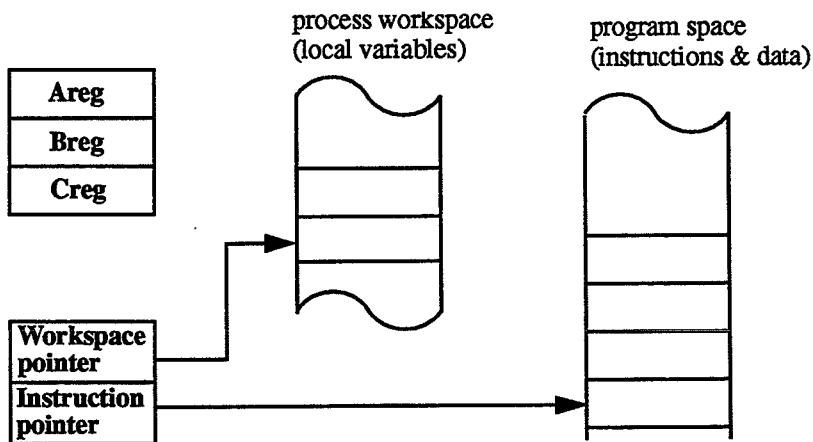

Transputers were explicitly designed for multi-processing, in addition to the specialised hardware functionality a Transputer model of concurrency has been developed. The programming model for Transputer systems consists of sequential processes which communicate using message passing, based on Hoare's Communicating Sequential Processes (CSP) [8]. Each process can be viewed as a black box with internal state, which can communicate and synchronise with other processes via point to point communication channels, as shown in Figure 2.1.

Communication is synchronous, if one process is not ready, both processes will be suspended. The correct input/output instruction must be executed on both communicating processes for the communication to take place.

FIGURE 2.1 The Transputer Model Of Concurrency

Each Transputer has an on chip hardware process scheduler which allows it to share its time between a number of processes. Communication between processes on the same Transputer is performed using the local memory; communication between processes on different Transputers is performed using a link. Consequently, a program can be executed either by a single Transputer or by a collection of Transputers in a network. The same communication model is maintained irrespective of whether processes are located on a single Transputer or a network of Transputers. Figure 2.2 shows two possible mappings based on the processes presented in Figure 2.1.

FIGURE 2.2 Mapping Of Processes to Processors

An application is not dependant upon a particular network configuration, thus a program can be run on various networks allowing optimisations in cost and performance.

## 2.2 Occam

Occam [9] is a parallel processing language based on Hoare's CSP. The Transputer was developed with the specific intention of providing an efficient platform for the execution of the occam programming language. Other languages exist for the Transputer (for example C) but none has such a close relation to the Transputer instruction set, hence other languages are often less efficient and require larger amounts of code. Occam is a language designed for parallel processing, C is not. Unless otherwise noted, all coding of Transputer programs within this thesis has been performed using occam.

An occam program consists of 1 to N concurrent sequential processes, that can communicate via point to point links, mirroring the Transputer model of concurrency.

All occam programs are built from three primitive operations; assignment, input and output. The primitives produce processes by specifying their order; sequential or parallel. In addition to these primitives there is support for repetition and conditional statements. Data objects and their types may also be defined. Table 2.1 lists the three occam statements which describe the relation between multiple processes; SEQ (sequential), PAR (parallel) and ALT (alternate).

TABLE 2.1 Important occam statements

| Statement        | Syntax                                                             | Description                                                                                                                        |

|------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| SEQ construction | SEQ<br><process 1><br>...<br><process N>                           | A collection of processes to be executed in sequence, where a process is any occam construct.                                      |

| PAR construction | PAR<br><process 1><br>...<br><process N>                           | A collection of processes to be executed concurrently with each process starting execution at the same time.                       |

| ALT construction | ALT<br><input 1><br><process 1><br>...<br><input N><br><process N> | Select one process from the list of alternative processes to be executed depending on which input guard has input available first. |

The five lines of occam in Figure 2.3 demonstrate the ease with which occam can provide communication of variables between processes. An output on a channel is performed using ‘!’ and input is performed using ‘?’.

The channels talkin and talkout are connected to one another in a configuration language, which will also map the code onto a processor. Details of the configuration process are presented in Section 2.5, “The T9000 Toolset Development System.”. The code would have the following effect: two processes would run concurrently, in the first process data would be sent on the channel talkout from variable a, in the second process data is received on the channel talkin into the variable b.

The equivalent task written in C is considerably longer and more complex, see Figure 2.3, therefore immediately less readable. A set of libraries providing the C sub-routine equivalent functions and predefined data types of the occam constructs extend the C language for concurrent programming. In the example the functions ChanInInt and ChanOutInt are used to send integers on a channel. ProcAlloc is used to reserve memory space and allocate heap space for processes. The function ProcPar runs multiple processes concurrently and ProcAllocClean releases all memory used by a process.

There are clear problems when constructs for parallel programming are added on to a language after its initial design. The occam programming language was designed specifically for parallel processing.

Familiarity with C or existing C code, which can be directly compiled, are possible advantages of using C. The disadvantages are the increased code complexity and the possibility of losing performance.

occam required to output an integer on a channel

```

CHAN OF INT talkin,talkout:

INT a,b:

PAR

talkout! a

talkin? b

```

C required to output an integer on a channel

```

void out_proc (Process *p, Channel * c) /* Code to send integer */

{

int a;

ChanOutInt (c,a);

return;

}

void in_proc (Process *p, Channel *c) /* Code to receive integer */

{

int b;

b = ChanInInt (c);

return;

}

int main(void)

{

Channel * talkin, * talkout; /* Declare two channels */

Process * in, * out; /* Declare two processes */

in=ProcAlloc (in_proc, 0, 1, talkin); /* Allocate memory for processes */

out=ProcAlloc (out_proc, 0, 1, talkout); /* Use procedures in_proc & out_proc */

ProcPar (in,out,NULL); /* Execute processes 'in' and 'out' */

ProcAllocClean(in); /* Release memory */

ProcAllocClean(out); /* Release memory */

}

```

FIGURE 2.3 A comparison between occam and C

### 2.3 The T9000 Transputer

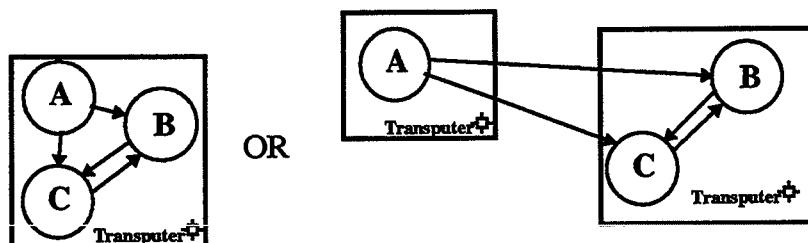

The T9000 is the latest generation of Transputers from SGS Thomson (see Figure 2.4). It has a 32-bit pipelined processor with a 64-bit FPU and 16 Kbytes of cache. There are four bi-directional serial data links and a Virtual Channel Processor (VCP) allowing efficient T9000-to-T9000 communications. There are two on chip 32 bit timer clocks with up to 1 microsecond resolution. These components are combined onto a single integrated circuit.

The T9000 has several improvements over previous generations of Transputers in both performance and functionality. Improved performance has been gained through an increase in design clock speed (50 MHz design), the implementation of an on-chip cache, and a pipelined superscalar architecture. This architecture allows multiple instructions to be executed every processor cycle.

Two separate control links allow the T9000 to be controlled (processor initialization and loading) and monitored for errors, even when there are faults in the normal communications network. These control links may be daisy chained and/or connected via C104 packet switches. A full description of the T9000 is given in the following sections.

FIGURE 2.4 The T9000 Transputer

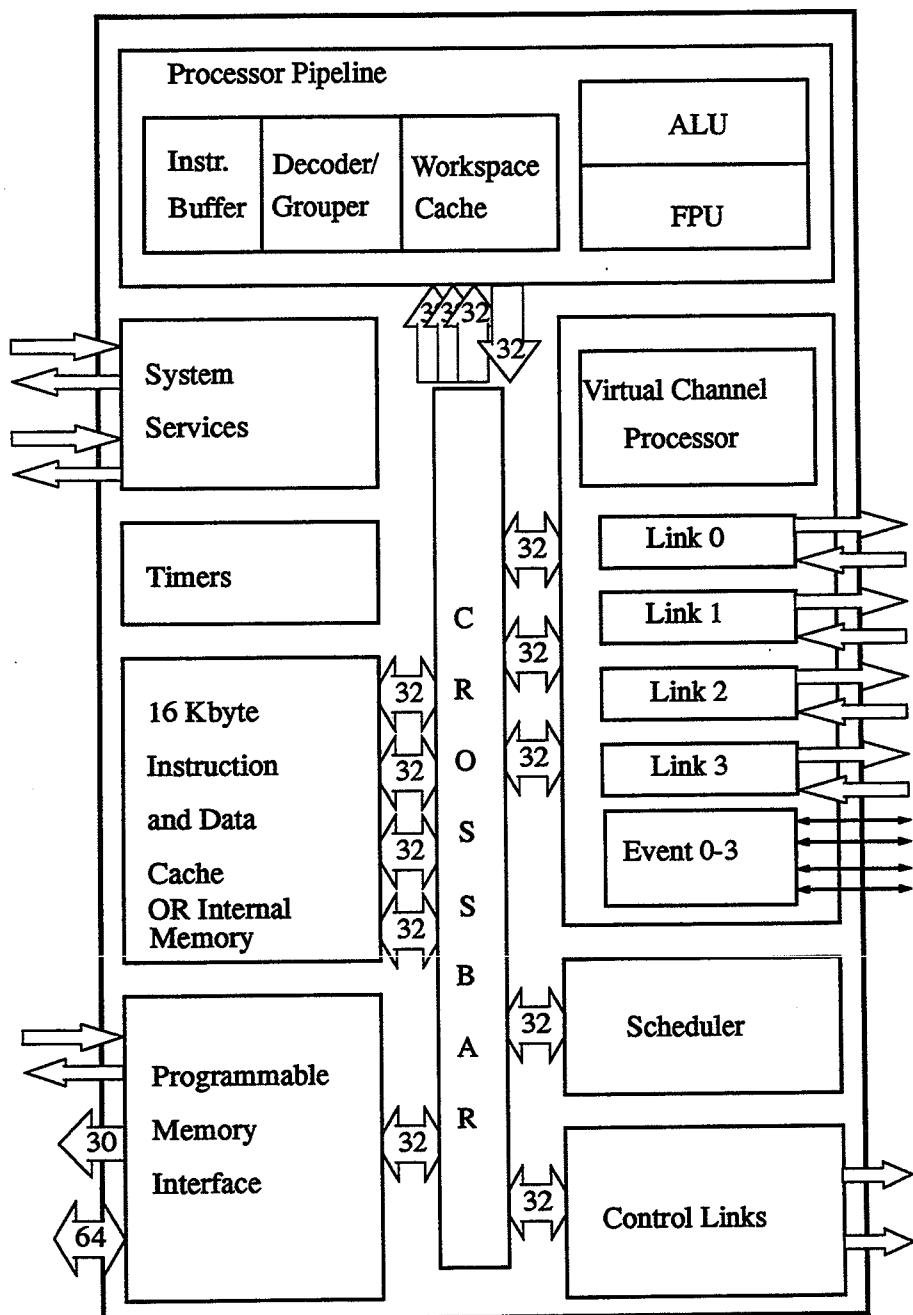

### 2.3.1 T9000 Architecture

The CPU contains three registers (Areg, Breg and Creg) used for expression evaluation which form a hardware stack. The floating point unit also contains three registers to form an evaluation stack. The Transputer uses two more registers to execute code: the instruction pointer to the next instruction to be executed and the workspace pointer (see Figure 2.5). The workspace is an area of memory where local variables are stored, which also has a dedicated cache. The workspace cache can hold up to the first 32 words of the process workspace, allowing fast access to the variables stored in this memory.

FIGURE 2.5 T9000 Architecture

### 2.3.2 DS Links

Improved communication is provided by the new Data/Strobe (DS) link technology which currently operates at 100 Mbits/s. I have carried out tests running C104 links successfully at 200 Mbits/s<sup>3</sup>, and T9000 links at up to 160 Mbits/s.

The DS link technology is part of the IEEE 1355 standard. The standard covers the physical connectors, cables, and electrical/logical protocols for implementing point to point serial interconnects operating at speeds of 100 Mbits/s (DS) and at 1 Gbit/s (HS) over copper and optical fibres. The DS links run over printed circuit and cable interconnections.

The DS link uses four different levels of protocol:

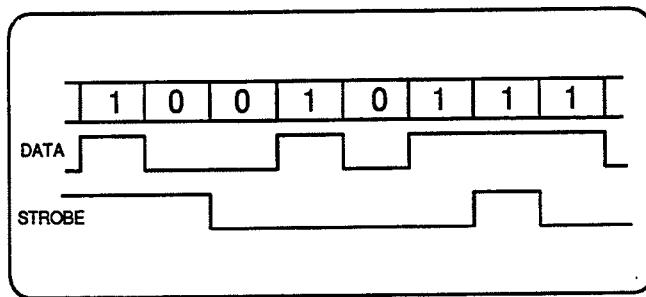

- Bit level. The DS link uses 4 wires: a data/strobe pair in each direction. The protocol guarantees that exactly one of the two wires (for a single direction: data and strobe) will have an edge in every bit frame. The levels on the data wire are the transmitted bits, see Figure 2.6.

3. SGS-Thomson plan to produce products using DS links at over 200 Mbits/s

FIGURE 2.6 Bit Level Protocol on a Data Strobe link

- **Tokens.** The next level of protocol is the token, there are two types of token: data and control. Data tokens are simply data bytes, but there are multiple control tokens most of which are used for flow control and alignment of clocks against skew. Figure 2.7 shows the construction of the tokens.

Token = Parity + Function + Body

10 bit Data Token = P 0 b b b b b b (8 data bits + 2 others)

| Control Tokens                 | Token                | Symbol | Bit Pattern   |

|--------------------------------|----------------------|--------|---------------|

|                                | Flow Control         | FCT    | P 1 0 0       |

|                                | End of Packet        | EOP    | P 1 0 1       |

|                                | End of Message       | EOM    | P 1 1 0       |

|                                | Escape               | ESC    | P 1 1 1       |

| P = parity bit<br>b = data bit | Disconnect Detection | NUL    | ESC + P 1 0 0 |

FIGURE 2.7 Token Level Protocol

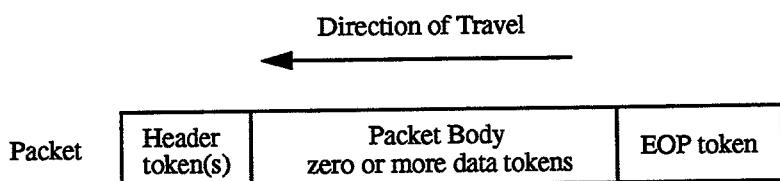

- **Packet.** A packet is a sequence of tokens with a specific order and format: a header (containing routing information), zero or more data tokens and then an end of packet control token (see Figure 2.8). The standard does not specify a limit to the number of data tokens contained in the packet.

- **Message.** Messages are a sequence of packets. The final data packet sent in the message is terminated with an end of message token. The message protocol used by the T9000 is presented in the next section: "Virtual channels and the T9000 virtual channel processor".

FIGURE 2.8 Packet Level Protocol

The output side of a DS link is set to run at a particular speed, the input side is clocked entirely by the incoming data, it does not need to know what speed to expect the incoming link to run at.

One of the four control tokens is an escape which allows for a number of composite control tokens made up of short sequences of 4 bit control tokens. DS link modules send a continuous stream of tokens, when there are no other tokens to send the link modules exchange composite NUL tokens. The link should continuously receive tokens, the absence of tokens on the link results in a link failure which is detected immediately. The failure is known as a link disconnect failure.

T9000 processors can be directly connected using their DS links or connected to a network of C104 packet switching chips, thus allowing the construction of large networks with scalable communication bandwidth between nodes. In the latter case, additional packet headers are required to route the packet through the switching network.

### 2.3.3 Virtual Channels and the T9000 Virtual Channel Processor (VCP)

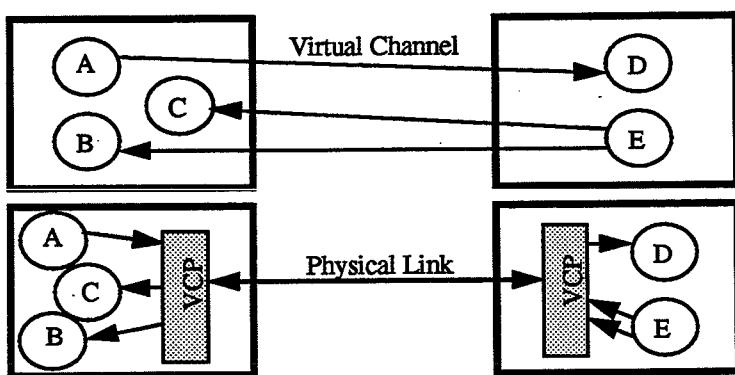

Communication between T9000 processes is performed via virtual channels. A virtual channel is a single logical communication connection between two processes mapped onto a physical processor link (see Figure 2.9). A single physical link may carry up to 64,000 virtual channels, the current implementation limit. Processes on any two Transputers may be directly connected by a channel regardless of their relative positions in the network. The connection and switching between the two processes can either be performed using C104 packet switches or if they are not available by software virtual channel routing on other T9000s. Virtual channels allow any application to be mapped onto a network configuration regardless of the network topology.

FIGURE 2.9 Virtual Channels

The VCP of the T9000 is a hardware communications processor which multiplexes the virtual channels onto a specified physical processor link. Packets from separate virtual channels are interleaved onto the physical link, allowing separate processes to communicate simultaneously. The virtual channel to which the packet is being sent is contained in the packet header. A virtual link is comprised of two virtual channels, one in each direction.

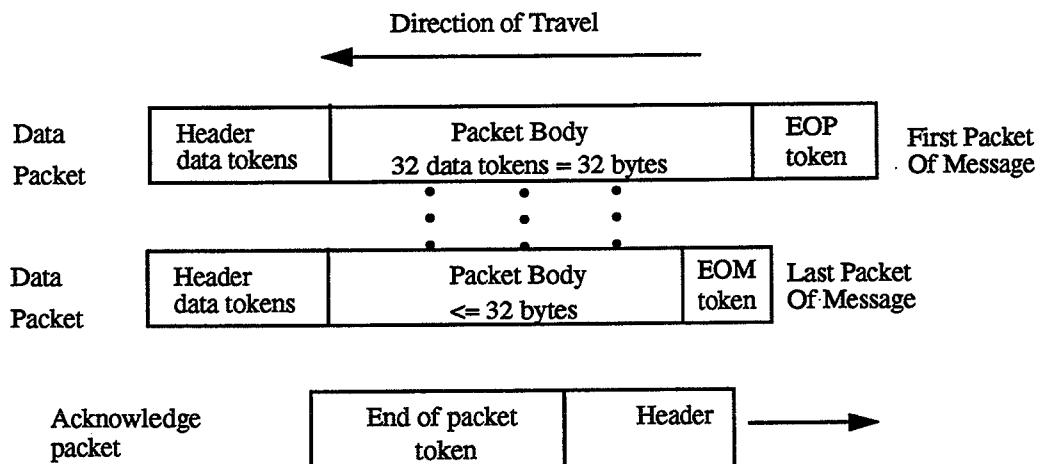

Messages are divided into a sequence of packets, each of which has the structure shown in Figure 2.10. All routing information is contained in the packet header. The T9000 imple-

ments a maximum packet body of 32 bytes. For example, a 48 byte message will be sent as a 32 byte packet followed by a 16 byte packet. Any device receiving a data packet replies to the sender with an acknowledge packet. No further packets are transmitted by the sender until the corresponding acknowledge has been received by the sender. The transmission of the packets on a single virtual channel is synchronous.

FIGURE 2.10 Packets on a DS Link

There can be only one message transmitting on a virtual link at any time. A process can only be communicating on a single virtual link at any time. If a single virtual link is in use, a packet is transmitted, then the virtual link is idle until the acknowledge for that packet is received. This utilises a small proportion of the available link bandwidth. If multiple virtual links are used (concurrently) then the first virtual link (waiting for an acknowledge) stays idle but another virtual link can use the physical link. The virtual links would require separate concurrent processes to drive them. If enough virtual links are used concurrently then the physical link can be saturated.

The VCP enables virtual links to share physical links. To achieve this, it maintains queues for each physical link. The receipt of an acknowledge packet for a data packet puts the next packet for that message (if any are remaining) on the back of the transmit queue for the appropriate link. The VCP alternately sends from the queue of data packets and acknowledge packets from high priority processes until both are empty. It will then send data and acknowledge packets from low priority processes. Packetisation, acknowledgements and link queuing are all handled by the VCP.

Each virtual link in a T9000 is represented by a structure called the virtual link control block (VLCB). The VLCBs are used to store the current status of communications on the virtual links. It also stores all header and routing information that is required for the packets to reach their destination virtual link.

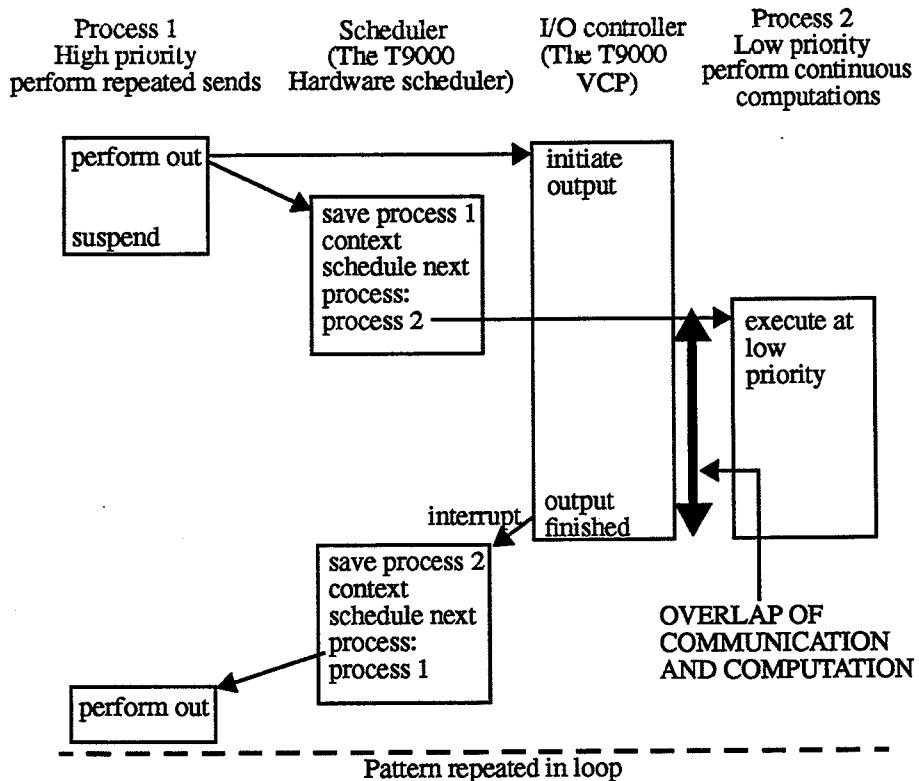

### 2.3.4 The Hardware Scheduler

In most embedded systems there is a need for a real-time response (both to external interrupts and efficient context switching in multi-tasking systems). In all HEP data acquisition systems investigated within this thesis there are often strict real-time requirements.

The hardware scheduler implements the Transputer model of concurrency, handling of interrupts and process scheduling. The T9000 CPU uses very few registers to store the state of the current process. The result is that there is little information to be stored when there is an interrupt or process switch, hence the operations are fast. In addition the operations are performed by a dedicated hardware scheduler, improving performance.

Both internal and external communications performance are affected by the efficiency of rescheduling and descheduling processes. In general, communications are performed using the following three steps: deschedule process, perform communication then reschedule process.

#### 2.3.4.1 The Transputer model of concurrency

The hardware scheduler on the T9000 allows the implementation of the Transputer model of concurrency, multiple processes executing concurrently on a single processor. A process can have one of two priorities: high or low. At any time, a transputer process may be:

| ACTIVE                                      | or | INACTIVE                            |

|---------------------------------------------|----|-------------------------------------|

| -Being executed, or                         |    | -Ready to input, or                 |

| -Descheduled by higher priority process, or |    | -Ready to output, or                |

| -On a list waiting to be executed           |    | -Waiting until a specified time, or |

|                                             |    | -Waiting on a semaphore             |

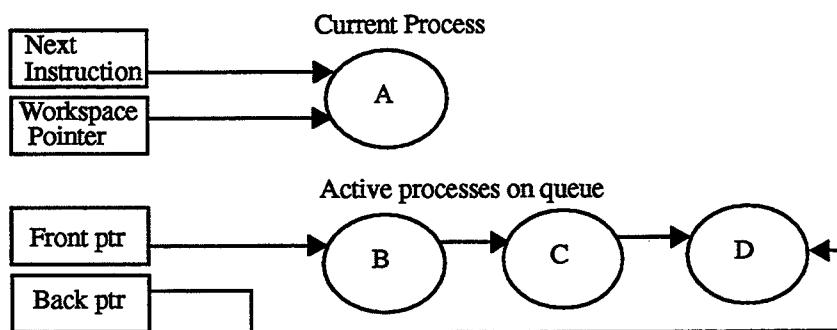

The inactive processes do not consume any processor time. The active processes waiting to be executed are held in a list of process workspaces. This is implemented using two registers, one of which points to the first process on the list, the other to the last. In Figure 2.11, A is executing, and B, C and D are active, awaiting execution. A separate queue is maintained for low and high priority processes, with low priority processes only being given CPU time when the high priority queue is empty.

FIGURE 2.11 T9000 Process Queue

#### 2.3.4.2 Low priority processes

A low priority process executes until it is unable to proceed, and is descheduled for one of the following reasons:

- It initiates I/O, i.e. waiting to input or waiting to output

- It is waiting for a value of the timer to be reached

- Any high priority process becomes active. Low priority processes will be pre-empted by any high priority process that is ready to execute (active).

- It has occupied the CPU for its 'timeslice' which is approximately 1 millisecond. The process is descheduled and added to the end of the low priority process queue. When no high priority processes are active the CPU is shared between all active low priority processes, each is allowed a timeslice before being descheduled. This process is known as timeslicing.

The next four points detail the requirements that must be satisfied before a low priority process can be rescheduled. In addition, the process will always have to wait until there are no active high priority processes before it can execute:

- If descheduled by I/O, the I/O must be completed before the process can be rescheduled

- If descheduled waiting for a timer, the required value of the timer must be reached

- If descheduled by a high priority process, that high priority process must become inactive

- If descheduled after executing for a timeslice period, all other active low priority processes must be allowed to execute before the process can be rescheduled

#### 2.3.4.3 High priority processes

A high priority process executes until it is unable to proceed, and is descheduled for one of the following reasons:

- It initiates I/O, i.e. waiting to input or waiting to output

- It is waiting for a value of the timer to be reached

When the I/O is complete or a timer value is reached the process becomes active. At that time it will pre-empt any low priority process executing, or if a high priority process is executing it will be added to the end of the high priority process queue.

#### 2.3.4.4 Full and partial context switch

When any current process is descheduled and another replaces it a context switch has occurred. I distinguish two types of context switch: a partial context switch and a full context switch.

A partial context switch can only occur when the current process is executing certain instructions, for example a jump or loop end instruction. The current process has very little 'state' or context that needs to be saved when it is executing a jump or loop end. The values of A, B and C registers are unused for these instructions and therefore do not need to be saved when the process is descheduled. A timeslice only requires a partial context switch.

A full context switch can occur when the current process is executing any instruction. A full context switch requires the entire 'state' or context of the current process to be stored before it is descheduled. The full context switch can occur for any instruction so the values of A, B

and C registers and floating point unit registers will need to be stored. A full context switch occurs when a high priority process pre-empts an executing low priority process. The high priority process pre-empts the executing low priority process immediately, regardless of the instruction the low priority process was executing. Shadow registers in the CPU are used to store the state or context of the descheduled low priority process, this process will be the first low priority process to execute when no more high priority processes are active. The rescheduling of the low priority process will also require a full context switch to allow all the state of the process stored in shadow registers to be re-loaded.

A partial context switch should be quicker than a full context switch. The difference being the time required to store the state of a low priority process into the shadow registers.

### 2.3.4.5 Interrupts

The hardware scheduler also supports the handling of interrupts and timers. Any event that a process may need to wait for (communication, interrupt or timeout) can be treated as a normal communication. The event causing the interrupt would be mapped to a communication channel (seen as a virtual channel). An interrupt handler is a process waiting on an input from the interrupt 'channel', in the same way it would wait on a communication channel.

The T9000 has four event pins or channels which can be used for control and synchronisation from external events and devices. The event pins can be configured as input or output. As input they can be used to trigger fast processor response to external signals. As output, the process outputting will be descheduled until the external device has performed the necessary handshaking on the event pin. If an interrupt occurs the processor immediately stops executing the current low priority process and begins executing the high priority interrupt handler (requiring a full context switch).

There are two timers: with 1 microsecond resolution and 64 microsecond resolution. The value of the processor timer can be read, or a timer input executed which will deschedule a process until a certain time is reached (interrupt from timer).

### 2.3.5 Memory system

The T9000 programmable memory interface (PMI) connects the crossbar of the T9000 to external memory. External memory (addressing up to 4 Gbyte) supports page mode and is partitioned into four banks which allows mixed memory systems. The timing and width of these four banks can be altered, with support for 8,16,32 and 64 bit data buses. If the 64 bit interface is in use then the memory must be cached.

The T9000 has a 16 Kbyte write back cache. Four independent banks each serve one quarter of the whole memory space. When the T9000 comes out of reset the cache acts as 16 Kbytes of internal memory. This allows the T9000 to operate with no external memory, for small amounts of data and code. The only compiler capable of producing code that may run within 16 Kbytes is the oc (occam) compiler. The minimum size of a linked C binary is greater than 16 Kbytes. At configuration time, the cache can have three modes of operation:

- 16 Kbytes internal memory (only on non 64 bit memory interfaces)

- 16 Kbytes cache

- 8 Kbytes internal memory, 8 Kbytes external memory

All measurements in this thesis use T9000s with 70 nanosecond DRAM (Dynamic Random Access Memory). Data is addressed using a memory page address (Row address) and an offset within that page (Column address). If subsequent memory addresses occur within the same page then it is only necessary to specify the column address. This is known as page mode and reduces the processor cycles required to access the memory.

### 2.3.5.1 Theoretical performance of the PMI

The theoretical performance of the PMI is shown in Table 2.2 for a 20 MHz T9000, giving a processor clock cycle time of 50 nanoseconds. The numbers estimate the rate that external memory can be accessed through the PMI by calculating the number of processor cycles required to transfer a single cache line. This is not affected by the revision type. A cache line is 16 bytes or 128 bits, which is also the size of a memory page. The second column shows the processor cycles required to read 128 bits into the PMI either into or from the external memory.

TABLE 2.2 Theoretical memory performance

| Memory type and access mode | Number of processor clock cycles required for single cache line (16bytes) | Theoretical memory bandwidth |

|-----------------------------|---------------------------------------------------------------------------|------------------------------|

| 32bit, non page mode        | 16                                                                        | 20.0 Mbytes/s                |

| 32bit, page mode            | 10                                                                        | 32.0 Mbytes/s                |

| 64bit, non page mode        | 8                                                                         | 40.0 Mbytes/s                |

| 64bit, page mode            | 6                                                                         | 53.3 Mbytes/s                |

### 2.3.5.2 Memory to memory transfer rates

Table 2.3 shows actual measured performance along with theoretical values based on results in Table 2.2. The results are for memory to memory transfer rates, i.e. the rate at which data can be copied from source to destination. The measurements have been made by copying an array using the T9000 'move' instruction, no page mode. The following points detail the calculation of the theoretical rates:

- Internal to internal, 32 bit interface. To write 32 bits from internal memory to internal memory will require 1 or 2 processor cycles, depending on whether the write and read can be performed in parallel over the 32 bit wide T9000 crossbar. This gives 40 to 80 Mbytes/s. There are four ports between internal memory and the central crossbar of the T9000, see Figure 2.4, each port reads from/writes to one quarter of internal memory. The relative position of the two 32 bit words dictates whether more than one port can be used per clock cycle, i.e. 1 or 2 processor cycles required to transfer a single 32 bit word.

- Internal to external, 32 bit interface. The external bandwidth from the PMI has been presented as 20 Mbytes/s in Table 2.2, requiring 16 processor cycles to transfer a single cacheline from the PMI into external memory. The extra cycles required are those to read the data from internal memory into the PMI. This should be at most one processor cycle for every 32 bits, or 4 per cacheline, which would reduce the bandwidth to 16 Mbytes/s. If the read from internal memory is overlapped with the writes to external memory the performance would stay at 20 Mbytes/s. This is theoretically possible, there are separate ports onto the T9000 crossbar for the PMI and internal memory (see Figure 2.4).

- External to internal, 32 bit interface. The same calculation as for internal to external.

- External to external, 32 bit interface. The bandwidth between two areas of external memory should be half of the rate data can be read into through the PMI, i.e. 10 Mbytes/s.

- External to internal, 64 bit interface. The external bandwidth into the PMI has been presented as 40 Mbytes/s. Again the cycles required to get the data into internal memory from the PMI must be added. At most this would be two processor cycles for every 64 bits, which reduce the performance to 32 Mbytes/s.

**TABLE 2.3 Memory to memory transfer rates, Revision D02 T9000s at 20 MHz, non page mode**

| Array location                                    | Memory interface | Measured memory to memory transfer rate | Number of processor clock cycles required for single cache line | Theoretical rate (Mbytes/s) |

|---------------------------------------------------|------------------|-----------------------------------------|-----------------------------------------------------------------|-----------------------------|

| Source: Internal RAM<br>Destination: Internal RAM | 32 bit           | 66.4 Mbytes/s                           | 4 to 8                                                          | 40.0 to 80.0                |

| Source: Internal RAM<br>Destination: External RAM | 32 bit           | 10.8 Mbytes/s                           | 16 to 20                                                        | 16.0 to 20.0                |

| Source: External RAM<br>Destination: Internal RAM | 32 bit           | 10.8 Mbytes/s                           | 16 to 20                                                        | 16.0 to 20.0                |

| Source: External RAM<br>Destination: External RAM | 32 bit           | 9.22 Mbytes/s                           | 32                                                              | 10.0                        |

| Source: External RAM<br>Destination: Internal RAM | 64 bit           | 16.4 Mbytes/s                           | 8 to 10                                                         | 32.0 to 40.0                |

The three benchmarks which use both internal and external memory result in half the maximum bandwidth expected. This has been investigated by using a scope to monitor the processor cycles required to move data between the PMI and internal memory. For a 32 bit interface I had expected 0 or 1 processor cycles to move the data from the PMI into internal memory, corresponding to the range in theoretical values in Table 2.3. Using a scope 3 cycles were observed to move data between the PMI and internal memory. For the 32 bit interface this reduces performance from 16 Mbytes/s (assuming 1 processor cycle for PMI to internal memory) to 10.8 Mbytes/s (using 3 processor cycles for PMI to internal memory).

The extra cycles required to read or write data between the PMI and internal memory also occur when a link reads/writes from the PMI. These limitations are demonstrated by communication benchmarks presented in the next chapter, the evaluation of the technology.

The problem has been partly solved on the revision E03 T9000. The external to internal memory bandwidth for a 32 bit interface is now 15.4 Mbytes/s. Which is still below the theoretical range of 16 to 20 Mbytes/s, but is a large improvement over 10.8 Mbytes/s for the revision D02. The memory performance will also increase linearly for 25 MHz T9000s, initial tests with 25 MHz revision E03 T9000s show 19 Mbytes/s external to internal transfers with a 32 bit interface.

The T9000 has 4 bi-directional links running at 100 Mbytes/s, corresponding to approximately 75 Mbytes/s. With the revision D02 T9000 there is a severe bottleneck in the memory interface when the links must be driven from external memory. This situation is improving with the new revision E03 of the T9000.

The external to external and internal to internal results are as expected. The slight reduction in performance for external to external is caused by the extra DRAM refresh cycles which are required, loop overheads and the time for the processor pipeline to start.

### 2.3.5.3 Memory transfers using the cache

Memory transfers which fit into the cache will be cached by the first memory transfer, subsequent transfers will effectively be performed as internal memory transfers. Larger arrays will not fit into the cache, at which performance will be limited by the external memory interface. The result is that the performance of a memory transfers can vary from the 9.22 Mbytes/s to the 66.4 Mbytes/s in Table 2.3 depending on whether the message will fit into the cache. The size of the array to be transferred is crucial.

### 2.3.6 T9000 Known Hardware Bugs and Problems

The experiences and results presented within this thesis are largely based upon the Gamma D02 revision of the T9000. There are four major problems with this revision affecting work within this thesis:

- The maximum stable clock speed is 20 MHz, some chips limited to 10 MHz, this compares to the design speed of 50 MHz.

- Double scheduling bug, causing a transmitting process to be rescheduled twice, can crash entire application

- Cache corruption bug, transmitted data is corrupted, crashes entire application

- The external memory interface is slow, causing up to a 50% degradation in performance compared to theoretical maximums

Further details of these problems (and other less serious bugs) and how I limited their effect are given in the relevant sections as they arise. General limitations related to the T9000 and software support are also presented as they arise.

The Gamma E03 revision has become available at the time of writing this thesis. The processor speed is still limited to 20 MHz, however the two main hardware bugs (cache corruption and double scheduling) have been removed. The external memory interface has also been significantly improved. For communications to internal memory or cache then the performance has remained identical. My initial tests suggest that the Gamma E03 can be used to build stable and reliable T9000 systems for arbitrarily complex traffic patterns and network configurations. The manufacturer also claims that the Gamma E03 will operate reliably at 25 MHz. I have yet to test this claim.

## 2.4 The C104 Packet Switch

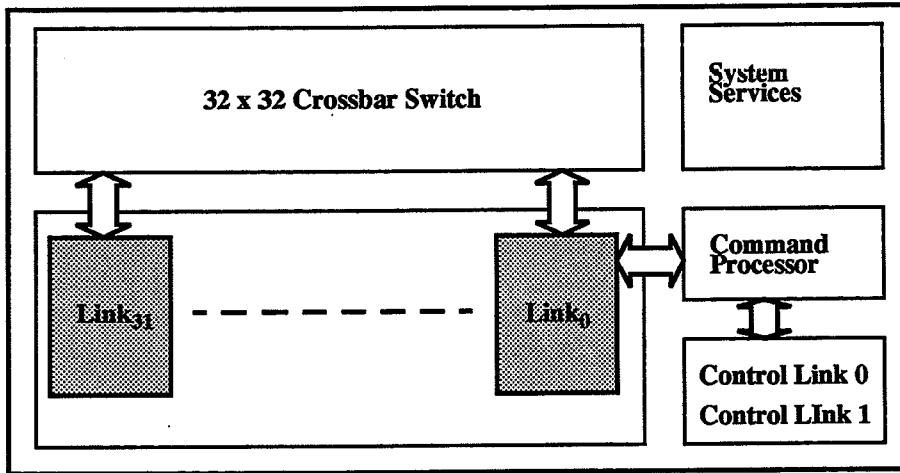

The C104, see Figure 2.12, developed by SGS Thomson, is an asynchronous 32-way dynamic packet switch with DS links operating at 100 Mbits/s. It can interconnect up to 32 devices (for instance T9000s), and may be cascaded to form large switching networks. I have carried out tests running C104 links at 200 Mbits/s, investigations are under way into the reliability of running links at this speed.

FIGURE 2.12 The C104 Packet Switch

The technique used to route packets through a C104, to select the required output link, is that of interval labelling. In this technique each link of a C104 is assigned a range of device labels (a device interval) which indicates the physical devices that are accessible via that link. Each physical device has a unique label associated to it. When a packet enters a C104, the device label contained in the packet header is compared to the device intervals. The output link whose device interval contains the required device label is selected to route the packet out of the C104.

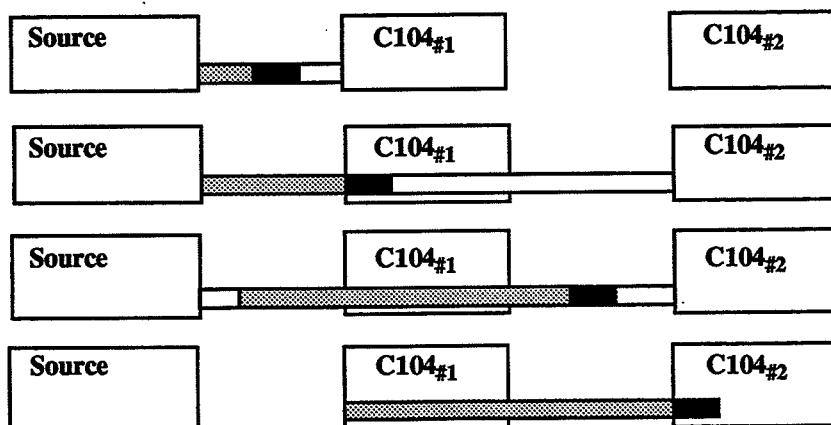

The C104 uses wormhole routing (see Figure 2.13). A routing decision is made as soon as a packet header enters the C104. This routing decision leads to the creation of a temporary circuit through the C104 which vanishes as the packet terminator passes through. As a consequence of wormhole routing a single packet may pass through multiple C104s at any one time and the header may be received at the destination before the whole packet has been transmitted, thus minimizing the time required to transmit the packet through the network.

FIGURE 2.13 Wormhole Routing

In switching networks, there will often be many possible routes that a packet may take to reach a specified destination. Should one of these links be in use or in error then it is desirable that an alternative link be chosen. To fulfil this requirement the C104 supports grouped adaptive routing. Output links can be grouped so that packets routed to the first link of a group can be routed to the other links of that group should the first link not be available.

In addition to grouped adaptive routing the C104 supports universal routing. In this technique packets are first sent by a C104 to a random device (another C104). At this device, the packets are then routed to their final destination. The initial randomisation spreads the load across the network, reducing hot spots. Hot spots are localised bottlenecks in a network.

#### 2.4.1 Hardware Bugs

There have been two major revisions of the C104 available during the work carried out for this thesis: revisions alpha and beta. There are no current plans for further revisions.

The alpha revision suffered from errors on the selection of interval separators, regarding whether the upper limit of the interval range was inclusive or not. The chip behaved differently from the hardware manual. This problem was solved for the beta revision.

On both alpha and beta revisions the links run at half the speed they are programmed to run at. This is solved by programming twice the speed required. The core speed of the C104 is also half the speed programmed, 15 MHz core speed is adequate for 100 Mbits/s link speed, so 30 MHz is programmed.

A link that is in error and part of a link group will still be selected to be used for output. The packets sent to this link will be discarded.

### 2.5 The T9000 Toolset Development System

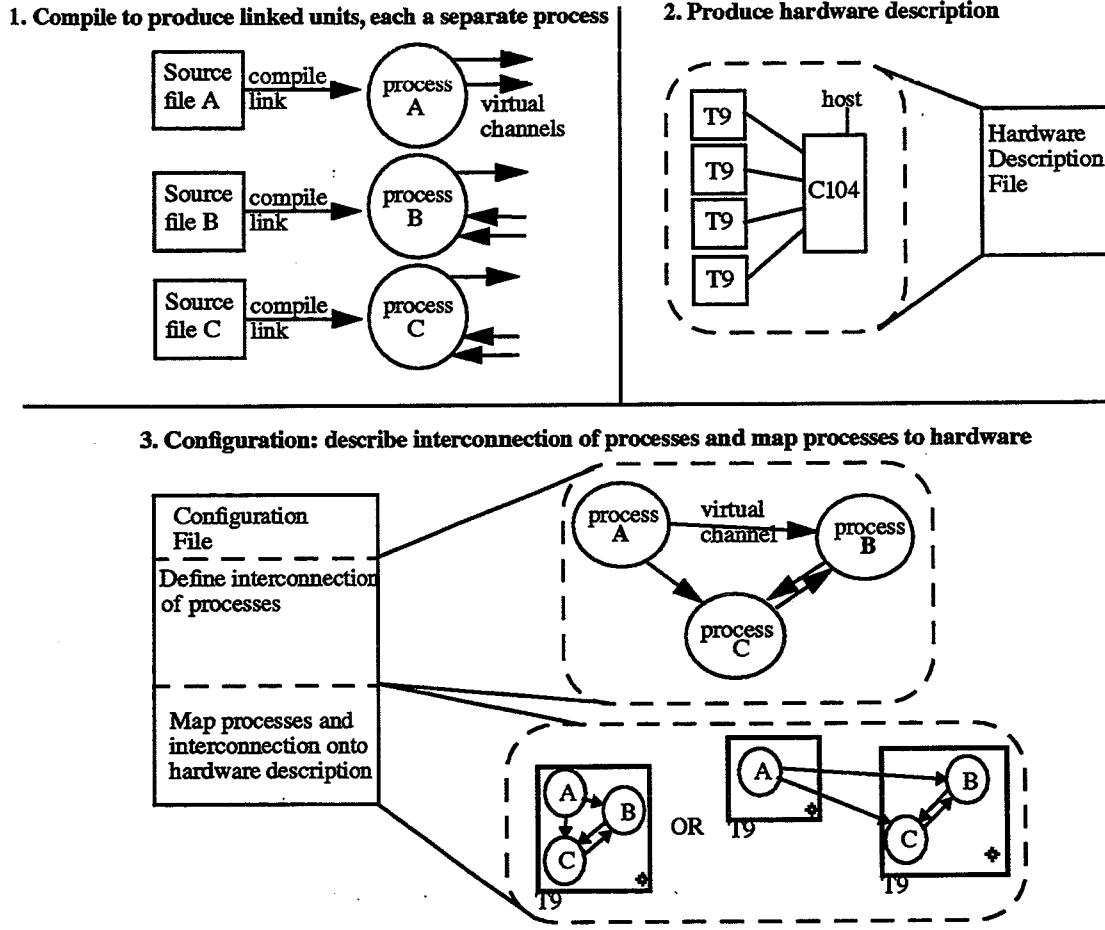

Programs and applications for T9000 systems are developed on a host system using a T9000 toolset. For the work in this thesis that host was a Sun workstation. The toolset allows the user to compile code to be used for processes, define the interconnection of these processes and map these processes onto Transputer hardware.

Creation of executable code for a Transputer or Transputer network requires several stages involving the use of specific tools at each stage. The stages are:

- Compile and link source code for individual processes, creating a linked unit for each process.

- Produce a description of the hardware. A network initialisation file is produced from this description which can initialise the hardware (T9000s and C104s).

- Define the interconnection of processes by virtual channels, and map the processes and their interconnection onto the hardware.

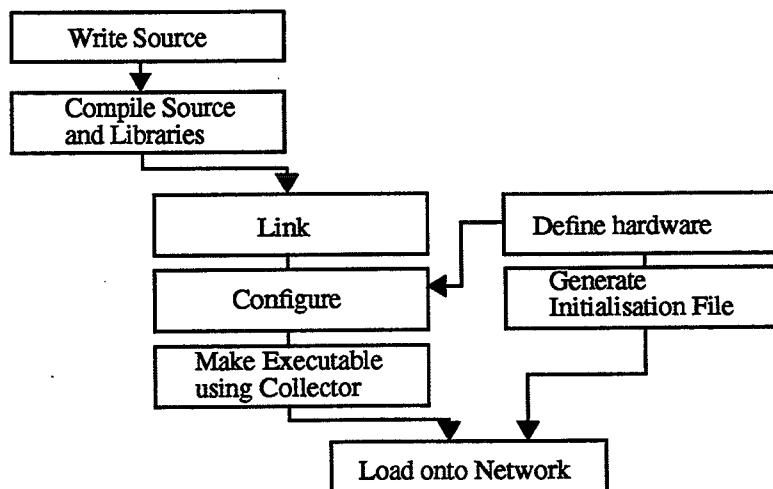

Figure 2.14 relates these three steps to the Transputer model of concurrency presented in Section 2.1, "Transputers,".

FIGURE 2.14 Overview of toolset

I now describe the stages of development in more detail. Figure 2.15 shows the main phases in development and Figure 2.16 details the tools that are used to achieve them.

FIGURE 2.15 Main Toolset Development Stages

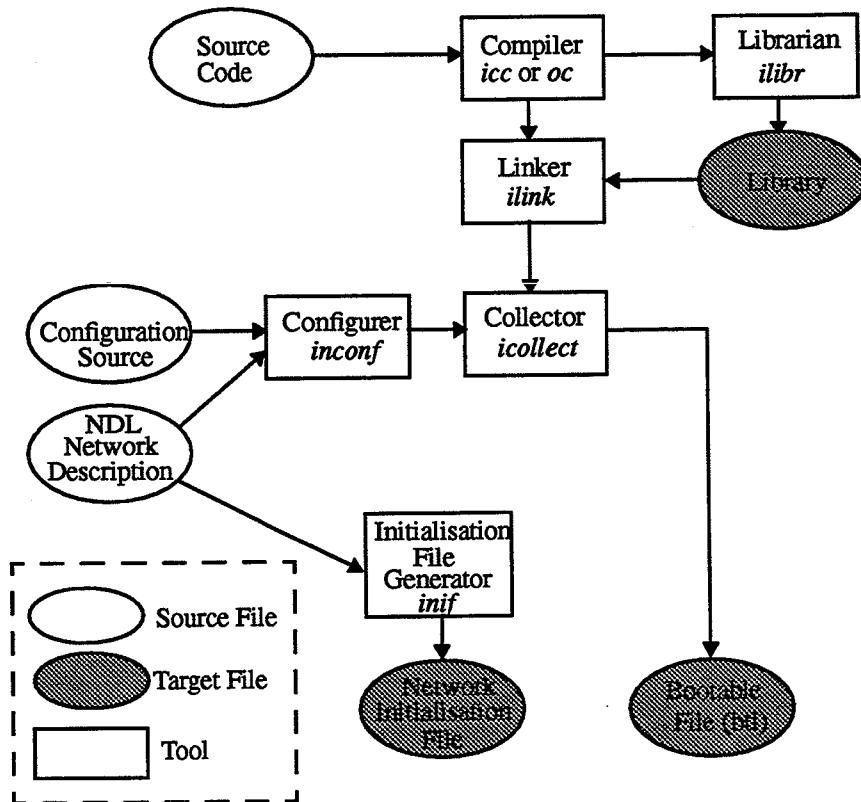

Source can be written in C or occam. Each source file is compiled using the appropriate language compiler (*oc* or *icc*) to produce one or more compiled object files. Commonly used object code can be combined into libraries using the librarian tool *ilibr*. The compiled object files and libraries are linked together using the linker *ilink*. This generates a single linked unit.

The configuration description is processed by the configuration tool *inconf* to produce a configuration data file.

The configuration description refers to a description of the hardware on which the code will run. The hardware description is written in NDL (Network Description Language).

T9000/C104 networks have a system of control links which are separate from the data network. The control network is used to configure the T9000s and C104s and in the case of the T9000 load the initial bootstrap code. The information required to perform this initialisation is held in the network initialisation file, which is generated by the initialisation file generator *inif* from the hardware description.

Before a program can be run it must be made executable. This involves adding bootstrap and loading information and is performed using the collector tool *icollect*. The configuration binary file generated by the configurer is read by *icollect* which generates a single executable file for a T9000 network, a *btl* file. A transputer network is initialised using the network initialisation file and the code is loaded onto the T9000s from the *btl* file.

FIGURE 2.16 Key Programs used in Developing an Application

### 2.5.1 Problems with the Toolset

The general problems of the Toolset environment are presented within this section. More detailed specific problems that apply to a certain areas of work within the thesis will be discussed later as they arise.

The list of tools that the user is required to use is long and the dependencies are complex. Figure 2.16 only shows the most important tools that are required to develop a Transputer application, there are more tools that would further complicate the explanation given. For example, there are a separate tools for aiding the writing of network description files.

There are many important areas of software that are not covered by the toolset. A hardware 'spy' is an important area not covered by the toolset. If the user wishes to confirm that a certain network exists or list the devices present in a network then a 'spy' is used. Unfortunately, this program is not supported as part of the toolset and has been unusable in any work carried out for this thesis. To discover whether all devices were present in a network the only method was to write an application that used all the devices and try to configure and load it.

A correctly operating 'spy'<sup>4</sup> would provide the following essential functionality:

- Recover if an error occurs in the network (currently the spy does not)

- Validate if a network matches a given network description file (NDL)

- Produce an NDL file for a physical network

- Tests the data links of all devices

The C104 has many attributes which are contained in the network description file (NDL), including information on intervals and grouped adaptive routing. The toolset was supposed to provide an automated procedure for producing NDL files, and the attributes it contains. The bugs in the tools that carried out this process were so severe that I had to write all NDL files used within the work for this thesis.

## 2.6 Hosting T9000 Systems

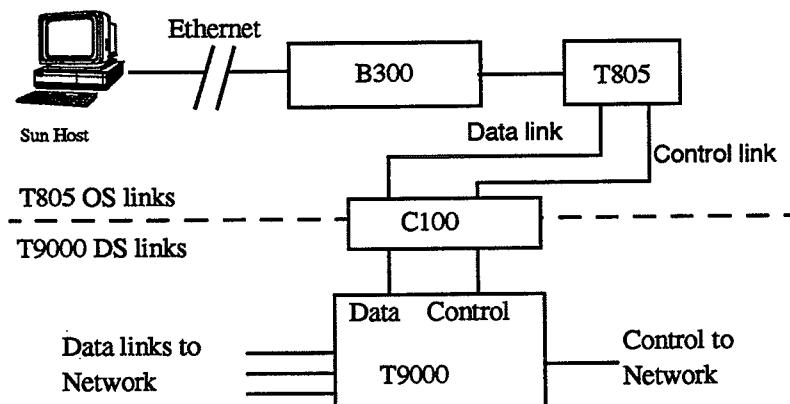

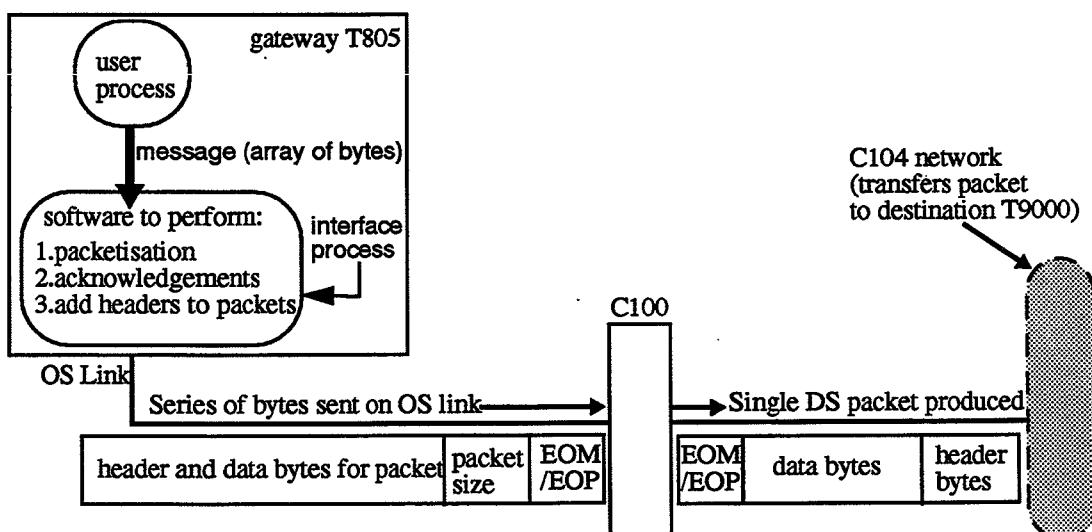

A T805 Transputer [11] initializes and loads applications onto the T9000 network. The T805 is the previous generation of Transputer to the T9000, which uses four serial bi-directional OS (over sampled) links running at up to 20 Mbits/s. The T805 is connected to a SUN workstation via an Ethernet-to-OS link converter (B300). A single link of the T805 is used to configure the T9000 system using the control link via a C100 [3] protocol converter. The C100 is used to interface the DS link to an OS link, since the DS link is based on the exchange of packets and the OS link on the exchange of bytes. Another link of this T805 is used to load applications via a T9000 data link (see Figure 2.17). Access to file systems and host system services by the T9000s is provided by the SUN workstation via the T805.

After a network has been initialised the application must be loaded onto the network. The software used to perform this has not been presented, there are multiple versions and methods, which often vary from manufacturer to manufacturer. The main problem with the particular type used within the scope of this thesis was the complete absence of error recovery

---

4. A spy with the required functionality is now being produced at CERN as part of the ESPRIT project ARCHES [10].

and fault tolerance. Any error with the host link would result in the shutdown of the entire system. The bandwidth between the network and the host was also very low (20 to 30 Kbytes/s), which became a problem when large amounts of code and data were required. All available host systems lack the following essential functionality<sup>5</sup>:

- Report errors in a way such that the user can readily identify the physical device that has suffered an error. Currently the relation of logical to physical device numbers is very difficult.

- Attempt to recover the error, instead of immediately exiting

Bandwidths to host should be at least an order of magnitude higher

FIGURE 2.17 Hosting T9000 Systems

## 2.7 The GPMIMD Machine

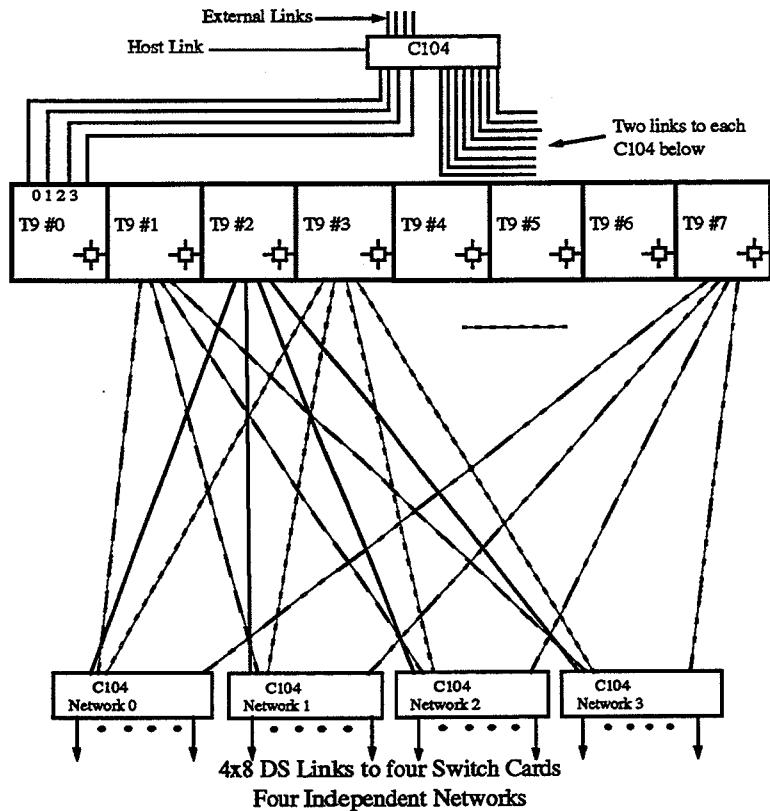

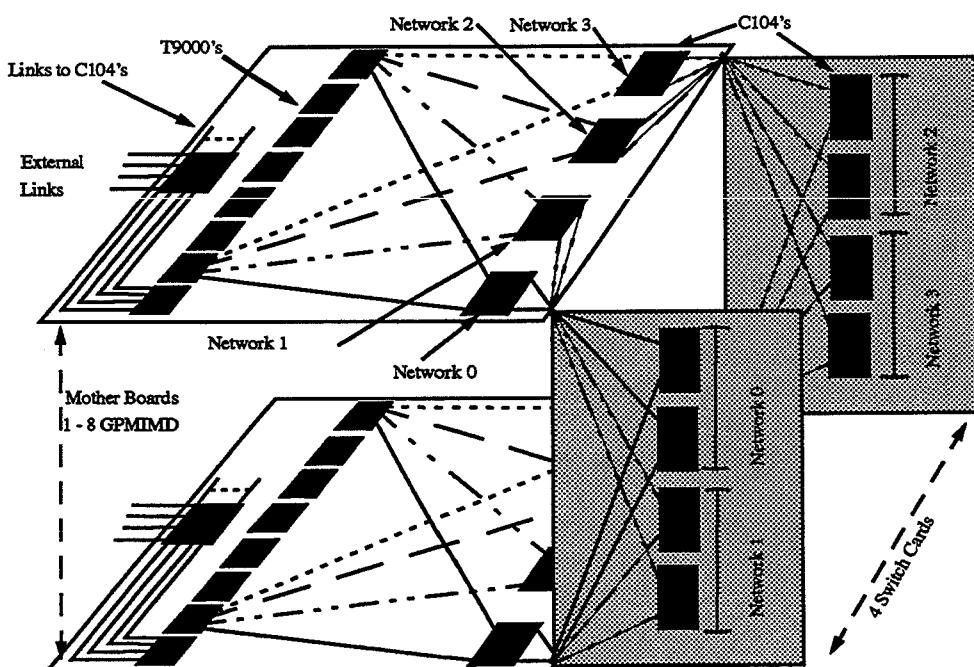

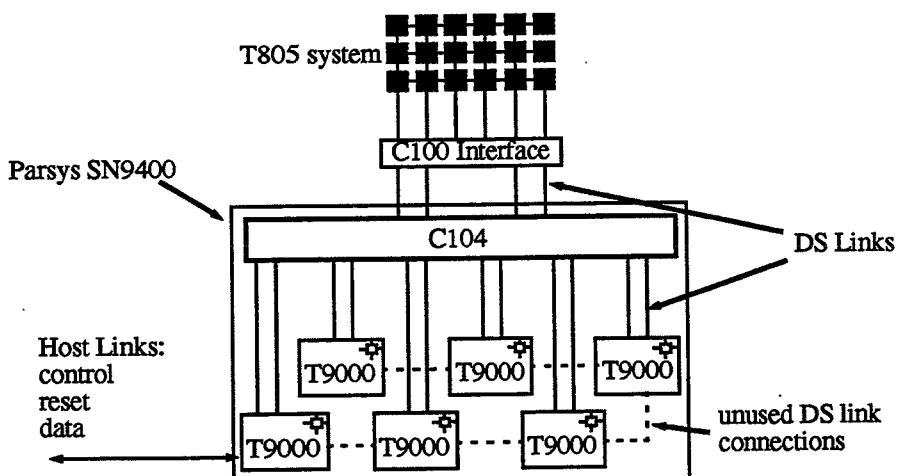

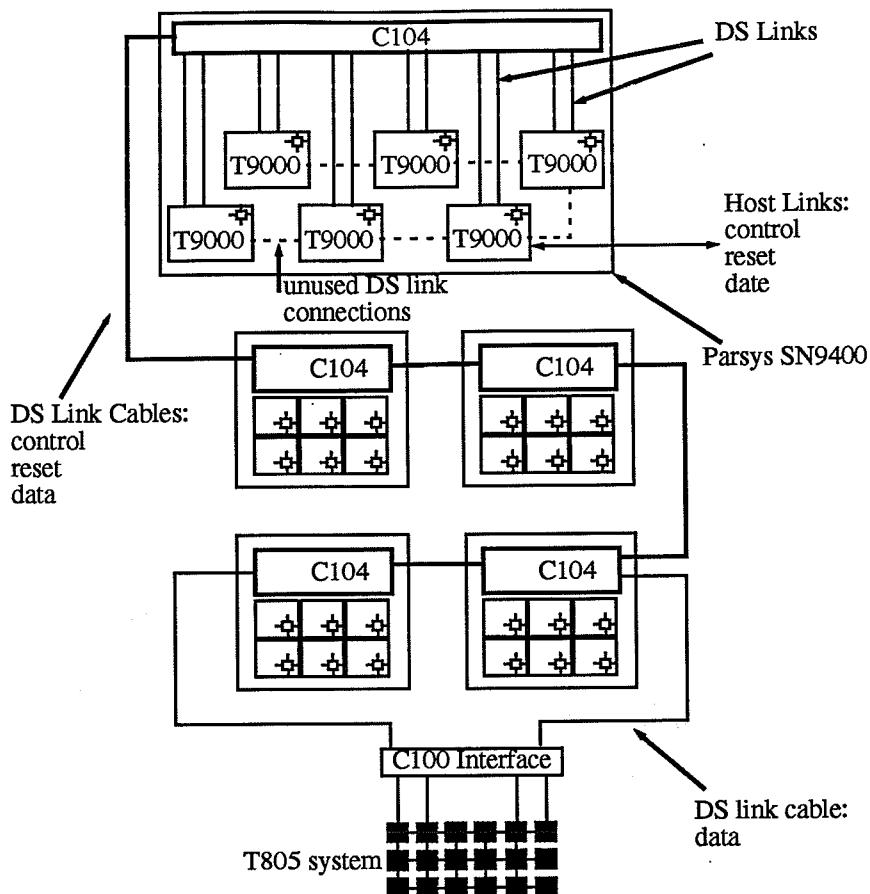

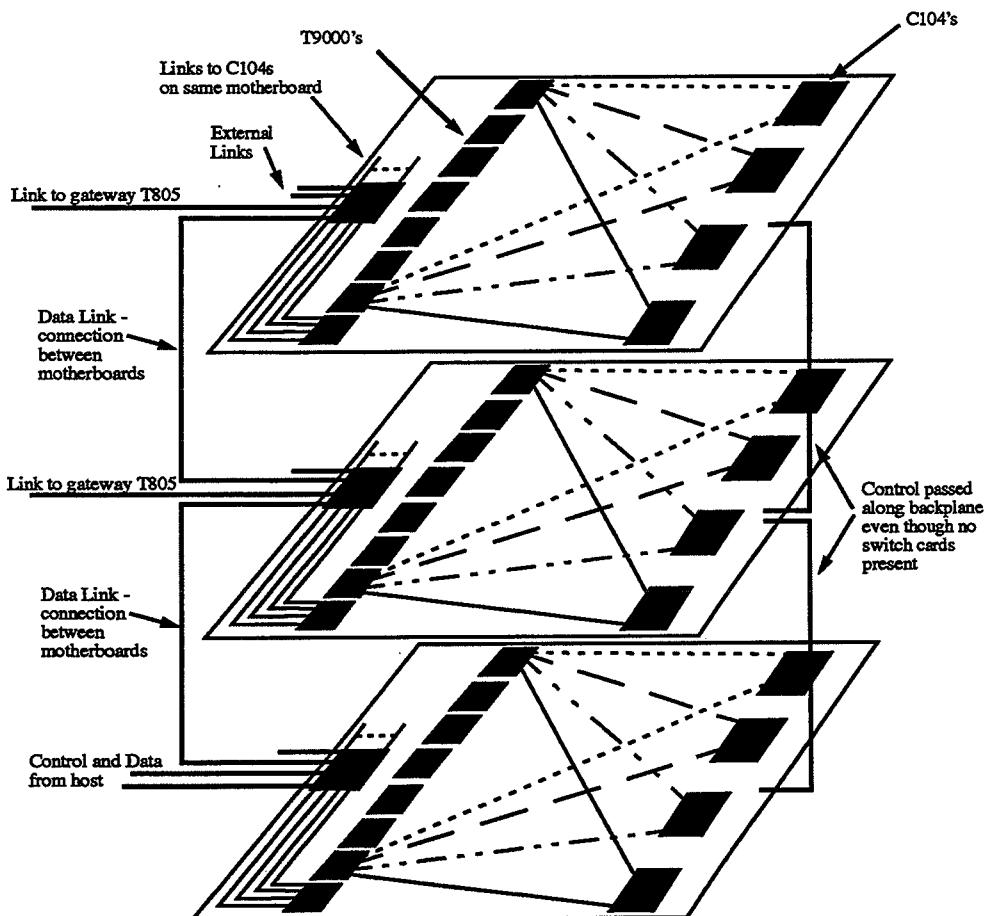

The GPMIMD machine has been designed as a switching fabric of 1000 DS links interconnecting up to 256 T9000 processors. In its present configuration 56 C104s provide full interconnectivity between 64 T9000s. The T9000s are mounted on small individual plug-in boards based on the SGS Thomson HTRAM (High performance TRAnsputer Modules) standard. A single size 4 HTRAM holding a T9000 and 16 Mbytes of memory is approximately 10 cm by 10 cm, and plugs into matching connectors on the motherboards.

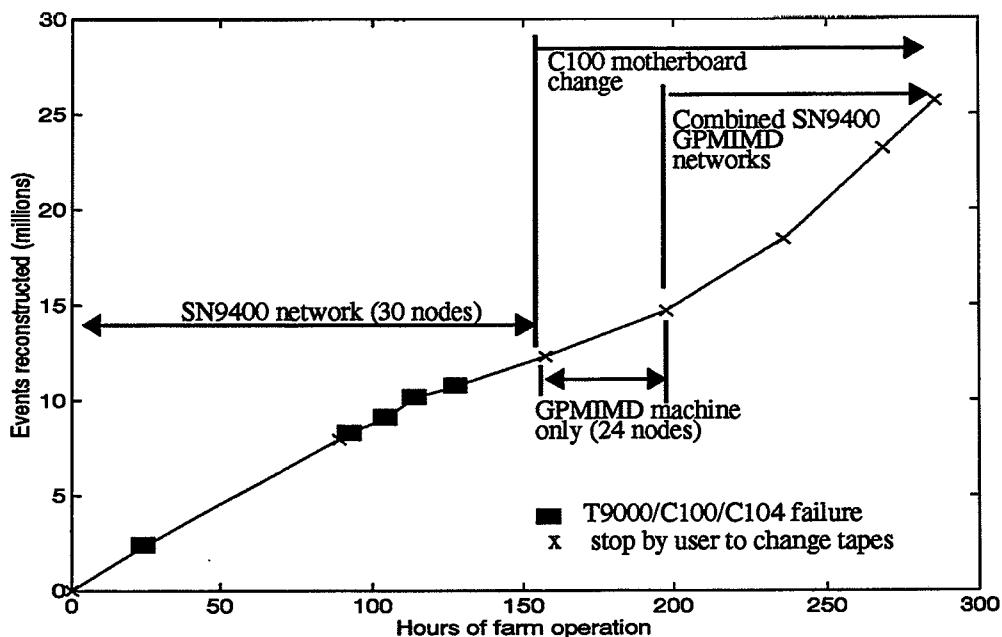

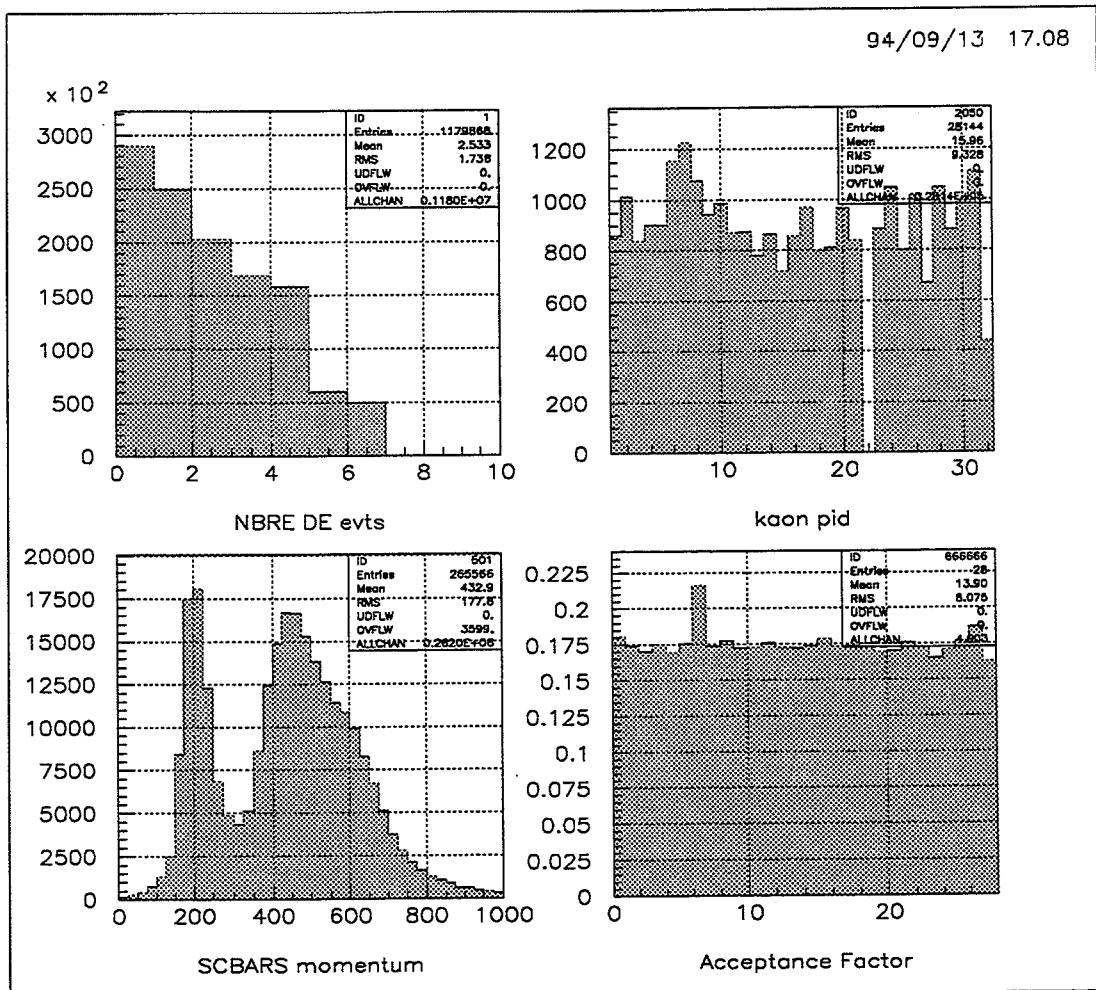

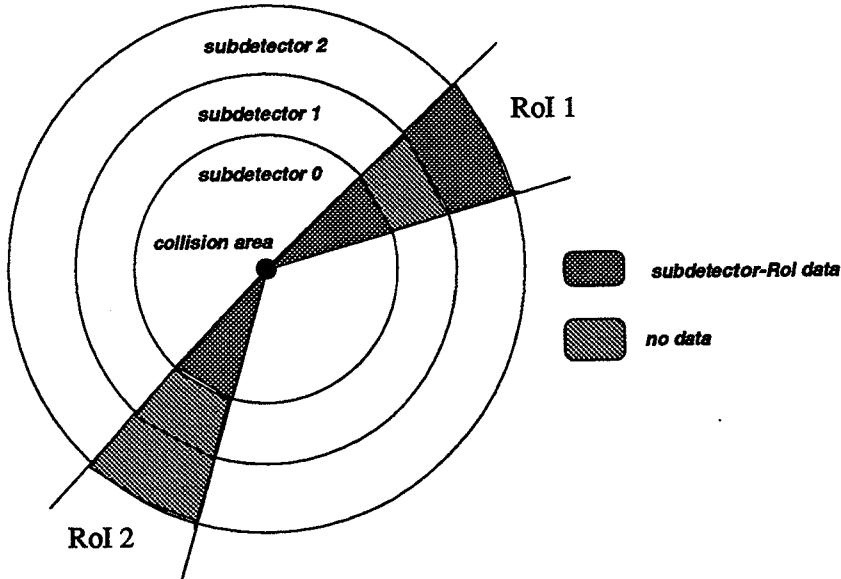

The present configuration contains a total of 8 motherboards (see Figure 2.18) each carrying 8 T9000s and 5 C104s. In addition, 4 switch cards, each carrying 4 C104s, provide the inter-motherboard connectivity (see Figure 2.19). Four independent folded Clos networks [12] have been implemented to efficiently use the four DS links connected to each of the T9000s.

One motherboard C104 is used for connection to external devices and as a control link fan-out. The other 4 C104s provide the 4 networks that connect to all T9000s, there are also links from each of these 4 C104s to the C104 with external connections.

---

5. Host systems are now being developed at CERN with the required functionality as part of the ESPRIT project ARCHES.

## The T9000 Transputer and DS links

FIGURE 2.18 A GPMIMD Machine Motherboard

FIGURE 2.19 The GPMIMD Machine: 8 horizontal motherboards and 4 vertical switch cards

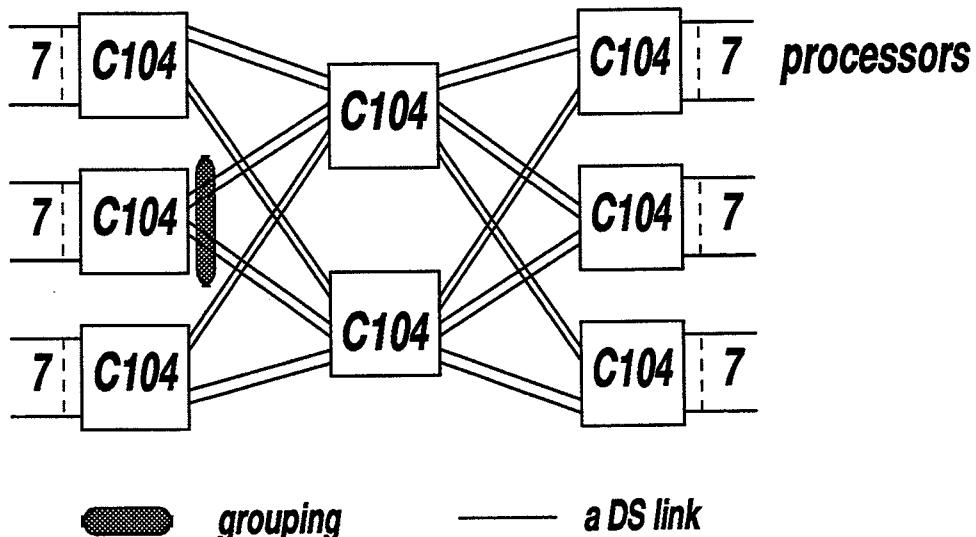

The topology of the Clos network for a 48 node, 6 motherboard machine with 2 switch cards is shown in Figure 2.20. This topology has been presented because all communication benchmarks and other communications measurements presented within this thesis were carried out on this topology. Each C104 on the left and right represent a single C104 on a motherboard and the switch card C104s are those in the centre. The 4 links between each motherboard and switch card C104 may be grouped into 'bundles' of 1 to 4 links. These links are performing grouped adaptive routing, as presented in Section 2.4, "The C104 Packet Switch,". A single network may consist of 3 to 12 links between the motherboards and the switch cards from one half of the machine to the other.

A message between T9000s on the same motherboard passes through one C104, a message between T9000s on different motherboards passes through three C104s. The layer of C104s connected to the T9000s is called the terminal stage of the Clos; the other stage is called the centre stage.

FIGURE 2.20 A Single (of 4) GPMIMD Machine Clos Network

## 2.8 The TransAlpha Module

The low clock speed of the T9000 (among other factors) has resulted in poor computational performance compared to its communication abilities. The resulting imbalance is being addressed by the TransAlpha module. The performance of the T9000 for communications, context switching and interrupt response is not matched by the low computational performance of a 20 MHz T9000 processor.

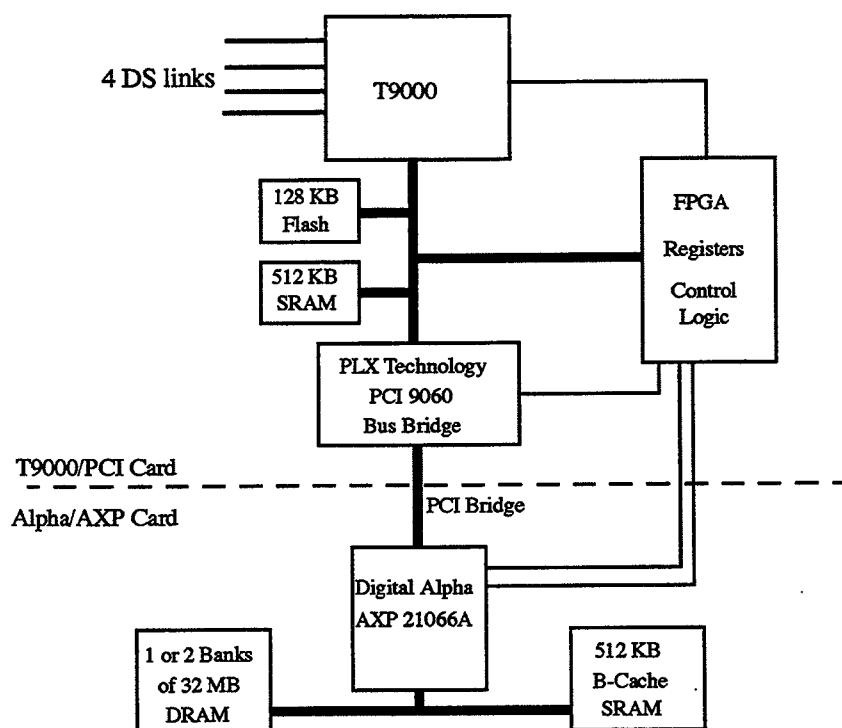

A high performance computing node has been designed using a T9000 as a communications controller for a DEC Alpha 21066A microprocessor [13]. This hybrid node is called the TransAlpha module, and is designed to combine the complementary strengths of the two processors. The module is being developed by Parsys in collaboration with my group at CERN.

Figure 2.21 shows the layout of the TransAlpha module, which connects the T9000 and Alpha via a 32-bit PCI standard bus. The module conforms to the SGS Thomson HTRAM standard and can therefore fit directly into existing T9000 systems. The TransAlpha module is a size 8 HTRAM, double the size of the current T9000 HTRAMs used in the GPMIMD machine. All components fit into the single HTRAM with dimensions of approximately 20 cm by 10 cm.

The hardware allows the direct replacement of two GPMIMD machine T9000 HTRAMs with a single TransAlpha module. The T9000 HTRAMs can be removed, and the TransAlphas plugged in to replace them. The result is that a single motherboard which now contains 8 T9000s can have them replaced with 4 TransAlpha modules. The full capacity of the present machine if all T9000s were replaced would then be 32 TransAlphas.

The module comprises of four parts:

- A 233 MHz 21066A DEC Alpha microprocessor with 512 Kbyte external cache and 32 or 64 Mbyte of 64-bit DRAM connected to its local bus.

- A 20 MHz T9000 with 512Kbyte of 32-bit SRAM and 128Kbyte of flash ROM.

- Bus bridge between T9000 local bus and PCI bus

- FPGA logic attached to the T9000 local bus used to adapt the T9000 bus to the PCI 9060 and to initialise and control the Alpha processor and the PCI 9060.

The occam programming environment is not available on these boards. The only option is the C programming environment, using extensions to allow the Alpha access to the point to point communication channels. The CSP model on which occam relies is still implemented, with some restrictions.

The communications performance of the TransAlpha relies heavily on the performance of the T9000 external memory interface. Results produced using the revision D02 T9000 have suffered from the limitations of the external memory interface. Work is currently ongoing to produce TransAlphas with revision E03 T9000s that will improve performance.

### 2.9 Conclusions

The technology used within the thesis have been presented. The T9000 and C104 have been shown to support functionality which is crucial to performance in multi-processor systems: concurrent communication and computation, fast interrupt response and context switching times. This performance is quantified in the following chapter.

---

## Conclusions

---

**FIGURE 2.21** The TransAlpha Board Layout

---

## **The T9000 Transputer and DS links**

---

# Chapter 3

## Evaluation of technology

In this chapter I present an evaluation of the technologies used within this thesis. Communication and computation benchmarks are presented along with context switching and interrupt response performance.

A comparison is then made to other platforms, including the PowerPC. I will show that in the areas crucial to multiprocessing the T9000 compares favourable to other less integrated technologies.

I have identified a set of critical factors which affect the performance of multi-processor systems, I evaluate these parameters for the T9000 and C104 within this chapter. These parameters are summarised at the end of the chapter in Table 3.6, along with their general relevance to multi-processing. In chapter 5, I use the performance of the T9000 and C104 compared to the requirements of the LHC to quantify the importance of each parameter.

General communication performance and networking results use a 48 node revision D02 T9000 machine using alpha C104s. Context switching performance and interrupt response related benchmarks only requiring small numbers of T9000s use revision E03 T9000s and beta C104s.

### 3.1 Communication Benchmarks

#### 3.1.1 Single Link Results

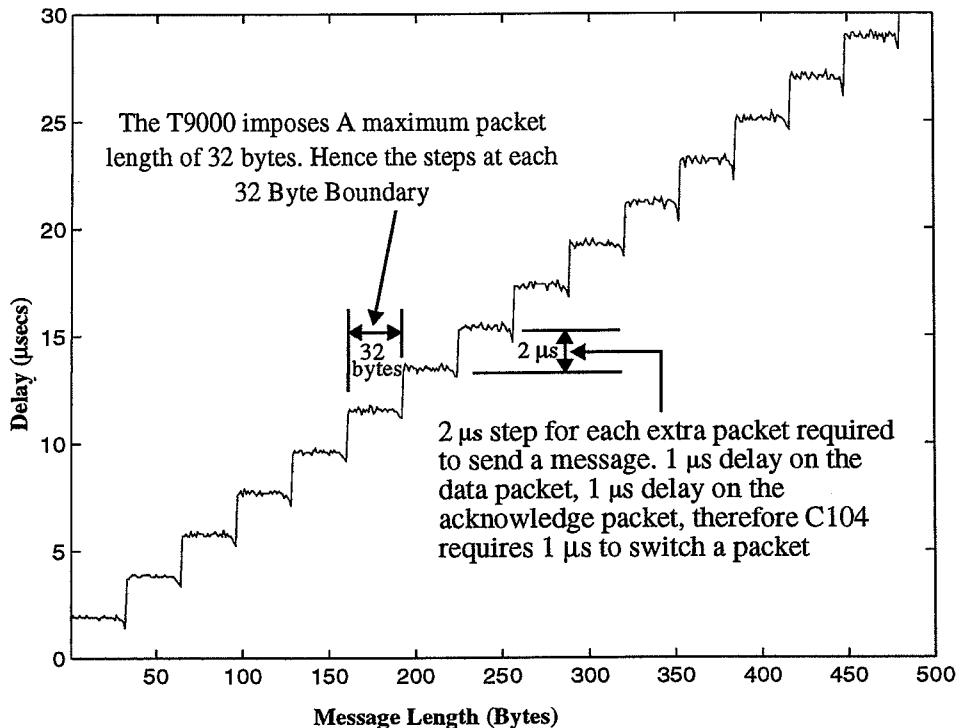

The time between the sending of a short packet (one word) and the reception of an acknowledgement packet between two directly connected 20 MHz revision D02 T9000s was measured to be 7.5  $\mu$ secs. The additional delay incurred by connecting two T9000s via a C104 was measured to be 1  $\mu$ sec (Figure 3.1 shows the difference in elapsed time for a message between two directly connected T9000s and T9000s connected via a C104). The curve intercepts the y-axis at 2  $\mu$ sec which represents the extra delay in transmitting two packets: an acknowledgement and data packet. For a single message the data packet itself will suffer a delay at the C104 and also its corresponding acknowledgement packet, hence the intercept is at 2  $\mu$ sec, not 1  $\mu$ sec. Therefore the C104 requires 1  $\mu$ sec to switch a packet.

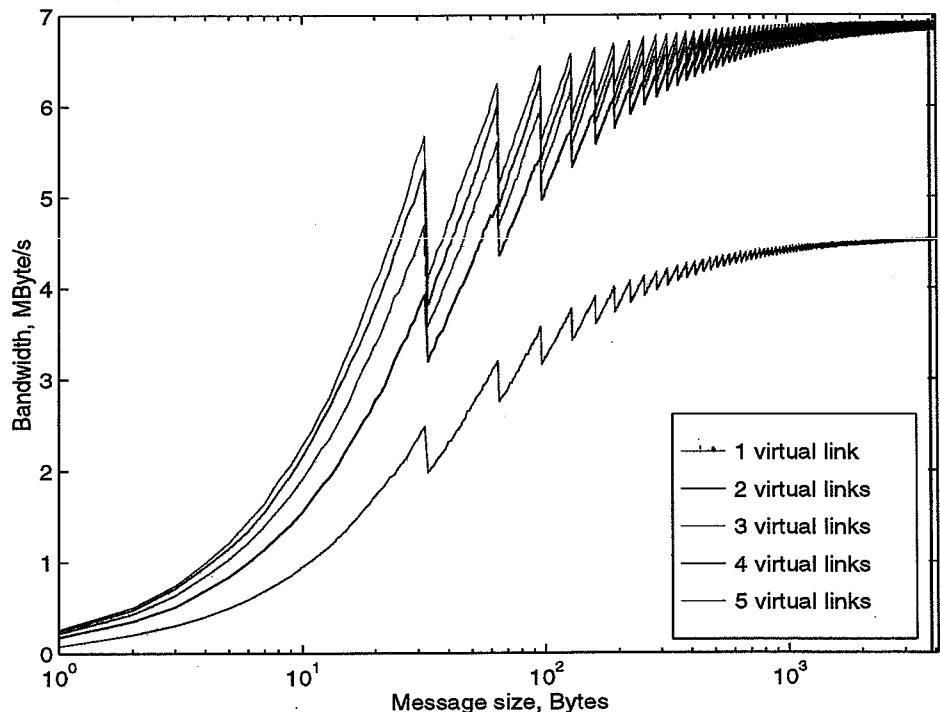

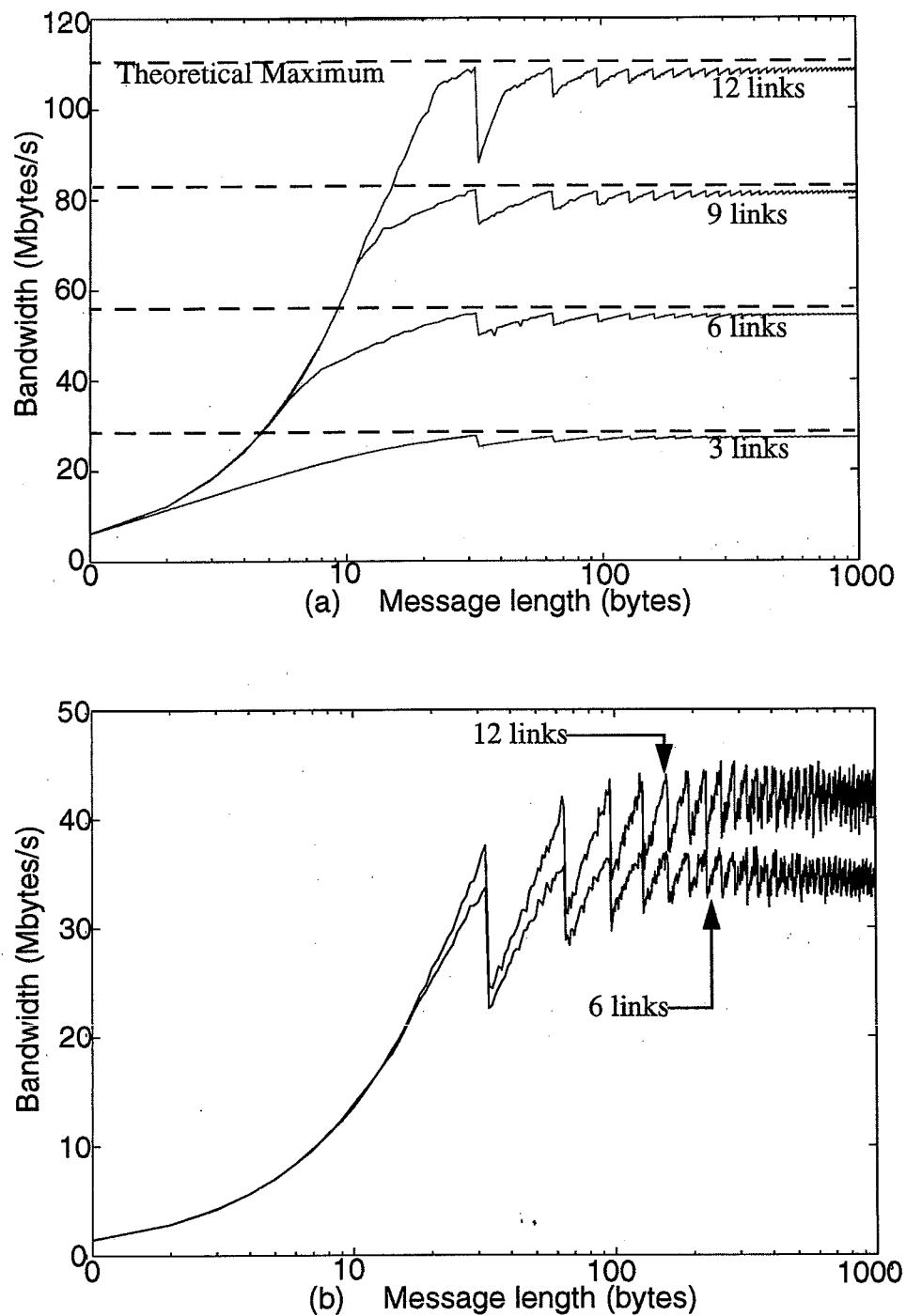

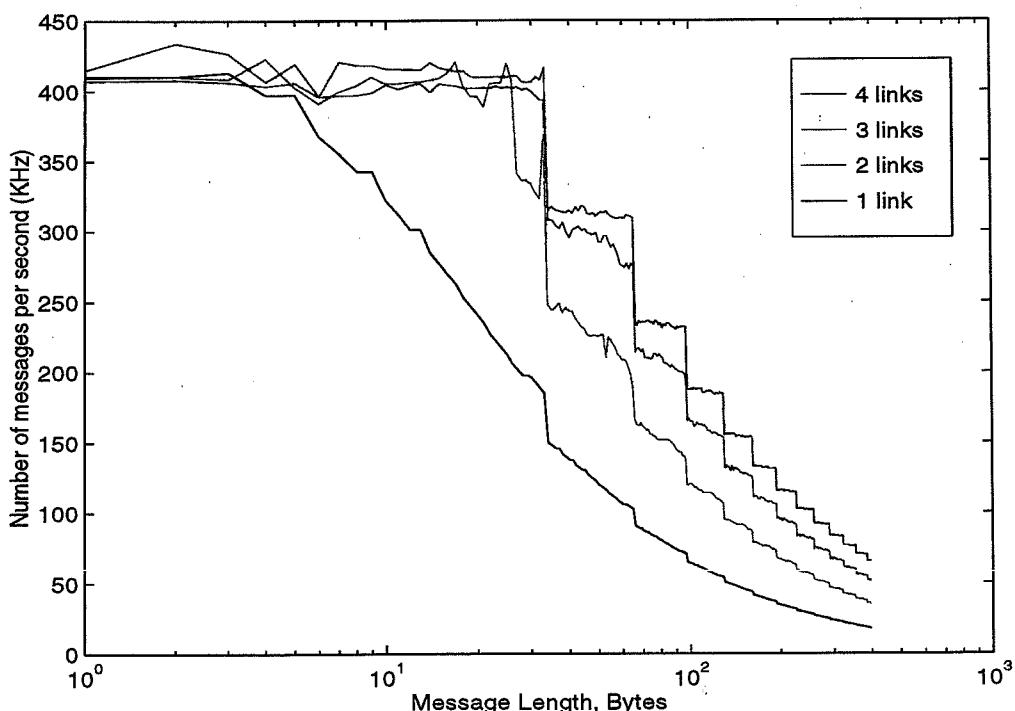

In Figure 3.2 the dependency of the bandwidth between two directly connected 20 MHz revision D02 T9000s on the number of virtual links used is presented. The figure shows the bandwidth as a function of message size for one to five virtual links mapped onto a single physical link. The bandwidth represents the usable amount of data exchanged between two T9000s running at 20 MHz. The discontinuity in bandwidth at each 32 byte boundary is due to the packetisation performed by the VCP. A 32 byte message requires a single packet to be

sent and acknowledged, whereas a 33 byte message requires two packets to be sent and acknowledged.

**FIGURE 3.1** Latency due to C104. 20 MHz D02 T9000s, 100 Mbits/s links, 16 K internal memory

**FIGURE 3.2** Single link bandwidth, uni-directional. 20 MHz D02 T9000s, 100 Mbits/s links, 64 bit interface, 8K cache 8K internal memory, directly connected links

In Figure 3.2 the increase in bandwidth for more virtual links can be accounted for by the increased packet inter-leaving performed by the VCP and more efficient use of its pipelined architecture. When multiple virtual links are used, packets for different virtual links may be transmitted independently of the reception of acknowledge packets on other virtual links. If a single virtual link is in use, a packet is sent, then the virtual link (and physical link) is idle until the acknowledge is received, which reduces the bandwidth. If another virtual link is in use, the first virtual link (waiting for an acknowledge) stays idle but the second can use the link. If enough virtual links are used then the bandwidth limit will be that of the VCP, or the limit of the memory to supply the VCP with data. A constant message start up time accounts for the reduced bandwidths for smaller packets.

The results give a maximum for the achievable performance of a 20 MHz T9000 processor. Conditions have been chosen such that all data is read from the cache memory and therefore the external memory interface of the T9000 does not have to be used.

The theoretical maximum of a DS link running at 100 Mbits/s using single byte headers is 9.55 Mbytes/s [14]. The measured limit is only 7.0 Mbytes/s, this is not a problem of memory bandwidth, all data resides in the cache. The problem is the limit of the VCP at 20 MHz, it is the only possible bottleneck other than the memory interface. The problem can be removed by increasing the clock speed of the T9000, and hence the speed at which the VCP operates. The VCP could fully saturate the links if the T9000 was running at 30 MHz. The T9000 was designed to run at 50 MHz, with the VCP able to saturate the links at 30 MHz.

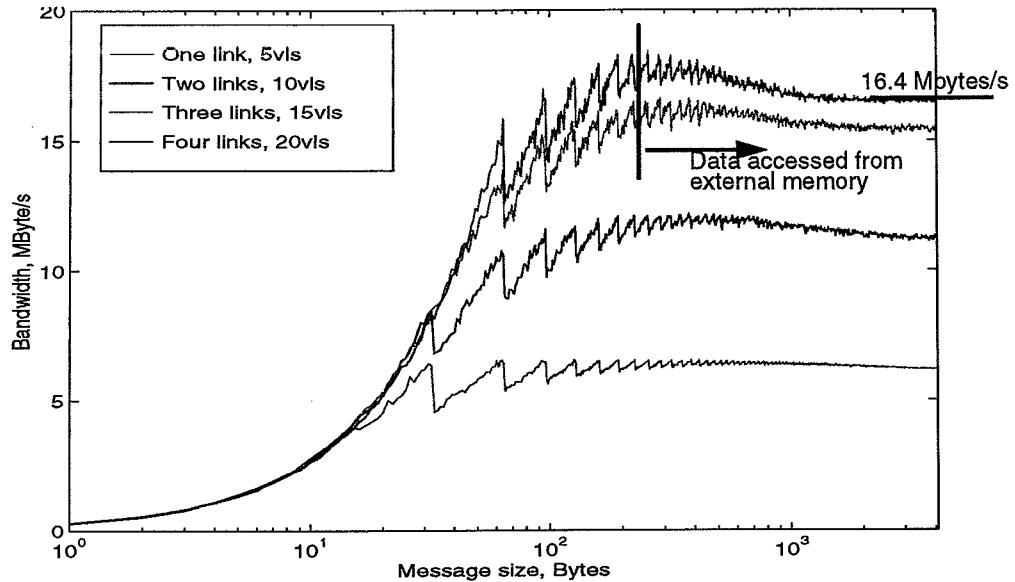

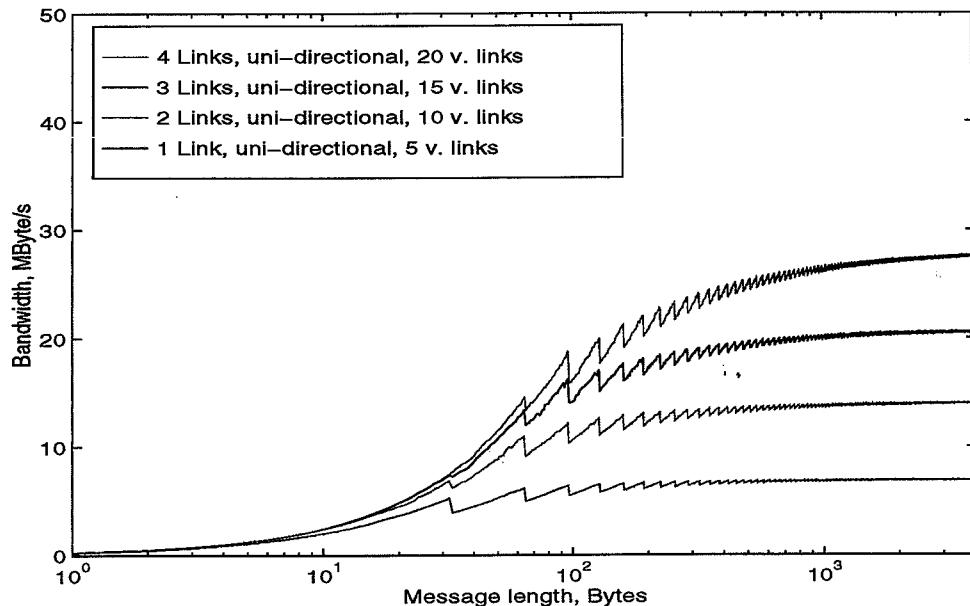

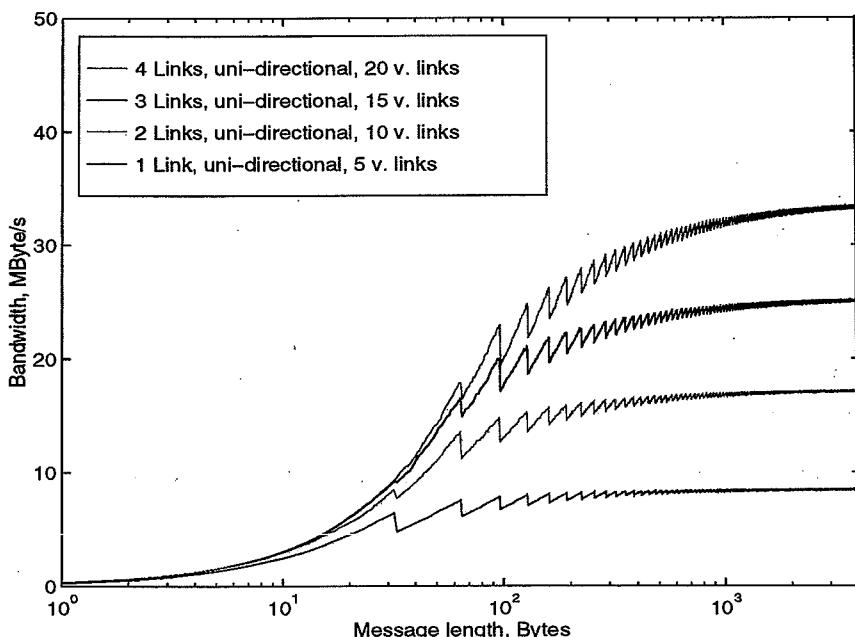

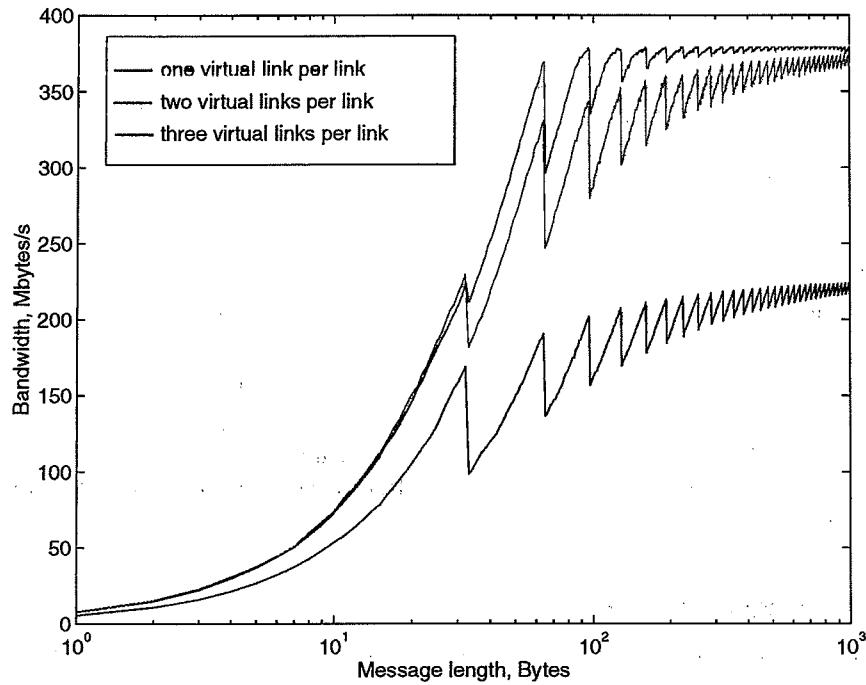

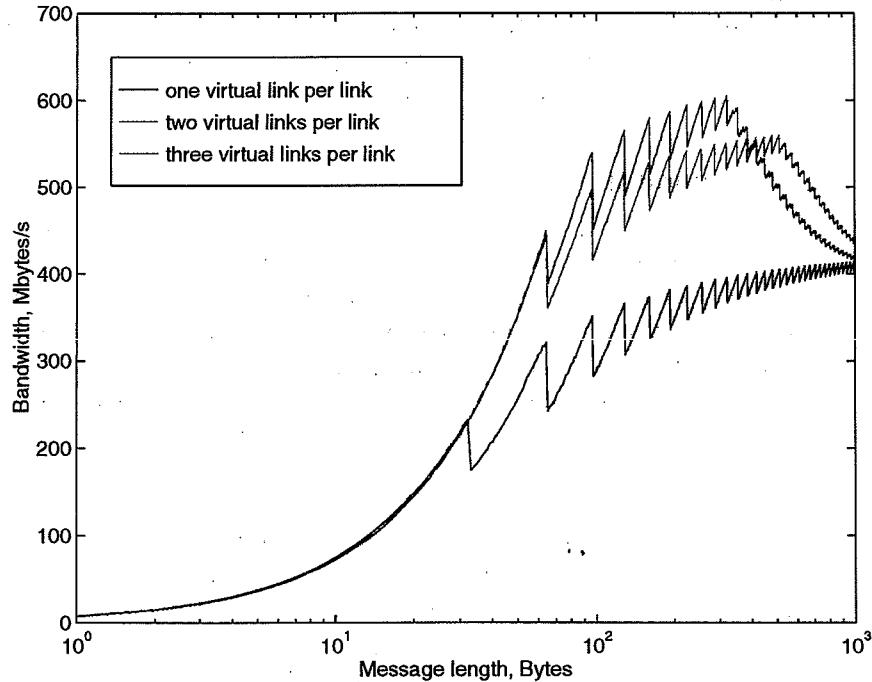

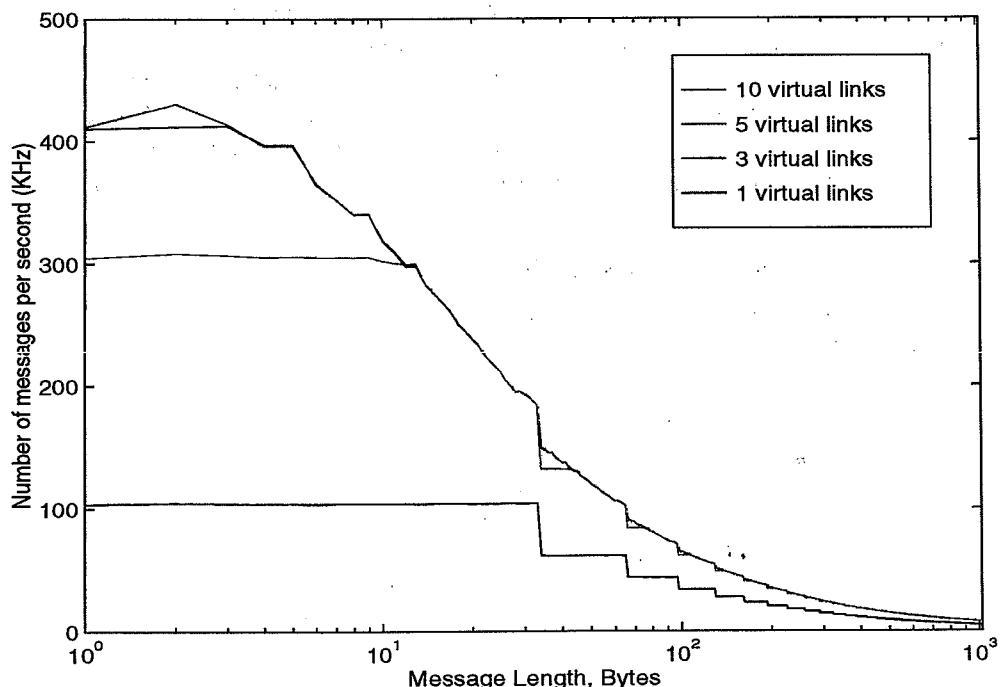

### 3.1.2 Dependence on memory bandwidth

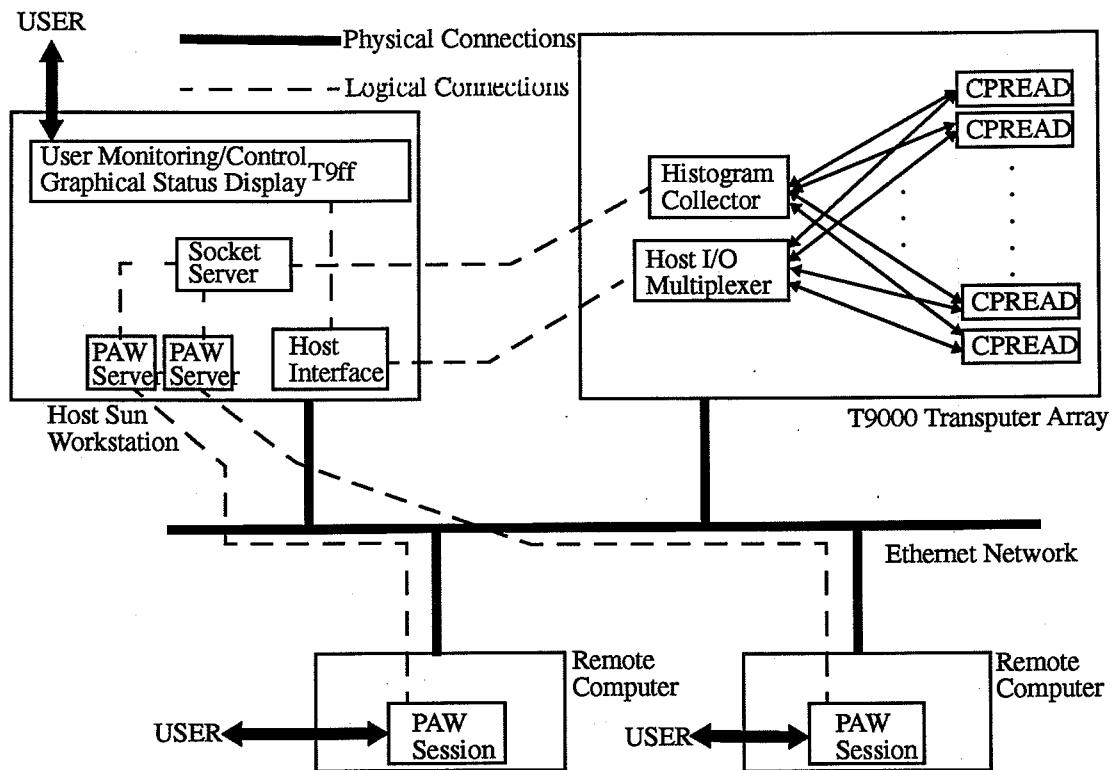

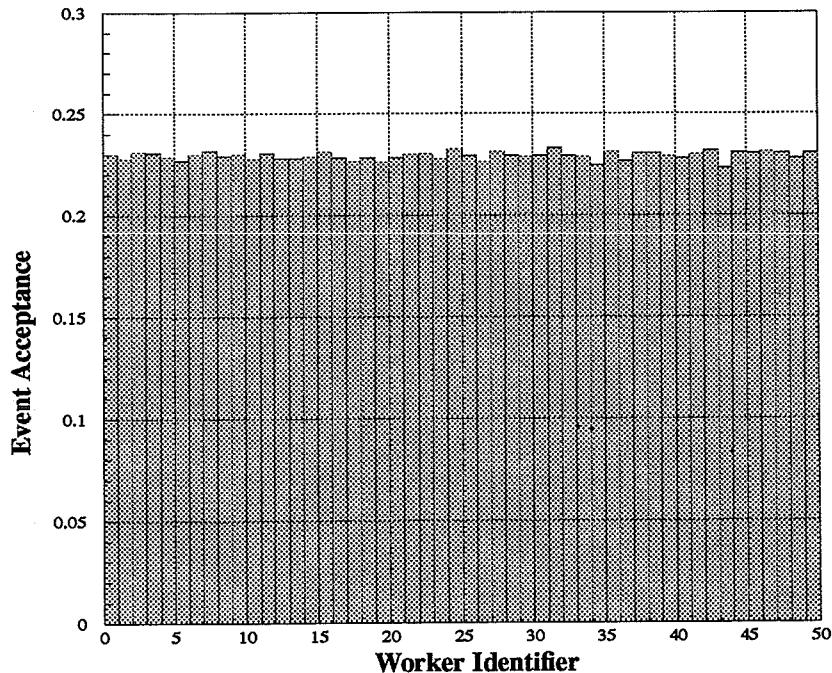

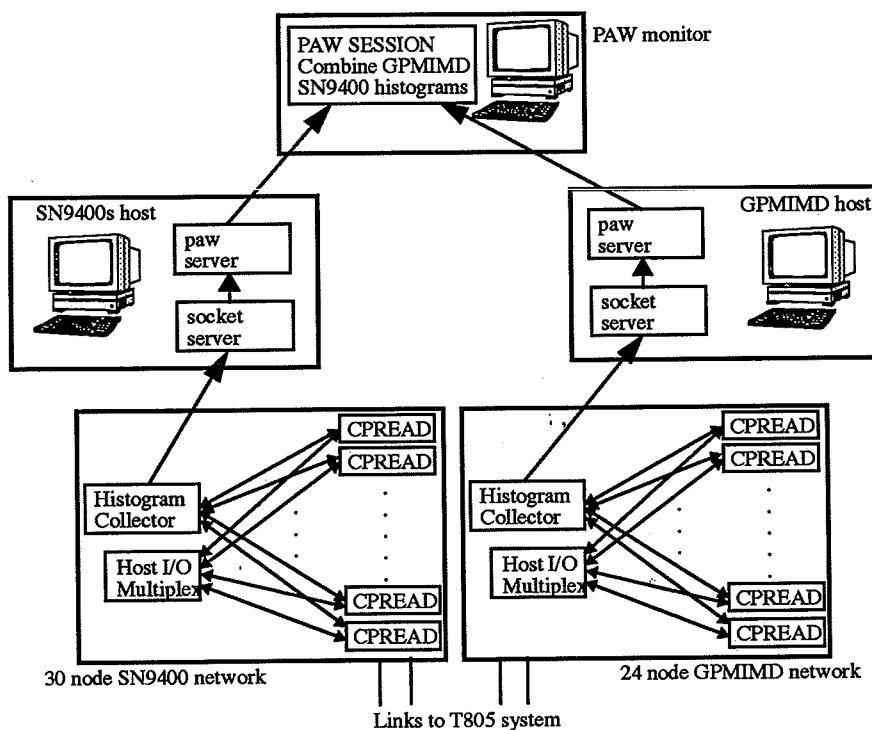

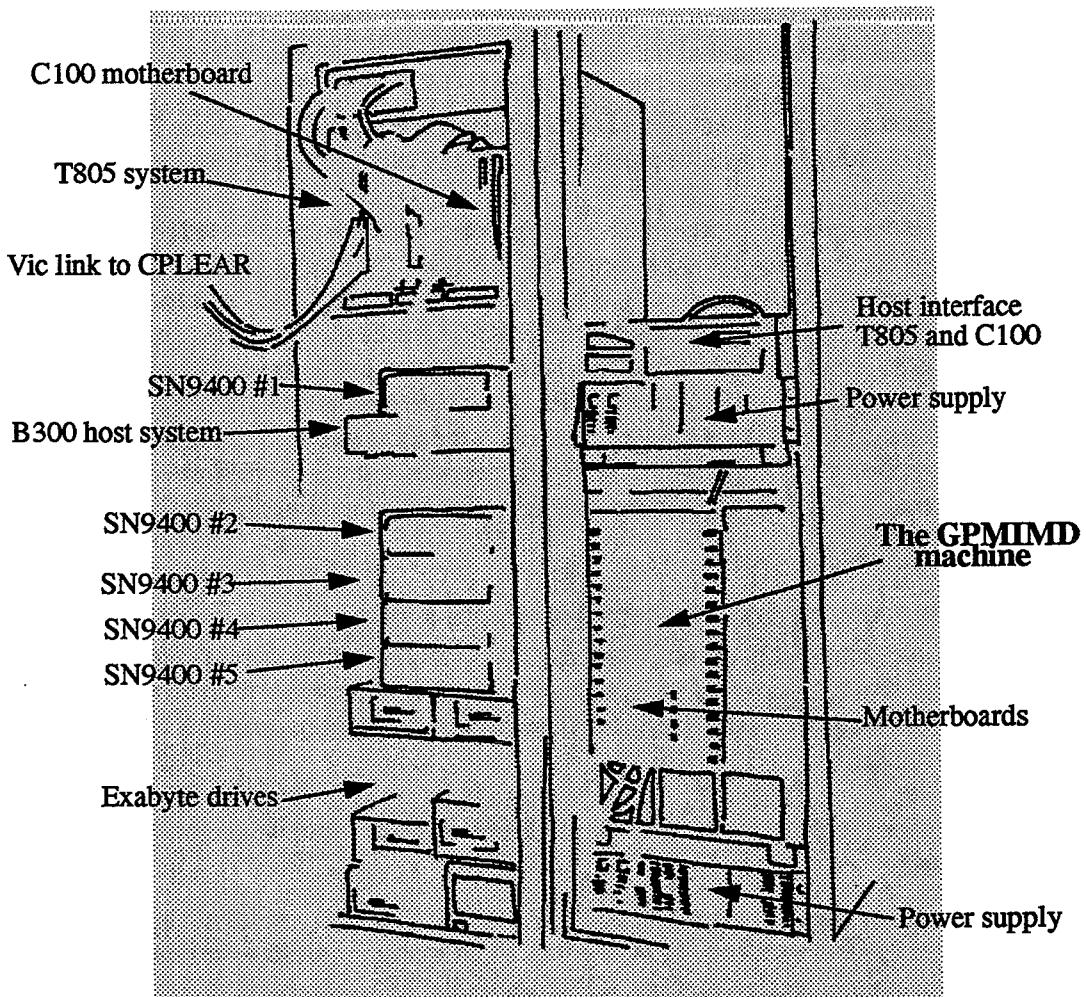

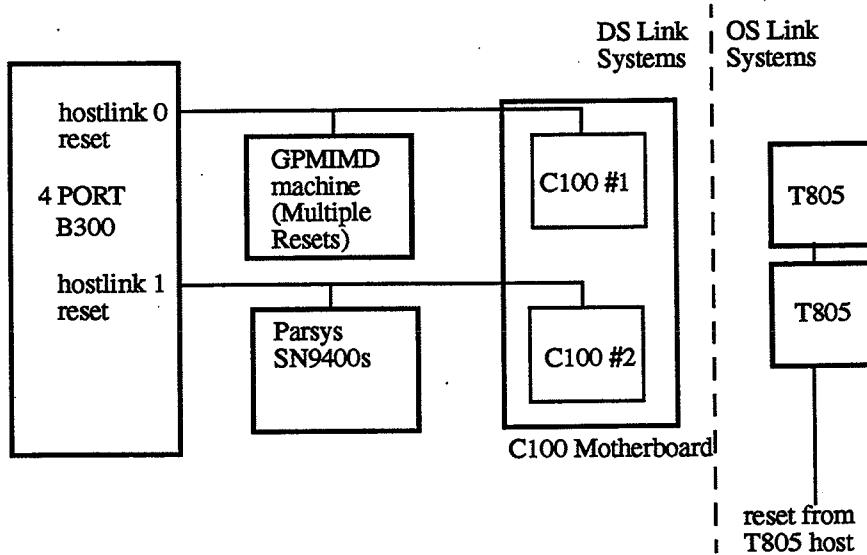

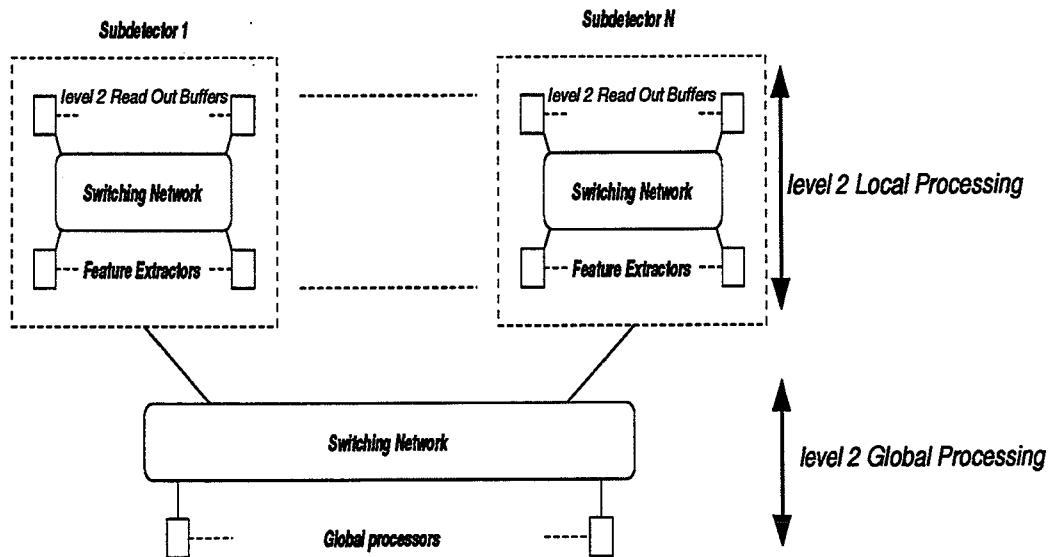

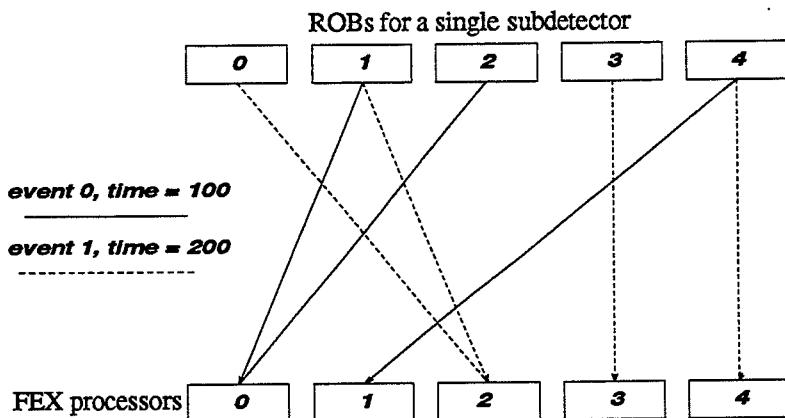

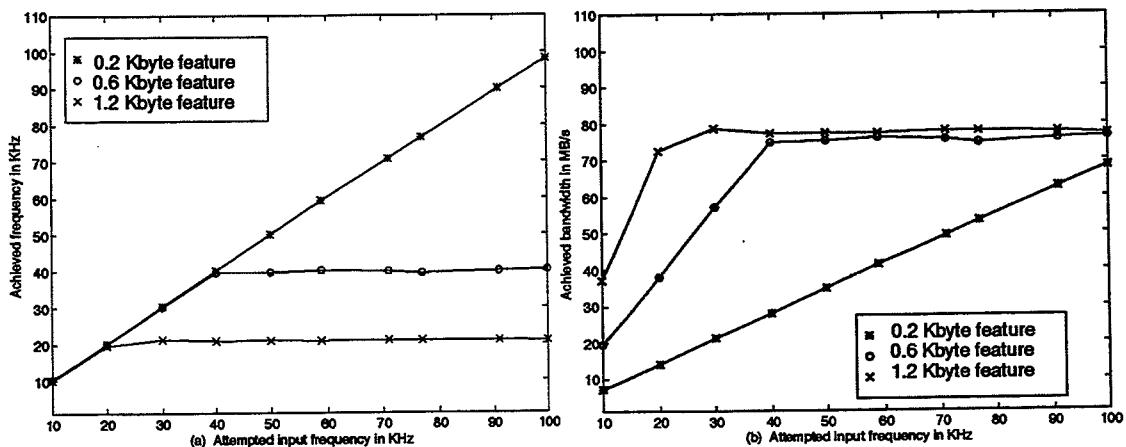

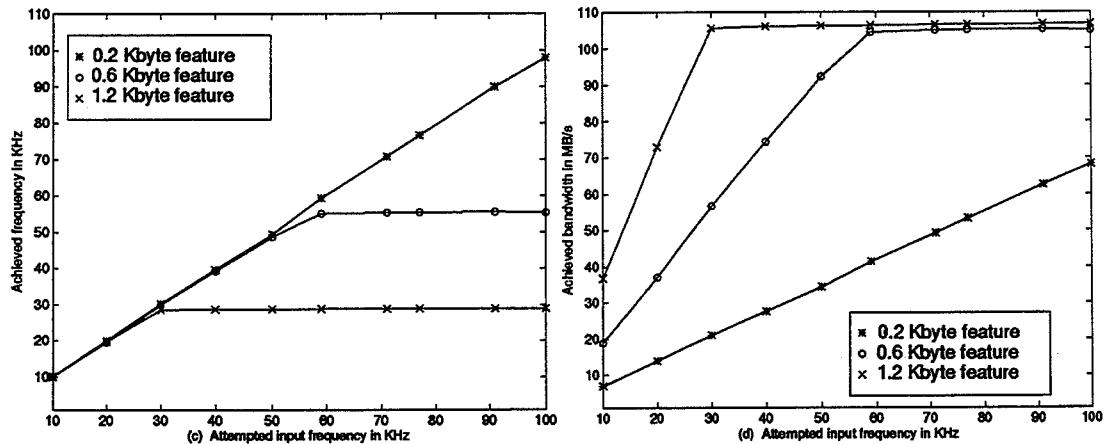

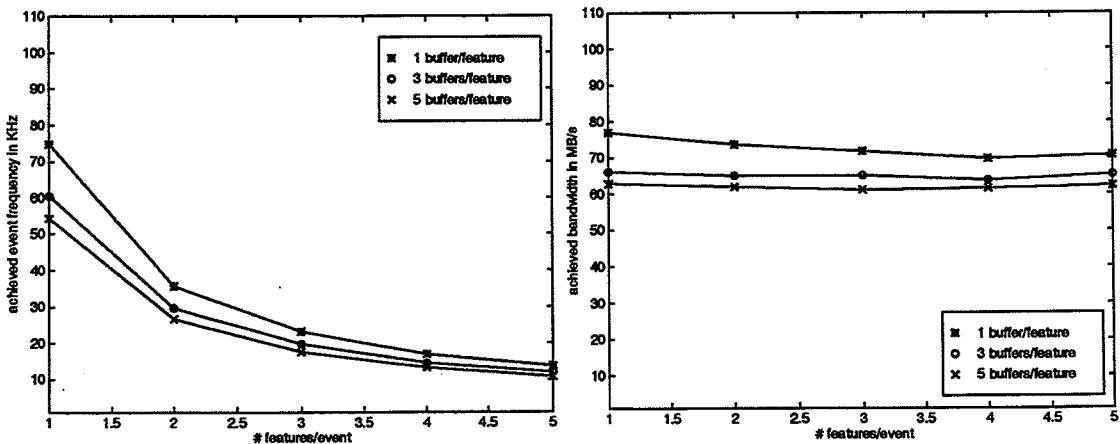

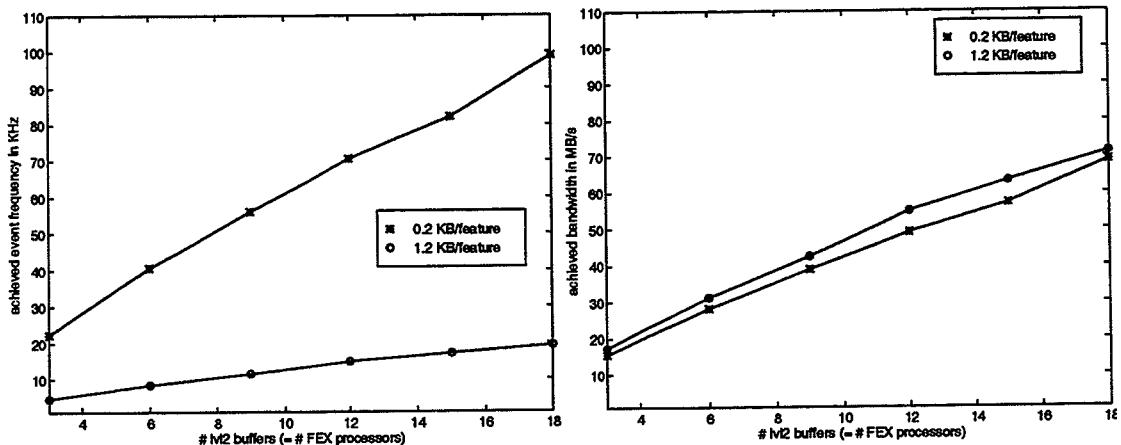

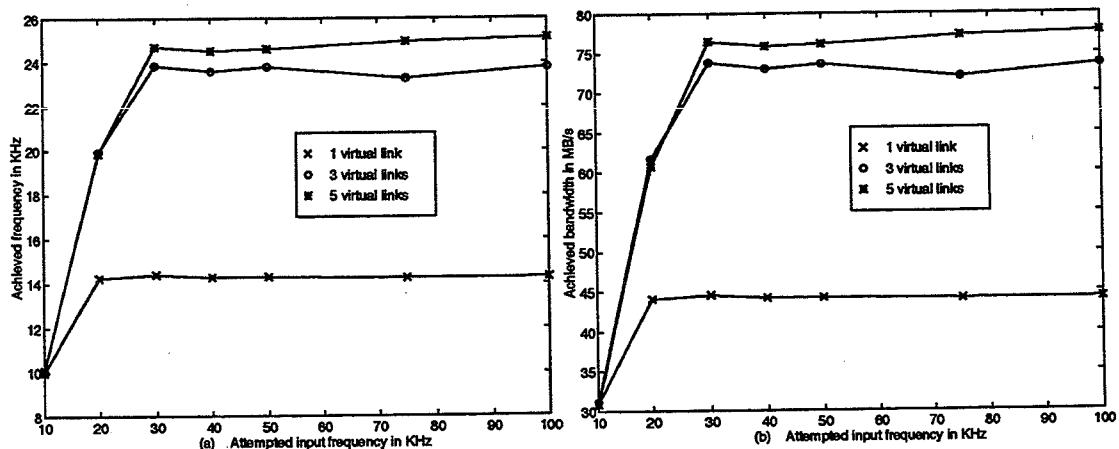

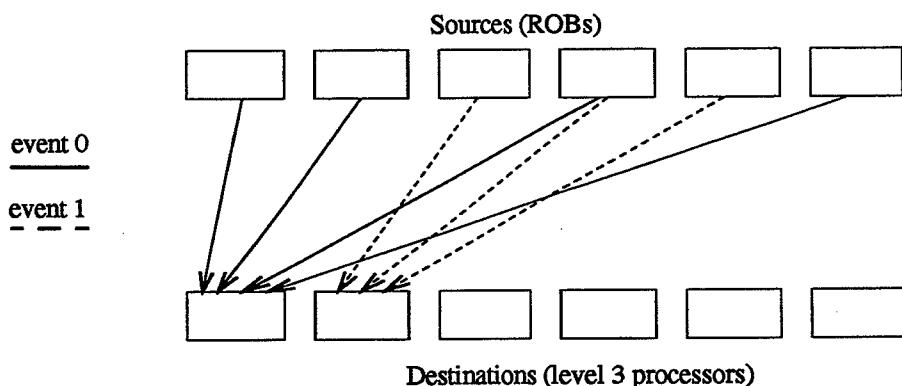

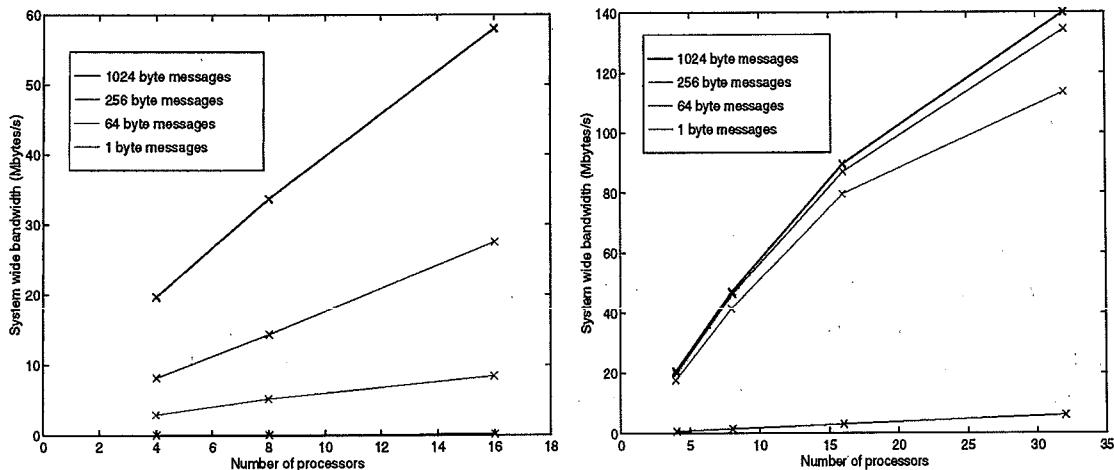

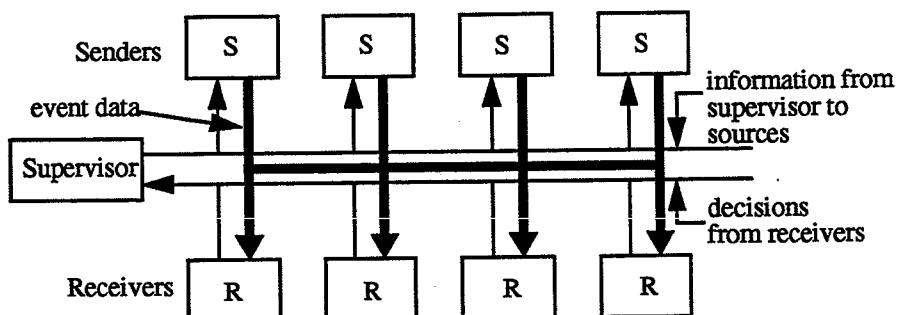

If Figure 3.3 is compared to Figure 3.4 the effect of reading data from external memory (as compared to internal memory) can be seen. The two figures show the achieved bandwidth out of the T9000 onto 1 to 4 physical links. In Figure 3.3 external memory is used, in Figure 3.4 data is always read from internal memory.