**UNIVERSITE MONTPELLIER II

SCIENCES ET TECHNIQUES DU LANGUEDOC**

**THESE**

pour obtenir le grade de

**DOCTEUR DE L' UNIVERSITE MONTPELLIER II**

*Discipline: « Électronique et Micro-optoélectronique »*

*Formation Doctorale: « Électronique: composants et systèmes »*

*préparée au sein du groupe de Microélectronique du

Laboratoire Européen pour la Recherche Nucléaire (CERN)*

*dans le cadre de l'École Doctorale:*

*«Information, Structures, Systèmes»*

présentée et soutenue publiquement par

**Roberto DINAPOLI**

le 23 Mars 2004

**Titre:**

**UN SYSTÈME DE DÉTECTION À PIXELS TOLÉRANT AUX

RAYONNEMENTS POUR LES EXPÉRIENCES ALICE ET LHCb AU

CERN**

**A RADIATION TOLERANT PIXEL DETECTOR SYSTEM FOR THE

ALICE AND LHCb EXPERIMENTS AT CERN**

***Directeur de thèse:***

**M. Jean GASIOT**

**JURY**

M. André TOUBOUL

Professeur, IXL

Rapporteur, Président

M. Raoul VELAZCO

Directeur de recherche, CNRS

Rapporteur

M. Jean GASIOT

Professeur, UMII

Directeur de thèse

M. Walter SNOEYS

Ingénieur de recherche, CERN

Resp. de thèse CERN

***UNIVERSITE MONTPELLIER II

SCIENCES ET TECHNIQUES DU LANGUEDOC***

*N° attribué par la bibliothèque*

**THÈSE**

pour obtenir le grade de

**DOCTEUR DE L' UNIVERSITE MONTPELLIER II**

*Discipline: « Électronique et Micro-optoélectronique »*

*Formation Doctorale: « Électronique: composants et systèmes »*

*préparée au sein du groupe de Microélectronique du

Laboratoire Européen pour la Recherche Nucléaire (CERN)

dans le cadre de l'Ecole Doctorale:

«Information, Structures, Systèmes»*

présentée et soutenue publiquement par

Roberto DINAPOLI

le 23 Mars 2004

**Titre:**

**UN SYSTÈME DE DÉTECTION À PIXELS TOLÉRANT AUX

RAYONNEMENTS POUR LES EXPÉRIENCES ALICE ET LHCb AU

CERN**

**A RADIATION TOLERANT PIXEL DETECTOR SYSTEM FOR THE

ALICE AND LHCb EXPERIMENTS AT CERN**

*Directeur de thèse:

M. Jean GASIOT*

**JURY**

M. André TOUBOUL

M. Raoul VELAZCO

M. Jean GASIOT

M. Walter SNOEYS

Professeur, IXL

Directeur de recherche, CNRS

Professeur, UMII

Ingénieur de recherche, CERN

Rapporteur, Président

Rapporteur

Directeur de thèse

Resp. de thèse CERN

After the torchlight red on sweaty faces

After the frosty silence in the gardens

After the agony in stony places

The shouting and the crying

Prison and palace and reverberation

Of thunder of spring over distant mountains...

T.S. Eliot, *The Waste Land*

# Table of Contents

|                                                                                |           |

|--------------------------------------------------------------------------------|-----------|

| <b>TABLE OF CONTENTS .....</b>                                                 | <b>i</b>  |

| <b>RÉSUMÉ.....</b>                                                             | <b>xi</b> |

| <b>INTRODUCTION.....</b>                                                       | <b>1</b>  |

| <b>CHAPTER 1 AN INTRODUCTION TO PARTICLE PHYSICS AT CERN .....</b>             | <b>5</b>  |

| 1.1    The Standard Model .....                                                | 5         |

| 1.2    Particle accelerators.....                                              | 7         |

| 1.3    From the Proton Synchrotron to the Large Hadron Collider .....          | 8         |

| 1.4    A Large Ion Collider Experiment (ALICE).....                            | 9         |

| 1.4.1    The Quark Gluon Plasma .....                                          | 9         |

| 1.4.2    Recreating and detecting QGP .....                                    | 10        |

| 1.4.3    The ALICE detector .....                                              | 11        |

| 1.5    Summary .....                                                           | 12        |

| <b>CHAPTER 2 SEMICONDUCTOR PARTICLE DETECTORS FOR HIGH ENERGY PHYSICS.....</b> | <b>13</b> |

| 2.1    Semiconductor detectors for trackers in high energy physics .....       | 13        |

| 2.1.1    Microstrip detectors.....                                             | 14        |

| 2.1.2    Pad Detectors.....                                                    | 15        |

| 2.1.3    Semiconductor drift detectors (SDD) .....                             | 15        |

| 2.1.4    Charge Coupled Device (CCD) Detectors.....                            | 17        |

| 2.1.5    Pixel detectors .....                                                 | 17        |

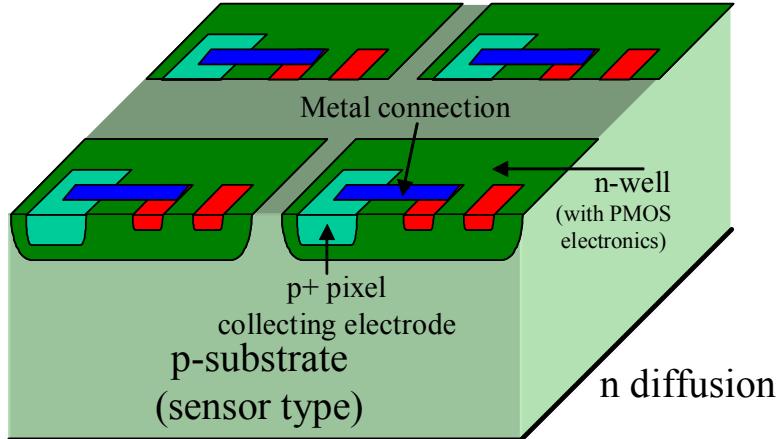

| 2.1.5.1    Monolithic pixel detectors.....                                     | 18        |

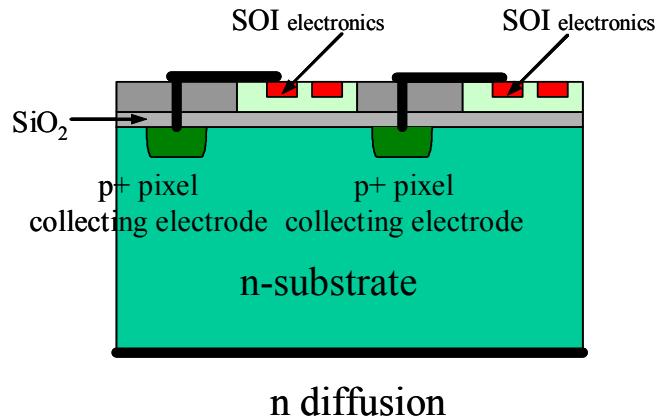

| 2.1.5.2    Silicon on insulator pixel detectors .....                          | 20        |

| 2.1.5.3    Hydrogenated Amorphous Silicon pixel detectors .....                | 21        |

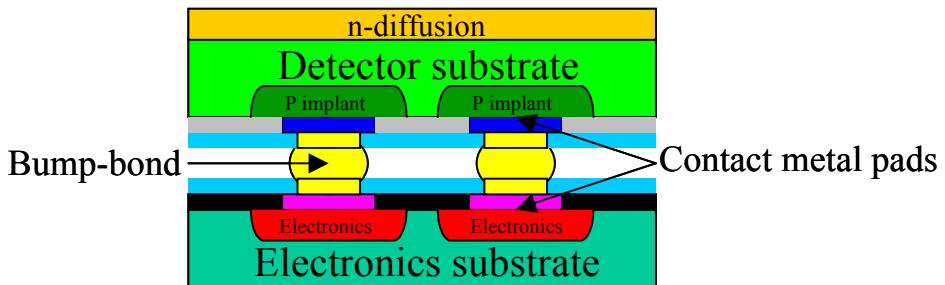

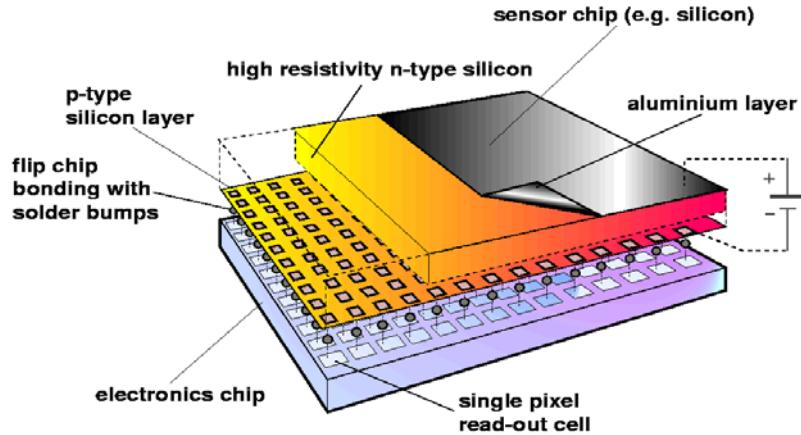

| 2.1.5.4    Hybrid pixel detectors .....                                        | 21        |

| 2.2    Radiation damage in semiconductor particle sensors .....                | 22        |

| 2.3    Summary .....                                                           | 24        |

## CHAPTER 3 THE ALICE SILICON PIXEL DETECTOR ..... 25

|                                                                                  |    |

|----------------------------------------------------------------------------------|----|

| 3.1 The ALICE Inner Tracking System .....                                        | 25 |

| 3.2 The Silicon Pixel Detector (SPD).....                                        | 27 |

| 3.2.1 The front-end chip.....                                                    | 29 |

| 3.2.2 The assemblies and the ladders.....                                        | 30 |

| 3.2.3 The On-detector read-out pixel Pilot System (OPS) .....                    | 31 |

| 3.2.3.1 The PILOT Multi Chip Module (MCM) and the Digital Pilot Chip (DPC) ..... | 31 |

| 3.2.3.2 The Gigabit Optical Link (GOL) .....                                     | 34 |

| 3.2.3.3 Link receiver daughter card.....                                         | 34 |

| 3.2.3.4 Pixel control transmitter and receiver .....                             | 34 |

| 3.2.3.5 The Analogue Pilot Chip (APC).....                                       | 35 |

| 3.2.3.6 The Multi Chip Module implementation .....                               | 35 |

| 3.2.4 The Pixel Bus .....                                                        | 36 |

| 3.2.5 The cooling system.....                                                    | 37 |

| 3.2.6 The Chip Test System .....                                                 | 38 |

| 3.3 Summary .....                                                                | 40 |

## CHAPTER 4 THE ALICE SPD AND LHCb RICH HYBRID ASSEMBLIES.... 41

|                                                         |    |

|---------------------------------------------------------|----|

| 4.1 The ALICE SPD sensors .....                         | 41 |

| 4.1.1 The basic pixel.....                              | 42 |

| 4.1.2 The single and the ladder .....                   | 44 |

| 4.1.3 The sensor periphery .....                        | 45 |

| 4.2 Tests of the ALICE SPD sensor.....                  | 47 |

| 4.2.1 Electrical tests.....                             | 48 |

| 4.2.2 Bump-bonding tests.....                           | 49 |

| 4.2.3 Irradiation tests .....                           | 52 |

| 4.2.3.1 Tests with the 27 MeV Legnaro proton beam ..... | 52 |

| 4.2.3.2 Tests with the 24 GeV CERN proton beam .....    | 54 |

| 4.2.4 Metrology measurements .....                      | 56 |

| 4.3 Summary .....                                       | 57 |

## CHAPTER 5 ELECTRONICS FOR HIGH ENERGY PHYSICS..... 59

|                                            |    |

|--------------------------------------------|----|

| 5.1 Radiation effects on MOS devices ..... | 60 |

| 5.1.1 Atomic displacement.....             | 60 |

|            |                                                                             |           |

|------------|-----------------------------------------------------------------------------|-----------|

| 5.1.2      | Ionisation .....                                                            | 61        |

| 5.1.2.1    | Oxide trapped charge.....                                                   | 63        |

| 5.1.2.2    | Interface states .....                                                      | 63        |

| 5.1.2.3    | Direct tunnelling .....                                                     | 64        |

| <b>5.2</b> | <b>Radiation effects on the electrical parameters of a MOS device .....</b> | <b>64</b> |

| 5.2.1      | Threshold voltage shift.....                                                | 64        |

| 5.2.1.1    | Oxide trapped charge.....                                                   | 64        |

| 5.2.1.2    | Interface states .....                                                      | 65        |

| 5.2.1.3    | Overall threshold voltage shift.....                                        | 65        |

| 5.2.2      | Subthreshold slope .....                                                    | 65        |

| 5.2.3      | Off-state and parasitic currents .....                                      | 66        |

| 5.2.3.1    | Effect of the subthreshold slope change and threshold voltage shift .....   | 66        |

| 5.2.3.2    | Edge leakage currents.....                                                  | 67        |

| 5.2.3.3    | Inter-transistor leakage .....                                              | 70        |

| 5.2.4      | Mobility and transconductance .....                                         | 71        |

| <b>5.3</b> | <b>Single Event Effects (SEE).....</b>                                      | <b>71</b> |

| 5.3.1      | Soft errors .....                                                           | 72        |

| 5.3.1.1    | Single Event Upset (SEU).....                                               | 72        |

| 5.3.1.2    | Multiple Bit Upset (MBU) .....                                              | 72        |

| 5.3.1.3    | Single Event Function interruption (SEFI) .....                             | 72        |

| 5.3.1.4    | Single Event Transient (SET) .....                                          | 73        |

| 5.3.2      | Hard errors.....                                                            | 73        |

| 5.3.2.1    | Single Event Latchup (SEL) .....                                            | 73        |

| 5.3.2.2    | Single Event Snapback (SES) .....                                           | 74        |

| 5.3.2.3    | Single Hard Error (SHE) .....                                               | 74        |

| 5.3.2.4    | Single Event Gate Rupture (SEGR).....                                       | 75        |

| 5.3.2.5    | Single Event Burn Out (SEBO) .....                                          | 75        |

| <b>5.4</b> | <b>Design for radiation tolerance .....</b>                                 | <b>75</b> |

| 5.4.1      | Hardening by process .....                                                  | 75        |

| 5.4.2      | Hardening by design (HBD) .....                                             | 76        |

| 5.4.3      | Components Off The Shelf .....                                              | 77        |

| <b>5.5</b> | <b>Deep submicron CMOS technologies for HEP.....</b>                        | <b>78</b> |

| 5.5.1      | Total ionising dose .....                                                   | 78        |

| 5.5.1.1    | Oxide trapped charge.....                                                   | 78        |

| 5.5.1.2    | Interface states .....                                                      | 79        |

| 5.5.1.3    | Total threshold voltage shift.....                                          | 80        |

|            |                                                           |            |

|------------|-----------------------------------------------------------|------------|

| 5.5.1.4    | Off-state currents .....                                  | 81         |

| 5.5.1.5    | Subthreshold slope.....                                   | 81         |

| 5.5.2      | Single event effects vulnerability.....                   | 81         |

| 5.5.2.1    | Single event upset.....                                   | 81         |

| 5.5.2.2    | Single event transient .....                              | 82         |

| 5.5.2.3    | Single event latch-up .....                               | 82         |

| 5.5.2.4    | Single event gate rupture .....                           | 82         |

| 5.5.3      | Circuit performance.....                                  | 83         |

| 5.5.3.1    | Transconductance .....                                    | 83         |

| 5.5.3.2    | Velocity saturation.....                                  | 83         |

| 5.5.3.3    | Weak inversion region operation .....                     | 84         |

| 5.5.3.4    | Electronic noise .....                                    | 84         |

| 5.5.3.5    | Matching .....                                            | 85         |

| 5.5.3.6    | Reduced voltage margins .....                             | 85         |

| <b>5.6</b> | <b>Hardening By Design.....</b>                           | <b>85</b>  |

| 5.6.1      | Hardening by layout.....                                  | 85         |

| 5.6.1.1    | Threshold voltage shift.....                              | 85         |

| 5.6.1.2    | Edge leakage.....                                         | 86         |

| 5.6.1.3    | Inter-transistor leakage .....                            | 88         |

| 5.6.1.4    | SEL vulnerability.....                                    | 90         |

| 5.6.2      | Hardening by circuit and system architecture .....        | 90         |

| 5.6.2.1    | Total Ionising Dose .....                                 | 90         |

| 5.6.2.2    | Single Event Upset .....                                  | 91         |

| 5.6.2.3    | Single Event Transient .....                              | 95         |

| <b>5.7</b> | <b>The Enclosed Layout Transistor (ELT).....</b>          | <b>96</b>  |

| 5.7.1      | Modelling of the enclosed layout transistor.....          | 96         |

| 5.7.2      | Matching properties of ELTs .....                         | 99         |

| 5.7.2.1    | Systematic effects .....                                  | 100        |

| 5.7.2.2    | Stochastic effects .....                                  | 100        |

| 5.7.3      | Noise performance of ELTs .....                           | 104        |

| 5.7.4      | Radiation tolerance of ELTs .....                         | 106        |

| <b>5.8</b> | <b>HBD area and performance penalties .....</b>           | <b>108</b> |

| <b>5.9</b> | <b>SEE tests on systems employing HBD techniques.....</b> | <b>110</b> |

| 5.9.1      | SEL sensitivity .....                                     | 111        |

| 5.9.2      | SEU sensitivity .....                                     | 111        |

|      |               |     |

|------|---------------|-----|

| 5.10 | Summary ..... | 113 |

|------|---------------|-----|

## CHAPTER 6 THE ALICE1TEST AND ALICE2TEST PROTOTYPE CHIPS... 19

|         |                                                                     |     |

|---------|---------------------------------------------------------------------|-----|

| 6.1     | The Omega2 and Omega3 chips.....                                    | 119 |

| 6.2     | The design of the ALICE1test and ALICE2test chips.....              | 120 |

| 6.3     | Experimental results form the ALICE1test and ALICE2test chips ..... | 124 |

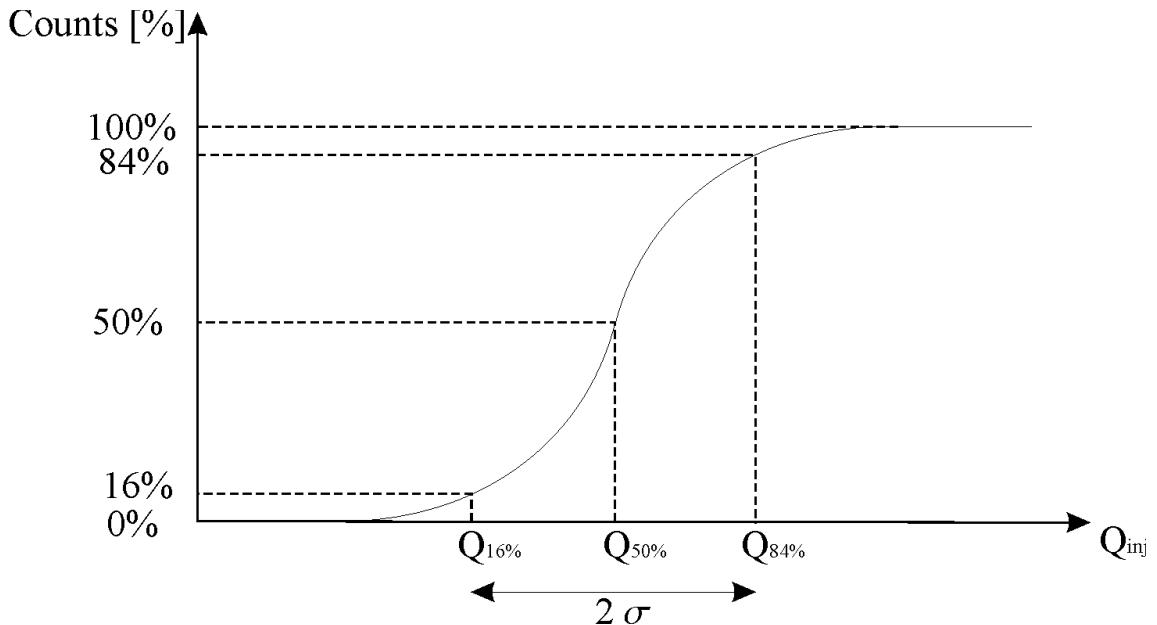

| 6.3.1   | The s-curve method.....                                             | 125 |

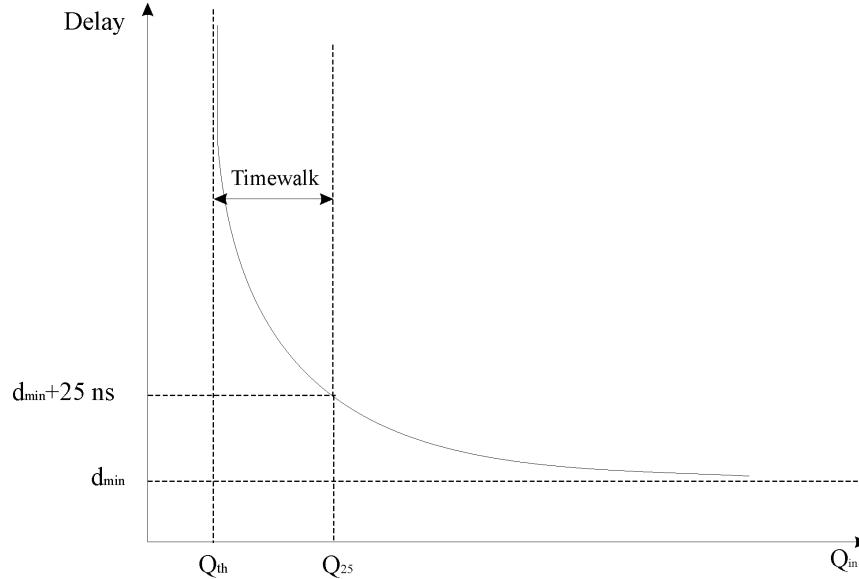

| 6.3.2   | Timewalk estimation.....                                            | 126 |

| 6.3.3   | Experimental results on the ALICE1test prototype chip.....          | 127 |

| 6.3.4   | Experimental results on the ALICE2test prototype chip.....          | 129 |

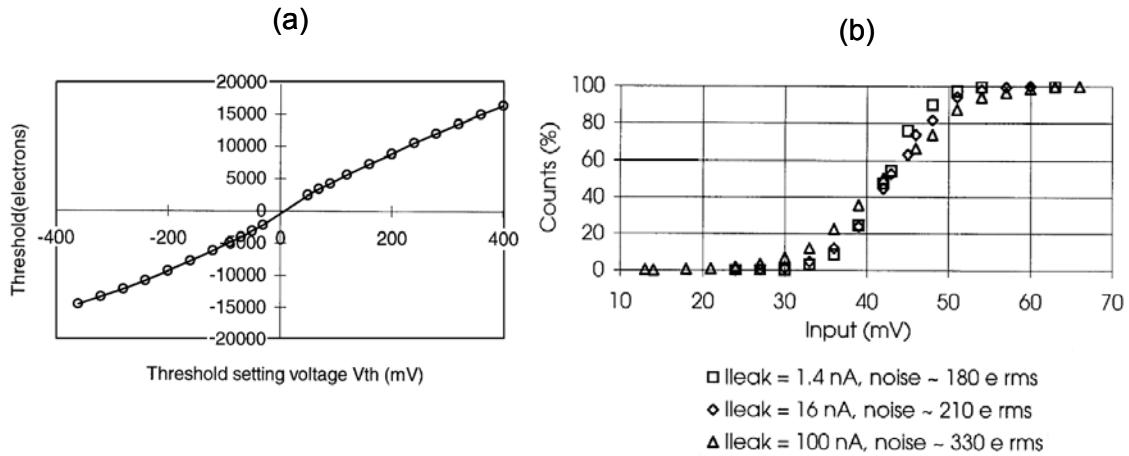

| 6.3.4.1 | Pre-irradiation tests.....                                          | 129 |

| 6.3.4.2 | Irradiation tests .....                                             | 133 |

| 6.4     | Summary .....                                                       | 137 |

## CHAPTER 7 THE ALICE1LHCb CHIP: CONCEPT AND IMPLEMENTATION . ..... 139

|         |                                                                |     |

|---------|----------------------------------------------------------------|-----|

| 7.1     | Requirements and specifications.....                           | 139 |

| 7.1.1   | LHCb requirements .....                                        | 139 |

| 7.1.2   | ALICE requirements .....                                       | 142 |

| 7.1.3   | Chip requirements .....                                        | 143 |

| 7.2     | Choice of the front-end scheme .....                           | 144 |

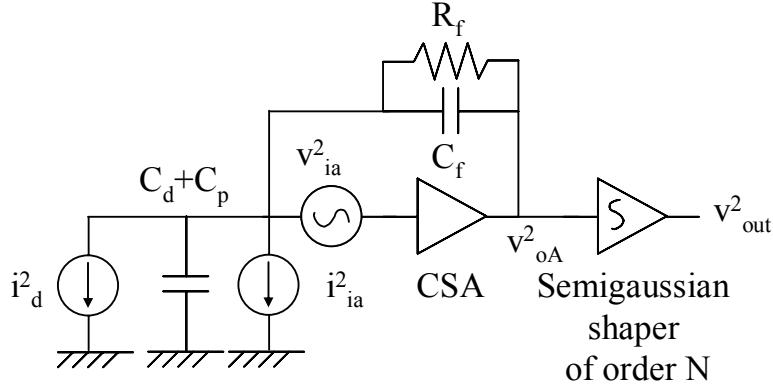

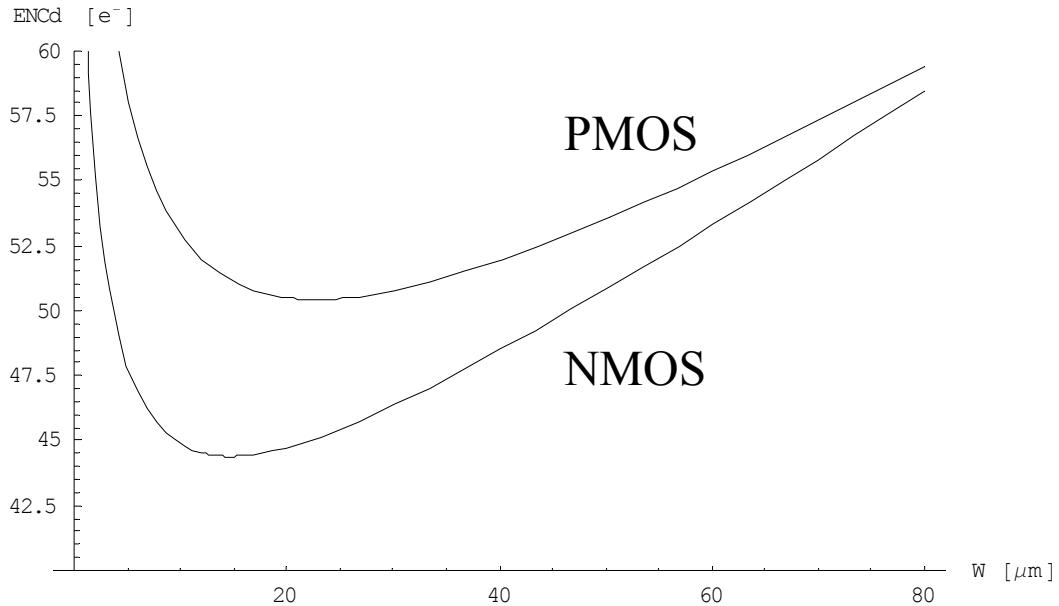

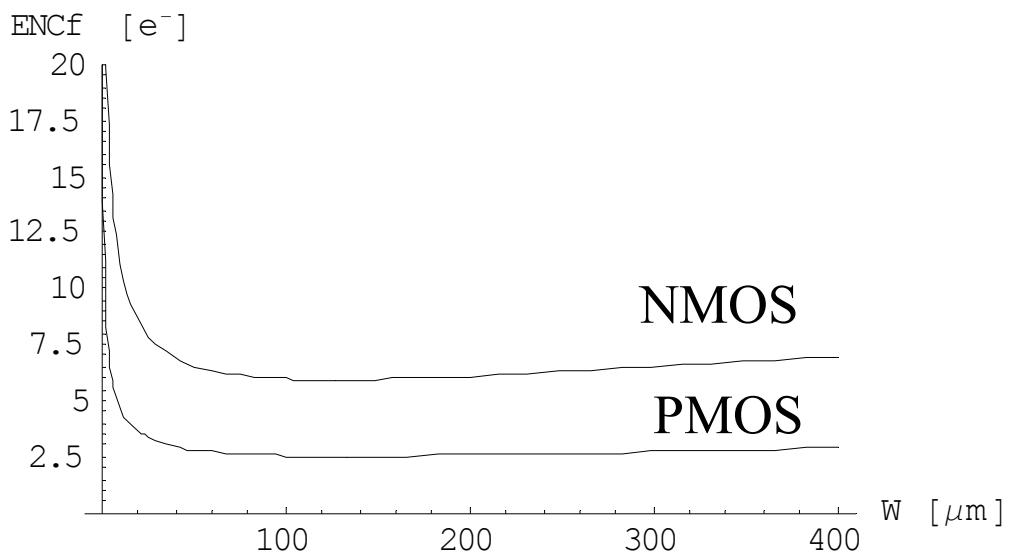

| 7.2.1   | The Charge Sensitive Amplifier with Semigaussian shaping ..... | 144 |

| 7.2.2   | The ALICE1LHCb front-end concept: two poles system .....       | 155 |

| 7.2.2.1 | The CSA .....                                                  | 156 |

| 7.2.2.2 | The first shaping stage.....                                   | 157 |

| 7.2.2.3 | The system in closed loop .....                                | 158 |

| 7.2.2.4 | Noise analysis .....                                           | 161 |

| 7.2.3   | The ALICE1LHCb front-end concept: three poles system .....     | 164 |

| 7.2.3.1 | The three poles system in closed loop .....                    | 165 |

| 7.2.3.2 | Noise analysis .....                                           | 168 |

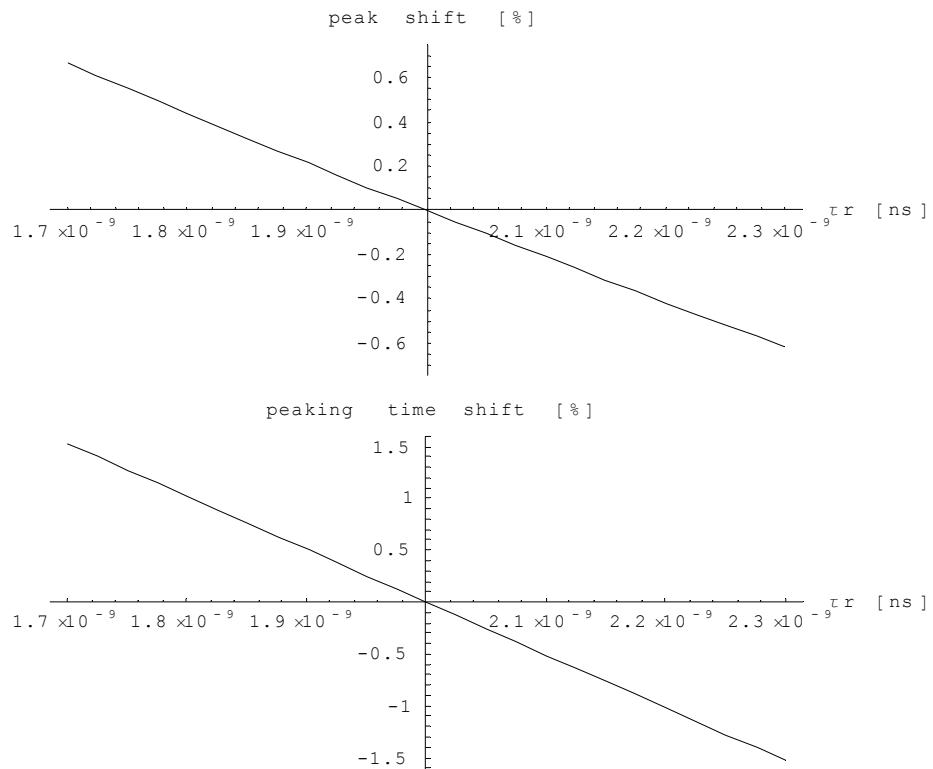

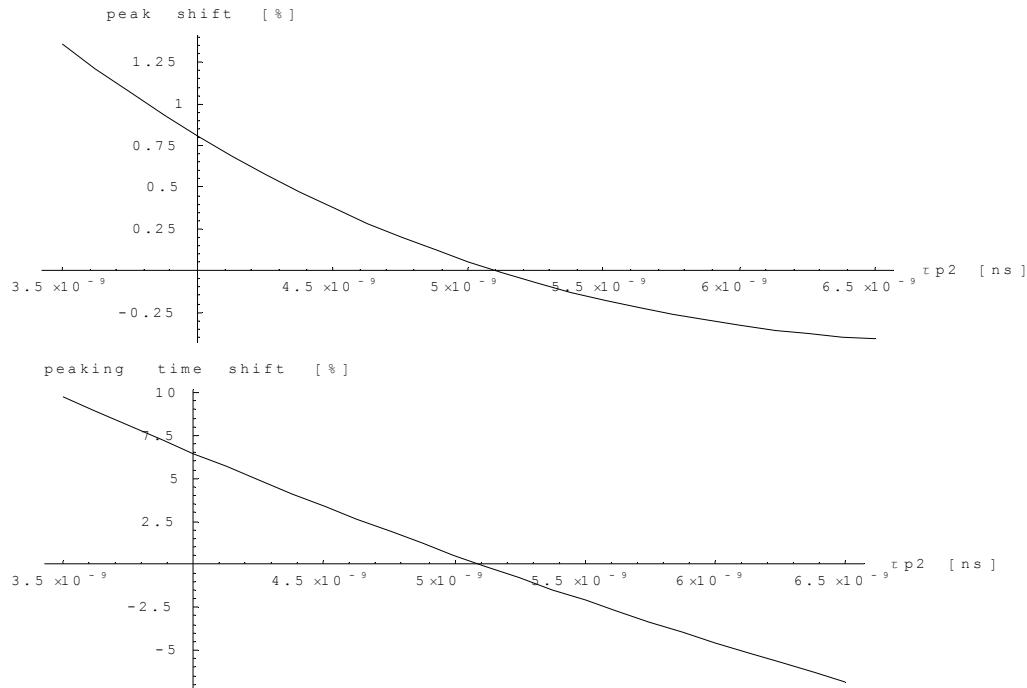

| 7.2.3.3 | Sensitivity analysis .....                                     | 170 |

| 7.2.4   | The ALICE1LHCb front end concept: the four poles system.....   | 171 |

| 7.2.4.1 | Sensitivity analysis .....                                     | 172 |

| 7.2.4.2 | Noise analysis .....                                           | 175 |

|                                                                |            |

|----------------------------------------------------------------|------------|

| <b>7.3 The ALICE1LHCb front-end implementation.....</b>        | <b>176</b> |

| 7.3.1 The Charge Sensitive Preamplifier .....                  | 176        |

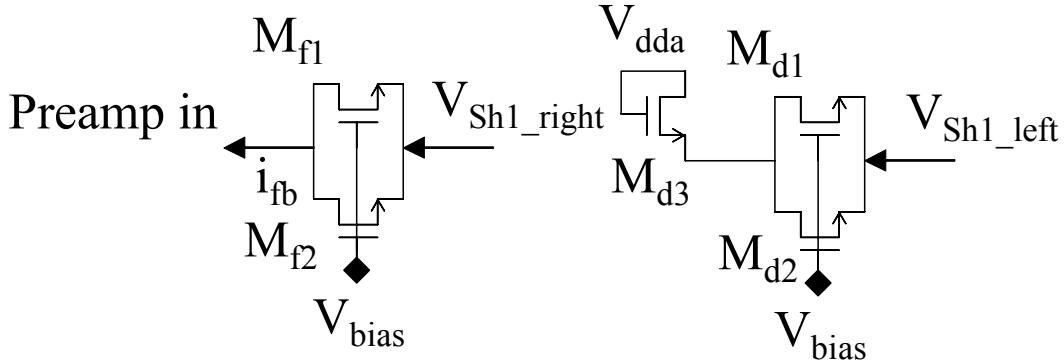

| 7.3.2 The first shaping stage .....                            | 179        |

| 7.3.3 The feedback stage .....                                 | 183        |

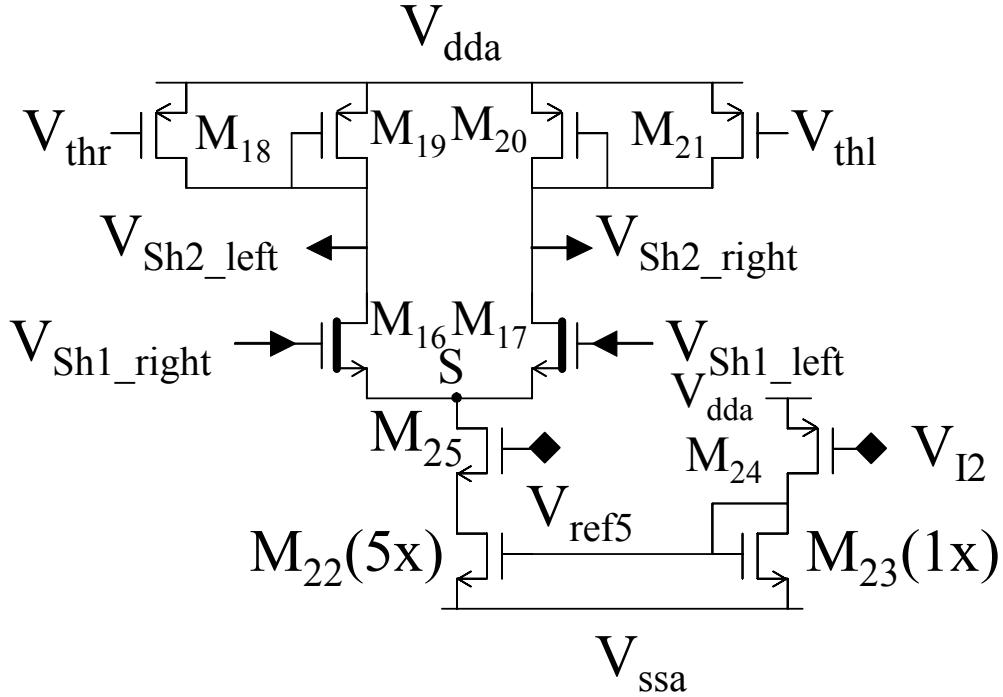

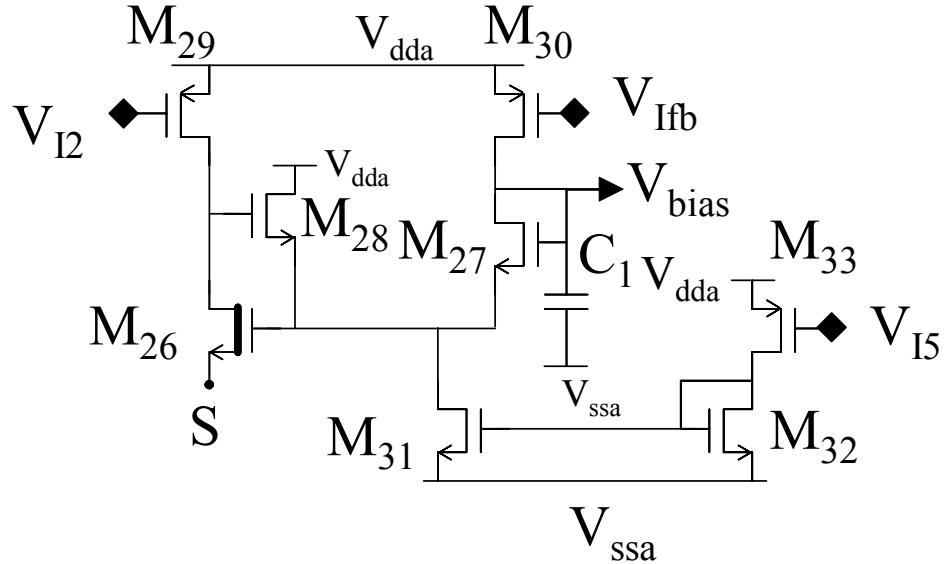

| 7.3.4 The second shaping stage.....                            | 183        |

| 7.3.5 The feedback bias stage .....                            | 186        |

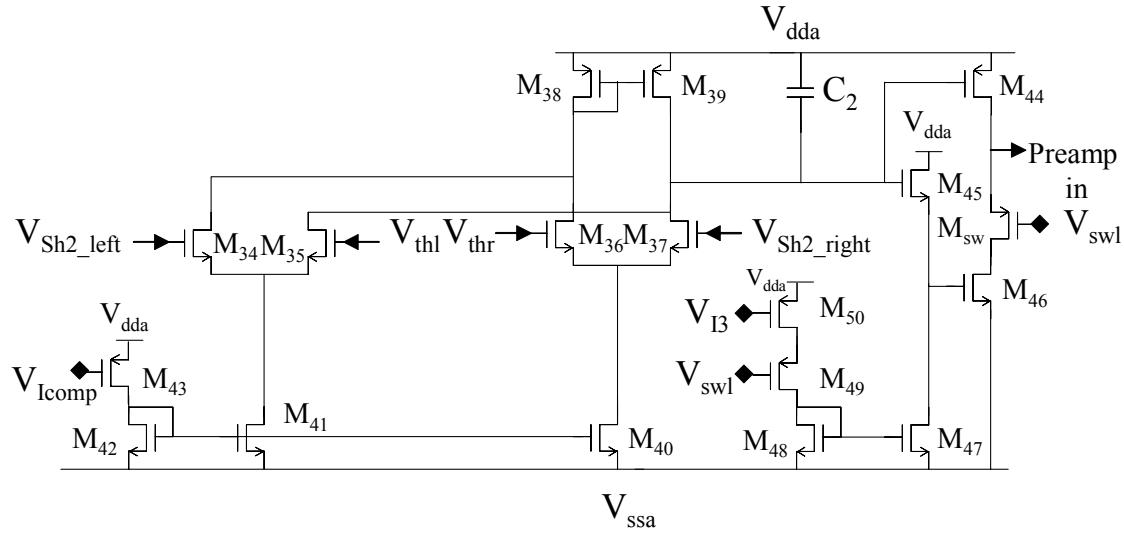

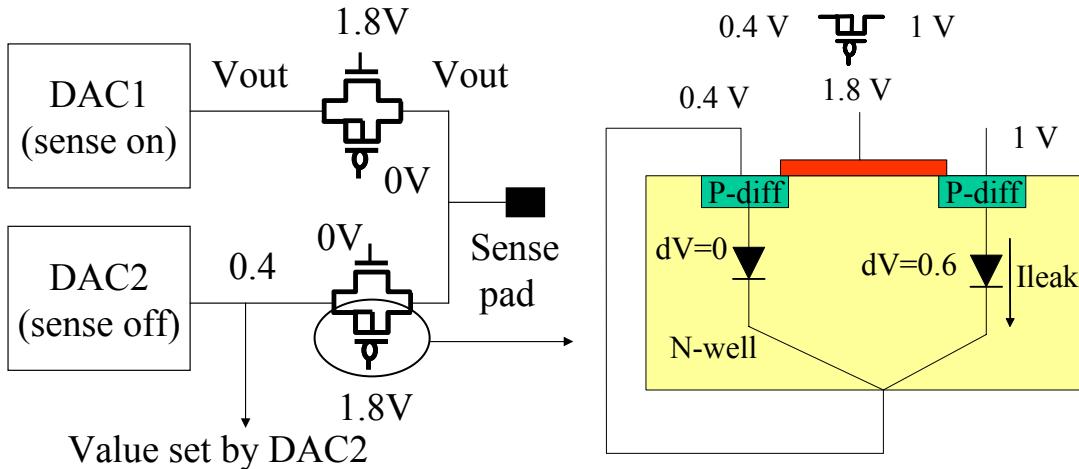

| 7.3.6 The leakage current and offset compensation scheme ..... | 187        |

| 7.3.7 Full front-end simulations and analysis.....             | 189        |

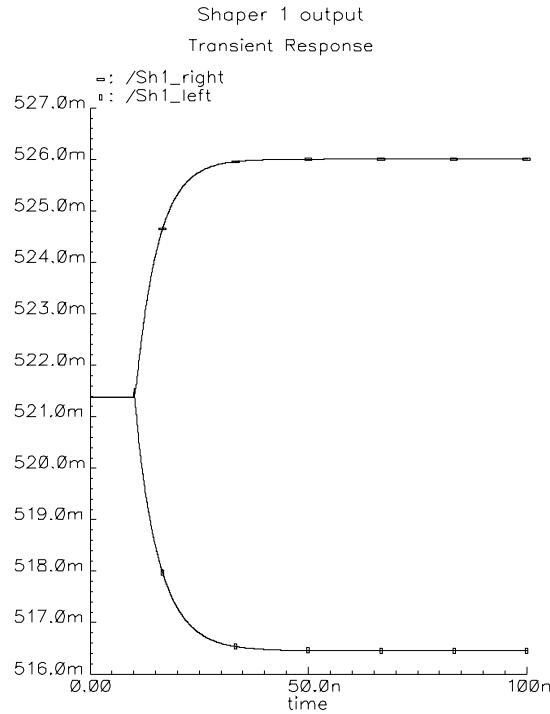

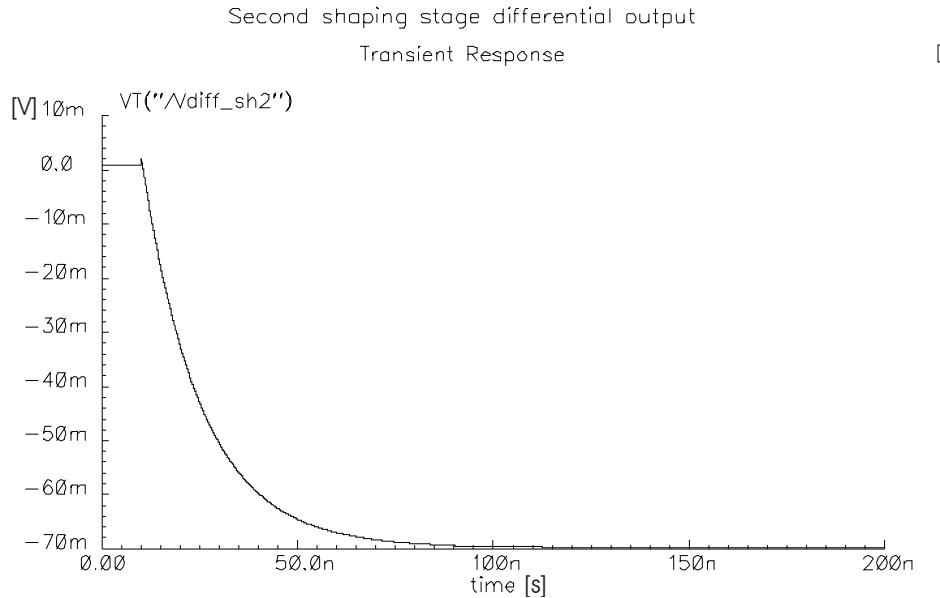

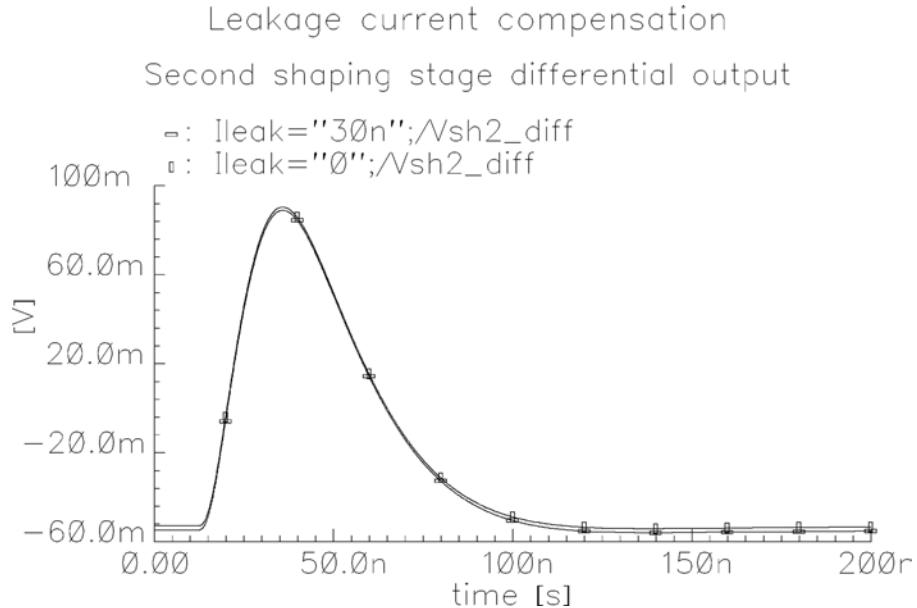

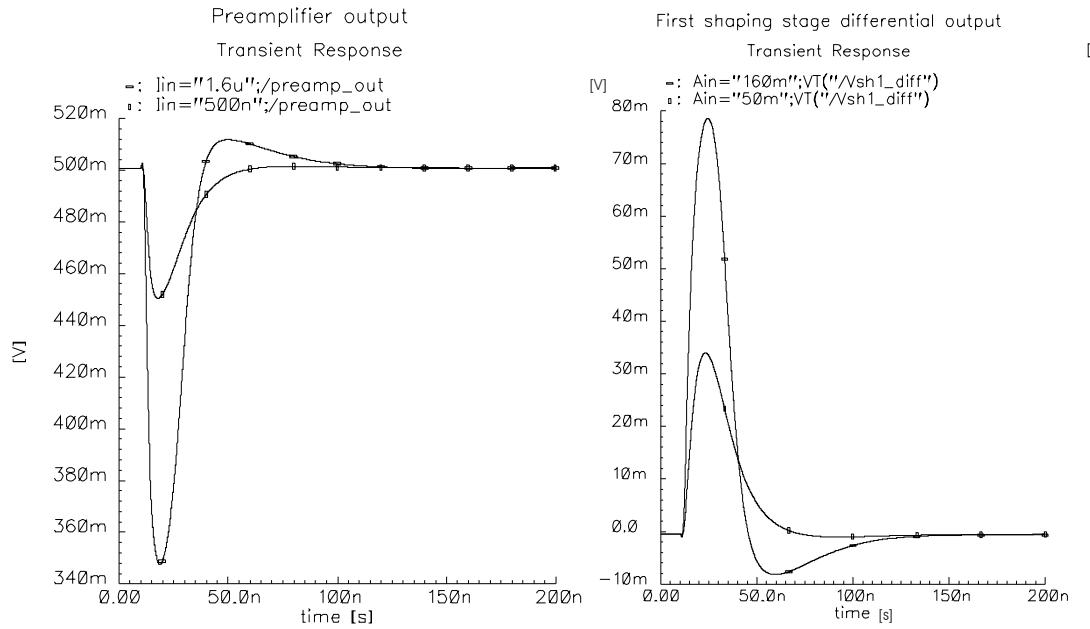

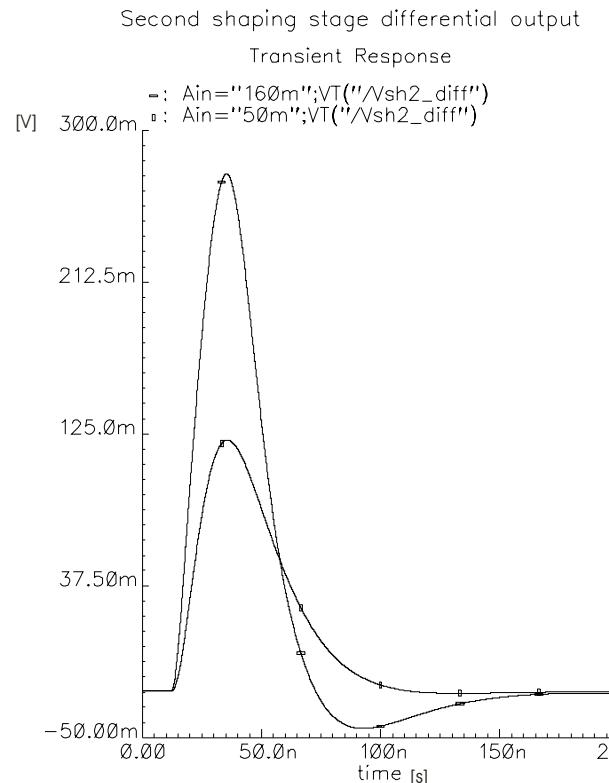

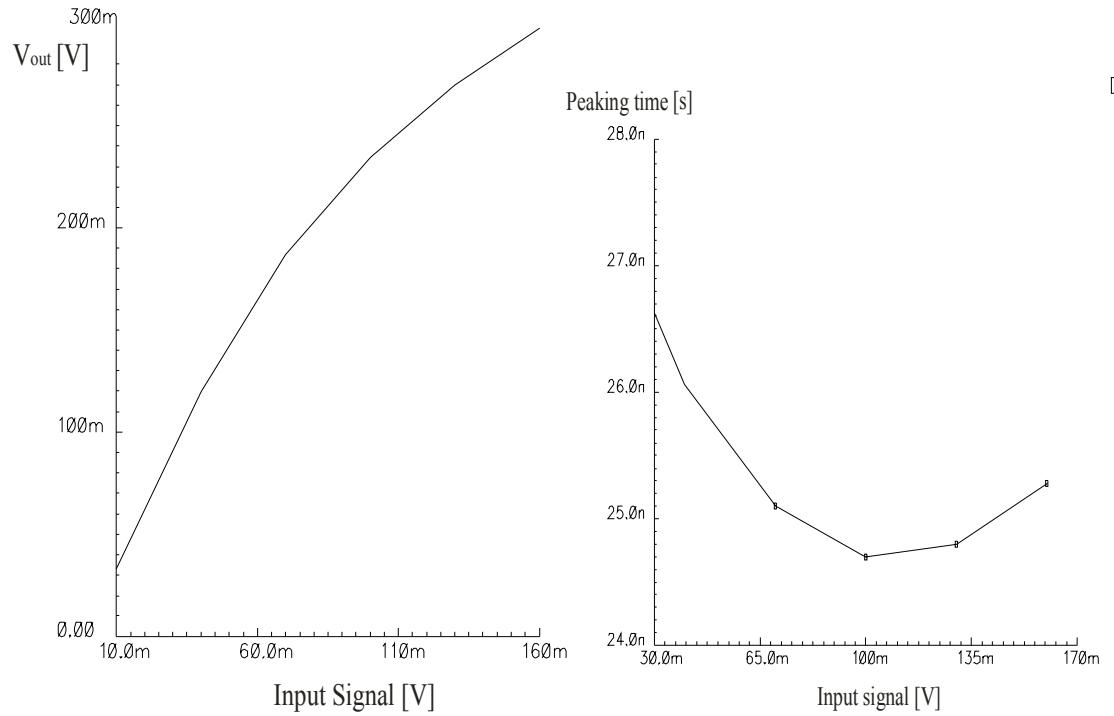

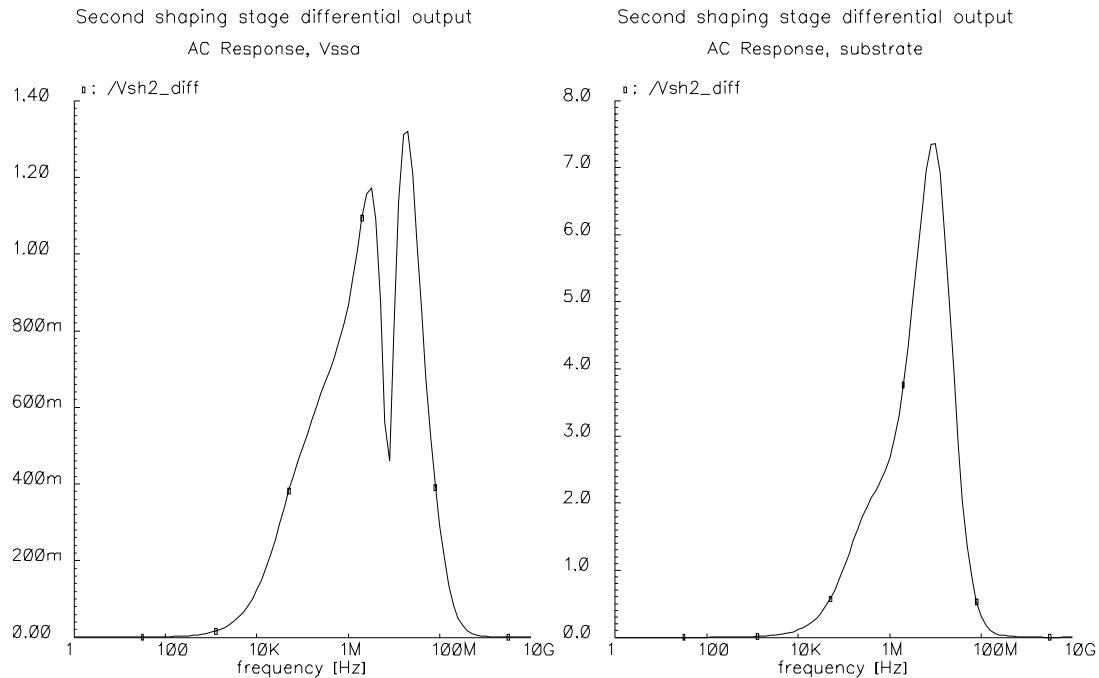

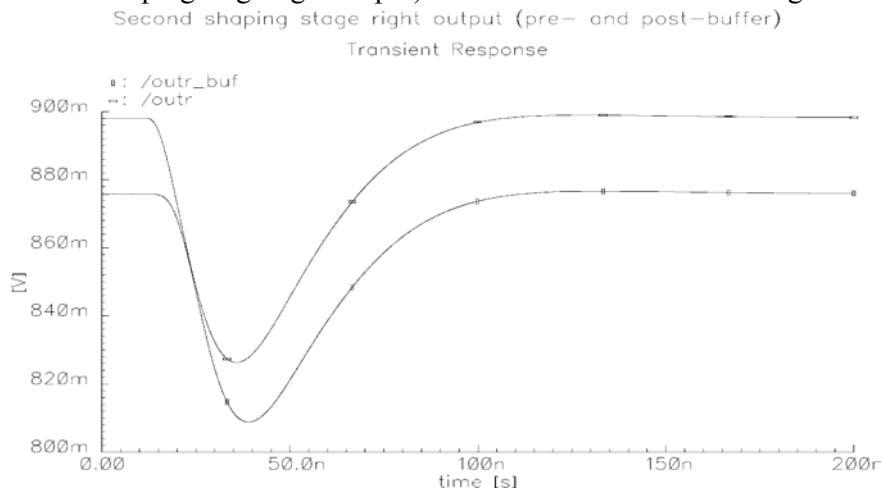

| 7.3.7.1 Transient response .....                               | 189        |

| 7.3.7.2 Peaking time and gain variations .....                 | 191        |

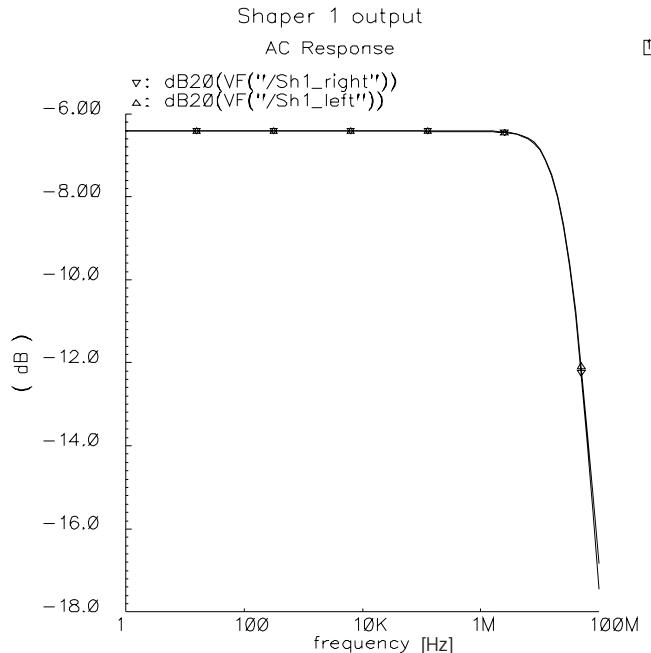

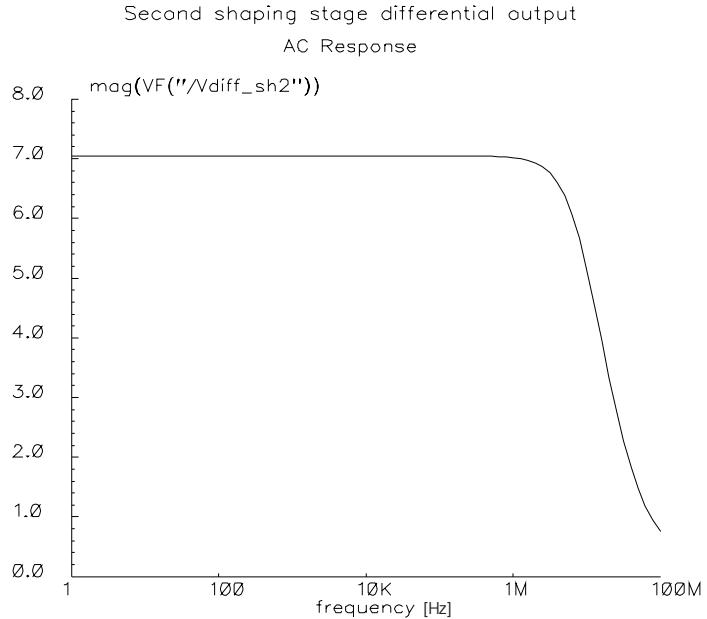

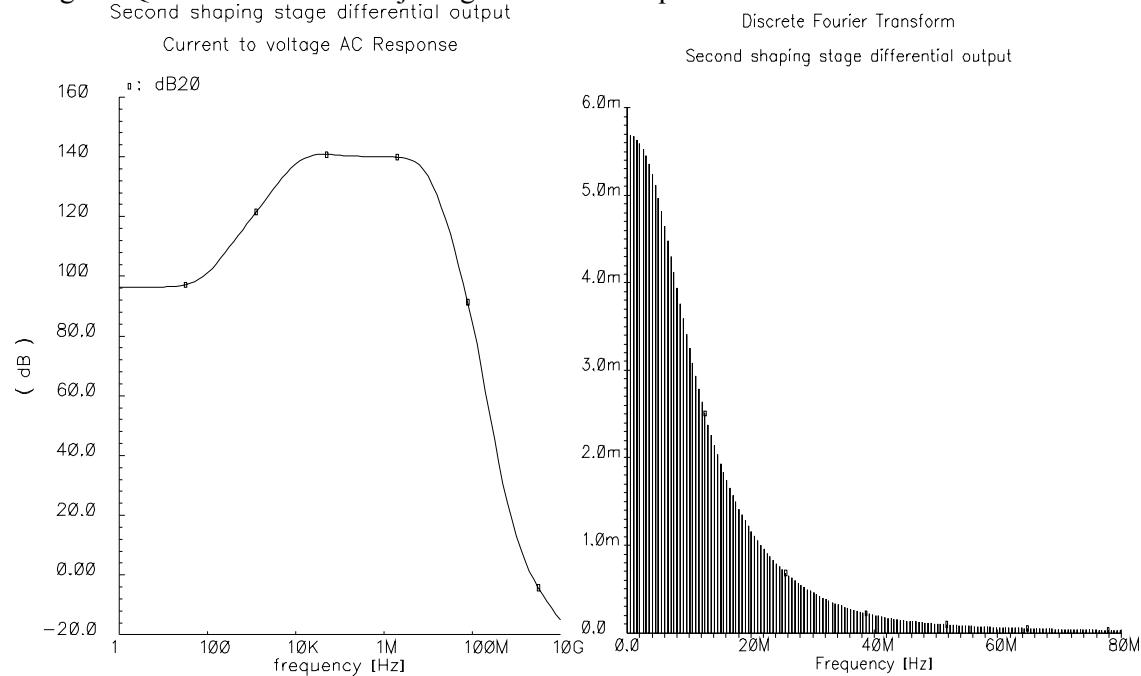

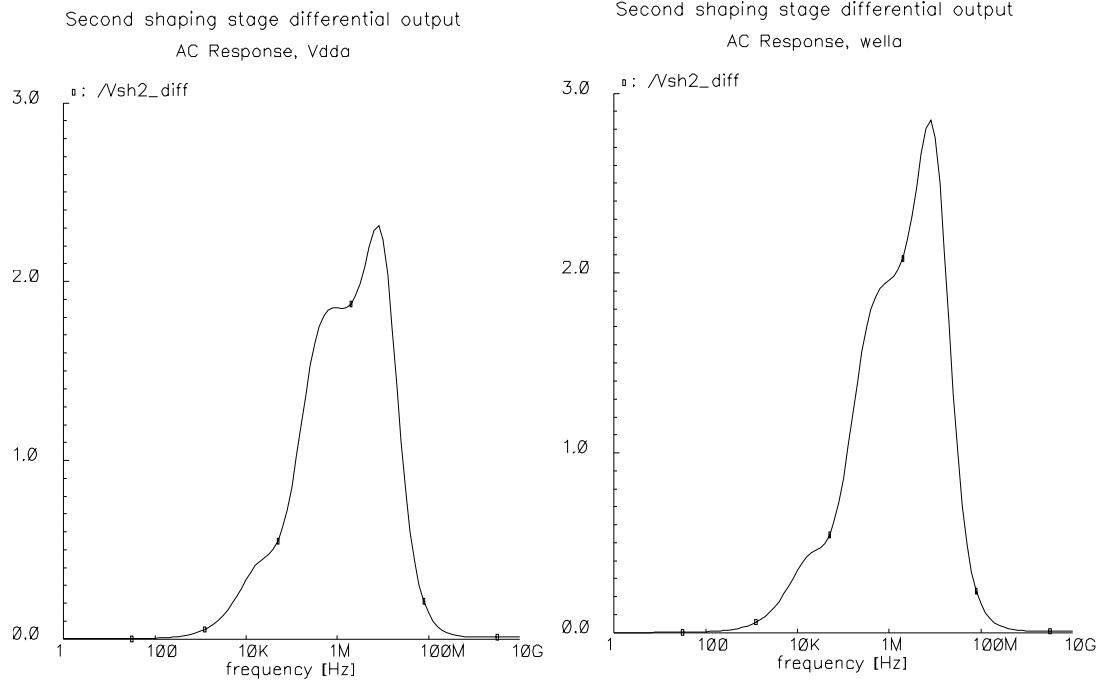

| 7.3.7.3 AC response.....                                       | 192        |

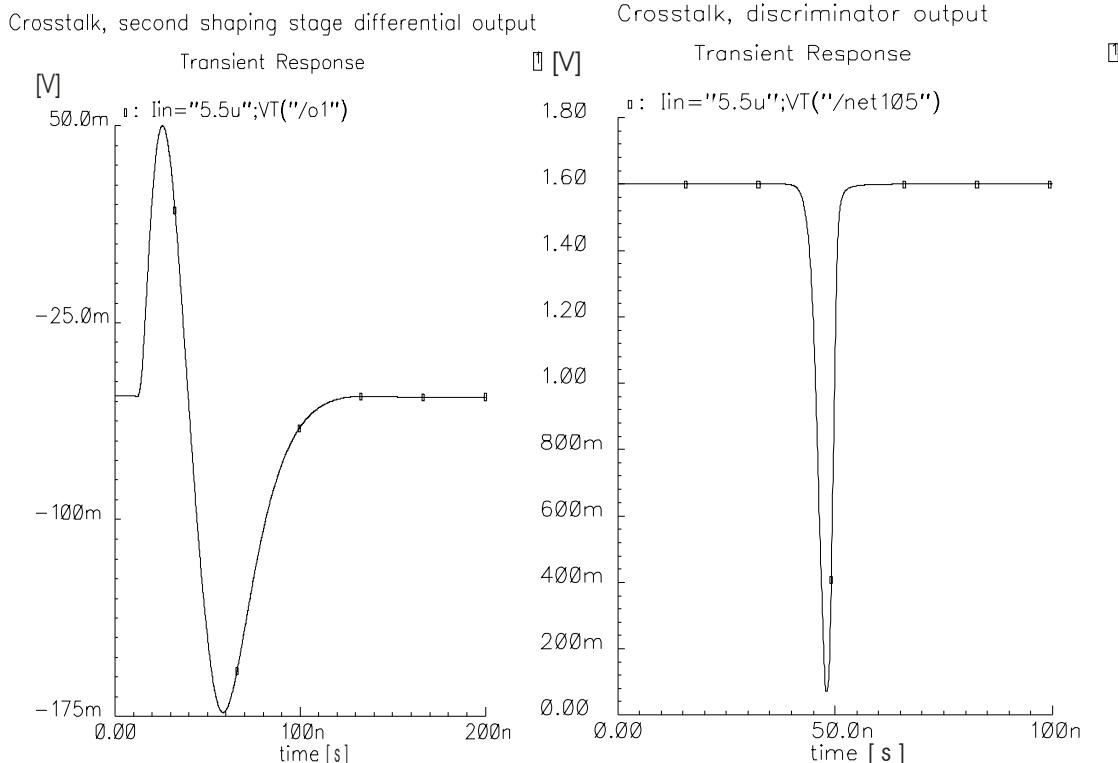

| 7.3.7.4 Crosstalk .....                                        | 192        |

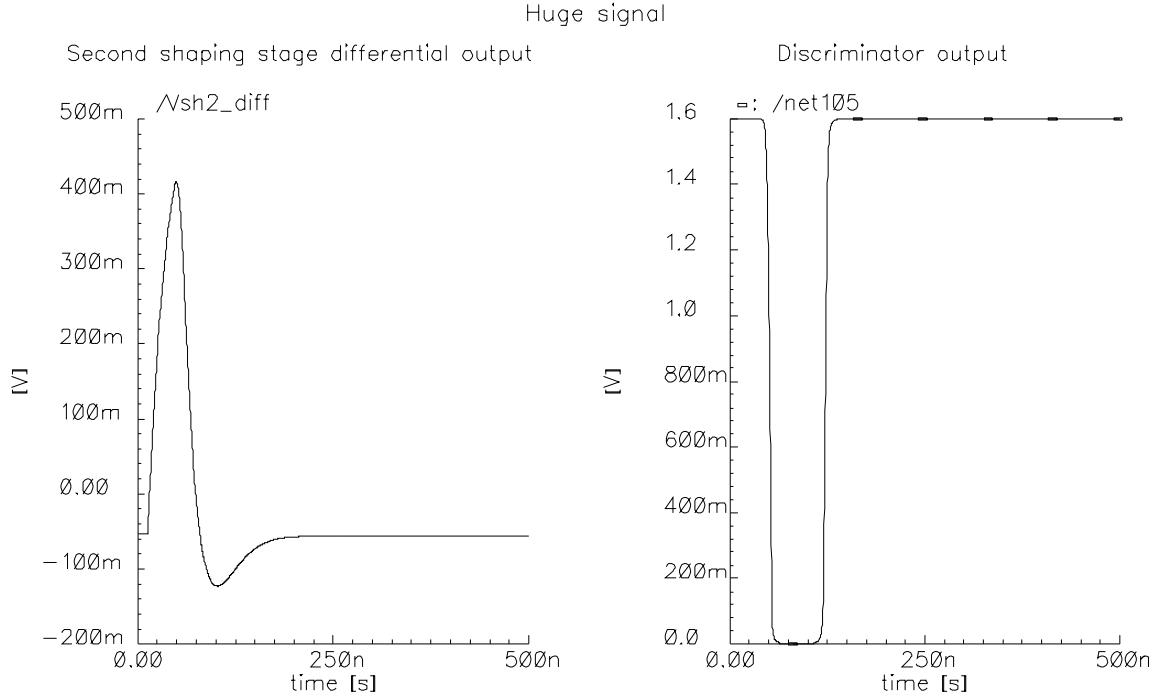

| 7.3.7.5 Response to a huge input signal.....                   | 193        |

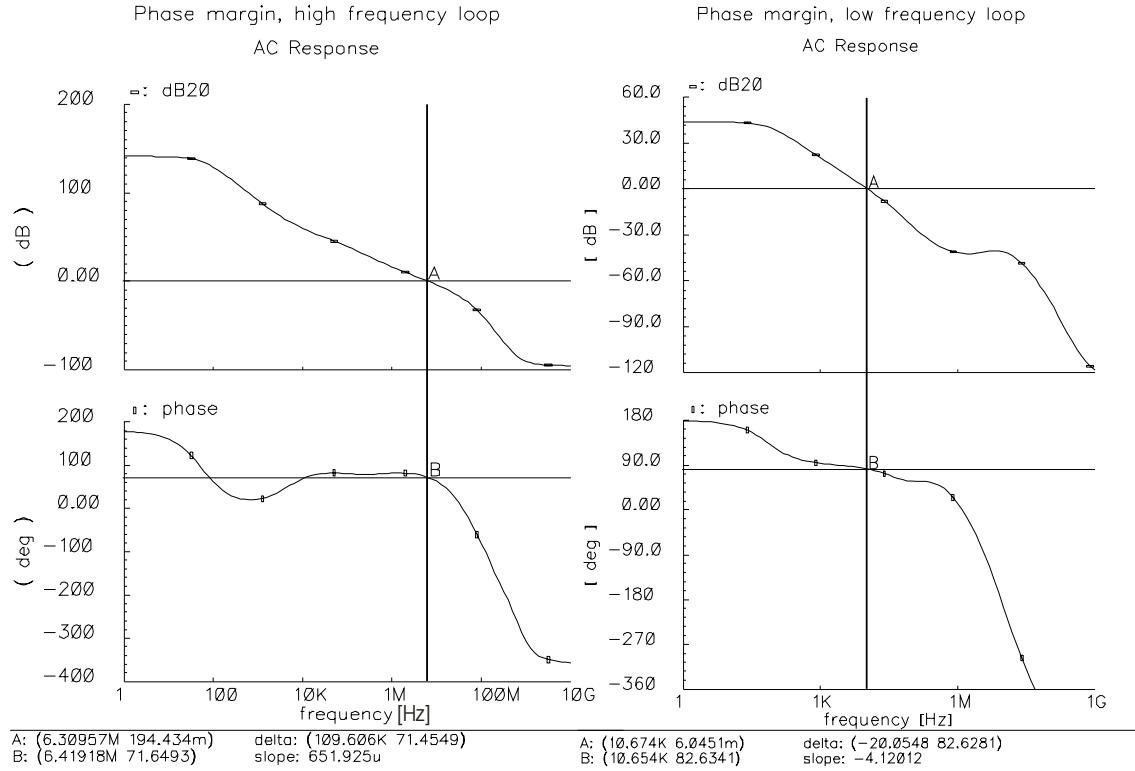

| 7.3.7.6 Phase margin.....                                      | 194        |

| 7.3.7.7 Power supply noise coupling.....                       | 195        |

| 7.3.7.8 Temperature sensitivity .....                          | 196        |

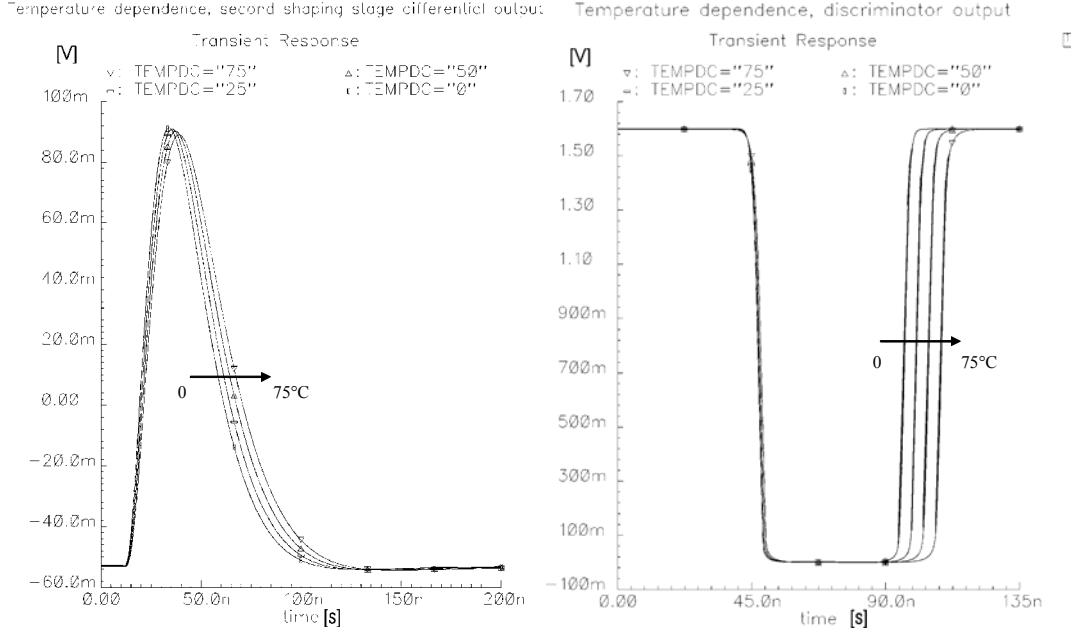

| 7.3.8 The discriminator .....                                  | 197        |

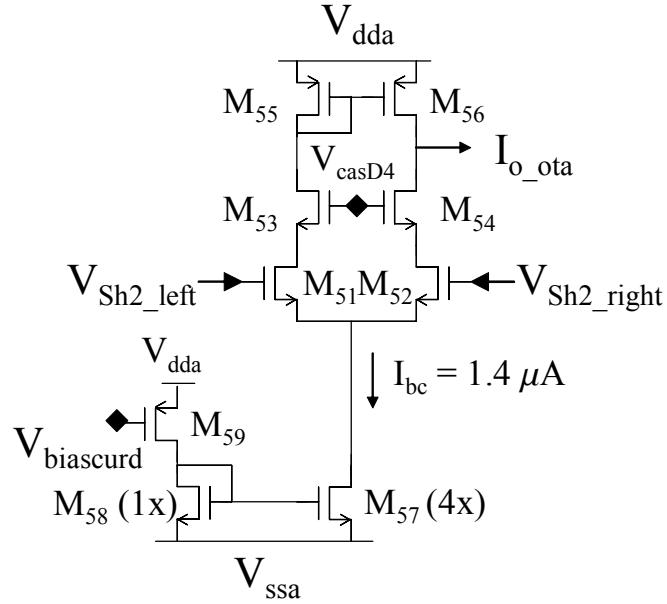

| 7.3.8.1 The Operational Transconductance Amplifier (OTA) ..... | 198        |

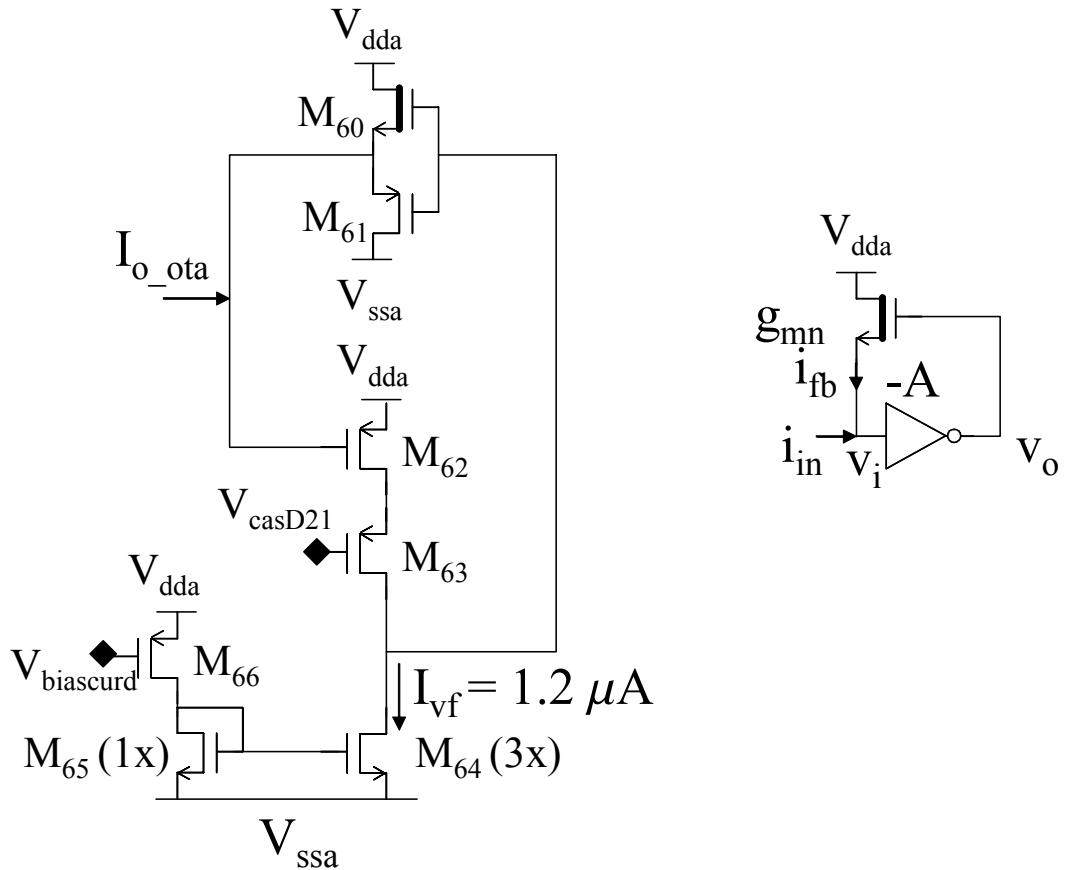

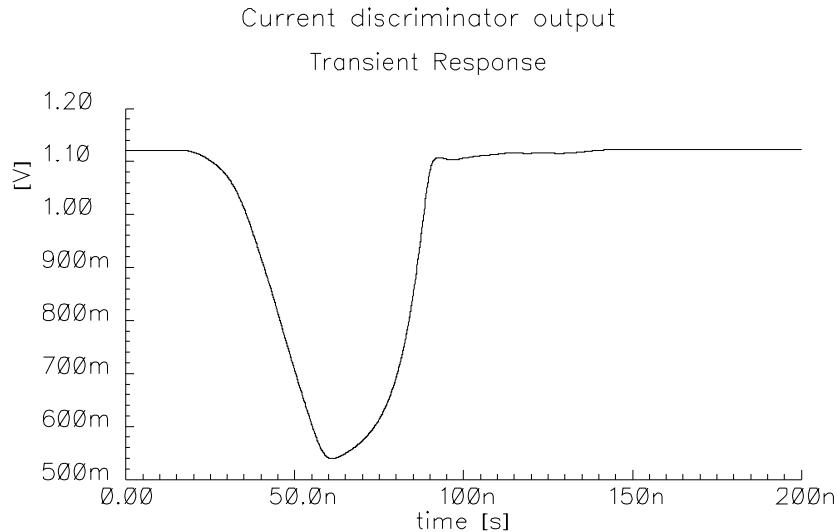

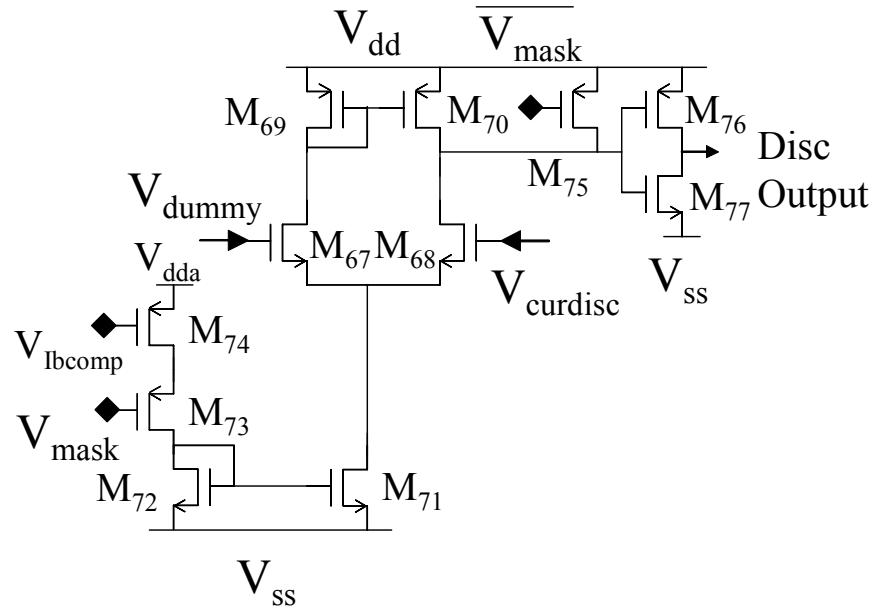

| 7.3.8.2 The current discriminator .....                        | 200        |

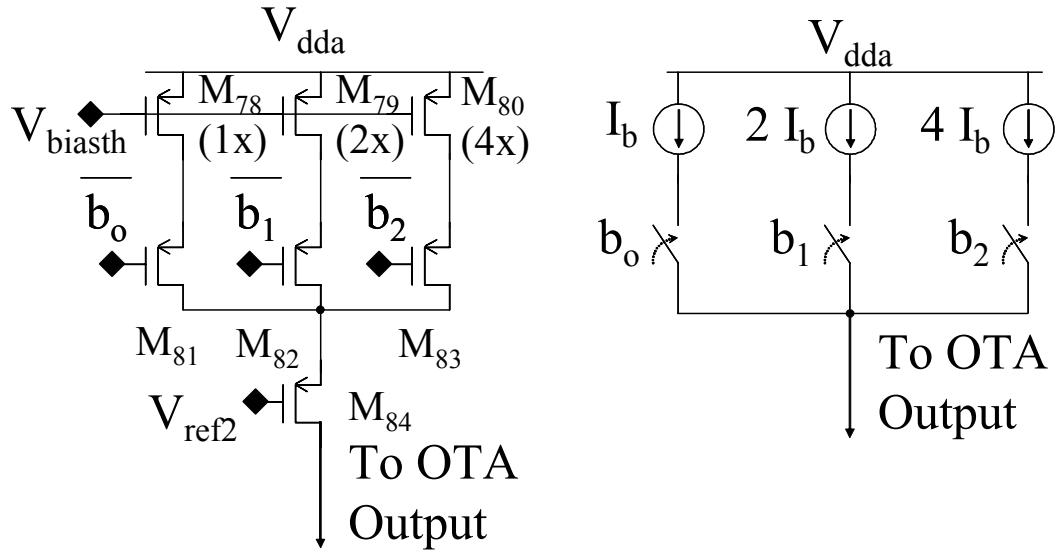

| 7.3.8.3 The threshold fine adjust block .....                  | 201        |

| 7.3.8.4 The digital conversion and the pixel masking .....     | 202        |

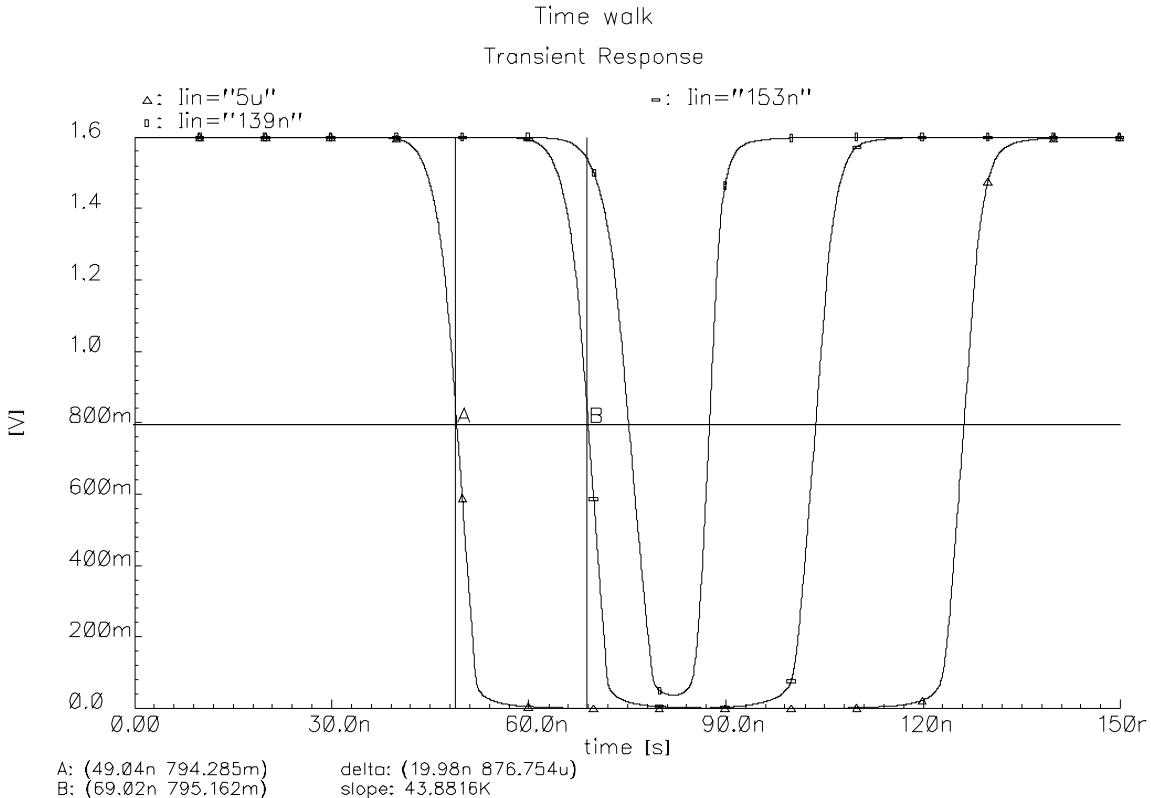

| 7.3.8.5 Time walk estimation .....                             | 203        |

| 7.3.8.6 The fast-OR and fast-multiplicity circuitry.....       | 204        |

| <b>7.4 The digital back end.....</b>                           | <b>204</b> |

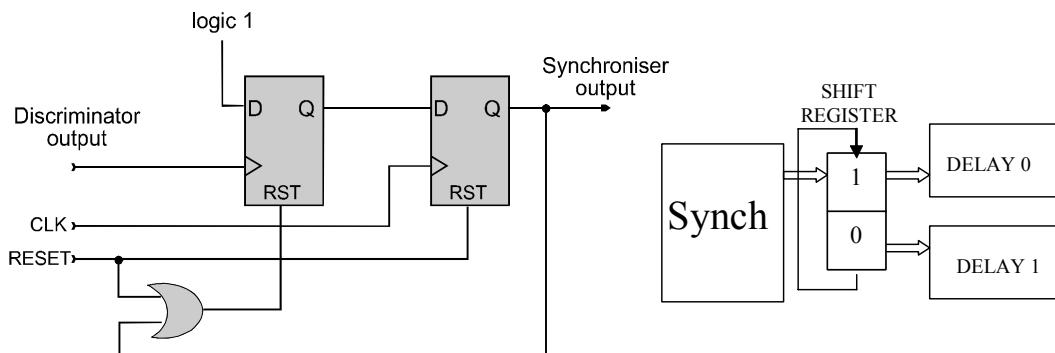

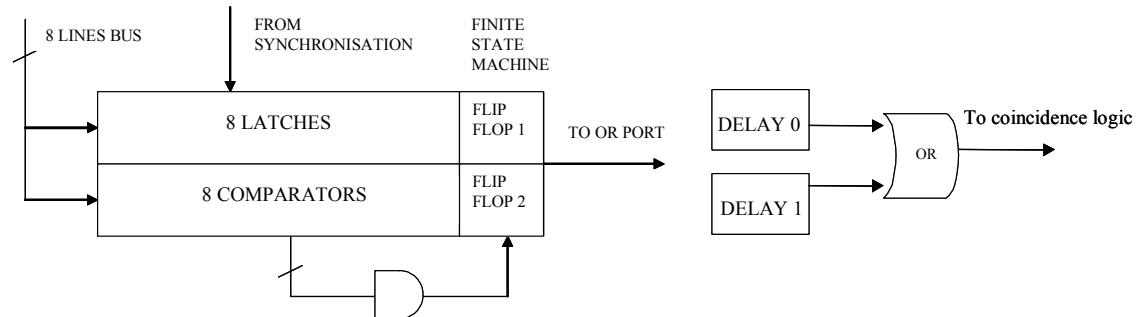

| 7.4.1 The synchroniser and the delay unit selection.....       | 204        |

| 7.4.2 The delay units .....                                    | 205        |

| 7.4.3 FIFO buffer and Readout logic .....                      | 206        |

| 7.4.4 The two operational modes .....                          | 207        |

| 7.4.4.1 The ALICE mode .....                                   | 207        |

| 7.4.4.2 The LHCb mode .....                                    | 207        |

| 7.4.4.3 Asynchronous operation.....                            | 208        |

| <b>7.5 The chip peripheral circuitry .....</b>                 | <b>209</b> |

| 7.5.1 Peripheral Control Logic.....                            | 209        |

| 7.5.2 The Digital-to-Analogue Converters (DACs) .....          | 210        |

| 7.5.3 Input/Output Pads.....                                   | 211        |

| 7.5.4 JTAG Interface .....                                     | 212        |

|                                                                               |            |

|-------------------------------------------------------------------------------|------------|

| <b>7.6 Layout considerations.....</b>                                         | <b>212</b> |

| 7.6.1    Hardening by design.....                                             | 212        |

| 7.6.2    Layout of the pixel cell .....                                       | 213        |

| 7.6.3    Signal routing and power distribution scheme .....                   | 214        |

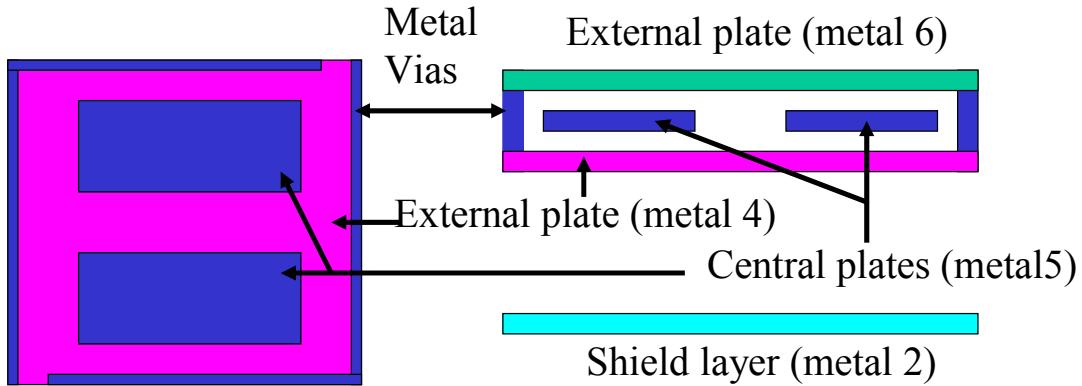

| 7.6.4    The feedback and injection capacitances.....                         | 215        |

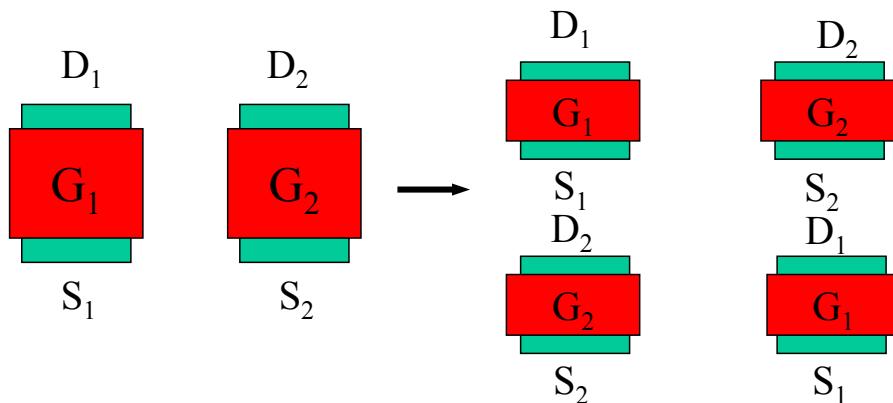

| 7.6.5    Transistor matching.....                                             | 215        |

| 7.6.6    The test structures.....                                             | 216        |

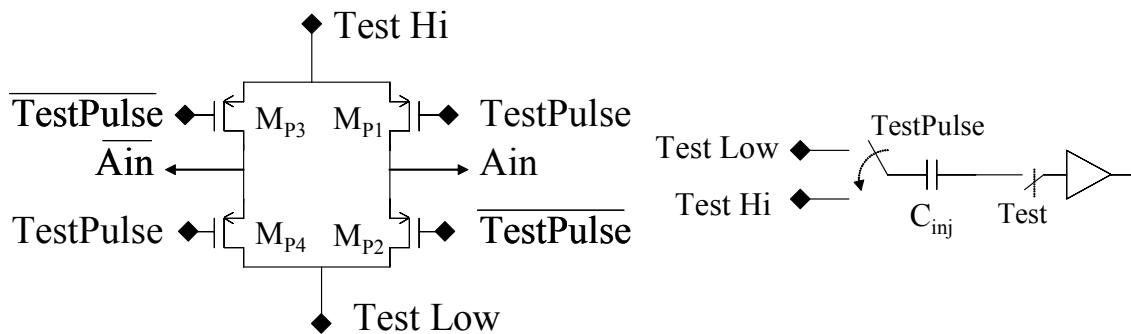

| 7.6.6.1    The injection circuitry and the on-chip pulser.....                | 216        |

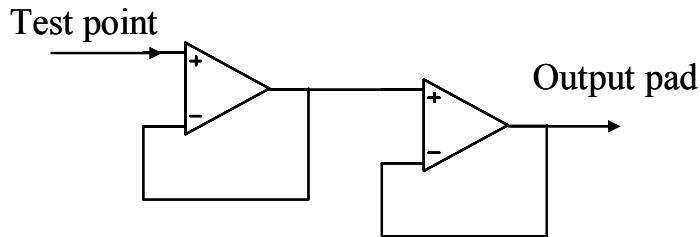

| 7.6.6.2    The analogue outputs.....                                          | 217        |

| <b>7.7 Summary .....</b>                                                      | <b>218</b> |

| <b>CHAPTER 8 THE ALICE1LHCB AND LHCPIX1 CHIPS: EXPERIMENTAL RESULTS .....</b> | <b>221</b> |

| <b>8.1 The two versions of the front-end chip.....</b>                        | <b>222</b> |

| <b>8.2 The DACs.....</b>                                                      | <b>224</b> |

| <b>8.3 Calibration of the test structures.....</b>                            | <b>225</b> |

| <b>8.4 The bare chip.....</b>                                                 | <b>226</b> |

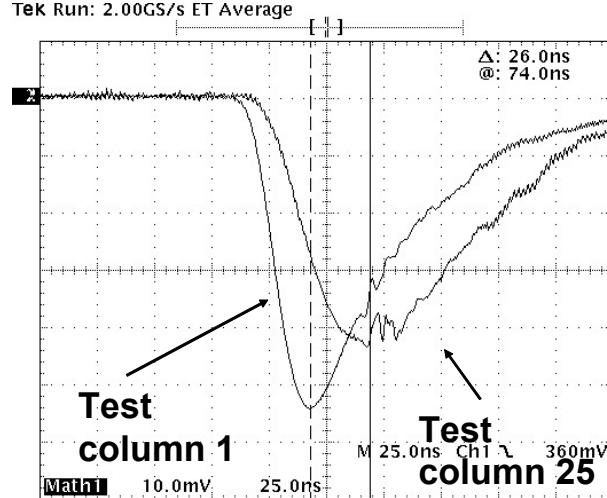

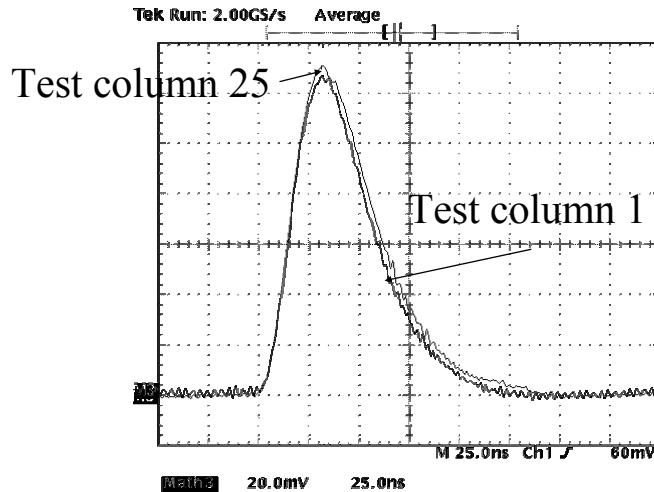

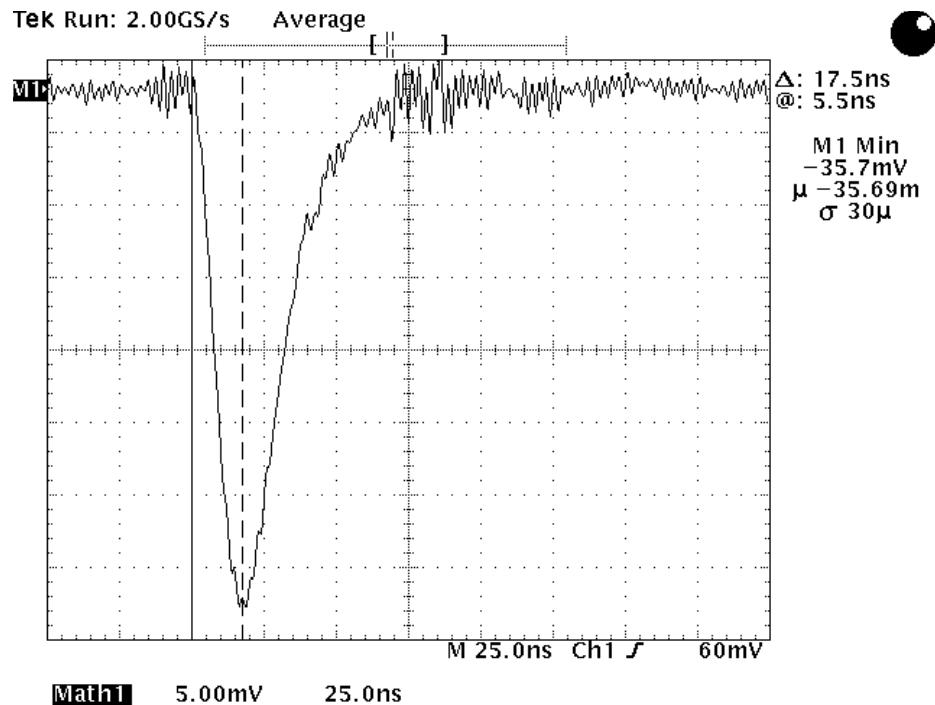

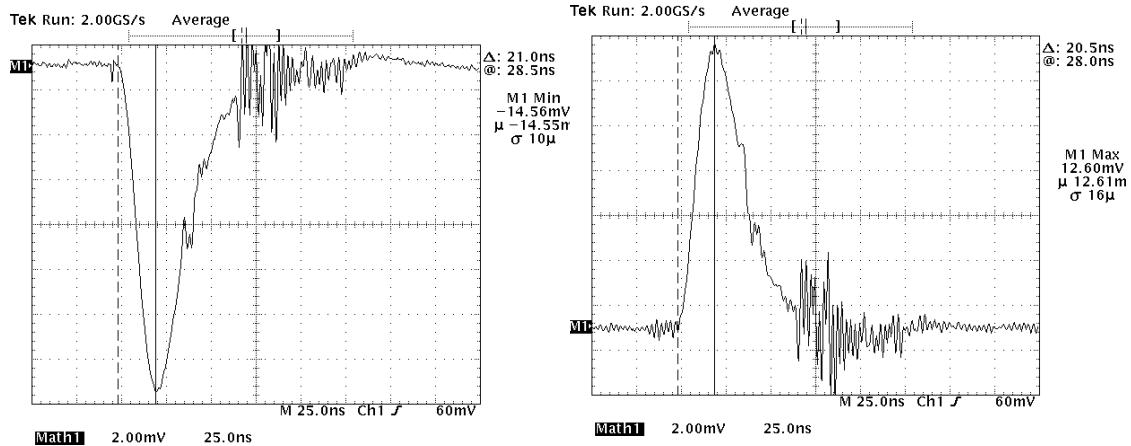

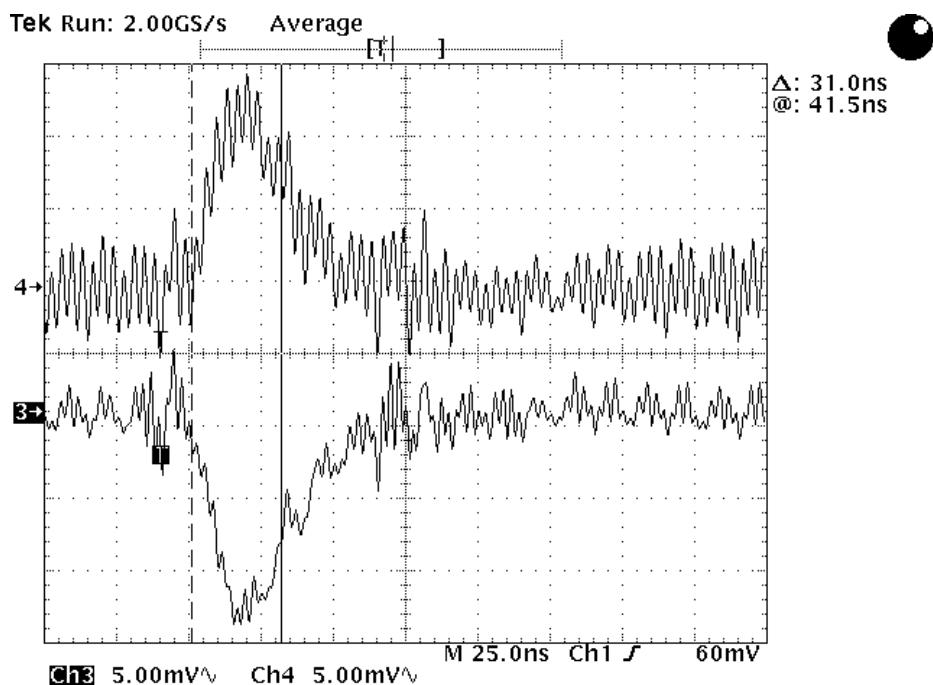

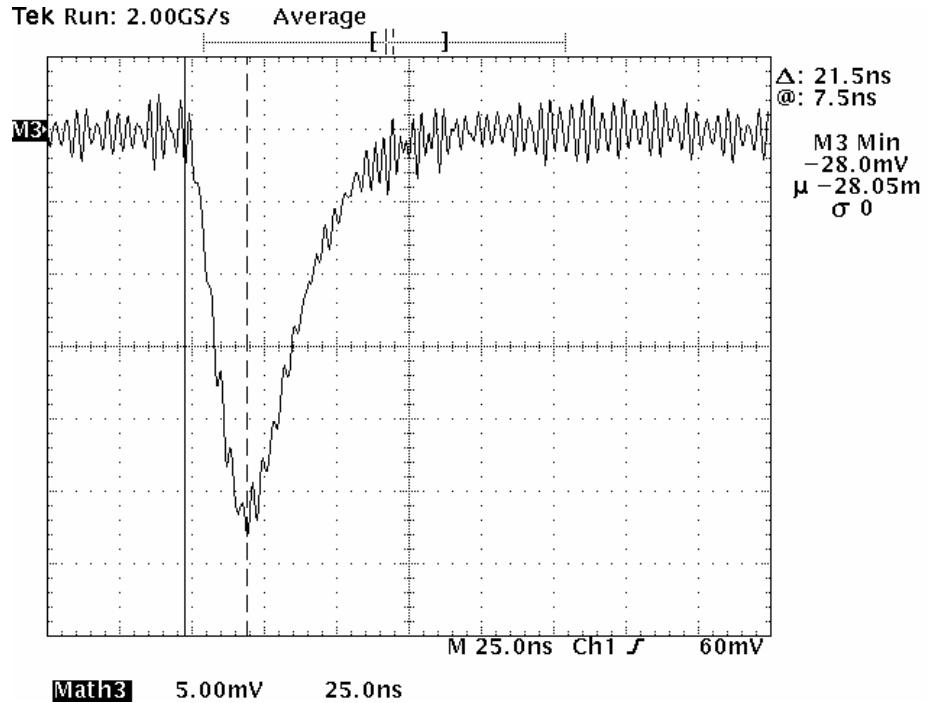

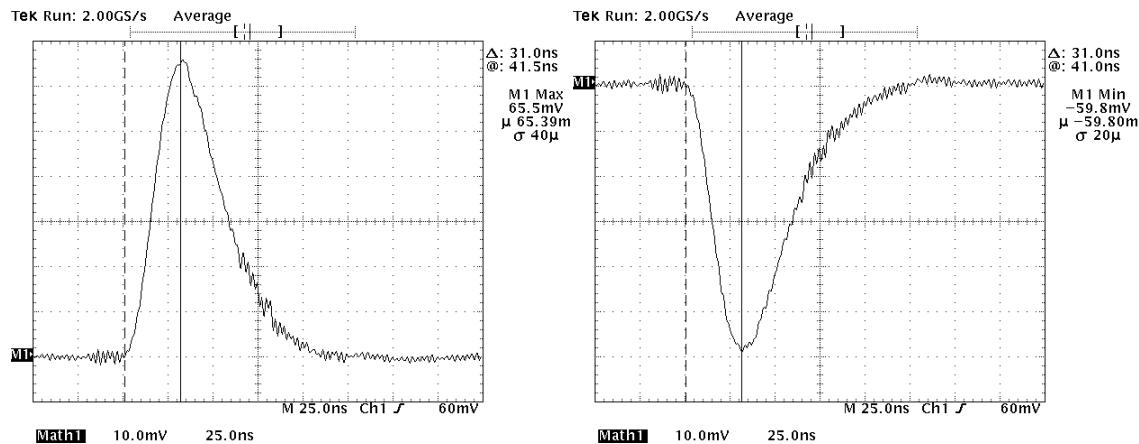

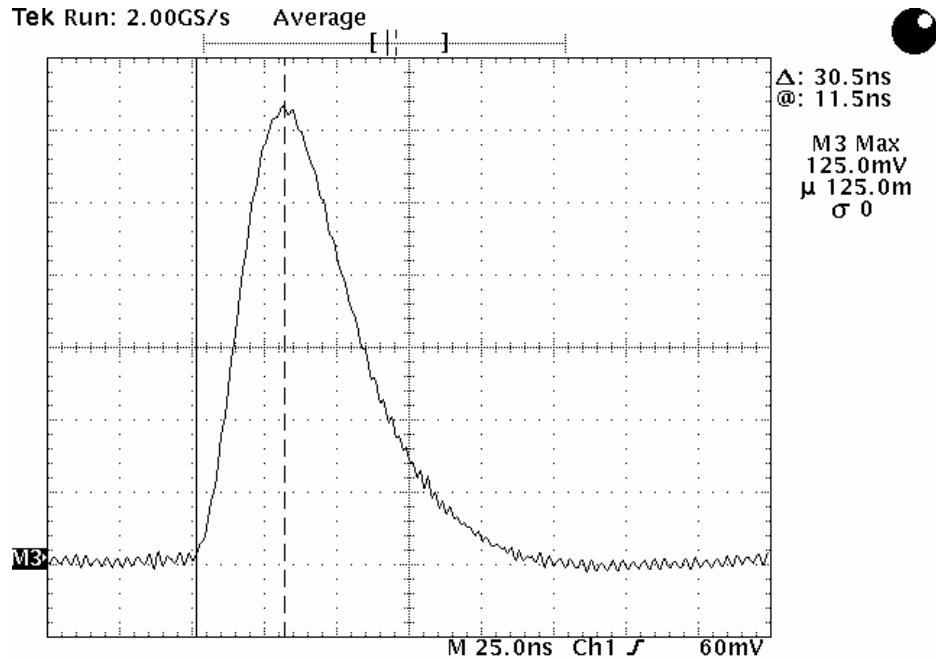

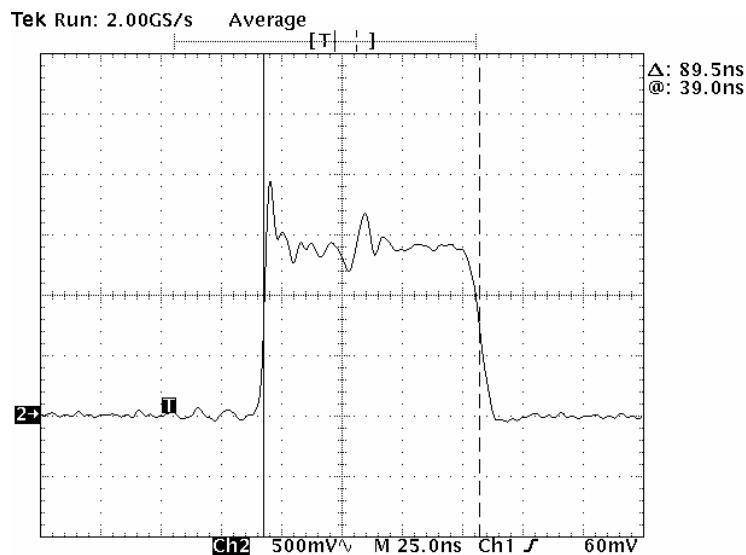

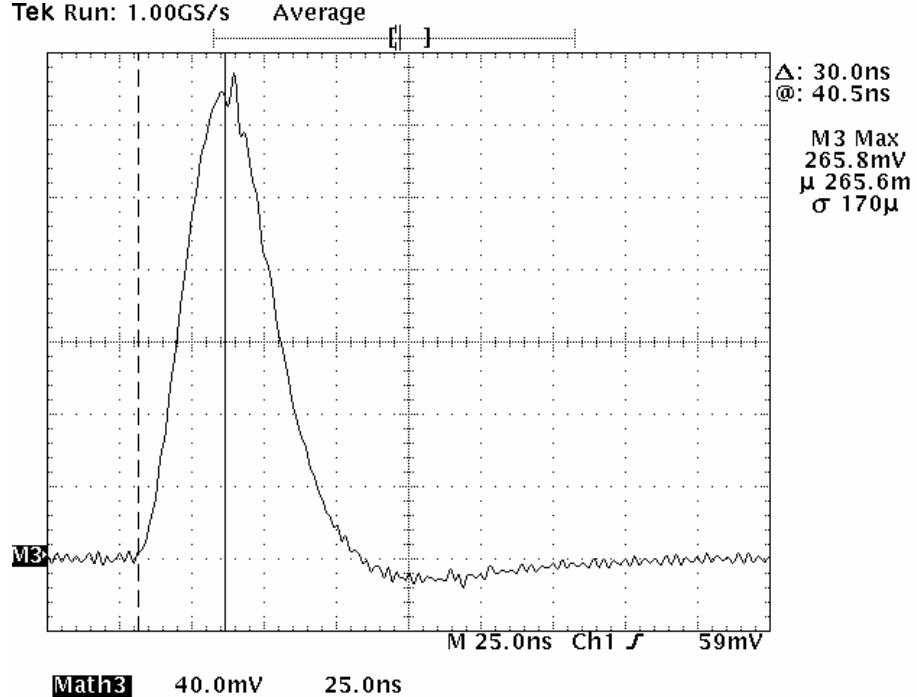

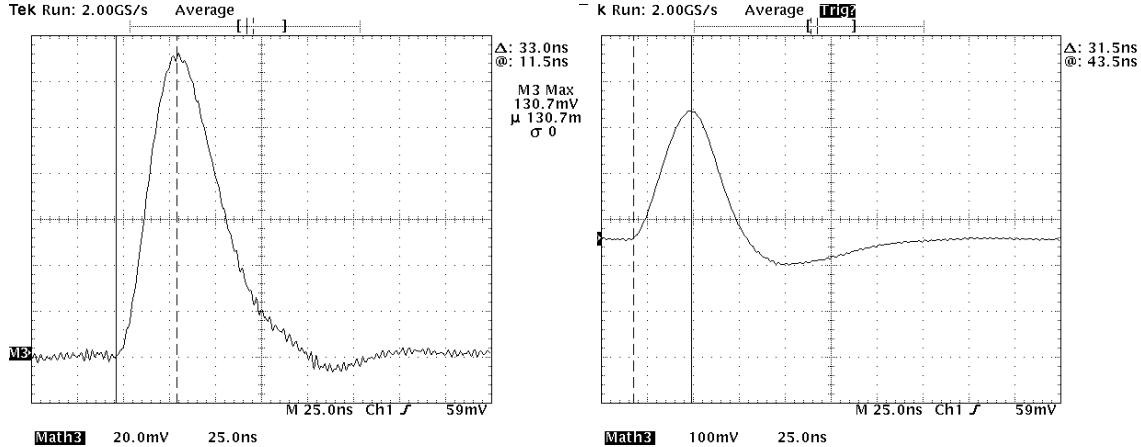

| 8.4.1    The front-end transient analysis.....                                | 227        |

| 8.4.2    Electrical crosstalk .....                                           | 232        |

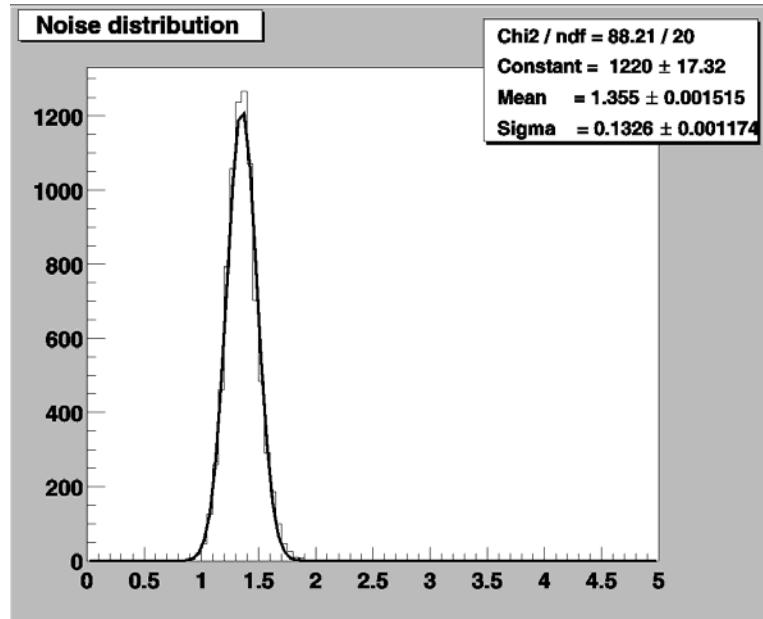

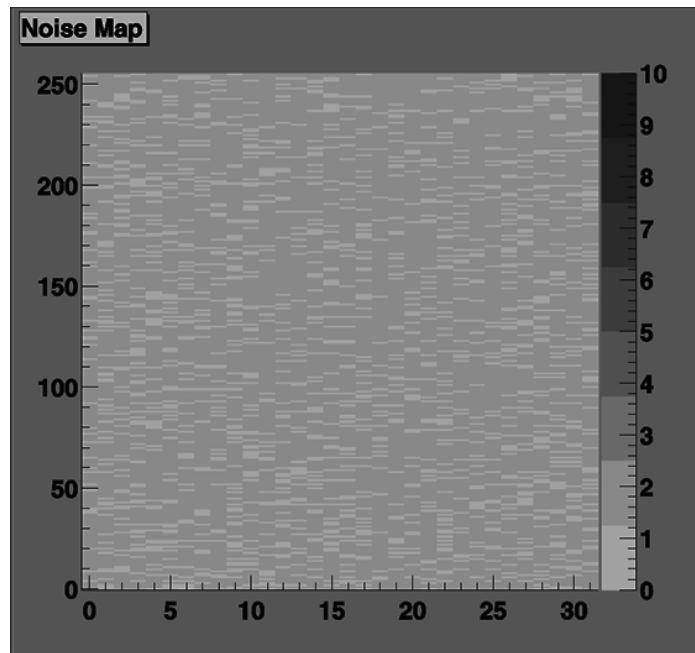

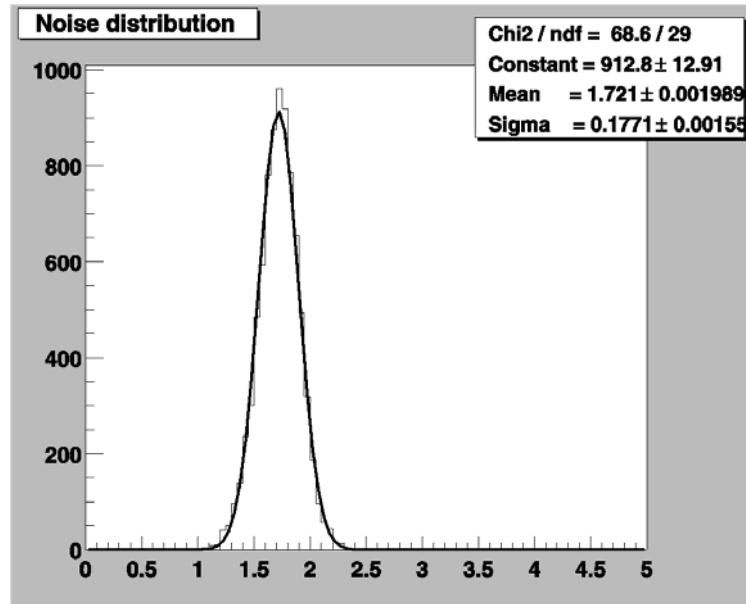

| 8.4.3    Noise measurements.....                                              | 232        |

| 8.4.4    Recovery after a huge signal .....                                   | 234        |

| 8.4.5    Threshold measurements.....                                          | 234        |

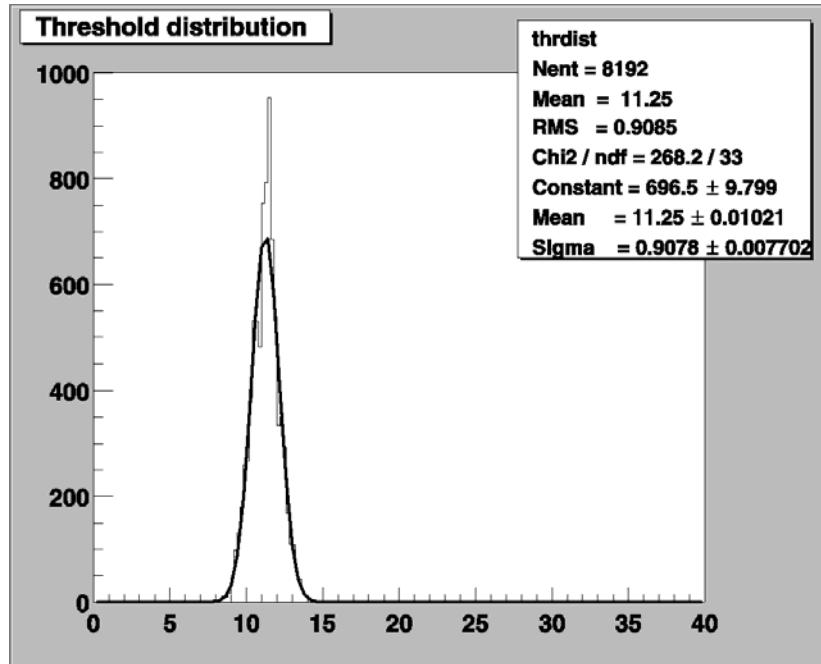

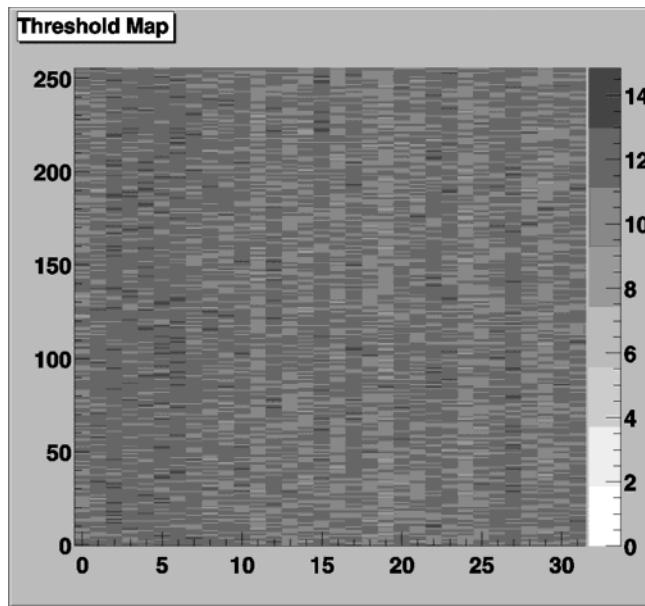

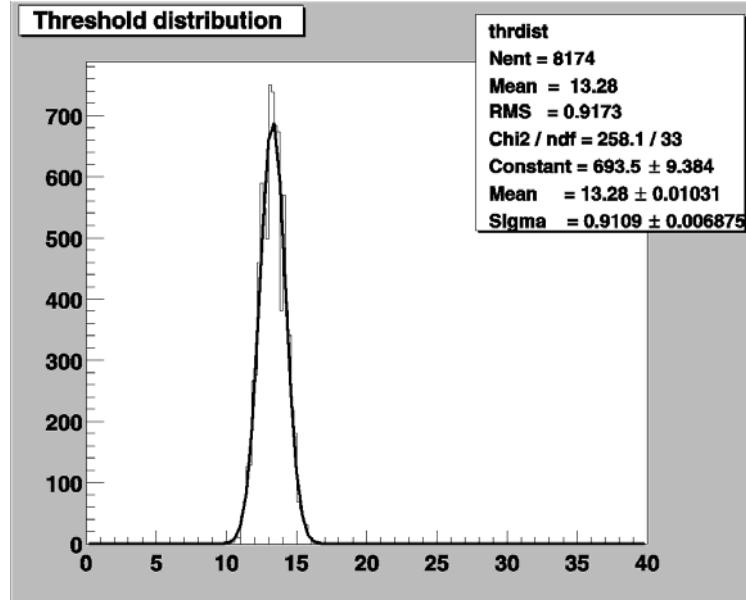

| 8.4.5.1    Threshold distribution and threshold spread.....                   | 234        |

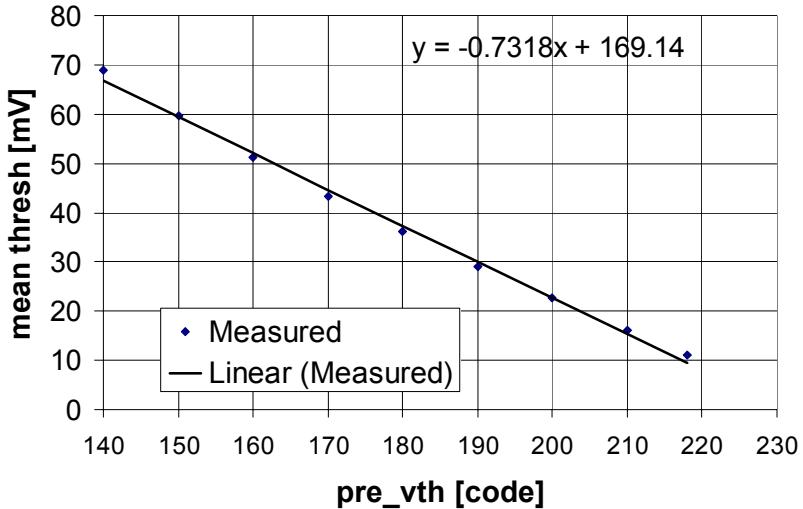

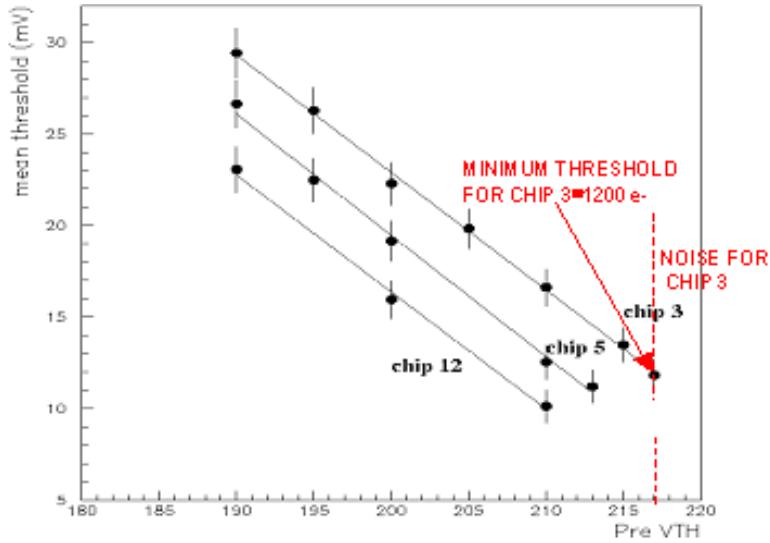

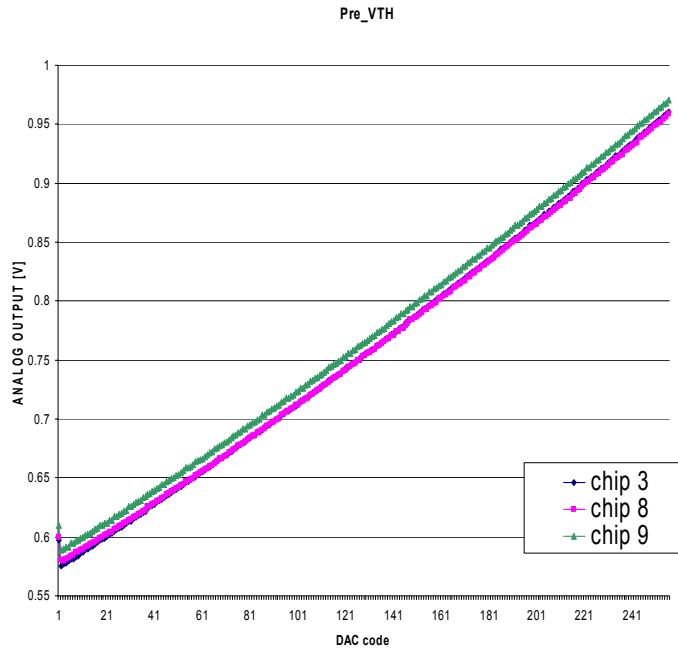

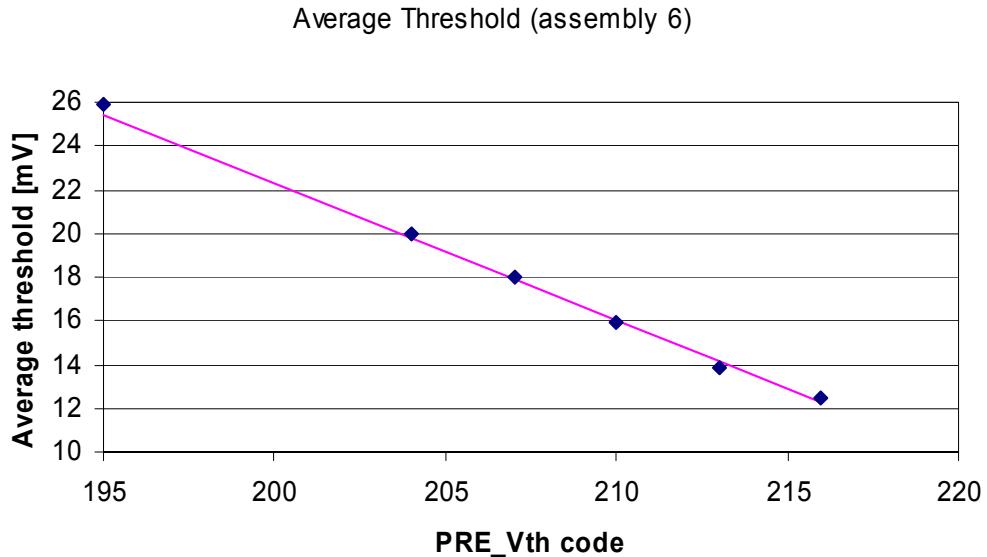

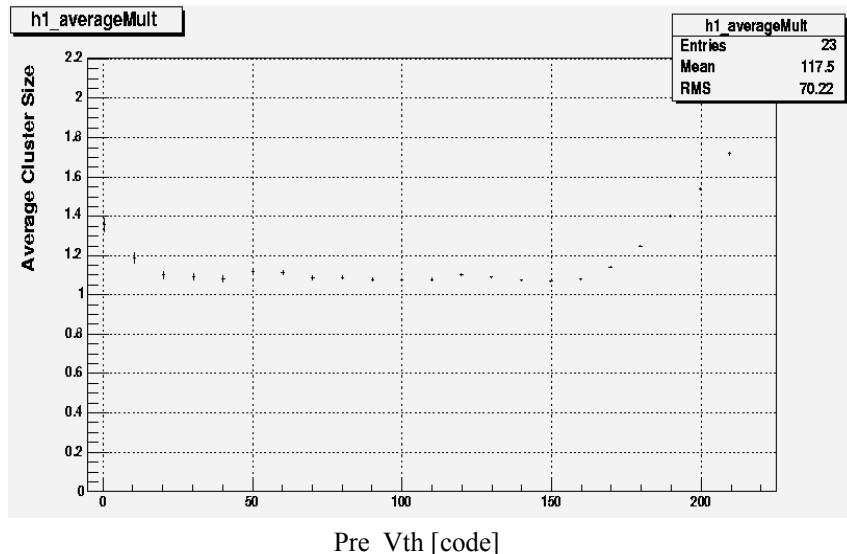

| 8.4.5.2    Effect of the mismatch of the DAC Pre_Vth on the threshold.....    | 236        |

| 8.4.5.3    Effect of the clock frequency on the minimum threshold .....       | 237        |

| 8.4.6    Threshold adjust .....                                               | 237        |

| 8.4.7    Wafer probing.....                                                   | 238        |

| 8.4.8    X-ray irradiations .....                                             | 240        |

| 8.4.9    Single event effects sensitivity.....                                | 244        |

| 8.4.9.1    Measurements with ions .....                                       | 244        |

| 8.4.9.2    Measurements with 60 MeV protons .....                             | 245        |

| 8.4.10    Temperature sensitivity .....                                       | 245        |

| <b>8.5 The assembly.....</b>                                                  | <b>247</b> |

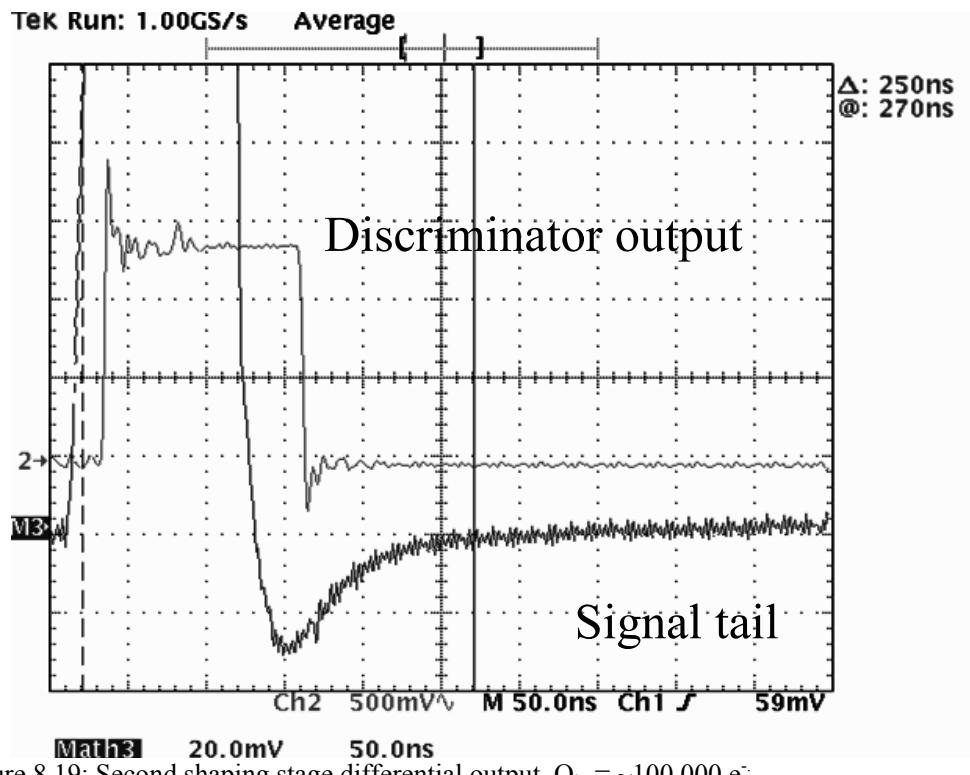

| 8.5.1    Transient analysis .....                                             | 248        |

|                                                                                                      |                                                                           |            |

|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------|

| 8.5.2                                                                                                | Threshold and noise measurements .....                                    | 248        |

| 8.5.3                                                                                                | Timewalk .....                                                            | 249        |

| 8.5.4                                                                                                | Capacitive charge sharing .....                                           | 251        |

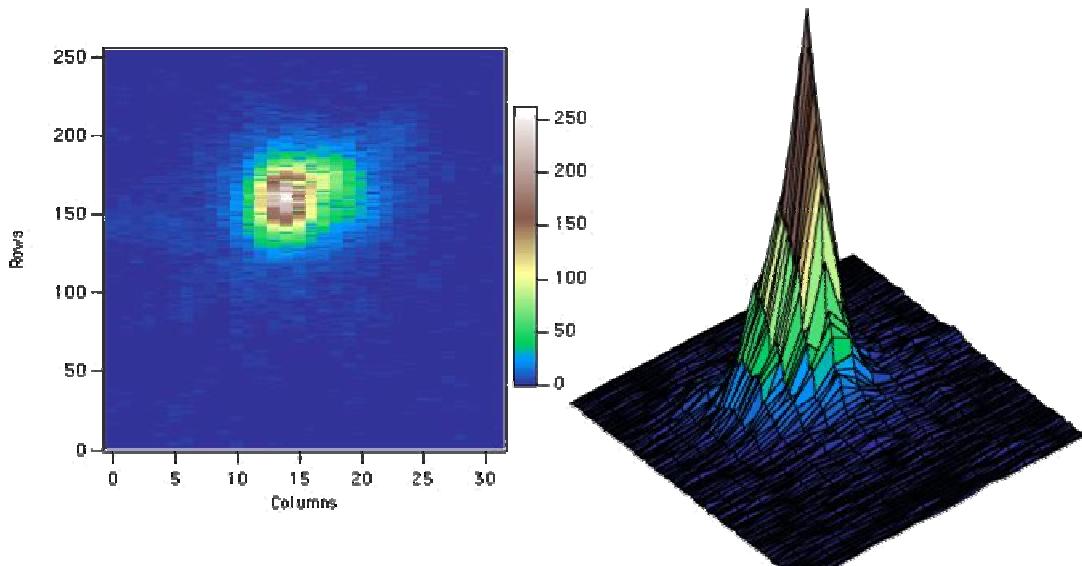

| 8.5.5                                                                                                | Source tests .....                                                        | 251        |

| 8.5.6                                                                                                | X-ray irradiation .....                                                   | 252        |

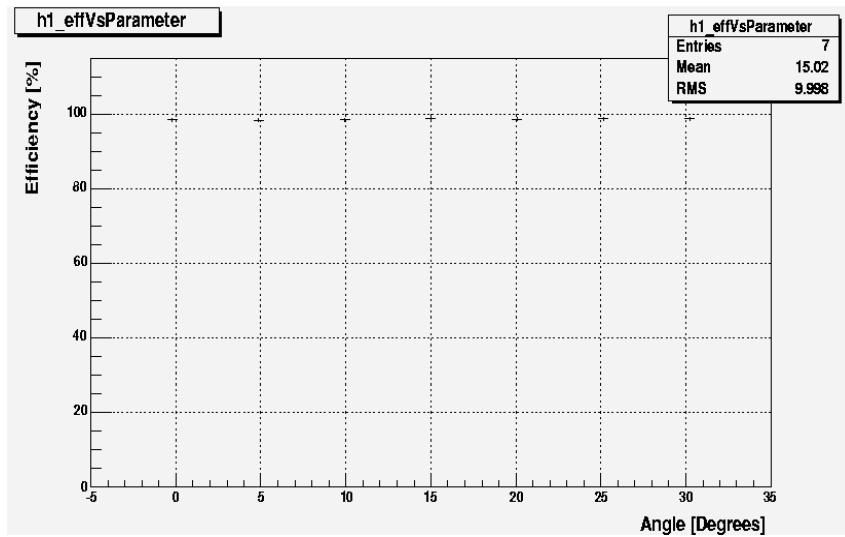

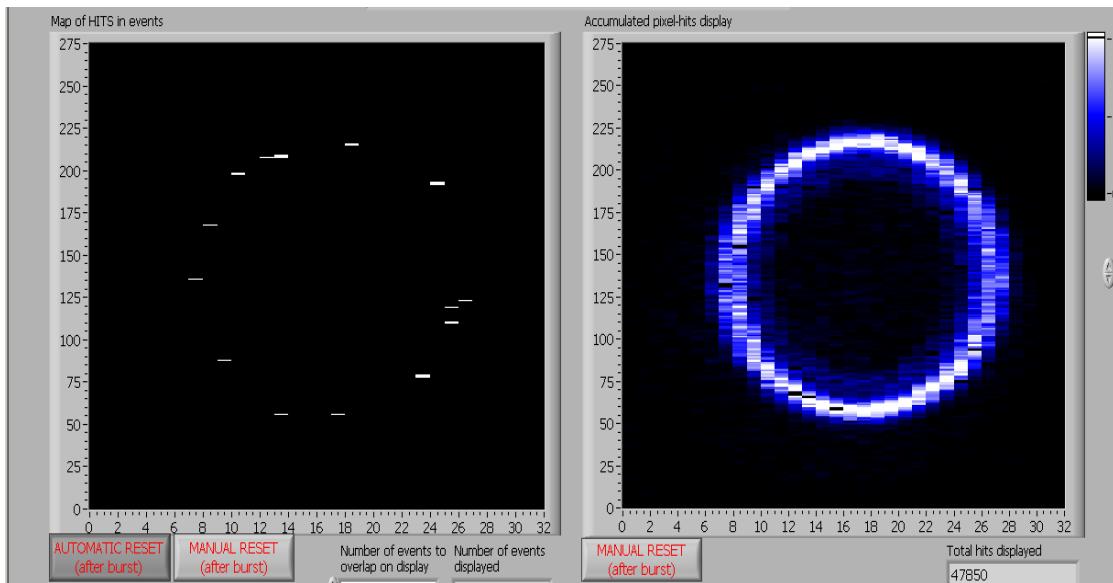

| 8.5.7                                                                                                | Test beam results .....                                                   | 253        |

| 8.5.7.1                                                                                              | Test beam with 150 GeV/c pions at CERN, 2001 .....                        | 253        |

| 8.5.7.2                                                                                              | Test beam with 350 GeV/c protons at CERN, 2002 .....                      | 256        |

| 8.5.7.3                                                                                              | Test beam with 158 GeV/c Indium and 120 GeV/c protons at CERN, 2003 ..... | 259        |

| <b>8.6</b>                                                                                           | <b>Summary .....</b>                                                      | <b>261</b> |

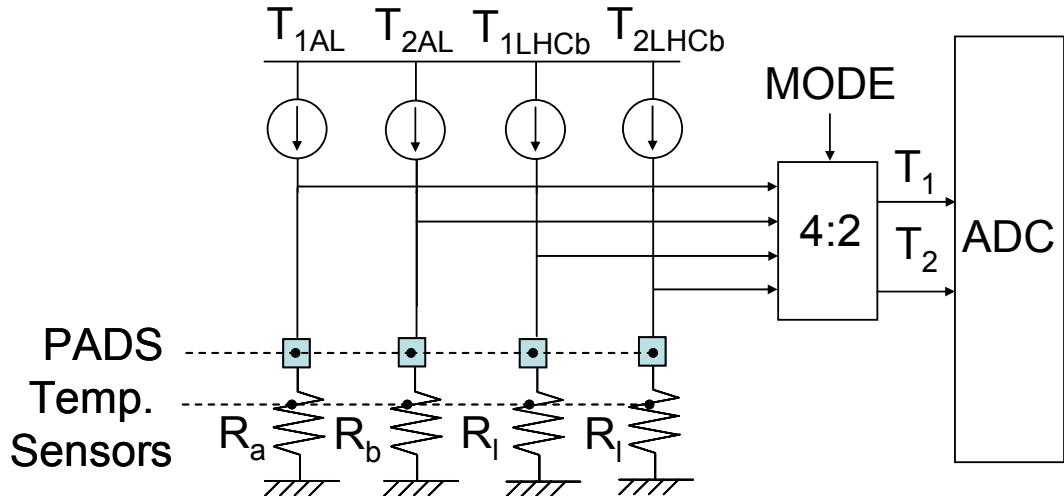

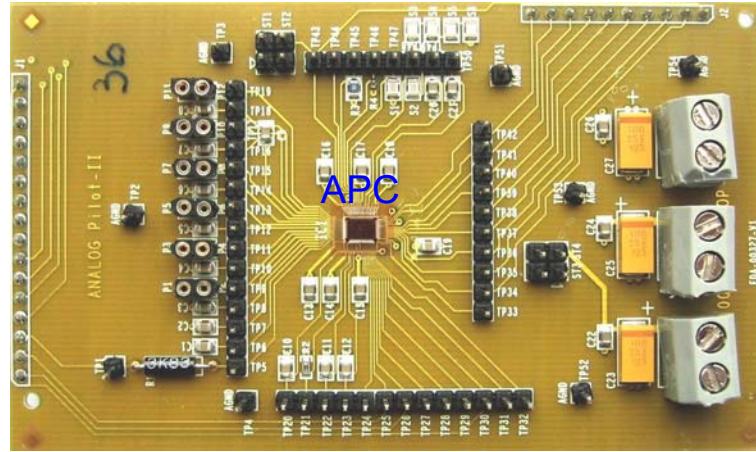

| <b>CHAPTER 9 AN AUXILIARY CHIP FOR THE ALICE AND LHCb PIXEL CHIPS: THE ANALOGUE PILOT CHIP .....</b> |                                                                           | <b>263</b> |

| <b>9.1</b>                                                                                           | <b>Chip building blocks .....</b>                                         | <b>263</b> |

| 9.1.1                                                                                                | General description .....                                                 | 263        |

| 9.1.2                                                                                                | The bandgap cell .....                                                    | 264        |

| 9.1.3                                                                                                | The reference circuits .....                                              | 265        |

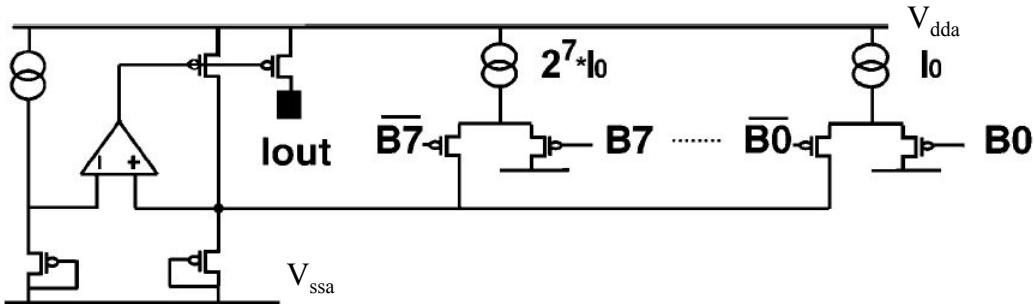

| 9.1.4                                                                                                | The DACs .....                                                            | 267        |

| 9.1.5                                                                                                | The ADC .....                                                             | 267        |

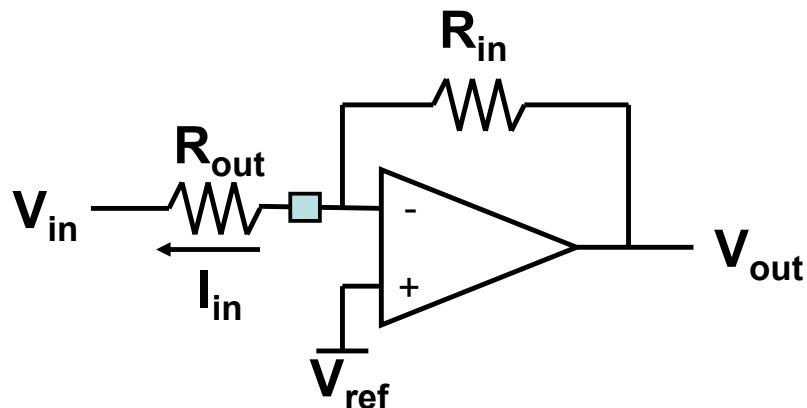

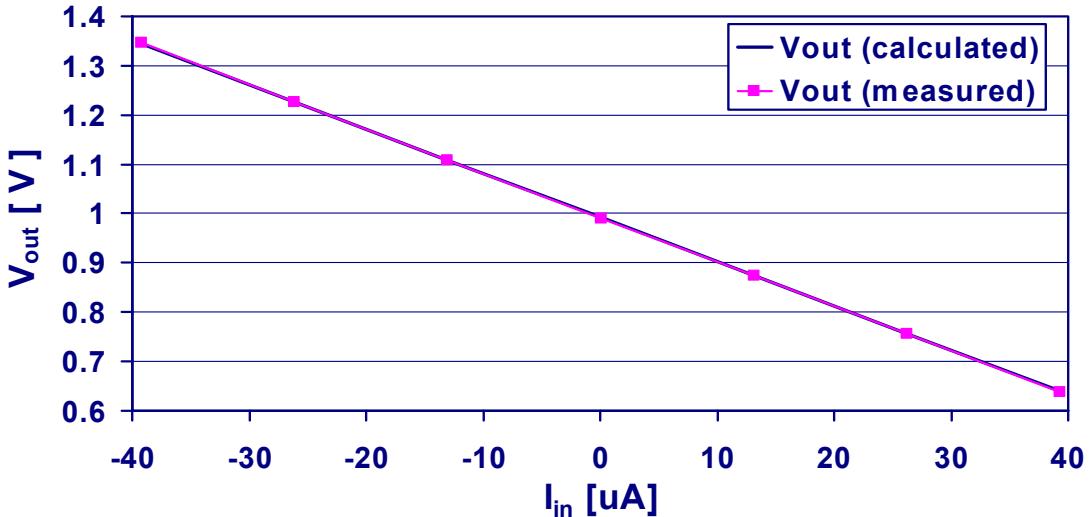

| 9.1.6                                                                                                | The current sensing stage .....                                           | 268        |

| 9.1.7                                                                                                | The current sources for temperature measurement .....                     | 269        |

| 9.1.8                                                                                                | The digital control section .....                                         | 270        |

| 9.1.8.1                                                                                              | Programming of the DACs .....                                             | 270        |

| 9.1.8.2                                                                                              | Conversion of the 16 analogue values .....                                | 270        |

| 9.1.8.3                                                                                              | Reading the measured analogue values .....                                | 270        |

| 9.1.8.4                                                                                              | Serial temperature transmission .....                                     | 270        |

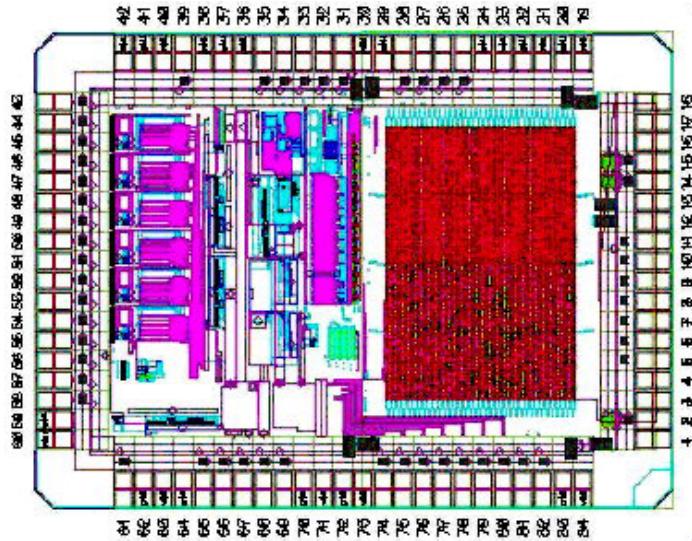

| 9.1.9                                                                                                | Chip layout .....                                                         | 270        |

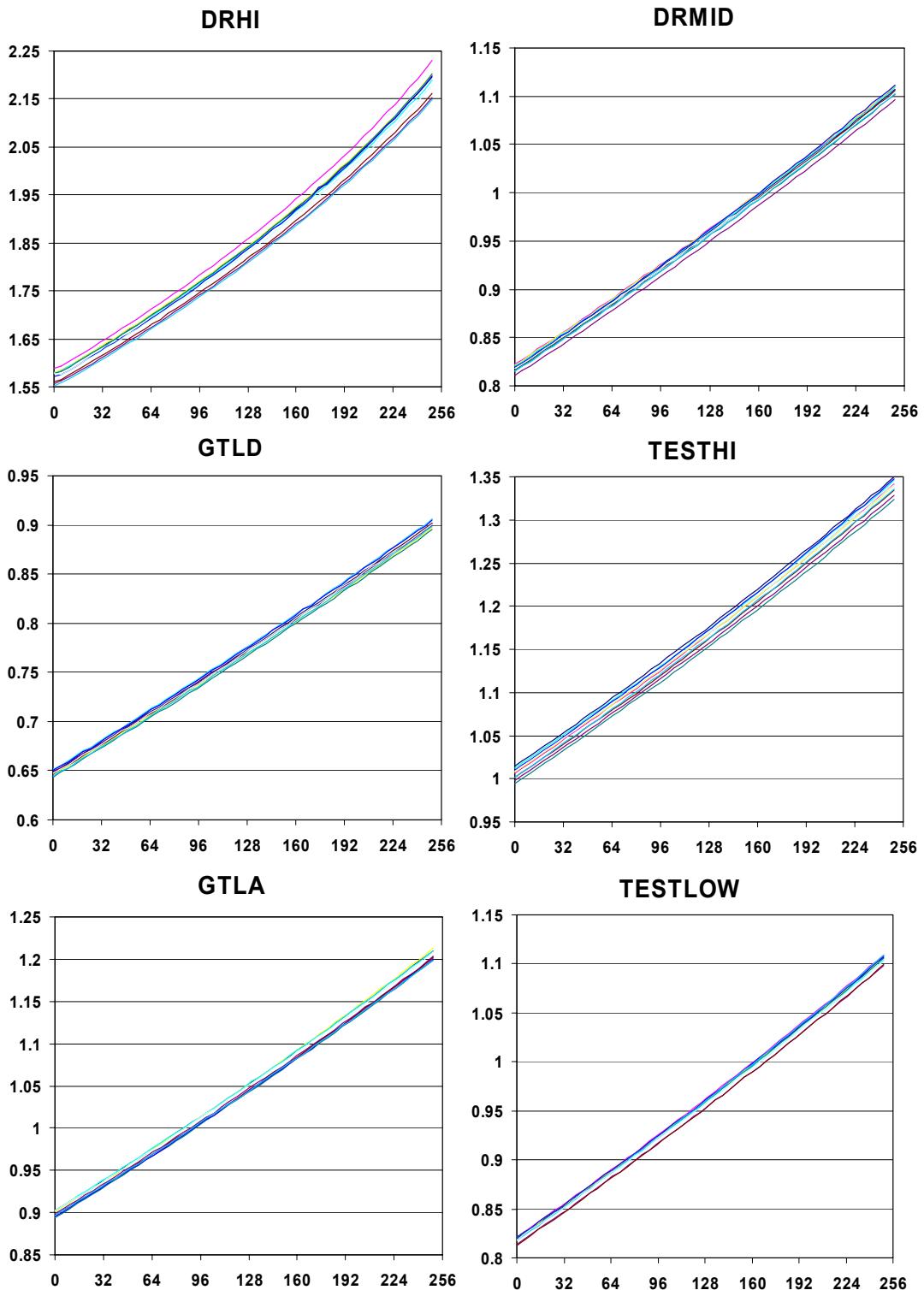

| <b>9.2</b>                                                                                           | <b>APC measurement results .....</b>                                      | <b>271</b> |

| 9.2.1                                                                                                | The bandgap cell and the reference circuits .....                         | 272        |

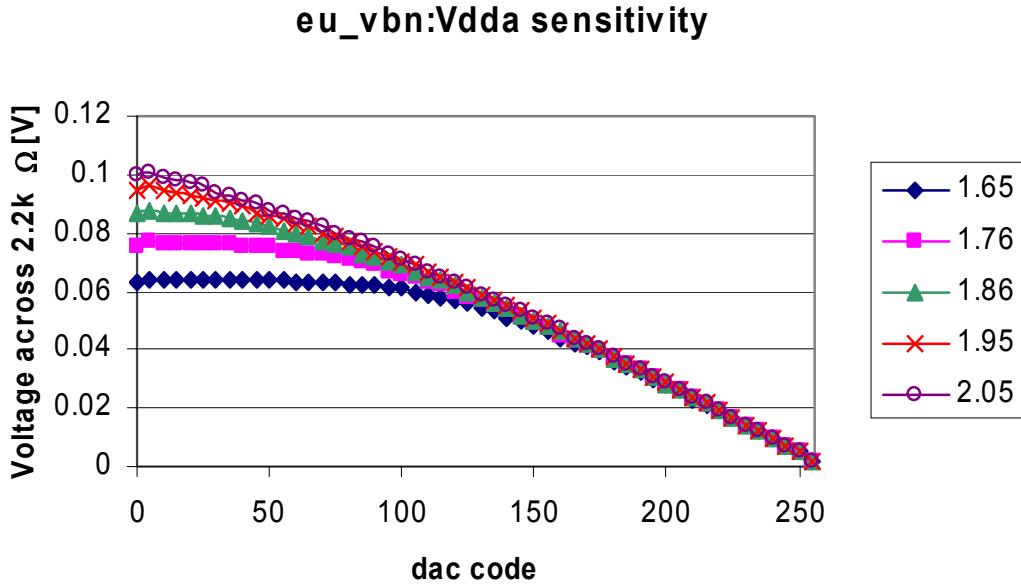

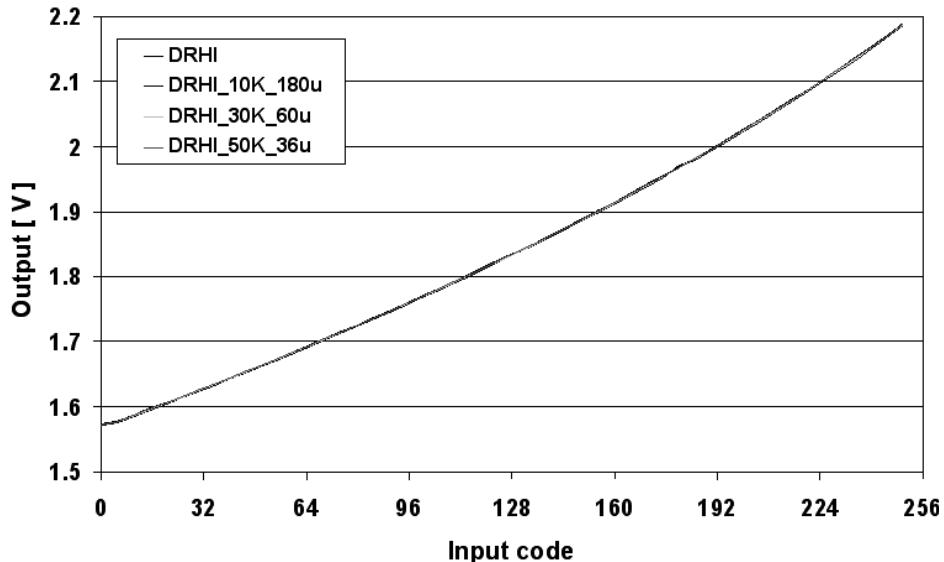

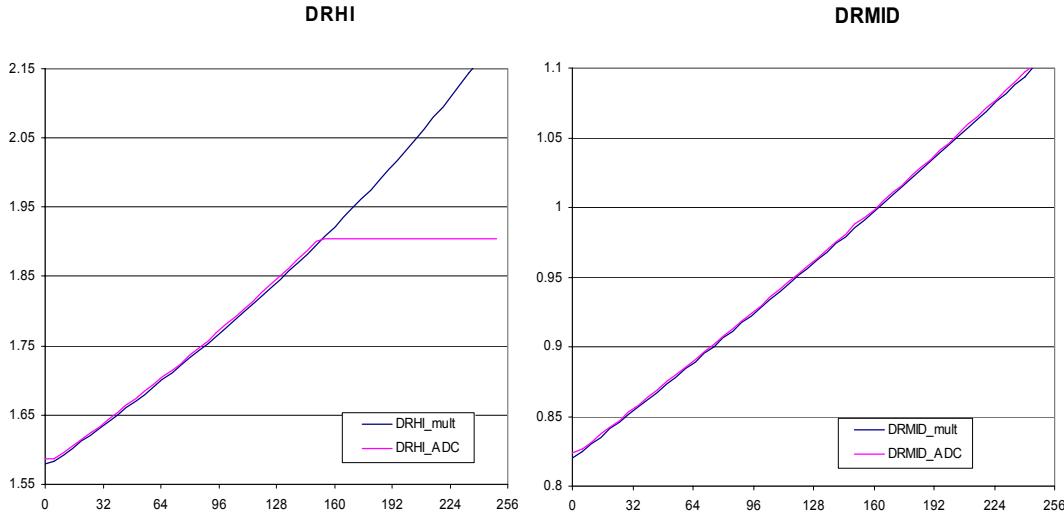

| 9.2.2                                                                                                | The DACs .....                                                            | 273        |

| 9.2.3                                                                                                | The ADC .....                                                             | 276        |

| 9.2.4                                                                                                | The current sensing stage .....                                           | 277        |

| 9.2.5                                                                                                | The current sources for temperature measurement .....                     | 279        |

| <b>9.3</b>                                                                                           | <b>Summary .....</b>                                                      | <b>279</b> |

| <b>CONCLUSIONS .....</b>                                                                             |                                                                           | <b>281</b> |

|                                                                     |              |

|---------------------------------------------------------------------|--------------|

| <b>MY CONTRIBUTION .....</b>                                        | <b>286</b>   |

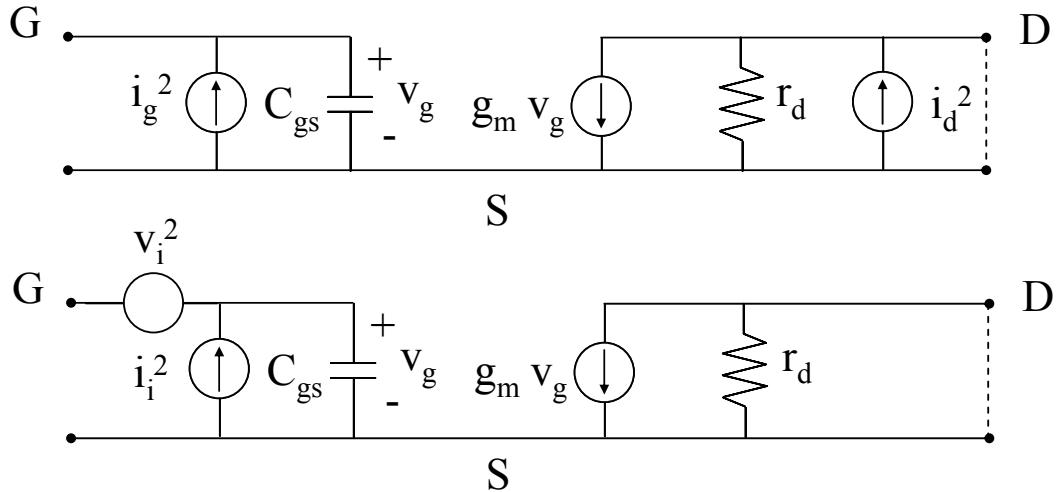

| <b>APPENDIX I NOISE MODELLING IN MOS TRANSISTORS .....</b> <b>I</b> |              |

| <b>I.1 Thermal noise .....</b>                                      | <b>I</b>     |

| I.1.1    Channel thermal noise .....                                | II           |

| I.1.2    Bulk resistance thermal noise .....                        | III          |

| I.1.3    Gate resistance thermal noise.....                         | III          |

| <b>I.2 Flicker noise.....</b>                                       | <b>IV</b>    |

| <b>I.3 Shot noise .....</b>                                         | <b>IV</b>    |

| I.3.1    Gate shot noise .....                                      | IV           |

| I.3.2    Bulk shot noise .....                                      | V            |

| I.3.3    External shot noise sources .....                          | V            |

| <b>I.4 Total input referred noise .....</b>                         | <b>V</b>     |

| <b>APPENDIX II MOST COMMON ABBREVIATIONS AND ACRONYMS.....VII</b>   |              |

| <b>BIBLIOGRAPHY .....</b>                                           | <b>IX</b>    |

| <b>ACKNOWLEDGEMENTS .....</b>                                       | <b>XXIII</b> |

---

## Résumé

---

Le travail présenté dans cette thèse a été effectué au sein du groupe Microélectronique du CERN, le laboratoire européen pour la physique des particules. Il s'agit d'un laboratoire situé près de Genève en Suisse, il a été créé dans les années 50 pour donner aux scientifiques européens les moyens d'étudier la physique des hautes énergies (HEP, High Energy Physics). Grâce aux accélérateurs de particules conçus et réalisés au CERN (en particulier le LEP, Large Electron Positron) il a été possible de développer le « Modèle Standard », une théorie qui essaye d'expliquer la matière en termes de forces et de particules. Ce modèle a été testé avec succès par les expériences de physique des particules, cependant il est incomplet, car il ne prend pas en compte la masse des particules fondamentales. L'idée la plus simple pour inclure cette dernière s'appelle le mécanisme de Higgs. Ce mécanisme implique l'existence de une particule additionnelle, appelée le boson de Higgs, et un type additionnel de force, se manifestant par des échanges de ce boson.

Pour évaluer cette hypothèse, ainsi que plusieurs autres phénomènes et théories, un nouvel accélérateur de particules est actuellement en construction au CERN, il s'agit du Large Hadron Collider (LHC). Le LHC sera l'accélérateur le plus puissant jamais construit.

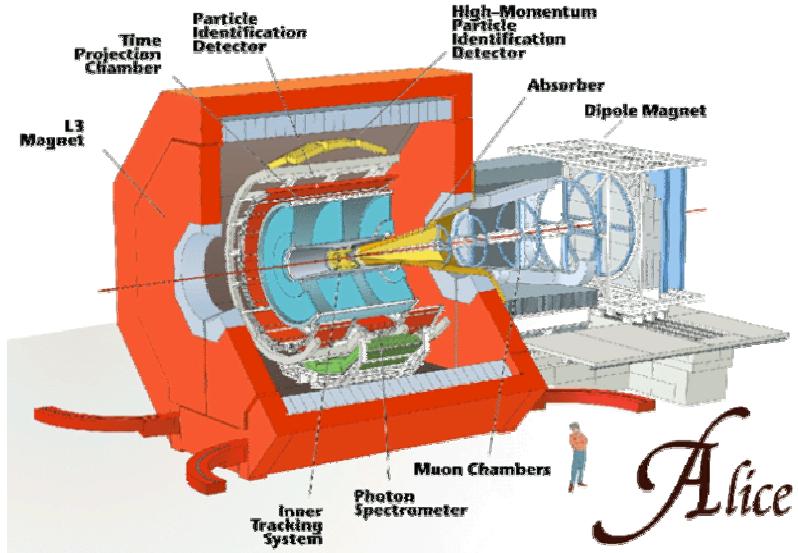

Le détecteur à pixels décrit dans cette thèse a été conçu pour l'expérience de physique ALICE du futur collisionneur LHC. Les scientifiques pensent qu'il y a eu un «Big Bang» initial duquel tout l'Univers connu a émergé. Quinze milliards d'années après, l'Univers est si grand que la lumière prendrait des milliards d'années à le traverser. Pourtant, au début, tout était contenu dans un volume comparable à celui d'une mouche. Toutes les particules qui forment la matière que nous connaissons aujourd'hui se sont alors formées. Les quarks et les gluons, qui sont les constituants des protons et des neutrons dans notre Univers refroidi, étaient alors trop chauds pour s'associer. Cet état de la matière initiale s'appelle un plasma quark-gluon (QGP). Découvrir et analyser le QGP est l'objectif principal d'ALICE. En effet, ALICE est un détecteur de collisions d'ions lourds conçu pour étudier la physique de la matière en interaction forte et le plasma quark-gluon dans les collisions de noyaux produits par le LHC.

Dans les expériences autour du LHC (ALICE, LHCb, ATLAS, CMS, TOTEM) les particules seront accélérées pour atteindre des énergies de l'ordre du Tera Electron Volt (TeV) et des luminosités très élevées ( $10^{34} \text{ cm}^{-2}\text{s}^{-1}$  pour les protons et  $1.95 \cdot 10^{27} \text{ cm}^{-2}\text{s}^{-1}$  pour des ions de plomb). Cela implique des niveaux de rayonnement qui peuvent être très élevés,

particulièrement pour les détecteurs situés très près du point d'interaction. Pour l'expérience ALICE, en dix ans de fonctionnement du LHC, la dose ionisante totale peut atteindre  $2.5 \cdot 10^3$  Gy et la fluence équivalente neutrons 1 MeV peut atteindre  $2.95 \cdot 10^{12}$  MeV n<sub>eq</sub>/cm<sup>2</sup>. Des niveaux de rayonnement beaucoup plus élevés peuvent être atteints dans les autres expériences.

Ceci pose un problème majeur pour la réalisation de l'électronique située près du point d'interaction, qui est habituellement celle des détecteurs de trajectoires. Cet environnement extrême, et la spécificité de l'électronique des détecteurs de trajectoires, font qu'aucun composant commercial n'est disponible. Le choix du développement d'ASICs dédiés s'est donc imposé. Une possibilité aurait consisté à résoudre le problème de la tolérance au rayonnement par durcissement du procédé technologique. En particulier quelques fondeurs spécialisés fournissent un procédé durci qualifié sous rayonnement. Ces technologies dont la pérennité ne peut être assurée sont toujours très coûteuses et souffrent de plus de divers handicaps liés à la difficulté de production des circuit : performances réduites, stabilité du procédé, l'obtention de rendements acceptables.

Le CERN a donc choisi de soutenir un projet de recherche (RD49) pour évaluer l'intérêt d'utiliser une technologie CMOS standard durcie aux effets des rayonnements par design (Hardening By Design, HBD). L'avantage de cette approche réside, en plus de son coût réduit, dans sa facilité d'adaptation aux nouvelles technologies submicroniques à venir. Le projet de construction du LHC s'échelonne sur une dizaine d'années, dans le même temps les technologies MOS évoluent très rapidement, les premiers essais de durcissement ont été effectués sur des technologies 0.5 µm. Celles-ci seront complètement obsolètes, tout comme les technologies durcies encore disponibles dans le commerce lorsque les approvisionnements de l'électronique pour les expériences du LHC seront réalisés. Jusqu'à ce jour, l'intégration qui accompagne l'évolution des composants s'accompagne d'une amélioration des caractéristiques des composants. D'ailleurs, plusieurs des circuits présentés dans cette thèse, ont été conçus en technologie CMOS standard 0.25 µm, durcis avec des techniques de HBD, ils répondent au cahier des charges pour l'électronique du détecteur à pixel en silicium de l'expérience ALICE (Silicon Pixel Detector, SPD), qui est le plus proche de l'aire de collision des particules.

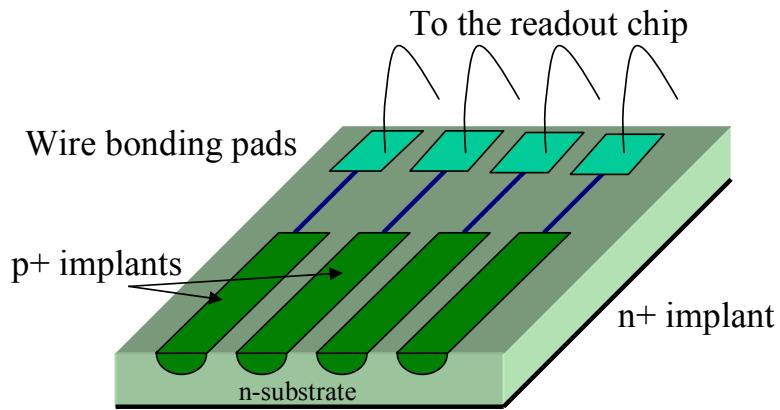

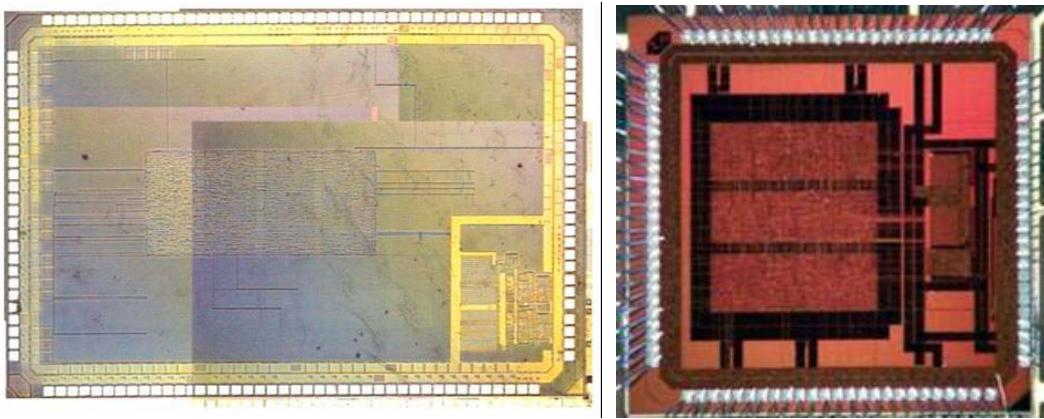

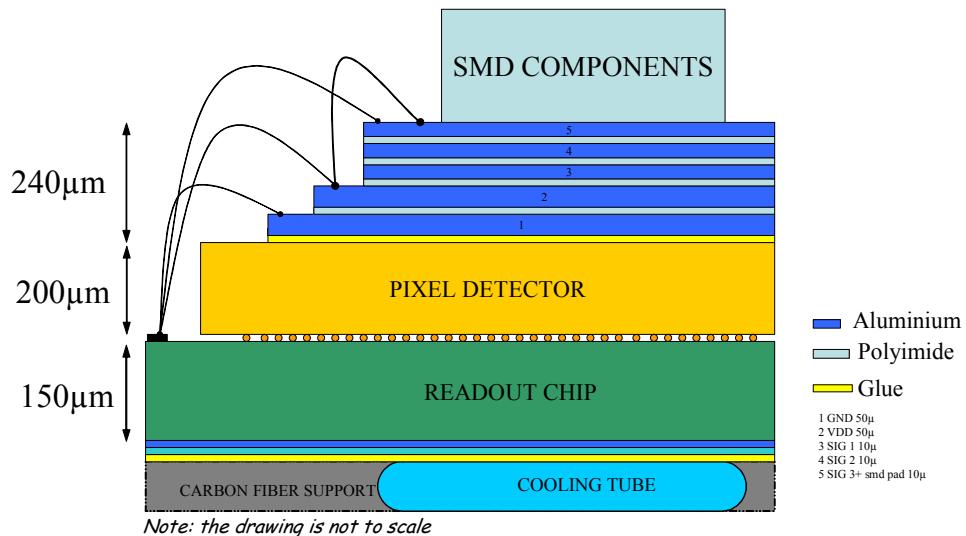

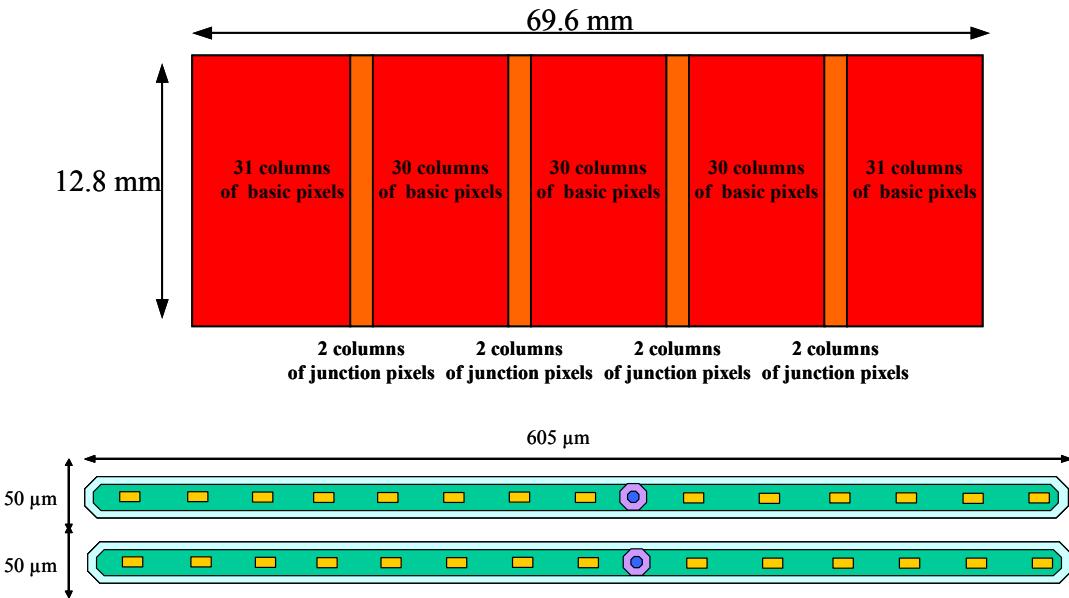

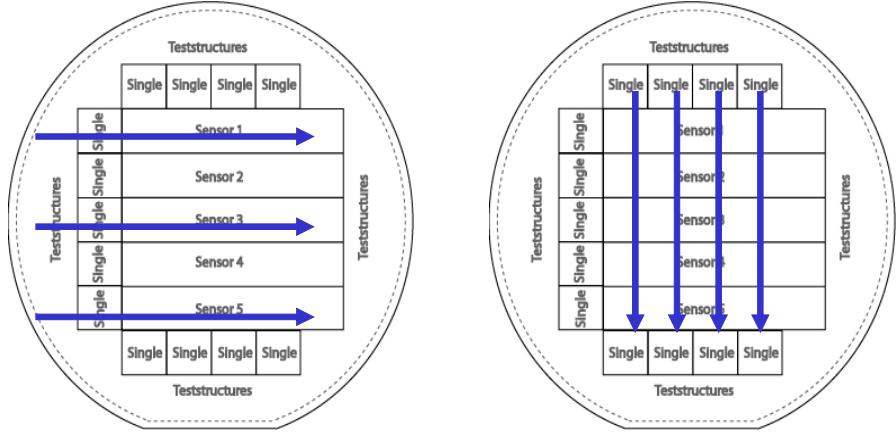

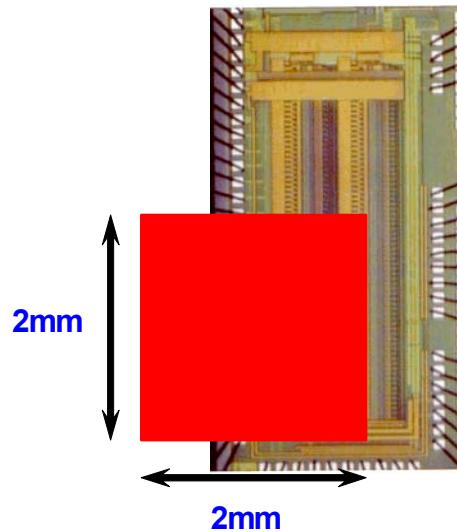

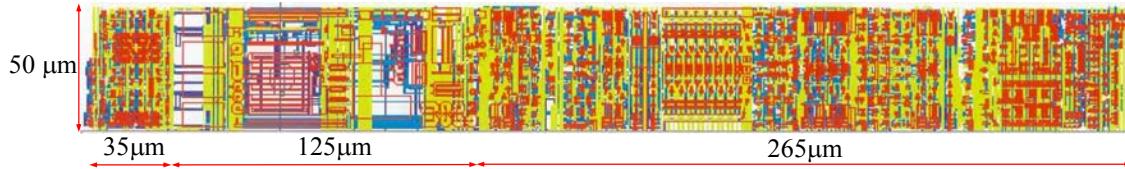

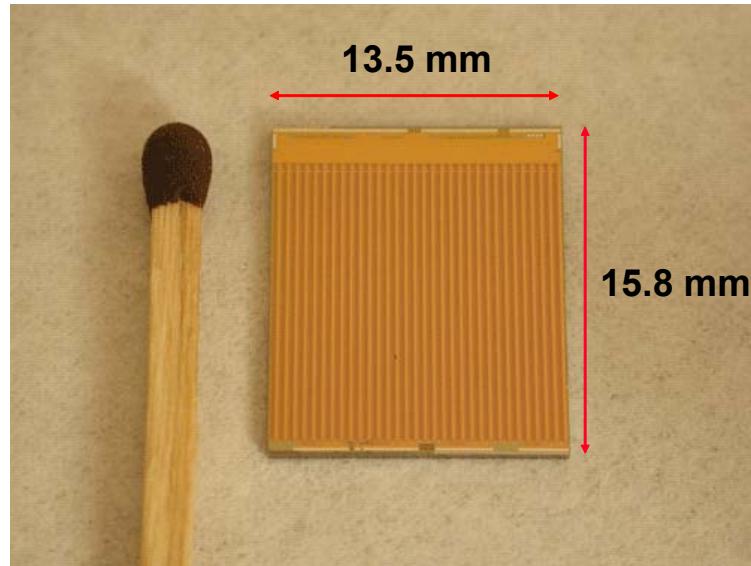

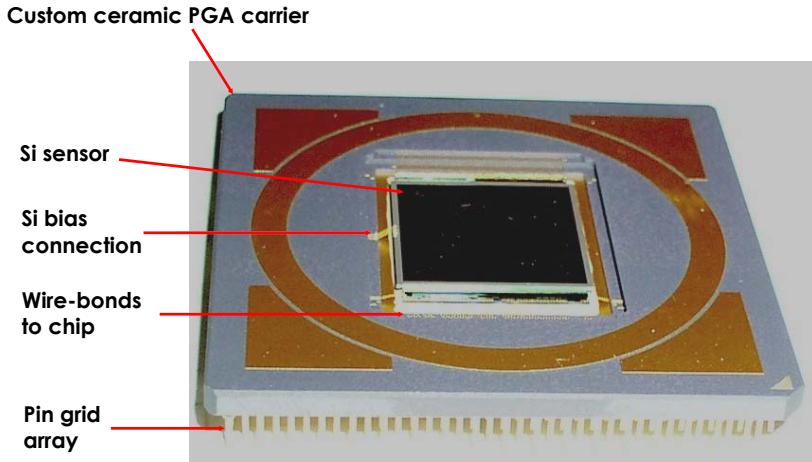

En particulier, le circuit ALICE1LHCb (ou Circuit Pixel) contient une matrice de 32 par 256 cellules de lecture (pour un total de 13 millions de transistors), mesurant 13.5 par 15.8 mm<sup>2</sup>. Des groupes de cinq circuits sont reliés électriquement par une technique de contact entre circuits sur des puces différentes, réalisés au moyen de rangées de billes métalliques microscopiques («bump-bonding»). On obtient ainsi un grand senseur (160 colonnes par 256 lignes) qui forme le bloc de base qui constitue le SPD de l'expérience ALICE, dénommé «ladder». Un circuit est connecté à un senseur (de même dimensions, 32 colonnes par 256 lignes) pour former un «single», l'élément de base de détection pour le détecteur hybride à

photons (Hybrid Photon Detector, HPD) de l'expérience LHCb. Le circuit est également employé pour le détecteur de trajectoires de l'expérience NA60.

Il utilise un schéma d'entrée différent des schémes classiques, qui utilisent l'intégration de charges, la compensation pole-zéro et la mise en forme semi-gaussienne. Le circuit d'entrée réalise une configuration avec trois pôles (deux pôles complexes et un pôle réel, tous avec la même composante réelle), qui a été conçue pour supporter un fort taux d'occupation. Des tests minutieux de la puce, au laboratoire et sous irradiation dans un faisceau de particules, ont montré que ce circuit est entièrement fonctionnel et ce pour des doses allant jusqu'à 300 kGy.

Le **premier chapitre** présente au lecteur les objectifs du CERN, et en particulier l'expérience ALICE (les autres expériences sont décrites dans l'Annexe I). Nous proposons d'abord une courte description du Modèle Standard. Cette théorie inclut l'interaction forte associée à la charge de couleur des quarks et des gluons et à une théorie combinée de l'interaction faible et électromagnétique, plus connue sous le nom de théorie électrofaible, qui introduit les bosons W et Z comme particules porteuses de l'interaction faible, et les photons comme médiateurs des interactions électromagnétiques. Les valeurs très élevées, à des niveaux jamais atteints, de l'énergie et de la luminosité du faisceau du LHC permettent de mieux appréhender les défis technologiques principaux. Certains sont récapitulés dans ce chapitre.

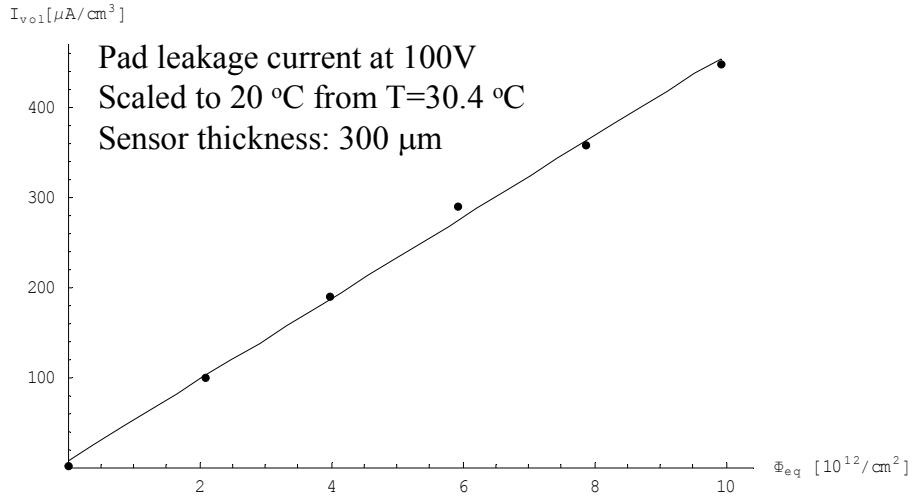

Le **deuxième chapitre** commence par une vue d'ensemble des détecteurs de particules à semi-conducteur les plus importants utilisés pour la physique des hautes énergies avec une description de leurs propriétés, en particulier pour ce qui concerne les détecteurs hybrides à pixels. Ceci permet de mieux comprendre les multiples utilisations dans les expériences au CERN des divers types de détecteurs, et en particulier dans le détecteur de trajectoires ITS (Inner Tracking System) de l'expérience ALICE. Une section de ce chapitre est consacrée aux dommages induits par le rayonnement dans les détecteurs de particules à semi-conducteur. Les dommages les plus communs sont discutés, et les définitions des quantités physiques les plus importantes liées à ces phénomènes sont données (fluence de particules  $\Phi$ , taux d'augmentation du courant de fuite  $\alpha$ , facteur de durcissement  $K$ ). Ces quantités seront employées pour la description des résultats de l'irradiation des détecteurs de particules d'ALICE.

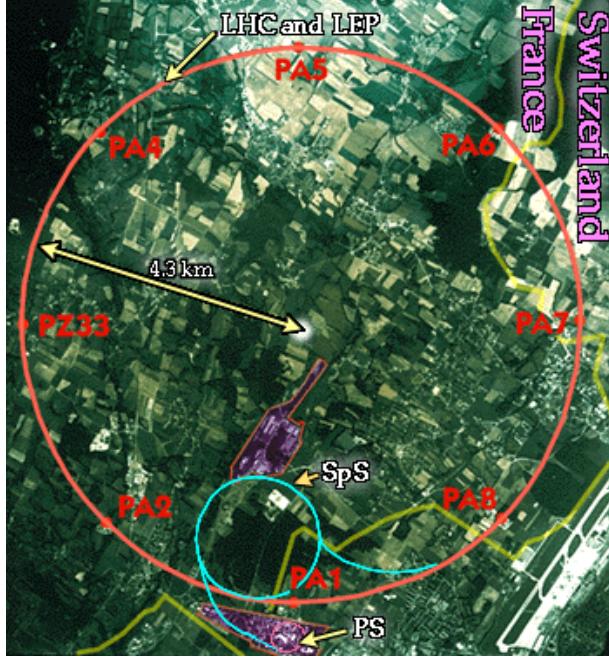

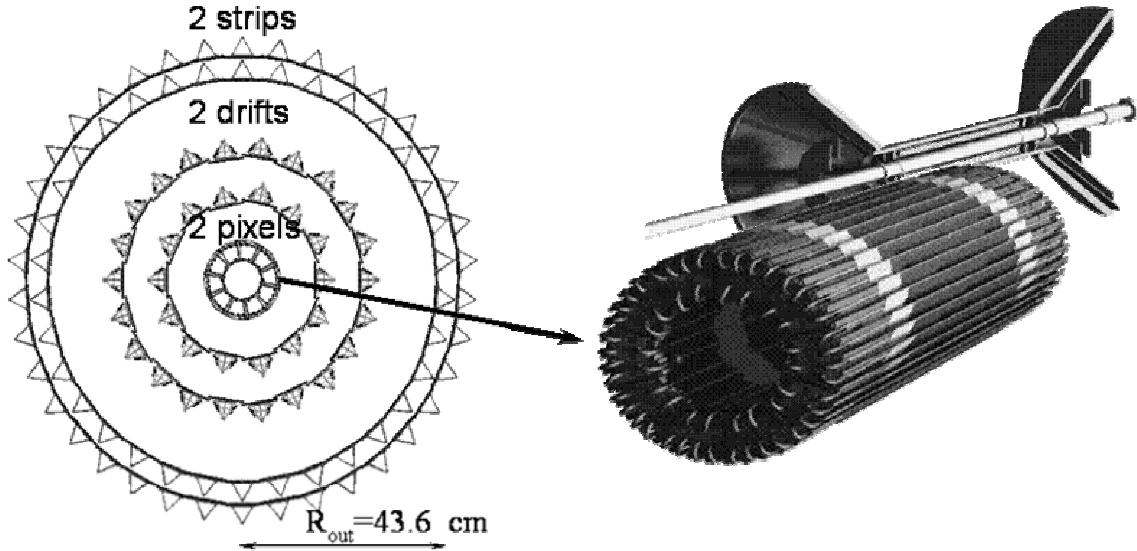

Le **troisième chapitre** commence par une vue d'ensemble du détecteur de trajectoires ITS d'ALICE, et puis se concentre sur ses deux couches les plus internes, à proximité du faisceau, qui forment le détecteur SPD (Silicon Pixel Detector) d'ALICE. La recherche des trajectoires dans les collisions d'ions lourds au LHC constitue un grand défi, en raison de leur densité extrêmement élevée. L'ITS d'ALICE se compose de six couches de détecteurs cylindriques coaxiaux optimisés pour l'efficacité de détection de trajectoires et la

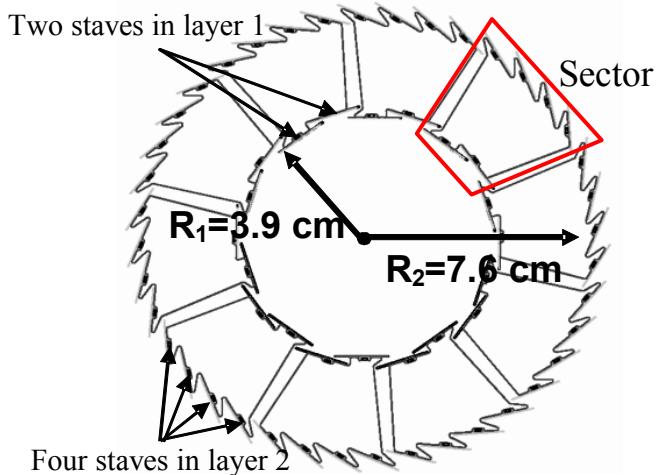

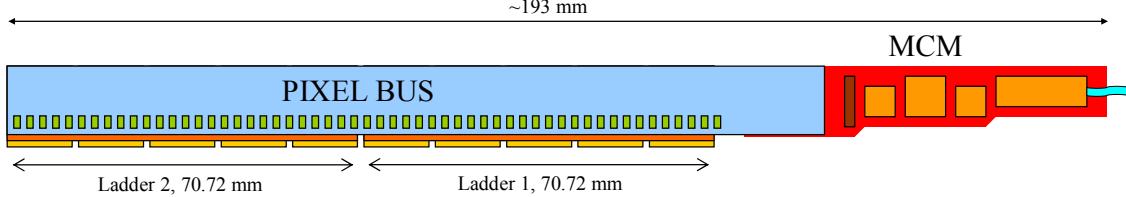

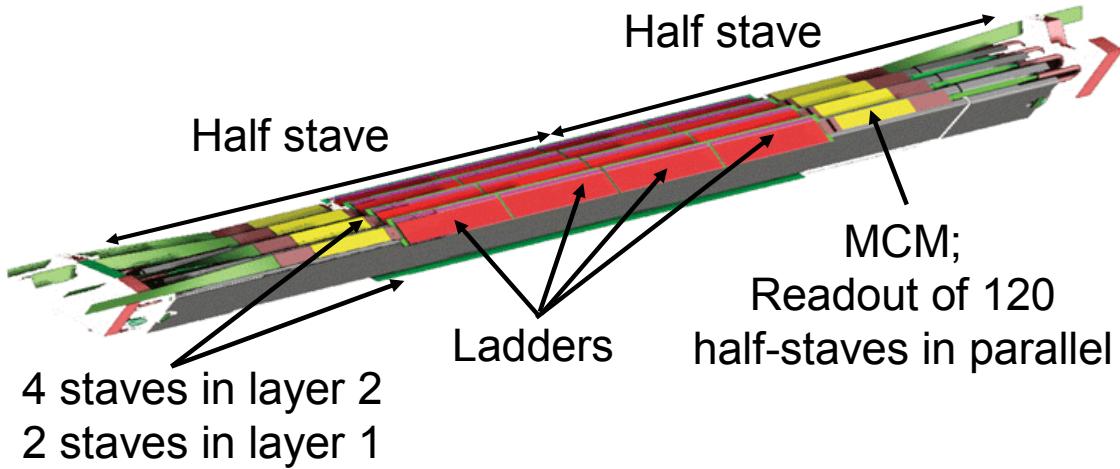

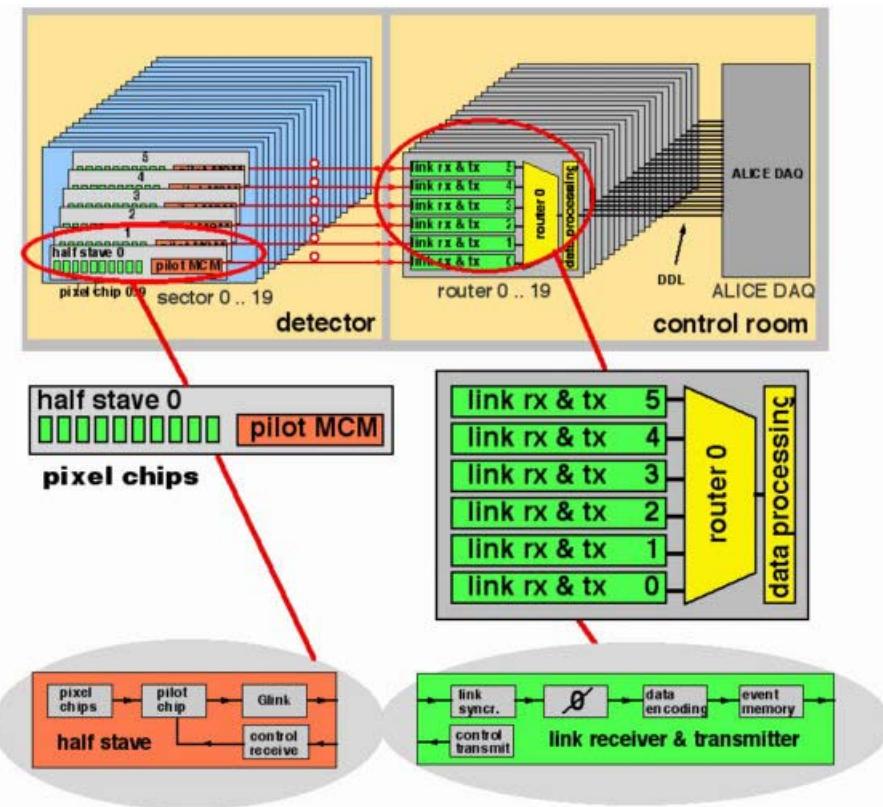

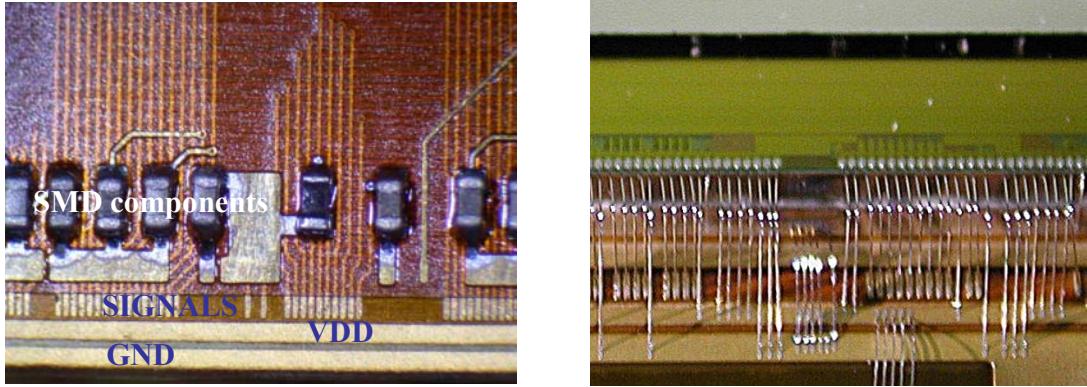

caractérisation des paramètres d'impact. Les deux couches externes sont équipées des détecteurs SDD (Silicon Drift Detectors), les deux couches intermédiaires avec des détecteurs SSD (Silicon Strip Detectors), et les deux couches les plus internes avec des détecteurs SPD. Ces SPD [ALI99] sont répartis sur deux couches cylindriques coaxiales, de rayons respectifs 3.9 et 7.6 centimètres. Le bloc fonctionnel de base du détecteur SPD d'ALICE est le ladder. Deux ladders sont connectées ensemble, puis sont reliées à un Multi Chip Module (MCM) à l'aide d'un bus spécial Kapton-Aluminium pour former une demi-barrette («half stave»). Le bus qui relie le module MCM à l'électronique des capteurs se compose de lignes de données, de contrôle et de puissance.

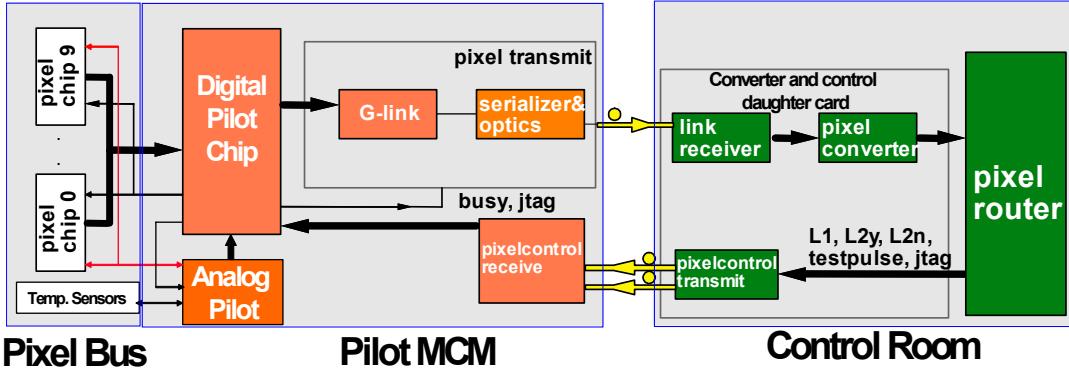

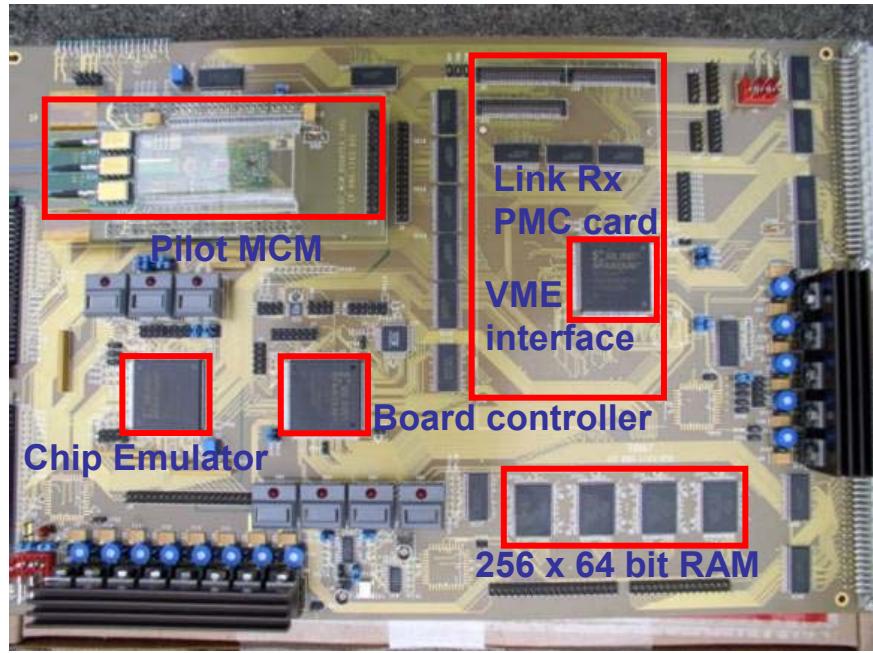

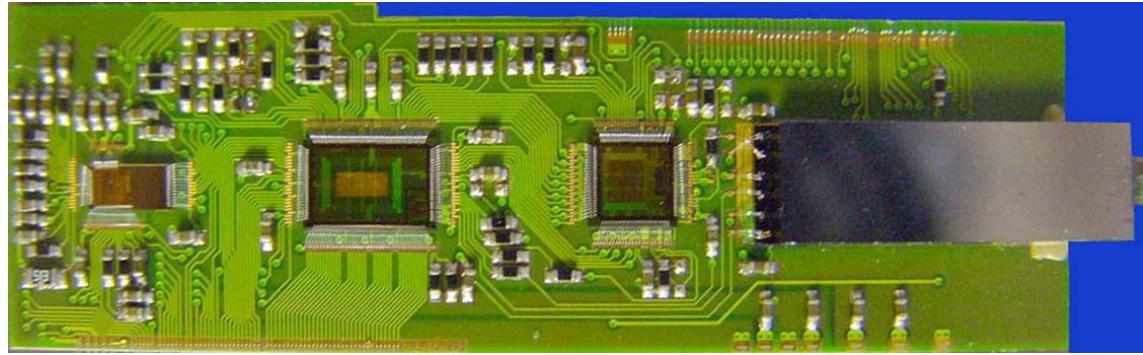

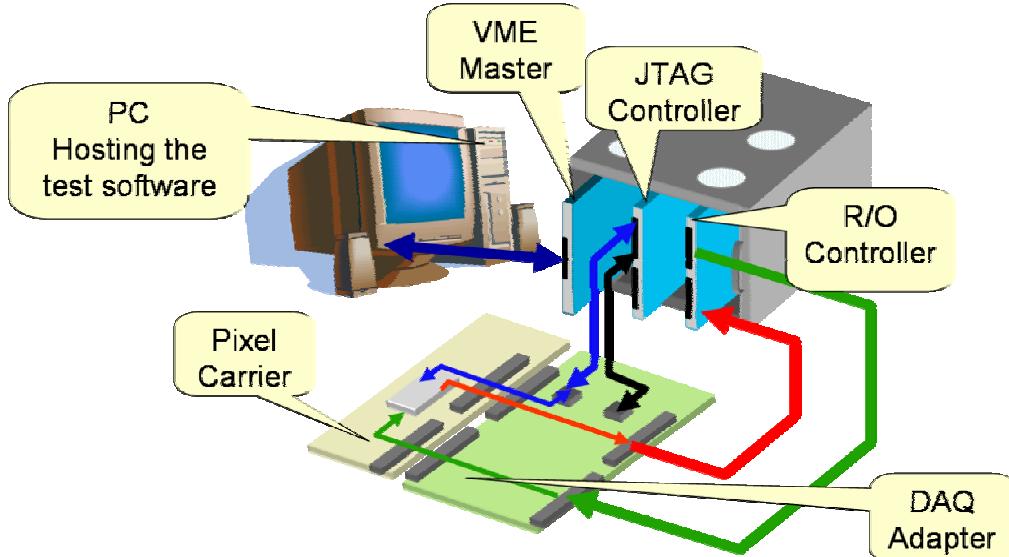

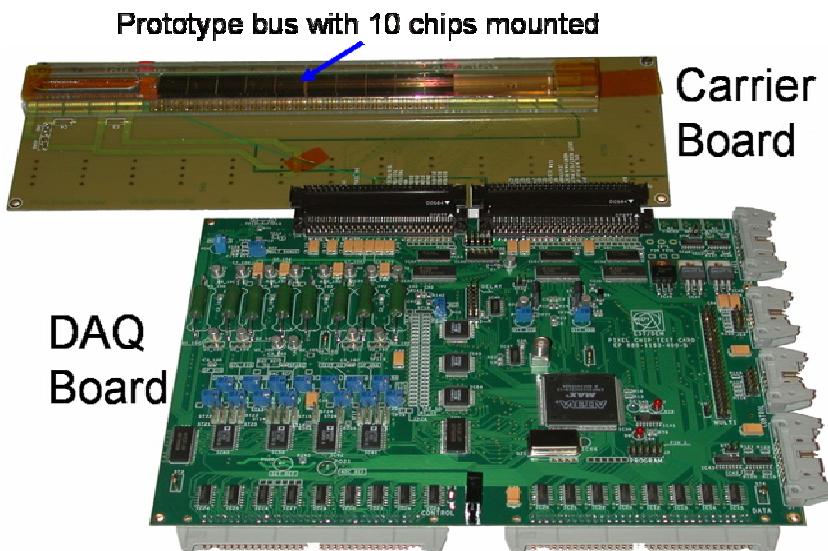

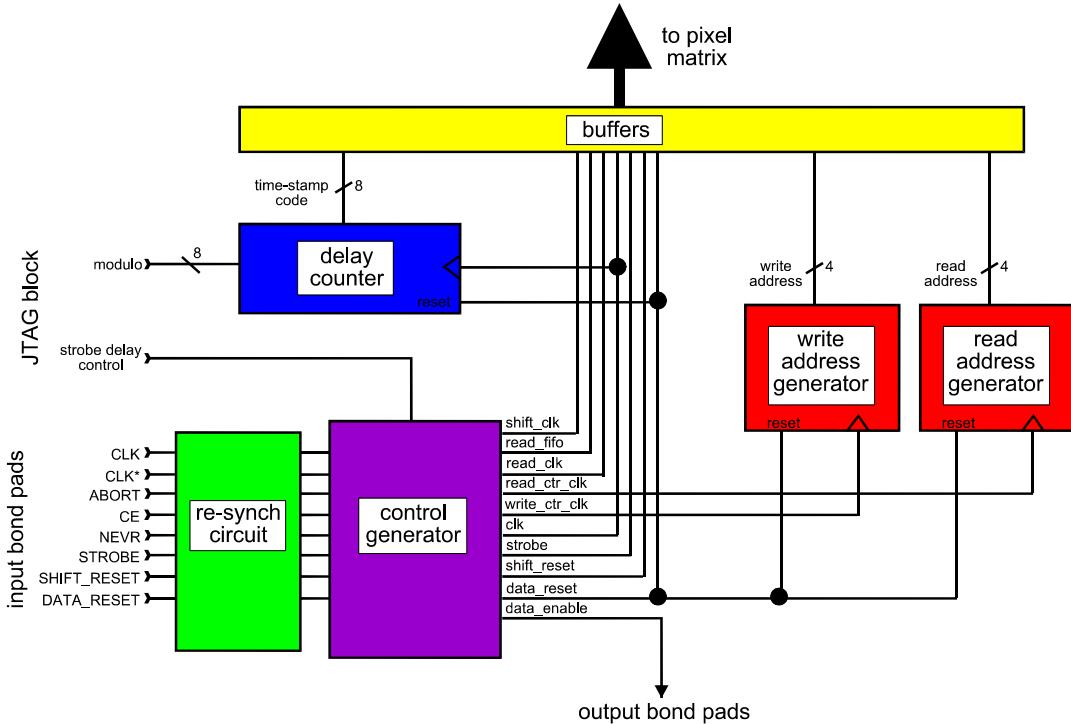

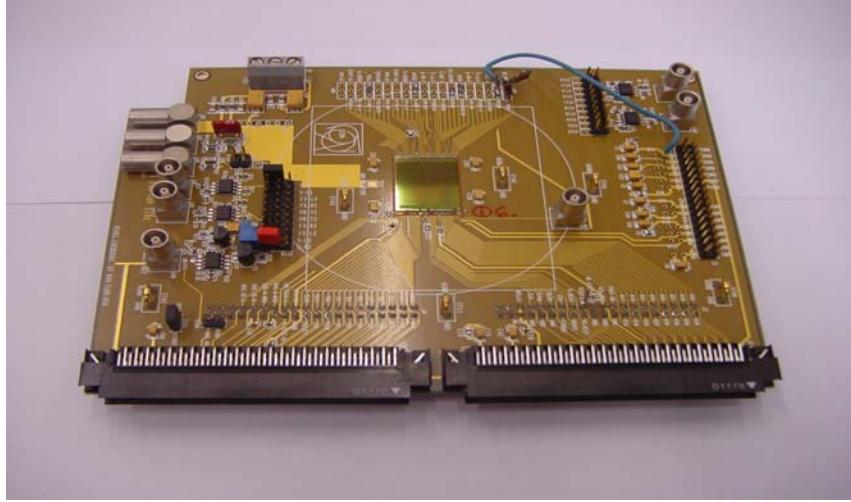

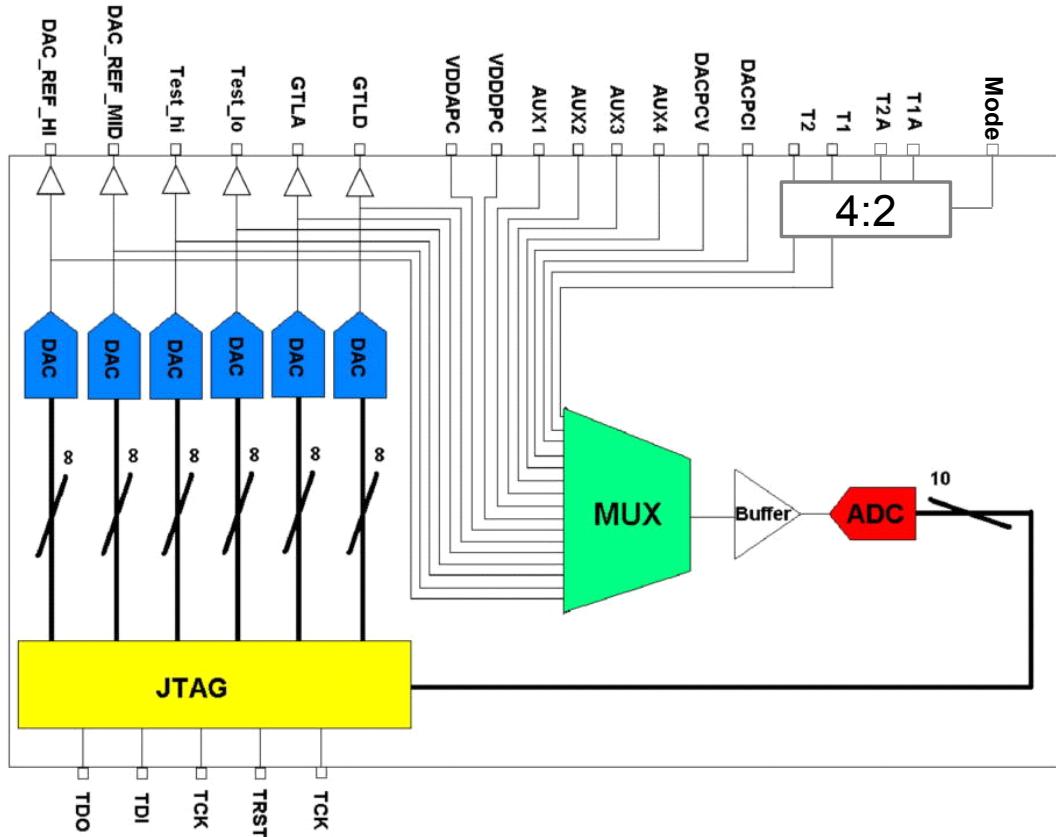

Les 10 Circuits Pixel d'une demi-barrette sont commandés et lus par un MCM pilote (PILOT MCM). Le module MCM est composé de trois ASICs différents: le circuit APC (Analogue Pilot Chip) pour la polarisation du Circuit Pixel et pour le contrôle de la température et des signaux continus ou faiblement variables sur le MCM; le circuit DPC (Digital Pilot Chip) pour la lecture numérique, et le GOL (Gigabit Optical Serializer) pour la transmission optique des données. Tous les ASICs présents dans le module MCM sont décrits, tout comme la carte consacrée aux tests qui peut également émuler le comportement du logiciel et des composantes électroniques de l'ensemble du SPD.

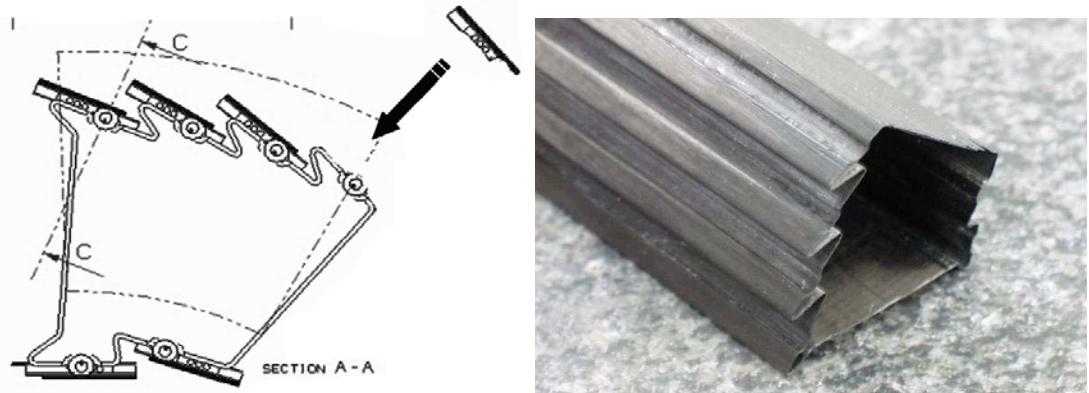

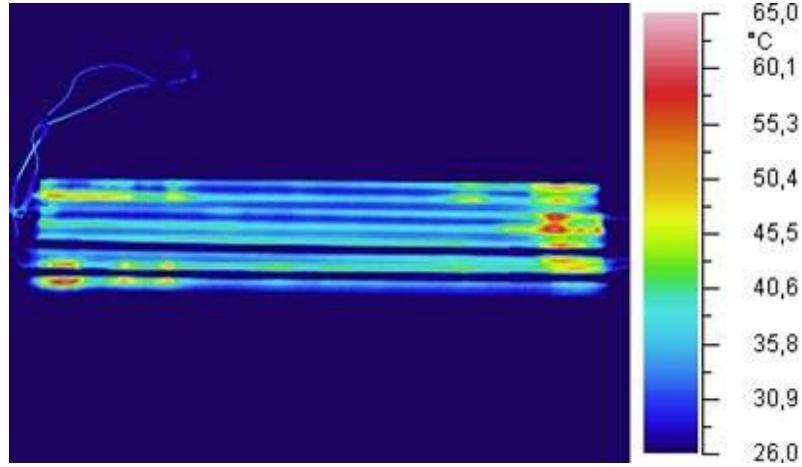

Deux demi-barrettes forment une barrette, et six barrettes montées sur un support de fibre de carbone constituent un secteur. Le détecteur SPD est formé de dix secteurs assemblés. Les détecteurs et les circuits électroniques produisent une grande quantité de chaleur qui doit être évacuée tout en gardant une bonne stabilité en température. Un soin particulier a dû être apporté à la conception du système de refroidissement et de contrôle de température. La minimisation de la consommation d'énergie par l'électronique a été l'un des éléments les plus importants du cahier des charges. Un système de test spécifique (DAQ), très flexible a été développé, il a pu être employé dans un grand nombre de scénarios de test différents.

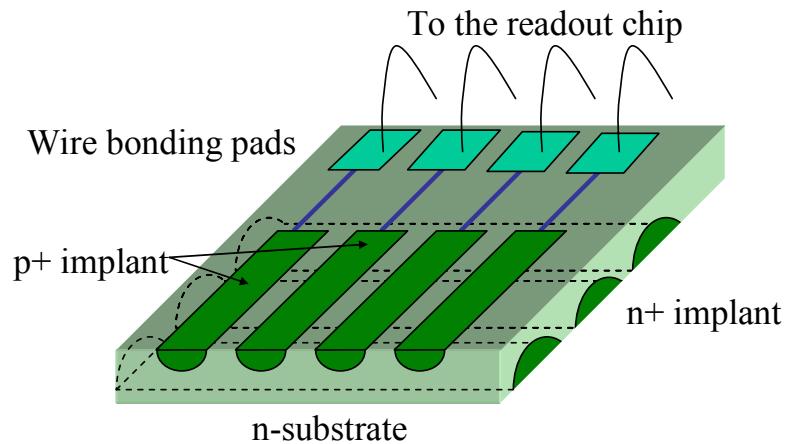

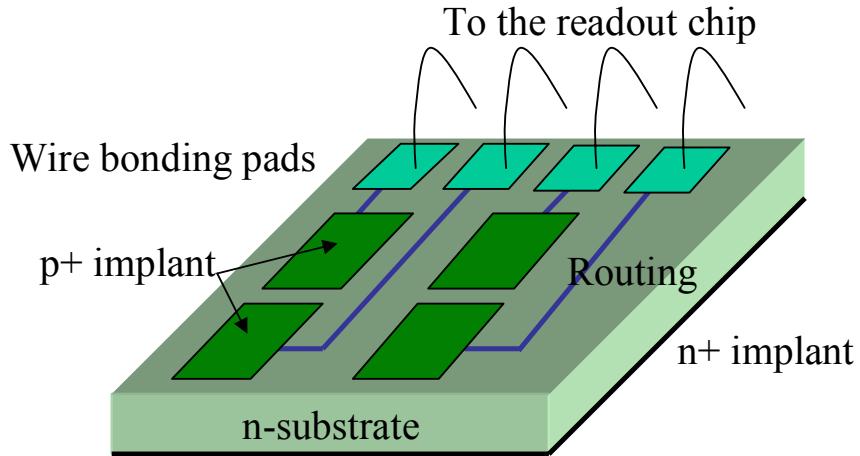

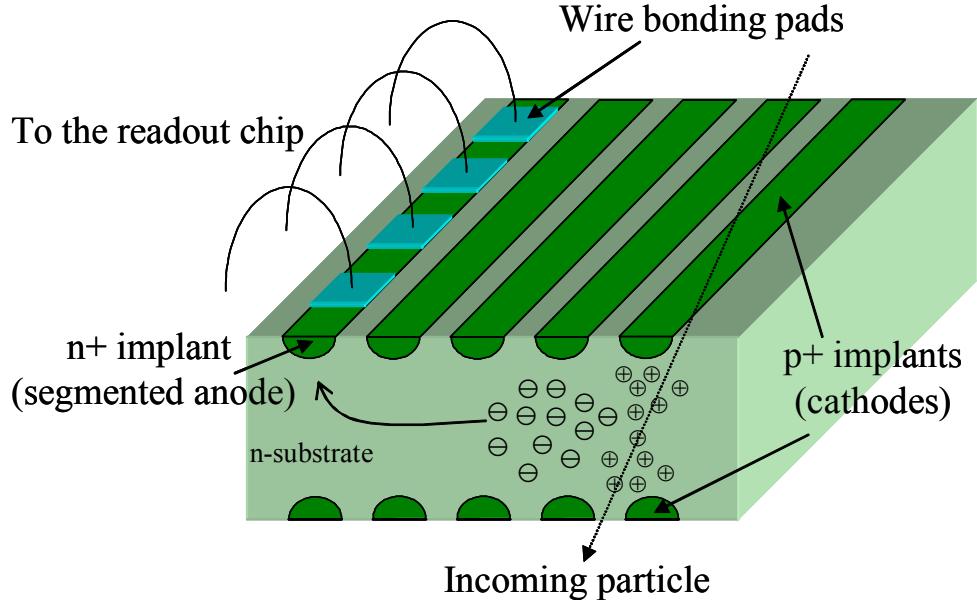

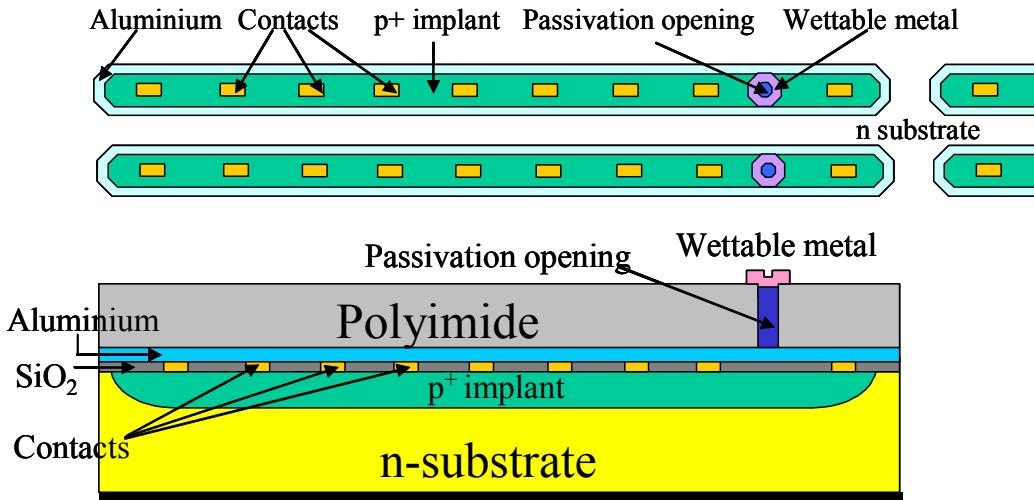

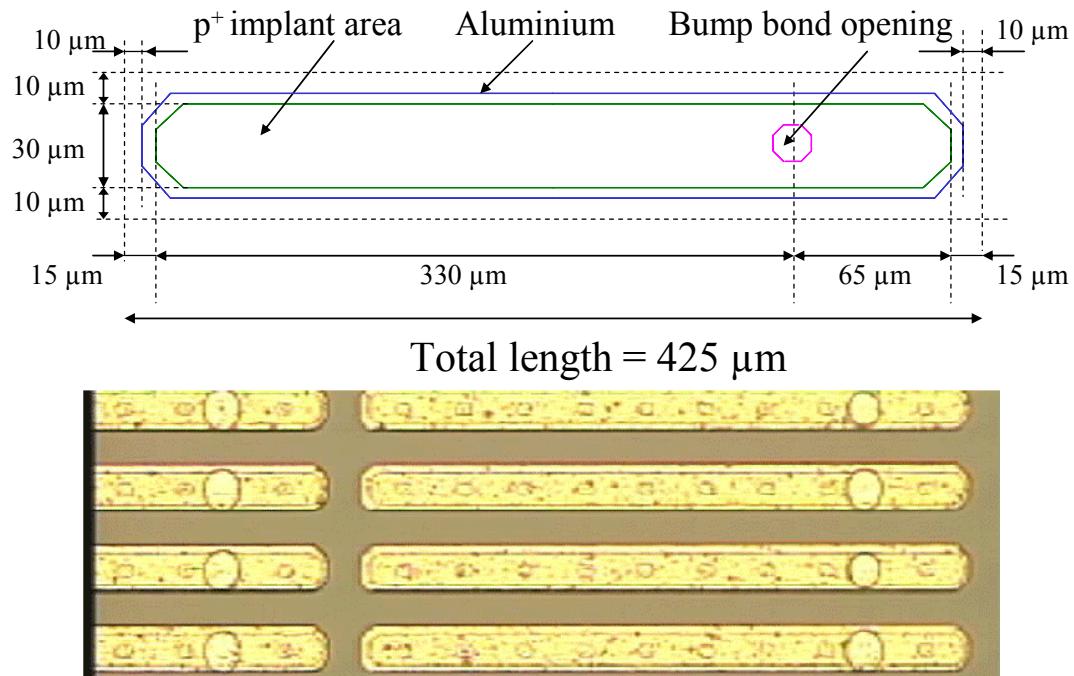

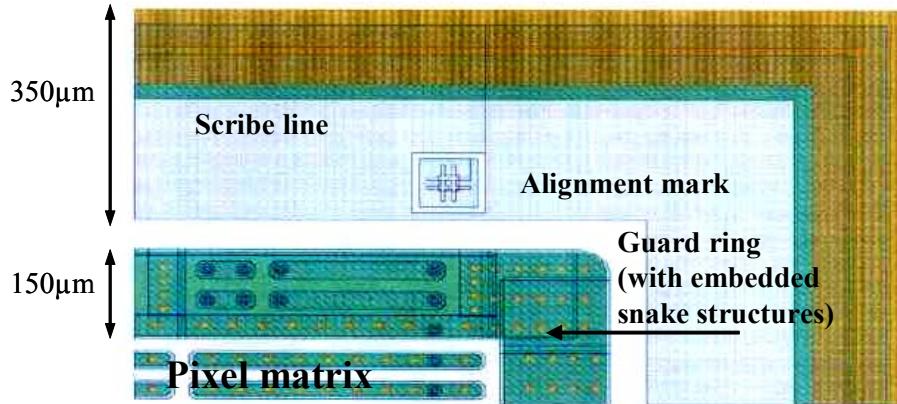

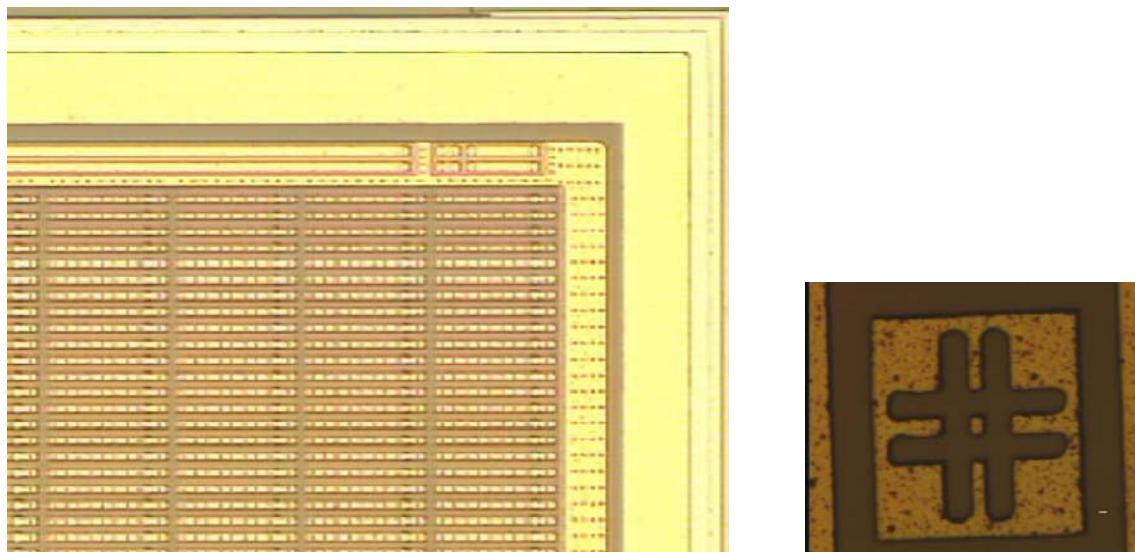

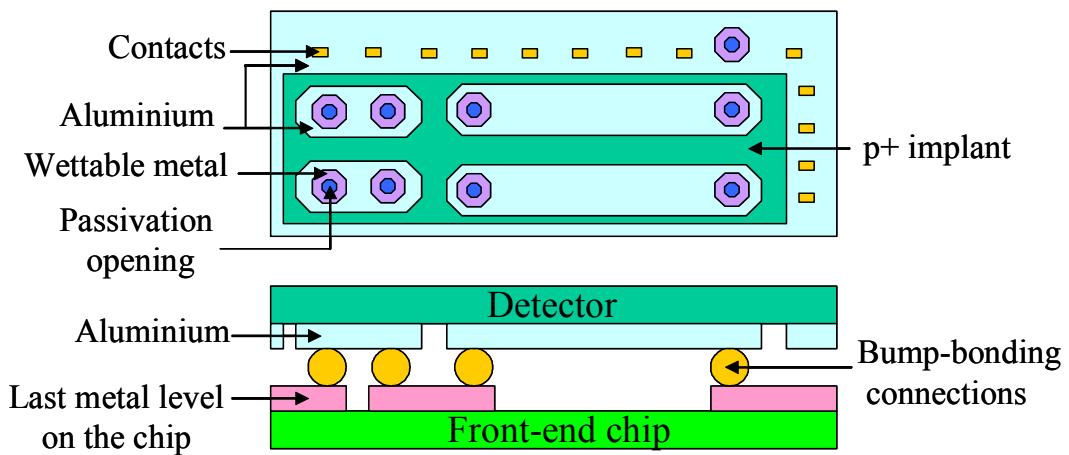

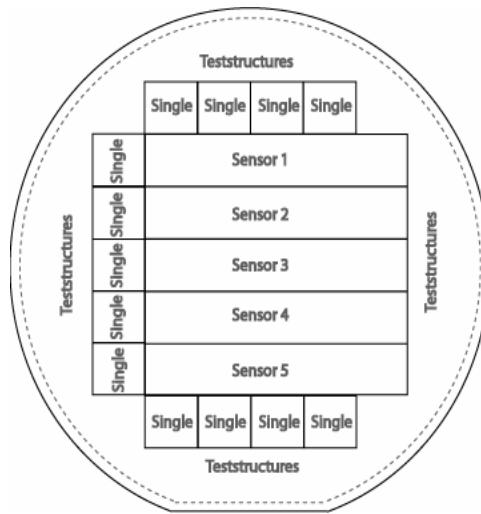

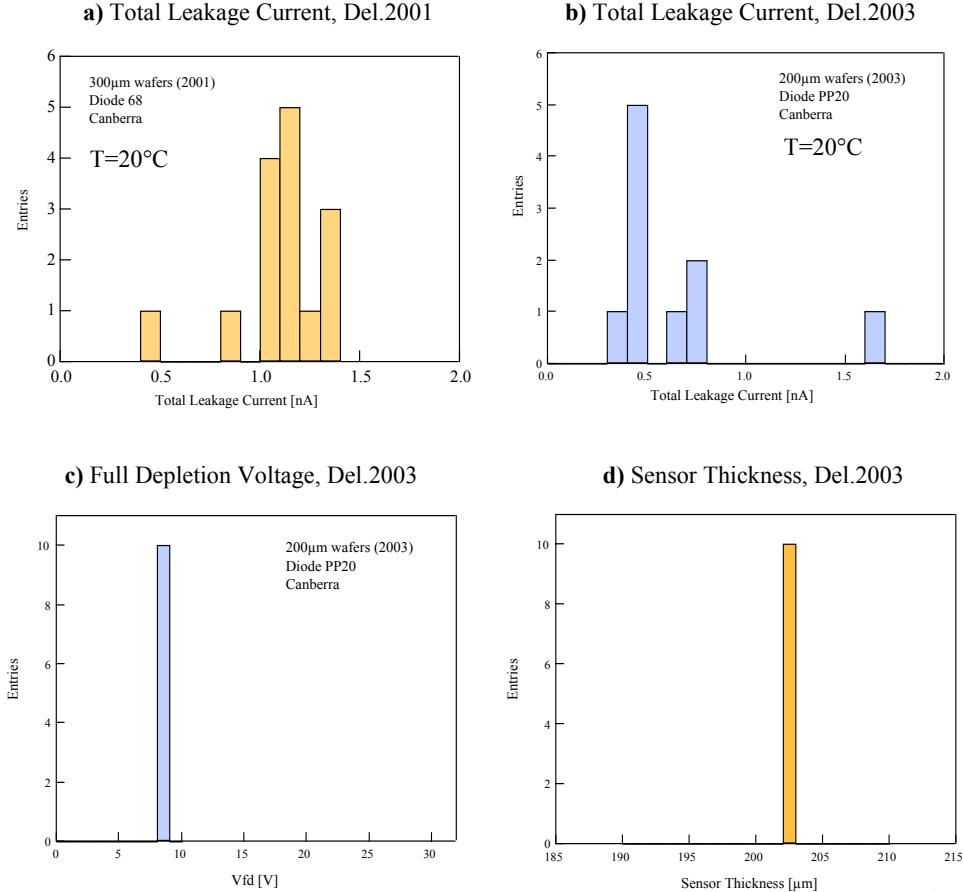

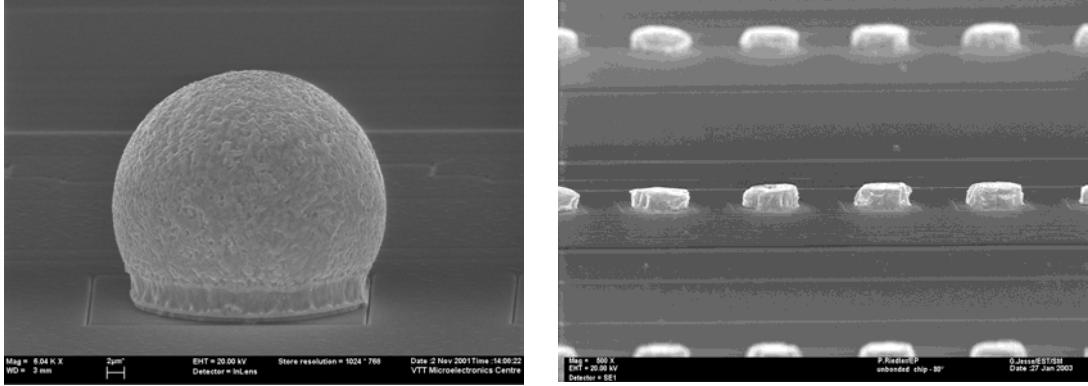

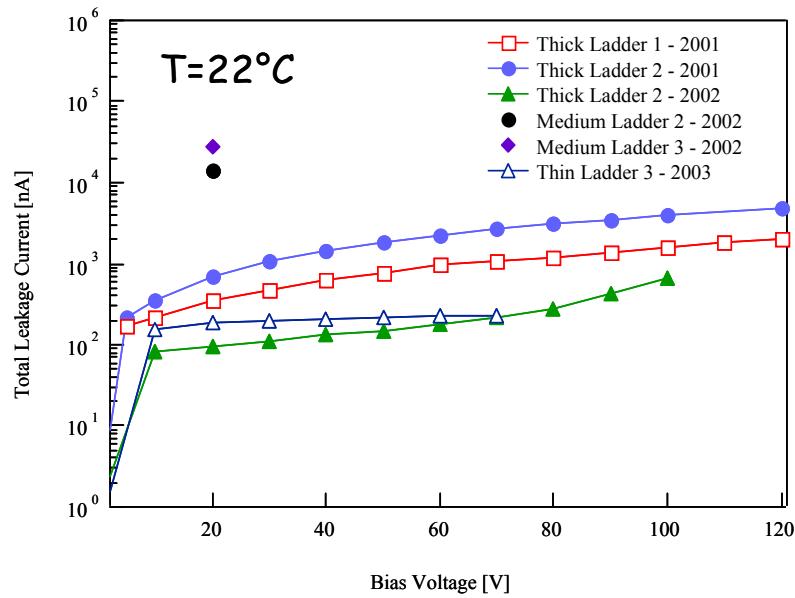

Le **quatrième chapitre** traite de la conception et des tests des détecteurs conçus pour les expériences ALICE et LHCb. Les détecteurs à pixels (senseurs) pour les expériences ALICE et LHCb sont constitués par une rangée de diodes p-in-n, réalisées par dopage au phosphore d'un substrat de type n. La valeur finale de l'épaisseur de plaquette sera de 300  $\mu\text{m}$  pour l'expérience LHCb, «détecteurs épais», et de 200  $\mu\text{m}$  pour ALICE, «détecteurs minces». Le détecteur est fabriqué par Canberra Électronique; une description des phases principales du procédé, correspondant à la conception des masques est présentée, ainsi que certaines caractéristiques particulières à la conception de détecteur (anneau de garde, ligne de découpe, structures de test «accordéon», dites aussi «snake test structures»). La deuxième partie du chapitre est consacrée aux résultats des tests du détecteur. Plusieurs tests ont été réalisés (en plus de ceux effectués par le fabricant) sur un ensemble de plaquettes de pré-série, épaisses et minces, fournies par Canberra. Des tests électriques ont été réalisés sur les diodes de 68  $\text{mm}^2$  présentes sur les plaquettes; ils portent sur la mesure de la tension correspondant à la désertion

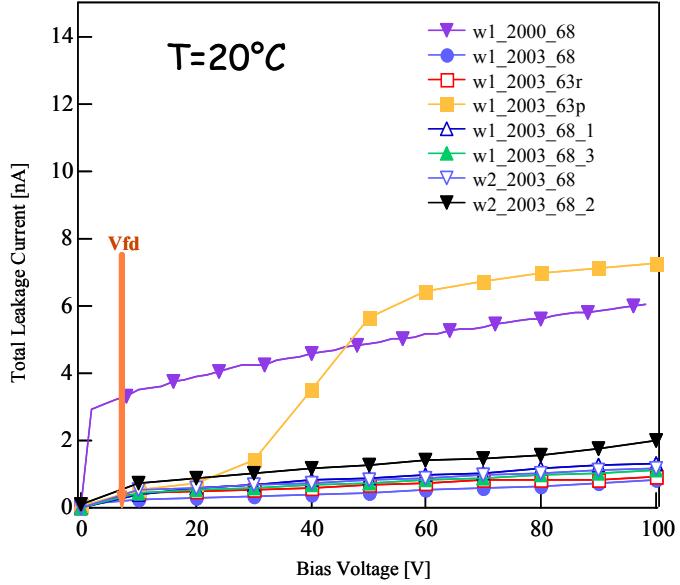

maximum ( $V_{fd}$ ) et sur la mesure du courant de fuite total. À part quelques problèmes sur les premiers lots, qui ont été résolus, toutes les caractéristiques électriques des senseurs répondent à celles données par le fabricant.

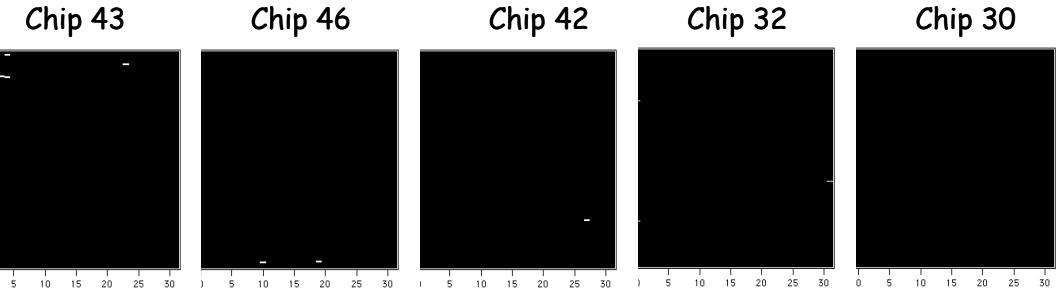

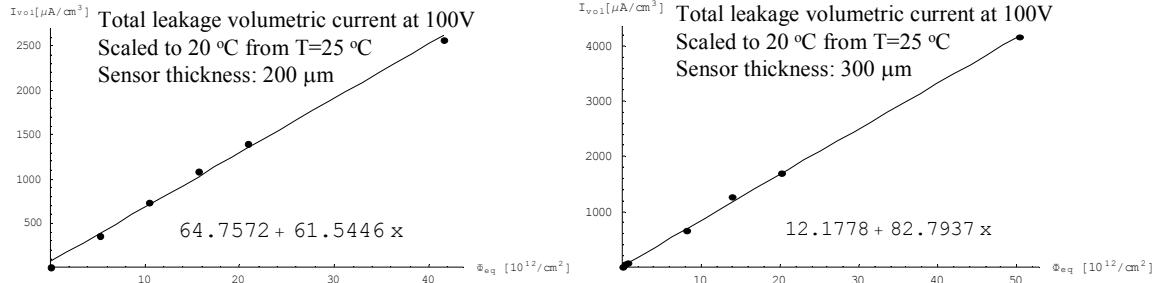

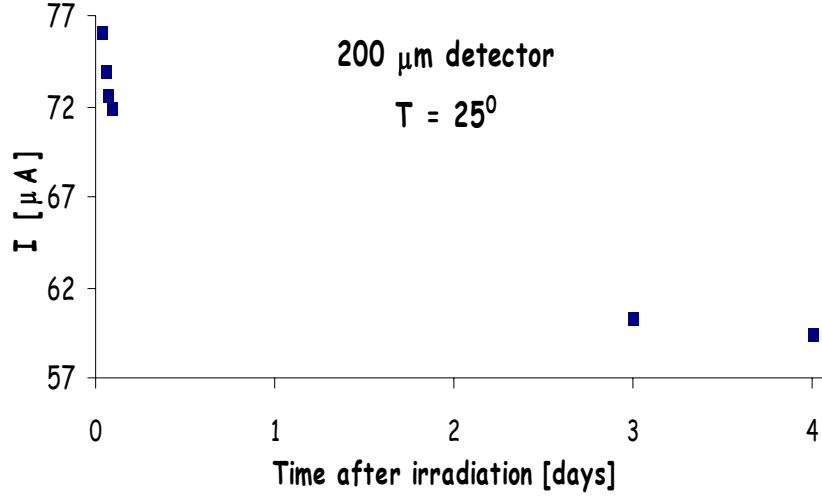

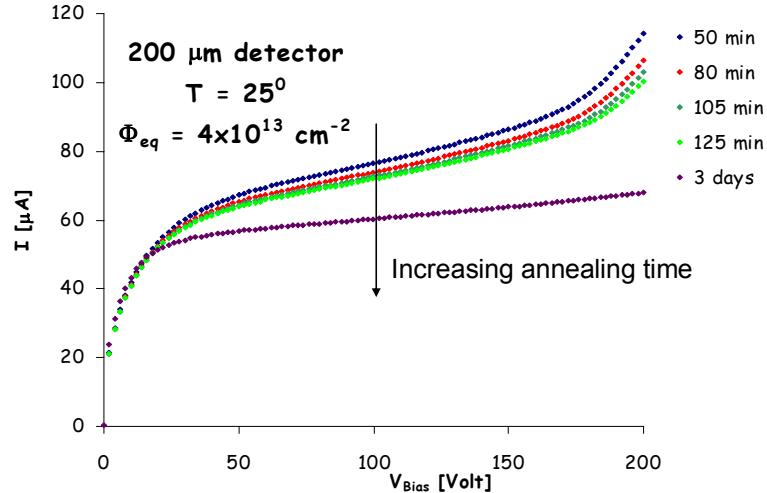

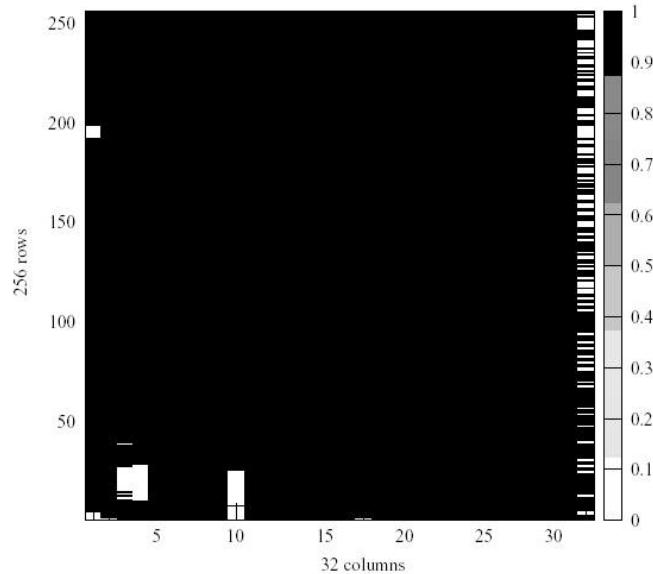

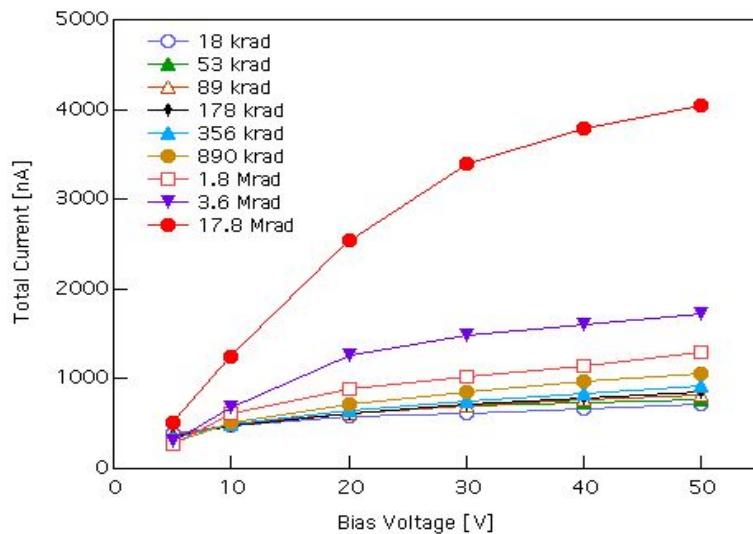

Le courant de fuite, mesuré sur une diode de test, est tout à fait uniforme et son maximum est la moitié de la valeur maximale admise. En outre la tension de désertion maximum (8 V), mesurée sur la même diode de test s'est avérée très uniforme et bien au-dessous de la valeur nominale maximum qui est de 20-30 V. Des tests ont été effectués sur plusieurs assemblages pour s'assurer de la qualité du bump-bonding. Sur une partie des derniers véhicules de test examinés avec une source radioactive de strontium 90, la quantité maximum de pixel manquants sur un circuit est inférieur à 0.3% en dessous de la valeur de 1% visé par l'expérience ALICE. Des essais d'irradiation des diodes de  $68 \text{ mm}^2$  avec un faisceau de protons de 27 MeV ont été réalisés à Legnaro, Italie, avec des fluences de 0.2 à  $25 \text{ } 10^{12} \text{ protons/cm}^2$ . La constante  $\alpha$  de dégradation du courant de fuite (pour une fluence équivalente neutrons 1 MeV) a été mesurée,  $\alpha = 0.62 \text{ } 10^{-16} \text{ A/cm}$  pour les détecteurs minces et  $\alpha = 0.83 \text{ } 10^{-16} \text{ A/cm}$  pour les détecteurs épais. Les mesures de recuit montrent que le courant de fuite diminue de 21% après 3 jours à la température ambiante, puis reste constant.

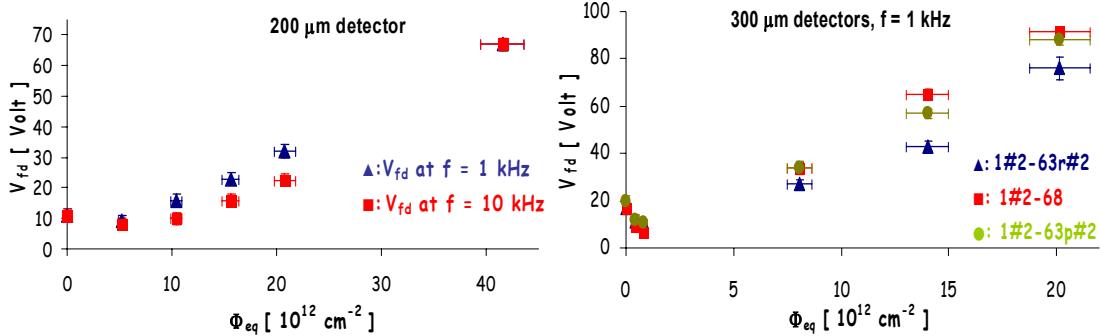

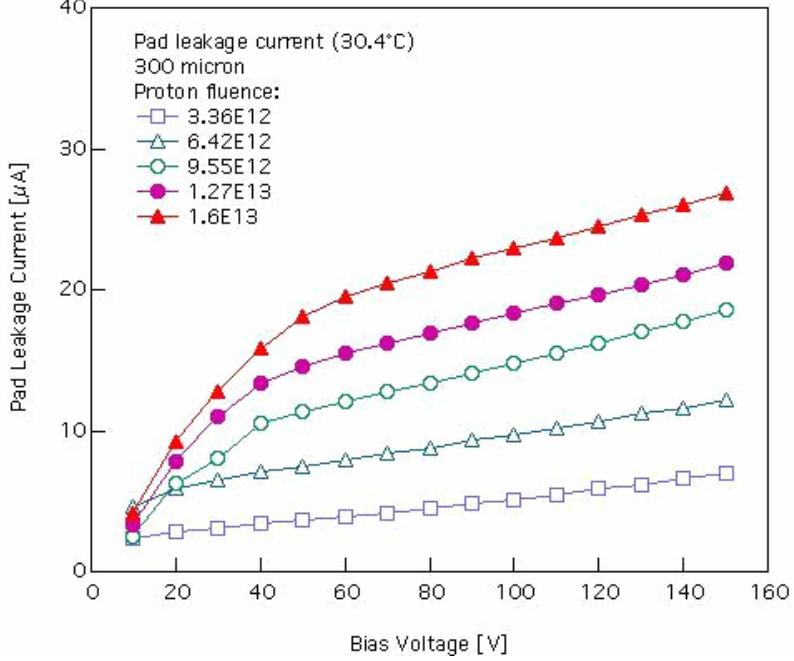

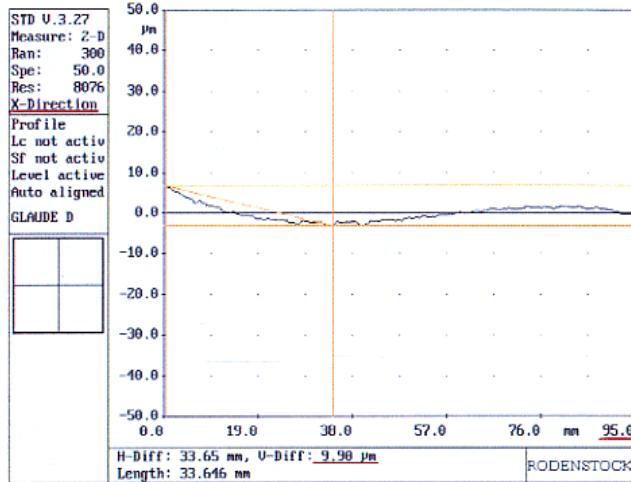

La tension correspondant à la désertion maximum ( $V_{fd}$ ) a été mesurée après irradiation (à deux fréquences de test différentes, à 1 kHz et à 10 kHz) pour les senseurs minces et épais.  $V_{fd}$  reste au dessous de 100 V pour une fluence équivalente neutrons 1 MeV qui est six fois la fluence attendue pour la couche la plus exposée d'ALICE en 10 ans d'opération. Pour étayer ces mesures, qui n'étaient pas faites dans des conditions de test standard, d'autres irradiations de capteurs ont été faites avec des protons de 24 GeV, et des fluences de  $3.36 \text{ à } 16 \text{ } 10^{12} \text{ protons/cm}^2$ . Dans ces conditions, nous avons mesuré la constante  $\alpha = 4.52 \text{ } 10^{-17} \text{ A/cm}$  (pour une fluence équivalente neutrons 1 MeV), ce résultat est en bon accord avec ceux présentés dans la littérature. Pour vérifier que l'épaisseur et la courbure de la plaquette sont selon les spécifications pour ALICE, quelques mesures ont été faites dans un laboratoire spécialisé du CERN. Les résultats de ces mesures sont entièrement conformes aux spécifications. En conclusion, nous pouvons assurer que les détecteurs fournis par Canberra sont conformes au cahier des charges, ils font même souvent mieux que ce qui est attendu. Ces détecteurs peuvent être employés sans risque avec les niveaux de rayonnement rencontrés dans l'expérience ALICE.

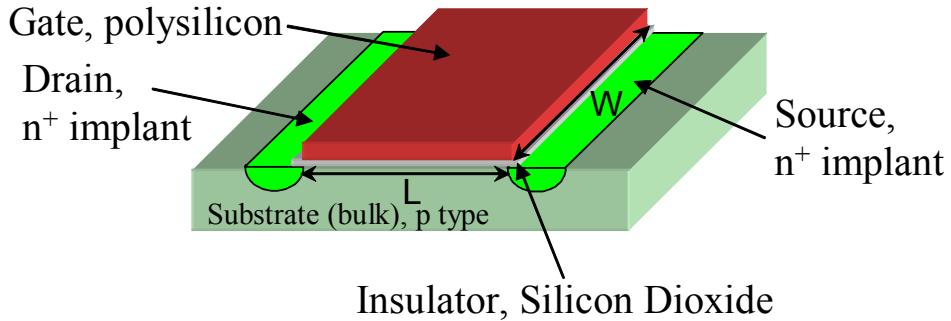

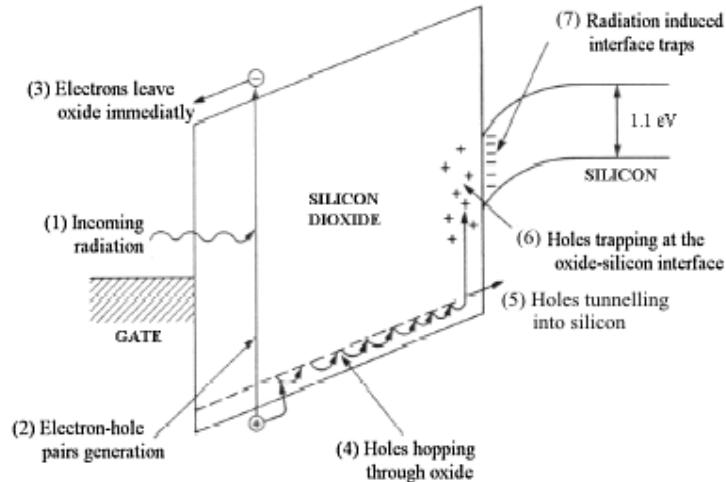

L'idée centrale qui a motivé ce travail est la possibilité de réaliser un détecteur hybride pour la physique des hautes énergies (HEP) avec une technologie MOS standard en réalisant un durcissement par design (HBD). Dans cette optique, nous exposons au **chapitre 5** les problèmes posés par les environnements fortement radiatifs sur des dispositifs électroniques. Nous décrivons les diverses solutions de durcissement, dont certaines ont été particulièrement étudiées au CERN. Pour ce qui est des effets cumulatifs induits par le rayonnement sur des dispositifs MOS, ils sont regroupés en deux classes : les effets d'ionisation et le déplacement

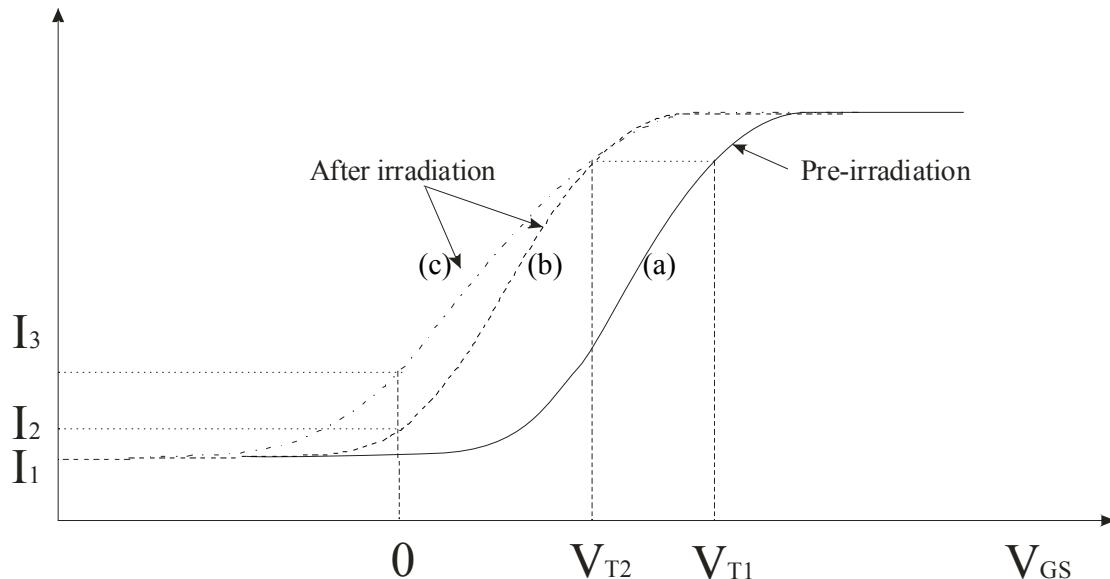

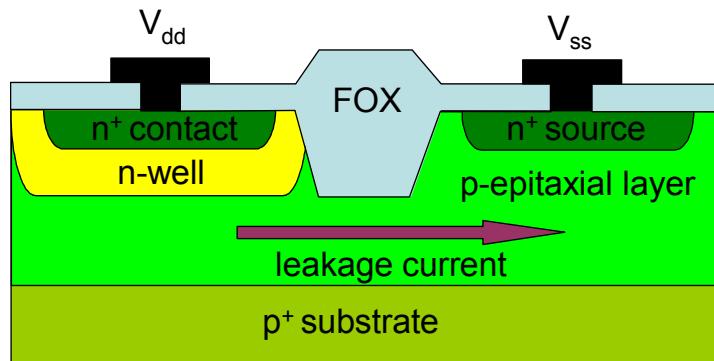

nucléaire (les composants MOS sont pratiquement insensibles aux effets de déplacement, mais à l'inverse, ils sont vulnérables à l'ionisation). L'effet d'ionisation ou de dose (ou encore TID, Total Ionizing Dose) est un effet cumulatif résultant de l'accumulation de charges induites par le rayonnement qui se piègent dans les oxydes, et se traduit par l'apparition de tensions parasites. Sur les MOS peuvent apparaître, en plus des variations dans la tension de seuil, des modifications dans la pente en inversion faible, de la transconductance, du comportement en bruit, entre autres caractéristiques. L'irradiation ionisante induit aussi différents types de courants parasites, résultant du piégeage de charge dans l'oxyde épais qui sépare des transistors (oxyde de champ). Une dose relativement faible dans un oxyde de champ peut induire suffisamment de piégeage de charges pour causer la défaillance d'un circuit intégré, due à une apparition des courants parasites drain-source et inter-transistor.

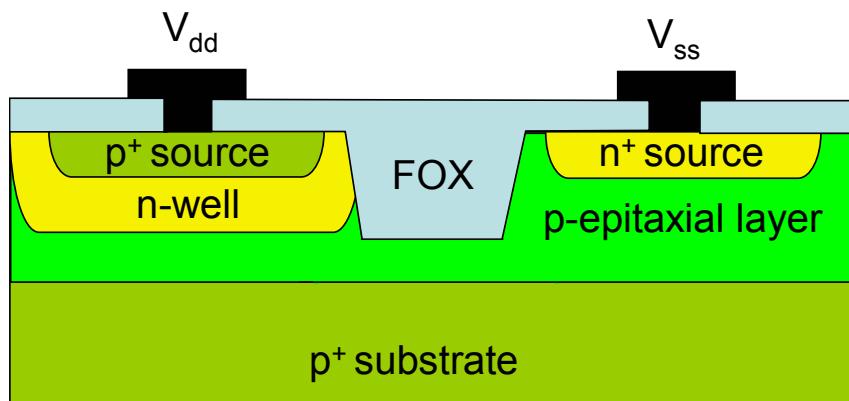

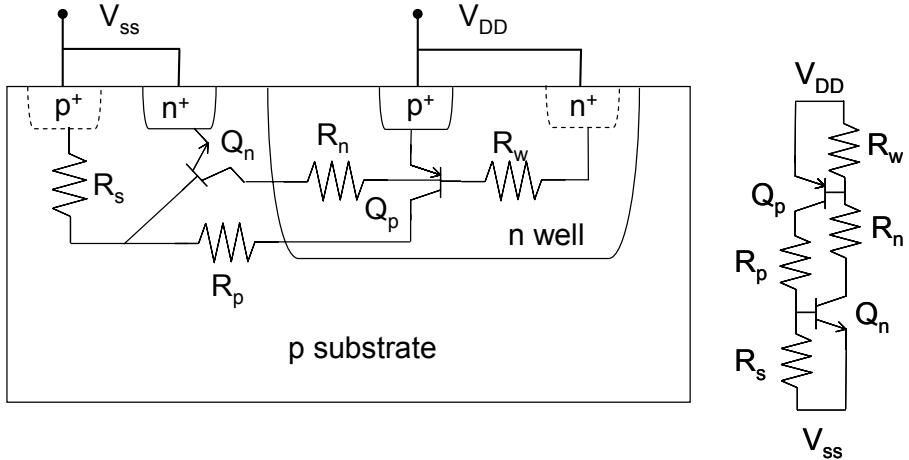

Une autre catégorie d'effets indésirables qui peuvent être induits par des rayonnements, est celle des phénomènes non récurrents (Single Event Effects, SEE). Ils sont produits par des particules fortement énergiques, lors de leur passage dans une partie sensible d'un transistor ou d'un circuit intégré. L'erreur la moins pénalisante et la plus courante est l'alea logique (Single Event Upset, SEU). Un SEU est un changement instantané et réversible de l'état logique d'une cellule. Il est produit par une particule ionisante lors de la traversée d'un point mémoire, qui induit (directement ou par des interactions secondaires) une charge suffisante pour modifier l'état logique de la cellule. Un autre effet non récurrent est le verrouillage maintenu (Single Event Latchup, SEL) qui peut (comme des autres phénomènes non récurrents) être à l'origine de la destruction des composants. Le SEL résulte du verrouillage d'un thyristor parasite qui court-circuite l'alimentation d'énergie, ce qui peut détruire le dispositif. Ce phénomène se rencontre dans quelques technologies CMOS; il peut aussi être provoqué lors de mise sous tension, faire suite à une élévation de température trop importante, mais également apparaître lorsqu'une particule ionisante traverse le composant.

Les trois options permettant de disposer de circuits tolérants au rayonnement sont discutées plus en détail: nous abordons le durcissement par le procédé, l'utilisation de composants qui existent dans le commerce, et l'adaptation de technologies standard durcies par HBD. Le principe de base du durcissement HBD consiste, à partir d'une technologie commerciale CMOS disponible et de coût réduit, à appliquer des techniques de conception de circuits propres à améliorer la tolérance au rayonnement. L'avantage principal de cette approche réside dans son prix réduit, et dans la possibilité de l'adapter simplement en fonction de l'évolution des technologies commerciales, dont l'amélioration des performances conduit à leur renouvellement très rapide.

Comme nous l'avons précisé, l'approche de durcissement HBD a été employée pour la conception du circuit ALICE1LHCb. Pour cette raison elle est présentée en détail, et nous évaluons l'impact de la réduction de la taille des composants sur l'effet du rayonnement et sur les performances du circuit.

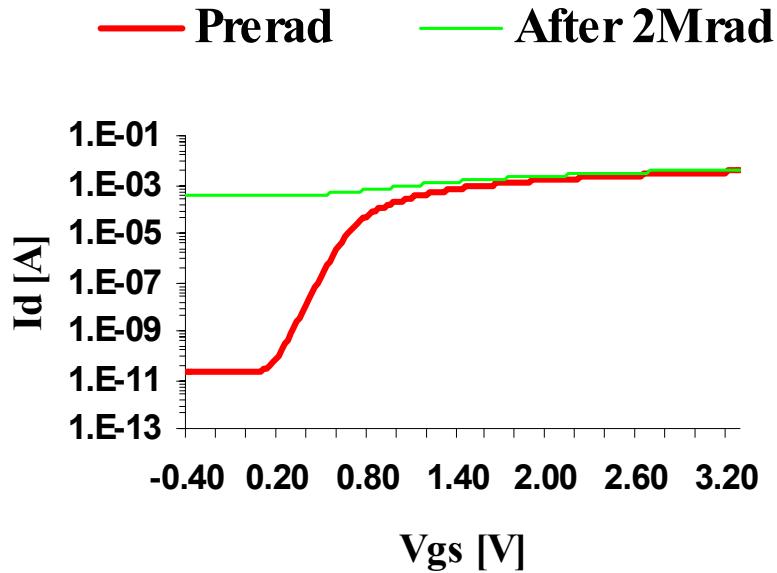

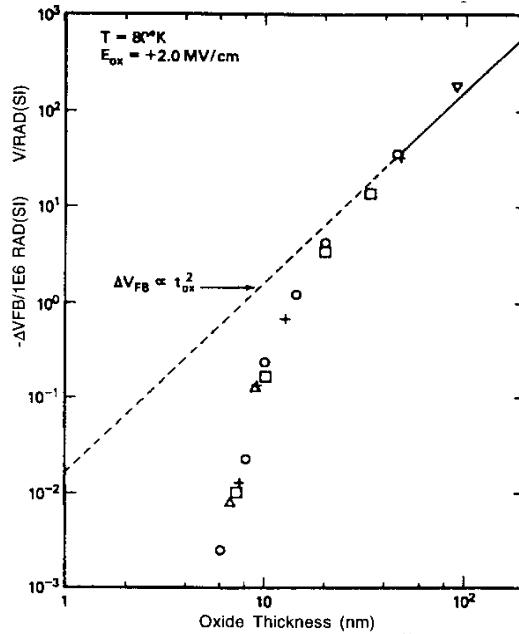

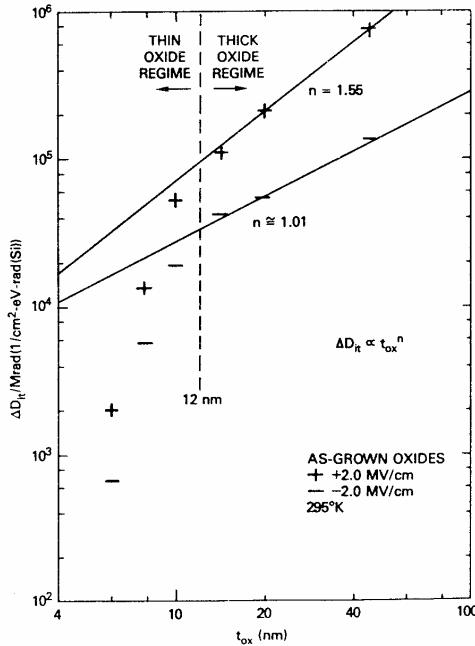

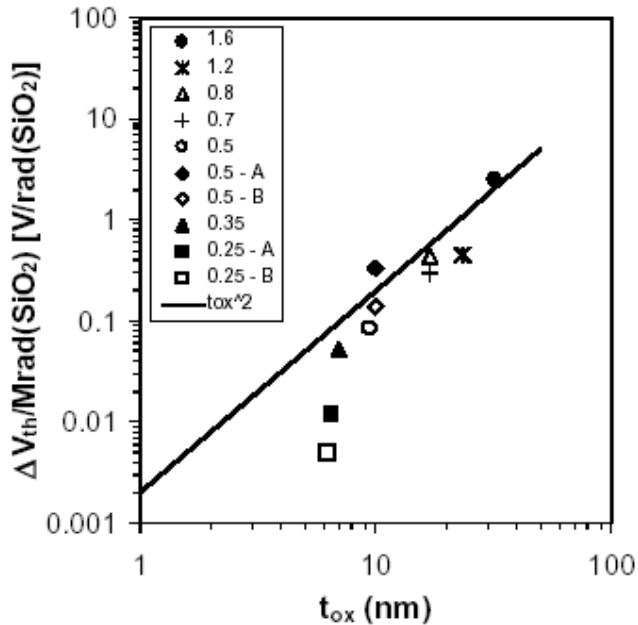

Lors du passage d'une génération de composants MOS à la suivante, l'épaisseur d'oxyde de grille,  $t_{ox}$ , est réduit. Comme l'a montré Saks, le décalage de tension de seuil induit par le rayonnement ionisante diminue avec  $(1/t_{ox})^2$  pour des oxydes de grille s'aminçissant jusqu'à environ 20 nm puis la dépendance devient beaucoup plus rapide. La technologie CMOS 0.25  $\mu\text{m}$  retenue pour la conception du circuit ALICE1LHCb a une épaisseur d'oxyde environ de 5.5 nm, et le décalage de la tension de seuil induit par le rayonnement est négligeable jusqu'à des doses cumulées de plusieurs dizaines de kGy. Les courants parasites sont diminués lors de la réduction des motifs de la technologie, mais pas éliminés, alors qu'aucun changement notable de la pente en inversion faible n'est induit par rayonnement dans les technologies submicroniques. Tous les phénomènes non récurrents sont atténués (ou éliminés) en technologie submicronique, excepté les SEU, parce que la sensibilité aux SEU est fortement dépendante de la technologie et de la conception.

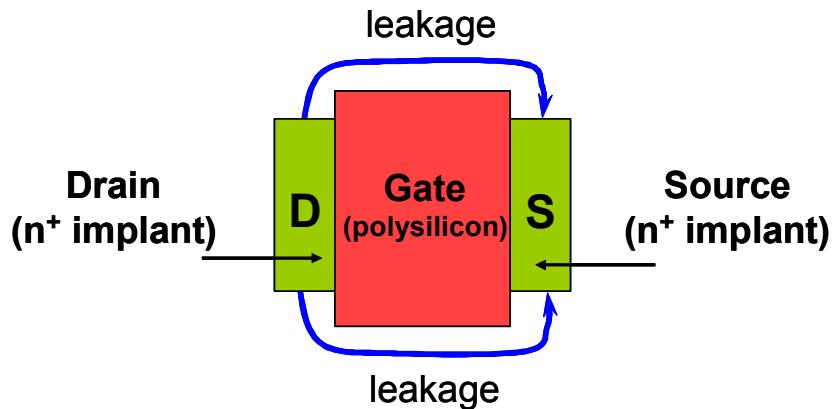

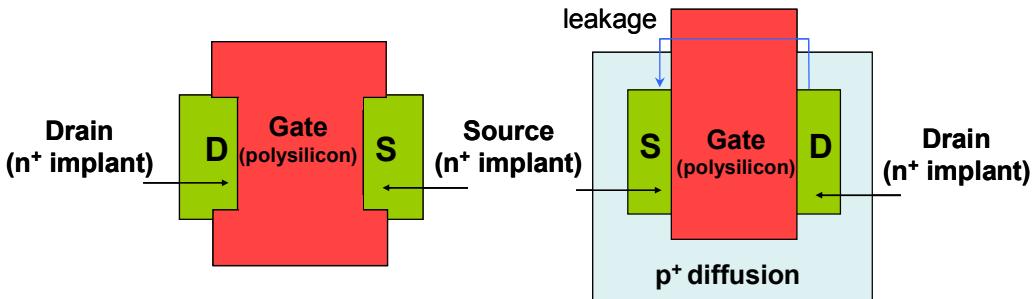

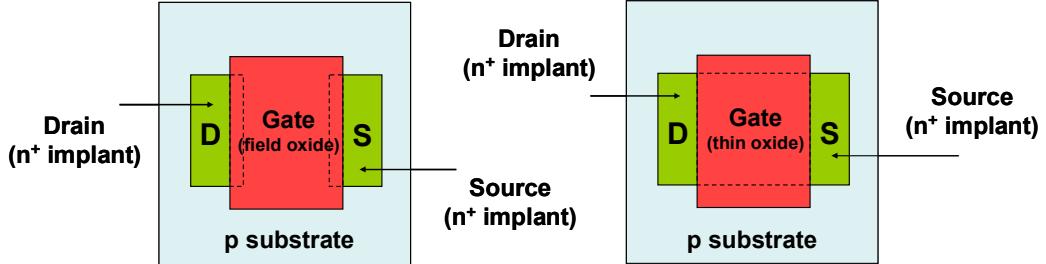

Le problème principal qui doit être résolu par les techniques de HBD est l'augmentation des courants parasites dans l'état bloqué. La solution au problème des fuites inter-transistor consiste à ajouter un anneau de garde de type  $p^+$  (également appelé « channel stop ») autour de chaque région de type n portée à un potentiel différent de l'alimentation plus basse, et autour de tous les caissons-n portés à un potentiel différent de l'alimentation plus élevé (ceci se produit par exemple lorsque la source des transistors canal-p est reliée au caisson).

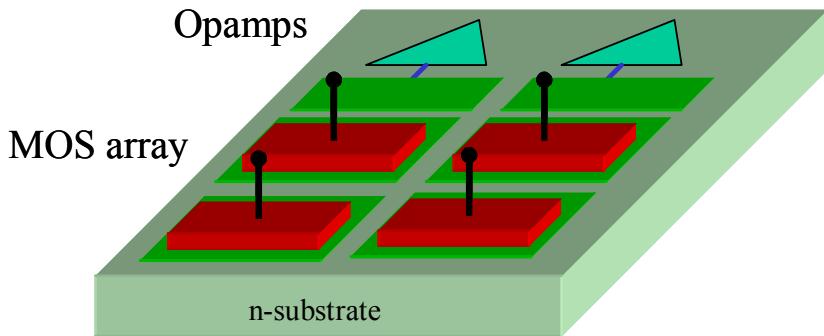

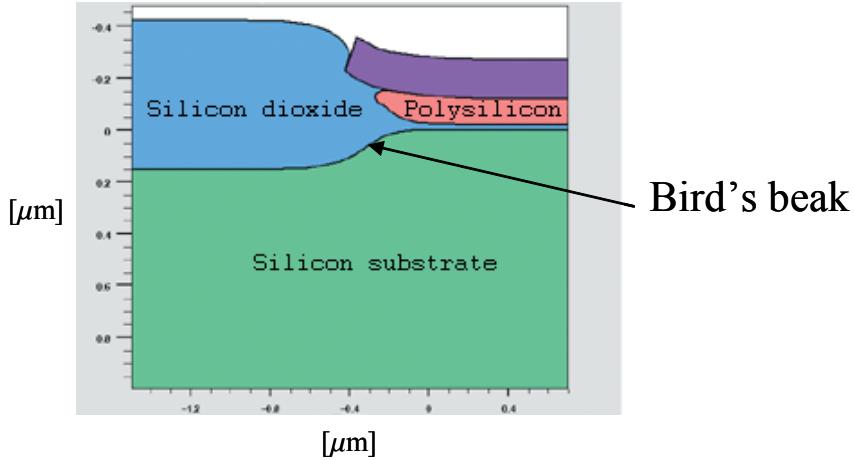

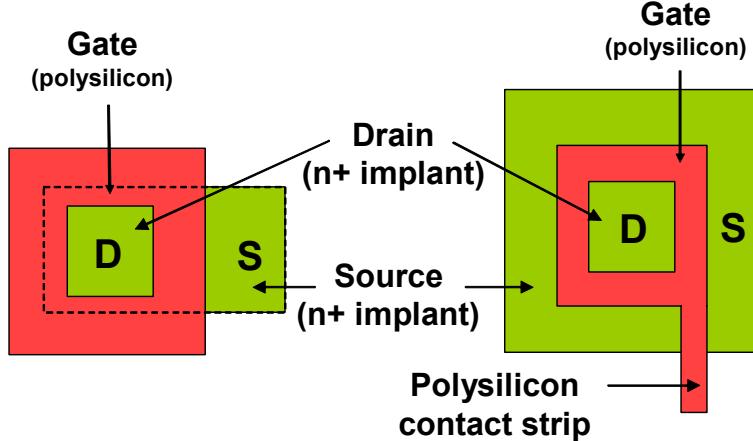

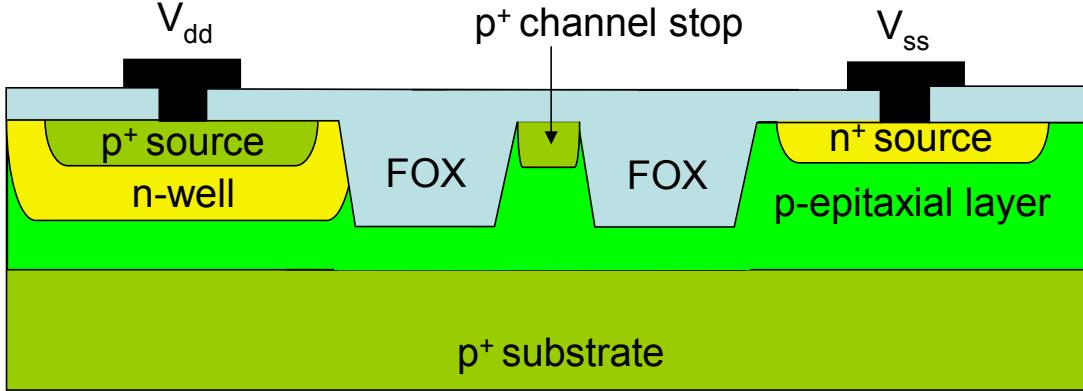

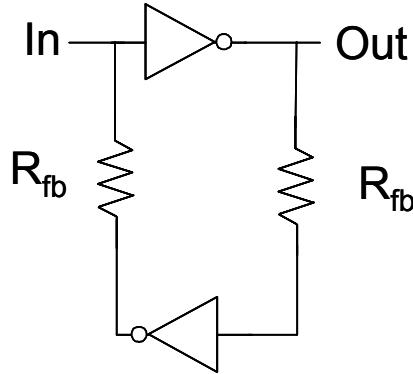

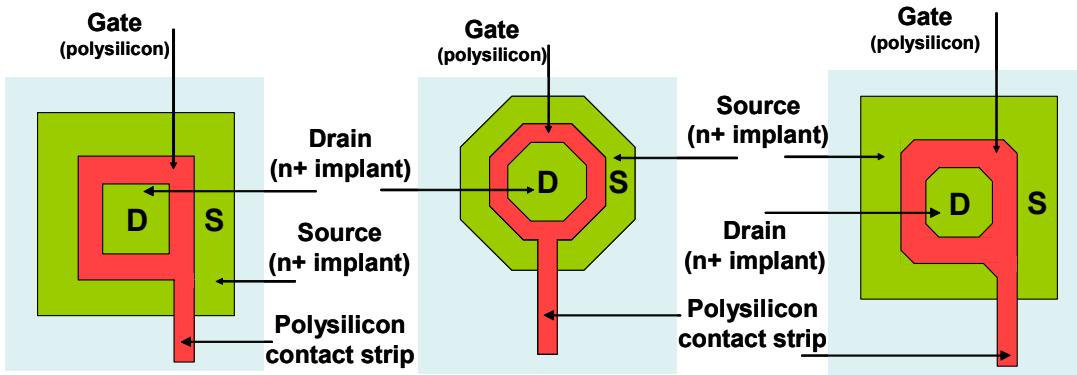

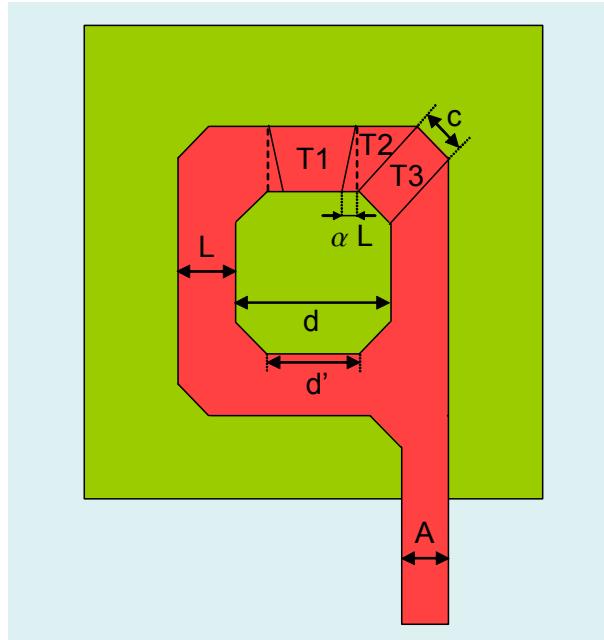

Quelques topologies de transistor qui réduisent ou éliminent les fuites drain-source sont présentées; parmi elles il y a le transistor ELT, «Enclosed Layout Transistor», qui utilise une grille annulaire dans la région active de sorte que le drain (ou la source) est à l'intérieur et la source (ou le drain) est à l'extérieur. Ces transistors occupent une surface supérieure à des transistors normaux, ils sont de plus asymétriques, leur capacité électrique est plus importante, mais ils constituent une solution très efficace pour le durcissement à la dose. D'autres techniques sont décrites pour augmenter la tolérance au rayonnement en agissant par exemple au niveau du système, et en particulier pour améliorer l'immunité aux phénomènes non récurrents.

Les transistors ELT entrent dans la conception du circuit ALICE1LHCb. De ce fait leurs caractéristiques, qui ont été étudiées au CERN dans le cadre du projet RD49, sont présentées en détail. Un modèle précis de l'une des formes possibles des transistors ELT est présenté, qui correspond bien aux résultats des mesures.

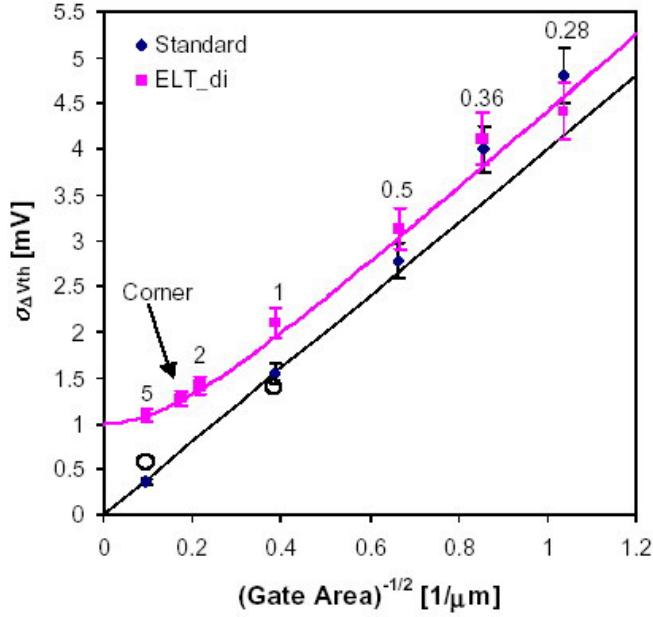

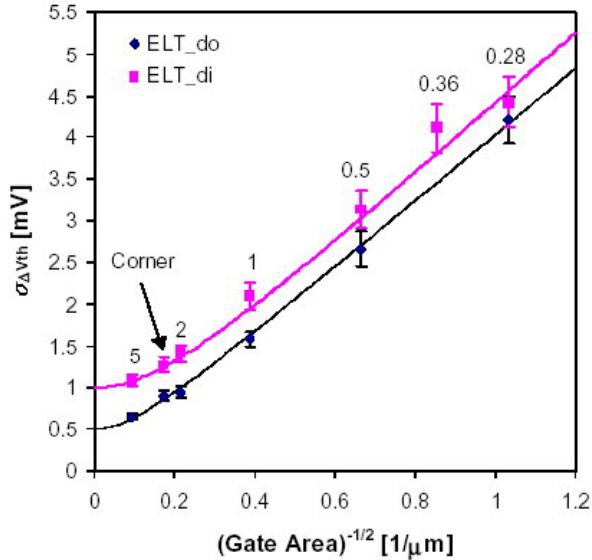

L'expression de l'appariement de transistors ELT identiques a une équation légèrement différente de celle des transistors standard (Standard Layout Transistors, SLT). Pour les transistors SLT, l'appariement s'améliore avec la taille du transistor, alors que pour les ELT il sature à une certaine valeur. A part cela, les paramètres sont semblables à ceux des SLT, comme montré dans le tableau 1.

|                                          | n SLT                                                 | n ELT (drain inside)                                                       | n ELT (drain outside)                                                      | p SLT                                                 |

|------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------|

| $V_{th}$<br>Matching equation            | $\sigma_{\Delta V_{th}}^2 = \frac{A_{V_{th}}^2}{WL}$  | $\sigma_{\Delta V_{th}} = \sqrt{\frac{A_{V_{th}}^2}{WL} + \sigma_0^2}$     | $\sigma_{\Delta V_{th}} = \sqrt{\frac{A_{V_{th}}^2}{WL} + \sigma_0^2}$     | $\sigma_{\Delta V_{th}}^2 = \frac{A_{V_{th}}^2}{WL}$  |

| $\Delta\beta/\beta$<br>Matching equation | $\sigma_{\Delta\beta/\beta}^2 = \frac{A_\beta^2}{WL}$ | $\sigma_{\Delta V_{th}} = \sqrt{\frac{A_\beta^2}{WL} + \sigma_{0\beta}^2}$ | $\sigma_{\Delta V_{th}} = \sqrt{\frac{A_\beta^2}{WL} + \sigma_{0\beta}^2}$ | $\sigma_{\Delta\beta/\beta}^2 = \frac{A_\beta^2}{WL}$ |

| $A_{V_{th}}$                             | 4 mV·μm                                               | 4.3 mV                                                                     | 4 mV·μm                                                                    | 3.7 mV·μm                                             |

| $\sigma_0$                               | -                                                     | 1 mV                                                                       | 0.5 mV                                                                     | -                                                     |

| $A_\beta$                                | 1 %·μm                                                | 1.3 %·μm                                                                   | 1.3 %                                                                      | 1 %·μm                                                |

| $\sigma_{0\beta}$                        | -                                                     | 0.3 %                                                                      | 0.3 %                                                                      | -                                                     |

Tableau 1: Performances d'appariement des transistors canal-n et canal-p pour les «Standard Layout Transistors» (SLT) et les «Enclosed Layout Transistors» (ELT), avec le drain à l'intérieur ou à l'extérieur de la grille annulaire.

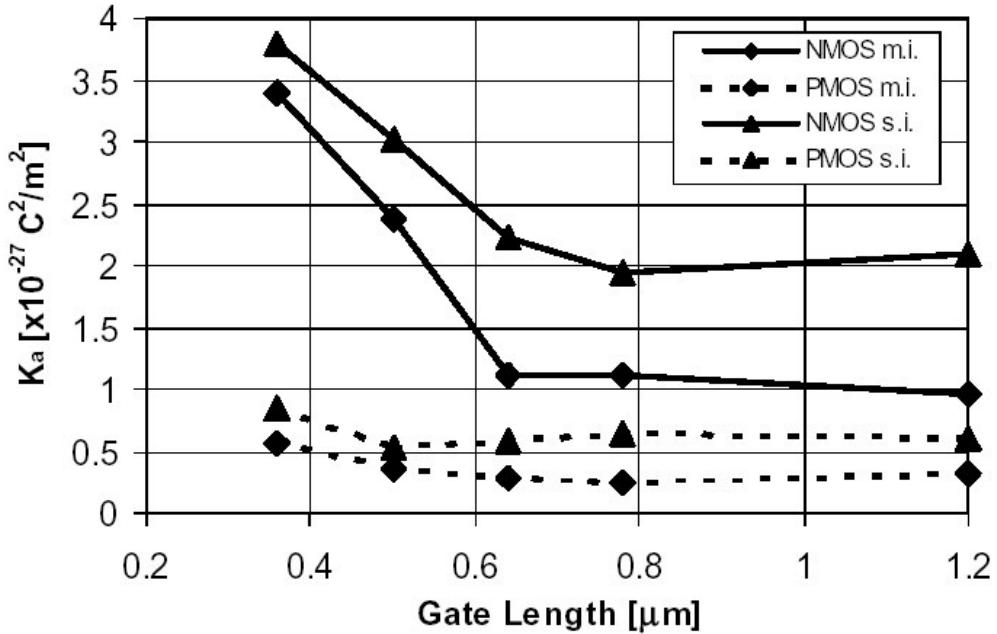

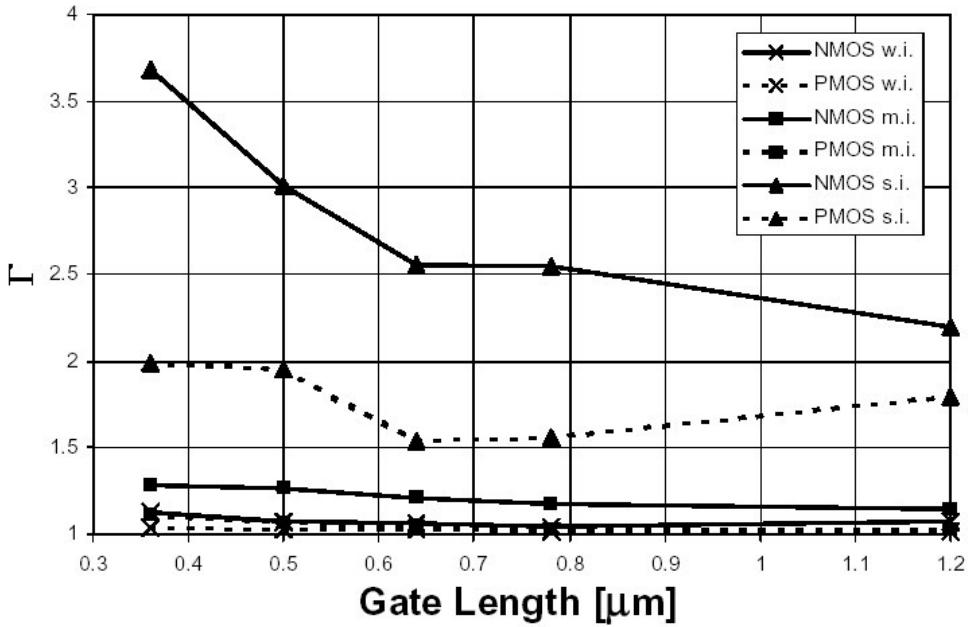

Une autre caractéristique très importante pour la conception de circuits intégrés est la performance en bruit de la technologie choisie. Des mesures ont été effectuées sur différents types de transistors en technologie 0.25 μm CMOS pour extraire les paramètres de bruit; les résultats sont récapitulés dans le tableau 2. Les valeurs des paramètres sont une fonction de la longueur L des transistors et sont plus élevées lorsque L diminue.

|                                 | n ELT s.i. | n ELT m.i. | n ELT w.i. | p SLT s.i. | p SLT m.i. | p SLT w.i. |

|---------------------------------|------------|------------|------------|------------|------------|------------|

| $\alpha$                        | .9 to .98  | .9 to .98  | .9 to .98  | .8 to .9   | .8 to .9   | .8 to .9   |

| $K_a$<br>[ $10^{-27} C^2/m^2$ ] | 3.8 to 2   | 3.4 to 1   | 3.4 to 1   | 0.8 to 0.6 | 0.6 to 0.4 | 0.6 to 0.4 |

| $\Gamma$                        | 3.7 to 2.2 | 1.3 to 1.2 | 1.2 to 1.1 | 2 to 1.6   | 1.2 to 1.1 | 1          |

Tableau 2: Performances en bruit de transistors canal-n et canal-p pour les «Standard Layout Transistors» (SLTs) et les «Enclosed Layout Transistors» (ELTs), pour une inversion forte (s.i.), faible (w.i.) ou modérée (m.i.).

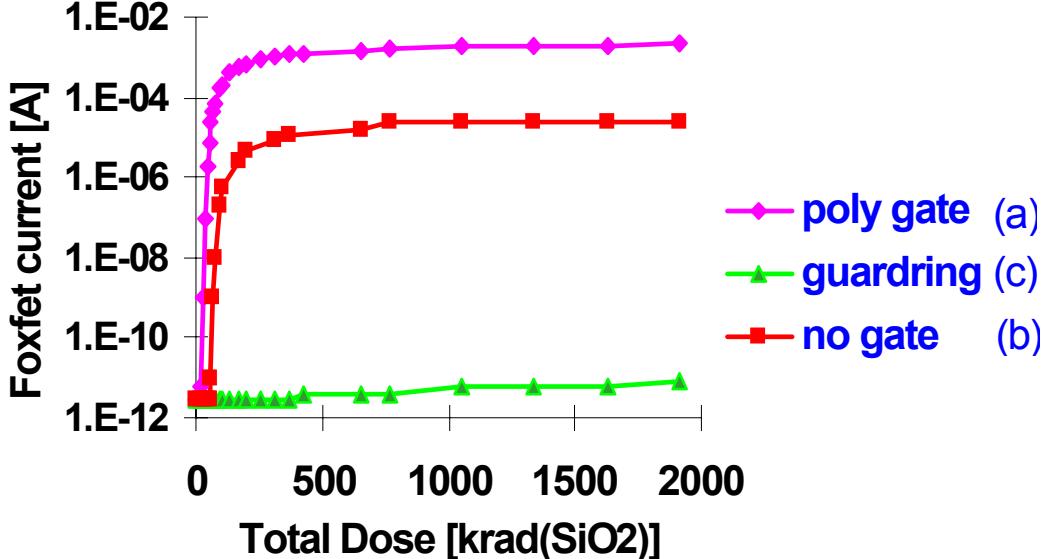

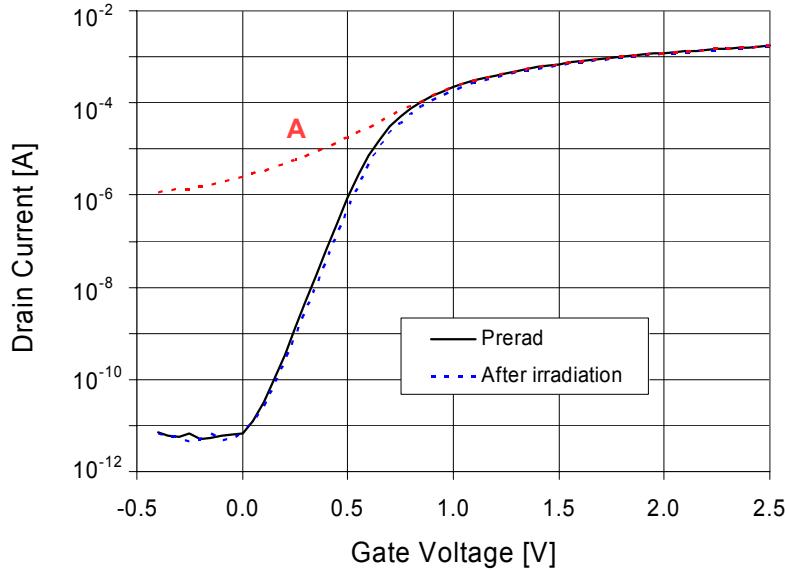

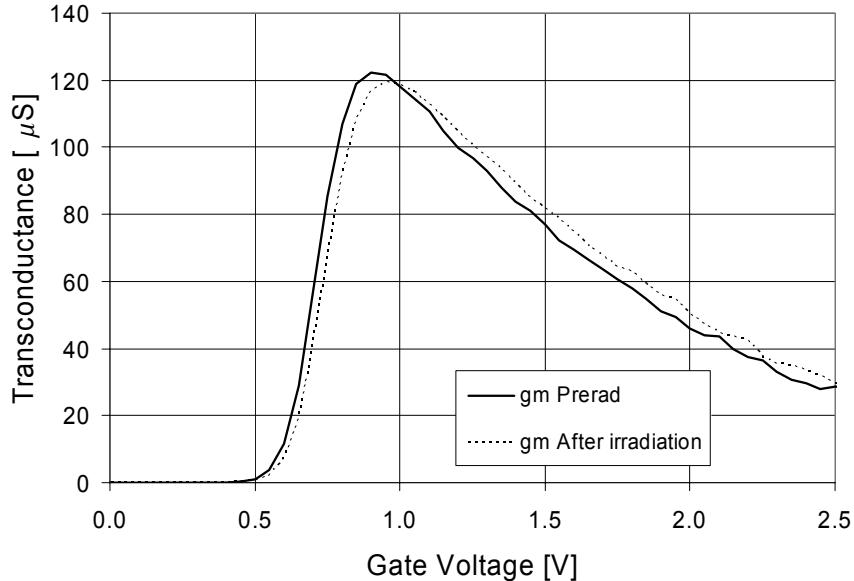

Les transistors (ELT et transistors standard) ont été irradiés en utilisant des rayons X de 10 keV, et une source de rayonnement  $\gamma$ ,  $^{60}Co$ . Toutes les irradiations ont été exécutées avec une polarisation «pire cas», et les mesures ont été effectuées après recuit. Les ELTs ne montrent aucun courant de fuite même après une dose de 10 kGy ( $SiO_2$ ). Sur tous les échantillons mesurés la diminution de la transconductance et de la mobilité est inférieure à 6%, et les variations de la pente en faible inversion et de la conductance de sortie sont de l'ordre de quelques pour cent. Le coefficient  $A_\beta$  d'appariement du gain de courant («current gain matching») ne se dégrade pas après une dose de 15 kGy ( $SiO_2$ ). Le coefficient

d'appariement de tension de seuil  $A_{vth}$  pour des transistors canal-p change de quelque pour cents, alors que pour des transistors canal-n  $A_{vth}$ , il augmente de 45% (mais la précision de la mesure est très pauvre). L'augmentation du bruit blanc est limitée dans toutes les régions d'inversion : maximum 15% pour les canal-n et 7% pour des dispositifs canal-p. La constante de bruit  $1/f$  ( $K_a$ ) augmente avec l'irradiation, d'un facteur 2 pour les transistors canal-n et d'un facteur 8 pour les transistors canal-p, pour une dose de 1 MGy ( $SiO_2$ ).

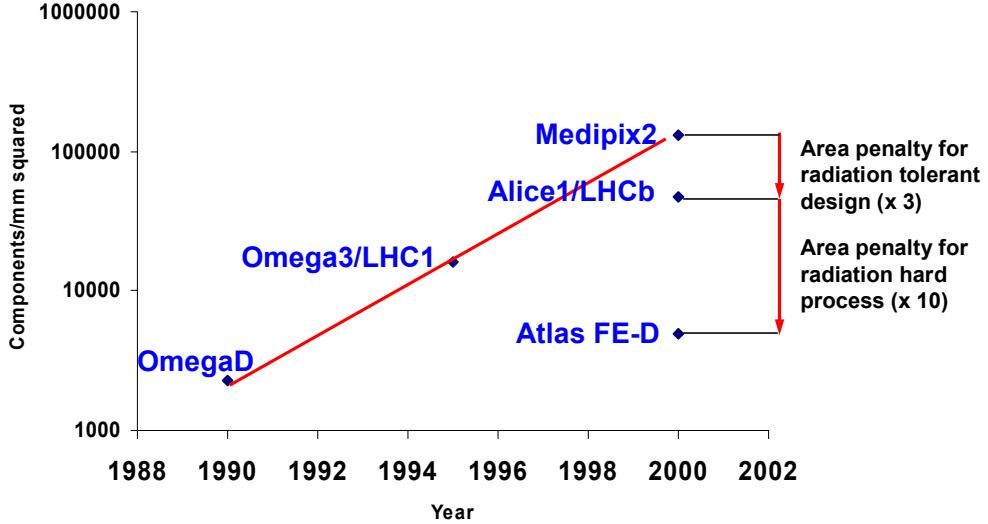

L'utilisation des techniques de durcissement HBD réduit la densité de composants que l'on peut intégrer, cela se traduit par une augmentation de la consommation. Cette surcharge a été évaluée pour des cellules et pour des systèmes complets. Bien que les résultats soient dépendants de la conception et de la technologie choisie, on peut estimer une pénalité pour la puissance d'environ un facteur 2 et pour la surface d'un facteur 2.5 à 3. Il est important de préciser que dans tous les cas étudiés de durcissement à la conception par HBD, les performances sont toujours supérieures au produit correspondant en technologies durcies disponibles dans le commerce.

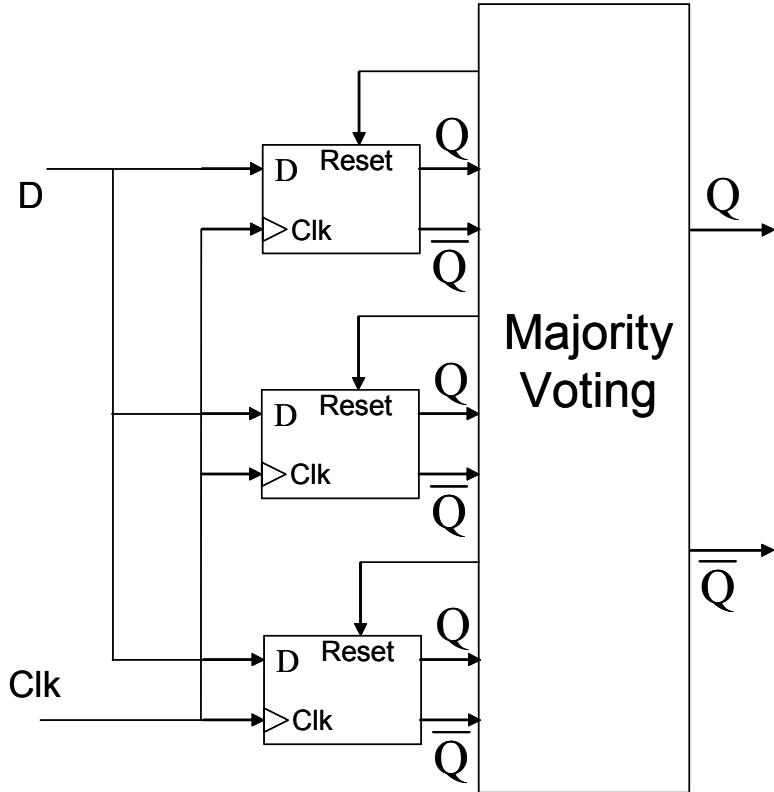

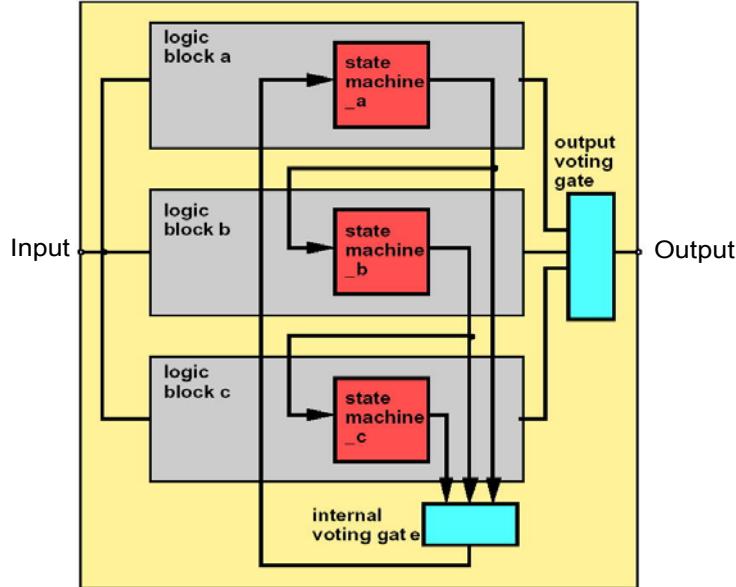

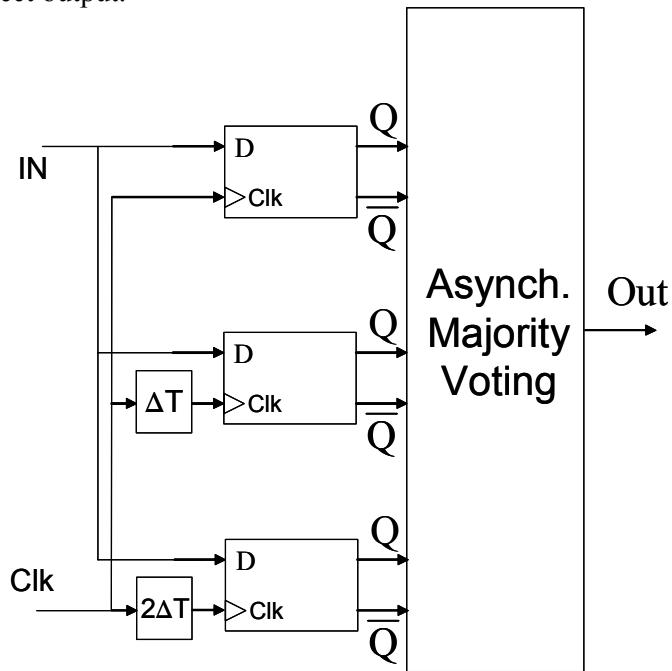

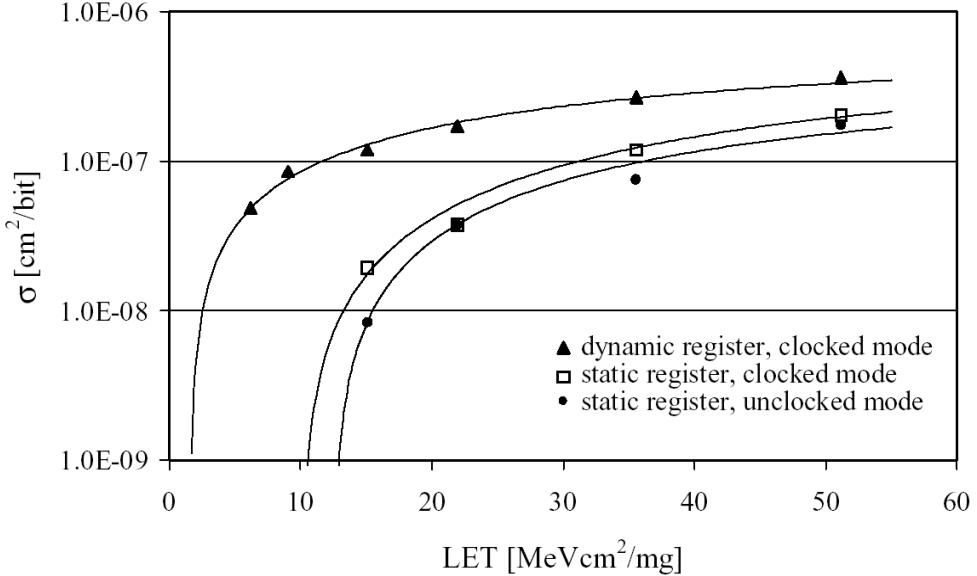

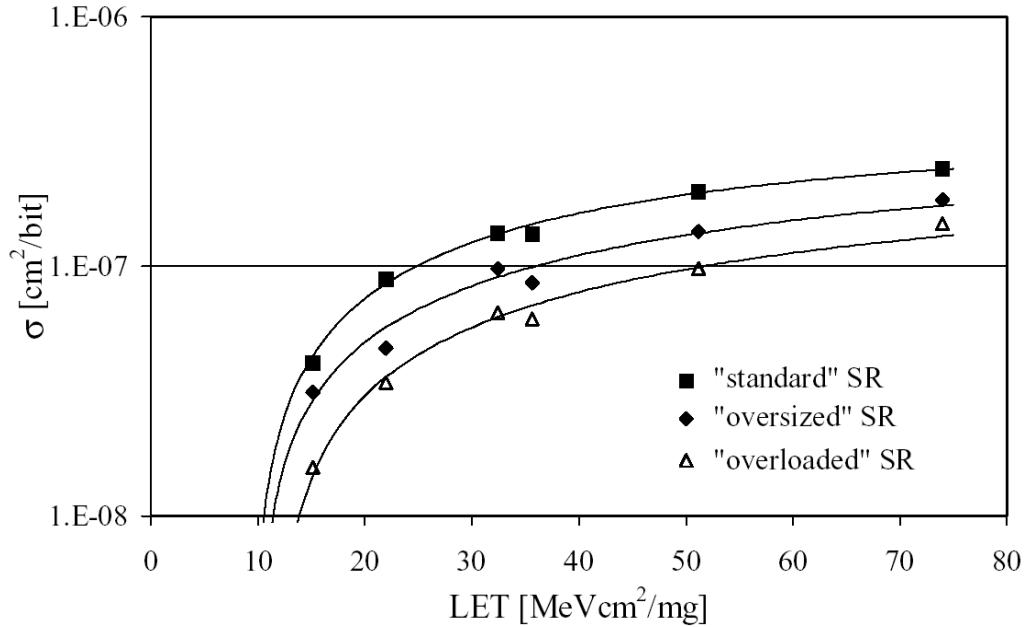

L'efficacité de l'approche durcissement HBD par rapport à la tolérance aux SEEs a été examinée au CERN en irradiant plusieurs types de registres à décalage avec des particules de haute énergie. La sensibilité des registres a été mesurée en fonction du transfert linéaire d'énergie (Linear Energy Transfer, LET) jusqu'à  $89 \text{ MeVcm}^2\text{mg}^{-1}$  : plus le LET est élevé, plus on a de risque de déclencher des phénomènes non récurrents. On n'a observé aucun effet SEL pendant toute la campagne d'irradiation. Les résultats d'irradiation montrent une meilleure tolérance aux SEU des transistors durcis par HBD que ceux de conception standard. Mais aussi une meilleure tolérance des structures statiques par rapport aux dynamiques. Pour se prémunir des SEU, le fait de charger une cellule avec une capacité de sortie plus élevée donne de meilleurs résultats que l'augmentation de la taille des transistors.

Le **chapitre 6** présente les circuits prototypes dont les développements mènent au circuit ALICE1LHCb. Ce chapitre donne une brève vue d'ensemble de deux des premiers circuits de lecture à pixels destinés à la physique des hautes énergies conçus au CERN. Il s'agit des circuits Omega2 et Omega3, réalisés à partir de technologies commerciales CMOS, respectivement de  $3 \mu\text{m}$  et de  $1 \mu\text{m}$ . Ils ont prouvé la possibilité d'employer des détecteurs à pixel pour la physique des hautes énergies, même si leur tolérance au rayonnement était insuffisante et nécessitait une amélioration sensible.

Le circuit de test ALICE1 était un premier prototype de circuit de lecture à pixels, conçu en technologie commerciale CMOS de  $0.5 \mu\text{m}$ . Il utilisait des techniques de dessin pour améliorer sa tolérance au rayonnement. Il a prouvé le bien fondé de l'approche de durcissement par HBD appliquée à un circuit fonctionnant en mode-mixte (fonctions analogiques et digitales sur le même silicium). Parmi les résultats de test présentés, nous pouvons mentionner le fait qu'il a résisté (selon le type de rayonnement) à une dose totale comprise entre 6 kGy et 17 kGy. Aucun courant de fuite induit par le rayonnement n'a été

observé, et le circuit a finalement été défaillant en raison des effets cumulatifs des décalages de seuil induits par le rayonnement.

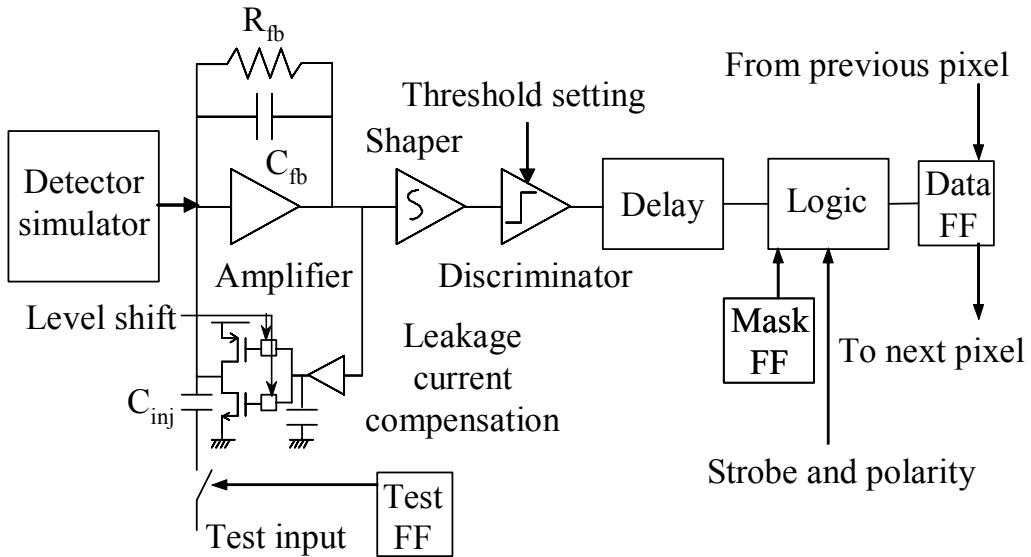

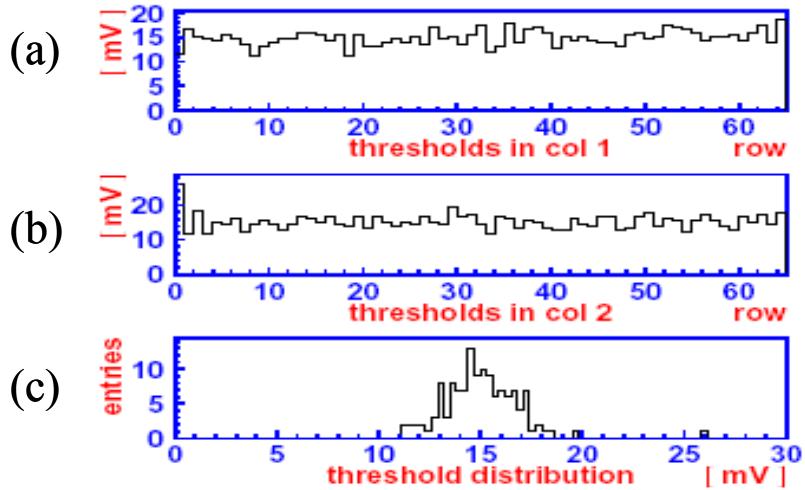

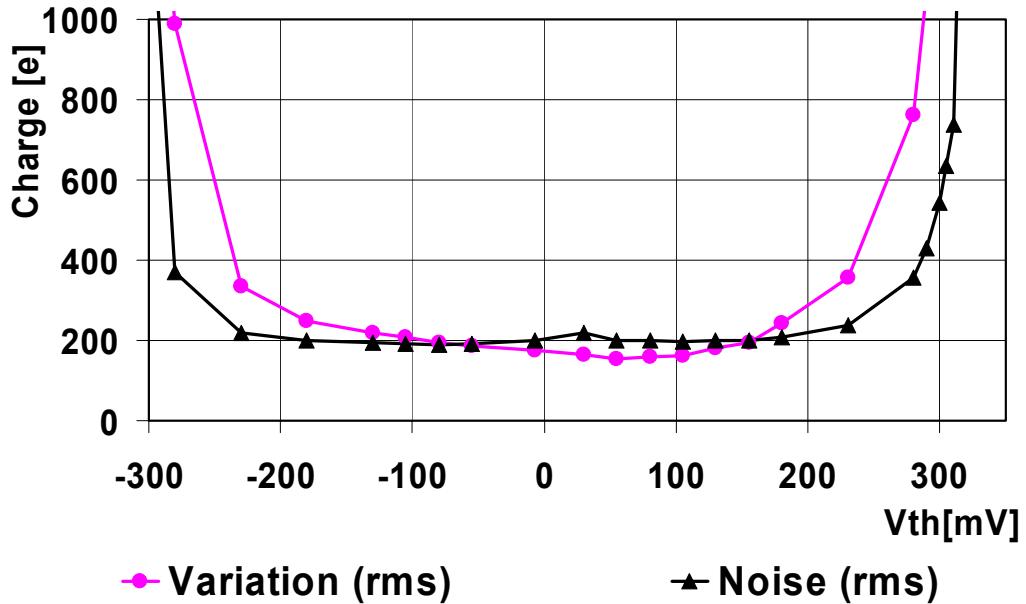

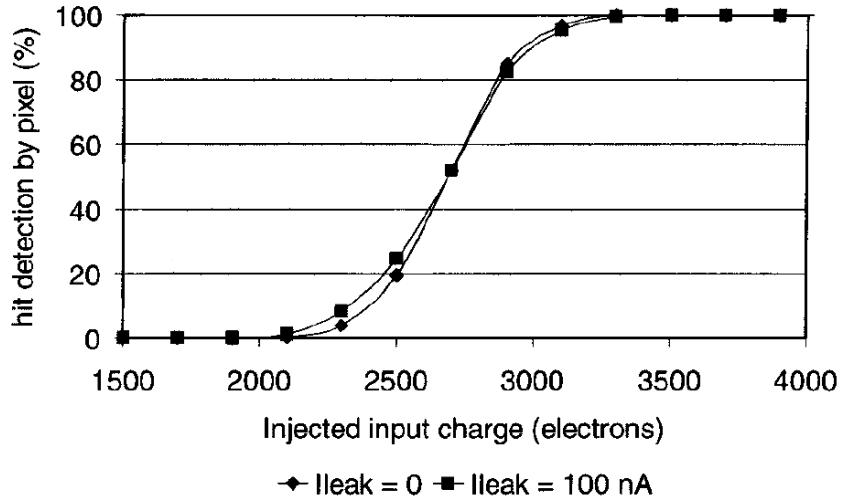

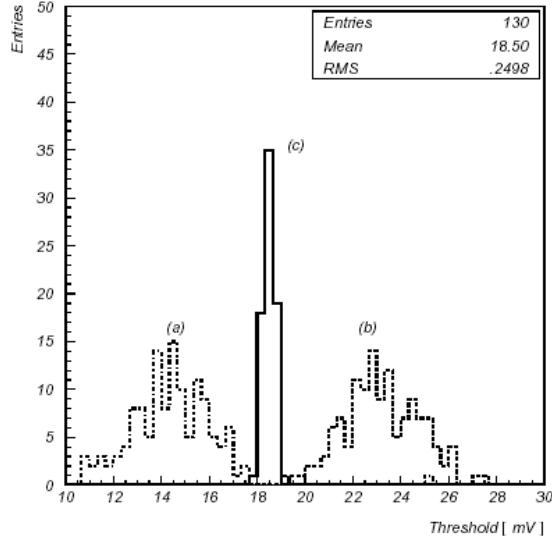

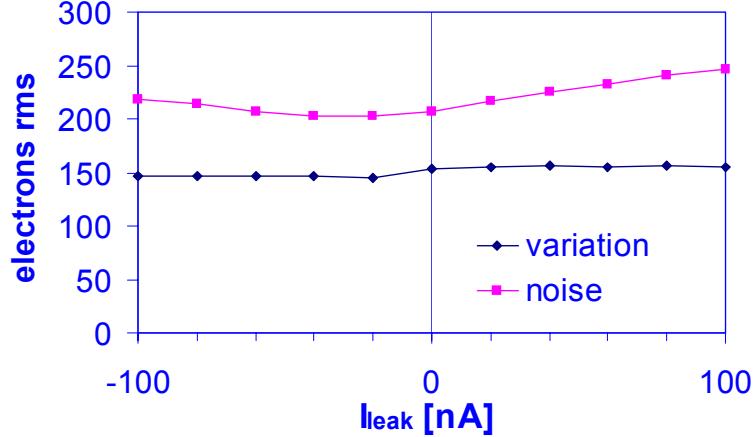

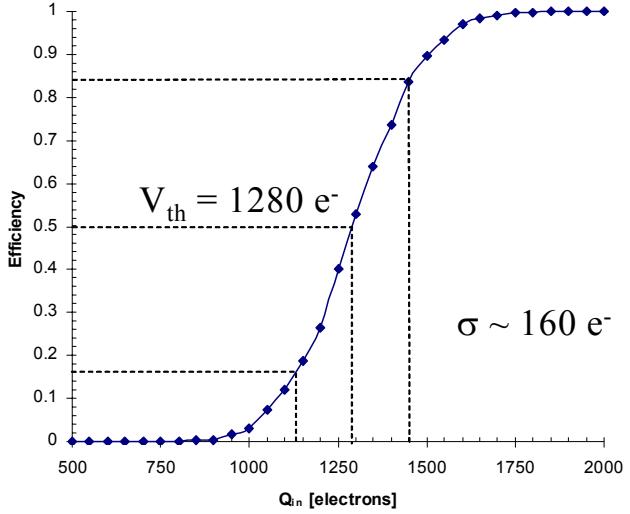

La disponibilité pour le CERN d'une technologie plus avancée (avec une lithographie de  $0.25 \mu\text{m}$ ) a conduit à la conception du circuit de test ALICE2, basé sur le prototype précédent mais avec quelques changements. Ce circuit, qui accepte à l'entrée des signaux positifs ou négatifs, comporte un préamplificateur, un filtre de mise en forme, un comparateur, une ligne à retard et la logique de lecture. Comme ce prototype n'a pas été prévu pour être connecté à un détecteur, une structure d'entrée a été ajoutée à chaque cellule pour simuler la capacité du détecteur, le couplage entre pixel, et le courant de fuite du détecteur. Quelques détails sur la structure du circuit sont présentés, ainsi que les résultats expérimentaux. Le circuit a été testé avant et après irradiation. Avant irradiation il est entièrement fonctionnel, et présente une tension minimum de seuil de détection du signal d'environ  $1500 \text{ e}^-$ , avec une dispersion de seuil d'environ  $160 \text{ e}^- \text{ rms}$  (sans ajustement de seuil) et  $25 \text{ e}^- \text{ rms}$  (après ajustement). Le bruit de pixel est environ  $220 \text{ e}^- \text{ rms}$ .

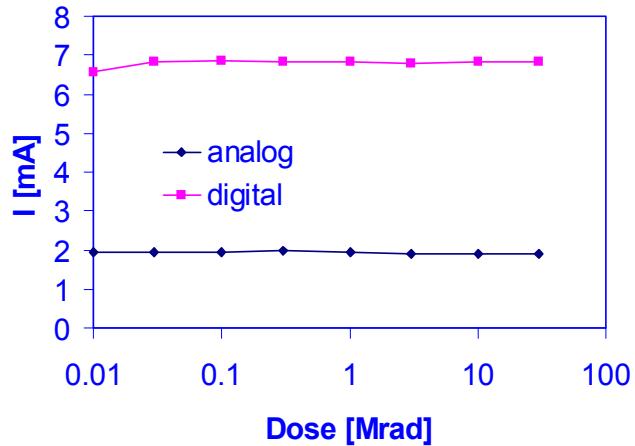

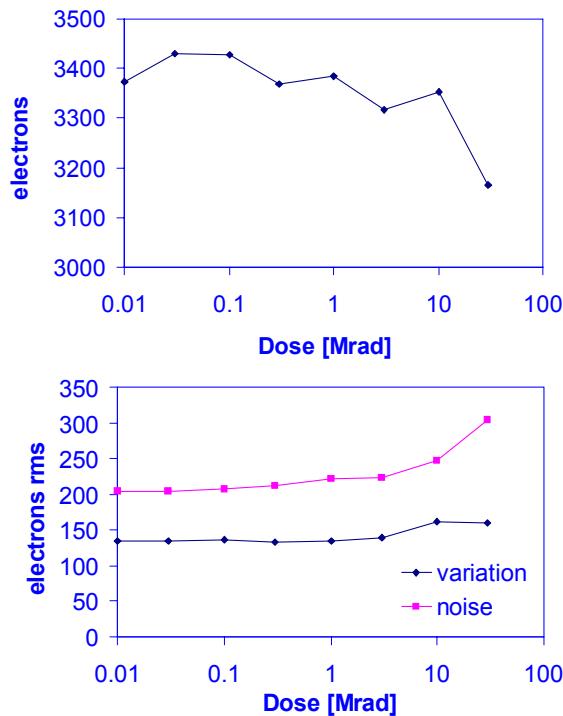

Les résultats les plus importants qui ont été dérivés des tests de ce prototype ont trait à sa tolérance aux rayonnements. En fait ce circuit a été irradié aux rayons X, avec des protons d'énergie élevée et avec un rayonnement  $\gamma$ . L'absence d'une quelconque augmentation de la puissance absorbée avec la dose totale confirmée sur un circuit complet, montre que l'utilisation des transistors ELT canal-n avec anneaux de garde évite les fuites induites par rayonnement. D'ailleurs, le circuit reste entièrement fonctionnel jusqu'à une dose ionisante totale de  $300 \text{ kGy}$  ( $\text{SiO}_2$ ) et une fluence de  $9 \cdot 10^{14} \text{ protons cm}^{-2}$ . L'irradiation a eu lieu au SPS du CERN, avec des protons de  $450 \text{ GeV/c}$ . Le circuit a été également irradié avec un accélérateur Van de Graaf délivrant des protons de  $6.5 \text{ MeV/c}$ . Un circuit a été irradié par paliers aux doses de  $90, 190$  et  $480 \text{ kGy}$ . Il a cessé de fonctionner à  $480 \text{ kGy}$ . Les sorties analogiques et la consommation de puissance ont montré un comportement semblable à celui observé dans les autres mesures. Un circuit a été également irradié avec des rayons gamma par palier aux doses de  $30, 190, 230$  et  $260 \text{ kGy}$ . Dans ce cas, une légère augmentation de consommation d'énergie dans la partie analogique a été enregistrée. Pour les autres paramètres, les résultats de cette irradiation ont étroitement reflété ceux de l'irradiation aux rayons X discutée ci-dessus.

Ce prototype a prouvé définitivement qu'il était possible de concevoir (en technologie commerciale) un circuit mixte entièrement fonctionnel pour les détecteurs à pixels hybrides. L'utilisation des techniques de durcissement par HBD, permet à ces circuits de résister à des doses de rayonnement et à fluences de particules beaucoup plus élevées que celles prévues pour le LHC.

Le **chapitre 7** présente la conception et les simulations de la puce ALICE1LHCb, et en particulier de son circuit d'entrée. Il utilise un schéma d'entrée différent des classiques, qui utilisent l'intégration de charges, la compensation pole-zéro et la mise en forme semi-

gaussienne. Ce circuit a été conçu pour supporter un fort taux d'occupation du canal, en permettant un retour à l'origine rapide de tous les blocs qui composent la chaîne de lecture, tout en gardant un bruit bas ( $< 200 \text{ e}^-$ ) et une faible consommation (de l'ordre de 50-100  $\mu\text{W}/\text{canal}$ ).

Dans la première section nous récapitulons toutes les exigences de ALICE et LHCb, pour motiver nos choix de conception. La deuxième section est consacrée à une analyse détaillée du choix du design de l'étage d'entrée. L'intégration de charge, plus la compensation pole-zéro et la mise en forme semi-gaussienne sont analysés, et s'avèrent extrêmement difficile à utiliser dans notre cas. En effet, le fort taux d'occupation du canal peut amener à la saturation des étages amplificateurs (pile-up); il serait également nécessaire de concevoir un arrangement différent de l'étage de contre-réaction, pour améliorer la précision de la compensation pole-zéro, et la diminution du temps de retour à l'origine (qui peut être amélioré seulement en augmentant l'ordre du filtre de mise en forme semi-gaussienne). En plus, l'approche analytique proposée par Chang et Sansen [Cha91] est seulement approximative pour un arrangement avec un amplificateur de charge (CSA, Charge Sensitive Amplifier) de basse puissance et un temps de mise en forme rapide.

Ceci nous a conduit à développer un schéma d'entrée différent, ayant des performances en bruit identiques (ou meilleures) à celles obtenues avec un schéma standard, mais avec des temps de retour à l'origine améliorés à la fois pour les sorties du circuit de mise en forme et pour le préamplificateur, ce qui permet d'utiliser ce circuit même dans le cas d'un fort taux d'occupation [Din03, Din01, Din00, Sno01, Sno01a, Wyl99].

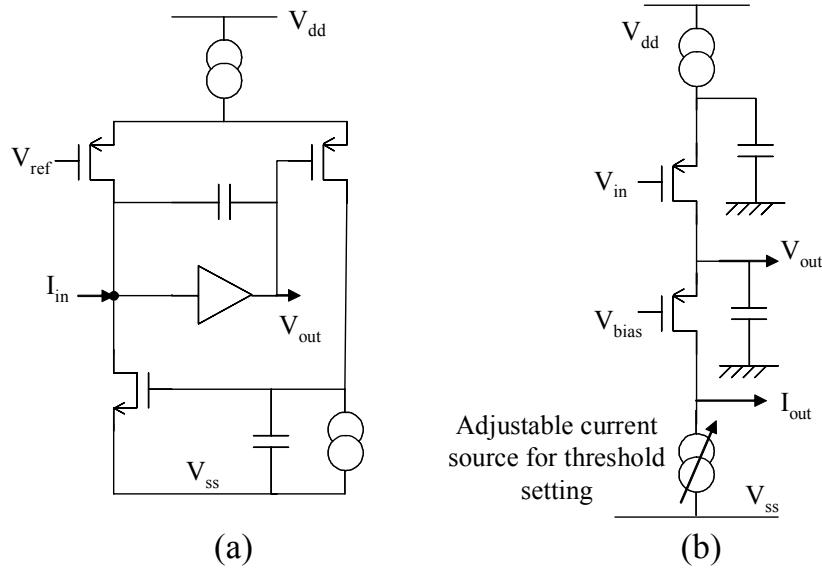

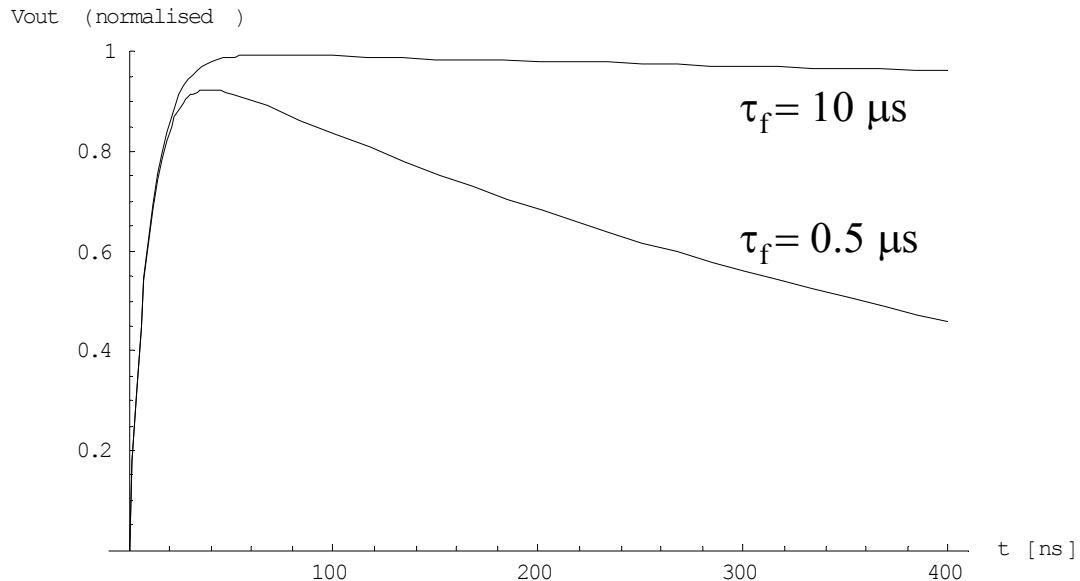

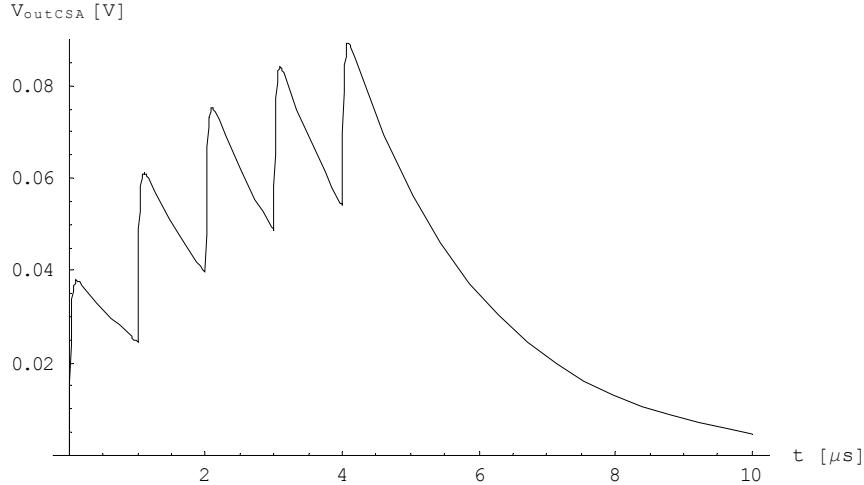

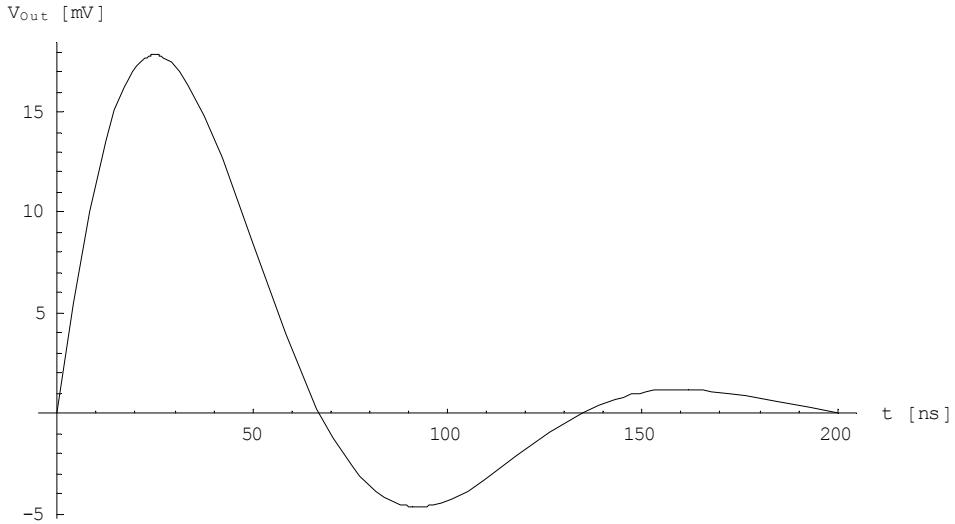

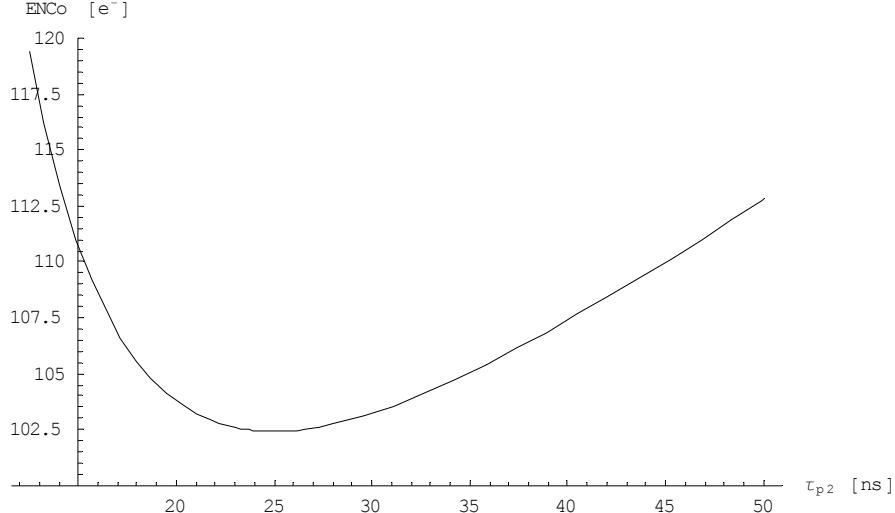

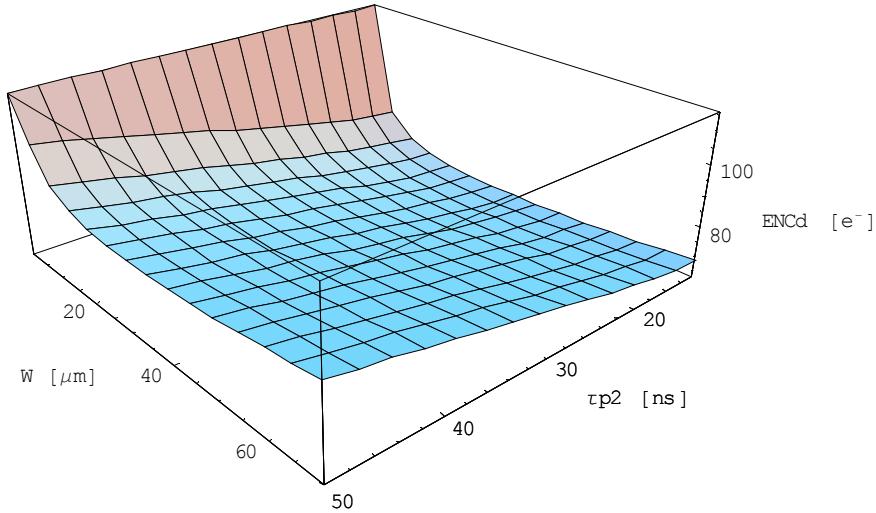

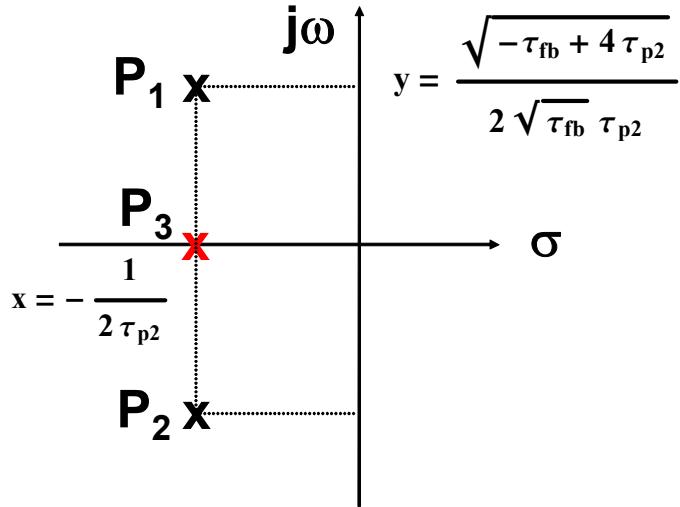

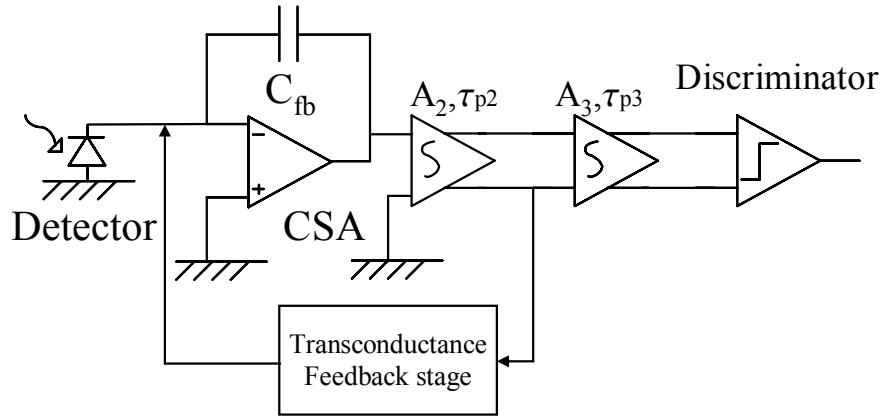

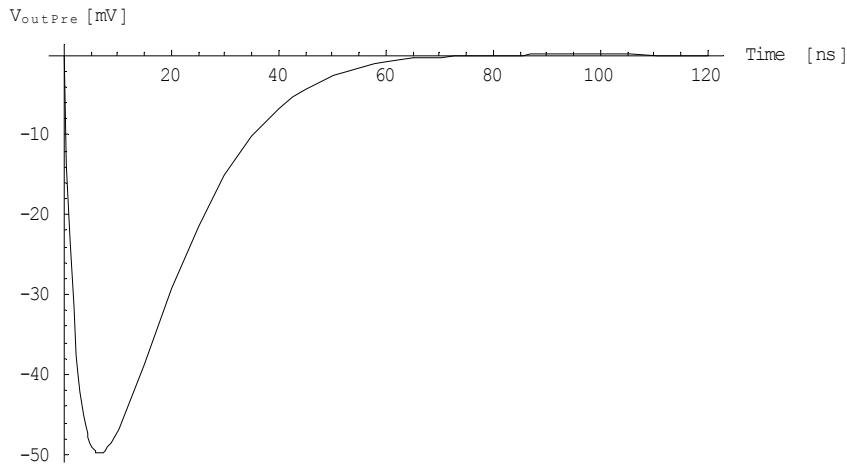

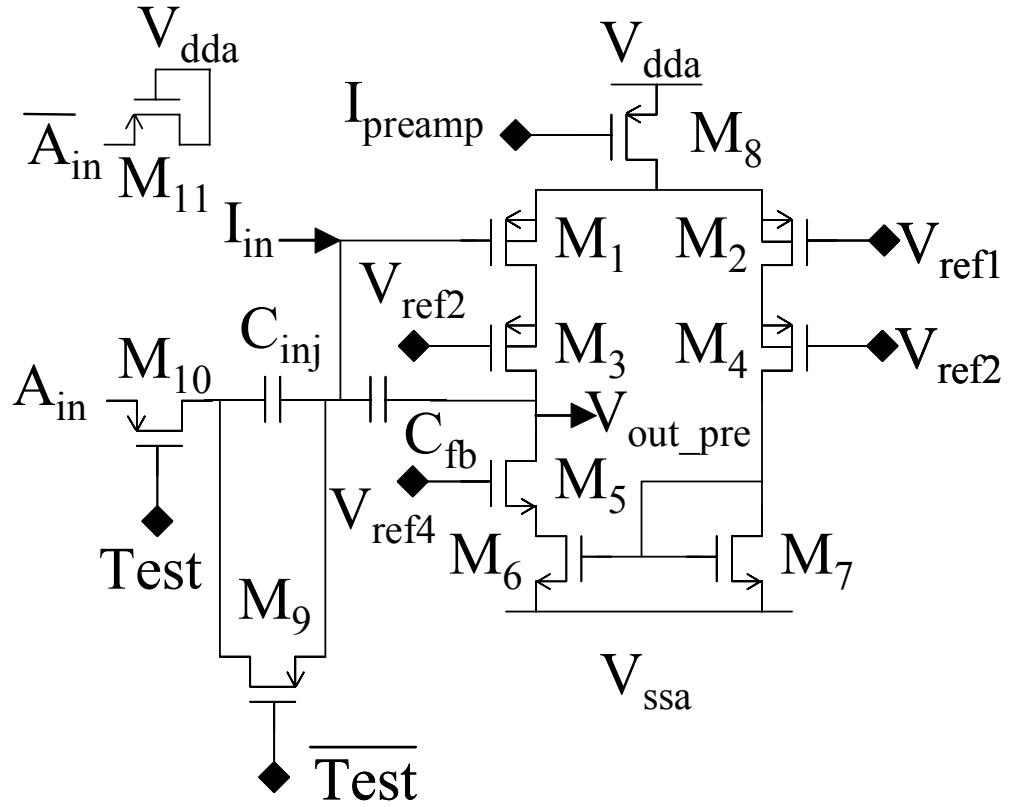

L'idée de base est qu'un système à pôles complexes peut avoir un retour à l'origine plus rapide qu'un système ayant des pôles réels. La proposition est que l'amplificateur de charge CSA soit suivi d'un étage simple (avec un gain en continu, A) ayant un pôle avec une constante de temps  $\tau_{p2}$ , et qu'un courant de contreréaction soit appliqué à l'amplificateur par un étage de contreréaction de transconductance  $g_{mf}$ . En choisissant correctement  $\tau_{p2}$ , A et  $g_{mf}$  il est possible de faire en sorte que les pôles soient complexes conjugués et de choisir la valeur de leurs composantes réelles et imaginaires. Des calculs doivent être effectués pour étudier la possibilité de réaliser les performances du système en termes de bruit, de retour à l'origine, de consommation et de surface occupée pour réaliser le circuit. Comme dans notre architecture aucune résistance n'est présente en parallèle avec la capacité de contreréaction, un élément de circuit a été conçu pour absorber le courant de fuite du détecteur, sans interférer avec le comportement à haute fréquence de l'étage d'entrée. Le circuit compense également le décalage (offset) présent à la sortie de l'étage de mise en forme.

Plusieurs éléments indiquent la possibilité d'amélioration du système à deux pôles. D'abord la forme de l'impulsion de sortie présente un rebond qui n'est pas souhaitable. Le retour à l'origine peut être amélioré, le gain doit aussi être augmenté d'un facteur environ 10; pour cela il sera plus adéquat de le réaliser dans un étage suivant pour éviter d'avoir un gain

trop élevé sur l'étage d'entrée. En outre pour ce qui a trait au bruit, les performances sont comparables à celles obtenues dans la mise en forme semi gaussienne, avec une contribution dominante du de bruit de grenaille (shot noise) qui pourrait être réduite. Pour cette raison nous avons essayé d'améliorer l'étage d'entrée en nous orientant vers à un circuit amplificateur et de mise en forme à trois pôles.

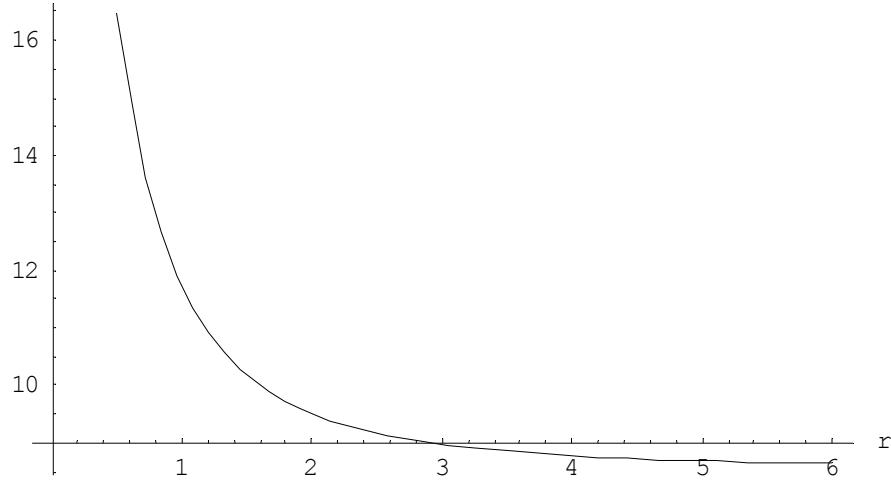

Intuitivement, la partie réelle des pôles (dans le plan s) représente la décroissance exponentielle de l'impulsion de sortie, et est dominée par le pôle le plus lent. Si tous les pôles ont la même composante réelle, aucun ne domine le temps de réponse et ceci devrait raccourcir le retour à l'origine du système. Ohkawa et ses collègues proposent un rapport optimum de 1.1 entre le pôle réel et la partie imaginaire des deux pôles complexes. En outre, si l'on prend trois pôles ayant la même composante réelle, cela simplifie considérablement les calculs, de sorte qu'ils peuvent être effectués analytiquement. Pour toutes ces raisons nous avons décidé d'analyser la configuration avec trois pôles alignés sur une droite. Toute l'analyse exécutée pour le système à deux pôles conjugués a été refaite pour un système à trois pôles, cette dernière configuration donnant de meilleures performances en ce qui concerne tous les paramètres du circuit.

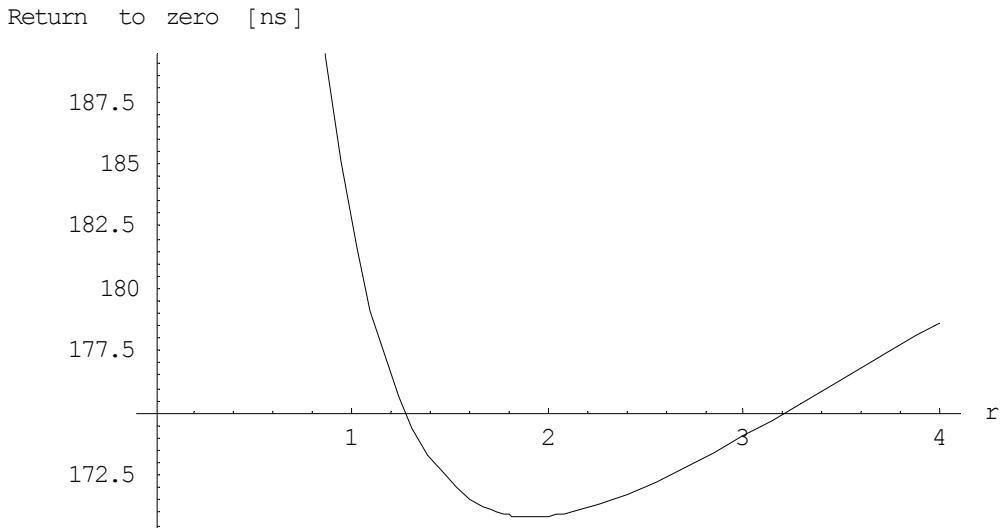

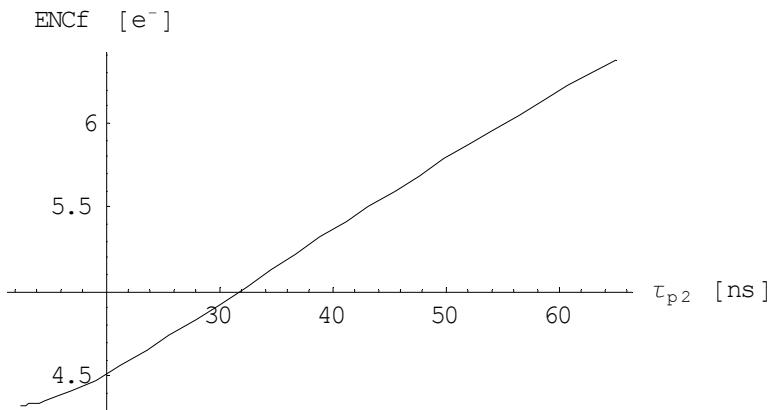

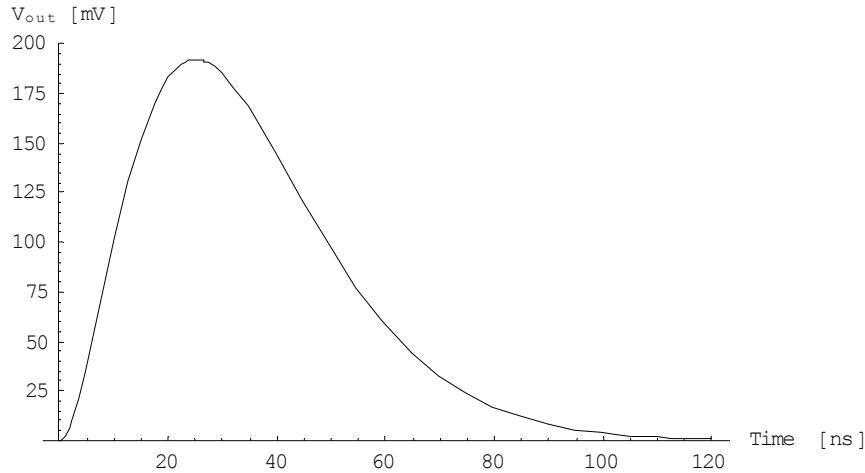

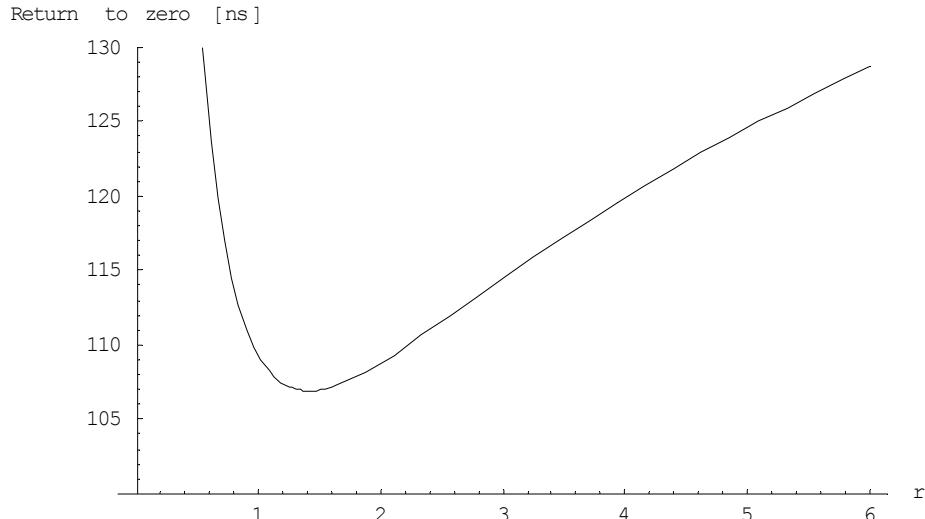

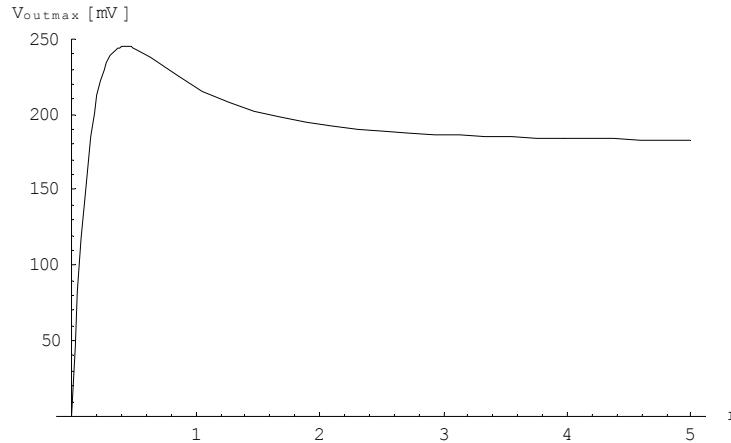

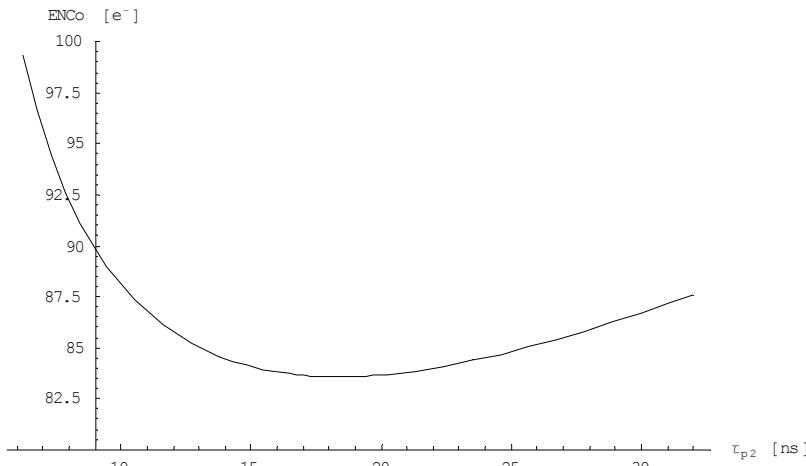

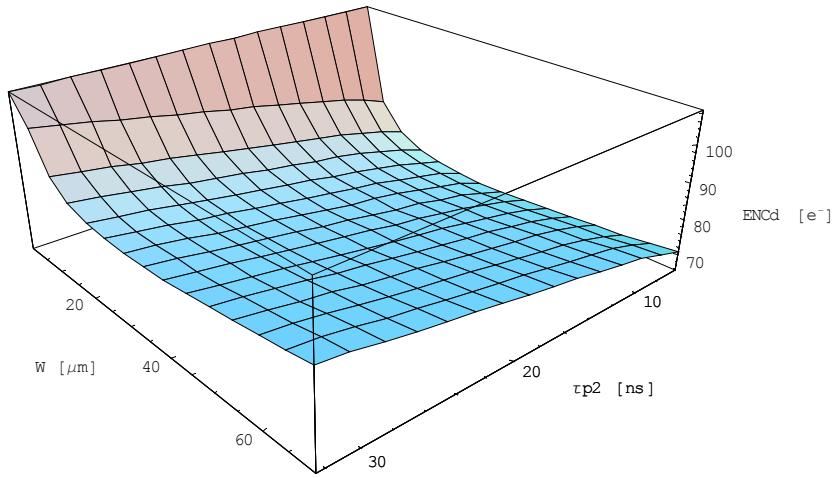

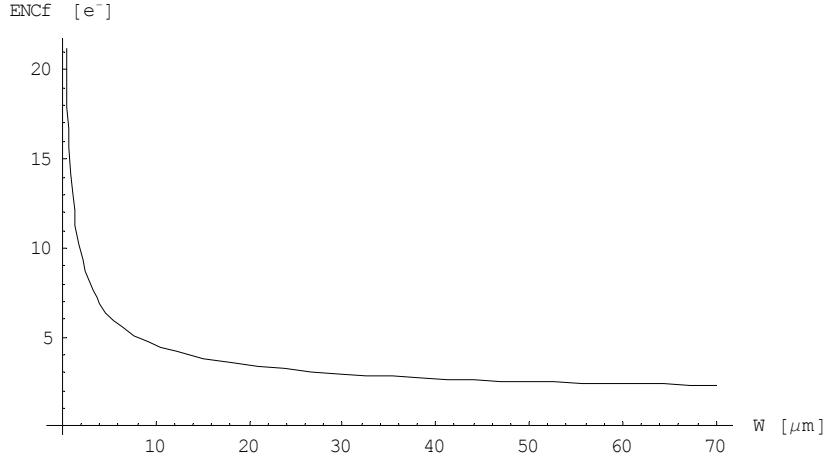

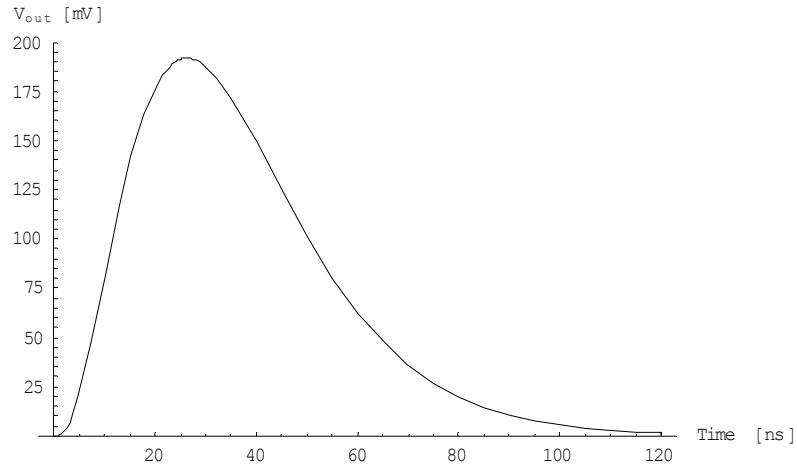

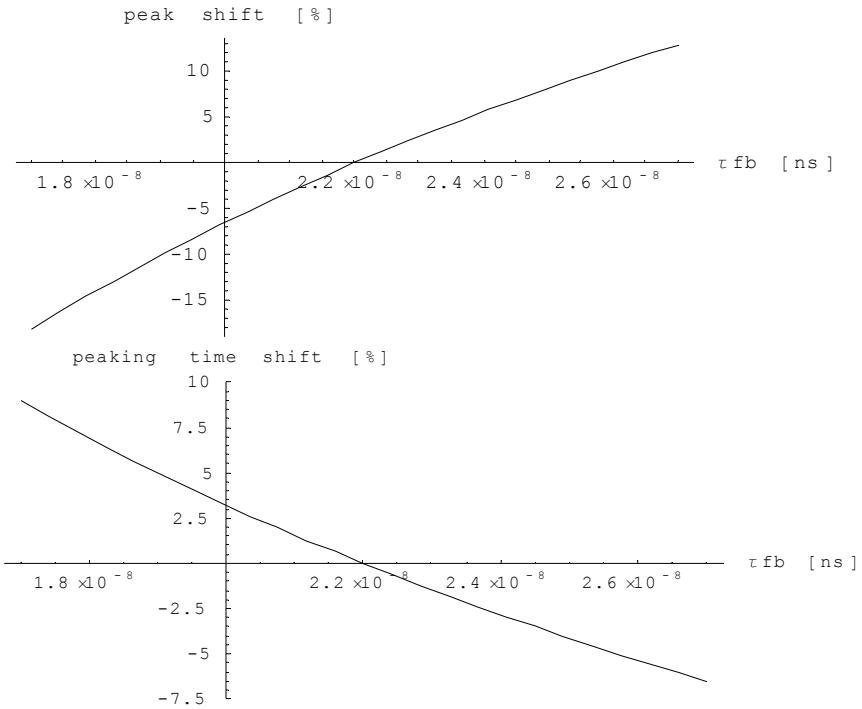

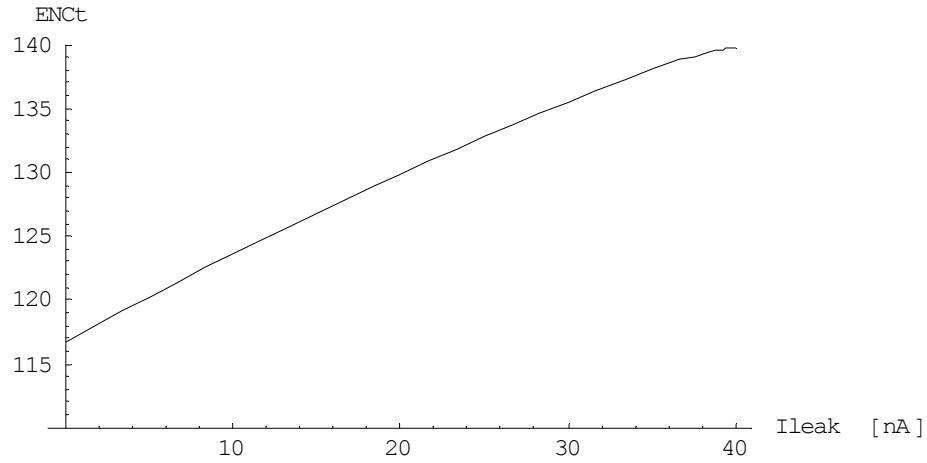

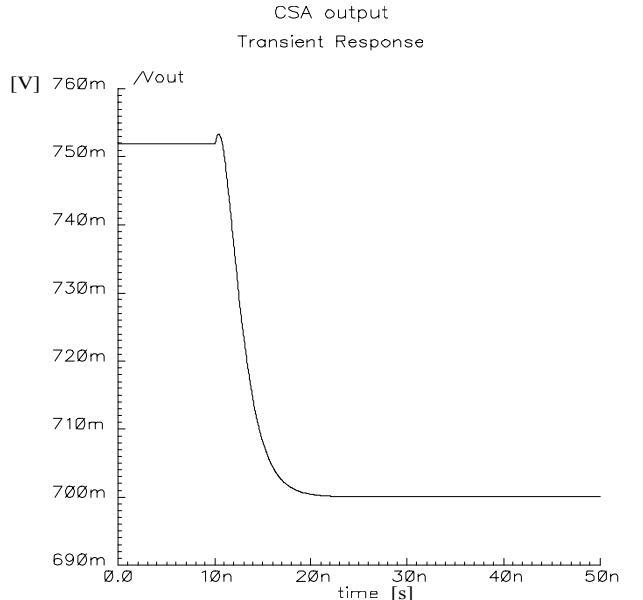

Une analyse plus réaliste a été conduite en tenant compte du temps de montée du préamplificateur. Le calcul du signal de sortie du système à quatre pôles pour une charge d'entrée  $Q_{in} = 5000 e^-$  montre un maximum de 192 mV à 26 ns, alors que le retour à l'origine à 1% intervient après 114 ns. Le préamplificateur a lui même un retour très rapide à l'origine, environ 65 ns (à 1%). Le bruit électronique total est de  $ENC_T = 117$  électrons rms.

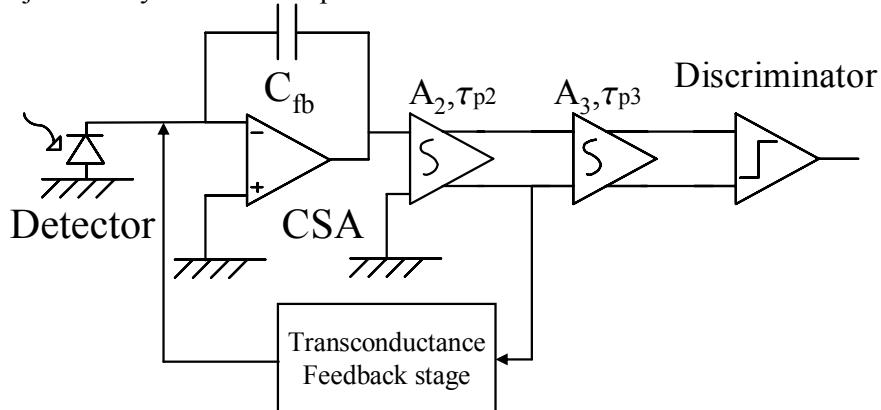

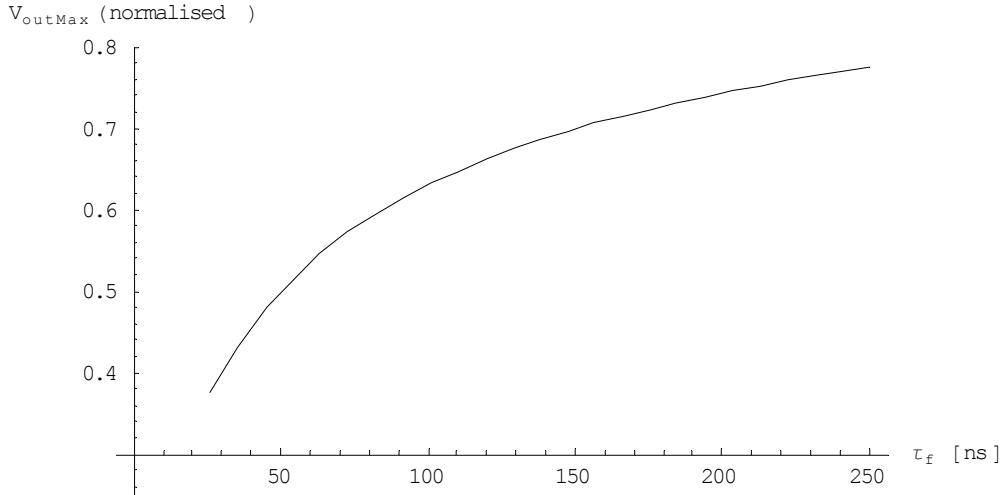

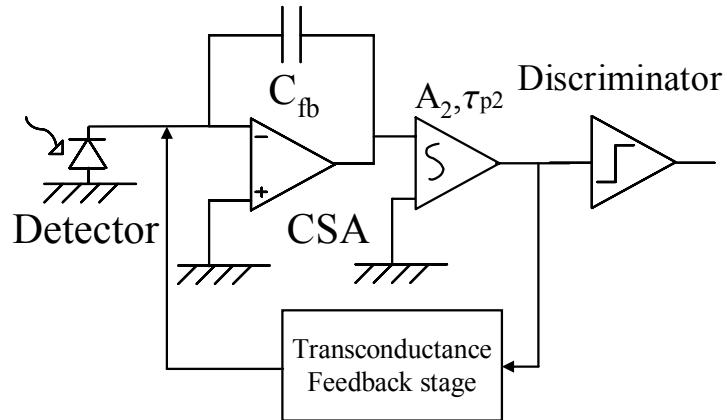

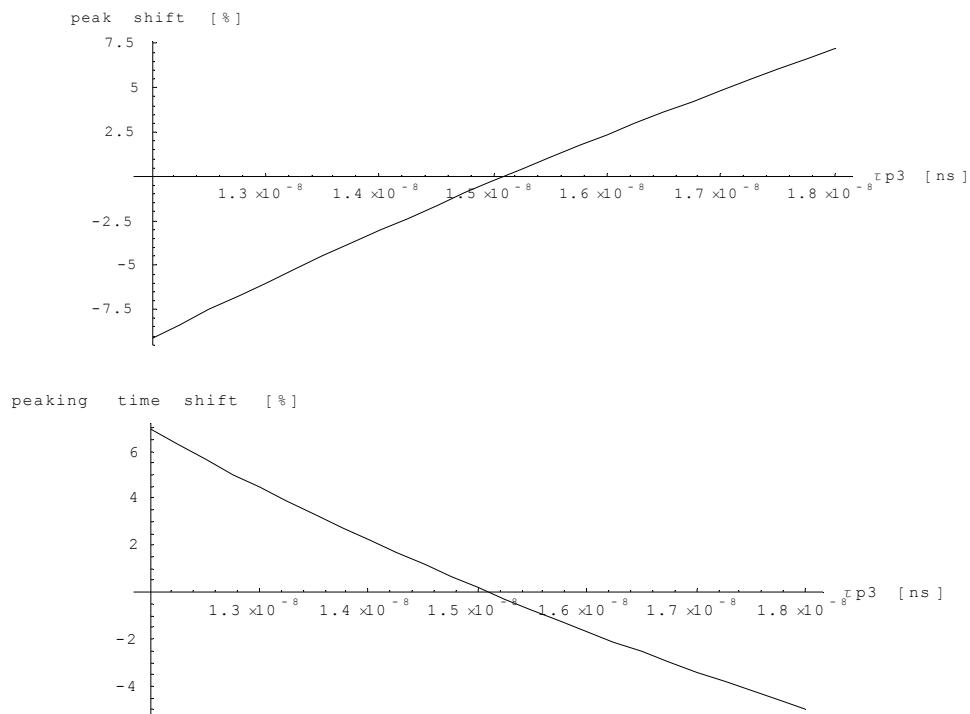

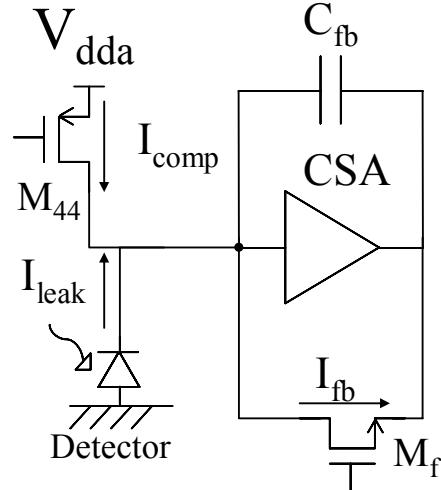

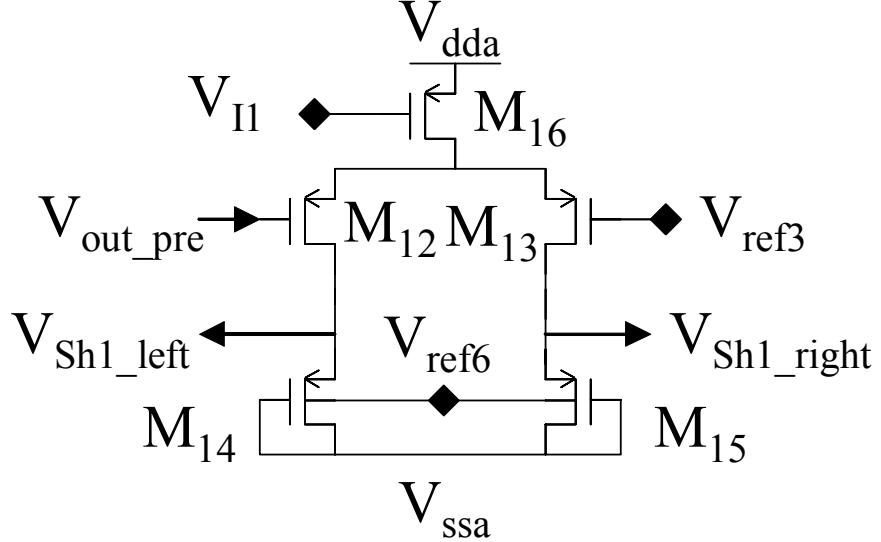

L'analyse détaillée du comportement de tous les étages qui composent le circuit d'entrée est présentée, avec les résultats de simulation, qui suivent de près les résultats donnés par l'analyse théorique. Un diagramme simplifié du schéma retenu pour mettre en application le système à trois pôles est montré sur la figure 1. Un étage qui réalise le pôle réel  $\tau_{p3}$  et un gain  $A_3$  est ajouté au système à deux pôles.

Figure 1: Schéma simplifié du système à trois pôles; un étage qui réalise un le pôle réel  $\tau_{p3}$  et un gain  $A_3$  est ajouté au système à deux pôles.

Les mesures faites sur les circuits de test ont montré clairement que le minimum du seuil de détection du signal et la performance en bruit sont dominés principalement par l'interférence numérique-analogique. Dans la nouvelle conception cette question a été abordée en priorité: par exemple, l'amplificateur de charge a été conçu avec une entrée différentielle qui rejette le bruit de mode commun (comme le bruit de substrat). D'ailleurs il est réalisé avec des transistors d'entrée canal-p, pour pouvoir être en mesure de court-circuiter le caisson du transistor avec la source et ainsi éviter l'injection de bruit à travers la capacité caisson-grille. Pour la même raison, tous les autres étages dans la chaîne d'entrée sont différentiels. Le système a été également optimisé pour réduire au minimum le couplage capacitif de pixel à pixel (aucune impulsion parasite due à l'interférence n'est observée dans les simulations jusqu'à une charge d'entrée de 55000 e<sup>-</sup> pour un seuil à 2300 e<sup>-</sup>), et pour récupérer rapidement après un signal d'entrée très grand. En effet, le système est prêt en environ 200 ns à traiter une autre impulsion, après avoir reçu une charge d'entrée de 50000 e<sup>-</sup>, pour un seuil de détection d'environ 2300 e<sup>-</sup>. Dans ce cas la composante lente de signal excentre légèrement le seuil; 50000 e<sup>-</sup> est la charge la plus élevée prévue dans l'expérience LHCb). L'étage d'entrée a été conçu pour que l'impact d'une variation de la température soit négligeable; une attention particulière a été aussi apportée au contrôle de la phase sur les boucles de contre réaction (72° pour la boucle à haute fréquence, et 82° pour la boucle de basse fréquence) et tout a été fait pour réduire l'injection de bruit par les lignes d'alimentation.

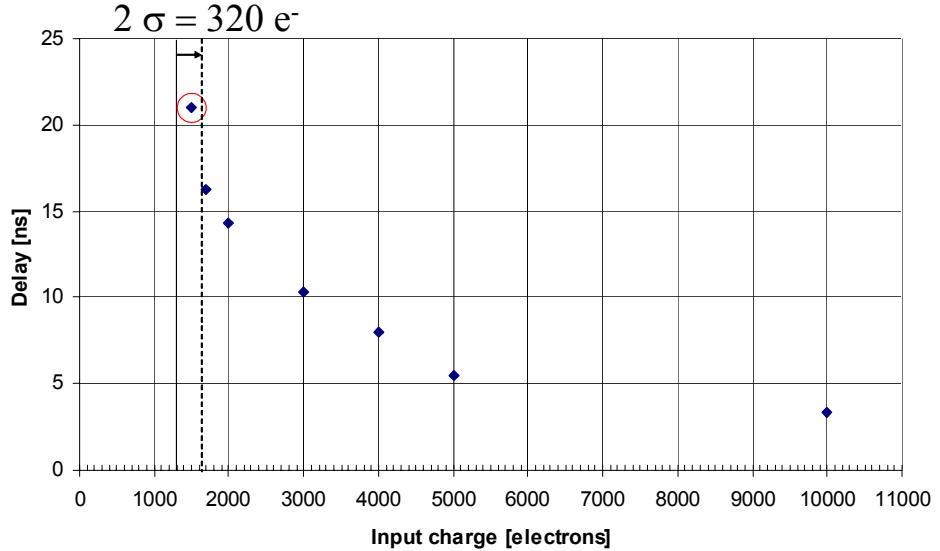

Le discriminateur, qui compare le signal analogique produit par l'étage d'entrée à un seuil global et produit une impulsion numérique si le signal est plus haut que le seuil, a été conçu pour être basse puissance. En outre, il doit réduire au minimum la différence de temps de réponse dû à des impulsions d'entrée d'amplitudes très différentes («time walk»). Le «time walk» à 20 ns a été simulé, et il est meilleur que 140 électrons.

La dispersion calculée du seuil (par rapport au préamplificateur d'entrée) est de 70 e<sup>-</sup> rms, mais un circuit de correction a été ajouté dans le discriminateur pour réduire cette dispersion au cas elle serait plus forte que prévu.

Une description de la partie numérique du circuit et des circuits périphériques est donnée dans les dernières sections, de même que quelques considérations sur l'architecture physique, expliquant quelques stratégies importantes de placement des éléments pour améliorer les performances du circuit. Le composant a été envoyé à la fabrication, puis testé intensivement, d'abord non relié à un détecteur, puis assemblé pour former des «singles» et des «ladders». Les résultats expérimentaux essentiels sont présentés au **chapitre 8**.

La première version du circuit (ALICE1LHCb) a montré une limitation de la fréquence d'horloge maximum utilisable (15-18 Méghertz); cela a conduit à la mise au point d'une deuxième version du circuit (LHCbpix1) pour l'expérience LHCb seulement, qui fonctionne avec une horloge de 40 Méghertz. Un problème avec le Convertisseur Numérique Analogique (CNA), a été résolu par l'augmentation de la tension d'alimentation de 1.6V à

1.8V et par une séquence appropriée des opérations de test pour la puce ALICE1LHCb. Il a été éliminé dans la version LHCbpix1.

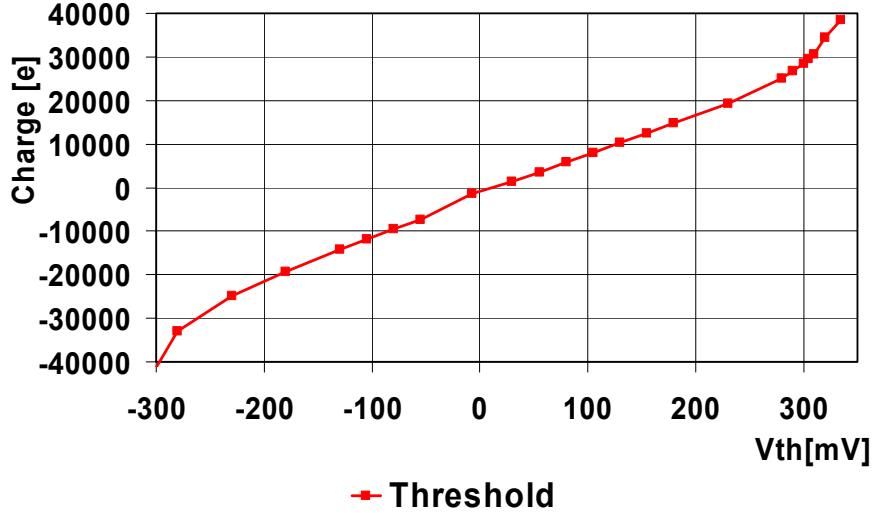

Des structures de test sont présentes sur le circuit, pour simuler l'injection de charge lorsque la puce n'est pas encore connectée avec un senseur. Une différence de tension connue  $V_{in}$  et appliquée sur une capacité de test  $C_{in}$ , ce qui se traduit par une charge d'entrée  $Q_{in} = C_{in} V_{in}$ .

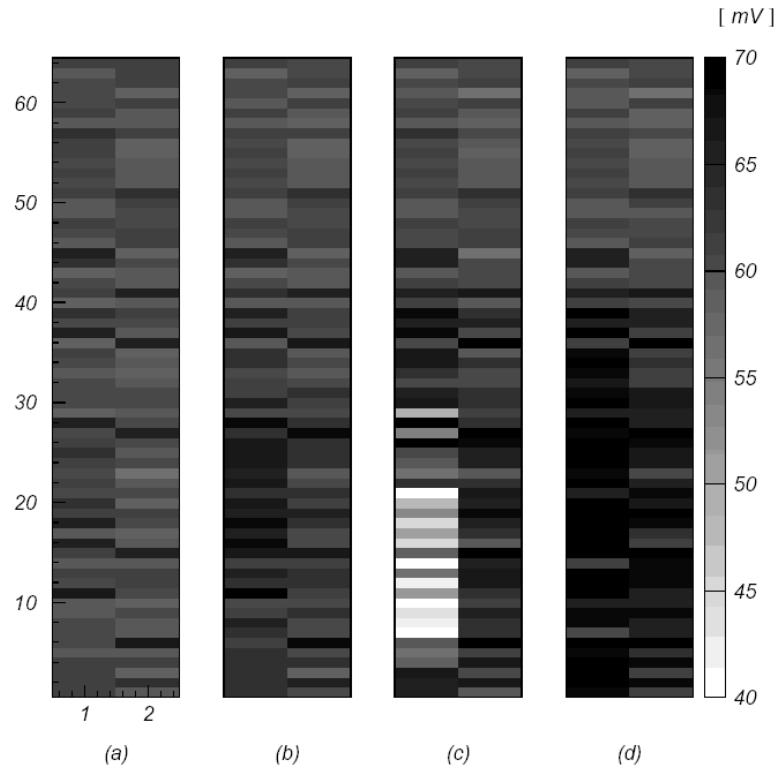

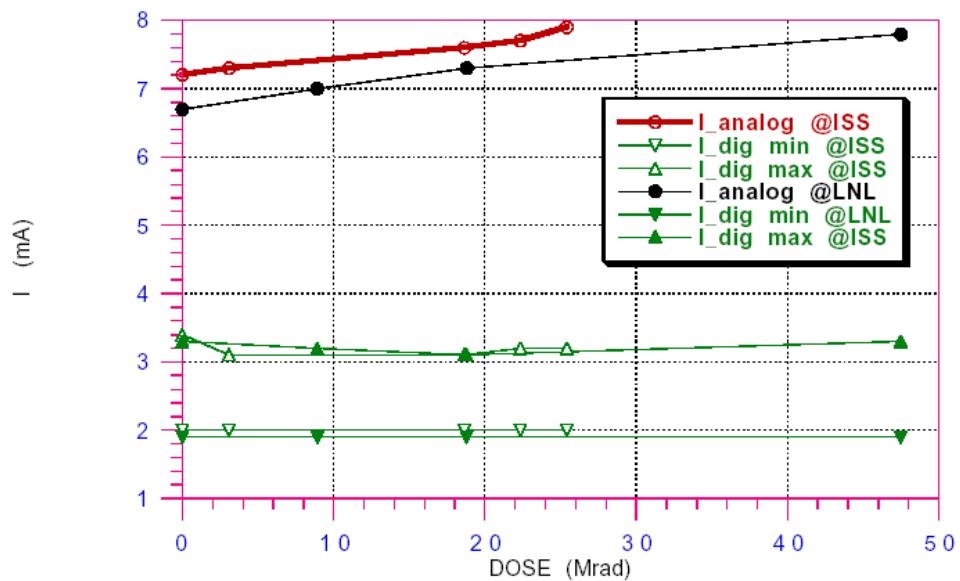

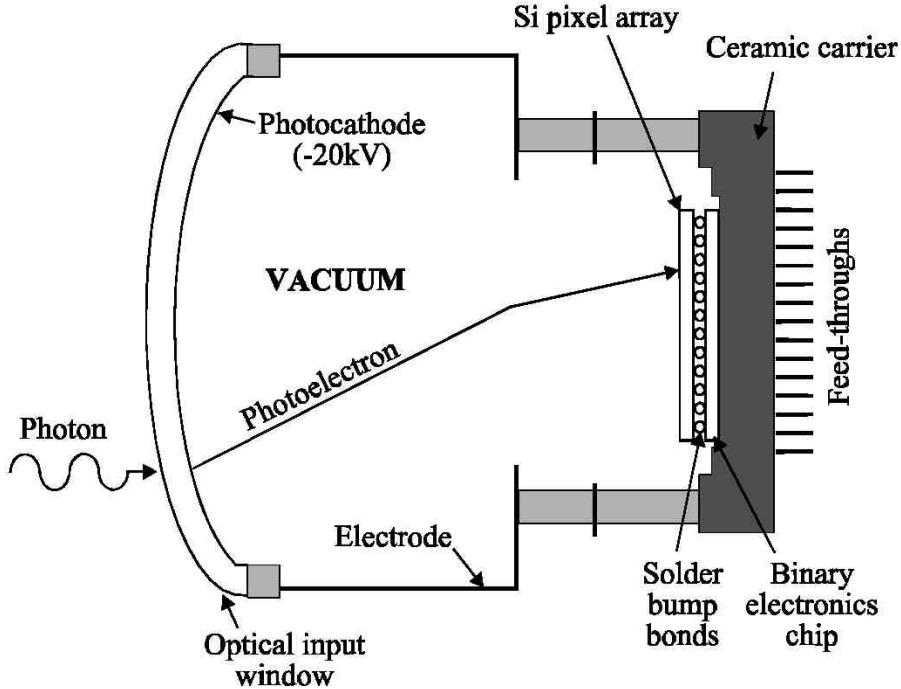

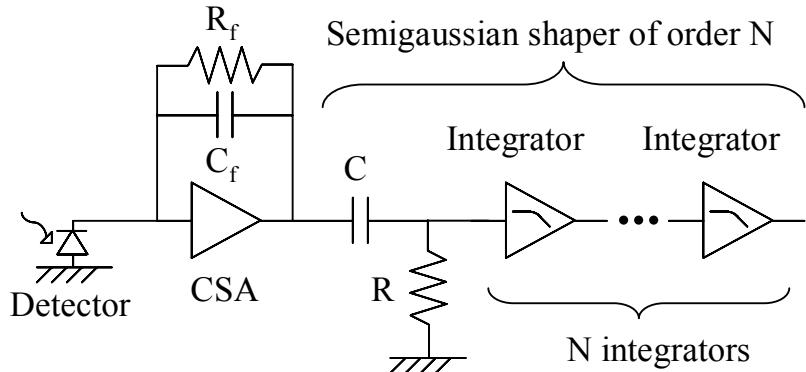

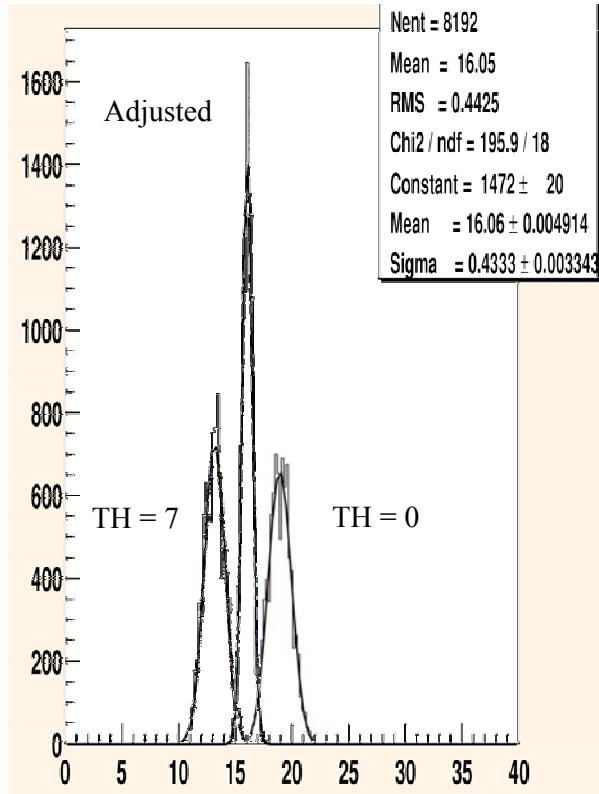

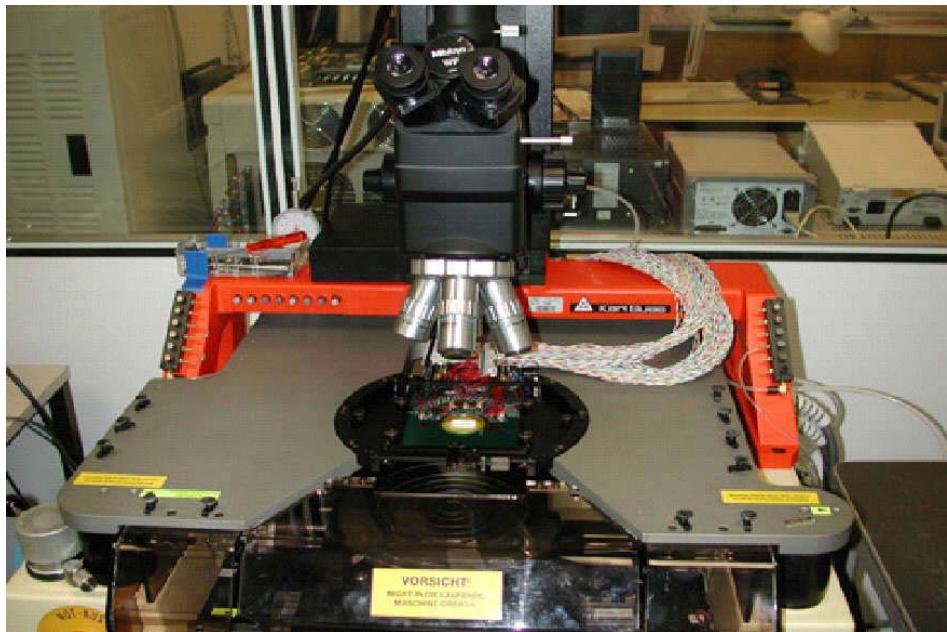

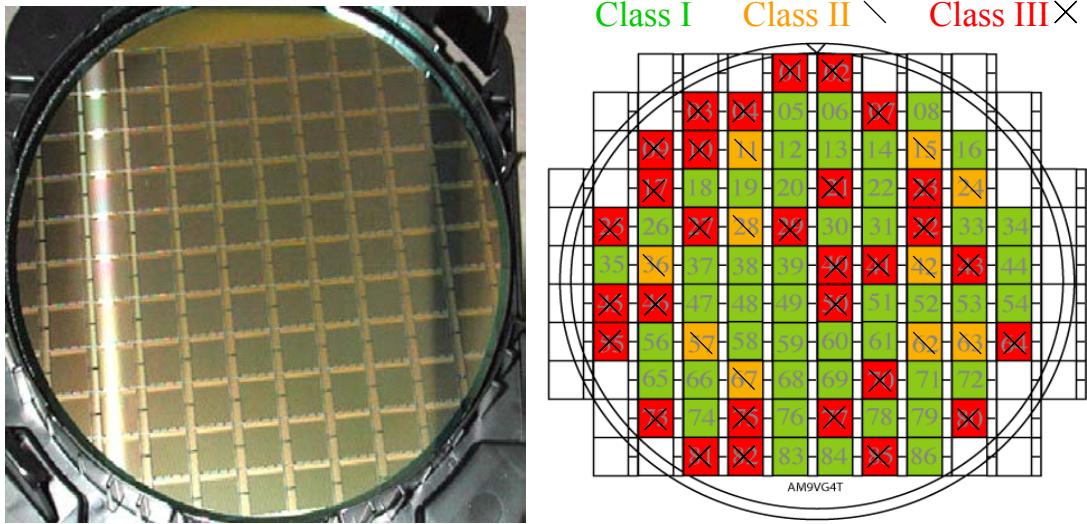

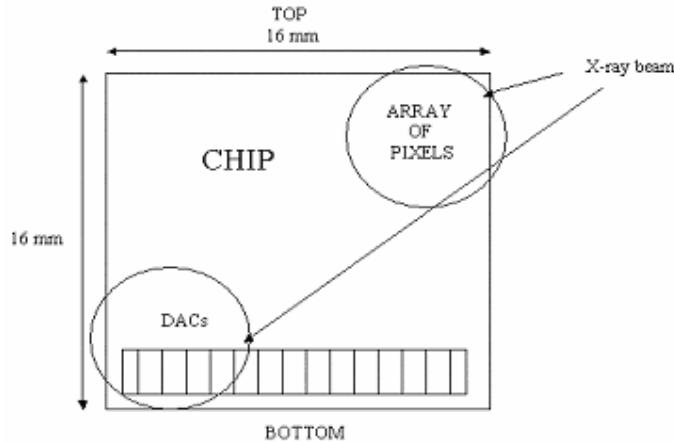

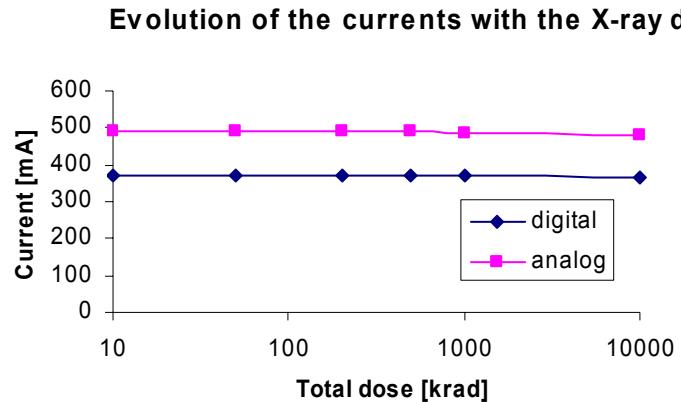

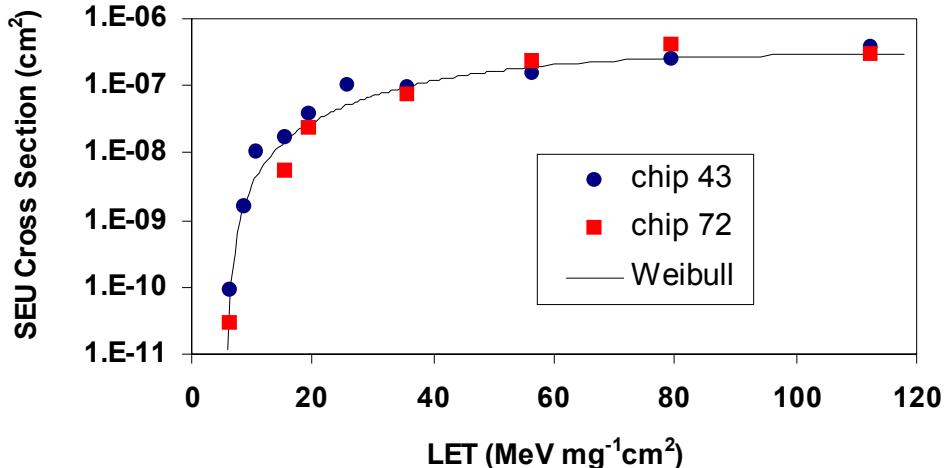

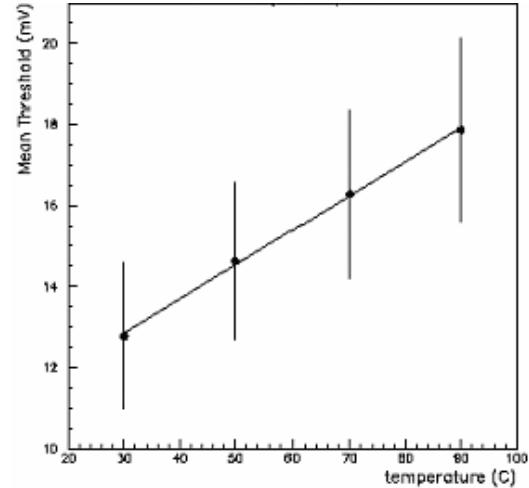

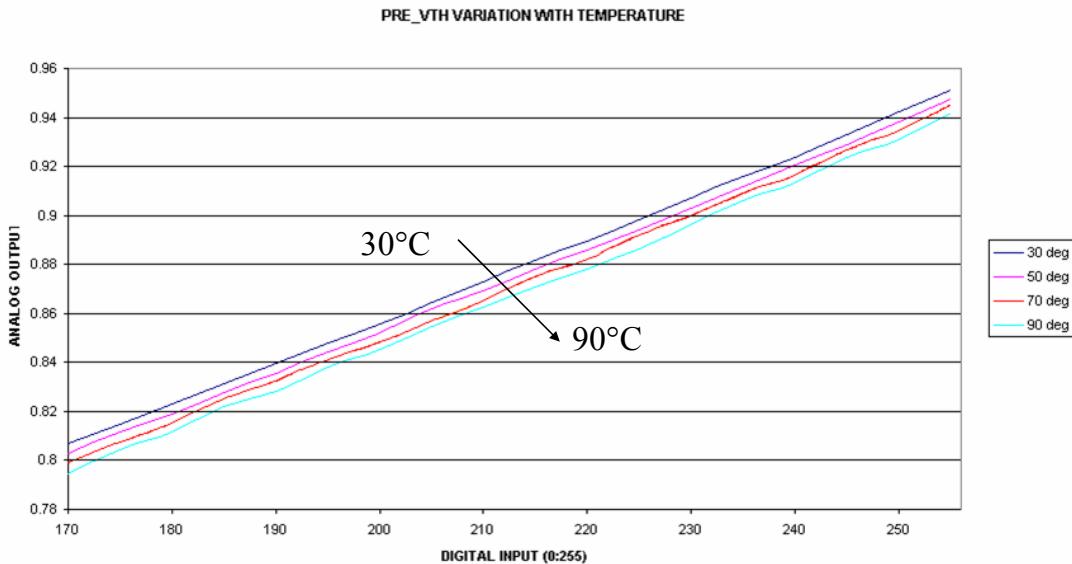

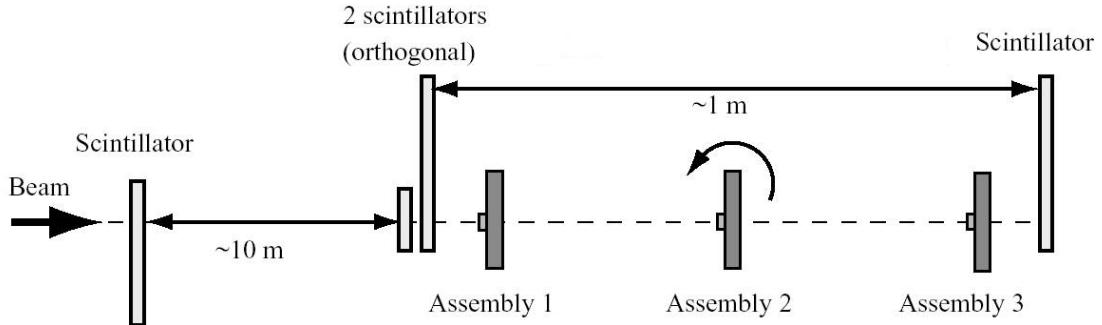

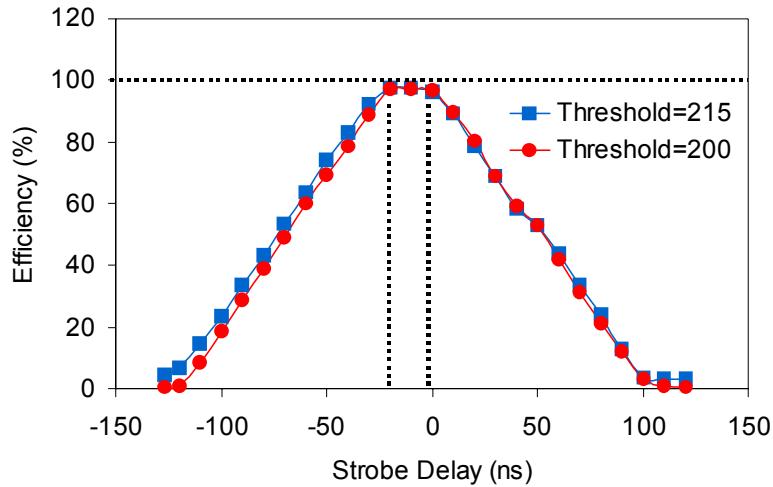

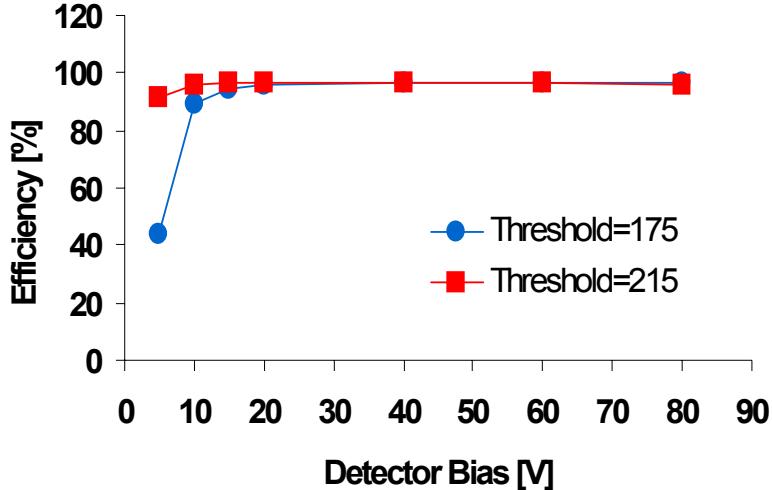

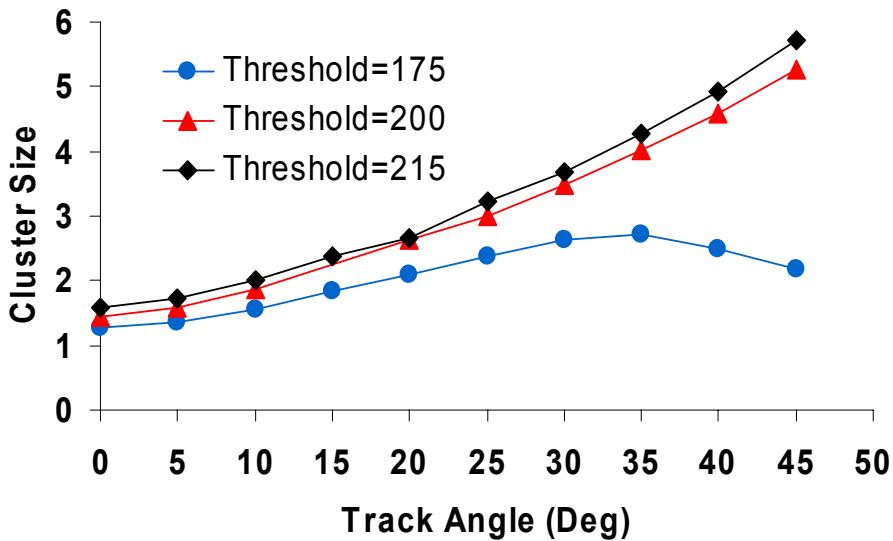

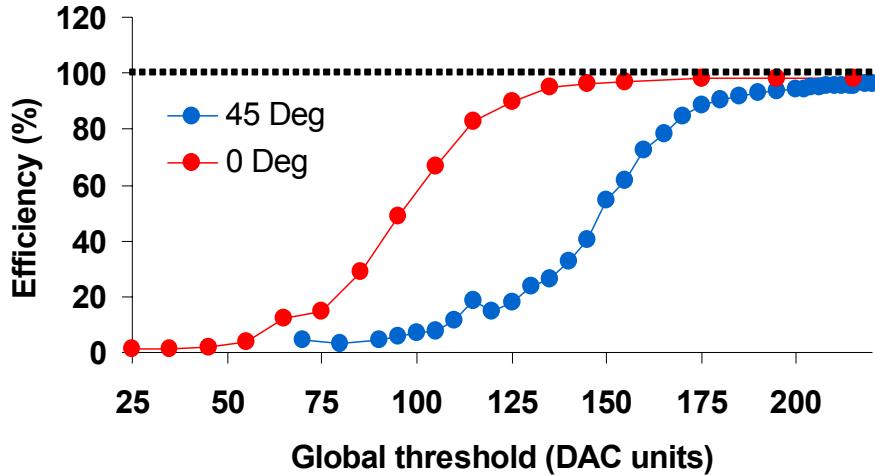

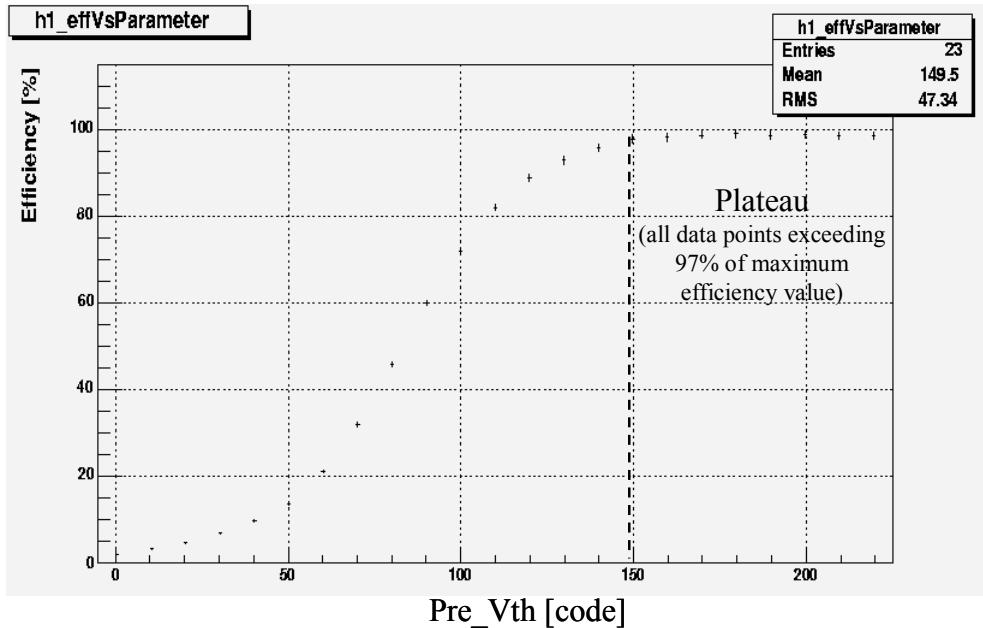

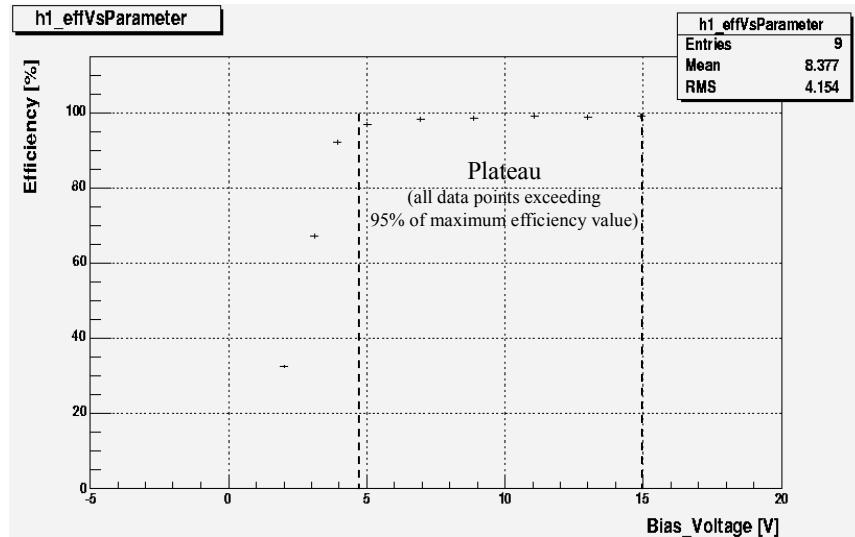

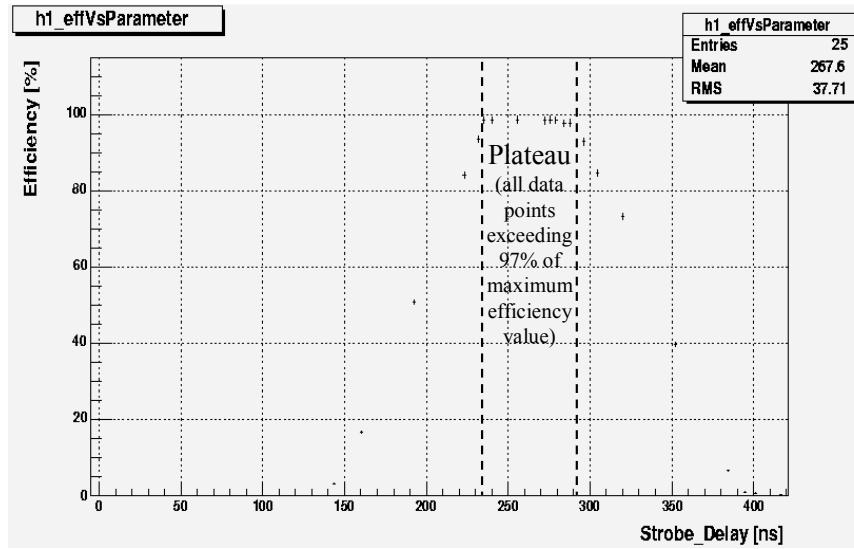

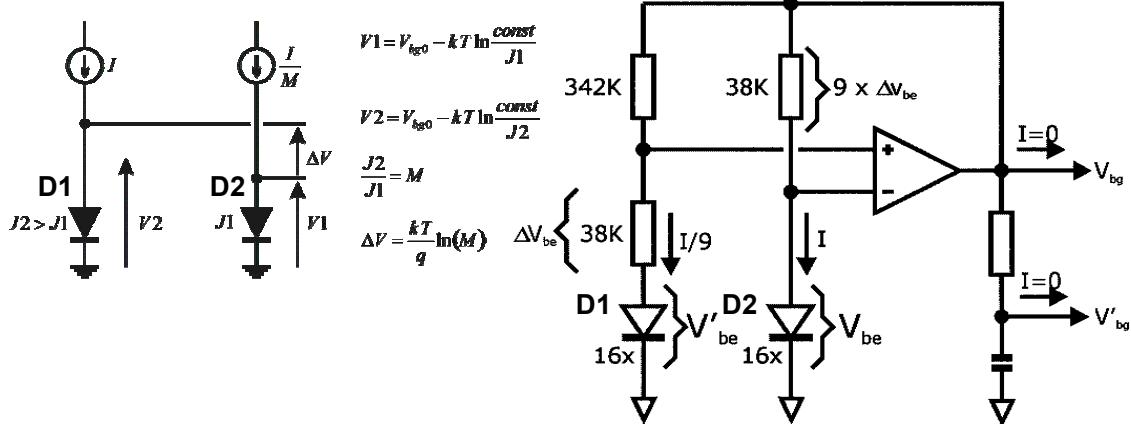

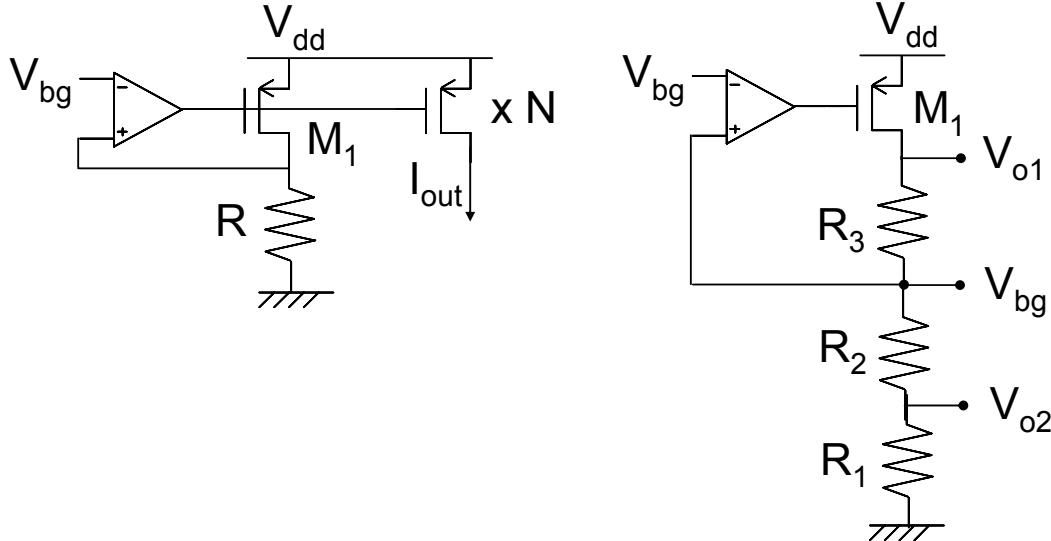

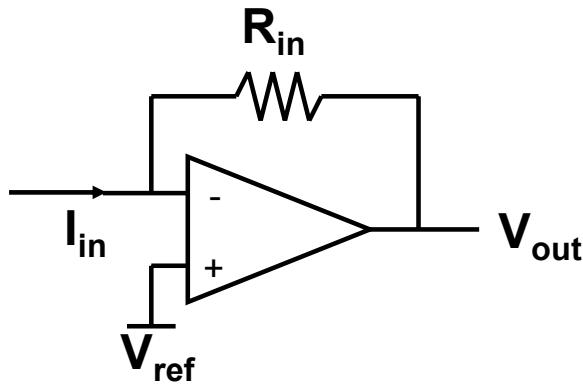

La calibration du circuit mène à la conclusion que  $V_{in} = 1$  mV correspond à  $Q_{in} = 100$  e<sup>-</sup> pour ce qui concerne les tests faits sur LHCbpix1. En raison d'un problème dans l'uniformité du circuit d'injection de charge de test sur le circuit ALICE1LHCb, il n'est pas aussi facile d'estimer le facteur de conversion tension/charge pour le circuit ALICE1LHCb; on a estimé que la valeur moyenne sur le circuit est d'environ 0.5-0.65 mV/100 e<sup>-</sup>.