# Chemical Reaction Simulator on Quantum Computers by First Quantization (II)—Basic Treatment: Implementation

Hideo Takahashi,\* Tatsuya Tomaru, Toshiyuki Hirano, Saisei Tahara, and Fumitoshi Sato\*

Cite This: *J. Chem. Theory Comput.* 2024, 20, 9290–9320

Read Online

ACCESS |

Metrics & More

Article Recommendations

**ABSTRACT:** Chemical simulation is a key application area that can leverage the power of quantum computers. A chemical simulator that implements a grid-based first quantization method has promising characteristics, but an implementation fully in quantum circuits seems to have not been published. Here, we present “crsQ” (chemical reaction simulator Q), which is a quantum circuit generator that generates such a chemical simulator. The generated simulator is capable of antisymmetrization of the initial wave function and time-evolution of the wave function based on the Suzuki–Trotter decomposition. The potential energy term of the Hamiltonian is implemented using arithmetic gates, such as adders, subtractors, multipliers, dividers, and square roots. Circuit diagrams and output samples are shown. The number of qubits in the circuits scales on the order of  $O(\eta \log \eta)$ , where  $\eta$  is the number of electrons. Each component of the generated circuit was verified in unit tests. Along with this development, we designed frameworks to ease the development of large-scale circuits, namely, a temporary qubit allocation framework and an abstract syntax tree framework for arithmetic formulas. These frameworks are expected to be useful in large-scale quantum circuit generators.

minimal first quantization Hamiltonian simulation written on a quantum computer SDK

## 1. INTRODUCTION

This study is the second part of a multipart report on the development of a quantum-computer-based simulator for chemical reactions. While the first part describes the simulator circuit design theoretically,<sup>1</sup> this second part describes the implementation of circuits on a quantum computer software development kit (SDK). The simulator implements a grid-based first-quantization method.<sup>1–4</sup> Such a simulator consists of a circuit for preparing the initial state of the wave function, a circuit for evolving the wave function in time, and a circuit for measurement. The time evolution circuit performs the Hamiltonian simulation by using arithmetic operations implemented as quantum circuits that operate on the values in a superposition stored in the qubits. Despite the numerous theoretical studies in the literature, a software implementation that includes all of these elements does not seem to have been published yet. In particular, the preceding studies on chemical simulators running on a quantum computer used simple circuits that lacked the elements needed for handling chemical reactions<sup>2,5</sup> or used a quantum computer simulator equipped with a “bespoke” (artificial) quantum gate that calculated a significant portion of the simulation by using classical computer code as if such a function were available as a built-in gate.<sup>6</sup> Such a simplification or optimization was chosen in order to make the circuits runnable on quantum computer simulators. As a result, the resulting chemical reaction simulator is not fully implemented in terms of the (actual) quantum gates.

Researchers could benefit from a complete implementation of quantum circuits in multiple ways: it could be used as packaged application software, a learning resource, a basis for implementing improvements, or as a basis for comparing improved versions of the circuits. The goal of this study was thus to combine the essential elements of the previous studies and describe and implement the overall circuit of a minimum essential chemical reaction simulator. The elements comprising the simulator are described in a separate paper, which is the first part of this report.<sup>1</sup> In this second part, we describe the implementation aspects of the circuits on Qiskit, a quantum computer SDK from IBM.<sup>7</sup> The goal is to implement the entire simulator on Qiskit and to verify the logical correctness of its circuits by testing the components individually in unit tests. In particular, this report describes the implementation of the state preparation circuit and the time evolution circuit.

Since the hardware requirements for the generated chemical simulator circuit cannot be met with what is available today, the simulator as a whole cannot be run on existing quantum computers or quantum computer simulators. What we have

Received: June 2, 2024

Revised: August 28, 2024

Accepted: September 20, 2024

Published: October 25, 2024

implemented so far is a circuit generator program written in python<sup>8</sup> that constructs a quantum circuit of the said chemical simulator. The program uses the SDK functions to construct the circuit on a quantum computer or a quantum computer simulator. The generated simulator comprises the initial state preparation with antisymmetrization, Coulomb potential energy calculation in 1D, 2D, or 3D coordinates using arithmetic gates, and the time evolution of the wave function through the Suzuki-Trotter decomposition. The measurement circuit is left for future work. We verified the components of the circuits by inspecting the simulated state vector after running the circuits with a test input.

As a far goal, we are interested in the simulation of large molecules such as proteins. However, at this point, we were able to generate simulator circuits for a model size up to simple amino acids. In this study, we show the generated circuits for simple models in the range of one atom in one or two dimensions (Section 3.1). For the amino acids, we present the generated circuit size (Section 3.2). Based on the qubit count of the generated circuits, we formulate the qubit count (Section 6.1) and estimate the resource requirements for some proteins (Section 6.2).

Throughout this work, we encountered several programming-level issues regarding the quantum circuit generator code and devised techniques to address them. One issue was the need to avoid interface mismatches when constructing a large circuit, which involves the decomposition of it into smaller subcircuits hierarchically. The other issue relates to the provision of a higher-level programming interface for implementing basic arithmetic formulas from low-level quantum computer instructions. Both issues become more serious as the circuit becomes larger and more complex. To deal with the first issue, we devised a design pattern<sup>9</sup> (a rule for structuring programs) for subcircuit invocation that features automated allocation of temporary qubits for local variables. To deal with the second issue, we applied the idea of an abstract syntax tree (AST), which is a widely known structure for compiler programs of classical computers.<sup>10</sup> Here, a source code expression, such as “ $r = \text{sqrt}(dx \times dx + dy \times dy)$ ”, would be converted into a tree structure reflecting the order of the operations. Then, quantum instructions are generated by using the tree. The AST utilizes the said temporary qubit allocation framework whenever ancilla qubits are required by the arithmetic gates. We also implemented decimal point adjustment as a feature of the AST. The AST was used to implement the Coulomb potential energy term of the Hamiltonian, and we confirmed that it simplified the coding task. The details of fixed-point decimal point tracking are totally hidden from the Hamiltonian calculation code by the AST, and thanks to that, its formulas can be modified easily without the need for the programmer to keep track of those details manually.

We have tested all of the described software components in bottom-up unit tests. These tests were run on the Qiskit Aer simulator,<sup>7</sup> and the test programs were organized as an automated test suite based on the Python pytest framework.<sup>11</sup> The Qiskit Aer simulator allowed us to inspect the simulated state vector, and the amplitudes of all state components of the system can be obtained. Besides the test suite, we plotted the circuit output for the selected input data to demonstrate the calculations performed by the components. We used only a single computer to run the simulator and have not pursued any simulations on clusters. Doubling the memory size for a quantum computer simulator adds only one simulated qubit.

Using a cluster for a quantum computer simulator would add several simulated qubits compared with those of a single computer, but currently, we do not have a strong need for those few extra qubits considering the significant cost increase.

The remainder of this study is structured as follows: Section 2 outlines the formulation of the simulator. The representation of wave functions and how they are processed are described. Section 3 describes selected samples of the simulator circuits. It starts by describing the overall circuit before detailing the subcircuits. A large portion of the subcircuits consists of arithmetic gates, such as adders and multipliers. Those gates are described in Appendix A. Section 4 discusses implementation issues. The overall simulator is composed of four components, and each component is described. Section 5 explains how the testing was performed, while Section 6 discusses the measurement of the circuit size of the current implementation and potential areas of improvement. Section 7 summarizes this work.

## 2. FORMULATION OF THE CHEMICAL REACTION SIMULATOR

In this section, we briefly describe the model and algorithm that we implemented. A detailed description can be found in the preceding study.<sup>1</sup>

**2.1. Representation of the Wave Function.** The wave function is stored in quantum registers that represent the discretized coordinates of the particles. For each electron or nucleus,  $n$  qubits are used to store the coordinates of all dimensions. The coordinates of each dimension are stored in a quantum register consisting of  $n_1$  qubits. We will describe this formulation for a 3-D model, but we will also describe simplified 2-D or 1-D models; in all cases,  $n$  represents the total number of qubits for all dimensions. Therefore, in the 2-D and 3-D models,  $n$  is  $2n_1$  and  $3n_1$ , respectively. The integer values in these registers are transformed from discretized positional coordinates into momentum coordinates (or vice versa) by using an inverse Fourier (or Fourier) transform. In the positional representation, or “ $q$ -space”, we define the simulated space to be a cube of size  $L \times L \times L$ . This space is discretized into  $2^{n_1}$  segments for each dimension with a unit of  $\delta q = L/2^{n_1}$ . The coordinates of an electron identified by an index  $i$  are denoted as  $q_i$ .

The discretized signed integer coordinates  $(x_i, y_i, z_i)$  are defined as

$$(x_i, y_i, z_i) = \frac{\mathbf{q}_i}{\delta q} \quad (1)$$

For atom nuclei, we will use capital letters such as  $X_i$  and  $Q_i$ . Following the conventions in the chemical literature, the variable  $Z_i$  with a capital  $Z$  will be used to denote the electric charge of nucleus  $i$ , which should be easily distinguishable from the  $z$  coordinate of a nucleus by context.

The values of the positional coordinates correspond to the values of the qubits. The wave function for a system with  $\eta$  electrons and  $L_n$  nuclei is stored in the index register in the tensor product form:

$$|\Psi(t)\rangle = \sum_{q_1, \dots, q_\eta; Q_1, \dots, Q_{L_n}} \Psi(\mathbf{q}_1, \dots, \mathbf{q}_\eta; \mathbf{Q}_1, \dots, \mathbf{Q}_{L_n}; t) |x_1, y_1, z_1, \dots, x_\eta, y_\eta, z_\eta; X_1, Y_1, Z_1, \dots, X_{L_n}, Y_{L_n}, Z_{L_n}\rangle \quad (2)$$

For a wave function in the momentum representation, the contents of the coordinate registers are transformed into the momentum of the particles. The momentum of electron  $i$ , denoted by  $p_i$ , is mapped to the same coordinate qubits that were used for the spatial coordinates such that

$$(x_i, y_i, z_i) = \frac{\mathbf{p}_i}{\delta p} \quad (3)$$

where  $\delta p = 2\pi\hbar/\delta q 2^{n_i}$  is the unit value for the discretization of momentum values.

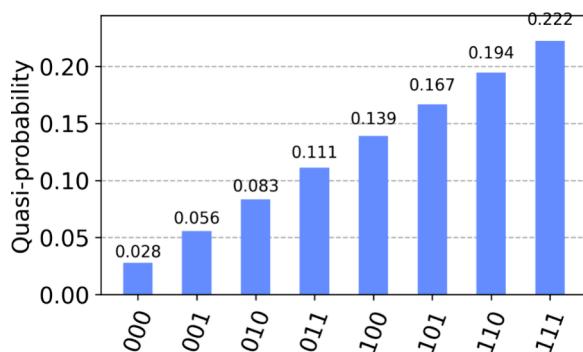

**2.2. Preparation of the Initial Wave Function.** To initialize a set of qubits of a coordinate register so that the amplitude of the qubits will follow a desired distribution defined by the wave function  $\phi_i$  provided as data, one must build a circuit to embed amplitude values to match the data.

$$|\phi_{\text{ini}}(\sigma_0)\rangle = \prod_{i=0}^{\eta-1} |\phi_i(i)\rangle = \prod_{i=0}^{\eta-1} \sum_{q_i=0}^{2^{n_i}-1} \phi_i(q_i) |q_i\rangle \quad (4)$$

Here,  $|\phi_{\text{ini}}(\sigma_0)\rangle$  is the tensor product of the orbital states  $|\phi_i\rangle$  and  $\sigma_0$  represents the sequence of electron indices  $0, 1, \dots, \eta-1$ , which means that orbital  $\phi_i$  is implemented to electron  $i$ .

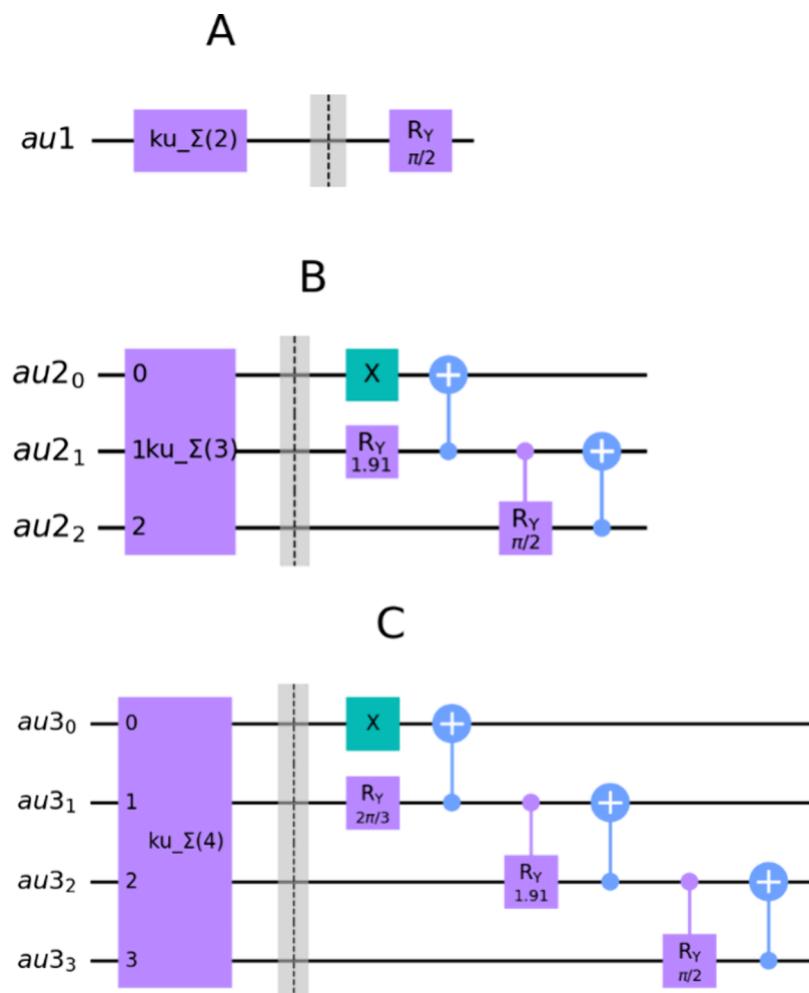

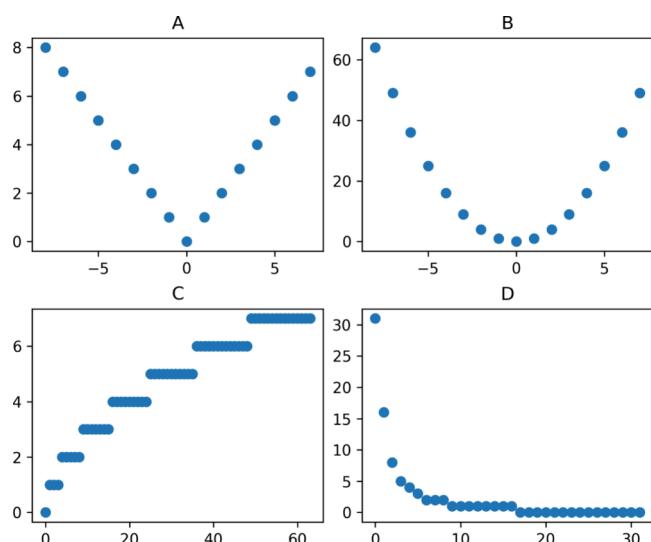

As the input for the preparation circuit, all coordinate registers are first set to  $|0\rangle$ , which means that the amplitude of  $|0\cdots 0\rangle$  is 1 and 0 for all other states. By applying the  $R_y(\theta)$  gate, the amplitude of  $|0\rangle$  can be distributed to  $|0\rangle$  and  $|1\rangle$  in a desired ratio of  $\cos(\theta/2)$ :  $\sin(\theta/2)$ . To decide the value for  $\theta$ , let  $s_1$  be the sum of squares of the amplitudes for the first half of the qubit states, i.e.,  $|00\cdots 0\rangle$  to  $|01\cdots 1\rangle$ , let  $s_2$  be the same for the second half, i.e.,  $|10\cdots 0\rangle$  to  $|11\cdots 1\rangle$ . Then,  $\theta = 2\tan^{-1}\sqrt{s_2/s_1}$ . The  $R_y(\theta)$  gate is applied to the most significant bit (MSB). This process distributes the amplitude into two states  $|00\cdots 0\rangle$  and  $|10\cdots 0\rangle$ . The next step is to further distribute the amplitude of each state into still other states; the amplitude of  $|00\cdots 0\rangle$  is distributed into  $|000\cdots 0\rangle$  and  $|010\cdots 0\rangle$ , and the amplitude of  $|10\cdots 0\rangle$  is distributed to  $|100\cdots 0\rangle$  and  $|110\cdots 0\rangle$ . This can be done with a controlled  $R_y$  gate applied to the second MSB. By repeating this step for all qubits, we prepared the amplitude of each state. For implementing the phases, a separate process of phase embedding, which mirrors the structure of amplitude embedding, follows the amplitude embedding process. This second process applies  $R_z$  gates instead of  $R_y$  gates. The corresponding circuit is shown in Figure 28 of ref 1.

**2.3. Preparation of Antisymmetric States.** After the initial wave function data are stored in the coordinate registers, the amplitudes in the registers are systematically shuffled to form the Slater determinant. We used a set of ancilla qubit registers, each labeled as  $a_k$ , to assist this process. The index  $k$  is in the range  $1\cdots\eta-1$ . These ancillae are collectively called register set  $a$ . Each value of the register set is related to a member of the permutation set  $S_\eta$  which is the set of all possible permutations of the sequence of numbers in the range  $0\cdots\eta-1$ . We show two versions of the shuffling algorithm based on the coding scheme for registers  $a_k$ . For the unary coding scheme,  $N$  bits are used to represent values from 0 to  $N-1$ . Here, the  $(k-1)$ -th bit is set to 1 to represent the number  $k-1$ . In the binary coding version,  $\lceil \log_2 N \rceil$  bits are used, just as in ordinary binary numbers.

The shuffling consists of two steps: (1) preparation of the ancillae to the  $k$ -sequence state, or the  $k_\Sigma$  state, and (2) shuffling.

In the first step, the registers  $a_k$  are initialized to a superposition of values which we call the  $k$ -sequence state  $k_\Sigma$ :

$$|k_\Sigma\rangle_{a(k-1)} = \frac{1}{\sqrt{k}} \sum_{i=0}^{k-1} |i\rangle \quad (5)$$

Once all registers  $a_k$  have been prepared in this way, the tensor product of all registers  $a_k$  will represent the factorial state of  $\eta$ :

$$|\eta!\rangle_a = \prod_{k=2}^{\eta} |k_\Sigma\rangle_{a(k-1)} \quad (6)$$

The second step, shuffling, is the permutation of the coordinate qubits based on the content of register set  $a$ . The content of each register is an integer ranging from 0 to  $k-1$ . Because each  $|k_\Sigma\rangle_{a(k-1)}$  in eq 6 is set individually, values for index  $i$  in eq 5 for each  $|k_\Sigma\rangle_{a(k-1)}$  can appear repeatedly, such as the 0 in  $\{i_{a3}, i_{a2}, i_{a1}\} = \{1, 0, 0\}$ . We call the sequence in the register set a  $\sigma'$ . For example,  $\{1, 0, 0\}$  is a  $\sigma'$  for  $\eta = 4$ . This sequence can be mapped to one of the sequences in  $S_\eta$ , where the elements of each sequence in  $S_\eta$  are all different. To obtain the map, we define permutation  $\tau$  to be a function of  $\sigma'$ . This is done recursively in eqs 7 and 8, where  $(i, j)$  is a permutation operator that swaps the  $i$ th and  $j$ th element of  $\sigma'$  and  $\eta \geq 2$ .

$$\tau(|k\rangle_{a1}) = (k, 1) \quad (7)$$

$$\tau(|k\rangle_{a(\eta-1)} |k'\rangle_{a(\eta-2)\dots a1}) = (k, \eta-1) \tau(|k'\rangle_{a(\eta-2)\dots a1}) \quad (8)$$

Here, "1" in eq 7 comes from  $\eta-1$  in eq 8 where  $\eta = 2$  in this case.  $\tau$  operates on  $\sigma_0$  such that  $\sigma = \tau(|i_{a(\eta-1)}\rangle |i_{a(\eta-2)}\rangle \dots |i_{a1}\rangle) \sigma_0$ . For example, when  $\sigma' = \{4, 3, 2, 1\}$ , i.e., registers  $a4$  through  $a1$  have the values 4, 3, 2 and 1, the resulting permutation would be the identity:  $\tau(|4\rangle_{a4} |3\rangle_{a3} |2\rangle_{a2} |1\rangle_{a1}) = (4, 4)(3, 3)(2, 2)(1, 1) = I$ , and for that case  $\sigma = I\sigma_0$ . On the basis of this relation, we can prepare the antisymmetrized wave function such as

$$|\Phi_{\text{ini}}\rangle \equiv |\phi_{\text{ini}}(\sigma_0)\rangle |\eta!\rangle_a \mapsto |\Psi_{\text{anti}}\rangle \equiv \frac{1}{\sqrt{\eta!}} \sum_{\sigma \in S_\eta} \text{sgn}(\sigma) |\phi_{\text{ini}}(\sigma)\rangle |\sigma'\rangle_a$$

**2.4. Preparation of a Mixed State of Energy Configurations.** To enable a simulation with a target temperature, several antisymmetrized wave functions with different energy levels can be combined to form a mixed state. An explanation of the circuit can be found in the first part of the report.<sup>1</sup>

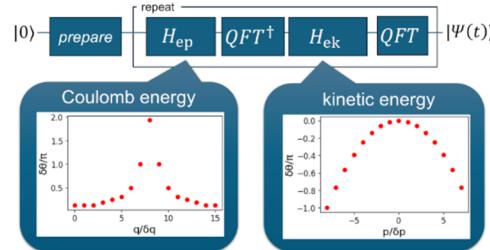

**2.5. Time Evolution.** The time evolution is calculated on the basis of the Schrödinger equation by using the Suzuki–Trotter decomposition. The time-independent Hamiltonian of the system is a sum of Hamiltonians for electrons and nuclei; these are further decomposed into kinetic energy terms and potential energy terms:

$$H = (H_{\text{ek}} + H_{\text{ep}}) + H_{\text{en}} + (H_{\text{nk}} + H_{\text{np}}) \quad (10)$$

$$H_{\text{ek}} = \sum_i \frac{\mathbf{p}_i^2}{2m_e}, \quad H_{\text{ep}} = \sum_{i>j} \frac{e^2}{|\mathbf{q}_i - \mathbf{q}_j|}$$

$$H_{\text{en}} = - \sum_{i,j} \frac{e^2 Z_j}{|\mathbf{q}_i - \mathbf{Q}_j|}$$

$$H_{\text{nk}} = \sum_i \frac{\mathbf{P}_i^2}{2M_i}, \quad H_{\text{np}} = \sum_{i>j} \frac{e^2 Z_i Z_j}{|\mathbf{Q}_i - \mathbf{Q}_j|}$$

Here,  $H_{\text{ek}}$  and  $H_{\text{ep}}$  are the kinetic and Coulomb energy terms of electrons, respectively, where  $H_{\text{en}}$  is the Coulomb energy

between electrons and nuclei.  $H_{nk}$  and  $H_{np}$  are the kinetic and Coulomb energies of nuclei, respectively.  $m_e$  and  $M_i$  are the mass of the electron and nucleus i.e., is the elementary charge, and  $Z_i$  is the atomic number of the nucleus  $i$ .

According to the Suzuki–Trotter formula, the time evolution for a period of  $t$  can be approximated as

$$\begin{aligned} |\Psi(t)\rangle &= e^{-iHt/\hbar}|\Psi_0\rangle \\ &\simeq (e^{-iH_{ek}t/\hbar n}e^{-iH_{ep}t/\hbar n}e^{-iH_{en}t/\hbar n}e^{-iH_{nk}t/\hbar n}e^{-iH_{np}t/\hbar n})^n|\Psi_0\rangle \end{aligned} \quad (11)$$

Paying attention to the fact that nuclei are much heavier than electrons, we can approximate eq 11 as

$$|\Psi(t)\rangle \simeq [(e^{-iH_{ek}t/\hbar nm}e^{-iH_{ep}t/\hbar nm}e^{-iH_{en}t/\hbar nm})^m e^{-iH_{nk}t/\hbar n}e^{-iH_{np}t/\hbar n}]^n|\Psi_0\rangle \quad (12)$$

We will use the Fourier transform and its inverse to convert the wave function from the positional representation to the momentum representation and vice versa. Note that the time evolution of the kinetic energy term becomes much simpler in momentum space.

### 3. DESIGNED CIRCUITS

The main outcome of this study is a Python program that generates a time evolution simulator as a quantum circuit. The

**Table 1. Configuration Parameters of the Circuit Generator**

| parameter           | definition                                                                                                       |

|---------------------|------------------------------------------------------------------------------------------------------------------|

| $d$                 | dimension of coordinates [1,3]                                                                                   |

| $n_1$               | number of bits per coordinate for a dimension                                                                    |

| $L$                 | length of simulation space along one axis                                                                        |

| $\eta$              | number of electrons                                                                                              |

| $L_n$               | number of nuclei                                                                                                 |

| $N_E$               | number of configurations in the mixed state                                                                      |

| $\phi_{c, i, d, x}$ | array holding data for electron orbital $\phi_i$ indexed by [energy configuration, orbital, dimension, position] |

| $\psi_{c, i, d, X}$ | array holding data for nucleus orbital $\psi_i$                                                                  |

| $\delta t$          | step of time evolution for an electron                                                                           |

| $T_N$               | number of nucleus-level iteration steps                                                                          |

| $T_e$               | number of electron-level iteration steps within one nucleus-level iteration step                                 |

circuit takes the initial state of the wave function as precalculated input data. Then, it repeatedly calculates the time-evolved wave function. This will cause changes in the spin–orbitals. After the time-evolution process has been repeated a specified number of times, the resulting wave function is measured. So far, we have completed our implementation up to the time-evolution loop and left the measurement part for future work. Note that the circuit parameters shown in Table 1 can be adjusted.

In this section, we show several examples of generated circuits and their subcircuits (Section 3.1) and describe the number of qubits required for the overall circuit for a selected range of parameters (Section 3.2).

**3.1. Examples of the Generated Simulator Circuit.** The circuits presented in this section are organized hierarchically. There are four simulator configurations: (1) a basic one-dimensional configuration with a 3-bit coordinate, one electron, one nucleus, and one initial wave function ( $d = 1, n = 3, \eta = 1, L_n = 1, N_E = 1$ ), (2) the first example with two dimensions instead of one ( $d = 2, n = 4, \eta = 1, L_n = 1, N_E = 1$ ), (3) a one-dimensional configuration with four electrons ( $d = 1, n = 2, \eta = 4, L_n = 1, N_E = 1$ )

) and (4) a one-dimensional configuration with two electrons, with four wave functions in the initial mixed state ( $d = 1, n = 2, \eta = 2, L_n = 1, N_E = 4$ ).

The circuits and their subcircuits are listed in Table 2.

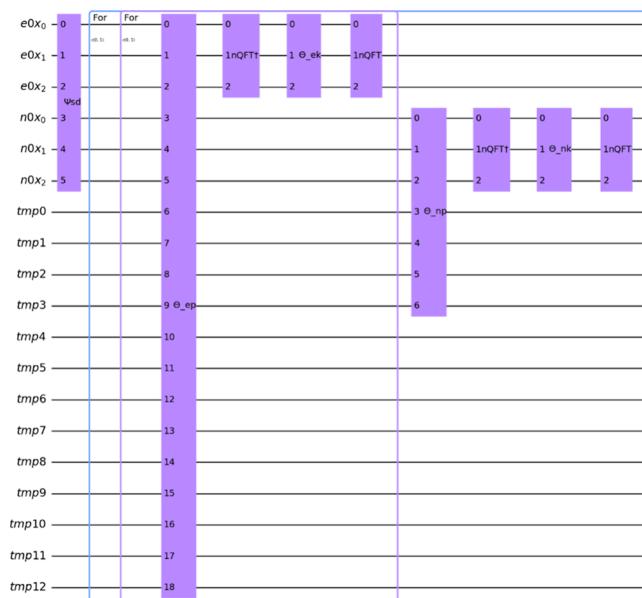

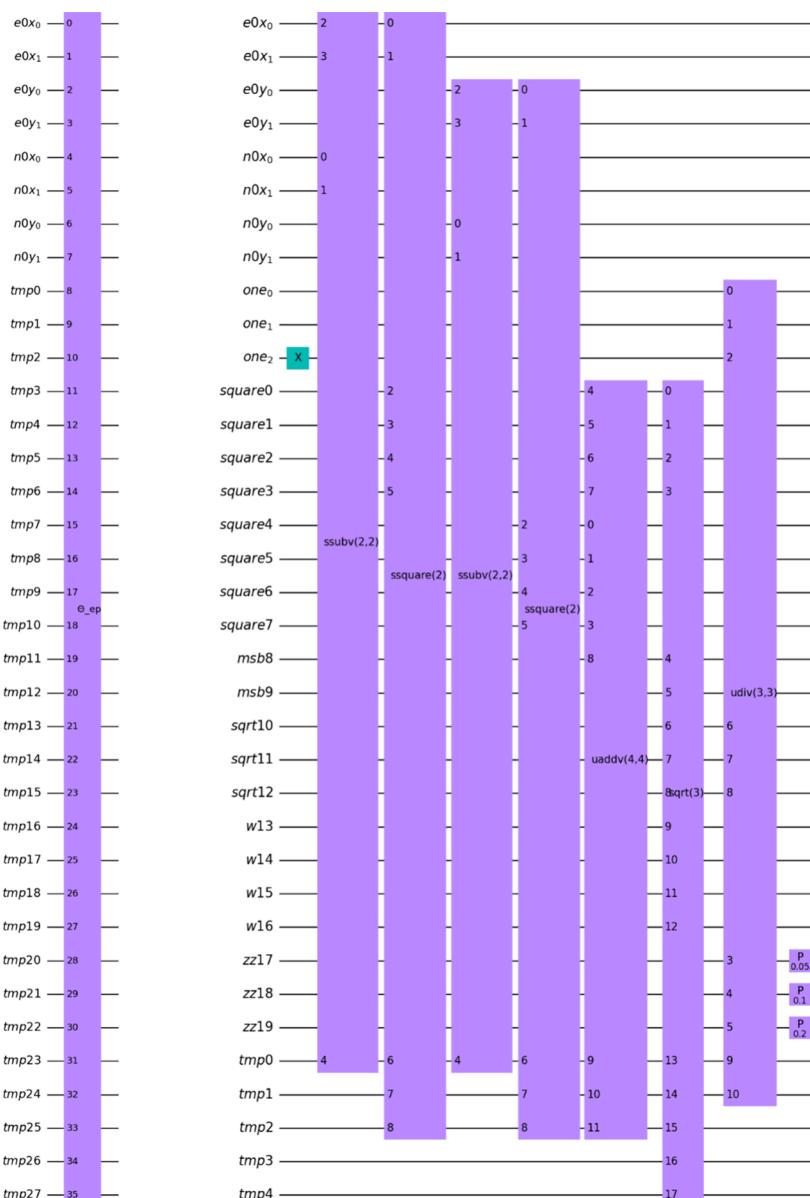

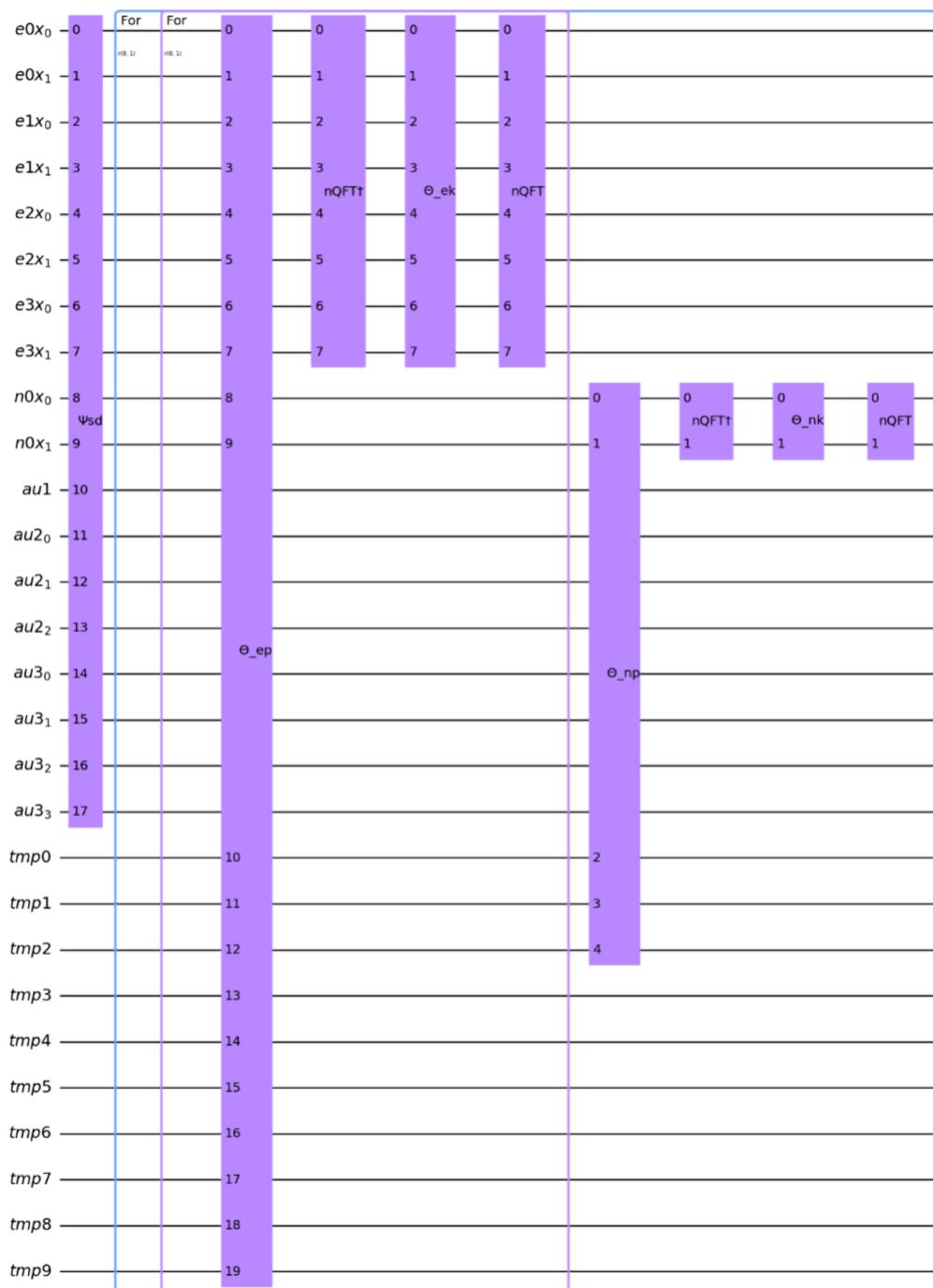

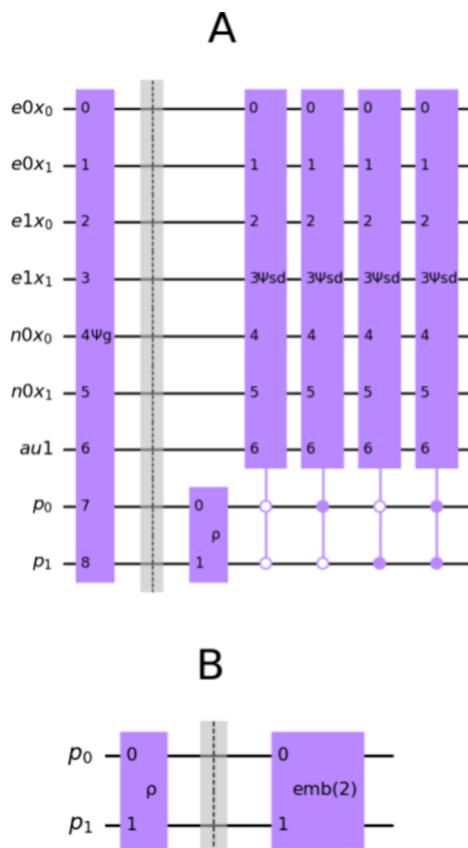

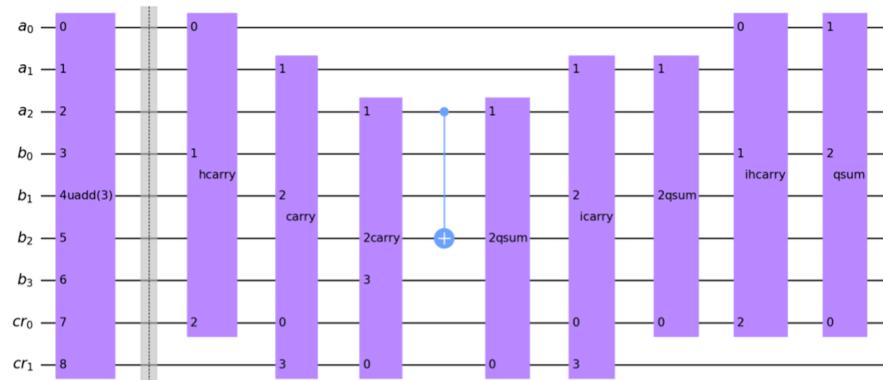

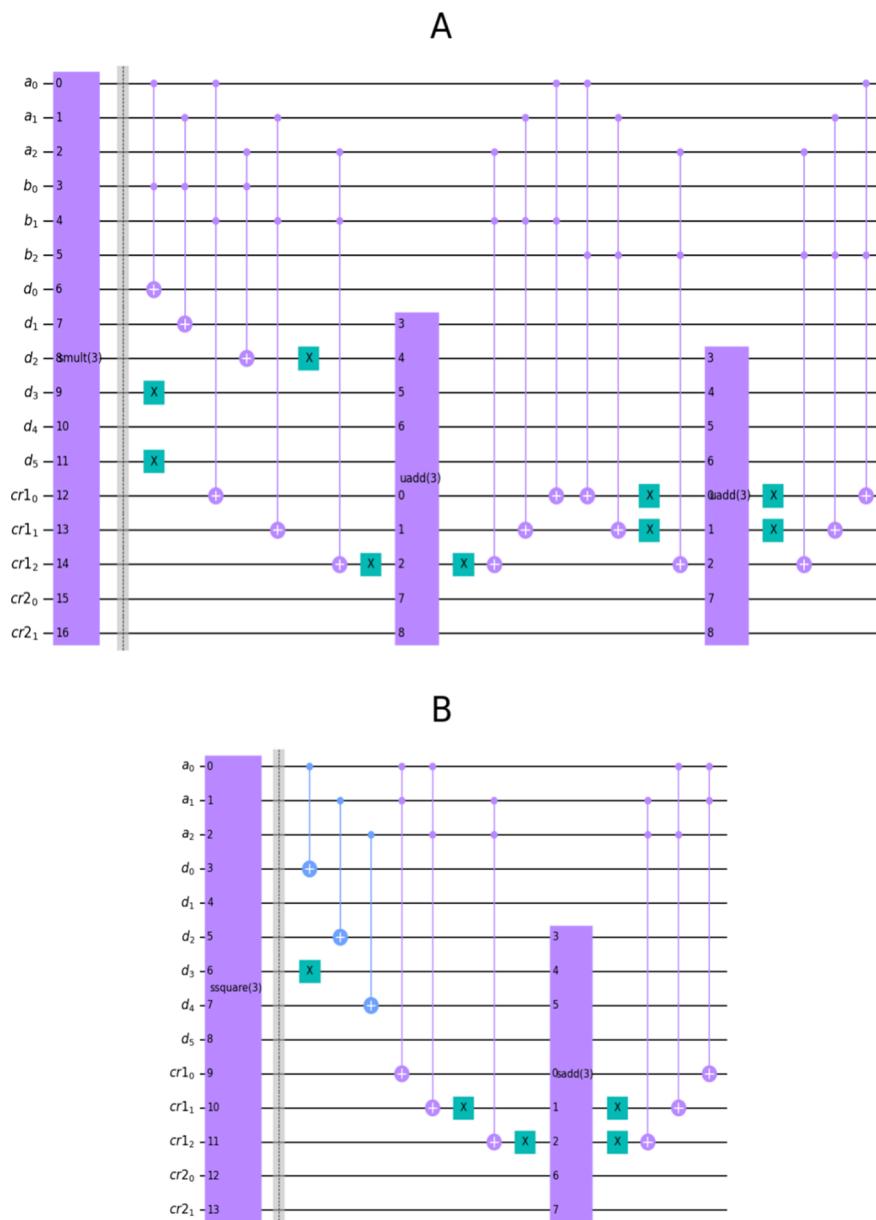

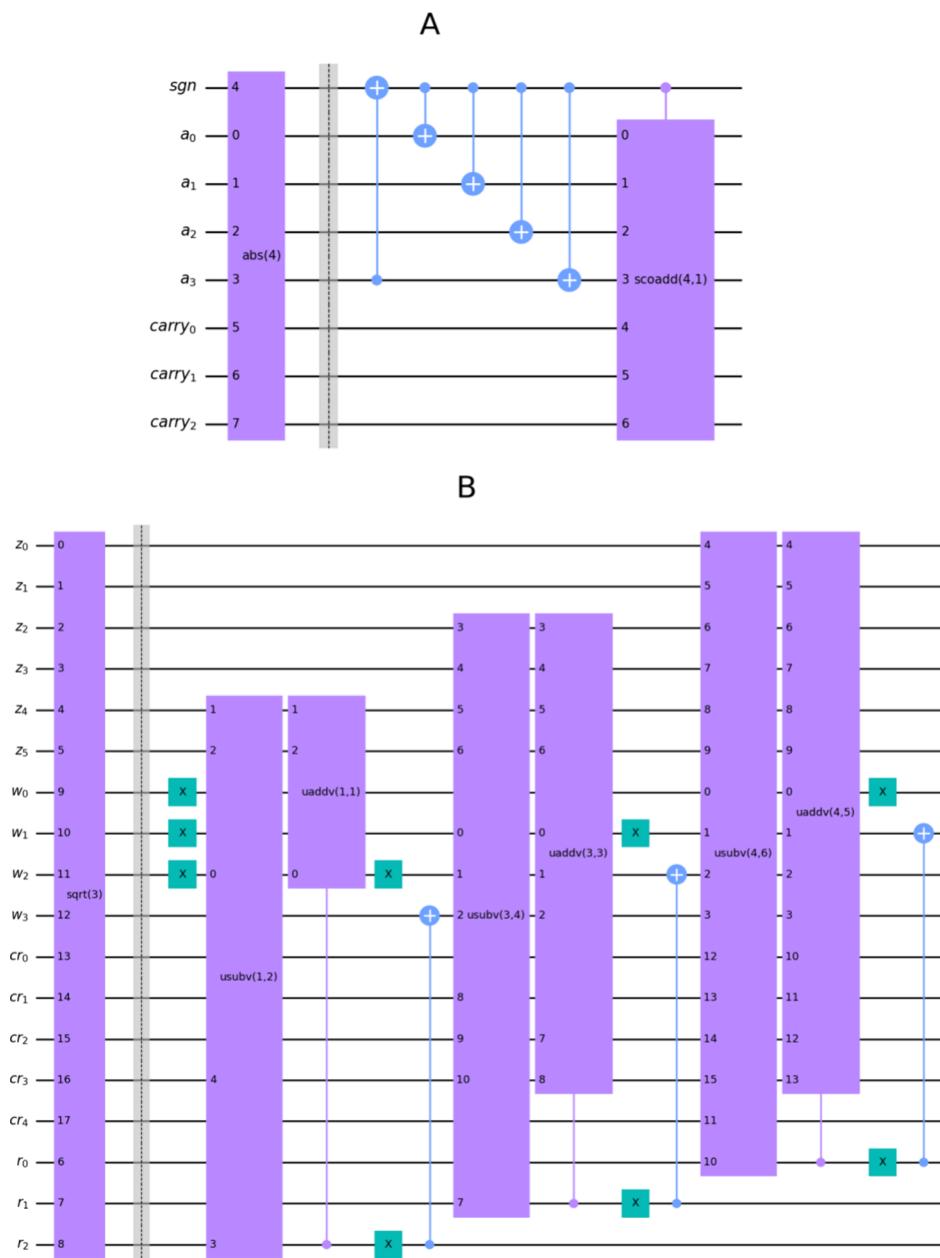

**3.1.1. Basic One-Dimensional Configuration.** The first example implements a minimal one-dimensional model with three coordinate bits and has one electron and one nucleus ( $d = 1, n = 3, \eta = 1, L_n = 1$ ), namely, a one-dimensional model of a hydrogen atom. Since the model is one-dimensional, the circuit for the Hamiltonian (eq 10) uses a simple absolute value gate instead of a sequence of gates to calculate the norm for the distance between the electron and the nucleus. The overall circuit is shown in Figure 1. The total number of qubits is 19. Each line of the diagram represents a qubit. The order of the qubits is the least significant bit (LSB) first or in little-endian. This order is the default used by Qiskit and is different from the one assumed in the first part of this report.<sup>1</sup> The top six lines are qubits for the coordinate bits. The labels  $e0x_0, \dots, e0x_2$  denote the three bits for the  $x$  coordinate of electron 0.  $n0x_0, \dots, n0x_2$  are the three bits for the  $x$  coordinate of nucleus 0. Thus, the bit count is 6, or  $(\eta + L_n)n$ . The lower 13 lines with labels  $tmpn$  are temporary qubits. Those qubits are internally used at the gates, such as the electron potential energy (P.E.) time evolution gate  $\Theta_{ep}$ ; they have no effect outside of the gates. The subcomponents function as follows: The Slater determinant (SD) state preparation gate,  $\Psi_{sd}$ , prepares the initial state of the wave function on the coordinate qubits on the basis of orbital data provided as input at the circuit generation time. The rest of the circuit consists of nested time-evolution loops that are executed repeatedly. The outer loop operates with nucleus scale time steps and the inner loop operates with electron scale time steps. The electron scale loop is the first element of the nucleus scale loop. The first gate inside the inner loop is the  $\Theta_{ep}$  gate. This gate calculates the electron–electron and electron–nucleus potential energy terms of the Hamiltonian, and each state in a superposition will have its phase altered according to the coordinates of the particles. Following  $\Theta_{ep}$  comes the  $n$ -element inverse quantum Fourier transform gate,  $nQFT^\dagger$ . This transforms the position representation into a momentum representation. Then follows the electron kinetic energy (K.E.) time evolution gate,  $\Theta_{ek}$ , which alters the phases according to the coordinates in  $p$ -space. After that comes the  $n$ -element Quantum Fourier transform gate,  $nQFT$ , that transforms the momentum representation back to the position representation. Outside the electron scale loop, the corresponding gates for nuclei will follow; the nucleus P.E. time evolution gate,  $\Theta_{np}$ , the  $nQFT^\dagger$  gate, the nucleus K.E. time evolution gate,  $\Theta_{nk}$  and the  $nQFT$  gate.

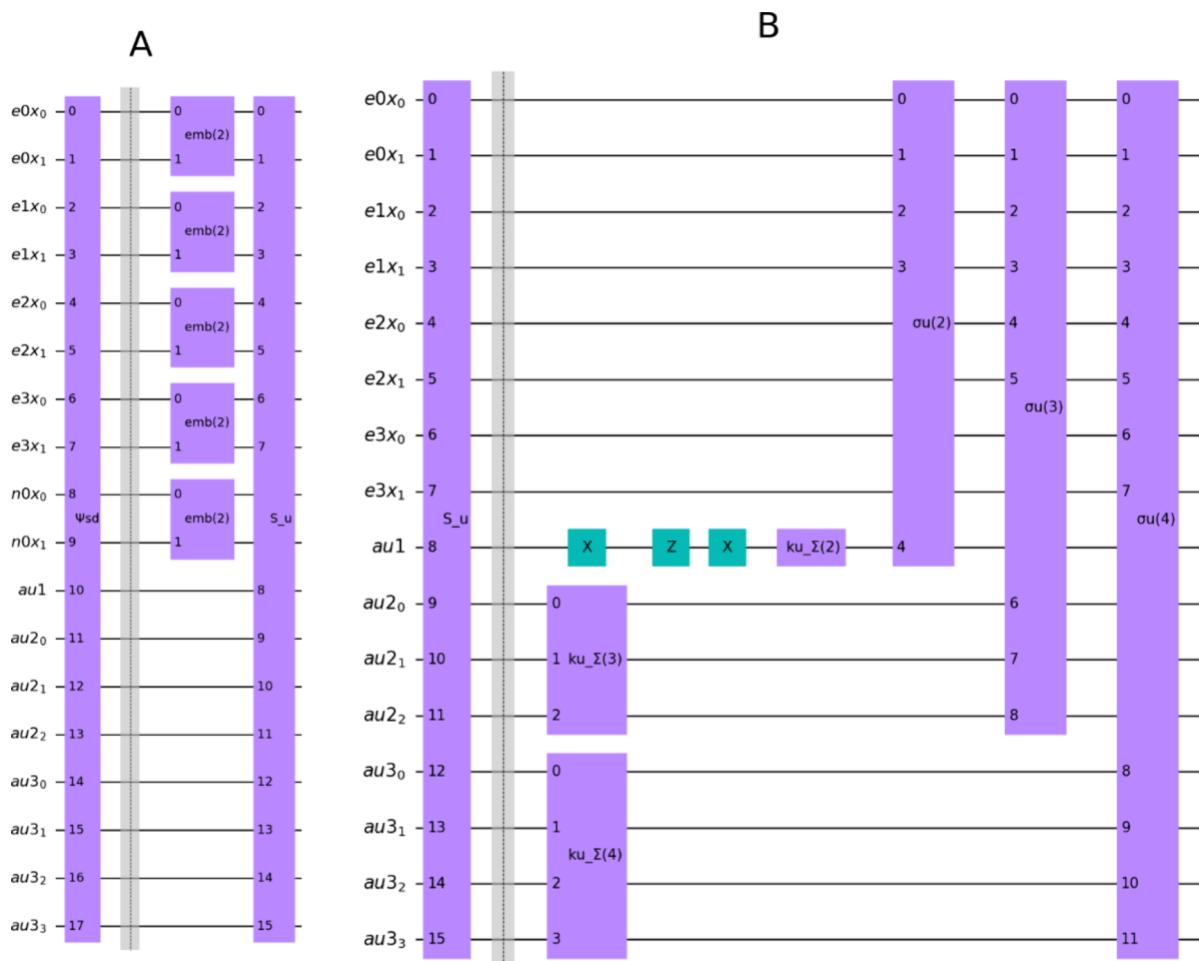

The SD state preparation gate,  $\Psi_{sd}$ , is shown in Figure 2A. Since there is only one electron in this first example, the gates that perform the permutations to build the Slater determinant are not present. They will appear in the third example. The three-bit state embedding gate,  $emb(3)$ , is applied to each of the two coordinate registers,  $e_0x$  and  $n_0x$ . Each  $emb(3)$  gate sets the amplitudes of 3-qubit states on the basis of data provided as an array. The internals of  $emb(3)$  are shown in Figure 2B. The  $emb(3)$  gate has two internal gates,  $emb\theta(3)$  that embeds amplitudes and  $emb\phi(3)$  that embeds phases. The recursive structures of those two gates are illustrated in Figure 2C through H.

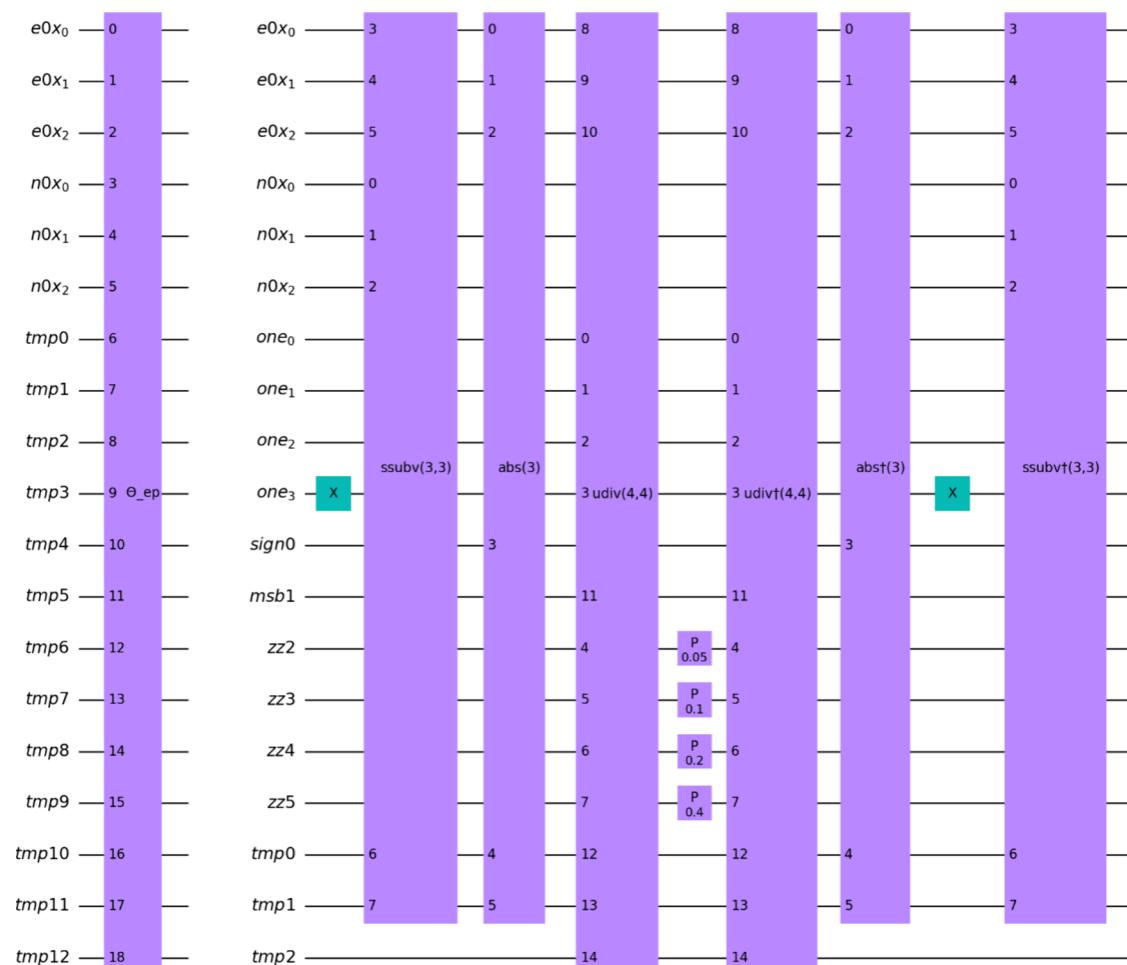

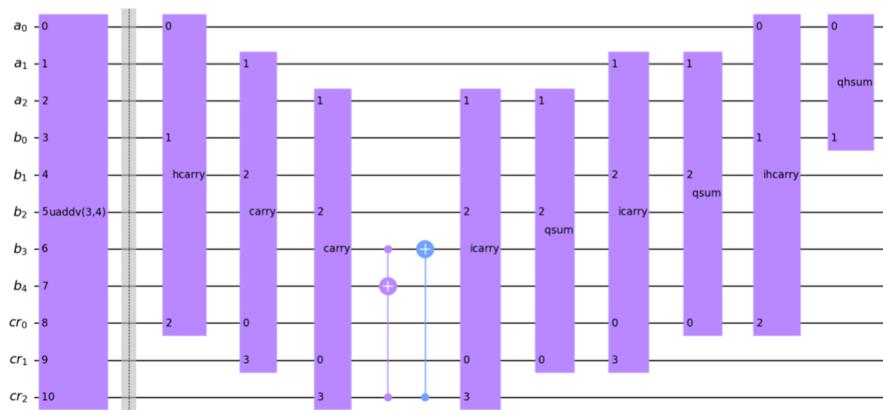

The content of the electron P.E. time evolution gate,  $\Theta_{ep}$ , is shown in Figure 3. This gate has the greatest number of parameter qubits in the first example, which is 19. It is

Table 2. List of Sample Circuits

| label       | description                                                                                         | label       | description                                                                 |

|-------------|-----------------------------------------------------------------------------------------------------|-------------|-----------------------------------------------------------------------------|

| Figure 1    | overall circuit for $d = 1, n = 3, \eta = 1, L_n = 1, N_E = 1$                                      | Figure A-3B | the signed subtractor ssub(3)                                               |

| Figure 2A   | the Slater determinant preparation gate $\Psi_{sd}$ for a single electron model                     | Figure A-4  | the unsigned multiplier umult(3)                                            |

| Figure 2B   | the 3-bit state embedding gate emb(3)                                                               | Figure A-5A | the signed multiplier smult(3)                                              |

| Figure 2C   | the 3-bit amplitude embedding gate emb $\theta$ (3)                                                 | Figure A-5B | the signed square ssquare(3)                                                |

| Figure 2D   | the 2-bit amplitude embedding gate emb $\theta$ (2)                                                 | Figure A-6  | the unsigned divider udiv(4,3)                                              |

| Figure 2E   | the 1-bit amplitude embedding gate emb $\theta$ (1)                                                 | Figure A-7A | the absolute value abs(4)                                                   |

| Figure 2F   | the 3-bit phase embedding gate emb $\phi$ (3)                                                       | Figure A-7B | the square root sqrt(3)                                                     |

| Figure 2G   | the 2-bit phase embedding gate emb $\phi$ (2)                                                       | Figure A-8A | the carry gate                                                              |

| Figure 2H   | the 1-bit phase embedding gate emb $\phi$ (1)                                                       | Figure A-8B | the carry gate with one input given as constant 0 cocarry(0)                |

| Figure 3    | the electron P.E. time evolution gate $\Theta_{ep}$                                                 | Figure A-8C | the carry gate with one input given as constant 1 cocarry(1)                |

| Figure 4A   | the electron K.E. time evolution gate $\Theta_{ek}$                                                 | Figure A-8D | the inverse carry gate icarry                                               |

| Figure 4B   | the $n$ -element inverse quantum Fourier transform gate $nQFT^\dagger$ for $d = 1, n = 3, \eta = 1$ | Figure A-8E | the inverse carry gate with one input given as constant 0 icocarry(0)       |

| Figure 5    | $\Theta_{ep}$ for $d = 2, n = 4, \eta = 1, L_n = 1, N_E = 1$                                        | Figure A-8F | the inverse carry gate with one input given as constant 1 icocarry(1)       |

| Figure 6    | the overall circuit for $d = 1, n = 2, \eta = 4, L_n = 1, N_E = 1$                                  | Figure A-8G | the half carry gate hcarry                                                  |

| Figure 7A   | the Slater determinant preparation gate $\Psi_{sd}$ for a multiple electron model                   | Figure A-8H | the half carry gate with one input given as constant 0 cohcarry(0)          |

| Figure 7B   | the unary-coded permutation gate $S_u$                                                              | Figure A-8I | the half carry gate with one input given as constant 1 cohcarry(1)          |

| Figure 8A   | the unary-coded sequence preparation gate $ku_\Sigma(2)$                                            | Figure A-8J | the inverse half carry gate ihcarry                                         |

| Figure 8B   | the gate $ku_\Sigma(3)$                                                                             | Figure A-8K | the inverse half carry gate with one input given as constant 0 icohcarry(0) |

| Figure 8C   | the gate $ku_\Sigma(4)$                                                                             | Figure A-8L | the inverse half carry gate with one input given as constant 1 icohcarry(1) |

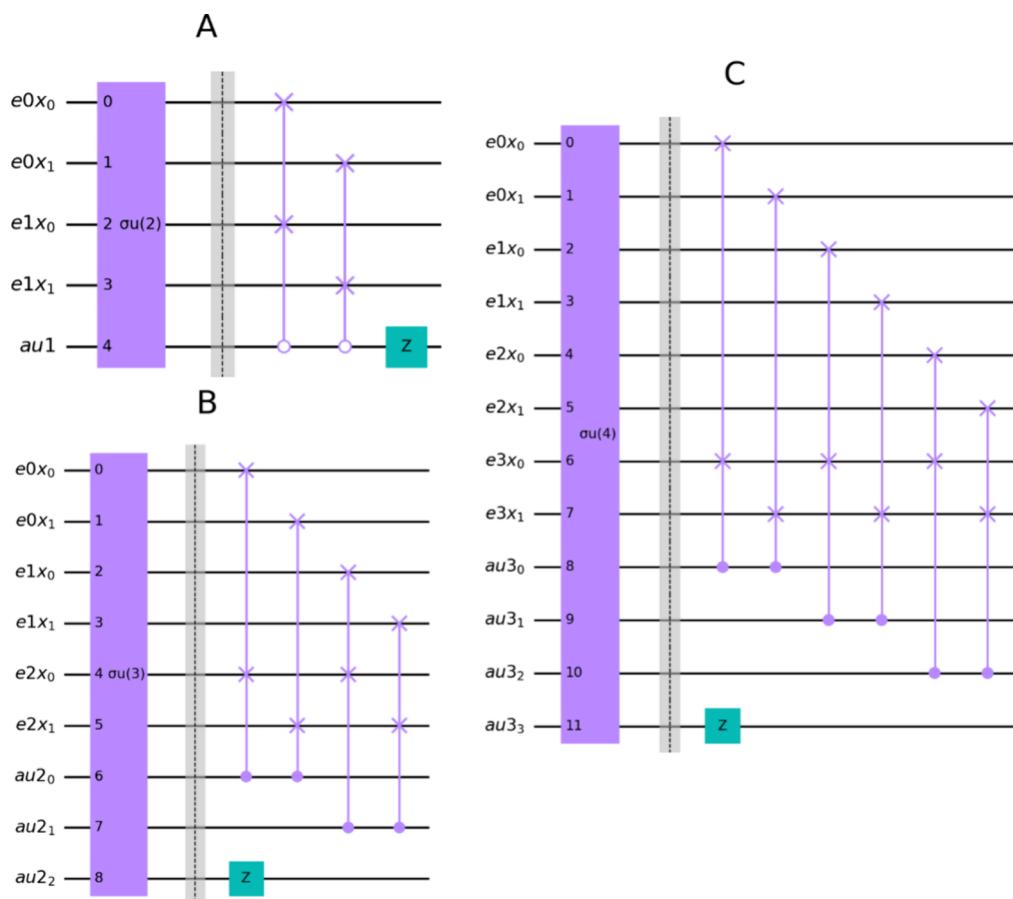

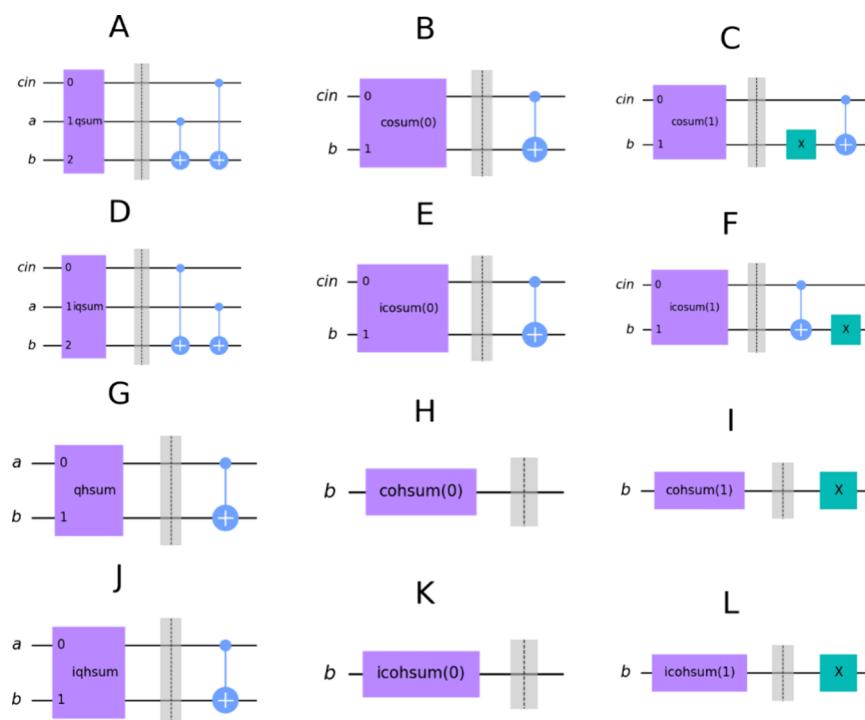

| Figure 9A   | the unary-coded conditional shuffling gate $\sigma u(2)$                                            | Figure A-9A | the sum gate qsum                                                           |

| Figure 9B   | the gate $\sigma u(3)$                                                                              | Figure A-9B | the sum gate with one input given as constant 0 cosum(0)                    |

| Figure 9C   | the gate $\sigma u(4)$                                                                              | Figure A-9C | the sum gate with one input given as constant 1 cosum(1)                    |

| Figure 10   | the binary coded permutation gate $S_b$                                                             | Figure A-9D | the inverse sum gate iqsum                                                  |

| Figure 11A  | the binary-coded sequence preparation gate $kb_\Sigma(2)$                                           | Figure A-9E | the inverse sum gate with one input given as constant 0 icosum(0)           |

| Figure 11B  | the gate $kb_\Sigma(3)$                                                                             | Figure A-9F | the inverse sum gate with one input given as constant 1 icosum(1)           |

| Figure 11C  | the gate $kb_\Sigma(4)$                                                                             | Figure A-9G | the half sum gate qhsum                                                     |

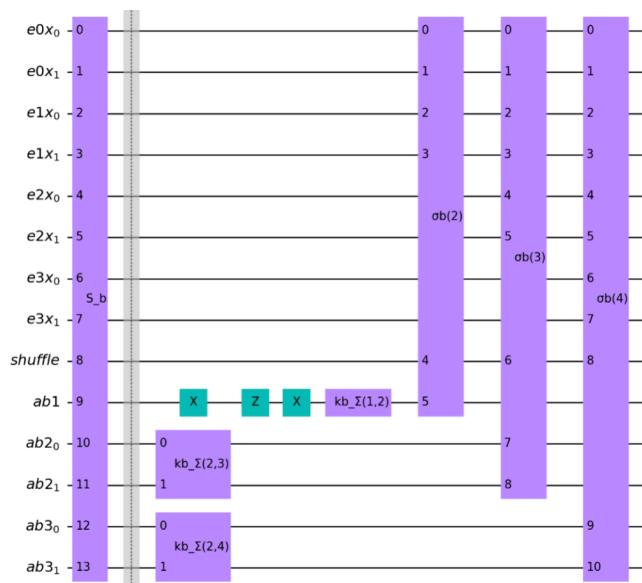

| Figure 11D  | the gate $kb_\Sigma(6)$                                                                             | Figure A-9H | the half sum gate with one input given as constant 0 cohsum(0)              |

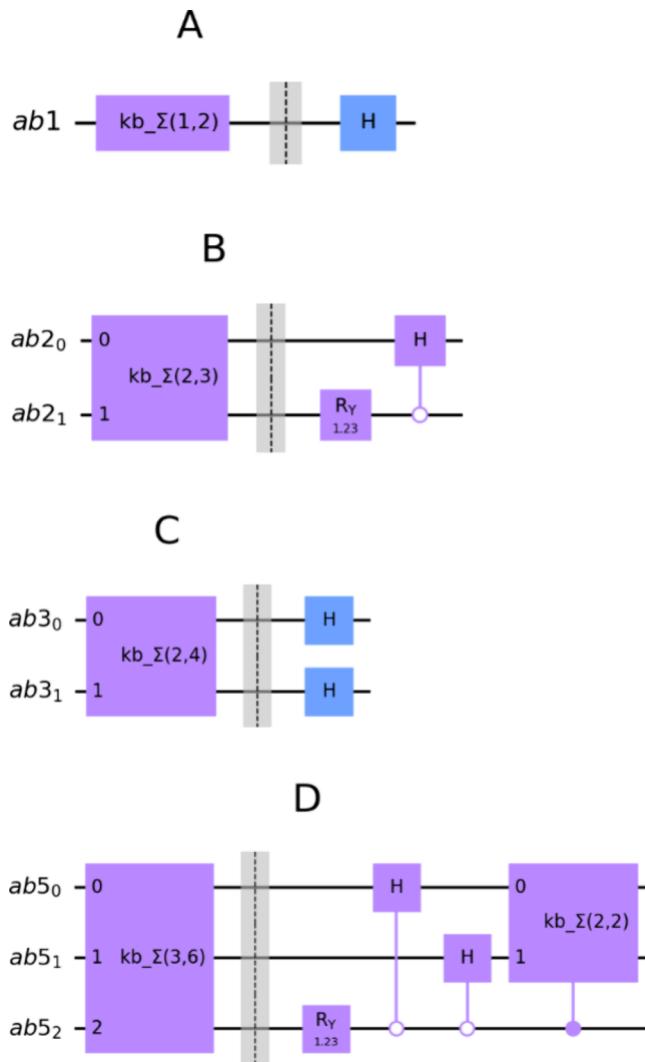

| Figure 12A  | the binary-coded conditional shuffling gate $\sigma b(2)$                                           | Figure A-9I | the half sum gate with one input given as constant 1 cohsum(1)              |

| Figure 12B  | the gate $\sigma b(3)$                                                                              | Figure A-9J | the inverse half sum gate iqhsu                                             |

| Figure 12C  | the gate $\sigma b(4)$                                                                              | Figure A-9K | the inverse half sum gate with one input given as constant 0 icohsum(0)     |

| Figure 13A  | the general state preparation gate $\Psi_g$ for $d = 1, n = 2, \eta = 2, L_n = 1, N_E = 4$          | Figure A-9L | the inverse half sum gate with one input given as constant 1 icohsum(1)     |

| Figure 13B  | the 2-bit configuration preparation gate                                                            |             |                                                                             |

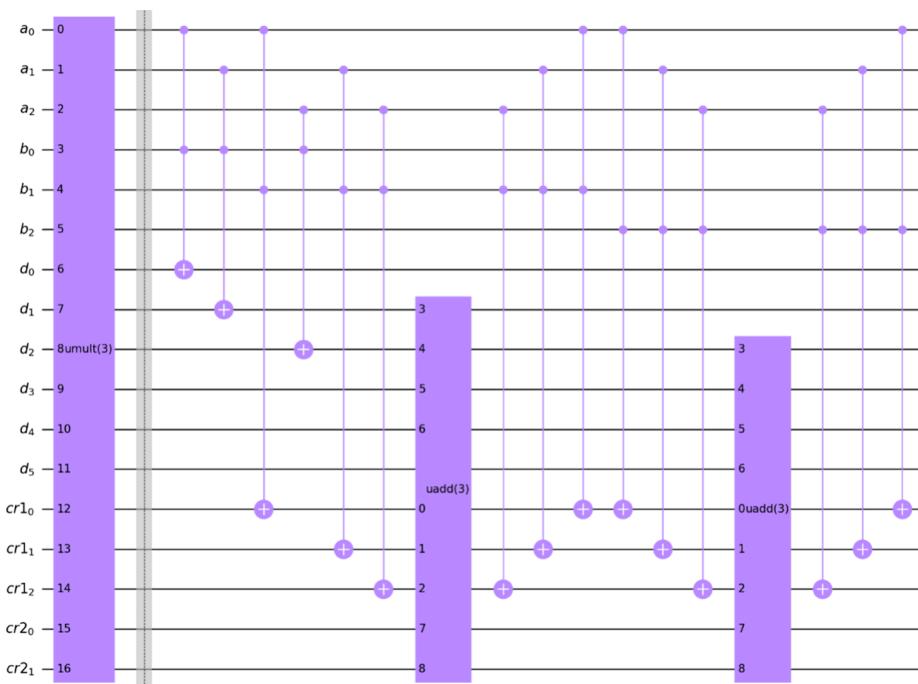

| Figure A-1A | the unsigned adder uadd(3)                                                                          |             |                                                                             |

| Figure A-1B | the unsigned mismatched bit length adder uaddv(3,4)                                                 |             |                                                                             |

| Figure A-2A | the signed adder sadd(3)                                                                            |             |                                                                             |

| Figure A-2B | the signed constant value adder scoadd(3,1)                                                         |             |                                                                             |

| Figure A-3A | the unsigned subtractor usub(3)                                                                     |             |                                                                             |

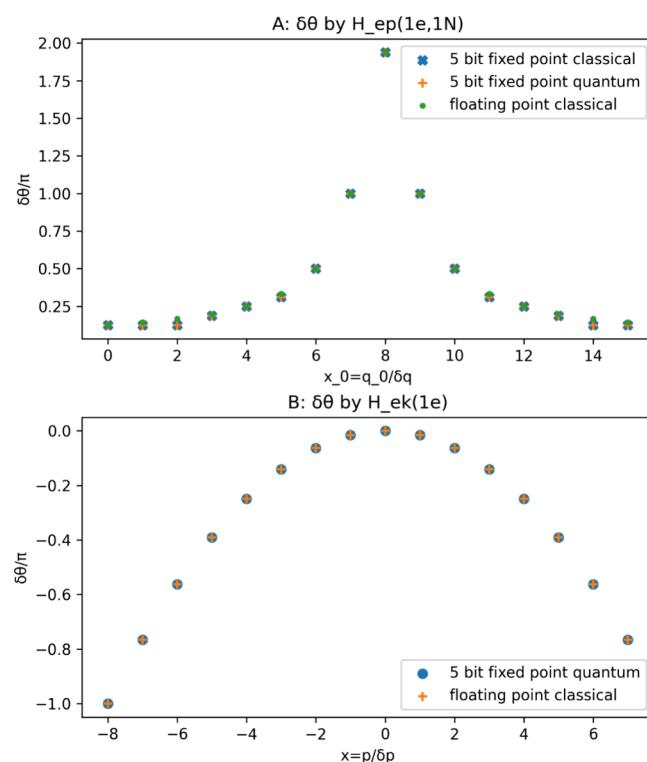

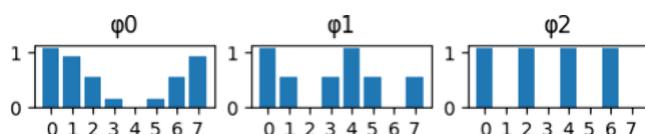

constructed as follows:  $\Theta_{ep}$  uses the arithmetic gates ssu<sub>b</sub> (signed subtractor), abs (absolute value), and udiv (unsigned divider). Since the coordinates are one-dimensional in this example, the electron–nucleus distance is calculated using a simple absolute value gate without square roots. Once the calculated result is used to alter the phase through  $P$  gates, the calculation is reversed using the inverse versions of the gates, denoted by a dagger on their names. Within the right half,  $tmp_0, \dots, tmp_2$  are the three temporary qubits used for carry bits. These are required for internal use at the arithmetic gates; they do not affect  $\Theta_{ep}$ . The lines with labels  $one_n, sign_0, msb_1$ , and  $zz_n$  are ancilla qubits that the  $\Theta_{ep}$  circuit uses for intermediate values. These qubits are used internally at  $\Theta_{ep}$ ; they have no effect outside  $\Theta_{ep}$ . The temporary qubits are labeled  $tmp_i$  in the leftmost column in Figure 3. The number of temporary qubits is a constant independent of the number of electrons. When the number of particle pairs increases, this same circuit structure is repeated for different pairs, while the same set of temporary qubits is reused. In this 1-D model with three qubit coordinates

( $d = 1, n = n_1 = 3$ ), the number of qubits for the coordinates of electrons and nuclei is  $dn_1(\eta + L_n)$  and the required number of temporary qubits is  $3n_1 + 4 = 13$ . The sum is  $dn_1(\eta + L_n) + 3n_1 + 4$ . The breakdown is shown in Table 3. Note that this formula is only for the single-electron case, since for multiple electrons additional qubits must be introduced to implement antisymmetrization.

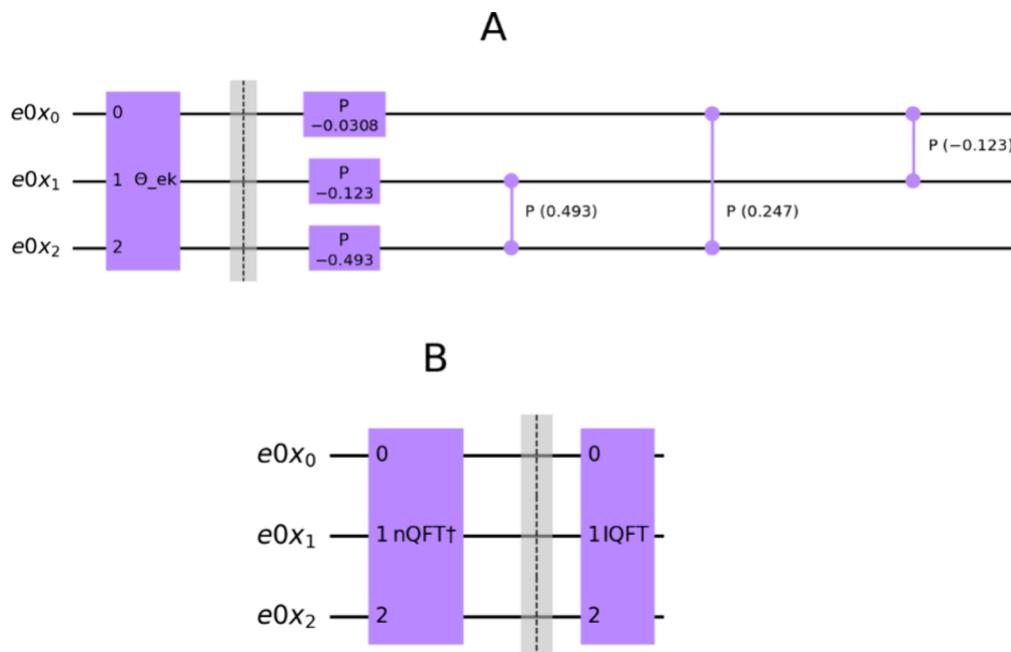

The content of the electron K.E. time evolution gate,  $\Theta_{ek}$ , is shown in Figure 4A. The depicted circuit is implemented with phase gates and controlled phase gates without using any arithmetic gates.

$\Theta_{np}$  and  $\Theta_{nk}$  are, respectively, the P.E. and K.E. terms for nuclei; their figures are omitted since they are analogous to the electron counterparts. In this example,  $\Theta_{np}$  is empty since only one nucleus is present and there are no nucleus–nucleus interaction terms.

The content of the  $n$ -element inverse quantum Fourier transform gate,  $nQFT^\dagger$ , is shown in Figure 4B. The inverse quantum Fourier transform gate IQFT from the Qiskit library is

**Figure 1.** Circuit diagram of generated results for  $d = 1, n = 3, \eta = 1, L_n = 1$ , and  $N_E = 1$ . The overall circuit consists of state-preparation and time-evolution gates. The initial state is prepared by the SD state preparation gate,  $\Psi_{sd}$  and then, nested time evolution loops are applied to the state. The inner electron time-scale loop consists of an electron P.E. time evolution gate,  $\Theta_{ep}$ , an  $n$ -element inverse quantum Fourier transform gate,  $nQFT^\dagger$ , an electron K.E. time evolution gate,  $\Theta_{ek}$ , and an  $n$ -element quantum Fourier transform gate,  $nQFT$ . The outer nucleus time-scale loop consists of the inner loop, the nucleus P.E. time evolution gate,  $\Theta_{np}$ , the  $nQFT^\dagger$  gate, the nucleus K.E. time evolution gate,  $\Theta_{nk}$ , and the  $nQFT$  gate.

used here. IQFT is independently applied to each of the coordinate bit sets.

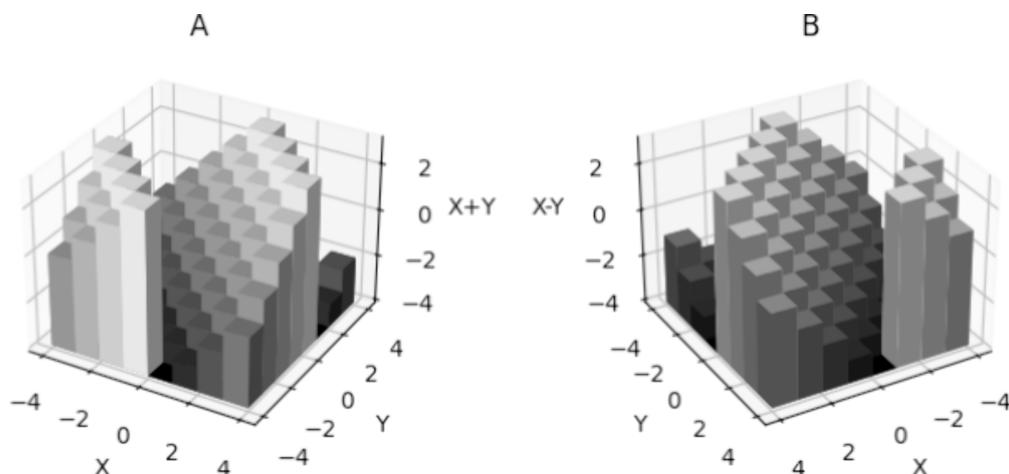

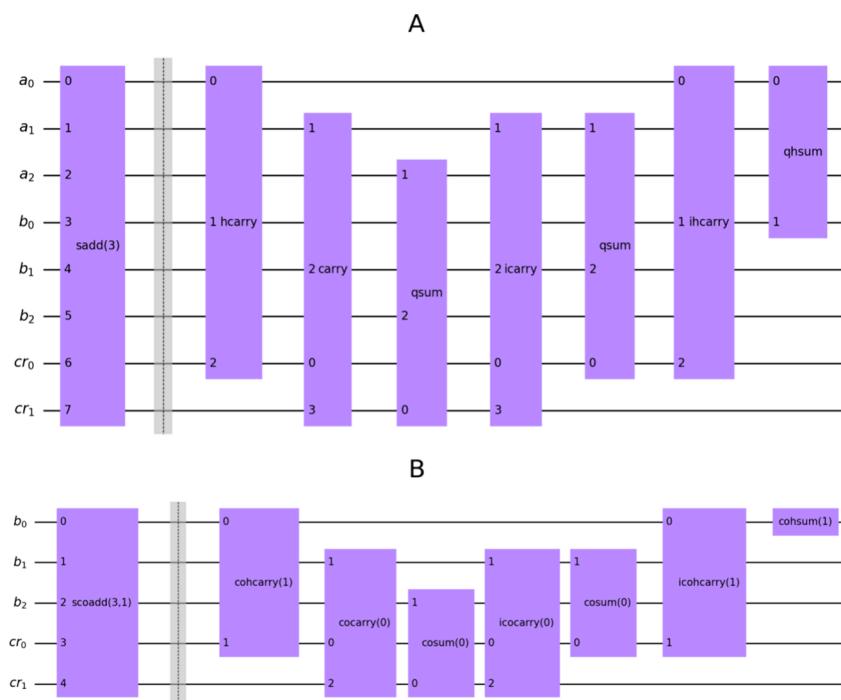

**3.1.2. Two-Dimensional Configuration.** The second example (Figure 5) is an extension of the first one to two dimensions ( $d = 2, n_1 = 2, n = dn_1 = 4, \eta = 1, L_n = 1$ ). This is also a model of a single hydrogen atom but in two dimensions. Compared to the first example, a more complex norm circuit is used to calculate the Hamiltonian. Only the  $\Theta_{ep}$  gate, which determines the overall circuit bit count, is shown; the other gates are omitted. The overall bit count is 36, and the number of coordinate qubits is 8, i.e.,  $(\eta + L_n)n$ . As a result of having multiple dimensions, the electron–nucleus distance calculation requires a norm calculation, which involves two square gates and one square root gate. In the circuit, the difference of coordinates is calculated with ssub (signed subtraction) gates, and the result is fed to an ssquare (signed square) gate for the  $x$  and  $y$  coordinates. Those squares are then summed by uaddv (unsigned adder) gate, and the sum is given to an sqrt (square root) gate. A udiv (unsigned divide) gate takes the inverse of the result of the sqrt gate. The number of temporary qubits for  $\Theta_{ep}$  in this example is 28, i.e.,  $(2d + 6)n_1 + 8$ . Their breakdown is shown in Table 4. The number of temporary qubits remains the same, even when the number of electrons is increased. The overall bit count for  $\Theta_{ep}$  is  $(\eta + L_n)n + (2d + 6)n_1 + 8 = 36$ . This same formula can also be used for  $d = 3$ , i.e., 3-dimensional models.

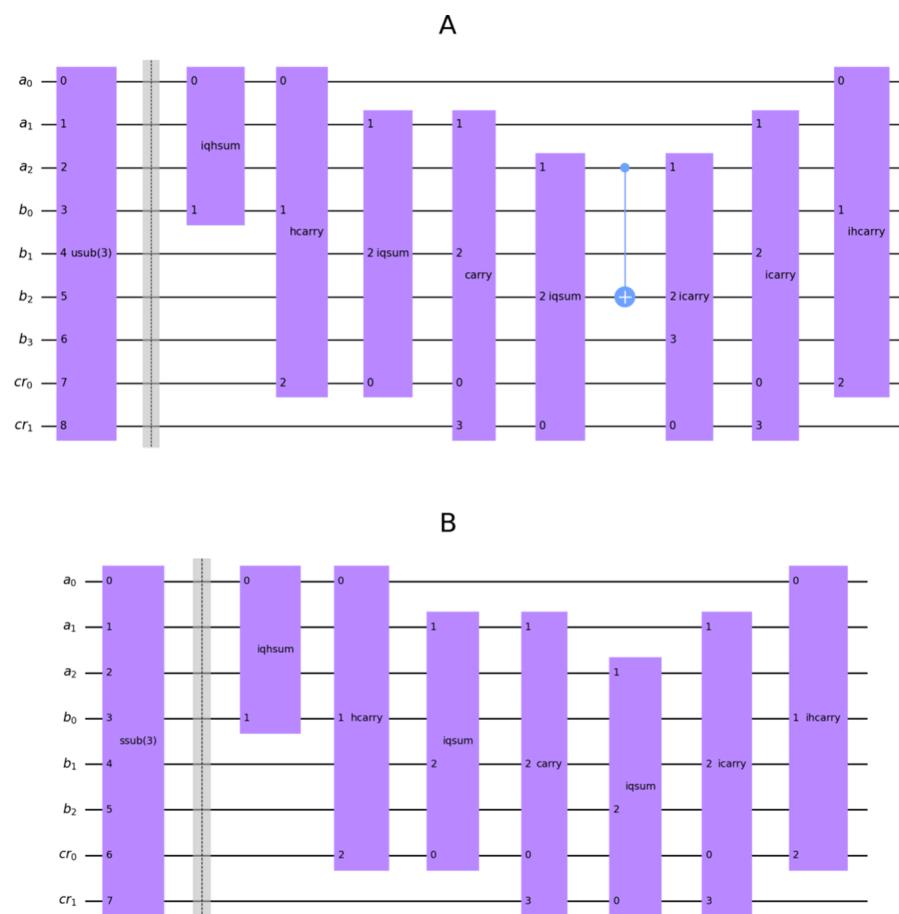

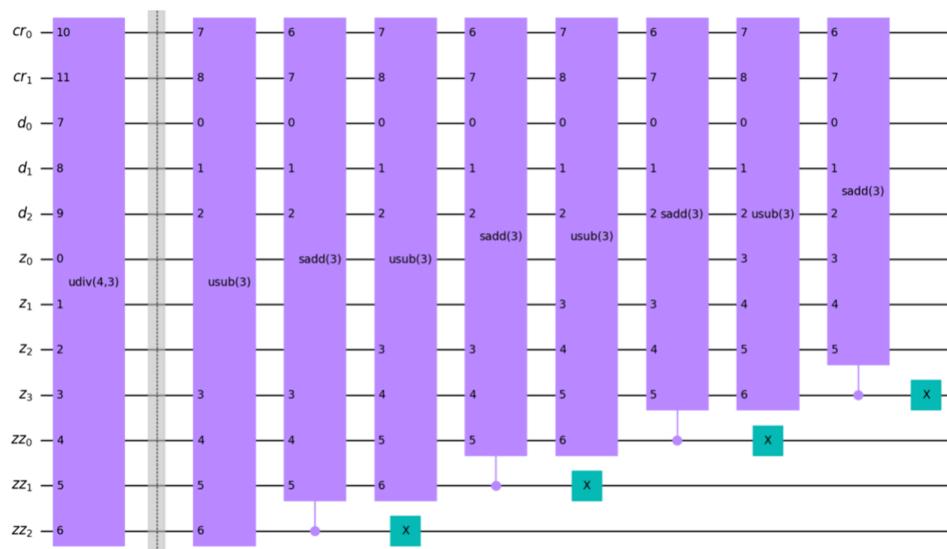

**3.1.3. Multiple Electron Configuration.** The third example implements a model with multiple electrons and introduces antisymmetrization. The overall circuit is shown in Figure 6. This example implements a one-dimensional model with four electrons and one nucleus, using two-bit coordinates ( $d = 1, n = 2, \eta = 4, L_n = 1$ ). This corresponds to a beryllium atom. The

**Figure 2.** SD preparation gate,  $\Psi_{sd}$ , and its internals. (A)  $\Psi_{sd}$  shown as a unit on the left and its internals on the right. In this example, with only one electron, the gates for permutations that are characteristic of the Slater determinant are not present. The two state embedding gate,  $emb(3)$ , embeds the orbital data in the two coordinate registers independently. (B) 3-bit state embedding gate,  $emb(3)$ . This gate consists of a 3-bit amplitude embedding gate,  $emb\theta(3)$ , and a phase embedding gate,  $emb\phi(3)$ . (C) 3-bit amplitude embedding gate,  $emb\theta(3)$ . This gate is defined recursively with the two-bit  $emb\theta(2)$  gate. The phase value shown on the  $R_y$  gate is an example; it varies depending on the amplitude data. (D) Gate  $emb\theta(2)$ , same for 2 bits, (E) gate  $emb\theta(1)$ , same for 1 bit. (F) 3-bit phase embedding gate,  $emb\phi(3)$ . This gate is also defined recursively. The difference from  $emb\theta(3)$  is in the use of the  $R_z$  gate instead of the  $R_y$  gate. (G) Same for 2 bits. (H) Same for 1 bit.

purpose of this example is to show the circuits related to antisymmetrization. As such, the one-dimensional model is used to simplify the circuit. The total number of qubits is 28. We will omit the formula for this number since the content of  $\Theta_{ep}$  for this sample takes much space to show.

When there are two or more electrons, the wave function of Fermions must be antisymmetrized. This is done using the SD state-preparation gate,  $\Psi_{sd}$ .

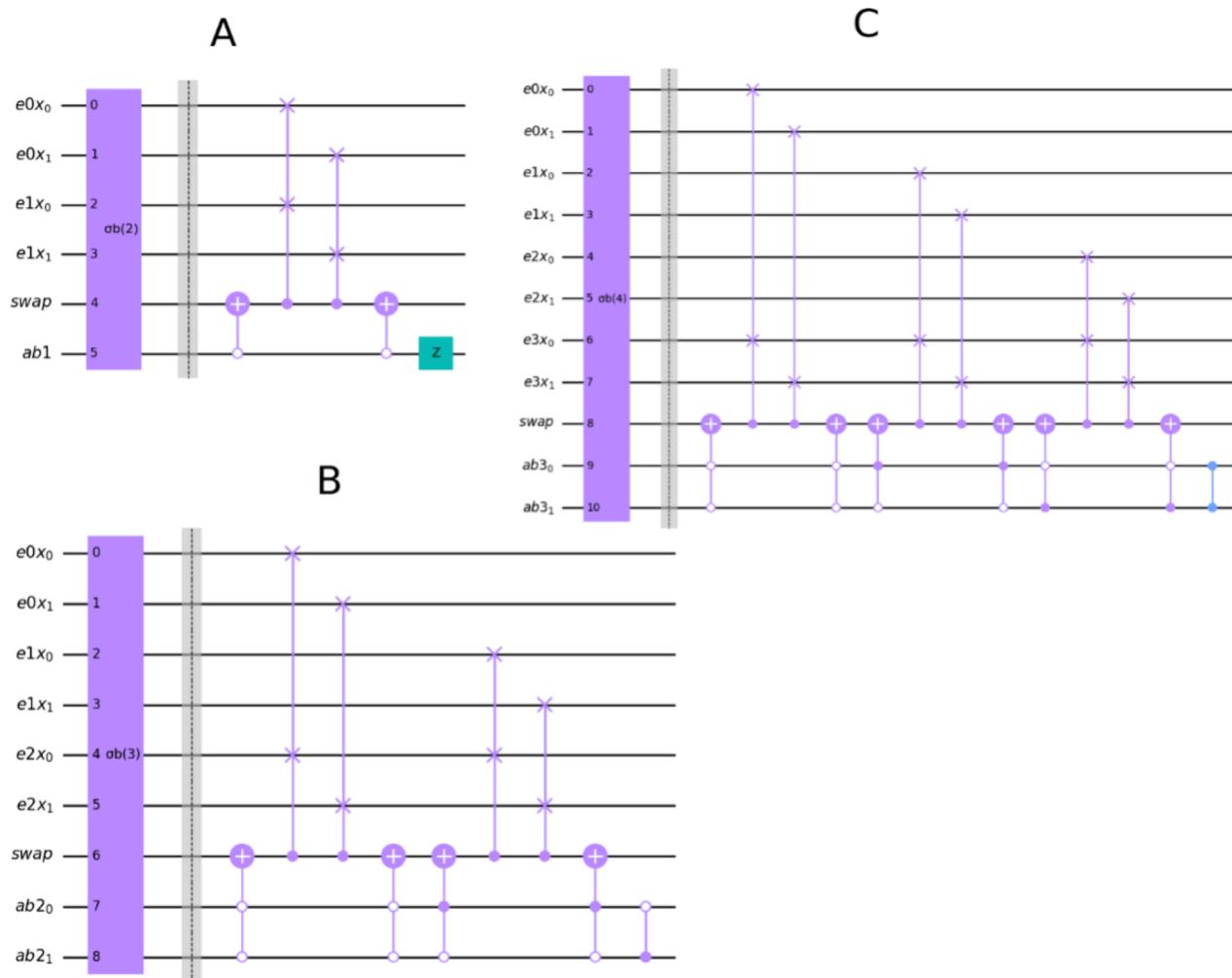

The SD gate,  $\Psi_{sd}$ , is shown in Figure 7A. This gate starts by embedding the individual orbital states and shuffles them to make 1 equiv of a Slater determinant. The shuffling is done inside a unary-coded permutation gate  $S_u$ . The subscript “u” signifies that the gate uses unary coding internally instead of binary coding. Later, we will show binary-coded versions of these gates.

After the coordinate qubits are set to a predetermined distribution by the state embedding gates,  $emb(n)$ , the  $S_u$  gate is applied. The content of the  $S_u$  gate is shown in Figure 7B. Each ancilla register  $auk$  is initialized to a  $k$ -sequence state  $|k_\Sigma\rangle$  by the sequence preparation gate,  $ku_\Sigma(k)$ .  $|k_\Sigma\rangle$  is used by the unary-coding-based shuffling gates,  $\sigma_u(k)$ . A gate sequence of  $XZX$  is inserted before the shuffling gates when  $\eta$  is even. This is to cancel an artificial global phase  $\pi$  added in the circuit in Figure 9. The input to  $XZX$  is  $|0\rangle$ , so the  $XZX$  sequence adds a global phase of  $\pi$ . The purpose of this article is as follows. There are three, or  $\eta - 1$ , shuffle gates  $\sigma_u(k)$  shown in Figure 7B. As will be

**Figure 3.** Electron P.E. time evolution gate,  $\Theta_{ep}$ , shown as a single gate on the left and its internals on the right.  $e0x_0$  through  $n0x_2$  are the coordinate qubits, and  $tmp0$  through  $tmp12$  are temporary qubits on the outside of the gate. Those temporary qubits are assigned more specific names inside the gate. The first  $X$  gate sets the MSB of the 4-bit fixed-point value ( $one_3, one_2, one_1, one_0$ ) to 1.000 in binary. This value is later used as the numerator of  $1/e0_x - n0_x$ . The  $ssubv(3,3)$  gate is a signed subtraction that computes  $e0x - n0x$  and sets the result to  $e0x$ . The bit assignments of the arithmetic gates are explained in [Appendix A](#). The  $abs(3)$  gate converts the subtraction result to its absolute value and stores the sign bit on the  $sign0$  bit for later use.  $msb1$ , which is initialized to 0 is added to the denominator to make the bit-count of the numerator and denominator match, whereby our implementation of the divisor gate produces 1.1111 (all bits set to 1) as quotient for the division-by-zero case, which is mathematically wrong but most reasonable; in other cases, 1.1111 is not obtained. Then  $udiv(4,4)$  computes the quotient  $1.000/e0_x - n0_x$ . The following phase gates are applied to the results of the division. The phase shift is executed according to the bit-wise results. After that, the arithmetic operations are executed in reverse order, restoring the qubit values to their original values except for the phase, which is not restored. The second  $X$  gate on the  $one_3$  bit should be rendered as the final gate in the sequence but appears in front of the  $ssubv(3,3)$  gate. This is due to the circuit drawing algorithm of Qiskit, which rearranges the display order of gates within a range that does not affect the result. In this case, the  $ssubv(3,3)$  gate does not affect the qubit labeled  $one_3$  bit, so changing the location of the  $X$  gate to a point before or after the  $ssubv(3,3)$  gate does not change the result.

**Table 3. Bit-count Breakdown of Registers Shown in Figure 3**

| label                 | count       | description                                                                                       |

|-----------------------|-------------|---------------------------------------------------------------------------------------------------|

| $e0x_0, \dots, e0x_2$ | $\eta dn_1$ | coordinates of electrons                                                                          |

| $n0x_0, \dots, n0x_2$ | $L_n dn_1$  | coordinates of nuclei                                                                             |

| $one_0, \dots, one_3$ | $n_1 + 1$   | numerator 1.0                                                                                     |

| $sign_0$              | 1           | ancilla for abs gate                                                                              |

| $msb_1$               | 1           | bit added to the MSB side of the divisor to make the bit-count coincide with that of the dividend |

| $zz_2, \dots, zz_5$   | $n_1 + 1$   | quotient                                                                                          |

| $tmp_0, \dots, tmp_2$ | $n_1$       |                                                                                                   |

explained in [Figure 9](#), each shuffle gate adds a global phase of  $\pi$ . When  $\eta$  is odd, an even number of  $\pi$  phases are added so they cancel out. In contrast, when  $\eta$  is even, an odd number of  $\pi$  phases are added so the phase remains. The global phase does not affect the result of the circuit, but when the circuit is run on a quantum computer simulator for debugging and the state vector is inspected directly, this global phase appears and may be confusing when judging if the result is correct. Hence, the global phase is compensated here to ease debugging.

Shuffling gate  $\sigma u(2)$  permutes  $|\phi_0\rangle$  and  $|\phi_1\rangle$  by using  $|2_\Sigma\rangle = \frac{1}{\sqrt{2}}(|11\rangle + |00\rangle)$ ; shuffling gate  $\sigma u(3)$  permutes  $|\phi_0\rangle$ ,  $|\phi_1\rangle$  and  $|\phi_2\rangle$  by using  $|3_\Sigma\rangle = \frac{1}{\sqrt{3}}(|100\rangle + |010\rangle + |001\rangle)$ ; the case for  $k = 4$  follows this pattern. Note that  $|2_\Sigma\rangle$  does not follow the rule of unary coding. That is,  $|2_\Sigma\rangle$  should be  $\frac{1}{\sqrt{2}}(|10\rangle + |01\rangle)$

**Figure 4.** (A) Electron K.E. time evolution gate,  $\Theta_{ek}(p)$  (B)  $n$ -element inverse quantum Fourier transform gate,  $nQFT^\dagger$ , for  $d = 1$ ,  $n = 3$ , and  $\eta = 1$ .

according to the rule, but the downstream circuits need only one of the two bits. Thus, the LSB of register  $au1$  is omitted as a qubit-saving optimization.

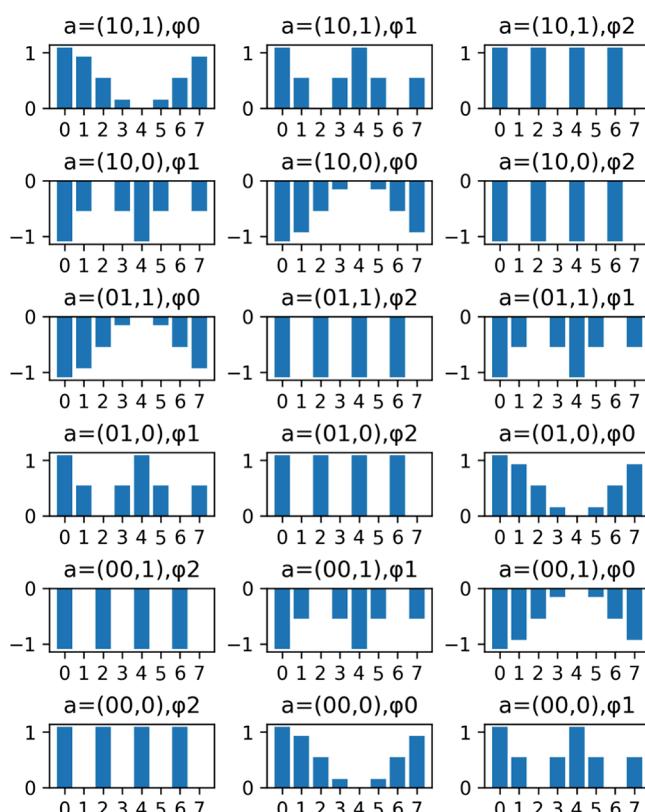

The sequence preparation gate  $ku_\Sigma$  for  $k = 2, 3$ , and  $4$  is shown in Figure 8. A CNOT gate follows each  $R_y$  gate. Thanks to the pair, only one of the output qubits is  $|1\rangle$ ; the other qubits are  $|0\rangle$ .

The unary-coded conditional shuffling gate,  $\sigma u(k)$ , for  $k = 2, 3, 4$  is shown in Figure 9. This gate shuffles the coordinate registers based on the value of  $au(k - 1)$ . Since  $au(k - 1)$  is unary-coded, its value is represented by the single bit within the bits of register  $au(k - 1)$  that is set to  $|1\rangle$ . Note that for the case of  $k = 2$ , we omit the LSB of register  $au1$ , so the remaining bit is the second bit of the original  $au1$ . Now, let  $l$  be the index of the  $|1\rangle$  bit within the bits of register  $au(k - 1)$ , i.e., the bit  $au(k - 1)_l$  is  $|1\rangle$ . The basic intent of the shuffle gate is to do nothing when  $l$  takes the greatest value,  $k - 1$ ; when  $l < k - 1$ , to swap the contents of the coordinate registers of index  $l$  and  $k - 1$  and at the same time negate the sign by adding  $\pi$  to the phase. When implementing this function in gates, it is easier to add the  $\pi$  phase for the inverse condition, i.e., when  $l = k - 1$  instead of when  $l < k - 1$ . This can be achieved using a single  $Z$  gate on the bit  $au(k - 1)_l$ . Different from the basic intent of the gate, this would add a global phase of  $\pi$ , but the added phase does not affect subsequent operations. This is why the global phase of  $\pi$  is added by each  $\sigma u(k)$  gate, as is mentioned in Figure 7.

Binary-coded versions of the sequence preparation gates and conditional shuffling gates can also be constructed. Here, the trade-off between the unary and binary versions is that the unary versions consume more qubits, but require fewer gates.<sup>1</sup> Figure 10 shows the binary-coding-based permutation gate  $S_b$ . The bit size of register  $ab(k - 1)$  is the number of bits required to express  $k - 1$  in binary.  $S_b$  consists of sequence preparation gates,  $kb_\Sigma(s, k)$ , and conditional shuffling gates,  $\sigma b(k)$ . Its structure is similar to that of  $S_u$ . Here,  $s$  is the number of qubits for constructing the register  $abk$ . For the same reason as the unary-coded version, a sequence of  $XZX$  is added when  $\eta$  is an even number to ease testing and debugging of the circuit based on the

inspection of the state vector. The  $XZX$  gates are not needed otherwise.

Figure 11 shows the binary-coded sequence preparation gate  $kb_\Sigma(s, k)$  for  $k = 2, 3, 4$ , and  $6$ ;  $s$  is  $1, 2, 2$  and  $3$ , respectively. The structure of this gate is dependent on  $k$ . When  $k$  is a power of  $2$ , the gate is constructed solely from  $H$  gates (the cases of  $k = 2$  and  $k = 4$  are illustrated). For the other cases, it is recursively constructed, as shown for  $k = 6$ .

Figure 12 shows binary-coded conditional shuffling gates  $\sigma b(k)$  for  $k = 2, 3$ , and  $4$ . The coordinate registers are swapped, depending on the value of the  $abk$  register. This value is the binary-coded integer held in the bits of  $ab(k - 1)$ . Let  $l$  be that value. The intent of this gate is the same as that of the unary-coded version shown in Figure 9; i.e., when  $l = k - 1$ , do nothing; when  $l < k - 1$ , swap the  $(k - 1)$ -th coordinate register for the  $l$ -th coordinate register and add a phase of  $\pi$ . However, it is easier to construct a circuit that adds the phase on the inverse condition, i.e., when  $l = k - 1$ . This can be achieved by using a  $Z$  gate in A, the controlled- $(-Z)$  gate in B, and the controlled- $Z$  gate in C. These circuits each add a global phase of  $\pi$ , which causes the artificial global phase mentioned in the description of Figure 10.

**3.1.4. Mixed State Preparation Configuration.** The fourth and final example highlights how a mixed state can be prepared, which is a model of excitation, thereby making chemical reactions possible. We will consider a model with one dimension, 2-bit coordinates, two electrons, one nucleus, and four sets of initial wave functions. The difference between this circuit and the previous examples is the state preparation gate. In place of the SD preparation gate that we have shown, we introduce the general state preparation gate,  $\Psi_g$  (Figure 13 A; see also ref 1, Section 4.2). Four  $\Psi_{sd}$  gates prepare four sets of wave functions. They are given different orbital data to initialize the coordinate qubits. The configuration preparation gate,  $\rho$  (Figure 13B) is responsible for setting the control bits for the wave function preparation gates according to the intended probability distribution.

**Figure 5.**  $\Theta_{\text{ep}}$  for 2-D coordinates ( $d = 2$ ,  $n = 4$ ,  $\eta = 1$ , and  $L_n = 1$ ). The overall circuit is omitted since it is analogous to the first example. Only the electron P.E. time evolution gate,  $\Theta_{\text{ep}}$ , is shown. It is followed by the inverses of all of the arithmetic gates in reverse order (not shown in the diagram) to restore the calculation result to the original state.

**Table 4. Bit-count Breakdown of Registers Shown on Figure 5**

| label                                       | bit count       | description                                                   |

|---------------------------------------------|-----------------|---------------------------------------------------------------|

| $\text{one}_0, \text{one}_1, \text{one}_2$  | $n_1 + 1$       | the numerator 1.0                                             |

| $\text{square}_0, \dots, \text{square}_7$   | $d \times 2n_1$ | $d$ sets of square results                                    |

| $\text{msb}_8$                              | 1               | carry for the uaddv gate                                      |

| $\text{msb}_9$                              | 1               | MSB added to make the bit-count of the square root input even |

| $\text{sqrt}_{10}, \dots, \text{sqrt}_{12}$ | $n_1 + 1$       | result of square root                                         |

| $w_{13}, \dots, w_{16}$                     | $n_1 + 2$       | ancilla bits required by square root                          |

| $zz_{17}, \dots, zz_{19}$                   | $n_1 + 1$       | quotient                                                      |

| $\text{tmp}_0, \dots, \text{tmp}_4$         | $2n_1 + 1$      | carry bits for the sqrt gate                                  |

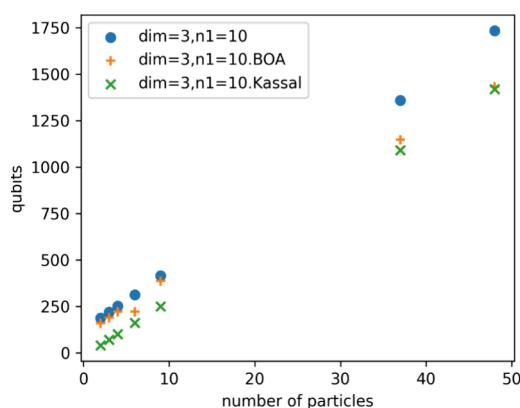

**3.2. Evaluation of the Qubit Count for Different Model Sizes.** The qubit counts of the generated circuit for several atom combinations are shown in Figure 14. The qubit counts scale as

$O(\eta \log \eta)$  with respect to the number of particles as given by eqs C-7 and C-8. The circuit generator can be configured to apply the Born–Oppenheimer approximation (BOA). When the BOA is applied, the coordinates of the nucleus are treated as constants and the qubits used to store the nuclei coordinates are omitted, thus requiring fewer qubits. Estimates by Kassal<sup>4</sup> are shown for comparison. The differences from Kassal’s estimate are discussed in Section 6.1. The breakdown of the qubit count is described in Appendix C.

## 4. DESIGN OF THE IMPLEMENTATION

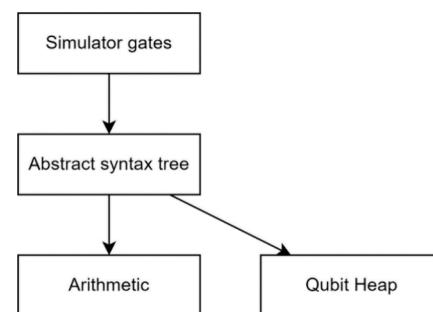

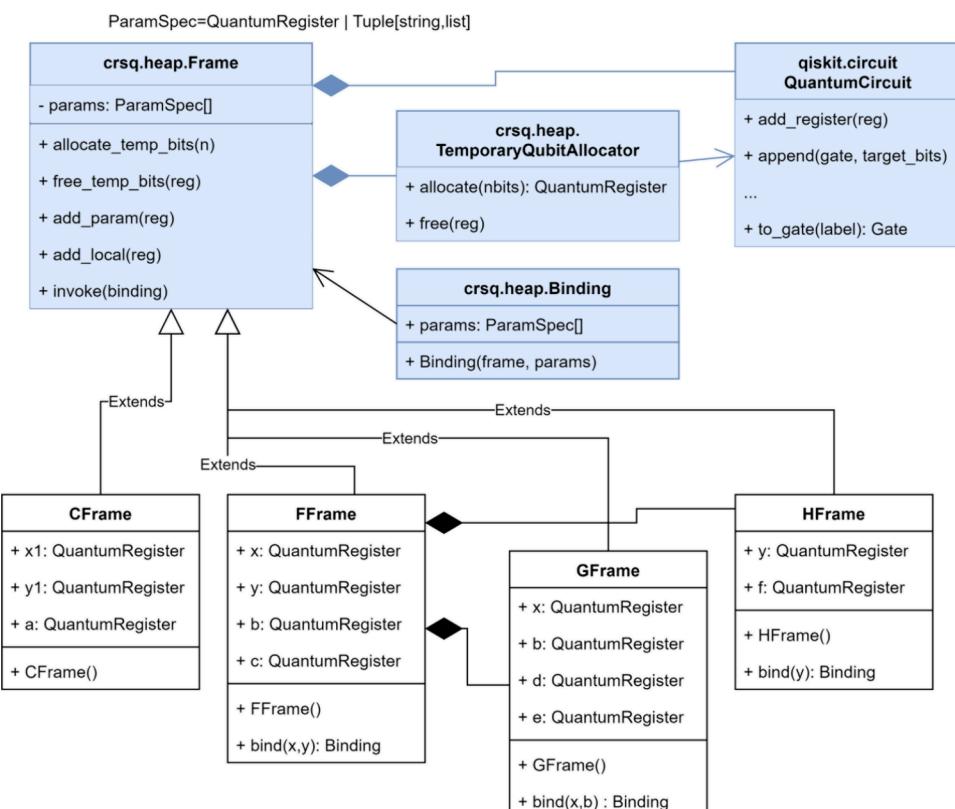

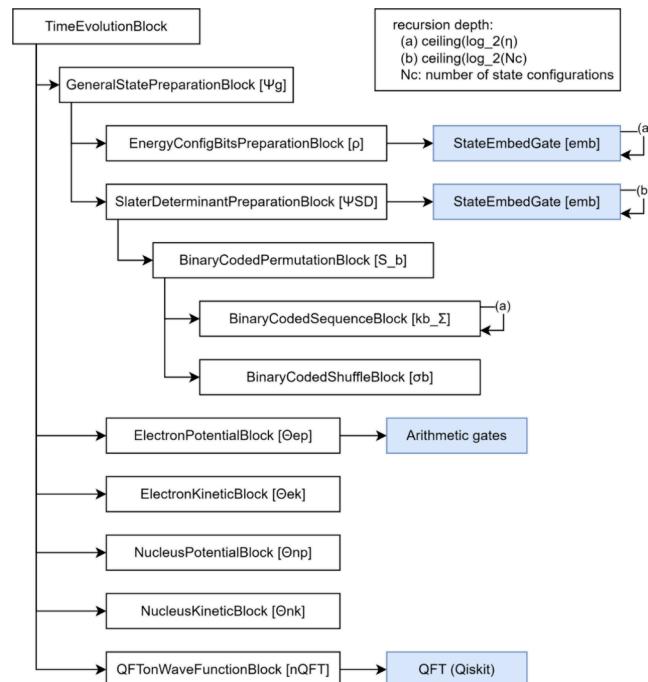

**4.1. Program Structure.** The simulator program consists of four components (Figure 15). The first component is the arithmetic component, which provides functions to build circuits for operations such as addition and subtraction. The second component is the qubit heap component, which maintains a heap or pool of qubits that can be assigned as

**Figure 6.** Circuit diagram of the overall circuit for the third example with four electrons ( $d = 1$ ,  $m = 2$ ,  $\eta = 4$ , and  $L_n = 1$ ). The difference from the preceding examples is that the SD gate,  $\Psi_{sd}$ , appears as the first gate. It takes additional ancilla registers  $au1$ ,  $au2$ , and  $au3$  which comprise the register set “a” in the formulation for state preparation. The registers are used to create a representation of  $|\eta\rangle$  and that value is used for shuffling the coordinate qubits.

temporary qubits required by arithmetic circuits. The third is the abstract syntax tree component, which provides node classes for a tree structure that represents a calculation of a formula. It uses the arithmetic and qubit heap components as subcomponents and provides a high-level interface on top of the arithmetic component. The fourth is the simulator gates component, which contains all of the gates that are specific to Hamiltonian simulation. It uses the abstract syntax tree component.

These components are described in the following subsections.

**4.2. Arithmetic Component.** The arithmetic component provides generator functions for the arithmetic circuits. The

time-evolution algorithm requires certain arithmetic operations to be executed on values represented as qubit states. These operations thus work on superposition states, wherein one execution of the circuit entails operations on multiple values. The circuits can be generated by calling one of the generator functions in this component. The functions come in two forms, instruction emitting functions and gate-creating functions, described as follows:

- Instruction emitting functions: These functions implement a specific arithmetic operation by emitting

**Figure 7.** SD preparation gate,  $\Psi_{sd}$ , is based on unary encoding. (A) the  $\Psi_{sd}$  gate on the left and its internals on the right. The  $\Psi_{sd}$  gate consists of a number of state embedding gates,  $emb(2)$ , and a unary-coded permutation gate,  $S_u$ . (B) Unary-coded permutation gate,  $S_u$ . This gate consists of unary-coded sequence preparation gates,  $ku_{\Sigma}(k)$ , that each produce a superposition state of  $\sum_{i=0}^{k-1} |i\rangle / \sqrt{k}$ . Index  $i$  is provided to the unary-coded conditional shuffling gates,  $\sigma u(k)$ . These gates conditionally swap the amplitudes of the coordinate qubits for electrons designated by the values of  $i$  and  $k - 1$  of the  $auk$  registers. A sequence of  $XZX$  is inserted in front of the  $ku_{\Sigma}(2)$  gate to cancel the global phase  $\pi$  that will be added by the three shuffle gates  $\sigma u(2) \dots \sigma u(4)$ . The bit to apply this gate sequence is not restricted to the single qubit of register  $au2$  and can be added to any qubit of B that has an initial value of  $|0\rangle$ . Any qubit of any register  $auk$  meets this condition.

elementary gates such as C-NOT gates. All such gates are visible in the resulting circuit diagram. This is useful when verifying the internal gates of an arithmetic operation.

- Gate-creating functions: These functions create a custom gate that implements an arithmetic operation. In Qiskit, a user-defined quantum circuit can be converted into a custom gate and can be used in the same way as standard gates provided by the quantum computer. In the resulting circuit diagram, the custom gate is represented by a single box, and the internal elementary gates are hidden. This is useful when verifying connections in a sequence of arithmetic gates because the internals of each gate are ignored.

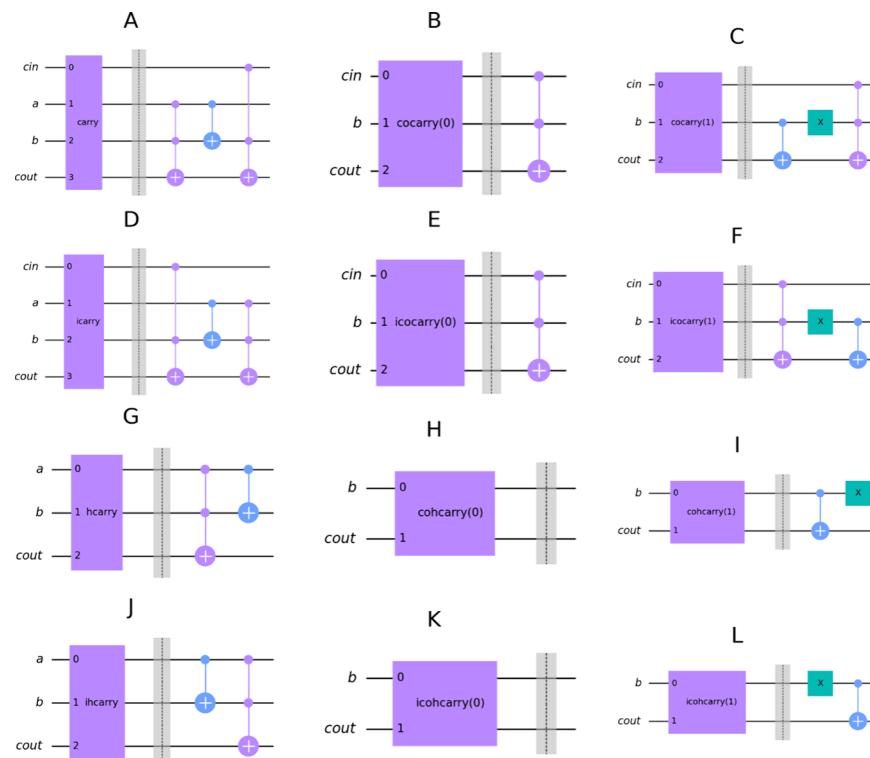

In the context of the time-evolution calculation based on the Schrödinger equation, arithmetic operations are required for computing the potential energy terms of the Hamiltonian, which computes the inverse of the distance between two coordinates. This requires subtraction, multiplication, addition, square root, and division operations. For a one-dimensional model, the distance calculation can be simplified to an absolute value function. The choice of operations to be implemented is based

on these needs. The design of the adder circuit is from Vedral et al.,<sup>12</sup> while the constant value adders and subtractors, and the absolute value were designed as part of this work. The rest are from Tomaru.<sup>1</sup> (See the references of Tomaru<sup>1</sup> for other circuit design proposals in the literature.)

- Adders: Several variations of adders are implemented. The unsigned adder takes two unsigned integer values of equal bit length and produces a value with one bit more to store the carry bit. The signed adder takes two signed integer values and produces a value with the same length as the inputs. A constant value adder takes the first input value in the form of qubits and the second input value in the form of a constant that is known at circuit generation time. Variations that take uneven length input values are also implemented.

- Subtractors: Variations analogous to the adders are implemented for subtractors. Unsigned, signed, and constant value subtractors, as well as their uneven length versions, are implemented.

- Multipliers: An unsigned multiplier, a signed multiplier are implemented.

**Figure 8.** Unary-coded sequence preparation gates: (A)  $ku_{\Sigma}(2)$ , (B)  $ku_{\Sigma}(3)$ , (C)  $ku_{\Sigma}(4)$ .

- Dividers: An unsigned divider is implemented.

- Single operand functions: A signed square, a square root, and an absolute value are implemented.

**4.3. Qubit Heap Component.** The qubit heap component provides functions and classes to deal with temporary or ancilla qubit allocation and to create target qubit lists for custom gate parameters.

In Qiskit, a sequence of instructions on qubits can be grouped into an atomic unit. There are two types of atomic units: a custom instruction and a custom gate. The two are similar in functionality, but custom gates are unitary and have the additional capability of having control bits added afterward or being converted to a gate that has the inverse effect. All circuits can be converted to instructions, but only circuits that consist solely of gates without any instructions can be converted into gates. Here, we will refer to “gates”, but the same discussion applies for instructions.

Custom gates are an effective means of organizing complex quantum circuits hierarchically and are used extensively in our development. They work well for circuits with a small number of input registers, such as arithmetic operations. However, when we tried to apply them to larger circuits, such as a gate to execute the Hamiltonian simulation, we found it challenging to avoid mistakes when passing argument qubits to the gate.

Custom gates take an array of qubit specifiers for the target of its operation. A qubit specifier is either an integer or a Qubit

object. A Qubit object is not a physical qubit device but a class in the Qiskit SDK that holds information to identify a physical qubit by name. We mostly used Qubit objects as specifiers. The handling of the list of target qubit specifiers becomes error-prone as the number of parameters increases. Unlike in programming languages of classical computers, there is no compiler support to check whether the caller side arguments match the callee gate parameters. It is helpful to have some means to ensure that the two matches.

Besides the input and output qubits of the intended operation, the temporary qubits required by the gate must also be included in the list of parameters. Since the programmer is interested in the input and output of the gate, but not in the temporary qubits, the responsibility to supply the exact number of temporary qubits is a burden. Making matters worse is that the number of required temporary qubits is sometimes hard to determine. This is because custom gates can be nested, and the number of temporary qubits depends recursively on the nested inner gates. Any inner gate might be modified, and the number of temporary qubits they require might be changed as a result. Therefore, an automated mechanism for determining the number of temporary qubits is desired.

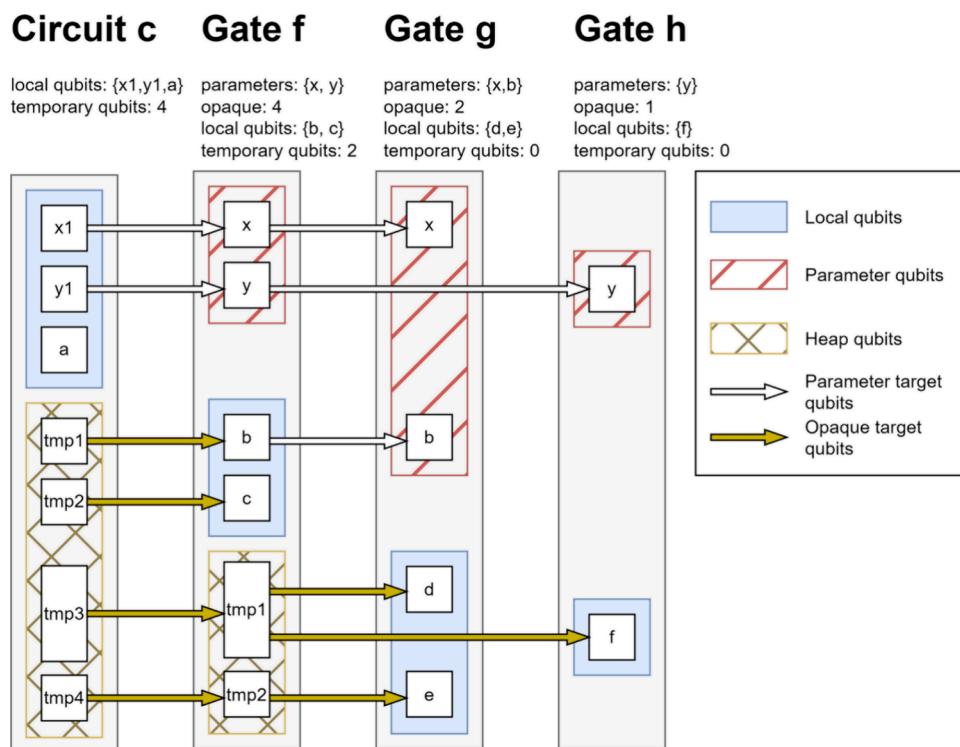

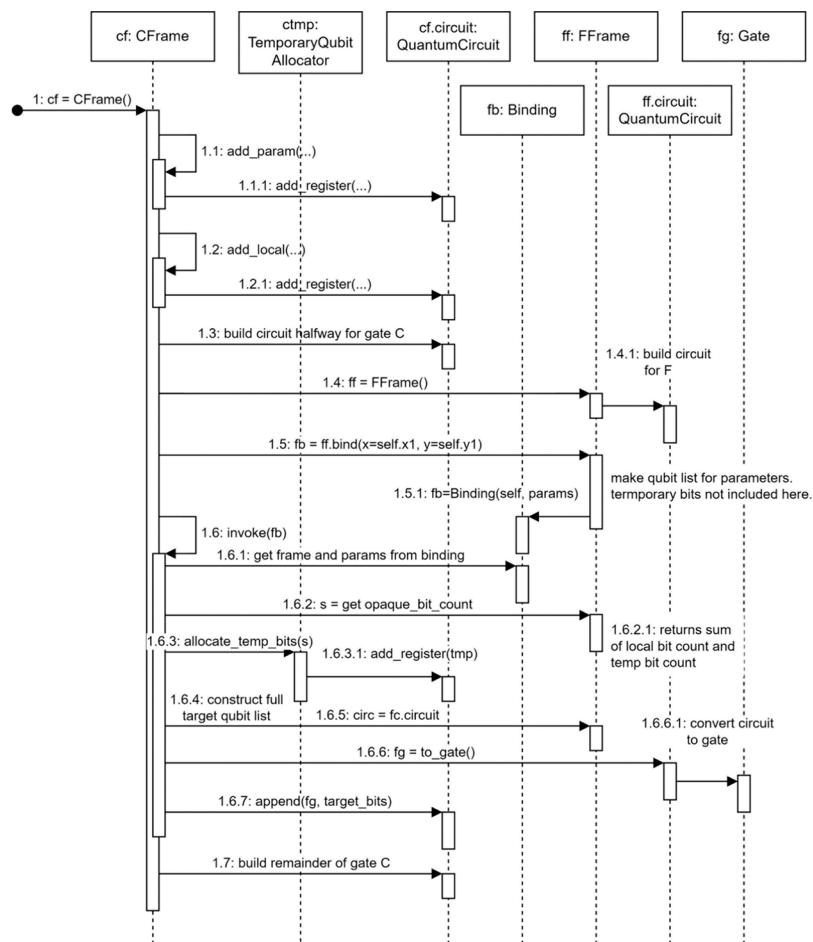

The situation is depicted in Figure 16. In the figure, circuit c invokes gate f, and gate f, in turn, invokes two gates g and h in sequence. Arrows represent the passing of target qubits from the caller to the callee. We classify target qubits into parameter

Figure 9. Unary-coded conditional shuffling gates: (A)  $\sigma u(2)$ , (B)  $\sigma u(3)$ , (C)  $\sigma u(4)$ .

target qubits and opaque target qubits. Parameter target qubits, denoted by white arrows, are target qubits whose meaning is known to the caller. Opaque target qubits, denoted by shaded arrows, are those whose meaning or usage is unknown to the caller. It only matters that the correct number of opaque qubits are passed and that their initial state is set to  $|0\rangle$ . When circuit c calls gate f, two parameters and four opaque target qubits are passed. Gate f uses the opaque qubits as two local qubits and two temporary qubits. Gate f passes two parameters and two opaque target qubits to gate g. Gate g uses the opaque qubits for two local qubits. Finally, gate f passes one parameter and one opaque target qubit to gate h. Gate h uses the opaque qubit for a local qubit.

Within a gate, the opaque qubits that have been provided by the caller of the gate are used for two purposes: (1) for use by the gate itself and (2) as a heap of temporary qubits from which opaque target qubits can be allocated when calling other subgates.

Deciding the heap size for each gate is nontrivial. For gate f, 2 is the maximum number of opaque qubits that is required at any single moment during the execution of this gate. Gate g requires 2 opaque qubits, and gate h requires 1, so the maximum of the two numbers is 2; therefore, the heap size for gate f is 2.

The orders of the parameter qubits of the caller and callee must match. The name given to the qubits for identification may be different between the caller side and callee side, such as  $x_1, y_1$  at circuit c versus  $x, y$  at gate f. Some sort of mapping must take place.

In typical programming languages of classical computers, the temporary memory allocation and mapping of parameters are

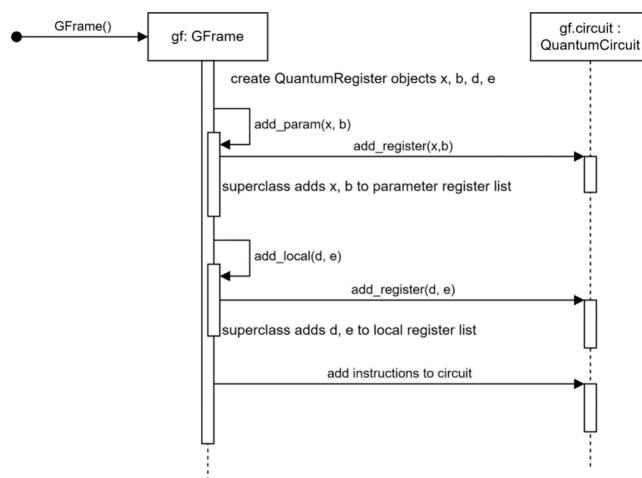

taken care of by function call mechanisms.<sup>13</sup> The callee defines a function. The caller passes parameters that match the function definition. The callee accepts those parameters. When temporary memory is required, the callee allocates space from the stack area, and no intervention from the caller is necessary. For the quantum computer case, the caller is responsible for the allocation of temporary qubits. After some exploration, we settled on a programming pattern involving two function calls to do one subcircuit call, as shown in Figure 17. The first call is on the callee side of a function named “bind”. The caller provides qubit specifiers for the arguments. The bind function puts those qubit specifiers in a list that the callee circuit expects. That list is sent back to the caller in the form of a class named “Binding”. The value is stored in a variable named “binding”. This value is given as a parameter to the “invoke” function on the caller object. This is defined in the common superclass from which the caller class must inherit from. The invoke function incorporates the instructions in the callee’s circuit into the caller circuit by using the target qubit list stored in the binding object. This pattern was inspired by the function objects found in the standard library for the programming language C++.<sup>14</sup>

The overall class structure to handle the aforementioned interaction is shown in the UML class diagram<sup>15</sup> in Figure 18. This is a set of classes that correspond to the scenario in Figure 16. The shaded classes, such as Frame and TemporaryQubitAllocator, are utility classes that can be reused for various circuits, and the white classes, such as FFrame and GFrame are classes that are specific to the circuit under concern. The white classes, CFrame, FFrame, GFrame, and HFrame correspond to circuit c and gates f, g, and h in Figure 16, and their main

**Figure 10.** Binary-coded permutation gate  $S_b$ . After a sequence of  $XZX$  gates, or a “-Z” gate, three  $kb_{\Sigma}(s, k)$  gates are applied to register set  $a$ . The results of the  $kb_{\Sigma}(s, k)$  gates are input to the binary-coded conditional shuffling gates,  $\sigma_b(k)$ . The  $XZX$  gates are for canceling an artificial global phase of  $\pi$  that is added when  $\eta$  is even. Each conditional shuffling gate  $\sigma_b(k)$  adds a global phase of  $\pi$ , as explained in Figure 12. The number of conditional shift gates is  $\eta - 1$ , so when  $\eta$  is odd, the sum of the phases cancels out, but when  $\eta$  is even, it equals  $\pi$ . That remaining phase is compensated by the  $XZX$  sequence to ease debugging by inspecting the statevector.

responsibility is to hold `QuantumRegister` objects that identify the qubits that belong to each of the gates. `Fframe`, for example, has member variables  $x, y, b$ , and  $c$  that correspond to the qubits belonging to gate  $f$ . These four classes all extend a common superclass `Frame`, which provides functionalities for temporary qubit management and target qubit list preparation. The constructor method of each class has the responsibility of generating the instructions on their circuits. It recursively calls the constructors of the subcircuits, so the overall circuit is generated by calling the constructor of the `CFrame` class.

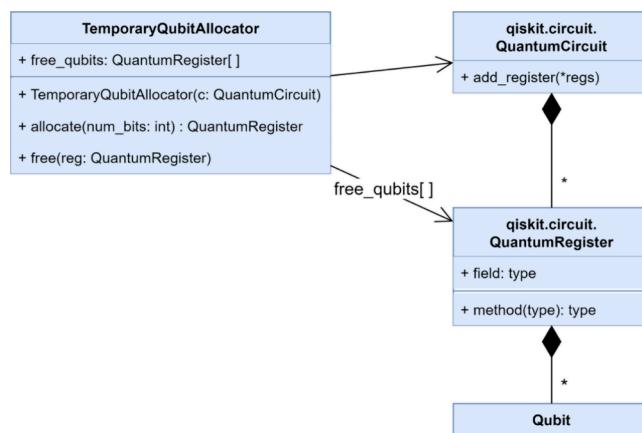

The class diagram of the utility class `TemporaryQubitAllocator` is shown in Figure 19. This class maintains a list of pooled qubits that can be borrowed from (allocated) for temporary use and returned after use. The number of qubits pooled in the list may grow to the maximum number of qubits that are simultaneously allocated during the circuit generation. It provides two methods, “allocate” and “free”. The allocator has an associated `QuantumCircuit` object, and when qubits are added to the pool, they are also added to the circuit.

Appendix B describes the circuit generation sequence in detail using UML sequence diagrams.

**4.4. AST Component.** The abstract syntax tree (AST) component provides a set of classes that lie on top of the arithmetic component to provide a higher level of abstraction in programming style for arithmetic formulas.<sup>10</sup> The AST hides the details of arithmetic gate usage, such as keeping track of the input and output registers and allocating the temporary qubits. Once an AST is constructed, it can generate sequences of arithmetic gates to compute the formula on a quantum device.

An abstract syntax tree or an abstract parse tree is a term used in compiler design. A compiler reads the source code character-by-character to recognize the syntactic tokens and their

**Figure 11.** Binary-coded sequence preparation gates,  $kb_{\Sigma}(s, k)$ . Each gate prepares an  $s$ -qubit state that has a superposition of  $0..k-1$  in the binary representation. (A)  $kb_{\Sigma}(1,2)$ , (B)  $kb_{\Sigma}(2,3)$ , (C)  $kb_{\Sigma}(2,4)$ , (D)  $kb_{\Sigma}(3,6)$ .

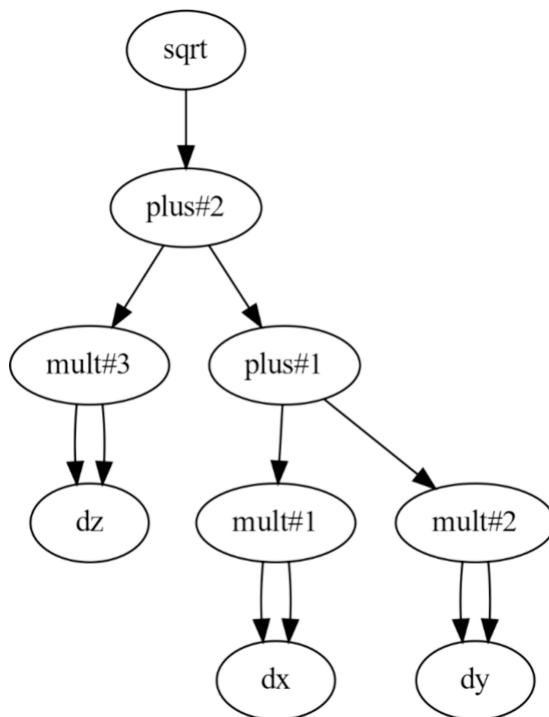

grammatical structure; after that, it constructs a tree structure, called an abstract syntax tree, as an internal representation of the recognized code. A schematic example of an AST for the expression “ $\text{sqrt}(dx \times dx + dy \times dy + dz \times dz)$ ” is shown in Figure 20.

ASTs are especially useful for representing arithmetic expressions because arithmetic expressions have a recursive tree structure. Once an AST is constructed, the target code becomes straightforward to generate. To construct the AST, we used Python’s customized arithmetic operators, whereby we can attach code that will be executed when operators such as “+” and “-” are used.

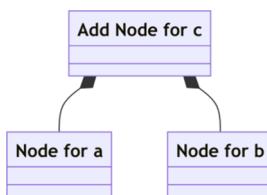

**4.4.1. Node Objects.** We designed the AST as a set of node objects that are tied together in the form of a tree. If there are two nodes  $a$  and  $b$ , then, in the program code “ $c = a + b$ ”, the “+” is a customized operator that produces a node for an add operation which points to “ $a$ ” and “ $b$ ” as its child nodes. The structure shown in Figure 21 is constructed in memory.

Later, when the circuit is generated, the tree will be traversed recursively and the gates for each node will be generated in postorder; i.e., each node is processed after all its child nodes

Figure 12. Binary-coded conditional shuffling gates  $\sigma_b(k)$ : (A)  $\sigma_b(2)$ , (B)  $\sigma_b(3)$ , (C)  $\sigma_b(4)$ .

have been processed recursively. For the case shown in Figure 21, the gates for a and b will be emitted, and after that, the gates for c will be emitted. The programmer does not need to worry about assigning the correct qubit registers for passing the results between the gates or allocating temporary work registers that the gates require.

**4.4.2. Scope Class.** A scope class is introduced in order to create the node objects and keep track of them. This class holds information related to AST nodes that belong to the same programming language scope. The scope object is obtained from the function `crsq.ast.new_scope()`.

The scope object provides methods to create leaf nodes. In typical usage of AST, the first step is to create leaf node objects from `QuantumRegister` objects that are the input for the formula. In such cases, the register method is used to create an AST node that wraps the `QuantumRegister`, as shown in Figure 22.

After the nodes are created, the circuit to compute the formula can be generated by using the `build_circuit` method. The inverse of the gates can also be generated by using the `build_inverse_circuit` method. This is often required in quantum algorithms when qubits must be returned to their initial state.

**4.4.3. Supported Operators.** The following operators are supported on node objects:  $+$ ,  $-$ ,  $*$ ,  $/$ .

The scope object provides the following functions that take one operand: `abs(x)`, `square(x)`, and `square_root(x)`.

**4.4.4. Fixed-Point Arithmetic Support.** All internal arithmetic functions are implemented as integer operations. Integer operations can be used as fixed-point fractional number operations by statically keeping track of the decimal point's location. The range of the value must fit in the register at all of the steps of the sequence of operations. A function to ensure this is implemented in the AST nodes. The numbers of fractional bits and the total bits (fractional bits and whole number bits together), a flag denoting whether the value is signed or unsigned, and the upper and lower bounds of the stored value are recorded on variables of the nodes. These variables are used for computing the total and fractional bit counts of the result of an operation or for checking the compatibility of operands before an operation. Table 5 shows the constraint on the bit count of both operands and the resulting bit count. The number of total bits is further adjusted based on the possibility of overflows, which can be determined from the value range information.

**4.4.5. Bit Count Adjustment.** In a fixed-point calculation, there may be a need to add or remove bits to or from the result of a calculation step before feeding that value to the next step. For this purpose, an "adjust\_precision" method is created on AST nodes. This method allows bits to be added to or removed from either the LSB end or the MSB end of the value represented by the node. As an example, when calculating the square root of small integer values, it may be useful to add 2 or 4 bits below the

**Figure 13.** General state preparation gate,  $\Psi_g$ , and its internals. (A) The  $\Psi_g$  gate is shown on the left as a unit, and its internals are on the right. The 2-bit version of the configuration preparation gate,  $\rho$ , prepares  $p_0$  and  $p_1$  that together store the probability amplitude of four different states.  $p_0$  and  $p_1$  control the 4 SD preparation gates,  $\Psi_{sd}$ , and each is given a different set of initial orbital data. (B) The configuration preparation gate,  $\rho$ , and its internals. The state embedding gate,  $\text{emb}(2)$ , sets the probability amplitudes.

**Figure 14.** Qubit counts with respect to different numbers of particles. Number of particles refers to the sum of the numbers of electrons and nuclei. The plots correspond to H, He, Li, H + H<sub>2</sub>, and O, glycine (C<sub>2</sub>NOH<sub>3</sub>), and alanine (C<sub>3</sub>NOH<sub>5</sub>). The plus(+) plots are results for when the circuit generator was configured to apply the BOA, i.e., to treat the coordinates of nuclei as fixed ones and omit qubits for those coordinates. The x plots are based on the formula by Kassal.<sup>4</sup>

decimal point to make it a fractional number before applying the square root gate. In this way, the result of the square root will have 1 or 2 digits below the decimal point.

**Figure 15.** Program structure.

**4.5. Simulator Gate Component.** The simulator gate component is the top-level component of the structure of the simulator program shown in Figure 15. The hierarchy of the Python classes that produce the gates is shown as a tree-structure call graph in Figure 23. It contains gates that are specific to the Hamiltonian simulation. All of the other low-level components are general-purpose and can be used in other programs besides Hamiltonian simulations. The classes in the simulator gates component generate custom gates that are shown in different configurations in Figures 1 and 13. The generated gates are described in the following subsections.