# THE CBETA BEAM POSITION MONITOR (BPM) SYSTEM DESIGN AND STRATEGY FOR MEASURING MULTIPLE SIMULTANEOUS BEAMS IN THE COMMON BEAM PIPE\*

R. Michnoff<sup>†</sup>, R. Hulsart, Brookhaven National Laboratory, Upton, NY, USA

J. Dobbins, Cornell University, Ithaca, NY, USA

## Abstract

CBETA, a 4-pass electron Energy Recovery Linac (ERL) is presently under construction at Cornell University and is a collaboration between Brookhaven National Laboratory (BNL) and Cornell University. Beam commissioning began in March 2019 with a single pass ERL configuration. Commissioning of the complete 4-pass machine is scheduled to begin in fall 2019. The fixed field alternating gradient (FFA) return loop for CBETA uses Halbach permanent magnets with a common beam pipe for seven different energy beams (4 accelerating energies and 3 decelerating energies). One of the most challenging requirements for the CBETA BPM system is to independently measure the position of each of these beams. The overall design of the CBETA BPM system and the techniques planned to measure the position of each energy beam will be presented.

## INTRODUCTION

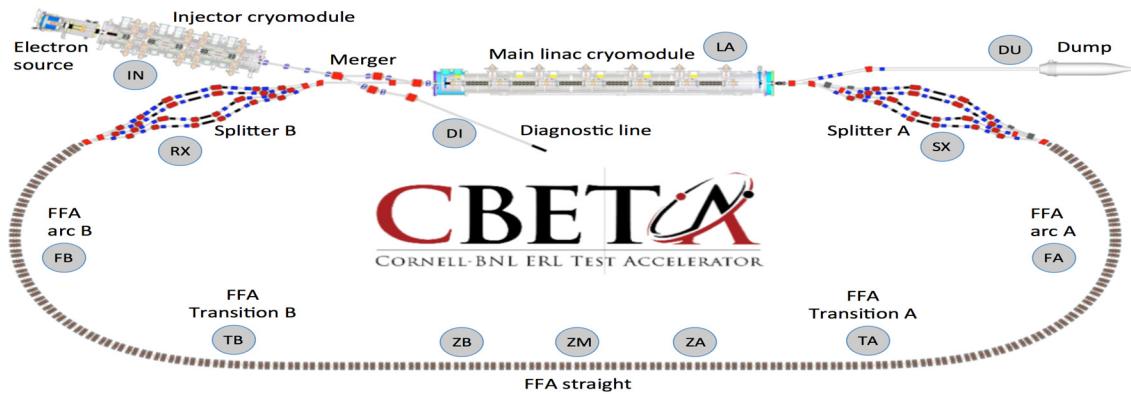

The full CBETA machine layout is shown further in this document (figure 4). The 6 MeV beam from the injector is accelerated by 36 MeV with each of 4 passes through the Main Linac Cryomodule (MLC) up to 150 MeV. The beam is then decelerated for 4 additional passes down to 6 MeV when the beam is sent to the dump line. Four splitter lines are provided on each end of the MLC, one for each of the 4 energies (42, 78, 114, 150 MeV), and are used to provide path length matching back to the MLC. The 150 MeV splitter path length includes an extra half RF period to cause the beam to begin the deceleration sequence through the next 4 MLC passes. Each loop of the beam travels through the common FFA beam pipe section [1].

## BUNCH PATTERN

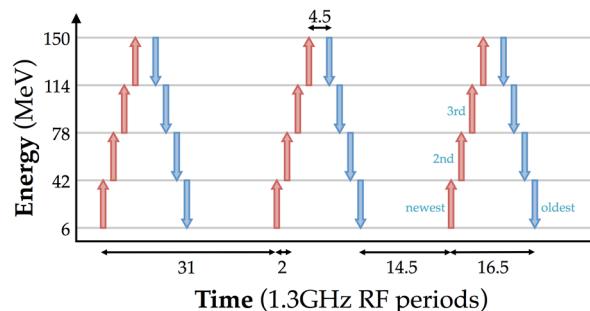

Before describing how the BPM system will measure each energy bunch, an explanation of the bunch pattern must first be provided. A bunch is injected every 31 1300 MHz RF periods, resulting in an injection rate of  $1300/31 = 41.935$  MHz. For splitters 1 (42 MeV), 2 (78 MeV) and 3 (114 MeV), the number of RF periods per turn is 343. With injections every 31 RF periods, 11 bunches are injected each turn with an injection turn rate of 341 RF periods, resulting in a newly injected bunch preceding the bunch injected on the previous turn by 2 RF periods. For splitter 4 (150 MeV) the number of RF periods per turn is

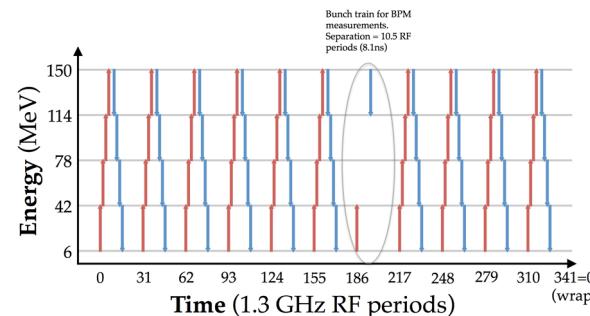

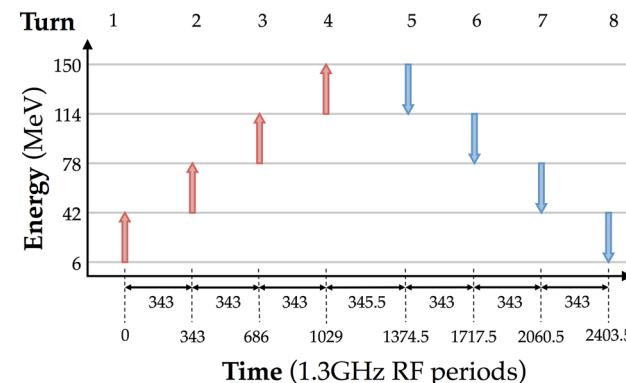

345.5 resulting in a bunch spacing of 4.5 RF periods between the 150 MeV bunch and the decelerating 114 MeV bunch. Figures 1-3 provide images of this explanation. Figure 4 shows the layout of the CBETA machine.

Figure 1: Bunch spacing within and between typical bunch trains as seen from the perspective of the MLC. Each bunch train is a group of accelerating and decelerating bunches. Three trains are shown here.

Figure 2: One full turn of all 11 CBETA bunch trains.

Figure 3: Number of RF periods between turns for a single bunch making 8 passes through the MLC, traversing through all of the accelerating and decelerating energies. Note that the number of periods between turns 4 and 5 is 2.5 more than the others. This is where the beam passes through splitter 4, which has a longer path length.

Figure 4: Layout of the CBETA machine. The machine circumference is 79m.

## POSITION MEASUREMENT METHOD

For the typical 2 RF period beam separation (1.5 ns), the bunch signals overlap and are therefore not usable for measurement of one selected energy. Therefore, one of the 11 bunch trains will provide larger bunch spacing specifically for BPM measurements. This dedicated bunch train includes one accelerating bunch and one decelerating bunch with a spacing of 10.5 RF periods (8.1 ns). This pattern is generated by injecting only one bunch every 4 turns for that bunch train only, resulting in 4 different energy pairs that repeat every 4 turns.

A bunch spacing of 8.1 ns still presents challenges for BPM measurements. The common technique of undersampling a ringing band-pass filter signal is not an option since typical band-pass filters ring for 50 ns or more.

The technique selected for CBETA BPM measurements is to acquire a single sample on the peak of the selected energy bunch. This requires a low jitter analog to digital converter (ADC) clock that is locked to the RF system, and ADC clock timing adjustments with adequate resolution to trigger on the peak of the bunch signal. This was first successfully tested during the fractional arc test in April and May 2018 [2].

## THE BPM HARDWARE

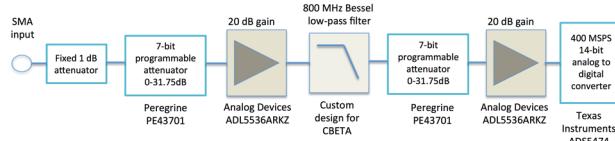

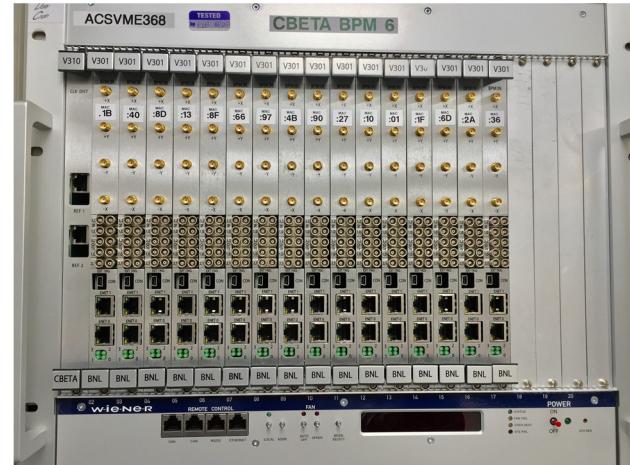

The BNL designed V301 BPM board has been selected for the CBETA BPM system [3]. This is a VME form factor module based on the Xilinx Zynq gate array and TI ADS5474 400 MSPS ADC converter. A custom low-pass filter was designed to broaden and smooth the incoming electron signal from the buttons. Figure 5 provides a block diagram of the RF front end and Fig. 6 provides a photo of a fully populated chassis. The complete system includes over 160 modules distributed in 12 VME chassis.

Figure 5: CBETA V301 BPM module analog signal chain (1 of 4 channels shown).

Figure 6: Photo of fully populated VME chassis with 1 clock distribution board (V310) and 16 BPM modules (V301). The four SMA connectors on each V301 are for the 4 button signal inputs per BPM. The bottom RJ45 connector on each V301 (ENET2) is for control system Ethernet communication. The RJ45 Ref 1 signal on the V310 is for the RF clock and BPM trigger input, and the RJ45 Ref 2 signal on each V310 is for future data synchronization triggers to the V301 modules.

An RF locked 41.935 MHz clock (1300/31) and BPM trigger are fanned out to a V310 clock and trigger distribution board located in each VME chassis. These signals are distributed on the VME backplane to each V301 module via a P2 overlay board.

An AD9517-4 phase lock loop (PLL) on each V301 module uses the 41.935 MHz RF locked clock to generate a 398.387 ADC clock ( $41.935 * 38/4$ ). This ADC clock rate was selected because it is near the 400 MHz max rate for the ADS5474 and it allows perfect alignment to every other 41.935 MHz bunch.

The BPM trigger will occur synchronously with the injection of each BPM measured bunch, which is typically once every 4 turns. After configuring timing to the peak of the selected energy bunches, the selected bunch for position measurement is defined by a programmable number of ADC clocks after the BPM trigger occurs.

## MEASURING EACH ENERGY

Each energy is measured by changing the programmable timing settings for the selected energy; so up to 8 different settings must be managed within each V301 BPM module. The configurable timing settings to align the RF locked 398.387 MHz ( $1300/31 * 38/4$ ) ADC clock to the peak of the selected energy bunch consist of:

- ADC trigger delay: ADC sample number after the BPM trigger is detected. Each count =  $\sim 2.5$  ns.

- VCO delay: This is common to all 4 ADCs and is a register on the PLL component. (range: -9 to +9,  $\sim 110$  ps/count, total range =  $\sim 2$  ns).

- PLL clock phase: This is an independent value for each of the 4 ADC clocks and is configured with registers on the PLL component. (range: 0-47,  $\sim 12$  ps/count, total range =  $\sim 550$  ps).

A single ADC measurement is acquired on the peak of the selected energy bunch typically every 4 turns. Several samples are used to generate an average position measurement. The non-linearity of the standard difference/sum position calculation will not be feasible for CBETA, especially in the FFA loop where the horizontal beam positions of the various energies is expected to span  $\pm 24$  mm in the 70mm diameter chamber. The computation described in [4] is planned to be implemented in the V301 hardware and the Poisson method [5] is planned to be implemented in higher-level software.

The present plan is to implement automatic switching between all energy bunches at a 10 Hz rate via VHDL gate array code on the V301.

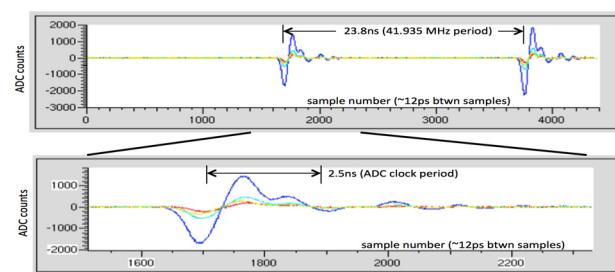

## TIMING TO THE BUNCH

Configuring the timing for each energy bunch will be performed with a profile scan. This is accomplished by sweeping the V301 ADC trigger timing through the  $\sim 2.5$  ns ADC clock period in increments of about 12 ps using the VCO delay and PLL clock phase settings and interspersing all data samples to provide a scope-like trace. For each timing setting a programmable number of values are acquired and averaged. This sweep generates about 210 samples between each ADC clock period, which provides sufficient timing resolution. A typical profile scan is shown in Fig. 7. Note that this profile scan required about 420 BPM injection triggers (210 different VCO delay/PLL clock phase settings \* 2 sample average for each setting).

The peak timing settings are determined by noting the VCO delay and PLL clock phase values used for the peak of the desired bunch. Two additional arrays are acquired during the scan – the VCO delay and the PLL clock phase setting. After finding the array element of the peak of the desired bunch, the VCO delay and PLL clock phase settings are determined by reading the same array element value in the respective arrays.

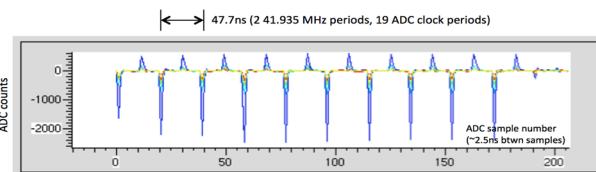

Raw ADC data for the 41.935 MHz bunch train after setting the timing values per the profile scan are shown in Fig 8.

Figure 7: FFA BPM profile scan during beam tests on May 7, 2019. ADC clock is stepped in  $\sim 12$  ps increments to fill in data between 2.5 ns ADC clock periods, resulting in  $\sim 210$  samples between ADC clock periods.

Figure 8: FFA BPM raw ADC data during beam tests May 7, 2019 after aligning the ADC clock to the bunch peak. Number of bunches is 20. Time between samples is one ADC clock (2.5 ns). The time between bunches is  $\sim 23.8$  ns (41.935 MHz bunch rate). Since a bunch is detected every 9.5 ADC clocks only every other bunch is detected at an interval of 19 ADC clocks. The small positive peaks are the in-between bunches.

## SUMMARY

Although the BPM system for CBETA presents several significant challenges, a solid plan has been developed and initial beam tests have been very successful. Locking the ADC clock to the RF locked clock has proven to be very stable and reliable.

Specific code development for sequencing through the different energy bunches is in progress and is expected to be tested with multiple energy beams in the fall of 2019.

## ACKNOWLEDGMENTS

Figures 1 and 2 showing the CBETA bunch train patterns were originally developed by Stephen Brooks.

## REFERENCES

- [1] Hoffstaetter, G. H., *et. al.*, [2017]. CBETA Design Report, Cornell-BNL ERL Test Accelerator, *ArXiv e-prints*

- [2] C. Gulliford, *et al.*, The CBETA Fractional Arc Test, September 2018

- [3] R. L. Hulsart, P. Cerniglia, N. M. Day, R. J. Michnoff, and Z. Sorrell, “A Versatile BPM Signal Processing System Based on the Xilinx Zynq SoC”, in *Proc. 5th Int. Beam Instrumentation Conf. (IBIC’16)*, Barcelona, Spain, Sep. 2016, pp. 646-649. doi:10.18429/JACoW-IBIC2016-WEPG12

- [4] P. Thieberger, *et al.*, Fast readout algorithm for cylindrical beam position monitors providing good accuracy for particle bunches with large offsets, *Review of Scientific Instruments* **89**, 043303 (2018)

- [5] A. Bartnik, Nonlinear BPM Positions using Poisson, July 2016