# MEMOIRE D'HABILITATION A ENCADRER DES RECHERCHES

# « Front-End Electronics in calorimetry : from LHC to ILC »

Christophe de LA TAILLE

soutenu le 25 septembre 2009 devant le jury :

Pr Stavros KATSANEVAS Dr Bruno MANSOULIÉ

Dr Veljko RADEKA : rapporteur Dr Félix SEFKOW : rapporteur Dr Marc WINTER : rapporteur

Dr Guy WORMSER

Laboratoire de l'Accélérateur Linéaire Orsay Micro Electronics Groups Associated IN2P3-CNRS

# REMERCIEMENTS

Je remercie tout d'abord les membres du jury: Veljko Radeka, Felix Sefkow et Marc Winter d'avoir accepté en plus de leurs multiples responsabilités, la charge d'être rapporteurs de ce travail. Je remercie également Stavros Katsanévas, Bruno Mansoulié et Guy Wormser de me faire l'honneur de faire partie du jury.

Le travail décrit couvre de nombreuses années de développement d'instrumentation, démarré sous la conduite de Bob Chase, Alex. Hrisoho et Veljko Radeka et je les remercie encore de leur enseignement et de leur soutien.

L'expérience ATLAS a servi de base à de nombreux développements nouveaux en calorimétrie tant les défis étaient nombreux à relever pour exploiter le formidable potentiel de découverte du LHC et construire les meilleurs détecteurs pour la meilleure physique. *Daniel Fournier* a été le père du calorimètre argon liquide « accordéon » et a toujours veillé à ce que les moindres détails soient tirés au clair pour que la performance reste optimisée. Je lui suis reconnaissant de la confiance qu'il m'a accordée pour les développements instrumentaux et les responsabilités qu'il m'a confiées dans la collaboration. Je remercie aussi *Laurent Serin* dont la rigueur et l'opiniâtreté ont permis que l'on obtienne toujours le maximum de la performance.

Le LHC démarrant tout juste après une quinzaine d'années de construction qu'il faut déjà développer la génération suivante : l'ILC et de nouveaux concepts de calorimétrie dédiée au « particle flow ». Là aussi, physique et instrumentation se complètent pour permettre les meilleurs détecteurs et j'ai beaucoup apprécié de travailler avec Henri Videau, Jean-Claude Brient et Félix Sefkow et la confiance mutuelle qui permet les meilleures collaborations.

Tous les développements décrits n'auraient jamais pu voir le jour sans l'aide quotidienne de *Nathalie Seguin-Moreau* et *Gisèle Martin-Chassard* qui ont depuis le début veillé à ce que rien ne soit négligé avant de passer à de nouvelles expériences et ont permis de donner corps et succès aux différents développements décrits ici.

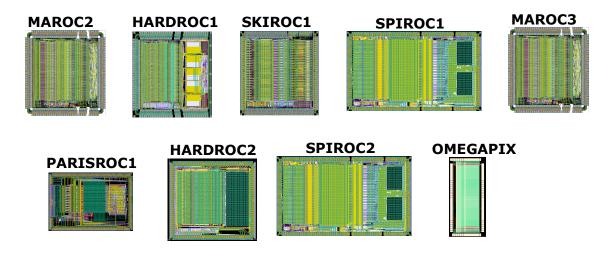

Enfin les années passant, avec l'augmentation du nombre de projets et la complexification des ASICS, c'est toute une équipe d'une douzaine de personnes qui forment le pôle de micro-électronique OMEGA et permettent la réalisation de circuits toujours plus performants dans des collaborations sympathiques. Qu'ils soient tous remerciés ici pour leur aide et leur implication dans les circuits réalisés.

Comme tente de le montrer ce rapport, la recherche est un métier formidable où l'on apprend tous les jours quelque chose de nouveau, surtout quand tout ne fonctionne pas (immédiatement) comme prévu! « Felix qui potuit cognosecere rerum causas ».

<sup>&</sup>lt;sup>1</sup> Pierre Barrillon, Sylvie Blin, Stéphane Callier, Selma Conforti Da Lorenzo, Frédéric Dulucq, Julien Fleury, Gisèle Martin-Chassard, Ludovic Raux, Nathalie Seguin-Moreau, Damien Thienpont, Yan Xiongbo

# INTRODUCTION

# 1. ATLAS and the Large Hadron Collider (LHC)

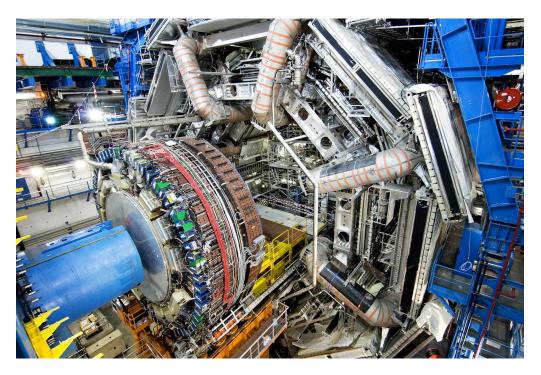

I have had the luck to start my research work on ATLAS calorimetry in 1990, when what is now the largest particle physics experiment in the world<sup>2</sup> (Figure 1) on the LHC was in its early phase<sup>3</sup> of coming from "artist views" and "conceptual drawings" to the first pieces of hardware that had to show that the calorimeter would be feasible.

Figure 1: view of the ATLAS experiment in 2008 at CERN, during insertion of the end-cap calorimeter (left).

The LHC (Large Hadron Collider) will be (is) the most powerful particle accelerator in the world, reaching energies of 14 TeV. It is installed in the 27 km long circular tunnel at CERN formerly used with electrons of 200 GeV for the LEP experiments which allowed detailed studies of the standard model for particle physics until its close-down in 2001. The LHC will allow to go above well above the present limits (currently set by LEP and by the US Tevatron) both in energy and luminosity and access to the last

$<sup>^2</sup>$  ATLAS is a worldwide collaboration of 2000 physicists from 200 countries. The detector housed at CERN (Geneva) measures 20x20x60 m<sup>3</sup>, weighs 50 000 tons and has cost 500 M€.

<sup>&</sup>lt;sup>3</sup> The first talks on the LHC date from 1984, but the official R&D only started in 1990, at the Evian workshop

missing element of the standard model: the Higgs boson. But more important, it should go beyond this model and hopefully discover the first new particles predicted by new models such as super-symmetry.

As often, calorimeters were crucial detectors to exploit the physics potential of the accelerator and in particular fulfil the first goal of the LHC which is the Higgs boson discovery in the most probable mass region of 120-200 GeV. However, it required a strong R&D effort in order to handle the huge collision rate of 40MHz and the high beam energy of 14 TeV, which on top generated a high radiation environment. Moreover, the small branching ratios for the Higgs boson detection in two photons or four leptons requires a high measurement accuracy, better than 1% on the calorimetric energy.

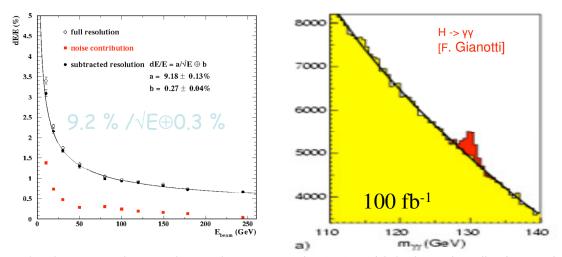

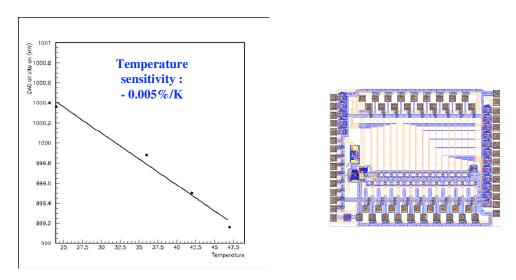

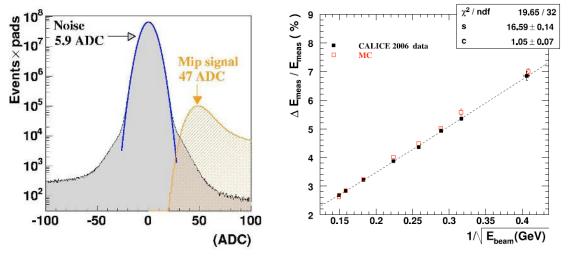

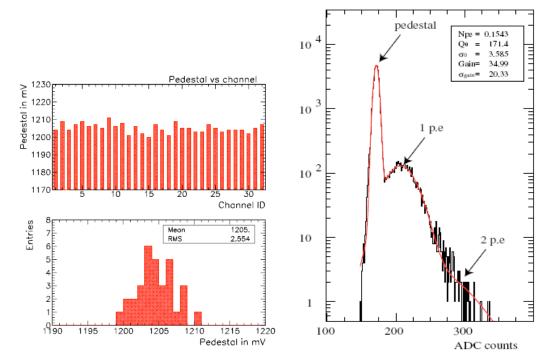

As will be seen in all this document, electronics performance plays an important role in the detector performance and physics. In the calorimeter resolution (Figure 2):

$$\frac{\sigma(E)}{E} = \frac{a}{E} \oplus \frac{b}{\sqrt{E}} \oplus c$$

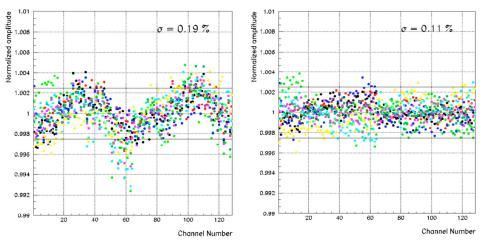

the first term (a/E "noise term") is due to the electronics noise and the last one ("constant term") comes mostly from non uniformities in the readout electronics that can be largely corrected by a good electronics calibration. This last term becomes all the more important at the LHC since the energy reached is unprecedented. The electronics performance is thus essential to obtain a good uniformity and stability energy response, as shown in Figure 2

Figure 2: <u>Left</u>: Energy resolution as a function of energy, measured on ATLAS module 0. After quadratically subtracting the noise term coming from the electronics,, the resolution goes from the black dots to the red ones and can be fitted as 9%/E (+) 0.3%. This small constant term is essential to get good resolution at the very high energies reached by the LHC and is also partially dependent on electronics performance. <u>Right</u>: signal from a Higgs decaying in 2 photons measured in the calorimeter. The signal appears in red on top of the irreducible physics background in yellow. The width of the red "spike" is determined by the calorimeter resolution, which needs to be around 1% at 100 GeV in order to resolve in from the background. (plots from [1])

For the electromagnetic calorimeter, the liquid argon technology has rapidly been chosen by the ATLAS proto-collaboration for it excellent stability, precision and uniformity. The slow speed issue had been overcome by the accordion geometry proposed by *D. Fournier* which shaped the absorbers in zigzag in order to form a projective tower while getting the signals on the front and rear face with minimal inductance<sup>5</sup>.

I worked at the beginning on the preamplifiers and shaping. As there is no gain in liquid argon, preamplifiers are key elements for low noise performance. Several technologies were in competition among several groups (AsGa, JFET, Bipolars...) and in the end the noise performance turned out not to

<sup>&</sup>lt;sup>4</sup> Mostly but not only, as mechanical dispersions, dead material... also affect the constant term. The main difference with respect to electronics is that this cause of non-uniformity does not vary in time and can thus me more easily corrected

<sup>&</sup>lt;sup>5</sup> It also minimized the projective cracks that bring the signals out.

be the main parameter for choice, as much as reliability, dead space and power dissipation also affected the overall performance. The performance and choice of preamplifiers will be described in Chapter 1, section 2. The shaping, essential to optimize the signal to noise ratio will be described in section 3, from a theoretical point of view and then in the practical realization of an ASIC in BiCMOS 1.2 µm AMS. After a few years of R&D, progress in analog pipelines made possible to digitize several samples on the waveform instead of the sole peak value so far used. This allowed the new technique (in our field) of digital filtering called "multiple sampling" introduced by *B. Cleland* to improve the signal to noise ratio and adapt to the changing luminosity. The first results turned out to be not as good as predicted by theory and with *L. Serin* and our PhD student *Y. Jacquier*, we tried to understand what was happening and study how close we could come to theory. This is described in section 4 of Chapter 1.

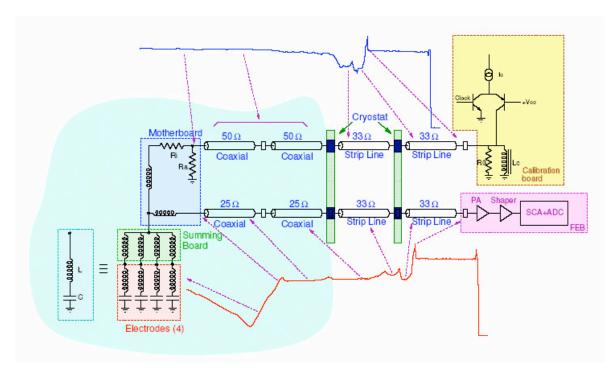

As all people working in calorimetry know, calibration is an essential feature of precision measurements over a huge number of channels. Liquid argon benefited of the reputation of being "easy to calibrate" as there is no internal gain and the cryogenic operation provides very stable temperature conditions. The main source of signal variations resides in the readout electronics which is followed and corrected by applying a known (and stable) reference electrical signal to the input. With the fast shaping, large dynamic range and high radiation levels at LHC, it turned out to be not so easy to generate 0.2% accuracy pulses over a 16 bits<sup>6</sup> over around 200 000 channels! This required a long effort, which was spurred by *L. Serin* and described in Chapter 2. The pulse distribution is explained in the first section, in particular concerning the influence of the cables bringing-in the pulses. The pulse generators which need to generate signals mimicking the liquid argon pulse with an excellent precision both in amplitude and pulse shape over 16 bits are described in the second section. A first version was developed in discrete components for module 0 tests. It was subsequently moved in radiation hard custom integrated circuits as described in the third section. The performance in ATLAS environment is shown in conclusion.

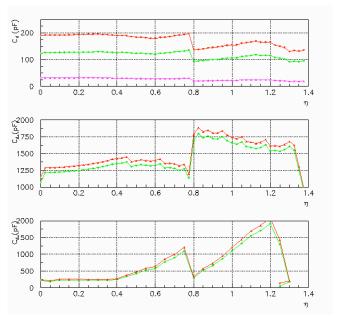

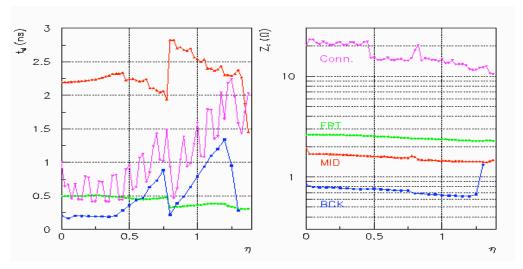

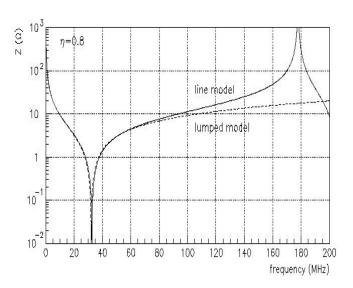

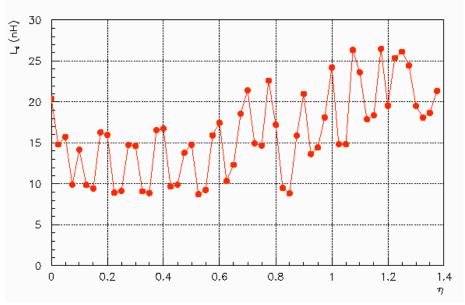

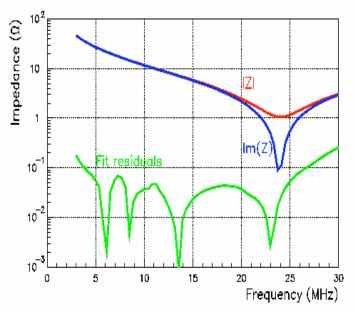

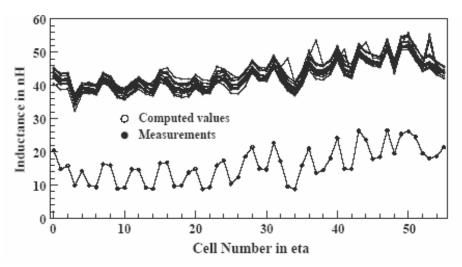

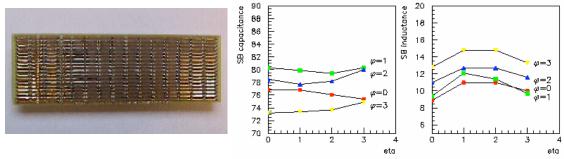

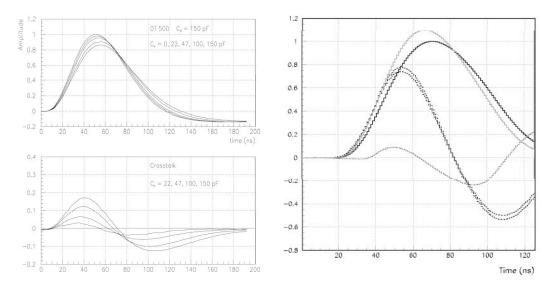

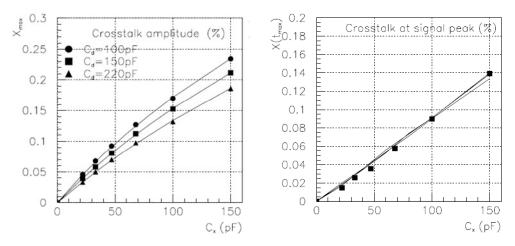

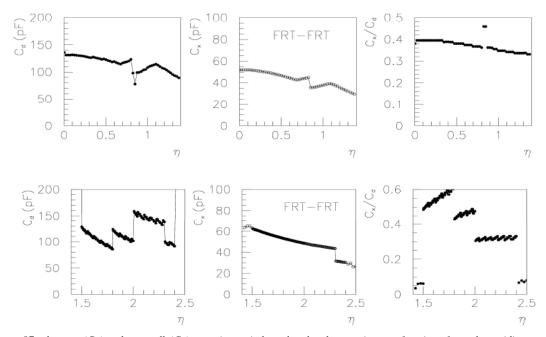

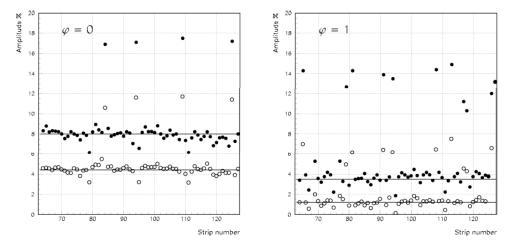

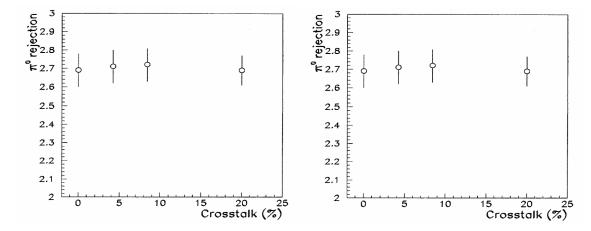

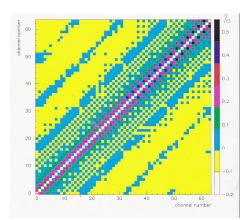

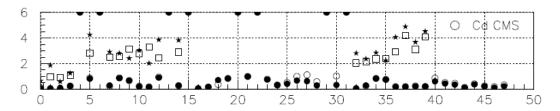

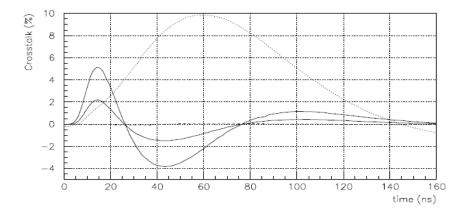

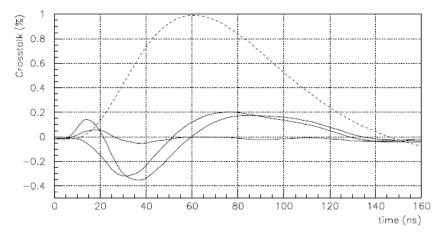

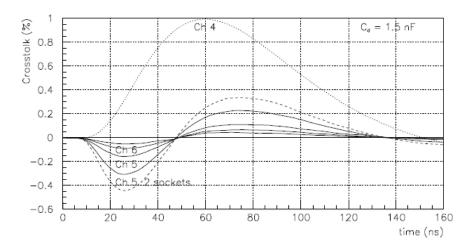

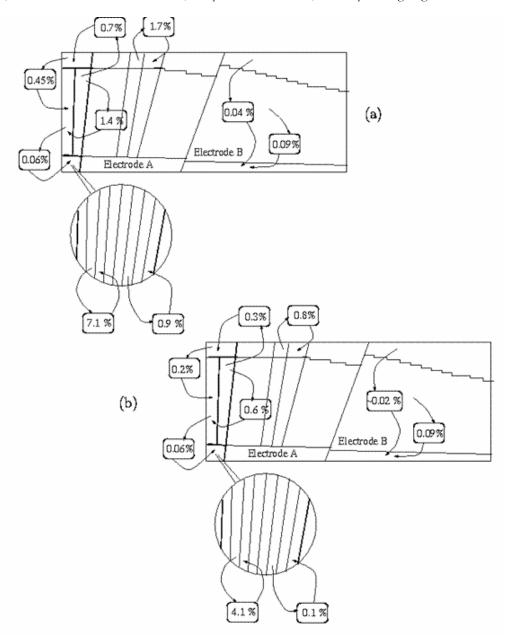

In the end, an excellent electronics calibration was not enough to bring the uniformity on large modules at the 0.5% targeted level. Testbeam data showed that many effects in the signal path created non uniformities at high speed readout. It was then necessary to refine the detector modelization and simulate and then measure all the parameters coming in the model. This is the content of Chapter 3. The first section studies the complete (multi-coupled) transmission line modelization and extracts a simpler RLC lumped model. It also shows how these parameters have been measured on all the 100 000 channels of the calorimeter The second section introduces the calculations of physics and calibration signals in order to correct for the bias introduced in the calibration signal (0.2%/nH) by this parasitic inductance of a few tens of nH. The third section deals entirely with crosstalk issues. In the front sampling of the calorimeter, the fine strips exhibit a capacitance to the neighbors that is of the same order than the capacitance to ground. With the fast shaping used, it gave rise to 5-10% crosstalk, which had to be modelized and corrected for. It also leads to noise correlation between channels, that could have jeopardized the fine algorithm of  $\gamma/\pi^0$  rejection that is essential for the Higgs identification in the 2 photons mode. Finally, one part retraces the steps taken by the "crosstalk task force" of which I was in charge to bring the crosstalk everywhere in the middle and back samplings, down to below 1%, starting from sometimes much higher values. There, many unusual sources were giving crosstalk, mostly from inductive effects that showed up due to the fast shaping.

# 2. ILC and CALICE

The LHC had not yet started that physicists were already thinking at the next generation of experiment. In order to study in detail the Higgs boson that is to be discovered at LHC, a lepton collider has been proposed at the end of the 90's to provide clean data with an accelerator of electrons tuned on the mass to be studied. In order to avoid the prohibitive losses by synchrotron radiation, a linear accelerator is necessary and the progress of accelerating cavities, reaching 40-50 MV/m made possible an affordable machine. In 2003, the TESLA proposal described in its technical design report (TDR) how

<sup>&</sup>lt;sup>6</sup> The electronic calibration is also used to correct non linearity (at the 0.1% level) in the readout chain.

such machine could be built with existing technology which is also now used for free electron laser light sources.

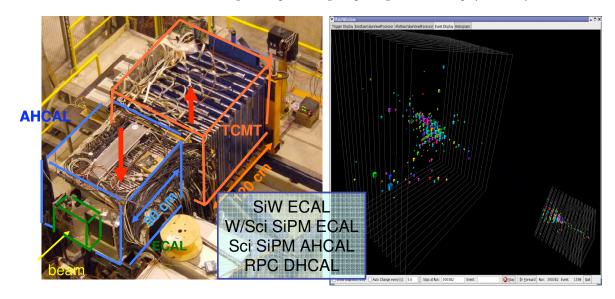

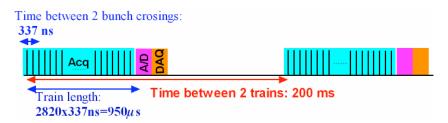

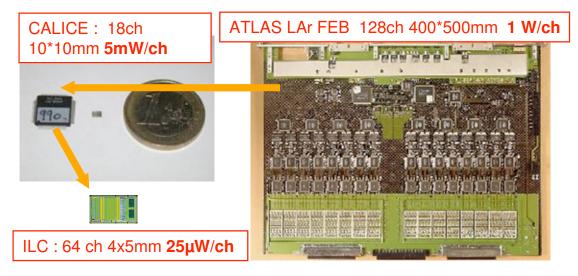

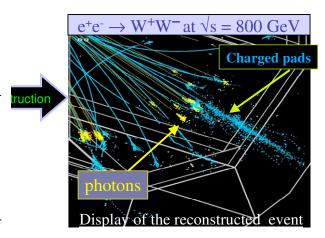

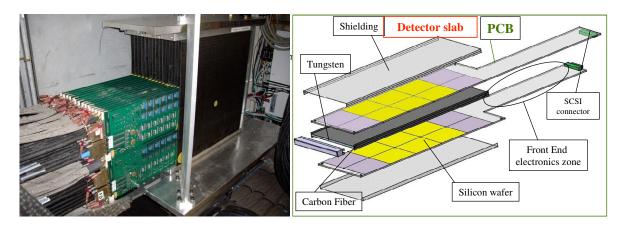

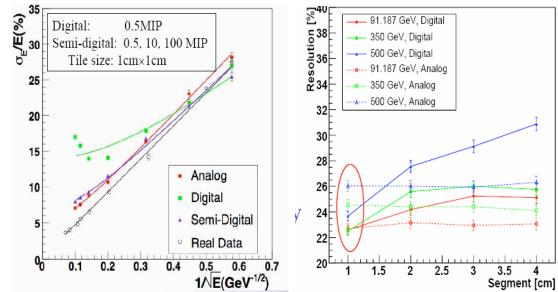

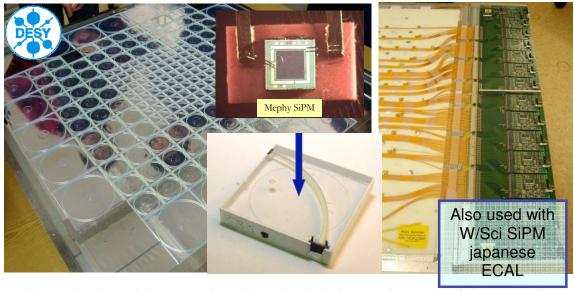

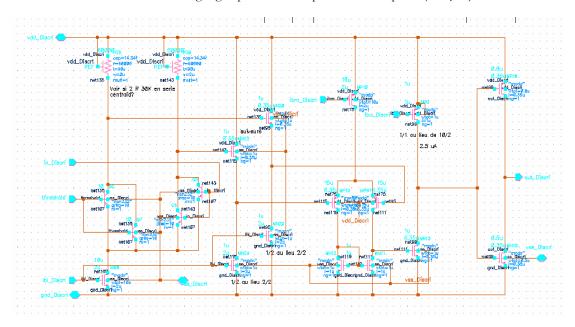

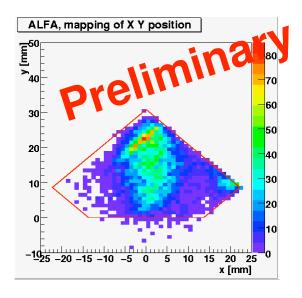

The detectors are also very different from the LHC as the emphasis comes to measuring precisely jets in the final state. In order to improve the energy resolution on jets and also avoid mixing them, an algorithm of particle flow has been proposed around *H. Videau* and *JC Brient*, in which the various components of hadronic showers (charged and neutral) are identified and measured individually. The algorithm requires an excellent granularity in order to achieve good particle identification and separation, hence the term of "imaging calorimetry". The huge number of channels (typically 100 millions) that stems from this requirement together with the need of very compact detectors necessitate a strong and interesting R&D effort that was started in 2001 in the framework of the CALICE collaboration.

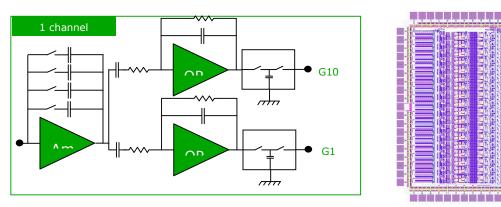

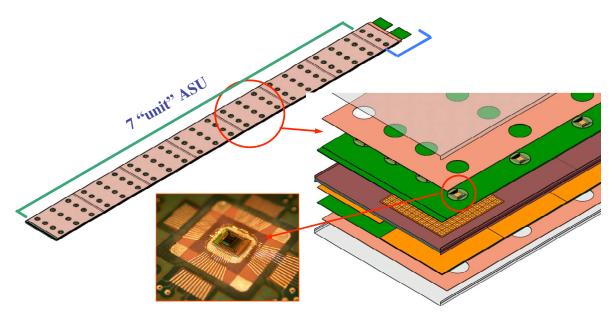

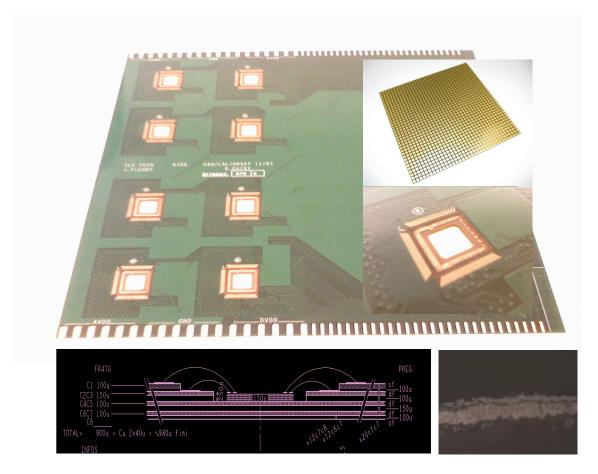

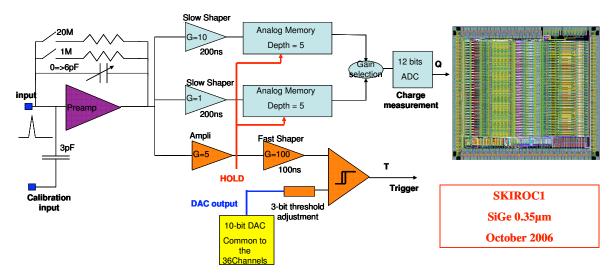

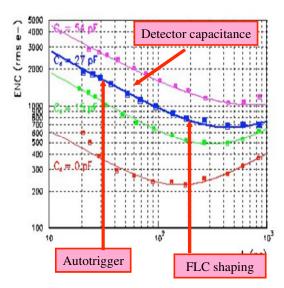

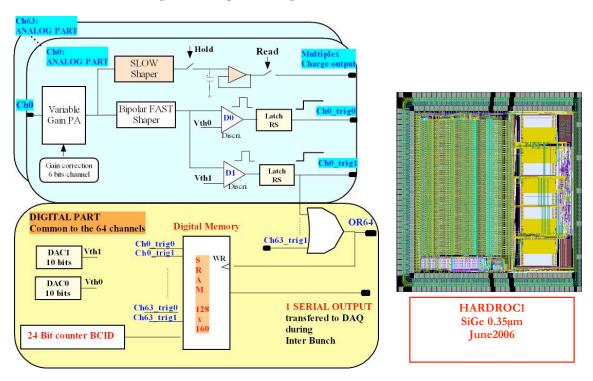

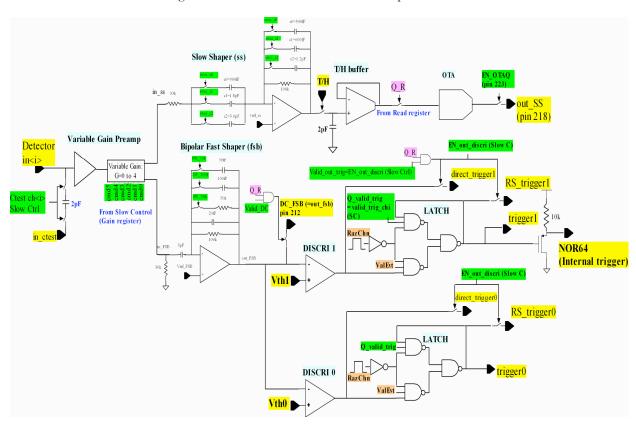

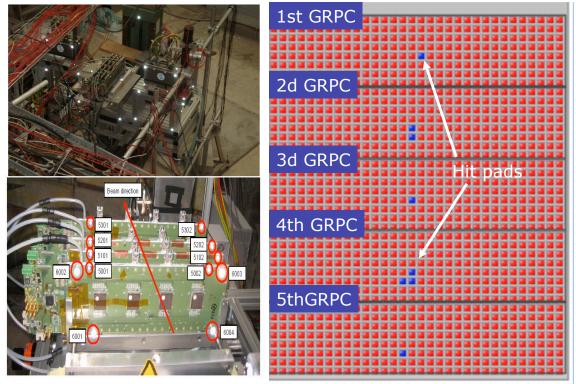

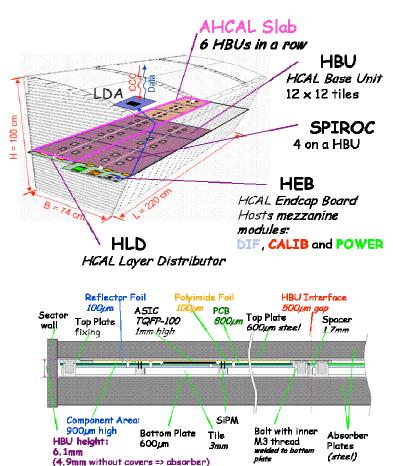

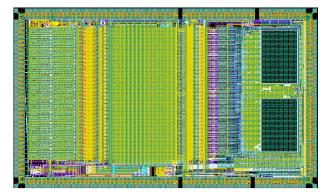

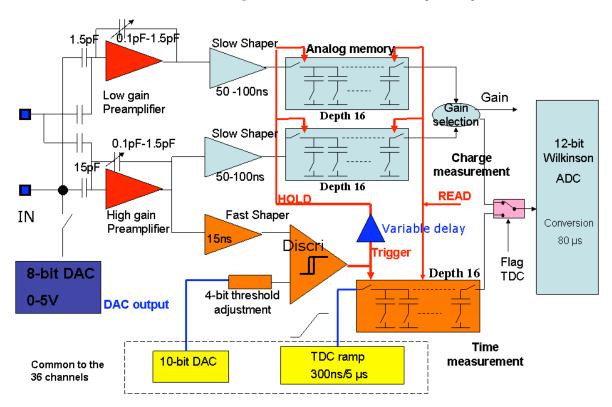

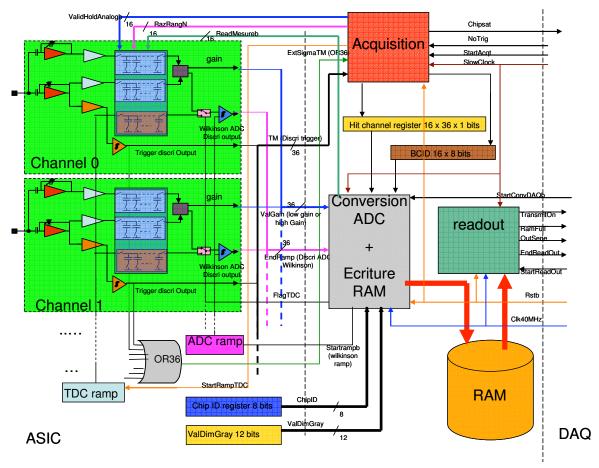

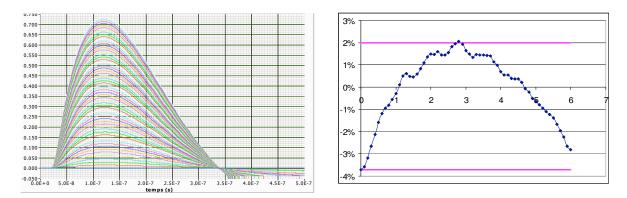

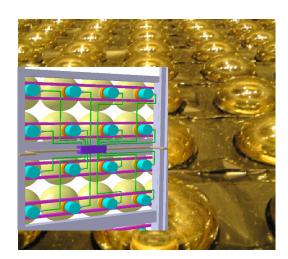

In Chapter 4, we describe the development of the readout ASICs for the three calorimeter proposals. The first section is devoted to the ECAL, with the physics prototype readout by ILCPHY3 whereas the technological prototype will be readout by SKIROC (Silicon Kalorimeter Read-Out Chip). The second section describes the development of HARDROC for the DHCAL technological prototype that is the first prototype to operate a 1m² detector with 10 000 channels of embedded electronics. The third section describes the Analog HCAL composed of scintillating tiles and silicon photomultipliers. The physics prototype has been realized in 2003 and equipped with an ASIC FLCSiPM that we have developed. Work is now moving to the technological prototype readout by a chip named SPIROC (Silicon Photomultiplier Integrated Read-Out Chip)

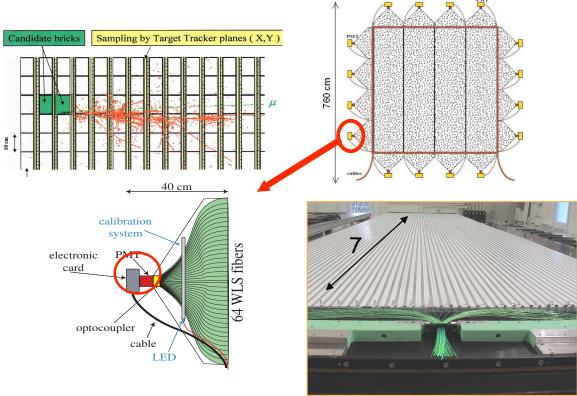

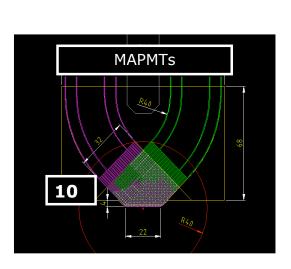

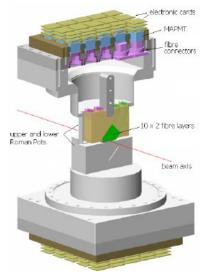

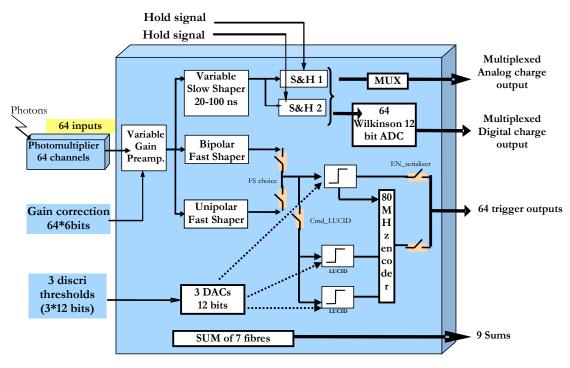

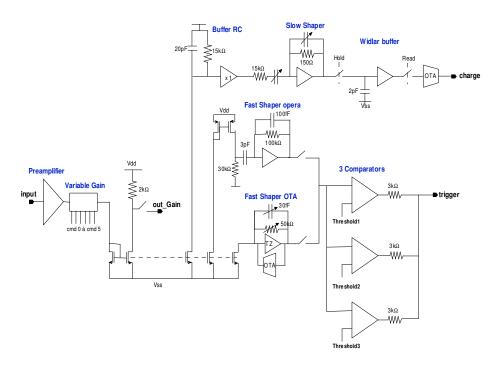

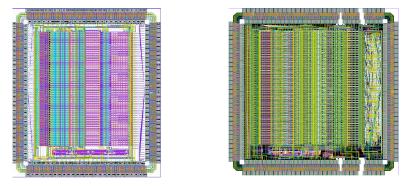

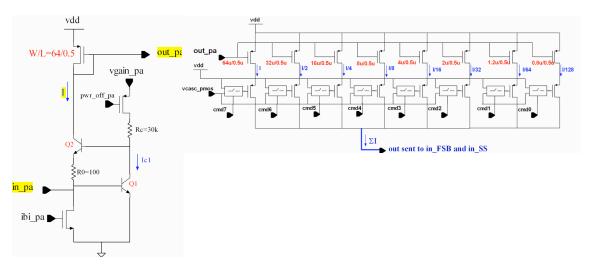

# 3. Multi-anode Photomultiplier readout

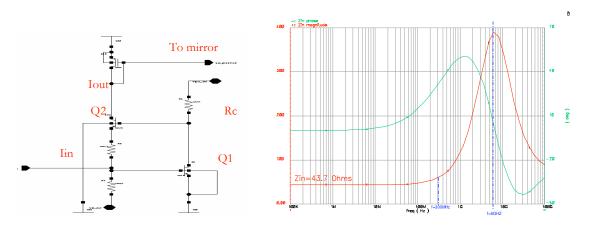

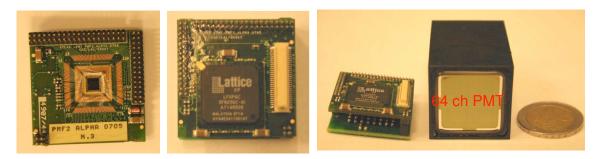

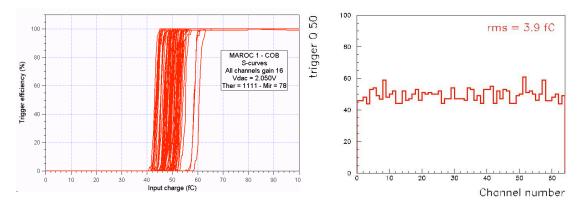

The appearance at the end of the 90's of photomultipliers with segmented anode (multi-anode PMTs) of 16 to 64 pixels of a few square millimeters allowed a cheaper readout of large number of optical fibers inserted in large scintillator planes. With the large number of channels, it was also natural to try to integrate the readout electronics inside an ASIC in order to keep the cost reasonable. This was quickly adopted by the OPERA experiment for reading out its scintillating planes of the Target Tracker detector. We entered the experiment in 1998, under the leadership of *JP Repellin* to provide the readout ASIC called OPERA\_ROC, that was the first ASIC developed to readout such new detectors. We chose to use a variable gain current conveyor in order to correct for the large gain dispersion in the different channels of the photomultiplier. The corrected signal would then feed discriminators to generate a trigger signal as well as a charge integrator to provide a multiplexed charge measurement. This chip is described in the first section of Chapter 5.

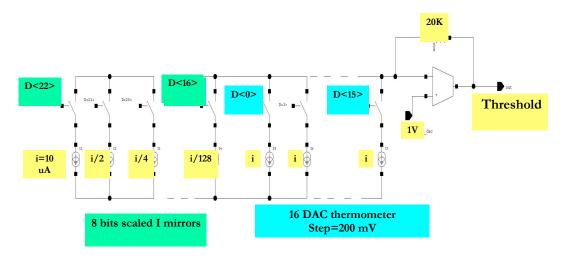

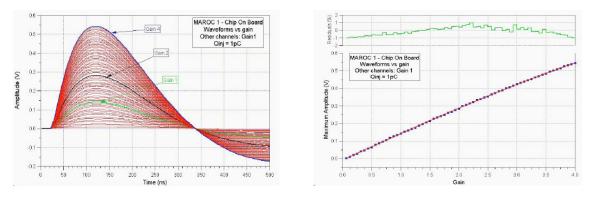

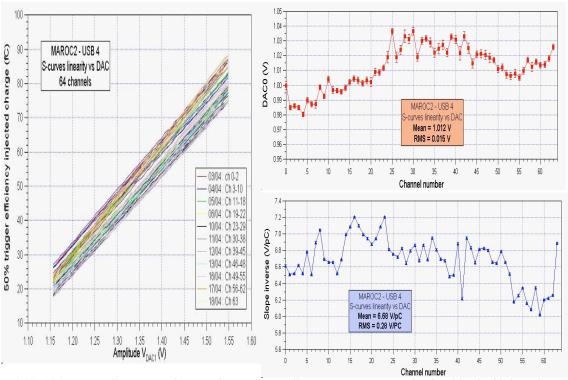

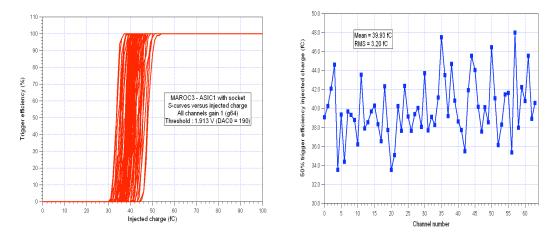

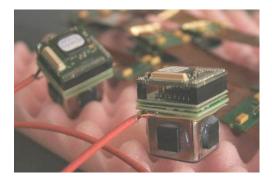

After the large volume production and successful operation in the Gran Sasso tunnel, the chip was interesting the ATLAS collaboration for its absolute luminosity measurements, realized with scintillating fibres at very small angle read out by the same Hamamatsu 64 channels PMT. The BiCMOS 0.8  $\mu$ m technology used for OPERA\_ROC was getting obsolete and the chip was moved and upgraded in the more recent 0.35  $\mu$ m SiGe BiCMOS, with excellent performance. This chip called MAROC and its implementation are described in the second section.

This sophisticated and highly ibntegrated chip pushed for a further step in integrating more and more functions in a chip and on detector, leading to "smart photodetectors" with integrated electronics and digital outputs. This turned out to potentially interest the next generations of neutrino experiments, to equip huge areas of photodetection at reasonable cost and a demonstrator was funded in an ANR<sup>7</sup> project led by *JE Campagne* named PMm². A chip named PARISROC was developed and successfully tested by our PhD student *S. Conforti* and is described in the last section.

$<sup>^{7}</sup>$  « Agence Nationale pour la Recherche », distributing funding on selected projects

# **CHAPTER 1**

# ATLAS FRONT-END ELECTRONICS

#### 1. Introduction

Calorimetry at LHC required a strong R&D effort in order to handle the huge collision rate of 40 MHz and the high beam energy of 14 TeV which on top generated a high radiation environment. Moreover, the small branching ratios for the Higgs boson detection in two photons or four leptons requires a high measurement accuracy, better than 1% on the calorimetric energy [1].

For the electromagnetic calorimeter, the liquid argon technology had rapidly been chosen by the ATLAS proto-collaboration for it excellent stability, precision and uniformity. This technology had notwithstanding the reputation of being slow because of a confusion between risetime and signal duration and also because of the large parasitic inductance necessary to gang together the different layers necessary to form a tower as pointed out by a paper by V. Radeka in 1990 [4].

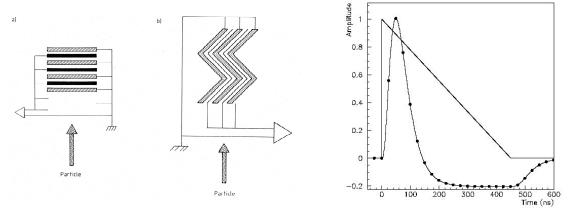

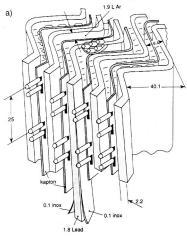

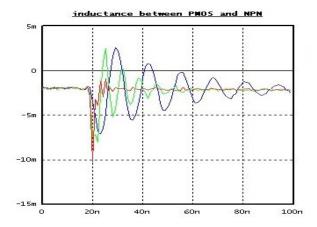

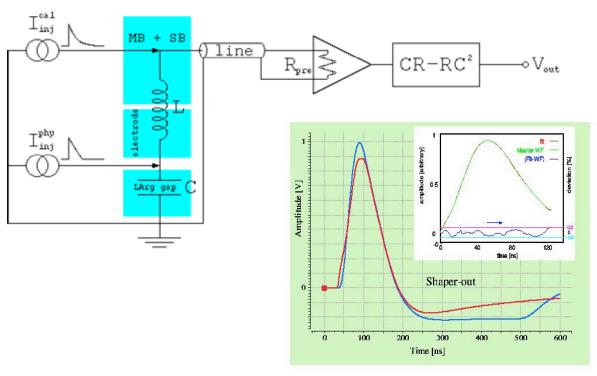

The first point has been addressed by electronics shaping and will be developed in § 3. The second was solved by the accordion geometry proposed by *D. Fournier* which shaped the absorbers in zigzag in order to form a projective tower while getting the signals on the front and rear face with minimal inductance (cf Figure 3) [2].

Figure 3: traditional and "accordion" absorber geometry and liquid argon pulse before and after electronics shaping

For the readout electronics, the preamplifiers received (as usual) a high attention as their noise performance determines the energy resolution at low energy. Several groups proposed competing

technologies and architectures, in particular charge or current sensitive, which will be summarized in section 2, with a particular emphasis on the ØT preamp which we proposed in Orsay and that is described in more details in § 2.3. and [5].

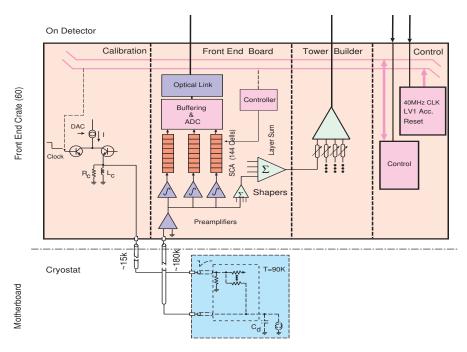

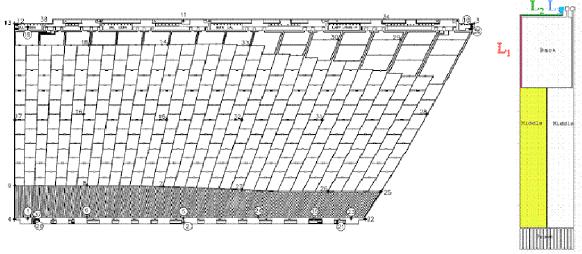

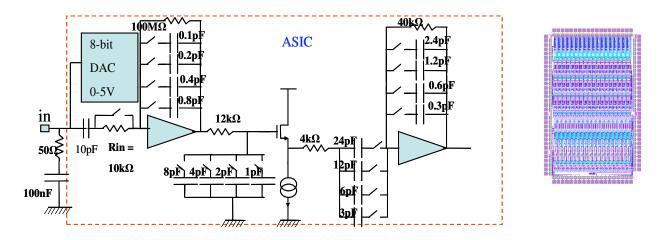

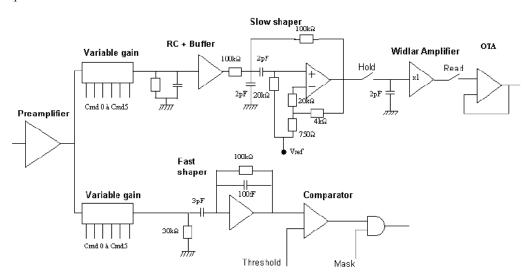

After the preamplifier, the signal is shaped in order to optimize the signal to noise ratio. Here, one unusual source of noise is the pileup of minimum bias events, due to the high luminosity operation which requires clipping the long decay of the liquid argon pulse (cf § 3). Conversely, reducing the electronics noise requires to cut down the bandwidth. Minimizing both noise contributions leads to an optimum shaping time which varies with the luminosity. Fortunately the introduction of multiple sampling (or digital filtering) by *B. Cleland* in 93 [6] has allowed to operate at the minimum noise in (almost) all conditions. The shaper is also used as a multi-gain amplifier in order to split the large 16 bits (10<sup>5</sup>) dynamic range into 3 linear ranges of 12 bits. We have been in charge in Orsay to develop and produce the shaper, which was my first experience in microelectronics and is described in § 3 and [8]. The signal is then stored in an analog memory, digitized after LVL1 trigger and sent out on optical fibres to the Read Out Drivers (RODs) that process the data. The overview is shown in Figure 4.

Figure 4: synoptic diagram of ATLAS LAr readout. In blue, the on-detector electronics which consists only of calibration resistors and connectors. 180 000 cables bring calorimeter signals outside of the cryostat, while ~20 000 bring the calibration signals in. On the cryostat itself, specially designed crates house front-end boards that readout the signals, calibration boards that generate the calibration pulses, tower-builder boards that perform analog sums for the LVL1 trigger and controller boards

Several prototypes were realized to progress on the comparison of different options and validation of choices.

In 1990 a small prototype was built (Figure 5) to validate the accordion concept on test beam as well as the behaviour at fast shaping. It was readout by charge preamps designed by BNL and fast shapers (30 ns) we designed at Orsay. The goal was to check that a good resolution could be obtained  $(10\%/\sqrt{E})$  and in particular a local constant term of 0.3% that would prove that the corrections necessitated by the accordion geometry were accurate. The fast readout of 30 ns was essential also to prove that LAR could be *fast* and the accordion geometry was really reducing the parasitic inductance that slowed the signal. By the end of 1990, the test was a success[3] and a larger prototype could be built.

Figure 5: Principle of accordion readout and picture of the first cubic prototype in 1990

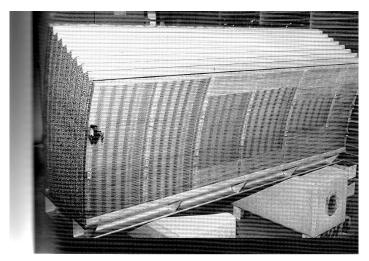

metric in large dimensions (Figure 6). The main issues concerned of course the mechanics and the electrodes that collected the signal, but there were also many issues on electronics. As will be detailed in §2, several preamplifiers were proposed by different groups, including one by us and the tests would help for the choice. We were again in charge of developing the fast shapers, now for 3000 channels, still in the form of small hybrids, which in the end occupied a cubic meter! The theoretical calculations on the shaping and optimum shaping time occupied us for some time as it strongly affects the noise and will be recalled in §3. After the shaper, the signal was in a first period sampled at the peak and digitized by Lecroy CAMAC ADCs and later on stored in the first prototypes of analog memories. This allowed to get several samples on the waveform and to combine them to do some digital filtering (cf § 3.3. ) to approach very closely the theoretical optimal filter and improve significantly the signal to noise ratio. This approach was very new in the domain and we made several studies to convince ourselves of the strengths and weaknesses of the method which is also detailed in §3. The detector also needed an electronics calibration system to correct for non uniformities and non linearity in the readout, which will be described in Chapter 2.

Figure 6: View of the 2 m barrel prototype

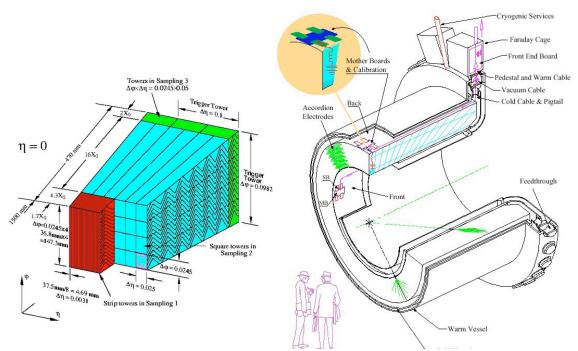

∞ From 1994 to 1996, two years were necessary to optimize by simulation and with the 2 m results the geometry and granularity. Many factors were coming in, such as physics performance, interaction with other sub-detectors, cost... The result is summarized in Figure 7 below which shows the granularity, segmentation in depth and arrangement of the electronics on the cryostat.

Figure 7. <u>Left</u>: final geometry of the ATLAS LAr barrel calorimeter after optimization of cell size, segmentation in depth and in eta-phi. The red part corresponds to the front finely segmented strips, the blue to the middle cells where most of the electromagnetic shower is contained and the green to the back compartment used at high energy. <u>Right</u>: overall view of half-barrel calorimeter with the feedthroughs at the end to bring-out the signals.

\* In 1997 it was now time to build a real module 0, as shown in Figure 8. It did not look very different from the 2 m prototype (3 m instead of 2), but bore in fact several key differences in the signal path that would necessitate long efforts in analysis, as will be detailed in chapter 3. In particular, the crosstalk was severely deteriorated. By that time, the final electronic architecture could be tested with radiation soft components. In 1999 the first module 0 was ready with its electronics to go into test beam.

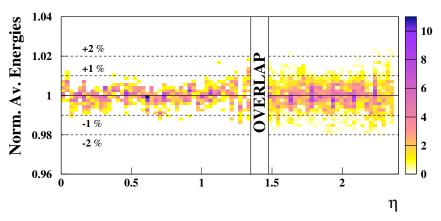

The module 0 was used to take testbeam data during several years and many important analysis results were obtained, not always without effort! As an example, the calorimeter uniformity is shown in Figure 9.

Figure 8: module 0 in testbeam at CERN in 1999 in its dedicated cryostat.

Figure 9: normalized energy response over the full calorimeter. The rms is 0.6% over morea than 2 000 channels.

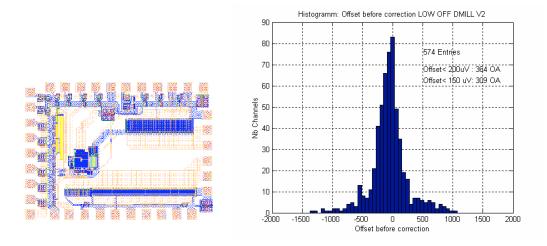

From 1998 to 2001 radiation hard components were developed and qualified in DMILL BiCMOS 0.8 µm, a military process developed by CEA. My group in Orsay had the responsibility of the shaper chips (80 000), three calibration ASICs and the calibration boards. We also had to organize the multi-chip production runs in DMILL and the test of all these chips.

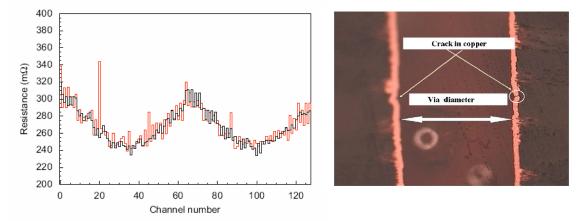

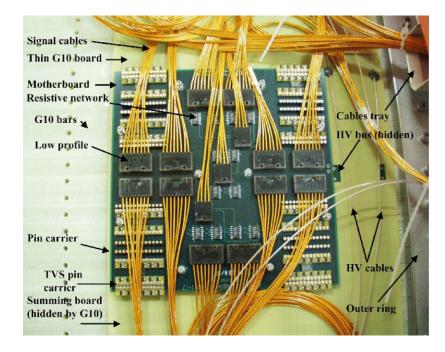

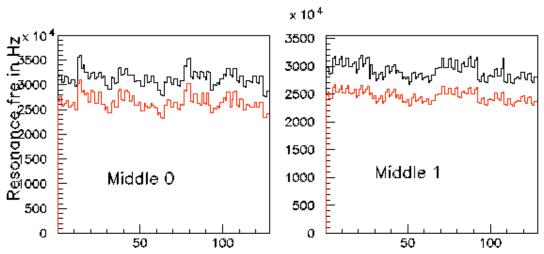

From 2002 to 2004 the calorimeter was assembled and tested. The assembly and individual test of the 32 barrel modules and as many endcaps was surprisingly fast in view of the time it took to build the module 0 and the whole detector could be closed in 2003. Once the calorimeter was complete we had to intervene once more to measure on the 200 000 channels the calibration resistors, the detector resonant frequency and feedthrough grounding quality, both in the warm and then in the cold. These measurements, essential to reach the 0.7% calorimeter accuracy are detailed in chapter 3.

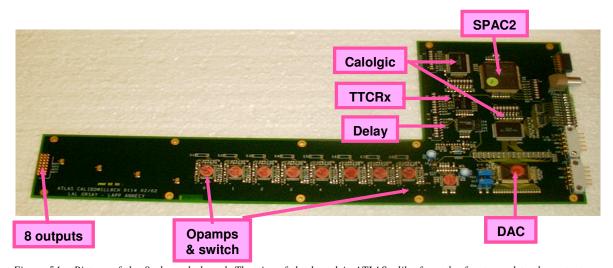

Final production of all the electronics was done and the boards progressively installed. For us, this concerned mostly the 130 calibration boards which were completed and tested in 2005, with a few surprises in the production phase that are described in chapter 2.

Figure 10: barrel calorimeter assembly

# 2. Preamplifiers

The three main issues for the preamplifiers were the following:

- $\infty$  Low noise: due to the large detector capacitance (400-1200 pF) the series noise is totally dominant and the series noise spectral density was targeted lower than  $e_n < 0.3 \text{ nV/VHz}$

- ∞ Large dynamic range : the maximum signal is 1 nC and the noise corresponds to 20 fC. This constraint turned out to be very difficult for charge preamplifiers.

- $\infty$  High speed: the optimum shaping time is around 25-50 ns, as will be shown in § 3

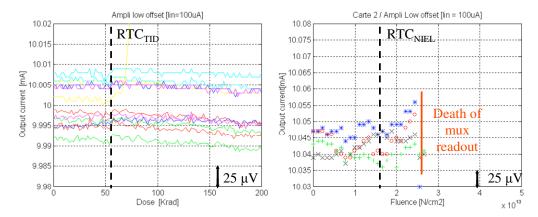

- ∞ Good radiation hardness: doses up to 1 kGy<sup>8</sup> and fluences of 10<sup>13</sup> N/cm<sup>2</sup> (1 MeV/eq.)

#### 2.1. Charge sensitive preamplifiers

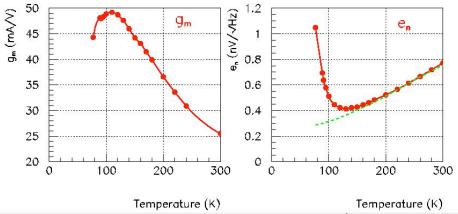

The charge preamps had the difficulty of accepting the maximum signal of 1 nC. With a feedback capacitance of C<sub>F</sub>=33 pF, the preamplifier saturated at 100 pC corresponding to 10% of the total charge. This saturation was acceptable as these events are very rare provided the preamp would not stay "dead" for a long time. The charge preamps proposed by BNL were following the classical "Radeka topology" of folded cascade entirely built with Si NJFETs (cf Figure 11) specially developed for this purpose by Interfet. The model NJ450 exhibits a large transconductance g<sub>m</sub>=20 mA/V at 5 mA drain current with a relatively high capacitance of 60 pF. It operated at liquid argon temperature (89 K) although the optimum temperature for the noise was 120 K. We measured (Figure 12) these preamplifiers during a stay at BNL and found interesting behavior of transconductance and series noise versus temperature. In the end, these preamplifiers were not used for ATLAS but equipped the NA48 liquid krypton calorimeter.

Figure 11: Schematic of JFET Charge preamp used in NA48 and ATLAS prototype as proposed and designed by BNL.

$\infty$

$<sup>^{8}</sup>$  1 kGy = 100 krad

<sup>&</sup>lt;sup>9</sup> The noise density follows nicely the theoretical value of  $4kT\gamma/g_m$  until 120 K. Below, it rises again to reach higher values at liquid nitrogen temperature than at room temperature, presumably due to non thermal equilibrium of the carriers with the lattice.

Figure 12. <u>Left</u>: transconductance  $g_m$  (at  $I_D$ =5 mA) of NJFET InterfetNJ450 as a function of temperature. <u>Right</u>: measured series noise  $e_n$ . It can be seen that the series noise departs from the theoretical thermal noise (green curve) below 120 K

#### 2.2. GaAs current sensitive preamplifiers

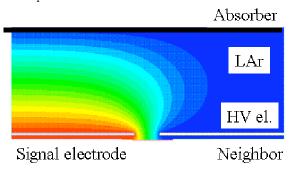

To overcome the limitation of charge preamps with the huge maximum incoming charge, a non-integrating configuration was proposed, referred to as current sensitive preamplifier, replacing the feedback capacitor  $C_F$  by a resistor  $R_F$ . In this configuration the preamp input impedance can be modelized as an inductor<sup>10</sup>: Leq= $R_F/\omega_c$  where  $R_F$  is the feedback resistance and  $\omega_c$  is the preamplifier bandwidth. This configuration is of course easily oscillatory with a capacitive detector and the faster the amplifier, the more stable it is<sup>11</sup>, which has pushed in favor of GaAs technology. Besides, the superior mobility in GaAs has a beneficial impact on transistor channel white noise. The traditionally poor 1/f performance of these transistors was alleviated by the operation at high frequency (~10 MHz) and lower temperature. These preamplifiers were developed by the Milano group led by *D. Camin* and showed series noise as low as  $e_n$ <0.2 nV/ $\sqrt{H}z$ . The schematic was similar as the JFET one shown in Figure 12, except for the feedback element now a resistor  $R_F$  = 1.5 k $\Omega$  and a compensation feedback capacitor  $C_F$ ~10 pF to ensure stability. They were also proposed and finally chosen (Figure 13) for the Hadronic End Cap.

One additional advantage of current sensitive preamplifiers in this case was the smaller sensitivity to second stage noise as shown in, which is due to the larger amplification at high frequencies (cf  $\S 3$ )

Figure 13: GaAs current sensitive preamplifier used in the Hadronic End Cap, developed by Munich MPI group

$<sup>^{10}</sup>$  The input impedance of the shunt-shunt configuration is  $Z_F/G.$  With the usual gain roll-off with frequency as  $G(\omega) = G_0 / (1 + j\omega/\omega_c)$  the input impedance becomes  $R_F/G_0 + j\omega R_F/\omega_c$  which is the series combination of a small resistance  $R_F/G_0$  (usually negligible) with and inductor  $R_F/\omega_c$

The smaller equivalent inductance  $(R_F/\omega_c)$  allows a smaller damping resistor  $\sqrt{Leq/C_D}$ , usually realized with a small  $C_F$

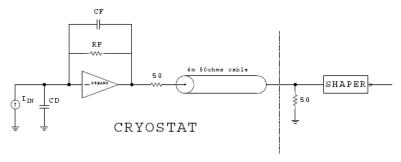

#### 2.3. Remote current-sensitive line-terminating preamplifiers (ØT) (PhD Y. Jacquier)

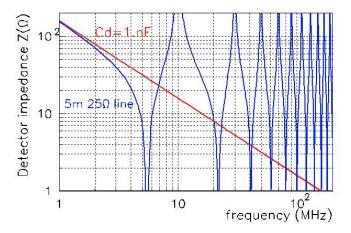

An unexpected consequence of operating at high speed with large detector capacitance was that a transmission line between detector and preamp did not degrade the noise with the usual penalty of  $\sim 100$  pF/m. Putting away the preamplifier largely alleviates constraints of radiation hardness, power dissipation inside the liquid argon with the risk of bubbles and allows maintenance operation in case of dead channels. The reason is explained on the plot in Figure 14 that shows the impedance Z of a line of characteristic impedance  $R_c$  and length  $t_d$ , terminated by the detector capacitance  $C_D$ :

$$Z = \frac{1 - \omega R_C C_d \tan \omega t_d}{j \omega C_d + j \tan \omega t_d / R_C}$$

(1)

As the series noise scales as  $e_n$  / Z, it can be noted that at the central frequency of the filter (~10 MHz) the impedance of a detector capacitance of  $C_D$ =1 nF is smaller than the cable impedance, thus the noise can be lower with a cable than with the detector capacitance alone.

Figure 14: detector impedance as a function of frequency at the input and output of a 5 m cable.

This new approach led to two publications in NIM [5][6] and was proposed to the collaboration as the "ØT option" meaning "Zero Transistor in the cold". The salient points in the two publications concerned

- Calculation of the noise with an ideal transmission line between detector and a line terminating preamp. The conditions under which the line does not degrade the noise performance is to have a long line with an impedance higher than the detector at the central frequency of the filter. In other terms, if  $t_p$  is the shaper peaking time :  $t_d > t_p$  and  $R_C$   $C_D > t_p$ , which applied to the ATLAS case ( $R_C$ =25  $\Omega$ ,  $C_D$ =1 nF, td=25 ns, tp=25 ns)

- ∞ Calculation with a real line, including signal attenuation due to skin effect in the line and the thermal noise generated by the skin effect resistance. This introduced a noise dependence with the line length, in good agreement with the experimental measurements, especially with the use of miniature coaxial cables in which the skin effect is non negligible.

- Design of the line terminating current sensitive preamplifier. In the first paper, a charge preamplifier was used to terminate the line as its input impedance  $Rin=C_P/g_mC_F$  is resistive  $^{12}$  and can be adjusted to 50  $\Omega$ . However, the difficulty of handling the full dynamic range and the poor linearity due to the change of input impedance with signal amplitude led to the development of a current-sensitive line terminating preamplifier. This preamplifier was also taking advantage of the excellent series noise of the bipolar technology as the ATLAS parameters (speed and large detector capacitance) were rendering the parallel noise of the base current completely negligible.

<sup>&</sup>lt;sup>12</sup> The input impedance of an amplifier of gain  $G(\omega)$  with  $Z_F$  feedback is  $Z_F/G+1$ . With  $Z_F=1/j$   $\omega C_F$  and  $G(\omega)=G_0/1+j$   $\omega/\omega_0$ , the input impedance becomes ZIN=1/j  $G_0$   $\omega C_F+G_0\omega_0 C_F$  where the second term dominates at the usual operating frequencies and is purely resistive.

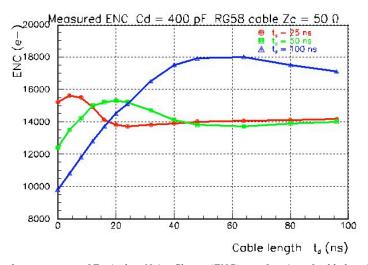

The experimental measurements validating the calculations are recalled in Figure 15

Figure 15: experimental measurement of Equivalent Noise Charge (ENC) as a function of cable length. The three curves are for three different shaping times: 25, 50 and 100 ns. ATLAS corresponds to the red curve (25 ns) which shows no noise penalty with a long line compared to without line. The classical case corresponds to the blue curve (100ns) which shows a linear increase of the noise with the cable length corresponding to an additional capacitance of 100 pF/m.

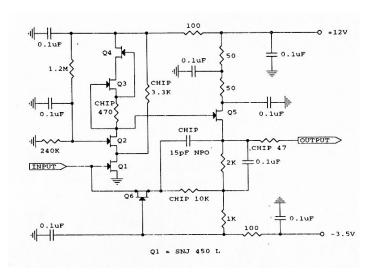

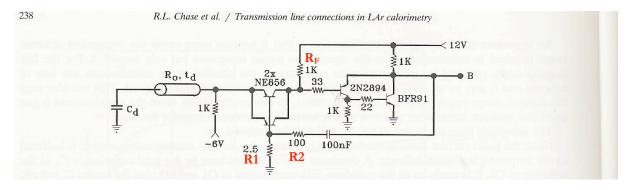

The preamplifier design started from a common base configuration which is very classical for current conveyor and line termination. The input impedance being  $1/g_m$ =26mV/I<sub>C</sub> can be tuned to the cable impedance by playing on the collector bias current I<sub>C</sub> while the series noise is only  $e_n^2$  = 4kT(1/2g<sub>m</sub>+R<sub>BB</sub>). The latter term is known to dominate at large current and several low noise high frequency transistors were tested to select the NE856 by NEC which exhibited the lowest R<sub>BB</sub> = 4  $\Omega$ . In order to reach the target noise of 0.4 nV/ $\sqrt{\text{Hz}}$ , corresponding to 10  $\Omega$  noise resistance, it is necessary to aim for a transconductance of  $g_m$ ~200 mA/V (!) and thus operate at Ic~5 mA. However, in that case the input impedance  $1/g_m$  = 5  $\Omega$  becomes too low to terminate the line and needs to be increased by applying series/parallel feedback with the divider R2/R1. The input impedance can be calculated as Rin=R<sub>F</sub>\*R1/R2. R1 needs to be order of a few ohms to limit its noise contribution making R2 a heavy load on the output. This in turn needs an ultra low output impedance buffer built with the closed loop configuration of "White follower". This resulted in the schematic below (Figure 16) extracted from [5]. It was subsequently upgraded by BNL to reduce the power dissipation and produced by BNL and Milano in the form of 4-channel hybrids.

Figure 16: schematic diagram of the first ØT preamplifier

#### 2.4. Preamplifier choice (LArG note 35)

The three types of preamps have been validated in test beam runs and the results were consistent with the electronics measurements performed on test bench. Rapidly, the preamp based on JFETs was dropped as it was more noisy than GaAs technology and did not cope well with the full dynamic range in charge sensitive configuration<sup>13</sup>. The choice remained between ØT and GaAs throughout numerous measurements in 1994-1996.

Very quickly ØT preamps were chosen in the front section as the granularity was much finer<sup>14</sup> to accommodate the space for preamps. Besides it was important in front of the calorimeter to minimize all the dead material and in particular liquid argon which was obtained by removing all the electronics. The impact on the noise was not large as only 10-20% of the energy is deposited in the front section.

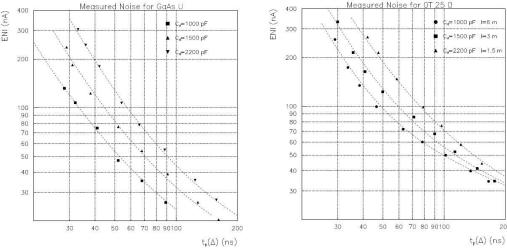

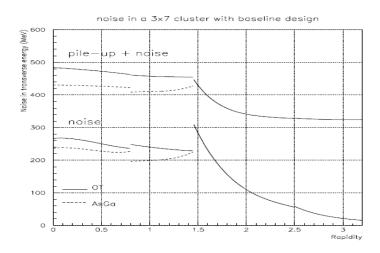

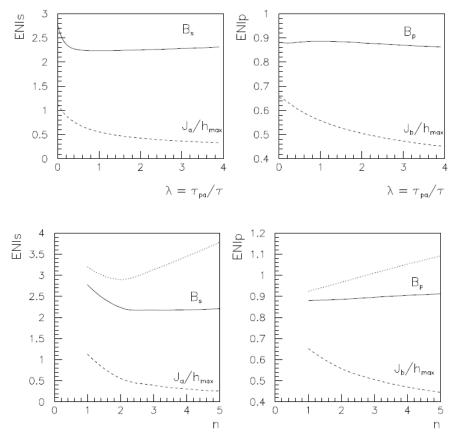

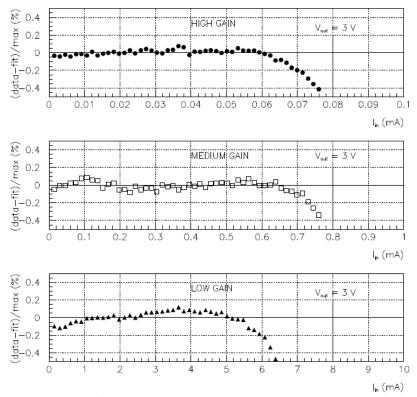

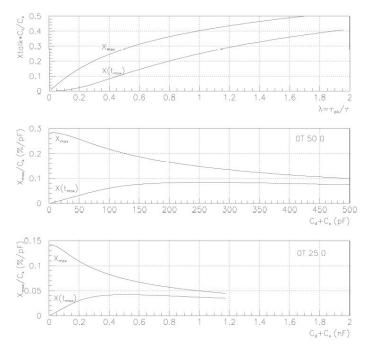

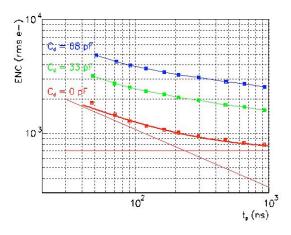

The results were summarized in a LAr note #35. As will be shown in the section describing the shaper, the noise in MeV was extremely sensitive to the actual shaping time and several effects needed to be taken into account to make a fair comparison. As explained in § 3.1. the noise is expressed as Equivalent Noise Current (ENI) and fitted on experimental measurements as a function of shaping time<sup>15</sup> for various detector capacitances as  $ENI^2 = A/tp^5 + B/tp^3 + C/tp$  (cf. Figure 17).

Figure 17: Equivalent noise current ENI as a function of shaping time as measured on GaAs preamplifiers and ØT preamplifiers for various detector capacitances (1, 1.5 and 2.2 nF). The experimental measurements are fitted in order to extrapolate the noise to all the various cells in the calorimeter.

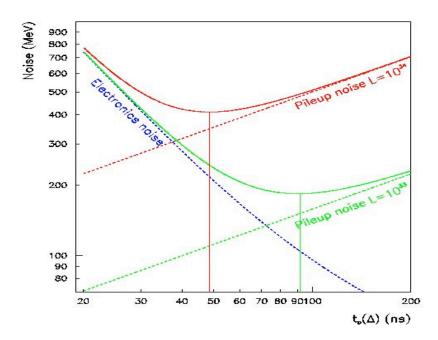

The noise is then calculated in a  $\Delta\eta x \Delta\phi = 3x7$  cluster<sup>16</sup>, summing 48 front cells, 21 middle ones and 12 back ones (see Chapter 3 for detector segmentation). It was then scaled into Equivalent Noise Energy (ENE) with the detailed calculation of the sampling fractions<sup>17</sup>, with typically  $I_0/E \sim 3$  nA/MeV. The pileup noise was then added, giving a noise scaling as  $C^*t_p$  (cf § 3.1. ). The total noise as a function of shaping time is then calculated as shown in Figure 23, exhibiting a minimum for an optimum shaping time at a given luminosity.

<sup>&</sup>lt;sup>13</sup> Si JFET was also not fast enough to be used in current sensitive configuration

$<sup>^{14}</sup>$  To get good position accuracy and  $\pi^0$  rejection (see chapter 3)

<sup>&</sup>lt;sup>15</sup> As shown in §3.1,  $ENI^2 = A e_nCt/tp^3 + B i_n/tp$ . The first term in  $tp^5$  has been added empirically in order to get a better fit at fast shaping.

The larger dimension in  $\Delta\phi$  is due to the shower "opening" in  $\phi$  with the magnetic field.

<sup>&</sup>lt;sup>17</sup> The sampling fraction is typically 0.25 corresponding to 4.2 mm of LAr (0.89 MeV) and 1.5 mm Pb + dead material (2.7 MeV)

This was then calculated over all the calorimeter rapidity, taking into account the variation of detector capacitance as well as the pileup increase with rapidity, as shown in Figure 18, providing an estimation of the electronics noise that is being used in the overall simulation of physics performance.

The small difference of total noise between  $\mathcal{O}T$  and GaAs led to the choice of  $\mathcal{O}T$  everywhere in the calorimeter to minimize the risk of dead channels in the cold where no maintenance is possible. The  $\mathcal{O}T$  preamps have then been taken in charge by BNL and Milano, modified to optimize their power dissipation and fabricated as 4-channel hybrids.

Figure 18: total noise in a 3x7 cluster as a function of rapidity

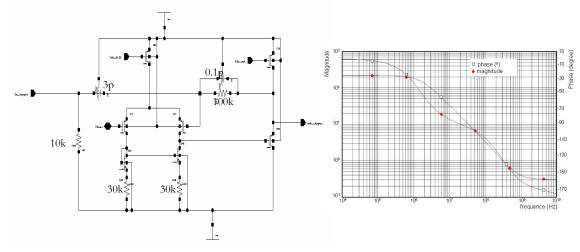

# 3. Shaping (3 LArG notes)

The shaping had been proposed very early in the paper from Radeka/Rescia [4] to make the long signal from liquid argon compatible with the high luminosity operation. The paper was comparing the benefit of bipolar (CR)<sup>2</sup>(RC)<sup>n</sup> and tripolar shaping (CR)<sup>3</sup>(RC)<sup>n</sup> to get rid of the trailing edge of the liquid argon pulse. It was used with a charge preamp in the input and calculated the pileup as a function of speed and urging for bipolar signal shape with zero net area to avoid the baseline shifts in all subsequent AC couplings.

Now, all the usual assumptions of detector signal short compared to the shaping time and preamplifier rise time negligible were not true in the LAr case, on the contrary, the signal was even almost infinitely long (500 ns) compared to the shaping time (20-50 ns). With the move towards current sensitive preamplifiers, it was clear than one less differentiation was needed in the shaper and that Charge Preamp +  $(CR)^2(RC)^n$  was equivalent to Curent Preamp +  $(CR)^2(RC)^{n+1}$ . However, the noise behaviour of current sensitive preamplifiers were not as well established as those of charge preamplifiers. It was then necessary to perform some theoretical calculations and introduce the notions of Equivalent Noise Current (ENI) and the peaking time to the step or the triangle  $(tp(\Delta))$  between 5% and the peak as robust description of the shaping. This replaced conveniently the notions of "effective integration time" necessary to convert ENC into MeV and took well into account all the detector and preamplifier contribution to the shaping time, which is not at all negligible at fast shaping.

19

The transfer function of an ideal charge preamplifier is  $1/sC_F$  where as it is just  $R_F$  for a current preamplifier. The 1/s term simplifies with the second differentiation of the  $CR^2RC^n$  shaper whose transfer function is  $(\tau s)^2/(1+\tau s)^{n+2}$

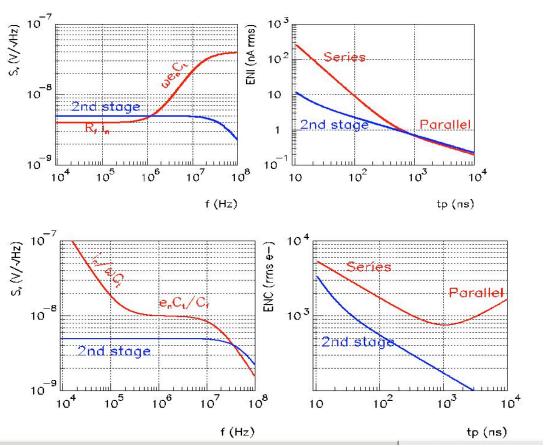

#### 3.1. Theoretical analysis (LArG note 010)

The detailed analysis of shaper architecture and fair way of comparing noise measurements, in particular to take into account the preamplifier rise time were detailed in the LArg010 note [10]. It gave theoretical expressions of signal and noise of current sensitive preamplifiers followed by CR RC<sup>n</sup> shapers.

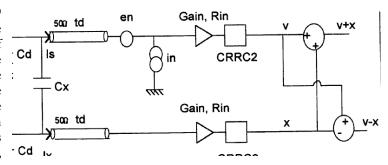

Figure 19: synoptic diagram of current sensitive preamplifier and shaper CRRC<sup>n</sup>. This diagram also applies for ØT preamplifier, for which the cable is located before the preamplifier instead of after.

The transfer function for the GaAs or ØT preamplifiers are very similar and are calculated in the frequency domain with a CRRC<sup>2</sup> shaper:

$$H(s) = \frac{R_F}{1 + s \tau_{PA}} \frac{s \tau_{SH}}{\left(1 + s \tau_{SH}\right)^3}$$

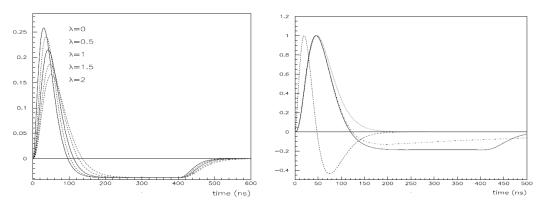

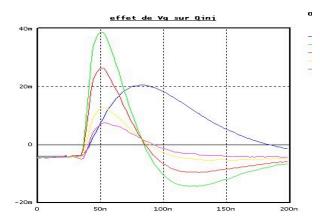

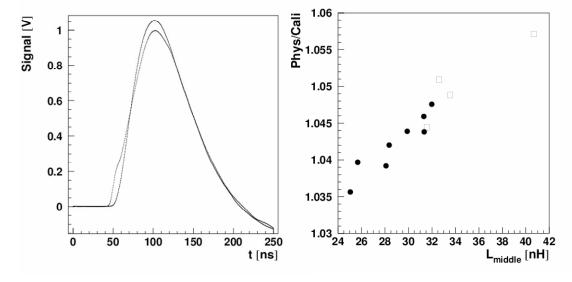

In which  $R_F$  is the preamplifier transimpedance,  $\tau_{PA}$  is the preamplifier pole<sup>19</sup> and  $\tau_{SH}$  the shaper time constant. The triangular signal from the liquid argon detector is also described in the frequency domain as well as the exponential pulse from the calibration system (cf. Chapter 2) or the step used in testbench measurements. The expressions are then calculated in the time domain by taking the inverse *Laplace* transform to provide literal expressions that can be used in the detector simulation. The effect of the preamp risetime on the overall response as well as the difference between step, triangular and exponential response are shown in Figure 20.

Figure 20. <u>Left</u>: shaper response to the triangular ionization current for various preamplifier time constants ( $\lambda = \tau_p / \tau_{sh}$ ). <u>Right</u>: response to the step, ionization current and exponential calibration pulse

20

In a current sensitive preamplifier,  $\tau_{pa} = R_F C_F$ ; in the case of the 0T preamp,  $\tau_{pa} = R^0 C_D$

The **rms noise** at shaper output is also classically calculated in the frequency domain:

$$v_n^2 = \frac{e_n^2 C_d^2 R_f^2}{\tau_{SH}^3} \int_0^\infty \frac{(\omega \tau_{SH})^4}{(1 + \omega^2 \tau_{pa}^2)(1 + \omega^2 \tau_{SH}^2)^3} \frac{d(\omega \tau)}{2\pi} + \frac{i_n^2 R_f^2}{\tau_{SH}} \int_0^\infty \frac{(\omega \tau)^2}{(1 + \omega^2 \tau_{pa}^2)(1 + \omega^2 \tau_{SH}^2)^3} \frac{d(\omega \tau_{SH})}{2\pi}$$

(1)

These two integrals depend only on  $\lambda = \tau_{pa}/\tau_{sh}$  and are noted  $J_a^2(\lambda)$  and  $J_b^2(\lambda)$ . It can be noticed that the rms noise  $v_n$  depends much more strongly on the shaping time (in  $\tau^{-3/2}$  and  $\tau^{-1/2}$ ) as with the usual charge sensitive configuration<sup>20</sup> as recalled in Figure 21. As for the signal response, the response to the triangular ionization current  $I_0$  is very similar to the response to a step of amplitude  $I_0$ , which gives a response independent of the shaping time and noted  $h_{max}(\Delta)$ . Thus the noise can be referred to the input as equivalent Noise Current (ENI) defined as ENI =  $v_n / h_{max}(\Delta)$ . Thus

$$ENI = e_n C_D \frac{Ja(\lambda)}{h_{\text{max}}(\Delta)(\lambda)\tau_{SH}^{3/2}} \oplus i_n \frac{Jb(\lambda)}{h_{\text{max}}(\Delta)(\lambda)\tau_{SH}^{1/2}}$$

(2)

in which  $e_n$  and  $i_n$  are the series and parallel noise spectral densities (nV and pA/ $\sqrt{Hz}$ ),  $C_D$  is the detector capacitance,  $h_{max}(\Delta)$  the shaper amplitude and  $\tau_{SH}$  its RC time constant.

Figure 21: Noise spectral density and Equivalent Noise Current (ENI) of current sensitive (top) and charge sensitive (bottom) configurations. The second stage noise is smaller at short shaping time for current sensitive configurations

The noise can anyhow be referred to the input as ENC, but with the current sensitive configuration, the impulse response  $h_{max}(\delta)$  is no longer independent of shaping time, but scales as  $1/\tau$ . Dividing  $v_n$  by  $1/\tau$ , yields the usual ENC behaviour as  $A/\sqrt{\tau}$  (+)  $B\sqrt{\tau}$ .

Moreover, after calculating the noise integrals for various preamplifier rise time, it has been shown (Figure 22) that they are invariant when the noise is expressed as a function of the peaking time (5%-100%) to the step (or the triangle) which is noted tp( $\Delta$ ) allowing to write:

$$ENI = e_n C_d \frac{Bs}{t_p^{3/2}(\Delta)} \oplus i_n \frac{Bp}{t_p^{1/2}(\Delta)}$$

(3)

in which Bs and Bp are almost constant, as shown in Figure 22. Similar calculation for higher order shapers CRRC<sup>n</sup> gives the same result, making of the peaking time a good estimator of the shaper response as shown in LArG10.

Figure 22: Series and parallel noise coefficients as a function of preamplifier risetime to shaping time ratio  $\lambda$ .(top) and CRRC<sup>n</sup> filter order (bottom). The terms Bs and Bp which are used in Equation (3) to calculate ENI are almost independent of  $\lambda$  or n making the peaking time tp( $\Delta$ ) 5-100% a good estimator of filter response.

The **Pileup noise** is mostly due to the superposition of numerous minimum bias events, whose low energy allows to handle them as a noise source. The calculation is done using *Campbell's* theorem and the variance of these events is given by <sup>21</sup>:

$$\sigma_{pu}^{2} = \iint n(E)V^{2}(E,t)dEdt = \sigma_{E}^{2} \int h_{\Delta}^{2}(t)dt = C\sigma_{E}^{2} I_{pu}^{2} = C\sigma_{E}^{2} t_{p}(\Delta)$$

(4)

The pileup integral  $I_{pu}^2$  is similarly proportional to the peaking time  $t_p(\Delta)$  5-100% and increases with slower pulses as intuitively expected.

<sup>&</sup>lt;sup>21</sup> The integral assumes a continuous sum on time, disregarding the bunching at 25 ns. The effect is negligible for peaking times longer than 25 ns, below it is of course asymptotic to the irreducible pileup contained inside one bunch crossing.

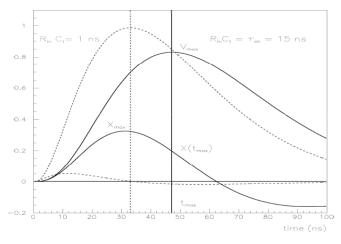

The **total noise** is the sum of all these contributions and is shown in Figure 23. The total noise exhibits an optimal shaping time at which the noise is minimal<sup>22</sup>:  $t_p^{opt} = K (e_n C_d/\sigma_E)^{1/2}$  and at this optimum the noise is given by  $ENE^{opt} = K' (e_n C_d)^{1/4} (\sigma_E)^{3/4}$  which shows that the pileup noise contribution  $\sigma_E$  is dominant. As the pileup noise is changing both in time and in rapidity, the optimum shaping time is varying and this will be done by digital filtering as shown in §3.3.

Figure 23: Total noise in a 3x7 cluster as a function of signal peaking time at low  $(L=10^{33} \text{ cm}^2\text{s}^{-1})$  and high  $(L=10^{34} \text{ cm}^2\text{s}^{-1})$  luminosity. The noise exhibits a minimum which is dominated by pileup noise.

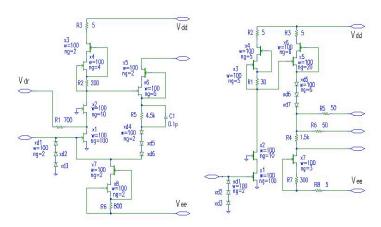

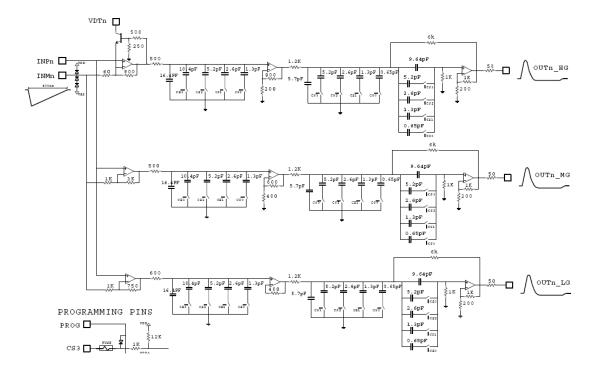

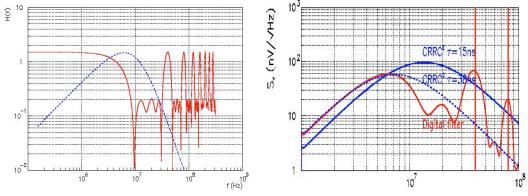

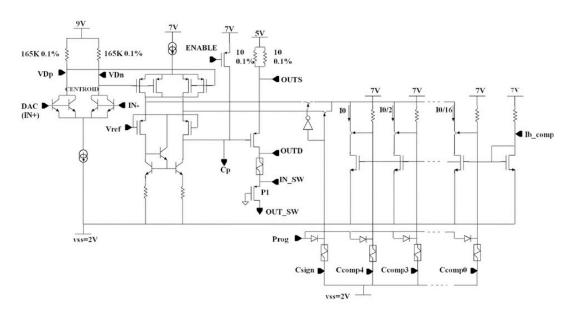

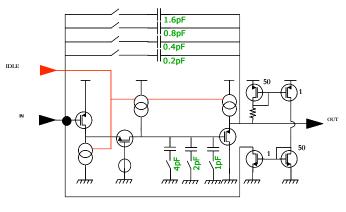

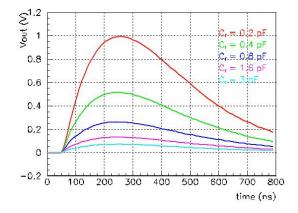

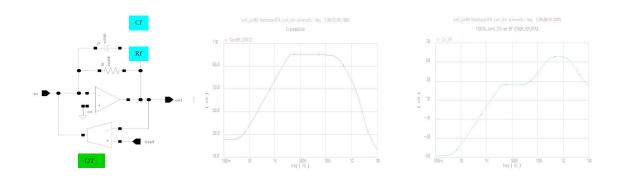

#### 3.2. Monolithic realization (LArG note 082)

As the readout electronics needed to be located right on the feedthroughs, in the crack between barrel and end-cap calorimeters, real estate was a major concern and it was obvious that the shaper needed to be integrated inside an ASIC. The schematic proposed in LARg10 was directly derived from the circuits realized with surface mount components for testbeam purposes and stubbornly oscillated<sup>23</sup>. A little later, the ØT preamp were chosen to equip the whole calorimeter, simplifying the problem of having to deal with both signal polarities and it was felt necessary<sup>24</sup> to split the 16 bits dynamic range in three linear ranges of 12 bits, with a gain ratio of 1-10-100. Afterwards, this can be considered as an overkill, but at that time the possibility of having large coherent noise in the subsequent stages (SCA, ADCs...) was very much feared. Also, as there was not such a high gain in the preamp, the shaper needed to be low noise (<2 nV/\dylambda, almost like a preamp) in order to add a negligible contribution. Moreover, the multiple sampling technique (see §3.3.) relaxed the complexity of the shaping function and a CRRC<sup>2</sup> was by far enough, minimizing the number of stages and power dissipation.

All these constraints led to the choice of an architecture based on custom low noise operational amplifiers in BiCMOS 1.2  $\mu$ m technology. To minimize the noise, the high gain amplifier was mounted in inverting configuration, providing a first gain of 10, with small resistor values (50-500). The unity gain was following the same architecture.

This calculation neglects the parallel noise which is much smaller than the series noise due to the fast shaping.

<sup>23</sup> despite the last sentence of the note!

In principle (and in the end) 2 gains with 12 bits were enough to cover the dynamic range, but coherent noise was very much feared at the time of design which pushed for having a large high gain of 100 and thus 3 gains.

Figure 24: schematic diagram of the LAr Trigain CRRC2 shaper.

Two prototypes were realized before the series production in 1999 of 65 000 chips. Between these two prototypes, the power supplies had been reduced, the RC values had been made tunable with fuses so that each shaper could be made identical irrespective of the large fluctuations on R and Cs of monolithic processes<sup>25</sup>. A linear mixer was also included, performing the analogue sum of the 4 channels in order to prepare the signal in a 0.1x0.1 tower for the LVL1 trigger.

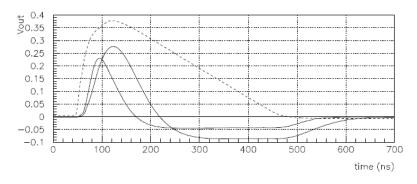

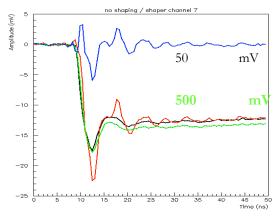

The performance is described in LArG92. An example of waveforms can be seen in Figure 25, showing the peaking time adjustment range. The 4 bits allowed the peaking time to span from 20 to 40 ns, giving a step of 1 ns for the peaking time or 0.5 ns for the time constant. In view of the results from digital filtering described in  $\S 3.3.$ , the time constant was also slowed down<sup>26</sup> to  $\tau_{SH} = 15$  ns.

Figure 25: shaper waveform for minimum and maximum peaking time adjustment. In dashed line the input signal from the  $\emptyset T$  preamplifier used to drive the shaper

Typically ±20% for resistors and capacitors

despite D. Fournier's resistance!

The three gain values were 0.8, 8 and 82 and the noise respectively 250  $\mu$ V, 350  $\mu$ V and 850  $\mu$ V giving a dynamic range of 3 V/850  $\mu$ V/82 = 400 000 = 18.5 bits

As shown in Figure 26, the linearity is within  $\pm$  0.1% on the three gains and the crosstalk at the 0.1% level.

Figure 26: linearity of the shaper  $+ \emptyset T$  preamplifier on the three gain ranges.

In 1998, 80 000 shapers were produced in an AMS 1.2  $\mu$ m BiCMOS dedicated run. They were packaged in QFP100 plastic package and tested by a robot developed by the Grenoble group (Figure 27) that allowed to test automatically this large quantity in around 6 months. The yield was found to be 85%. Later, when all the chips were soldered on the Front-End Boards, it was observed that a few per mil of the chips had instabilities in the shape, traced to fuses partially blown, that tended to reconnect.

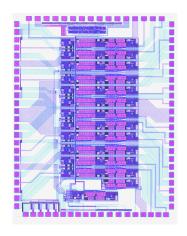

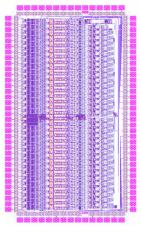

Figure 27: shaper layout (4 channels) and view of the robot developed by Grenoble group to test automatically the 80 000 chips

#### 3.3. Multiple sampling or digital filtering (LArG 80, PhD Y. Jacquier)

The multiple sampling technique was introduced in our field<sup>27</sup> by *B. Cleland* in 1993 [7]. It was a way to approach very close to the theoretical optimum filter by digital signal processing which rendered the old approach of complex filters completely obsolete. Moreover, it was flexible and adaptative, it could thus allow to always run at the optimum signal to noise ratio, on the whole calorimeter regions and adapting to the change in luminosity as the machine tuning progresses.

The calculation has been detailed several times to optimize the amplitude measurement knowing several samples on the waveform and combining them with optimized weights to form the energy. It showed than in our practical case, when the experiment would start at low luminosity, the noise could be lowered by more than a factor of 2.5 which sounded unbelievable! Naively, we were imagining that "summing" a few samples would increase the amplitude but the noise would only increase by the square root of the number of samples. This naïve approach was completely missing the role of the noise autocorrelation function.

To convince ourselves, we needed to make the calculation ourselves with the help of *L. Serin* and our PhD student *Y. Jacquier* and to do testbench measurements and actually reach the calculated values. After that, the first experimental measurements on the test beam data turned out to be very disappointing and more work was needed to understand them, in particular how could we evaluate the digital filtering transfer function and compare it with classical analog filters.

In the course of this study, several questions arose, such as:

- ∞ What is the transfer function of the digital filter, what is its effect on the signal?

- ∞ What is the noise improvement for different shaping times used ?

- Mow many samples are necessary on the waveform ?

- Mow does it compare to an optimized analog shaper ?

- ∞ On what luminosity range can it improve the signal to noise ratio ?

- ∞ For what luminosity should the analog shaper be optimized ?

- ∞ Is the analog shaper really necessary, can't we use directly the preamp signal?

- Mow accurately needs the signal shape to be known?

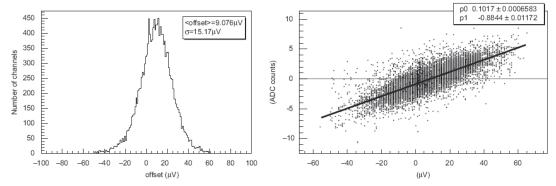

All these issues have been addressed in a detailed LAr note LArg80 (1998) **Erreur! Source du renvoi introuvable.** Without going into technical details, the pulse amplitude A is obtained by combining linearly n samples  $S_i$  on the waveform g(t) with a weight  $a_i$  and requesting the normalization  $\sum a_i g_i = 1$ . The optimum weights are obtained from the noise autocorrelation matrix  $R_{ij}$  with:

$$A = \sum_{i=1}^{n} a_i S_i \quad \text{with a}_i \text{ given by :} \quad a_i = \sum_{j=1}^{n} R_{ij}^{-1} g_j$$

(5)

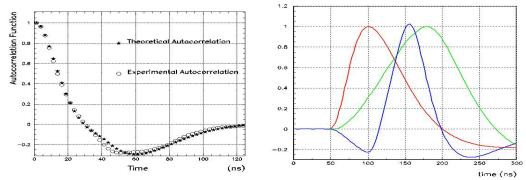

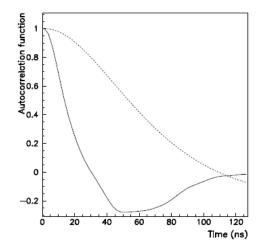

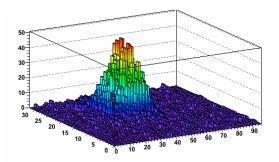

The autocorrelation function can be calculated literally as shown in *Jacquier's* thesis [8] and it is shown in Figure 28, in the case of the electronics noise of the  $\varnothing$ T preamplifier, without any pileup noise. In that case, the coefficients calculated to reduce the noise are typically  $a_i$ ={0.17, 0.34, 0.4, 0.31, 0.28}, which corresponds to a "sliding window" or close to an average over the 5 samples. The resulting waveform can be calculated at all time using Equation (5 left) and is displayed in Figure 28, showing a slower (and more symmetrical) waveform by a factor close to two. As will be discussed later, it is also possible to accelerate the pulse, also by a factor of two, for operation at very high luminosity.

<sup>&</sup>lt;sup>27</sup> It was known in other domains as "digital filtering" or Finite Impulse Response (FIR) filters

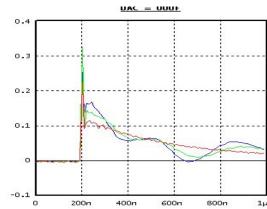

Figure 28 <u>Left</u>: autocorrelation function of  $\emptyset$ T preamplifiers. Right: signal before and after digital filtering. The red curve is the signal before digital filtering, from which the 5 samples  $g_i$ ={0, 0.63, 1, 0.8, 0.4} are taken. The green curve is the signal after digital filtering at low luminosity, applying coefficients  $a_i$ ={0.17, 0.34, 0.4, 0.31, 0.28}, resulting in a twice slower signal and reducing the electronics noise by a factor 1.8. The blue curve is the output waveform at maximum luminosity, applying coefficients  $a_i$ = (-0.75, 0.47, 0.75, 0.07, -0.19) resulting in a faster and narrower waveform, minimizing the pileup noise.

To see it in a more "electronics way", it is possible to calculate the transfer function using the z-transforms:  $H(z) = \sum a_i \ z^{-i}$  and letting  $z = \exp(j\omega T_{ech})$ , in which  $T_{ech}$  is the sampling period = 25 ns in the case of ATLAS. This is represented in Figure 29, in the case of low luminosity, showing that the digital filter is cutting down the high frequencies (low pass filter), slowing down the signal and reducing the electronics noise. The bumps at multiple of the sampling frequency (40 MHz) correspond to the classical aliases of the sampled spectrum that are folded over multiples of  $f_{ech}$ .

Figure 29. <u>Left</u>: digital shaper transfer function corresponding to the slower pulse as obtained with the z-transfrom.

<u>Right</u>: noise after digital filtering. The bumps at multiples of the sampling frequency (40MHz) produce aliases of the noise that have a sizeable contribution to the overall rms noise.

Then the noise spectrum after preamp + analog shaping + multiple sampling could also be plotted and an example is shown in Figure 29. The bumps (aliases) at multiples of 40 MHz explained why the results were not as good as expected in testbeam as the analog filter was too fast compared to the 40 MHz sampling frequency and leaving HF components that were folded by the digital filter.

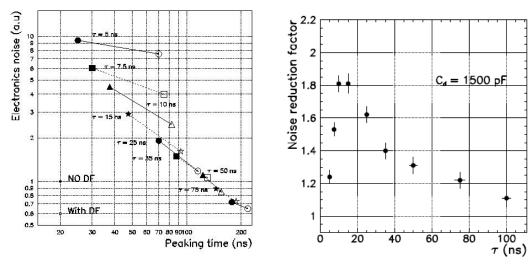

The noise improvement for different analog shaping times can then be measured and is represented in Figure 30. It can be seen that if the original signal is very fast (10-20 ns) the digital filter is slowing it down by a large factor (more than 2) but the noise is not much improved because of aliasing. The best results are obtained with analog shaping around 20-40 ns where a factor close to 2 is obtained, whereas with a slower signal (50-100 ns) the signal and noise are almost unchanged, as the samples are too close apart, being highly correlated.

Figure 30: Noise reduction as a function of analog shaper peaking time

The last exercise<sup>28</sup> consists in adding (in simulation) the pileup noise in the autocorrelation function, as shown in Figure 31, resulting in a much longer autocorrelation. The fraction of each noise source scales with the luminosity.

At low luminosity (L=10<sup>33</sup> cm<sup>2</sup>s<sup>-1</sup>) the pileup noise is small compared to the electronics noise and the digital filtering gives positive coefficients in order to minimize the electronics noise and slow down the signal. At high luminosity, the algorithm gives some negative coefficients in order to substract residuals of previous events and accelerate the signal. The resulting waveforms are shown in Figure 28, exhibiting a twice faster pulse.

Figure 31: noise autocorrelation function: solid line: electronics noise, dashed line: pileup noise.

For each luminosity, the total noise can then be calculated after optimization and is displayed in Figure 32. It can be seen that the noise after digital filtering (dashed line) is minimum over a wide luminosity range of 1033 to 1034 cm<sup>2</sup>s<sup>-1</sup>. It compares to the total noise if no filtering is done (solid line) as being always well below, and particularly at low luminosity (large electronics noise reduction). An interesting comparison is also with the optimal hardware shaping (green solid curve), if it were possible to change it dynamically and throughout the detector. It intersects the black solid curve at L=1034 cm2s-1, as the hardware shaping is optimized for this high luminosity. It can be seen that the digital filter is better than the optimized analog filter on the whole range 10<sup>33</sup> cm<sup>2</sup>s<sup>-1</sup>to 10<sup>34</sup> cm<sup>2</sup>s<sup>-1</sup> by around 10% and that it is only below 1033 that the analog filter is better again, mostly because there are not enough points taken to further slow down the pulse at very low luminosity.

28

Unfortunately, most of the analysis in ATLAS are made with the multiple sampling coefficients tuned for low luminosity operation which tends to alleviate all the systematic effects that appear at high speed, such as detector inductance impact on calibration and physics waveforms (cf Chapter 2 and 3)

Figure 32: total noise after optimal filtering for various luminosities

#### 4. Conclusion on ATLAS Front-End electronics

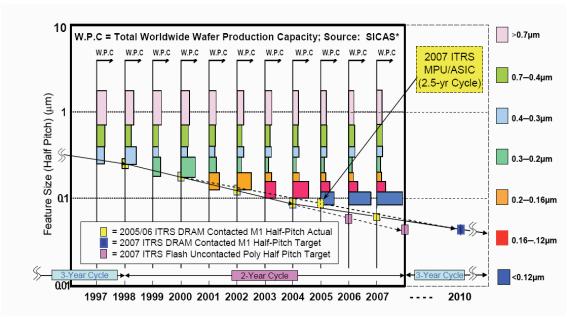

From the first prototypes to the production of all the final electronics chips and boards, more than ten years were necessary to overcome all the technical difficulties, in particular due to the speed, large dynamic range and radiation hardness encountered at the LHC. The architectural choices (current sensitive preamplifiers, fast shapers, analog memories, warm voltage driven calibration...) were made relatively early (1994-1996) and the design has barely changed compared to what was written in the TDR (1996) where most issues and problems had been found. The relatively long time between design and production was largely due to the difficulties of mastering the radiation hard DMILL process and the long irradiation and qualification tests. In 2001, all the analog ASICS were being produced in DMILL, but several digital chips had to be moved to DSM (deep sub-micron) 0.25 µm technology.

All ATLAS electronics was produced in 2003-2005 and finished to be installed in nov 2005. It has been running continuously since 2007, with only 0.06% bad or dead channels. As always, most difficulties lied in (commercial) power supplies and connectors.

Although the LHC has not yet really started, that studies are well advanced to increase the maximum luminosity from 10<sup>34</sup> cm<sup>2</sup>s<sup>-1</sup>to 10<sup>35</sup> cm<sup>2</sup>s<sup>-1</sup>. The ten-time increase in pileup and radiation levels is very cumbersome for the tracking detectors, but as shown just above, the calorimeter can easily cope with this rate, provided no un-foreseen degradation happens on a component with radiation. In effect, all the technologies used are now obsolete and it could not be reproduced or redesigned. It will thus be important to start the R&D effort to redesign all the on-detector electronics, just to be ready in case of failure and we share a R&D program with BNL, Nevis, Munich to redesign the front-end in SiGe.

As the tracker will also need to be redone for SLHC, we joined the R&D program, led by Fermilab to study new technologies of 3D electronics.

# **CHAPTER 2**

# ATLAS ELECTRONIC CALIBRATION

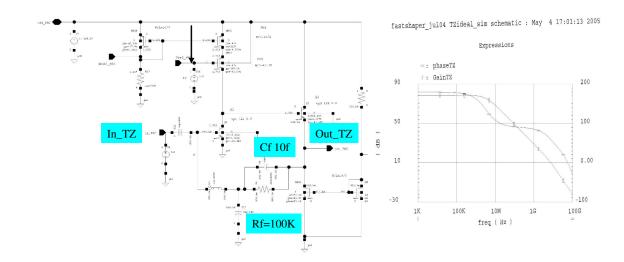

#### 1. Introduction

Traditionally, Liquid Argon calorimetry is "uniform, stable and easy to calibrate". This last point compares to detectors with internal gain where the gain is always difficult to track. In liquid Argon, it is traditionally possible to inject an accurate electric charge that corresponds to the charge created by an electromagnetic shower and to equalize all the readout channels. This used to be done with calibrated capacitors and precise voltage steps in the previous experiments and no matter how the charge arrived, only the total charge counted.

In fast calorimetry this ceased to be true and the electronic calibration started being more difficult, all the more since the requirement on overall constant term was more stringent than before due to the high energies reached. In order to correct for readout non uniformities, the calibration pulse should

- ∞ Follow the same path as the physics (or ionization) signal

- ∞ Have a similar shape as the physics signal

- ∞ Be accurate to the precision requested by the energy resolution and distributed uniformly.

Besides, the calibration pulse is used to inter-calibrate the 3 gains of the readout and must thus be very linear and is used to correct for the non linearity of the readout chain.

Very early, it was recognized that the injection of a current signal through a resistor was much more convenient than through the traditional capacitor: it is easy and relatively inexpensive to buy 0.1% accuracy resistors which solved the always difficult problem encountered with the traditional injection capacitor. Moreover, the parallel noise was no longer a concern and it did not require elaborate circuitry to generate the correct signal shape. Concerning the signal shape, the fast shaping compared to the ionization signal duration did not require an accurate triangular shape and an exponential decay with the same time constant as the decay was found to be sufficient. Two problems remained:

- Distribute the pulse uniformly over the 200 000 channels

- ∞ Generate high precision pulses over the 16 bits dynamic range

The first issue is addressed in §2. and the second in §3. and 4. as three versions of pulser have been made, starting from a 12 channel CAMAC version followed by a similar version ATLAS size but radiation soft for module 0, finished by the final radiation hard ATLAS version.

### 2. Pulse distribution

The first and determinant issue was to see whether a precise pulse could be brought inside the cryostat, right onto the electrodes without losing its accuracy or if the pulse had to be generated *in situ*.

#### 2.1. Effect of cables

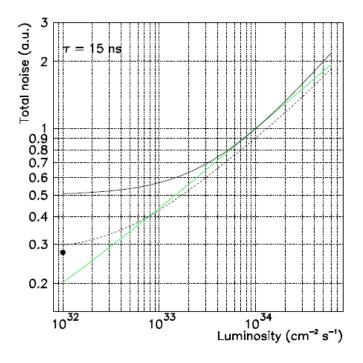

The main concern for a remote location of the pulse generator was of the course the cable that brought the signal inside, over several meters. In particular, is was well known especially after the work on the  $\mathcal{O}T$  preamps, that the cable characteristic impedance  $R_C$  could not be specified better than  $\pm 5\%$  and that was difficult to measure better than a few percent [13]. If the cable had to be at the permil level it would have been hopeless. Fortunately, for the calibration pulse, the cable could be terminated on its characteristic impedance at both ends (which was not the case for the signal for noise problems) and in that case the voltage at the output depends only to the second order on the cable impedance. To be more precise, a voltage  $V_0$  sent from a source impedance  $R_0$  into the same load  $R_0$  through a cable of impedance  $R_C=R_0(1+x)$  with  $x\ll 1$  gives a voltage V:

$$V = \frac{V_o}{2} \frac{1+x}{(1+x/2)^2} \approx \frac{V_o}{2} \left(1 - \frac{x^2}{4}\right)$$

(1)

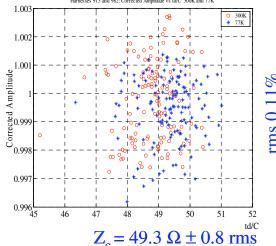

This was of course a great relief, especially when some experimental measurements comforted it, as shown in Figure 33 and as expected a 5% *rms* dispersion on the cable impedance gives 0.1% on the amplitude. Another comforting measurement on the right plot was the amplitude at the end of a real bundle of cables, which remained within 0.1% at warm and at cold.

Figure 33. <u>Left</u>: signal amplitude at the end of a cable of mismatched impedance Rc terminated in  $50\Omega$ .

<u>Right</u>: signal amplitude at the end of a calibration bundle in the warm (red) and in the cold (blue)

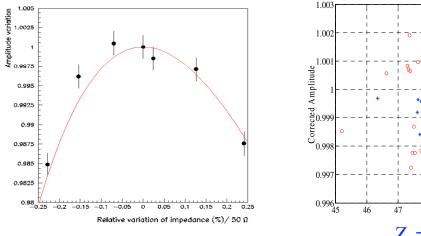

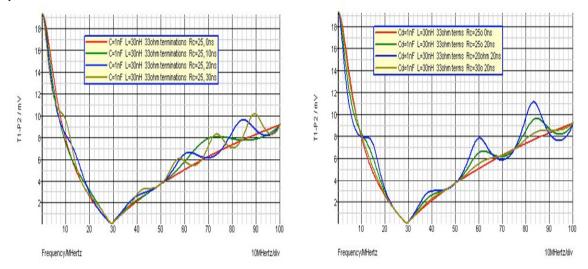

In effect, if the cable impedance is a second order effect, the skin effect which is not negligible in these miniature coaxial cable, is a first order effect, which has to be corrected. This is illustrated in the measurement from Figure 34, performed with a bundle of the final ATLAS calibration cables. The amplitude is measured for different cables lengths at room temperature and in liquid nitrogen. The attenuation is well visible at room temperature for the longest cables (typically 5 m) and improves by almost a factor of 3 in the cold<sup>29</sup>. The propagation velocity also varies with temperature, but only by -3%.

<sup>&</sup>lt;sup>29</sup> This can be expected as the copper resistivity decreases from 1.8 to 0.25 from 300K to 77K, but the skin depth scales as the square root of the resistivity, giving a net effect improvement of 2.2.

The attenuation at warm and at cold have been fitted as straight lines, as shown in Figure 34, giving:

- $\sim$  T = 300 K dV/VdT = -1.2%/K v = 5.50 ns/m

- $\infty$  T = 80 K dV/VdT = -0.5 %/K v = 5.35 ns/m

It will thus be corrected off-line. After correction the overall dispersion of the calibration pulse amplitude has also been measured on 25 harnesses of 64 cables, giving an *rms* of 0.15%

Figure 34. <u>Left</u>: calibration pulse amplitude at the end of the calibration harness, showing the attenuation due to skin effect in the warm (red) and in the cold (blue). <u>Right</u>: attenuation as a function of cable length warm and cold. The effect of several % needs to be corrected offline.

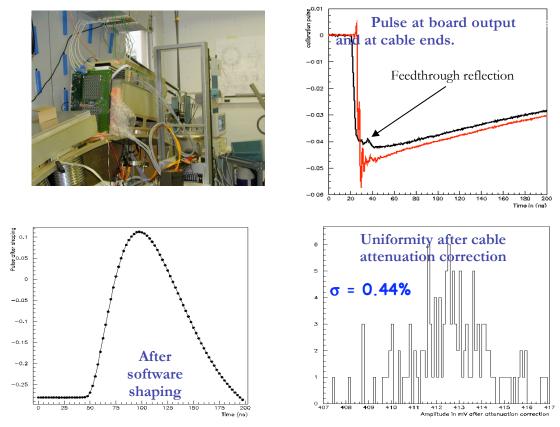

Several additional effects, worrisome with % accuracies have been verified, in particular the effect of the feedthroughs and their 33  $\Omega$  characteristic impedance (Figure 35) and all the various connections. The simulations have shown that their effect was negligible, however once again their DC resistance came as a first order effect (typically 2  $\Omega$  in a 100  $\Omega$  chain) and resulted in a tight specification and quality control.

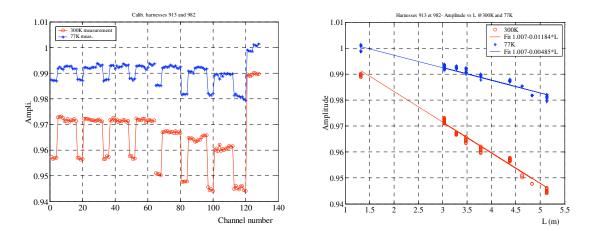

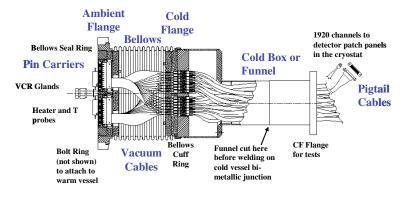

Figure 35: synoptic diagram of the calibration signal path, made of several different cables: Harness A from motherboards to patch panel, Harness B form patch panel to feedthroughs, harness C inside the feedthrough and Harness D from Feedthrough to calibration boards

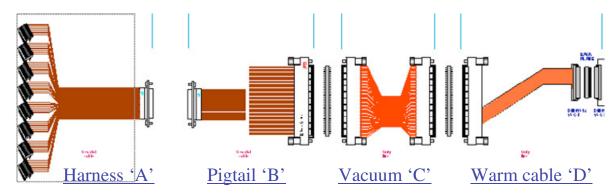

As usual, simulations are comforting but the real physicists believes only in (his) measurements and the calibration pulses were all measured on the mockup that was setup at BNL in april 2003 with the final calibration boards (Figure 36). Although the signal did not look so good at the end of the cable, all the waveforms were recorded, the LArG shaping was applied by software<sup>30</sup>, the cable attenuation of -1%/m was corrected for and the result gave a uniformity of 0.44%, which should further improve in the cold.

$<sup>^{30}</sup>$  By a simple convolution with the impulse response of a CRRC2 shaper with tau=25 ns.

Figure 36: Overview of the calibration mockup at BNL (top left). Example of calibration pulse recorded at the beginning and end of the calibration distribution path. Pulse shape reconstructed after digital filtering simulating LAr readout chain and reconstructed amplitude uniformity

#### 2.2. Pulse distribution on motherboards

Having an accurate pulse at the cable output is nice, but it still has to be delivered to several distant channels (Figure 37) through the calibration injection resistors  $R_{INJ}$ . As these are 3 k $\Omega$ , 1 k $\Omega$  and 500  $\Omega$ , 16 channels could be pulsed in the front and 8 in the middle or back (see Figure 7) for detector segmentation). These were grouped in resistive networks designed by BNL and produced by Sfernice with 0.1% accuracy and low temperature coefficient (-70 ppm).

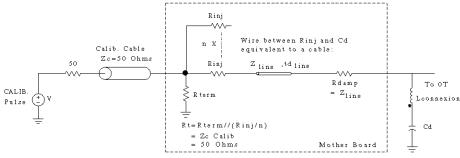

Figure 37: principle of calibration pulse distribution. The calibration line is terminated by a resistor  $R_{TERM}$  and drives 8 to 16 injection resistors  $R_{INJ}$ . The lines on the motherboard that bring the calibration pulse to the detector are equalized in length and terminated in series at their receiving end by a 50  $\Omega$  resistor  $R_{DAMP}$

The networks incorporate the injection resistor itself  $(R_{INJ})$  and a termination resistor so that the input impedance of the network be precisely  $50~\Omega$ . Moreover, as the line on the PCB that connects the injection resistor to the detector is already a few ns long and is not terminated, it makes wiggles on the calibration pulse and it was necessary to add a damping resistor of its characteristic impedance  $50~\Omega$  at its receiving end called  $R_{DAMP}.$  The injection resitor is thus  $R_{INJ} + R_{DAMP}.$  Three types of networks have been produced with the following values (at cold) :

Front : 16 resistors of 2950  $\Omega$  and a termination resistor of 214.3  $\Omega$

Middle A and Back : 8 resistors of 950  $\Omega$  and a termination resistor of 83.3  $\Omega$

Middle B: 8 resistors of 550  $\Omega$  and a termination resistor of 250  $\Omega$

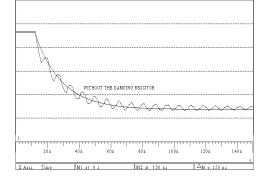

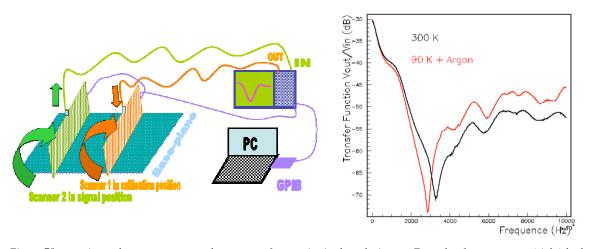

The termination resistor value is a first effect on the signal amplitude (as well as the injection resistors). Hence, they have all been measured to 0.1% accuracy, including several times in-situ, on the feedthroughs with an automated developed setup developed in Orsay. A scanner board that plugged into the feedthroughs connectors allowed to scan all the channels through a GPIB interface and perform a three-points measurement<sup>31</sup> to reach the required accuracy.

Figure 38: measured values of calibration resistors in Presampler, Front, Middle and Back sections of the calorimeter. The dispersion is always lower than 0.1%, as requested.

Finally, the crosstalk was measured to be lower than 0.1%, dominated by low profile connectors, which is also a very important measurement (cf Chapter 3, section 3). Some faulty feedthroughs initially produced much larger crosstalk through the ground return impedance that would have rendered the calibration almost useless.

<sup>&</sup>lt;sup>31</sup> The DC current was injected with the calibration input and the resulting voltage was measured on each channel, producing a three-points measurement (the ground is common for both current and voltage probes).

# 3. Module 0 pulse generator design

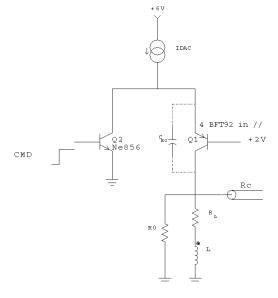

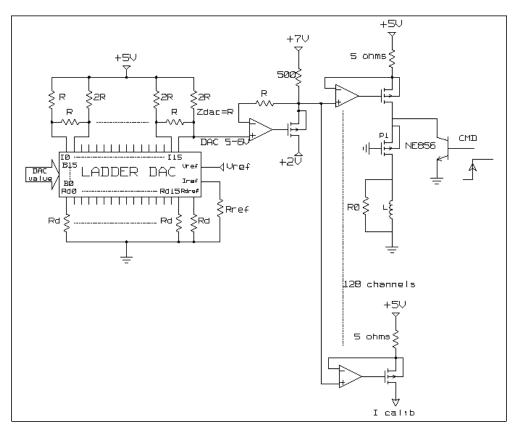

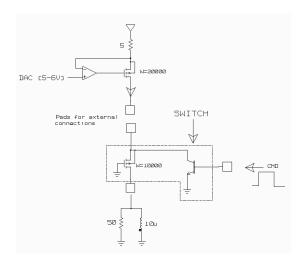

The pulse generator aims at providing 1 ns risetime pulses up to 5 V in 50  $\Omega$  load with a 0.2% absolute accuracy or uniformity between channels, a dynamic range of 16 bits and a linearity at the 0.1% level. To cover the 16 bits, when the maximum pulse is 5 V, the minimum one (LSB) is around 80  $\mu$ V. The pulse generator is derived from the H1 pulse generator designed by *B. Chase* and composed of a precision DC current source  $I_{DAC}$  transformed into a pulse by a High Frequency switch (Figure 39).

#### 3.1. HF PNP switch

The pulse is made from a precise DC current  $I_{DAC}$  flowing into a 0.1% precision resistor  $R_0 = 50~\Omega$  and when the current is cut, the voltage goes from  $-R_0I_{DAC}$  to 0 producing a negative steep voltage step. One important improvement was made by adding an inductor in parallel with the resistor  $R_0$ , producing the exponential pulse decay matched to the ionization current decay but also improving greatly the linearity as the voltage remains constant to almost zero when the current  $I_{DAC}$  is changing. The pulse is made by the inductor stored magnetic energy discharging into the resistor  $R_0$ . This was also important to minimize the power dissipated in  $R_0$  which produces non linearity.

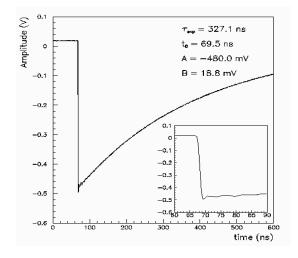

The pulse obtained is shown in Figure 40, with indeed a nanosecond fall time and a decay time given by the inductor of  $L=10~\mu H$ ,  $t_{CAL}=320~ns$ , matched to the drift time in LAr. It can also be seen that the signal doesn't start from zero, but from a small DC value, given by the parasitic series resistance of the inductor  $R_L$ . However, this element does not change the absolute pulse amplitude<sup>32</sup> which is given only by  $I_{DAC}$  and  $R_0$ .

Indeed the pulse is defined by

- $\infty$  Vout(t) = (R<sub>L</sub> | | R<sub>0</sub>/2) I<sub>DAC</sub> t<0

- $\sim Vout(t) = R_0^2/4(R_L + R_0/2) I_{DAC} exp(-t/t_{cal}) t>0$

In which

- $\infty$  R<sub>0</sub> = 50  $\Omega \pm 0.1\%$

- $\infty$  R<sub>L</sub> = 1.8  $\Omega \pm 2\%$

- $\infty$  I<sub>DAC</sub> = 3  $\mu$ A 200 mA

- $\infty$  t<sub>CAL</sub> = 2L/R0 = 317 µs

- $\infty$  L = 9.3  $\mu$ H  $\pm$  0.15

All these component values have been measured on the module 0 calibration boards described in the next section and dispersions are *rms* values on these measurements.

Figure 39: simplified schematic of the pulse generator

Figure 40: calibration pulse shape

$<sup>^{32}</sup>$  The resistance is in series with the current generator loaded by R0/2, the voltage across R/2 is still  $I_{\rm DAC}*R0/2$ . What changes is that the pulse does not start from 0V but from (RL//R0/2)\* $I_{\rm DAC}$  but actually decays to 0V. This small change departure from a pure exponential pulse will be modelized in the pulse reconstruction

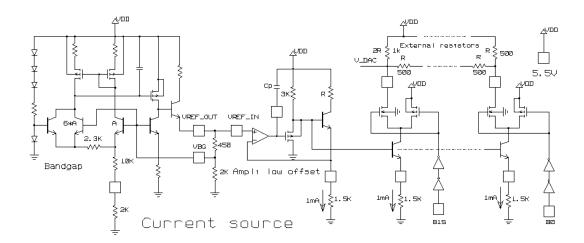

#### 3.2. DC current source

The first design (Figure 41) was done in CAMAC in 1994 with discrete components for the test beam. The precision current source used commercial low-offset opamps. To produce 5 V into 25  $\Omega$ , the maximum current  $I_{DAC}$  needs to go up to 200 mA and power dissipation issues quickly become determinant. The current source is thus made around a 5  $\Omega$  precision resistor and an opamp regulating a DAC voltage up to 1 V across it. The DAC Least Significant Bit (LSB) is thus <sup>33</sup> 16  $\mu$ V and it is important to use an opamp with an offset lower than this value, we used the OP07. As the HF switch was using bipolar transistors, it was necessary to compensate for their base current, which was measured in a separate branch and added to the reference current.

Figure 41: photograph and detailed schematic of the first CAMAC calibration pulse generator used in the testbeam of the 2 m prototype in 1992-1994. The same schematic was kept for Module 0 calibration boards, but the apparition of surface mount components allowed to implement 128 channels on a 400x500 mm board.

37

$<sup>33 \</sup>text{ 1 V/65 536} = 16 \,\mu\text{V}$

#### 3.3. Module 0 board realization

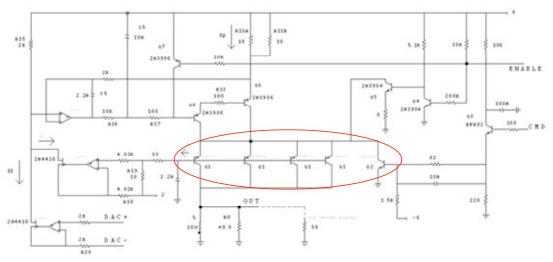

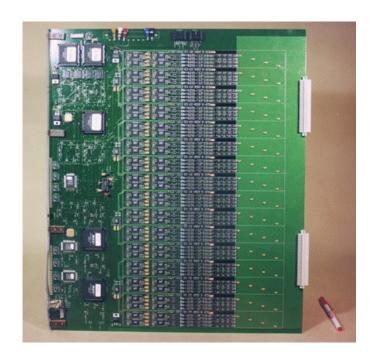

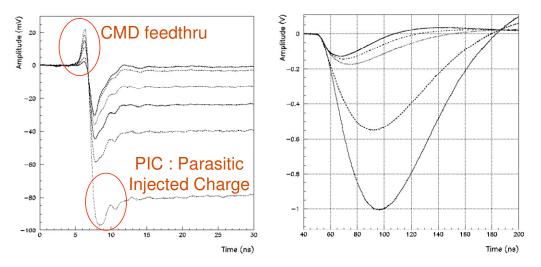

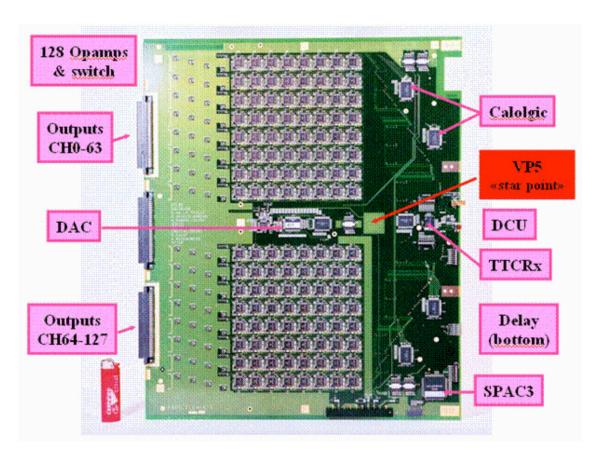

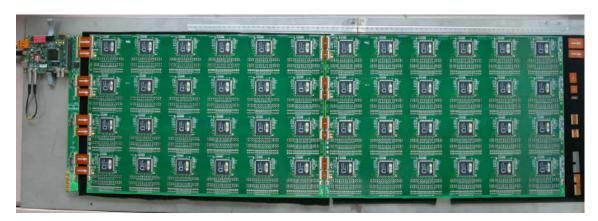

The boards were the full ATLAS size (400x500 mm) and had to fit 128 channels. In order to be as uniform as possible, all the analogue channels were identical and fitting in a width of 5 mm to accommodate 64 channels on both sides, which was very challenging at the time<sup>34</sup>. As can be seen in Figure 42, a large area was taken by the inductors which needed to be 2 cm apart in order to make crosstalk by mutual inductance negligible.

The digital part had been designed by LAPP Annecy and was very ambitious. One could load a full sequence of calibration in FPGAs that would sequence the usual runs of loops on DAC values, patterns and number of trigger pulses.

Figure 42: module 0 Calibration boards

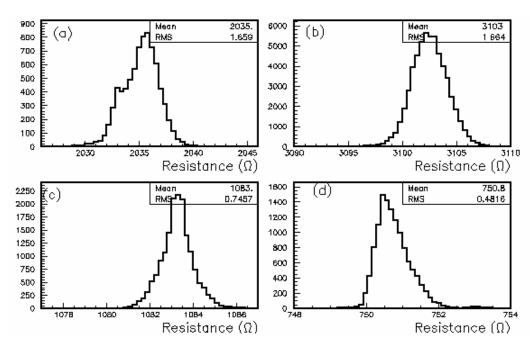

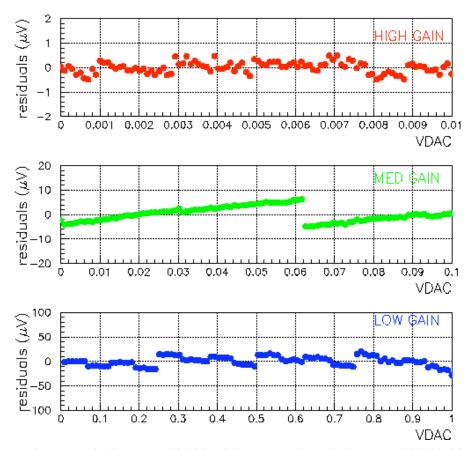

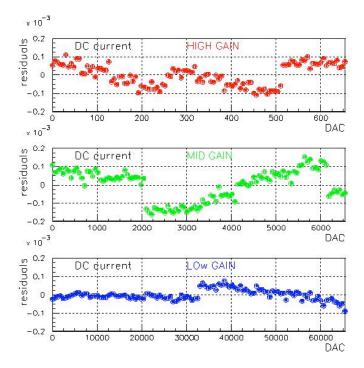

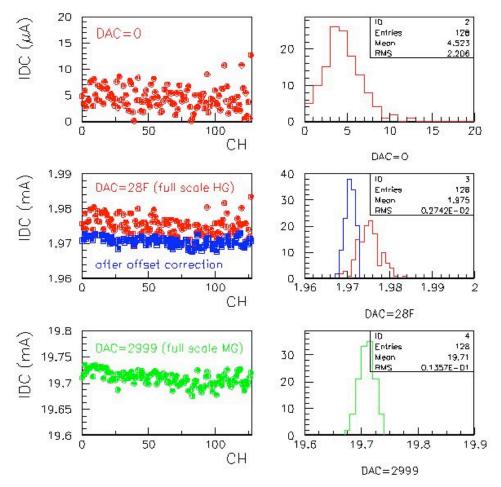

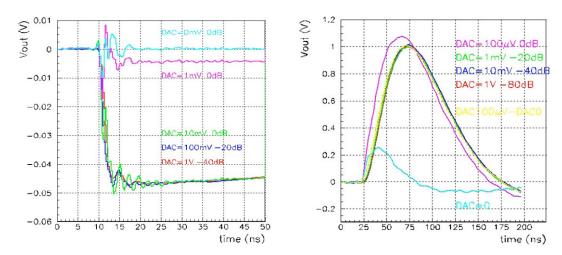

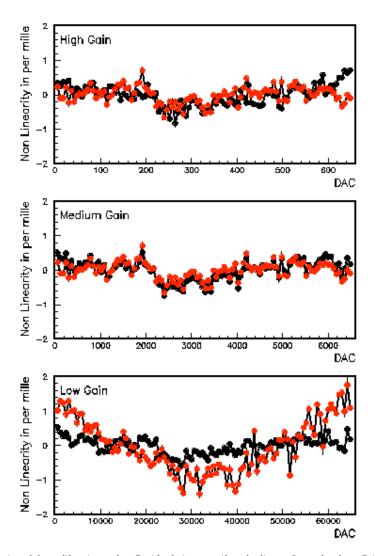

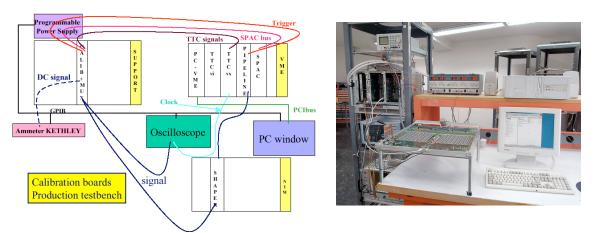

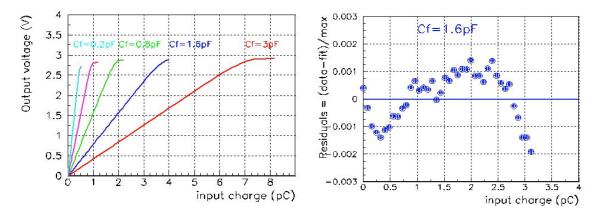

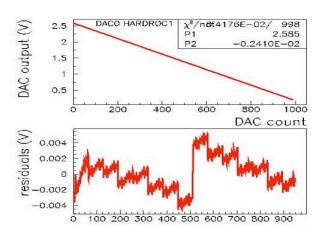

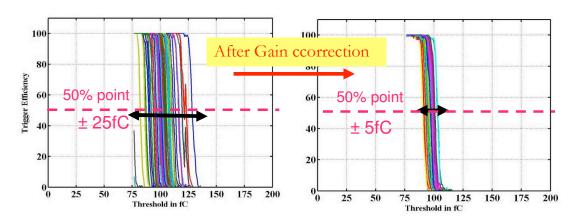

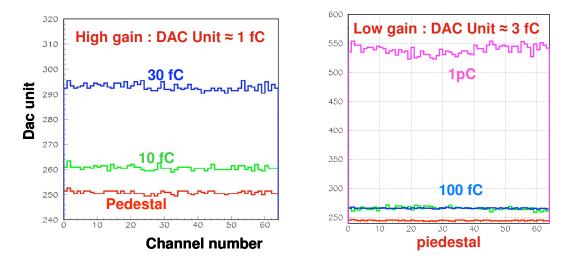

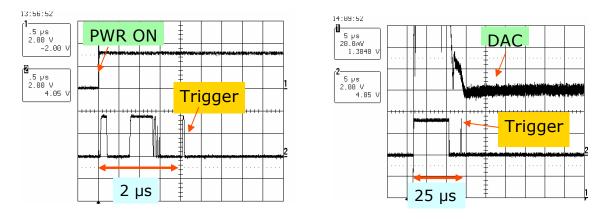

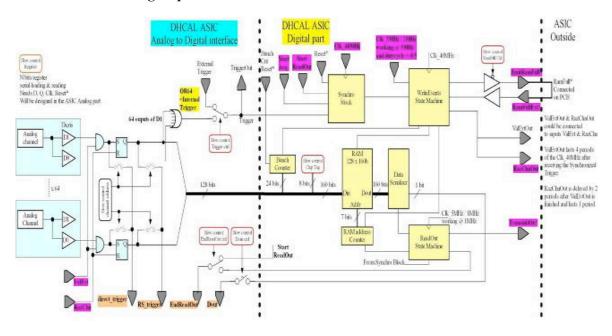

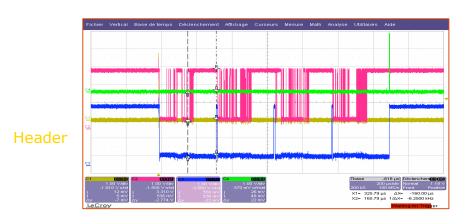

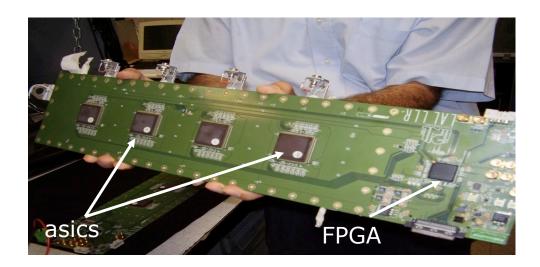

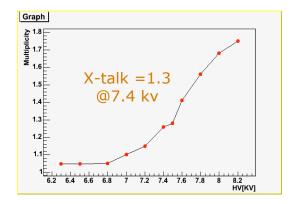

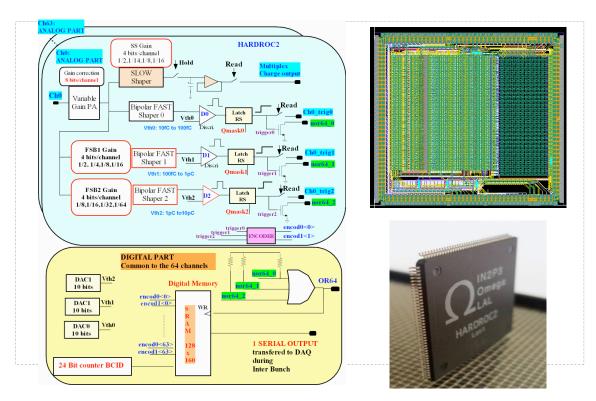

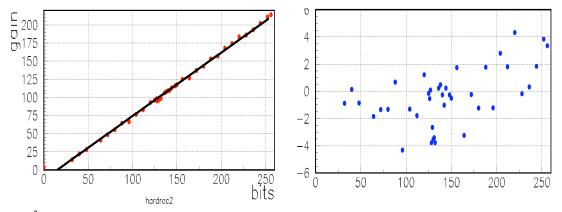

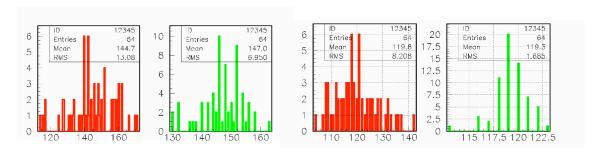

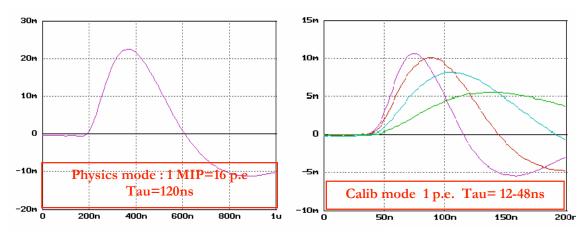

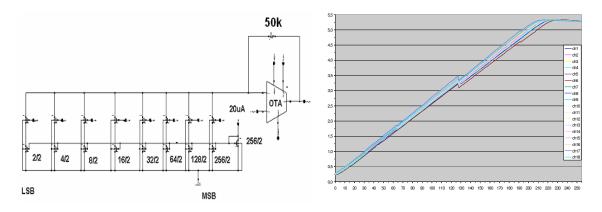

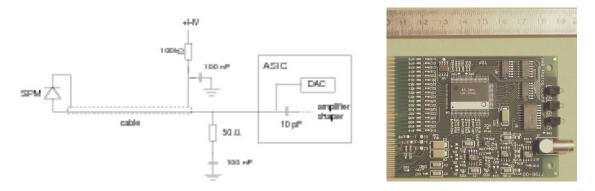

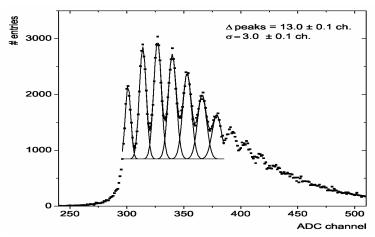

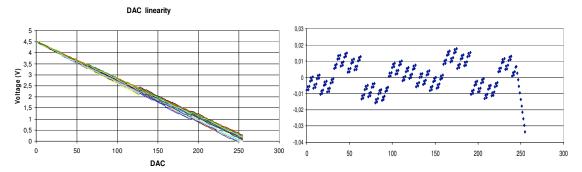

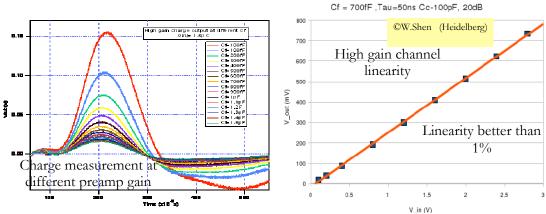

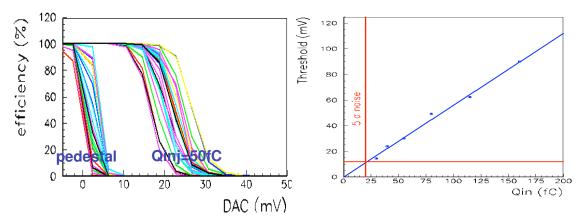

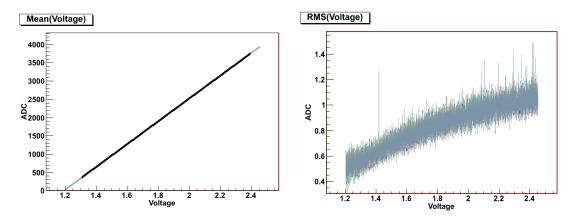

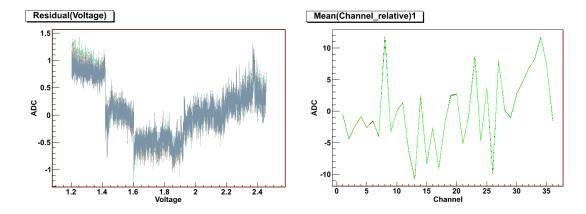

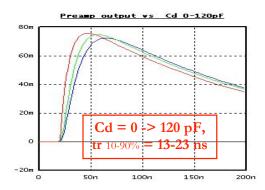

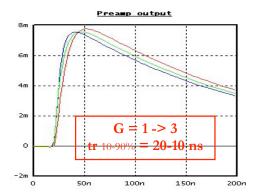

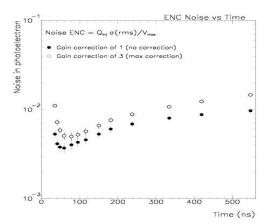

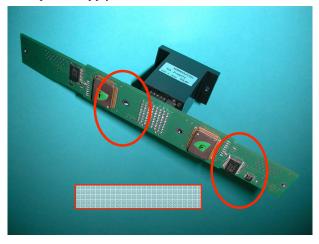

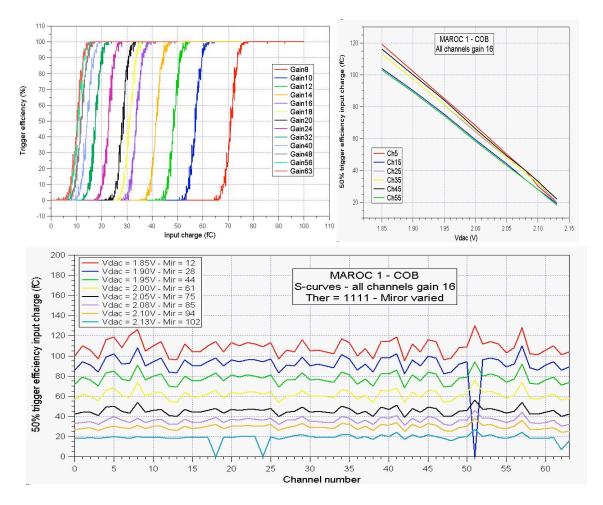

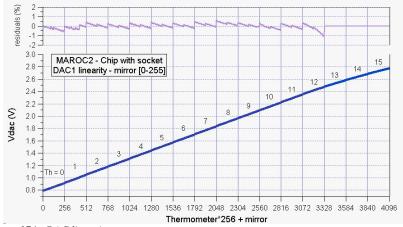

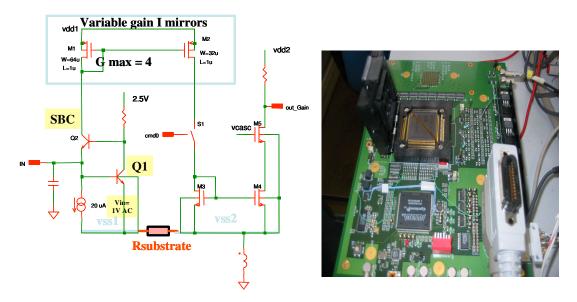

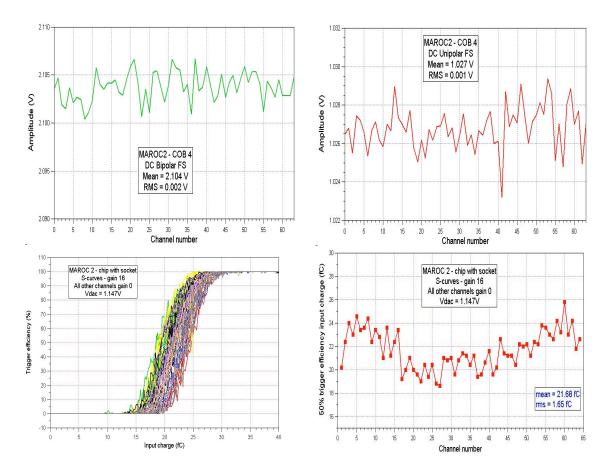

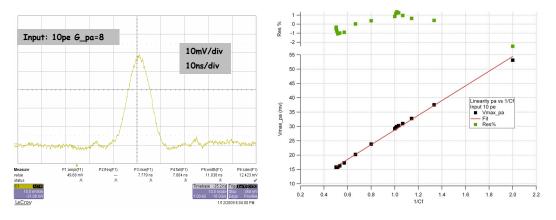

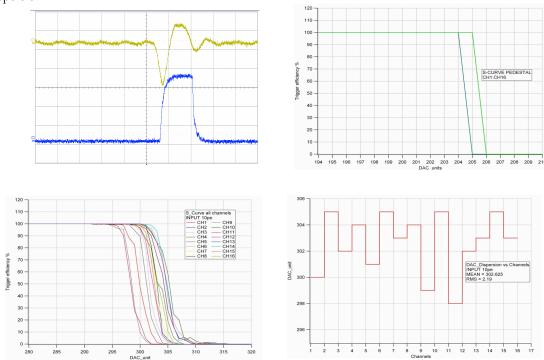

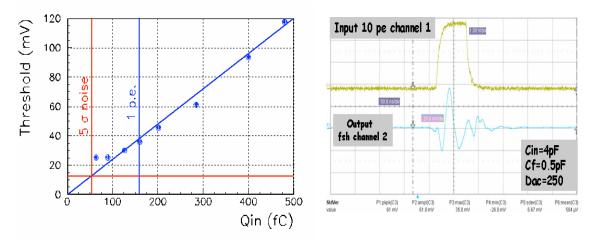

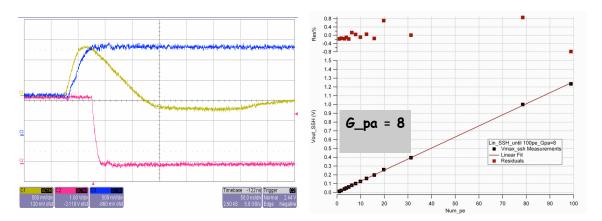

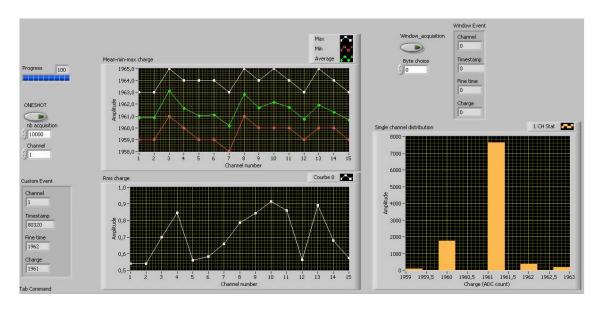

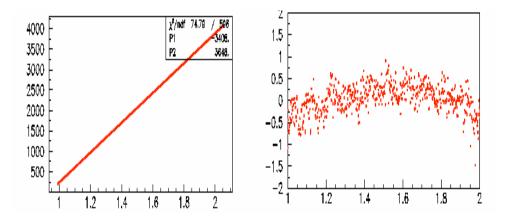

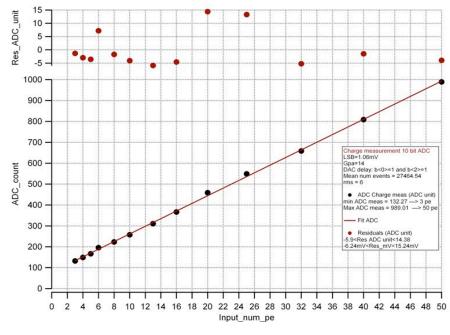

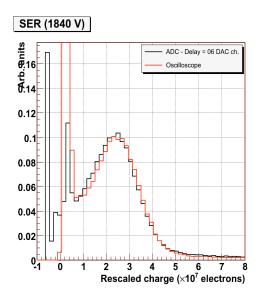

# 3.4. Performance