---

# **Evaluation of scalable gate architecture components for Si/SiGe spin qubits**

Single-shot spin readout, enhanced charge sensing

and noise spectroscopy

---

DISSERTATION

*zur Erlangung des

Doktorgrades der Naturwissenschaften (Dr. rer. nat.)

der Fakultät für Physik der Universität Regensburg*

*vorgelegt von

Andreas Schmidbauer

aus München

2024*

Das Promotionsgesuch wurde eingereicht im Februar 2024.

Die Arbeit wurde angeleitet von Prof. Dr. Dominique Bougeard.

Erstgutachter: Prof. Dr. Dominique Bougeard

Zweitgutachter: Dr. Lars Schreiber

Vorsitzende: Prof. Dr. Milena Grifoni

Prüfungsausschuss: PD Dr. Andreas Hüttel

# Contents

|            |                                                                                                     |           |

|------------|-----------------------------------------------------------------------------------------------------|-----------|

| <b>1</b>   | <b>Introduction</b>                                                                                 | <b>1</b>  |

| <b>2</b>   | <b>Concepts</b>                                                                                     | <b>5</b>  |

| <b>2.1</b> | <b>Experimental platforms for quantum computers</b>                                                 | <b>5</b>  |

| 2.1.1      | State-of-the-art of spin qubits in semiconductors                                                   | 9         |

| <b>2.2</b> | <b>Gate-defined quantum dots in a silicon quantum well heterostructure</b>                          | <b>11</b> |

| 2.2.1      | Formation of a 2DEG in a quantum well by heterostructure engineering and electrostatic band bending | 11        |

| 2.2.2      | Heterostructure analysis by magnetotransport                                                        | 14        |

| <b>2.3</b> | <b>Single-electron physics in Si/SiGe</b>                                                           | <b>15</b> |

| 2.3.1      | Coulomb blockade: Single energy states according to electron occupation                             | 16        |

| 2.3.2      | Readout of a spin qubit via charge sensing                                                          | 18        |

| 2.3.3      | Spin qubit in a magnetic field                                                                      | 20        |

| <b>3</b>   | <b>Setup and measurement techniques</b>                                                             | <b>25</b> |

| <b>3.1</b> | <b>Fabrication</b>                                                                                  | <b>25</b> |

| 3.1.1      | Epitaxial growth of the heterostructure                                                             | 25        |

| 3.1.2      | Sample fabrication                                                                                  | 26        |

| 3.1.3      | Qubit device: Accumulation vs. depletion mode                                                       | 27        |

| 3.1.4      | Hall bar sample                                                                                     | 29        |

| <b>3.2</b> | <b>Cryostat</b>                                                                                     | <b>30</b> |

| 3.2.1      | Liquid helium cryostats                                                                             | 30        |

| 3.2.2      | Dilution cryostat                                                                                   | 33        |

## Contents

---

|                                                                                                      |            |

|------------------------------------------------------------------------------------------------------|------------|

| <b>3.3 Electrical equipment</b> .....                                                                | <b>34</b>  |

| 3.3.1 Electrical connecting concepts in the different measurement setups .....                       | 35         |

| 3.3.2 Printed circuit board (PCB) .....                                                              | 38         |

| 3.3.3 Digital-to-analog converter (DAC) and arbitrary waveform generator (AWG) .....                 | 39         |

| 3.3.4 Sample readout circuit .....                                                                   | 41         |

| <b>3.4 Noise floor measurement of the setup</b> .....                                                | <b>42</b>  |

| <b>4 Hall bar study of the electron density</b> .....                                                | <b>45</b>  |

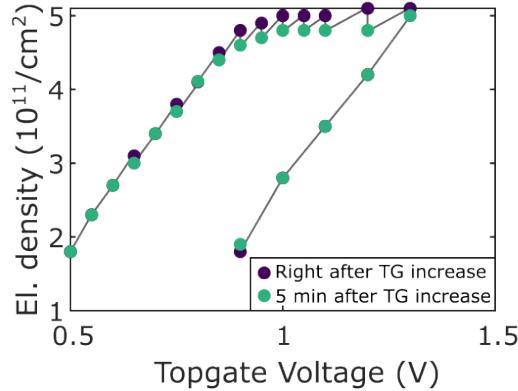

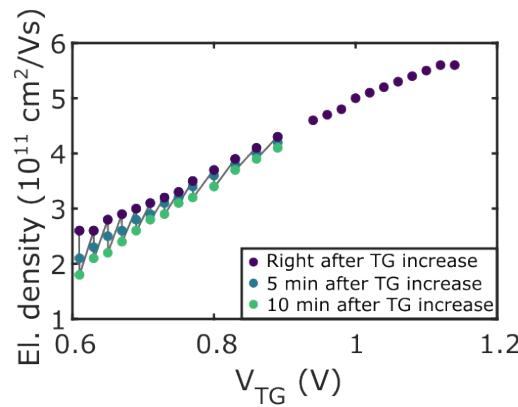

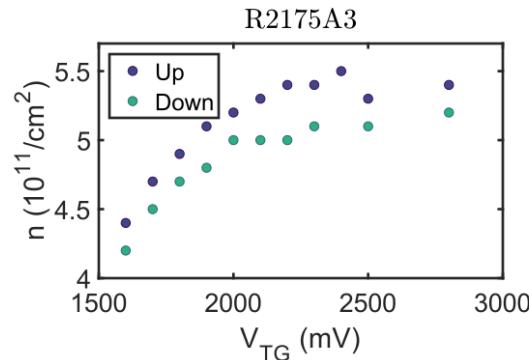

| <b>4.1 Stability of the accumulated electron density</b> .....                                       | <b>45</b>  |

| 4.1.1 Different gate voltage dependent regimes .....                                                 | 45         |

| 4.1.2 Effects of the oxide quality on the stability of the charge carrier density .....              | 48         |

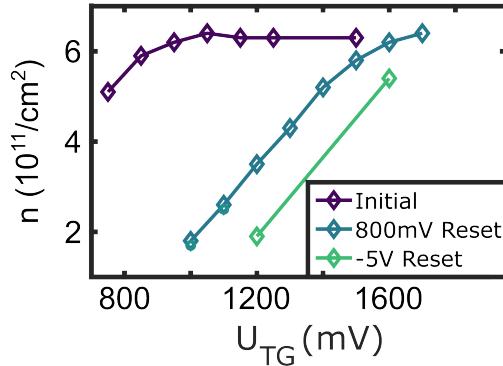

| <b>4.2 Handling interface trap states in gate-defined quantum devices</b> .....                      | <b>49</b>  |

| 4.2.1 Reset of charge carriers .....                                                                 | 49         |

| 4.2.2 Biased cooling .....                                                                           | 50         |

| 4.2.3 Illumination of the sample .....                                                               | 51         |

| <b>4.3 Summary</b> .....                                                                             | <b>52</b>  |

| <b>5 Asymmetric sensing dot (ASD)</b> .....                                                          | <b>53</b>  |

| <b>5.1 Concept</b> .....                                                                             | <b>55</b>  |

| <b>5.2 Characterization of a 1<sup>st</sup> generation proof of concept gate layout</b> .....        | <b>58</b>  |

| 5.2.1 Transport measurements at 360 mK .....                                                         | 61         |

| 5.2.2 Experimental proof of the ASD concept .....                                                    | 62         |

| 5.2.3 Interim conclusion .....                                                                       | 65         |

| <b>5.3 2<sup>nd</sup> generation ASD device</b> .....                                                | <b>66</b>  |

| 5.3.1 Layout considerations and simulations .....                                                    | 67         |

| 5.3.2 Device tuning and constant voltage bias charge sensing .....                                   | 69         |

| 5.3.3 Tuning of the sensor asymmetry .....                                                           | 72         |

| 5.3.4 Makima fit .....                                                                               | 74         |

| 5.3.5 Current gap at positive bias .....                                                             | 77         |

| <b>5.4 Constant current charge sensing</b> .....                                                     | <b>77</b>  |

| <b>5.5 Conclusion</b> .....                                                                          | <b>80</b>  |

| <b>6 Spin qubit device (Qubus)</b> .....                                                             | <b>81</b>  |

| <b>6.1 Device initialization and tuning</b> .....                                                    | <b>82</b>  |

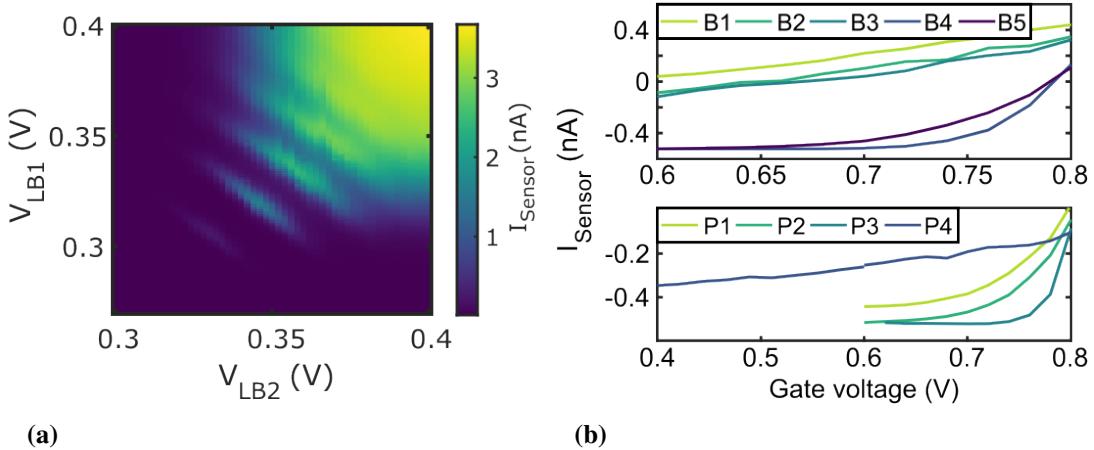

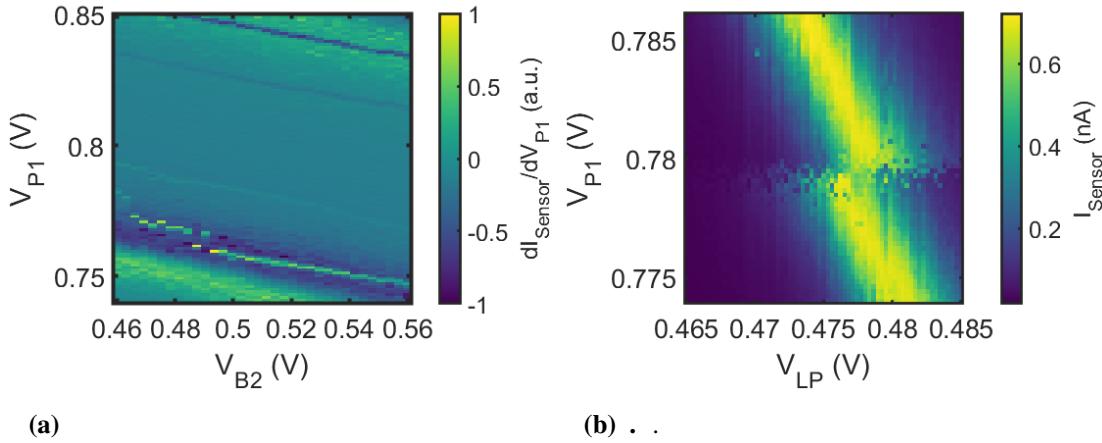

| 6.1.1 Tuning the sensor, a single and a double qubit system .....                                    | 83         |

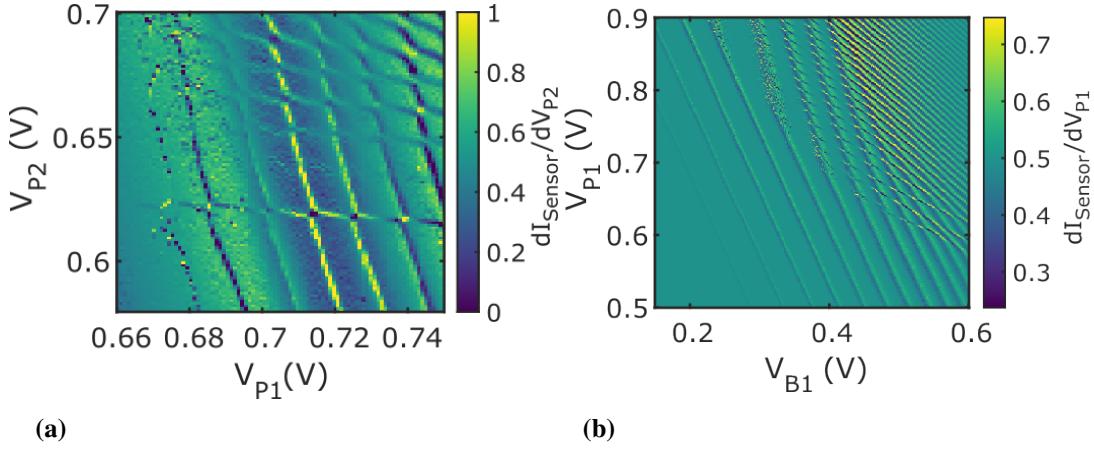

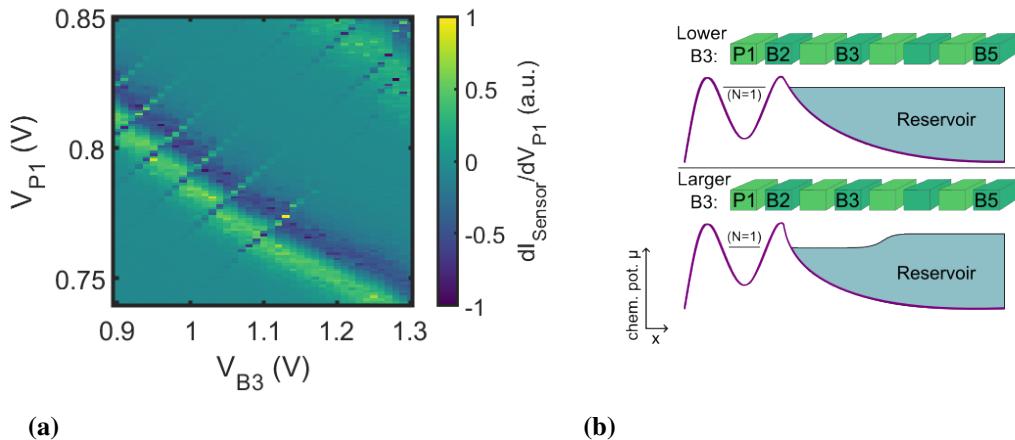

| 6.1.2 Tunnel rate tuning by barrier and plunger gates .....                                          | 88         |

| 6.1.3 Simultaneous use of the sensor dot as electron reservoir .....                                 | 92         |

| 6.1.4 Using the Qubus channel as elongated electron reservoir .....                                  | 97         |

| <b>6.2 Single-shot spin readout via spin-dependent tunneling to low-dimensional reservoirs</b> ..... | <b>104</b> |

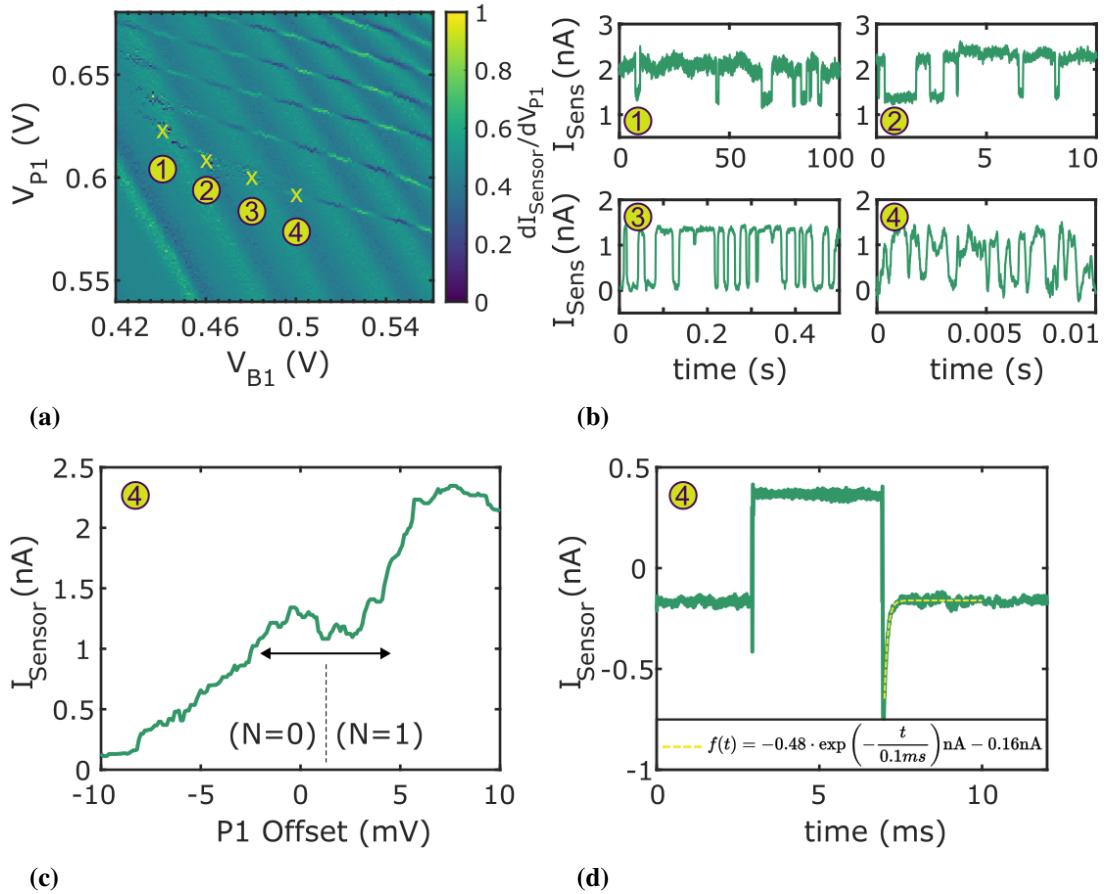

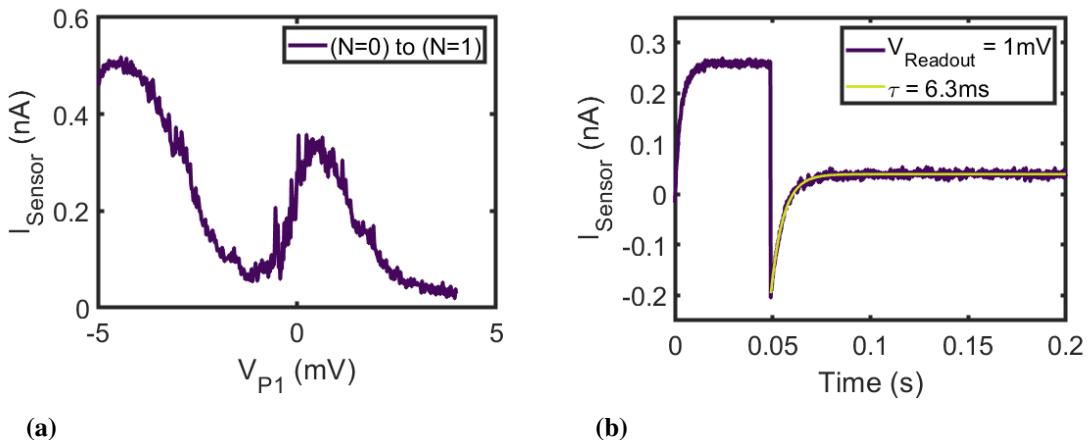

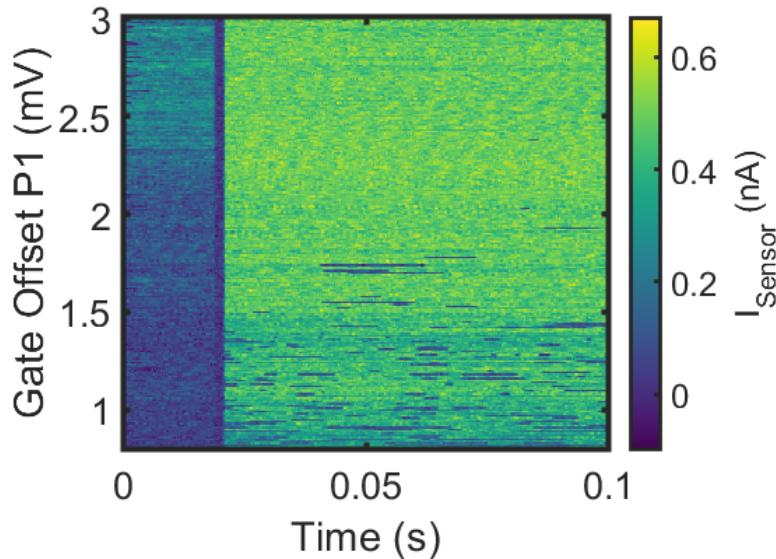

| 6.2.1 Adjusting the readout position and first spin to charge conversion .....                       | 105        |

|            |                                                                                        |            |

|------------|----------------------------------------------------------------------------------------|------------|

| 6.2.2      | Fidelity evaluation of the spin readout via reservoir tunneling . . . . .              | 109        |

| 6.2.3      | $T_1$ measurement . . . . .                                                            | 111        |

| 6.2.4      | Summary and outlook . . . . .                                                          | 113        |

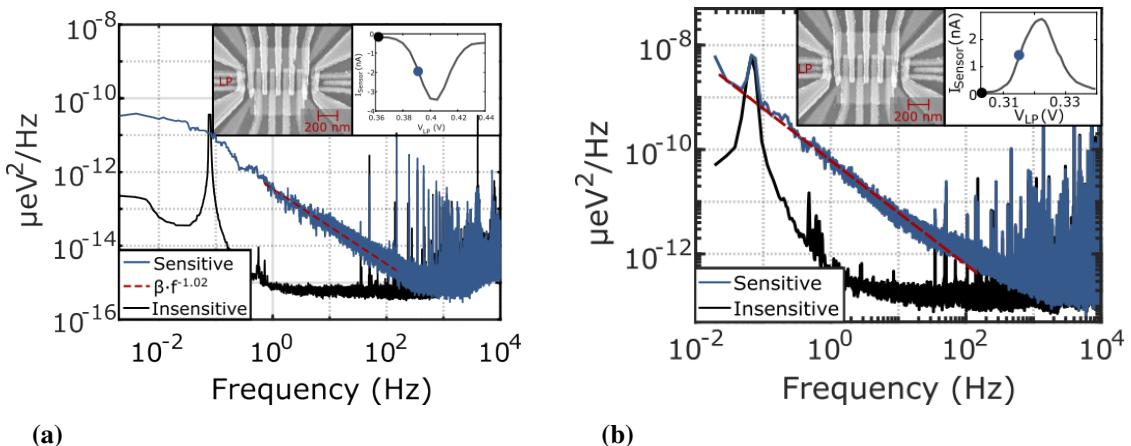

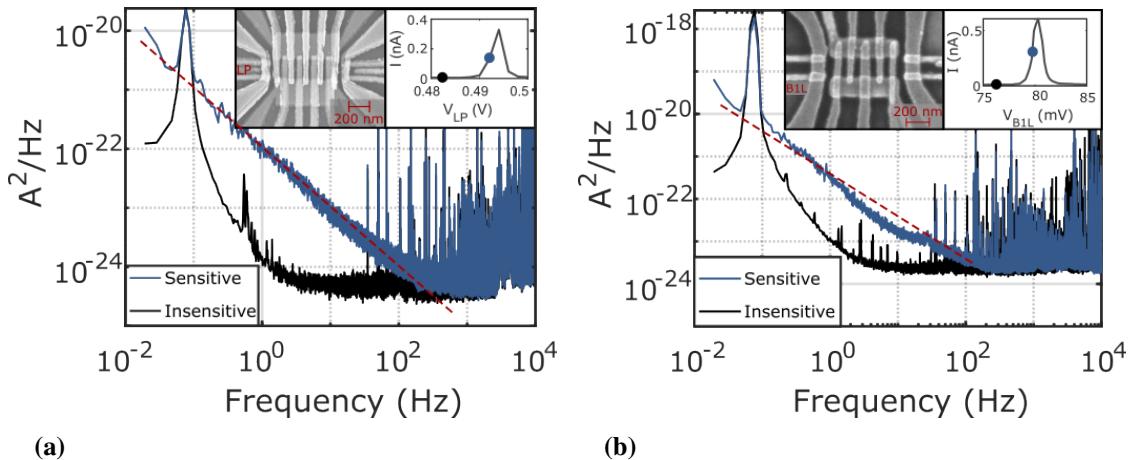

| <b>7</b>   | <b>Charge noise power spectral density . . . . .</b>                                   | <b>115</b> |

| <b>7.1</b> | <b>Calculation of the power spectral density . . . . .</b>                             | <b>116</b> |

| <b>7.2</b> | <b>Analyzing the noise floor . . . . .</b>                                             | <b>116</b> |

| <b>7.3</b> | <b>Quantification of device-related noise: <math>S_0(1\text{ Hz})</math> . . . . .</b> | <b>118</b> |

| <b>7.4</b> | <b>Discussion of sensor charge noise: <math>f^{-\alpha}</math> . . . . .</b>           | <b>119</b> |

| 7.4.1      | A $f^{-1}$ spectral dependence of the noise . . . . .                                  | 119        |

| 7.4.2      | Gate voltage induced deviation from $f^{-1}$ . . . . .                                 | 122        |

| <b>7.5</b> | <b>Conclusion . . . . .</b>                                                            | <b>126</b> |

| <b>8</b>   | <b>Conclusion . . . . .</b>                                                            | <b>129</b> |

| <b>A</b>   | <b>Appendix A . . . . .</b>                                                            | <b>133</b> |

| <b>A.1</b> | <b>Appendix - Hall bar . . . . .</b>                                                   | <b>133</b> |

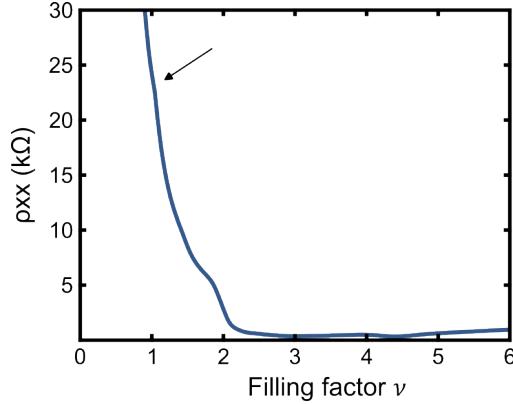

| A.1.1      | Approaching filling factor $\nu = 2$ , spin and valley splitting . . . . .             | 133        |

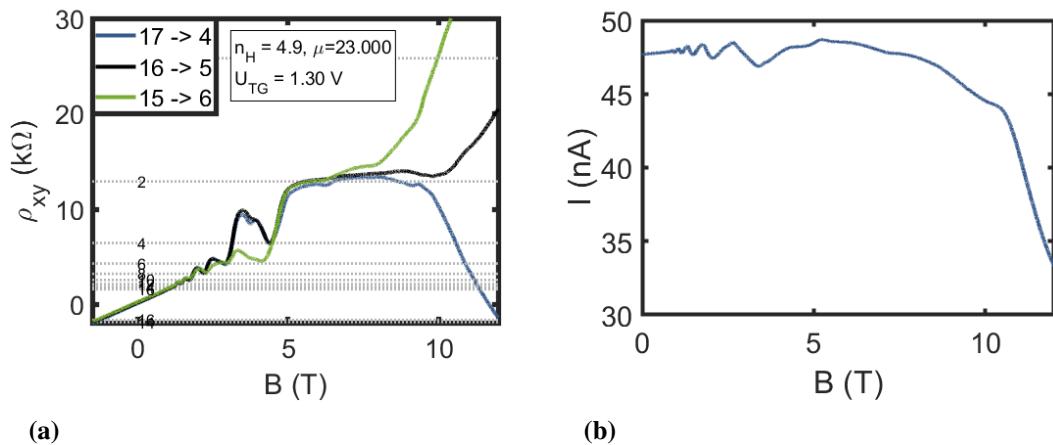

| A.1.2      | Measurements at low mobility and low filling factor: A technical consideration         | 136        |

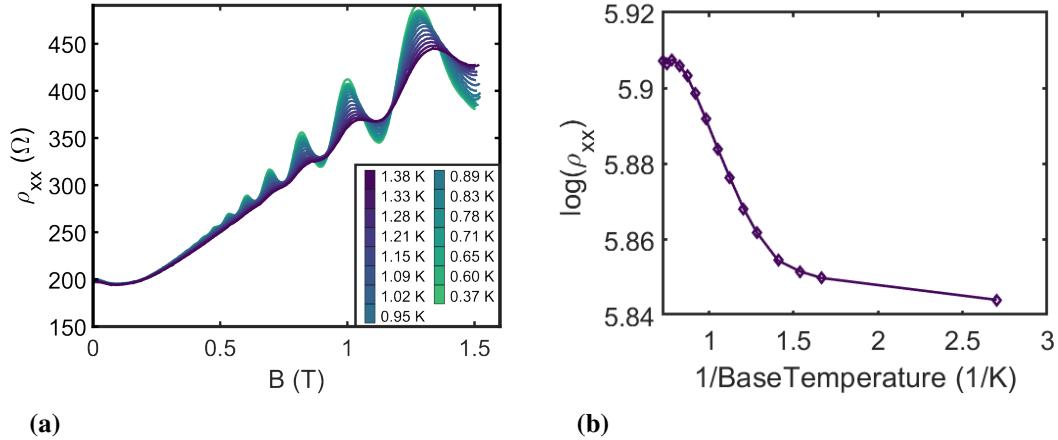

| A.1.3      | Base temperature $\neq$ electron temperature . . . . .                                 | 138        |

| <b>A.2</b> | <b>Appendix - ASD . . . . .</b>                                                        | <b>142</b> |

| A.2.1      | Reverse bias application . . . . .                                                     | 142        |

| A.2.2      | Back-action . . . . .                                                                  | 143        |

| <b>A.3</b> | <b>Appendix - Spin qubit device (Qubus) . . . . .</b>                                  | <b>144</b> |

| A.3.1      | Electron temperature . . . . .                                                         | 144        |

| A.3.2      | Lever arm $\alpha_{P1}$ determination . . . . .                                        | 150        |

| A.3.3      | Sweep direction . . . . .                                                              | 150        |

| A.3.4      | Spikes . . . . .                                                                       | 151        |

| A.3.5      | Pulsed gate spectroscopy . . . . .                                                     | 153        |

| A.3.6      | Digitizing . . . . .                                                                   | 154        |

| <b>A.4</b> | <b>Appendix - Charge noise power spectral density . . . . .</b>                        | <b>156</b> |

| A.4.1      | PSD measurements before installation of a DC cryostat filter . . . . .                 | 156        |

| A.4.2      | Complementary accumulation-mode device PSD measurement . . . . .                       | 157        |

|            | <b>Bibliography . . . . .</b>                                                          | <b>159</b> |

|            | <b>List of publications . . . . .</b>                                                  | <b>169</b> |

|            | <b>Acknowledgments . . . . .</b>                                                       | <b>171</b> |

## Contents

---

# 1

## Introduction

While the first quantum revolution, that resulted in indispensable electrical components such as a transistor or a LED, turned first quantum mechanical effects like the concept of an electron band structure to a noisy degree into a technology, the second quantum revolution is expected to make full use of quantum mechanical effects such as superposition or entanglement. Quantum computing is an example for an engine of this second quantum revolution and got greater attention for the first time, when mentioned about 40 years ago in a talk by Richard Feynman [1]. It took another 20 years until concrete concepts were developed, when for example in the year 2000 D. DiVincenzo, a quantum computation pioneer, formulated 5 criteria for a successful implementation of a quantum mechanical two-level system as a quantum processor [2]. A first simple algorithm of prime-factorizing the number  $N=15$  into the factors 3 and 5 was then demonstrated in a liquid NMR platform in 2001 [3]. While this platform turned out challenging for scaling of the quantum processor, such results paved the way for the further development of quantum algorithms and the search for new qubit platforms.

It soon became evident that in many realistic quantum bit (qubit) implementations, the quantum mechanical two-level system is very fragile and prone to dephasing and relaxation, induced by interaction with the environment. However, a minimum level of qubit coupling is always required for manipulating, coupling and readout of the quantum information. This consideration as an example makes it apparent that the development of quantum computing is not exclusively an engineering task, but ever deeper understanding of the underlying physics has always been required.

## 1 Introduction

---

Over recent years several physically completely different platforms emerged as serious candidates for the implementation of quantum computing. Such concepts comprise the quantum mechanical two-level implementation using superconductor circuits, a photon's degrees of freedom such as polarization, trapped ions or confined spins in semiconductors. Every platforms comes with specific advantages and drawbacks regarding the criteria for universal quantum computing.

At the time of the beginning of this PhD project, the state of research in quantum computation science across all these platforms was termed noisy intermediate-scale quantum (NISQ) era. The term designates that control of two level systems became as good that a new technology branch started to form and usage of a quantum mechanical two-level system for computation became accessible. In various promising qubit implementations, single qubit gates, the proof-of-principle for quantum computing, had been demonstrated and provided an opportunity to develop first quantum algorithms. Simultaneously with few working qubits in place, implementation and testing of error-correction schemes was pursued and gate fidelities were aspired to improve. But also scaling of the qubit systems to a size as large as necessary emerged as one of the most important tasks.

Right from the emergence of quantum computing, a single spin has been one of the most investigated platforms, as it provides a natural quantum mechanical two-level system and when for example confined within a semiconductor, this technology ansatz seemed to be compatible with the existing microelectronics industry and device fabrication techniques. Also the integration of both, a quantum processor as well as classical electronics on the same chip seemed auspicious. Within a semiconductor, the nuclear spin of a dedicated dopant atom can for example be used as the quantum mechanical two-level system, but also other implementations like an electrostatically confined electron or a hole are conceivable. Although the spin in such an implementation does not couple directly to electric fields, hyperfine interaction with the fluctuating surrounding nuclei of the host material turned out detrimental for the spin coherence time. Therefore, silicon soon started to be most-used material platform as it does provide only a small amount of nuclear spin carrying isotopes.

Especially gate-defined qubit devices based on a silicon/silicon-germanium quantum well heterostructure demonstrated tremendous progress recently. At the start of this PhD project, first two-qubit gates were performed [4]. Furthermore, single-electron spin coherence times of 20  $\mu$ s and single-qubit gate fidelities of 99.9% [5] were achieved. Notably, by isotopically purifying the silicon host material, the coherence time turned out to be limited by charge noise instead of hyperfine interaction. Moreover, initial efforts of turning the qubit from the fundamental research level into a technology were pursued. Concepts for this intention were first industrially fabricated qubit devices, operation of

---

qubits at elevated temperatures, automated tuning of qubit devices, gate-based qubit readout [6] or long-range coupling of qubits via spin-photon interaction [7].

While all these efforts are important steps for entering the next era of universal quantum computing, a deeper understanding of the underlying quantum physics and improvement of the experimental control of the qubit system is still required to potentially push forward quantum computing into a widespread technology.

Especial importance can be attributed to the readout of the spin qubit, as the sensor receives a pivotal role in the examination and development of new aspects in the dynamically advancing field of quantum computing with single spins. A high fidelity spin qubit readout will be crucial for successful realization of upcoming tasks like intermediate-scale coupling of spin qubits or the strive to improve coherence and relaxation times to just name a few. Simultaneously, a strategy for the qubit readout has to be developed when the number of coupled qubits on a single chip will scale in the near term. As a third aspect, the sensor receives a leading role as part of a spin qubit device as under the background that the qubit coherence turns out to be limited by charge noise instead of hyperfine interaction, the sensor of a qubit device also provides a straightforward mean to measure the charge noise via spectroscopy of the sensor signal.

In this thesis we therefore focus on the sensor as one of the most important architecture components of a spin qubit device with the aim of developing a deeper physical understanding regarding its functionality and some of the above mentioned aspects. The thesis is organized as follows:

1. **Chapters 2 and 3** provide an overview of the different qubit platforms, before the here-used silicon quantum well heterostructure is introduced and a concept of electron accumulation and confinement in the quantum well is presented. Also, the basics of the qubit operation, such as the sensor dot formation, charge sensing of the qubit occupation or single-shot spin readout via spin-dependent tunneling are discussed. Moreover, technical aspects like the heterostructure growth, the difference between the accumulation- and the depletion-architecture gate design, an overview of the cryostats, the electrical wiring or the characterization of the noise in the empty setup are presented.

2. **Chapter 4** presents magnetospectroscopy measurements of Hall bar devices, with a focus on the stability of the accumulated electrons, gate hysteresis and the experimental control of the accumulation turn on voltage. The chapter also discusses an established model of interface trap states that limit the charge stability.

3. **Chapter 5** introduces a new operation principle and a new gate design for a sensor dot, capable of increasing the sensor output response for a single-shot spin qubit readout via spin-to-charge-conversion by an order of magnitude. The concept is

## 1 Introduction

---

based on an asymmetric design of the capacitances between sensor dot and Ohmic contacts. The increased sensor signal significantly reduces the demands on the first ensuing amplification stage which may either be located on the same processor chip or at least at cryostat temperature in close proximity to the device.

4. **Chapter 6** addresses challenges for the tuning and the spin readout fidelity of an accumulation-type spin qubit device that uses a sensor quantum dot or a 1D-like channel with a partially discrete electron density of states (DOS) for an electron reservoir. We especially aim to compare the single-shot fidelity of the spin readout via spin-dependent tunneling to results measured earlier on a depletion-architecture spin qubit device that featured a 2D-electron gas with a continuous DOS as reservoir.

5. **Chapter 7** presents a study of charge noise power spectral densities in dependence of the accumulation voltage, measured in our accumulation-type sensor dot, against the background of charge noise limiting the qubit dephasing in current isotopically purified devices. We also use the noise analysis as a tool to characterize a new dilution cryostat setup that was installed with all related measurement equipment as part of this PhD project.

6. **Appendix:** Completes the preceding chapters 4-7 and provides additional information regarding the presented measurements.

# 2

## Concepts

Currently, the efforts of implementing quantum computation have entered the noisy intermediate-scale quantum (NISQ) era. For the realization of the ensuing era of universal quantum computing however, millions of at least partially entangled qubits may be required. Currently, many different physical platforms for the implementation of quantum mechanical two-level systems exist. Of these approaches, each comes with certain advantages and drawbacks regarding the challenges of scalability, gate fidelity or the required technical overhead to just name a few.

### 2.1 Experimental platforms for quantum computers

This section provides an overview of 5 promising quantum computing platforms, which will all briefly be introduced. We focus on the most advanced and the chronologically first qubit systems here. This section does not have the intention of all-embracingly covering the whole research field, which is still vastly growing and there are many different approaches. Some concepts like NMR, CV centers or graphene based systems will not be discussed throughout the following section. The following section is inspired by the review article [8], but features many concepts that have developed over the past 14 years since the review article was published. Also ideas of the reviews [9, 10] are picked up.

### Superconductors

The maybe most well-known approach, also outside the university research community, is encoding a quantum bit in a superconducting electrical circuit. This implementation of a qubit processor also demonstrates currently the largest number of qubits and is very present as not only universities and other research organizations but big IT service providers launched own quantum computing programs following this strategy. Starting in 2017 IBM made the usage of quantum computing accessible for everyone to use, first limited to simple algorithms on their 7-qubit quantum processors [11], but recently increased the processor to 127 qubits [12, 13]. Also Google demonstrated first quantum supremacy in 2019 [14, 15] on a chip featuring 53 working qubits and subsequently demonstrated error correction on 49 qubits in 2023 [16, 17].

The recent progress of superconducting qubits is well described in the two reviews [18, 19], on which this short summary here is based.

The simplest description of such a superconducting LC circuit seems obvious: The two levels required for the computation may be defined when the excitation energy is either stored within the capacitor or in the inductance and the potential is described by the quantum harmonic oscillator [8, 19]. To address individual states of the system however, some anharmonicity is required in order to distinguish the resulting harmonic states. This anharmonicity typically is introduced via the integration of a Josephson junction into the circuit [8, 19]. In combination with the Josephson junction different flavors of the superconducting loop have been demonstrated, each flavor engineering the potential in a different way. The most common approach, which is also pursued by Google and IBM, are transmon superconducting qubits [20]. Other implementations are termed flux or phase qubits [18].

The single and two qubit gate durations are as fast as a few tens of nanoseconds [17] and demonstrate high gate fidelity, exceeding 99% [21]. The coherence times of such qubits are significantly longer than the gate operation times. A pure dephasing constant  $T_2 = 127 \mu\text{s}$  [13] has been reported as well as a relaxation time of  $T_1 = 288 \mu\text{s}$  [13].

### Photons

Photons have also been demonstrated to serve as a possible qubit candidate and will be introduced in the following. The explanation of photon based quantum computing here was mainly adapted from [22], [23] and the notes in [24].

There are different physical degrees of freedom to encode the qubit. Using the polarization of a photon as quantum mechanical two-level system allows for very simple single-qubit gate implementations using a birefringent waveplate [22]. Information encoding in the photon trajectory following the transition through a beamsplitter or exploiting the orbital

angular momentum are also possible implementations [25].

The availability of two-qubit interactions became possible by the Knill-Laflamme-Milburn (KLM-) scheme [26]. The authors marked also the field of a conceptually totally different approach towards quantum computation: The emergence of so-called "measurement-based" quantum computation.

Applied to photonic quantum computing this measurement-based concept enables two-qubit gates using only linear optical elements, like beam splitters and phase shifters, as well as single photon sources and detectors [26]. The approach by Knill et al. relies on the Gottesman-Chuang quantum teleportation concept and entangling with ancilla photons. A good explanation can be found for example in [22] and in [23]. Using the KLM-scheme, two-qubit gate fidelities as large as 99.69% and single-qubit gates of 99.84% were demonstrated recently in [27]. Incorporating the KLM-scheme, also 18 qubits using 3 degrees of freedom from 6 entangled photons were presented in [25].

Around the same time the KLM scheme emerged, also a second measurement-based concept was introduced, which is called the "one-way" measurement-based quantum computing ansatz [28]. This concept relies on a grid of with-each-other entangled photons as resource state, often called graph or in some special cases cluster state. The concept is well described in [29] and in [23] and was first experimentally demonstrated in [30].

### Trapped Ions

The maybe lowest error rate when performing qubit gates is demonstrated on a third quantum computing platform employing trapped ions [31, 32]. Ions can be trapped and cooled in so-called Pauli traps using laser cooling and are typically arranged in a linear array. The ground state and an intrinsically stable exited state of the ions serve as two-level systems. Coupling of neighboring ions and lifting the degeneracy in resonance frequency is achieved by inducing a laser-controlled common and quantized motion of the string of ions [33]. Quantum algorithms have been demonstrated with up to 50 coupled qubits. Very long coherence times up to minutes [33] and large gate fidelities, exceeding 99.9% for two qubit gates and 99.99% for single qubit gates are reported at gate durations faster than 100  $\mu$ s [33–35].

However, scaling seems technically demanding, as the technical overhead required for scaling to millions of qubits remains challenging at the moment. A good review for the current state of quantum computing using trapped ions can be found in [36]. Ideas for this short summary are adapted from [8] and the reviews [33, 35].

### Topological quantum computer

Even higher fidelity and lower decoherence is predicted for topologically protected qubits. With Microsoft, also a big IT service provider pursues this ansatz [37].

In the original proposal, Kitaev suggested the usage of anyons for quantum computing [38]. To understand the concept of anyons, we look at the common wave function of two indistinguishable particles. Exchanging indistinguishable particles results in either the same wave function (1, boson) or in a wave function with negative sign (-1, fermion), because exchanging twice has to restore the original wave function:  $(-1)^2 = (1)^2 = 1$ . Non-abelian quasiparticles like anyons behave differently. Their wave function contains a history upon two-fold exchange as not the identical wave function is restored, but a certain phase factor is picked up. This is why often the term braiding is used in this context [39]. Possible candidates for the realization of these quasiparticles are predicted to emerge in the 2-dimensional fractional quantum Hall effect [40, 41] but also for the majorana zero mode at the nanowire-semiconductor to superconductor interface [42].

First experimental hints for the existence were reported in 2012 [43]. But the research field suffered a big drawback when multiple promising articles for the experimental proof of majorana fermions from the year of 2017/2018 [44, 45] had to be retracted 4 years later [46, 47]. Up to date, no experimental proof of non-abelian quasiparticles has been reported.

A short introduction to topological quantum computing, can be found in the reviews [48, 49], which served as a basis for this short overview.

### Spin in semiconductor

As the last platform here, we introduce quantum computing using a spin confined in a semiconductor host material. This is the approach we pursue in our research group and also within this thesis at hand.

Using spins for quantum computation was postulated by Loss and di Vincenzo in the pioneering paper [50] as well as by Kane in [51]. Both articles envisioned technically different access and confinement of the electron spin.

Advantages of this platform are on the one hand the compatibility with existing microelectronic industry, both in fabrication as well as considering the integration with current classical computer hardware. Both aspects are promising for an eventual scaling to millions of qubits. On the other hand, the spin is a priori insensitive to electric fields, providing protection of the qubit information, while the charge of an electron or hole can be controlled by electric fields for example for qubit initialization and readout [10]. With Intel, again a big microelectronics company supports this ansatz, and high device yield and state-of-the-art relaxation and dephasing constants have been published on

industrially fabricated devices [52].

For the spin confinement in the semiconductor host, there are different realization [53–55]: A single electron or hole can be confined electrostatically inside a semiconductor quantum dot as envisioned by Loss and DiVincenzo. Also the confinement of multiple adjacent spins is possible and the overlapping shared wave function may be used for the qubit encoding in the resulting singlet triplet basis. Depending on the number of sites and spins even more complex realizations are conceivable [10].

A second parallel ansatz is to incorporate a single donor atom like phosphor inside a silicon semiconductor as proposed by Kane. Both the phosphorus nuclear spin 1/2 as well as the excess electron can be used for encoding the qubit information.

Depending on the type of qubit encoding, the approaches for initialization, manipulation, readout and interaction with other qubits differ [9] and some basic properties and recent advances are displayed in the next section. Currently, devices featuring up to 6 qubits were demonstrated. Also, single and two qubit gates with fidelities exceeding the error correction threshold as well as  $T_2^*$  times of microseconds and seconds long  $T_1$  times have been reported recently [10]. As this platform will be employed in the remainder of this thesis, the next section will present more details regarding latest efforts in this research field.

### 2.1.1 State-of-the-art of spin qubits in semiconductors

#### Single electron spin qubit in gate-defined quantum dots

A big advantage of using a single confined electron spin inside a quantum dot for quantum computing is the promising scalability prospect. Soon, first working qubit devices in doped GaAs quantum well heterostructures were reported. In this material system, the effective electron mass is comparatively low  $m^* \simeq 0.07 \cdot m_e$ . Hence the fabrication of metallic feature sizes of 100 nm sufficed to electrostatically define potential minima in the quantum well. By metallic gates and applied gate voltages the electron number stored in these quantum dots as well as tunnel barriers to electron reservoirs or between neighboring quantum dots could be controlled. Using the singlet-triplet basis of two entangled neighboring electron spins as a two-level system, first electrically controlled Rabi oscillations were demonstrated [56], which however were limited by short dephasing times of only  $T_2^* \leq 10$  ns. Hyperfine interaction with GaAs host nuclei caused the fast dephasing of the quantum state. Recently, the dephasing time in this material system has been improved by pulsing techniques but remains still comparatively short with reported dephasing times of  $T_2^* \leq 100$  ns [57].

Soon, the focus turned to silicon which naturally features only 5%  $^{29}\text{Si}$  isotopes. The

## 2 Concepts

---

remaining  $^{28}\text{Si}$  and  $^{30}\text{Si}$  isotopes do not possess a total nuclear spin and hence do not cause dephasing of the electron spin via hyperfine interaction. Also further isotopical purification as low as only 60 parts per million (ppm) remaining  $^{29}\text{Si}$  is technically possible for the silicon base material [58, 59]. Two approaches using silicon as host material emerged. In the first ansatz, the electron spin is confined in a silicon/silicon-germanium quantum well heterostructure, in the second ansatz, a quantum dot is formed at the silicon to oxide interface (CMOS) interface.

For both approaches, the qubit readout is performed by linking the spin information and the electron charge and spin-dependent tunneling constitutes the readout process. The linking can be implemented either by alignment of the Zeeman split spin states to the Fermi energy of an electron reservoir or using Pauli spin blockade in a double-dot system. Charge tunneling or the absence thereof is either detected via a sensor quantum dot, RF reflectrometry or gate dispersive readout. Spin manipulation of the qubit in turn can be implemented by applying a resonant microwave signal via a nano-stripline (Electron spin resonance, ESR) or artificial spin-orbit coupling in a magnetic field gradient (Electric dipole spin resonance, EDSR).

Long coherence times of  $T_2^* = 120 \mu\text{s}$  [60] have been reported. Both single [5, 60–62] and two-qubit gates [4, 63, 64] with fidelity beyond the threshold for fault tolerant operation [65–67] have been reported recently.

For scaling, which may be a promising advantage of this material platform, some concepts like the spider-web array [68] have been proposed, but the available cooling power as well as the electronics close to the qubit device remain under discussion.

### Hole spin qubit

Tremendous progress has been achieved in recent years by using the spin of holes. A big advantage holes in Ge/SiGe or CMOS structures have compared to electrons is their p-type wave function character, resulting in no overlap with the host nuclei, eliminating the contact hyperfine interaction. The large intrinsic spin-orbit coupling in germanium makes hole qubits susceptible to electric noise but also makes the use of magnetic field gradients redundant and allows for very fast gate operations. Single hole confinement in CMOS structures is possible with coherence times of  $T_2^* = 1 \mu\text{s}$ , lower than for electron spins [69]. In that material system single qubit gates with fidelities >99.9% were demonstrated. Also two-qubit gates on a device with up to 4 qubits have been demonstrated recently [70] [71] [64].

### **Donor spin qubit**

As a last semiconductor platform for potential quantum computation using spins we want to introduce single dopant atoms in a semiconductor environment. The fundamental proposal by Kane in 1998 [51] used the nuclear spin of a single dopant atom and qubit coupling was proposed via the excess electron and hyperfine interaction with the nucleus. Here, we mainly focus on phosphorus in silicon, following the two reviews [9, 10].

Nowadays, both the electron and the nuclear spin are used individually as quantum mechanical two-level systems. Decoherence times of 270  $\mu$ s for the electron spin [72] and  $T_2^*$  of 840  $\mu$ s for the neutral and 3.3 ms for the ionized dopant nucleus [73] at single-qubit gate fidelities exceeding 99.9% [72] have been reported. Just like the quantum dot spin qubits, the readout of such qubits is performed via spin-to-charge conversion using a sensor dot in the vicinity of the qubit dot [9]. A challenge for this platform is scaling and the implementation of two-dopant interaction as the donor placement so far typically is performed by implantation or STM placement [10]. Last year two-qubit gates using two donor dopant atoms with fidelities exceeding 99% were demonstrated [74].

## **2.2 Gate-defined quantum dots in a silicon quantum well heterostructure**

In this section we introduce all concepts leading to the confinement of a single spin inside the quantum well of a semiconductor heterostructure. We highlight some of the advantageous properties by using silicon compared to different semiconductor materials, and outline briefly the basics of characterizing a 2-dimensional electron gas (2DEG) in the quantum well by magnetotransport measurements. Subsequently, we discuss the physical properties leading to the formation of quantum dots in the quantum well and analyze the resulting consequences for the energy levels of a confined spin. A more detailed introduction, also comprising other spin-qubit related fundamentals like the spin manipulation, is given in my Master's thesis [75].

### **2.2.1 Formation of a 2DEG in a quantum well by heterostructure engineering and electrostatic band bending**

Using silicon as a host material for gate-defined quantum dots provides many advantages compared to other semiconductor materials. Foremost, existing microelectronics technologies are promising for industrial large scale of quantum processors. Also, the

## 2 Concepts

integration with classical technologies on the same chip seems possible this way. In contrast to for example GaAs, only 4.7% of the naturally occurring silicon isotopes carry a nuclear spin. These  $^{29}\text{Si}$  isotopes can further be isotopically purified, leading to substrate materials with a remaining  $^{29}\text{Si}$  concentration as low as 60 ppm, limiting the hyperfine interaction with the host material to only  $\mathcal{O}(10)$  non-zero nuclear spins [59]. Moreover, the low spin-orbit coupling in silicon also turns out beneficial for long coherence times. For our qubit devices we will confine a single electron spin inside the quantum well of a Si/SiGe heterostructure, which will be introduced in the following.

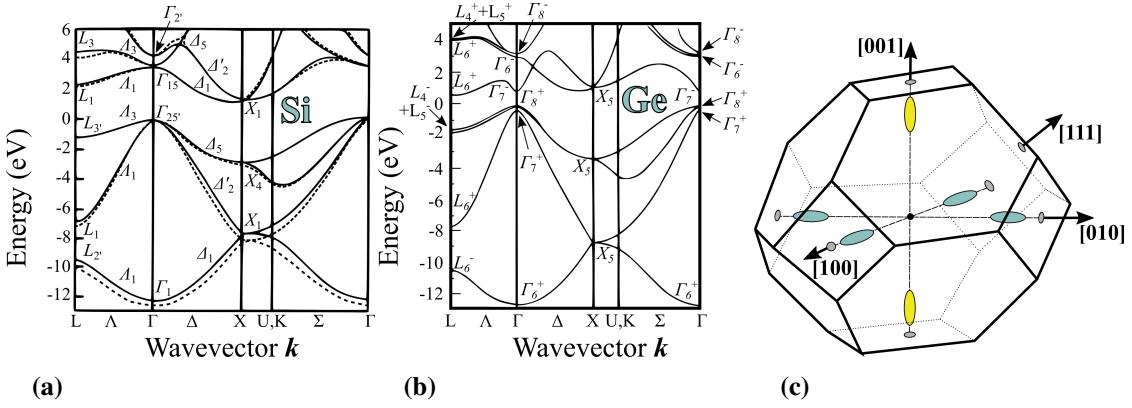

With lattice constant of  $a_{\text{Si}} = 5.331 \text{ \AA}$  and  $a_{\text{Ge}} = 5.657 \text{ \AA}$  [76], silicon and germanium are arbitrarily mixable in an alloy [77]. Figure 2.1a shows the band structure of silicon and Figure 2.1b the band structure of germanium [79]. The band gap of silicon is 1.11 eV. The band structure has a valence band maximum at the  $\Gamma$  point and a six-fold degenerate conduction band minimum along the [100] direction between the  $\Gamma$  and X point, as shown in Figure 2.1c. For germanium, the band gap is significantly smaller with only 0.66 eV. The valence band maximum is also at the  $\Gamma$ -point, the conduction band minimum at L-point.

**Figure 2.1: Silicon and germanium as spin qubit host materials.** (a),(b) Band structures of silicon and germanium. Diagrams taken from [78]. (c) Illustration of the conduction band minima in a Si and Si/Ge alloy with silicon concentration  $\geq 15\%$  along the  $\Gamma$  to X-point ([100]-direction). Figure adapted from [79].

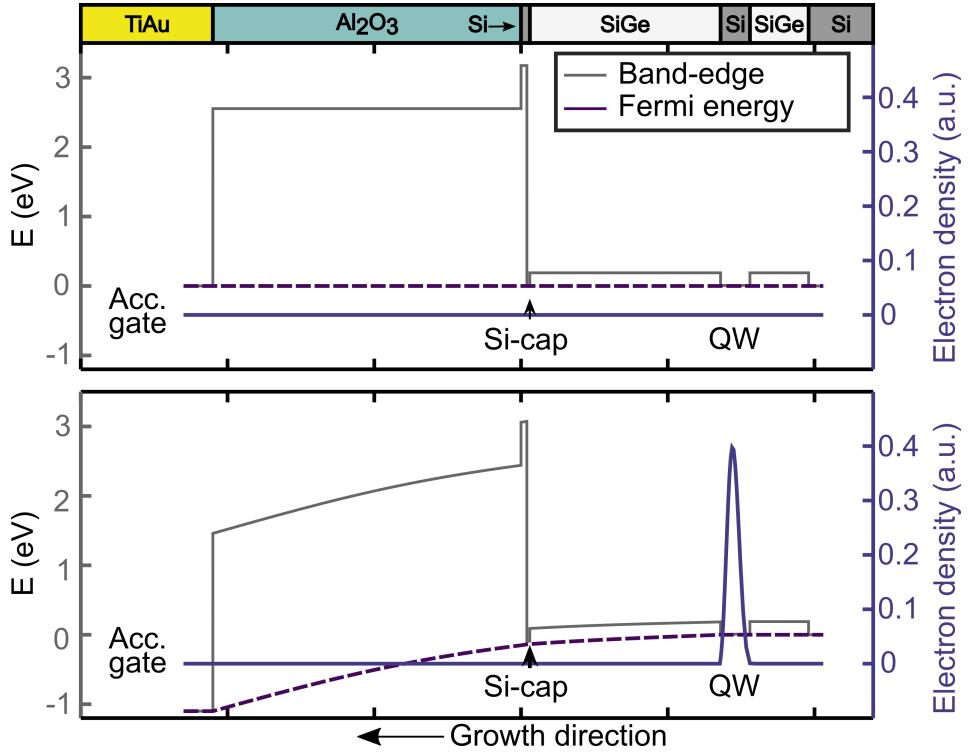

We utilize the miscibility of both elements to engineer a heterostructure, that features an around 10 nm thin layer of silicon between two  $\text{Si}_x\text{Ge}_{1-x}$  barriers. In our samples, the heterostructure is grown on a silicon substrate and the structure is capped by 1 nm of silicon, to prevent oxidation of the SiGe barrier. A typical cross section as well as the energy of the conduction band minimum along the growth direction is shown in the upper

## 2.2 Gate-defined quantum dots in a silicon quantum well heterostructure

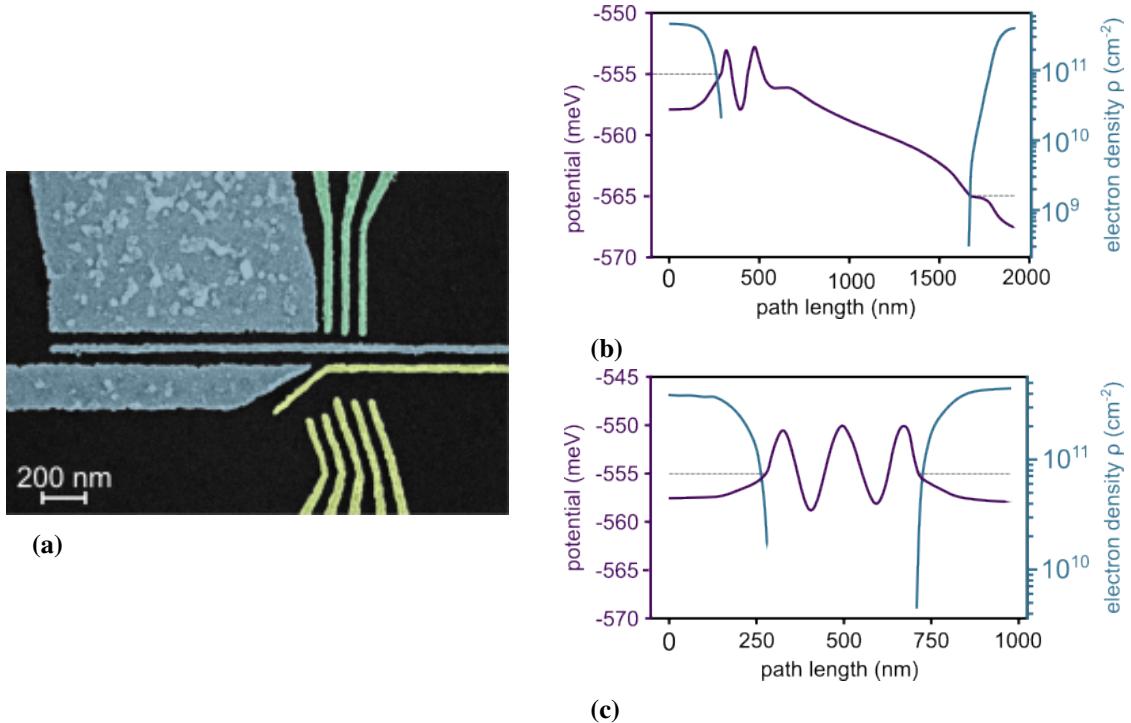

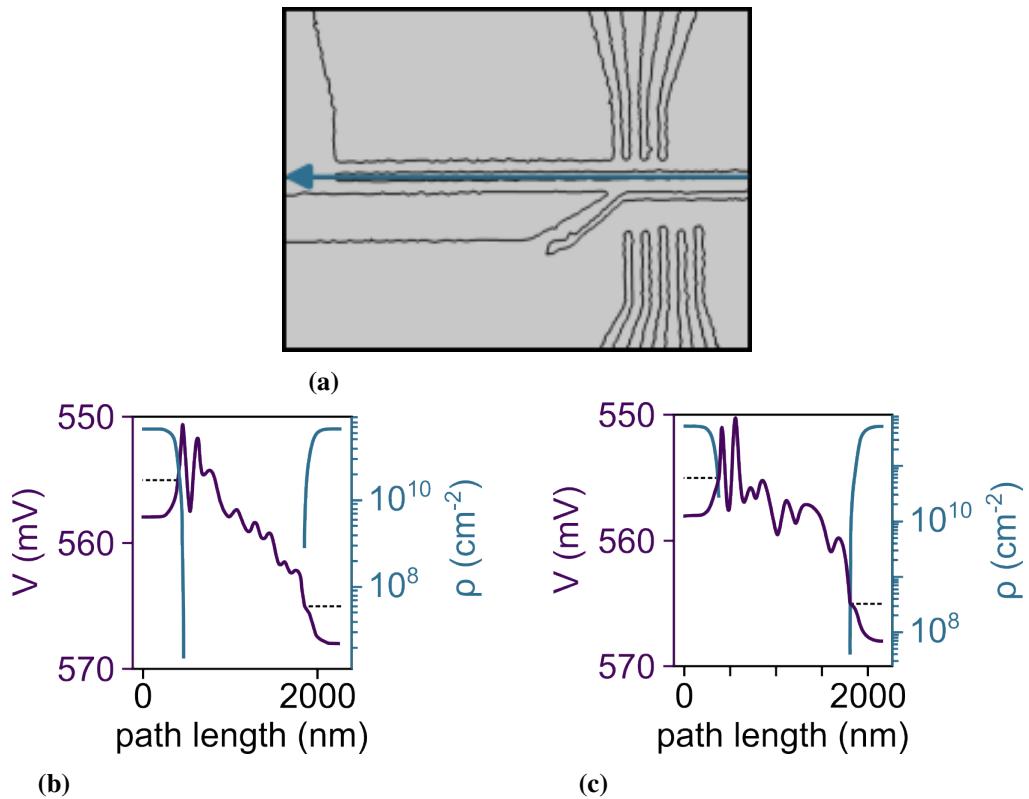

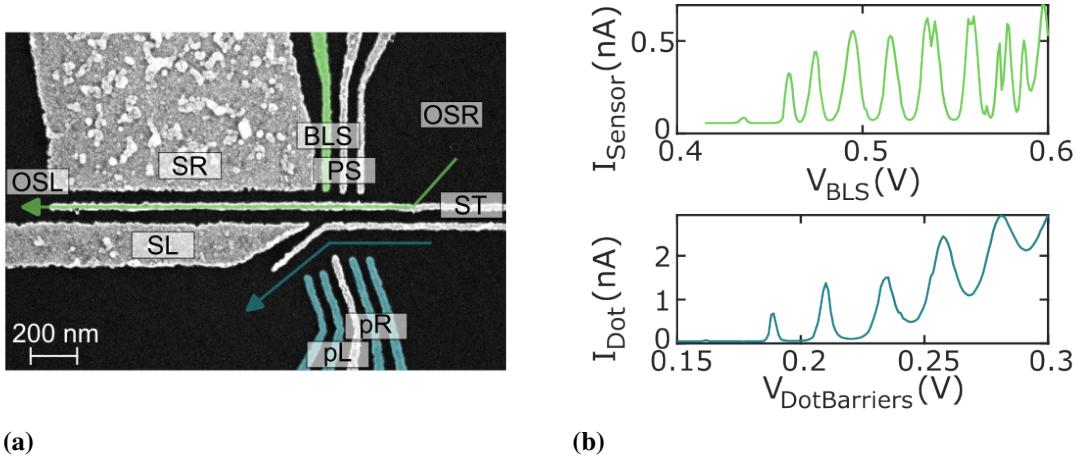

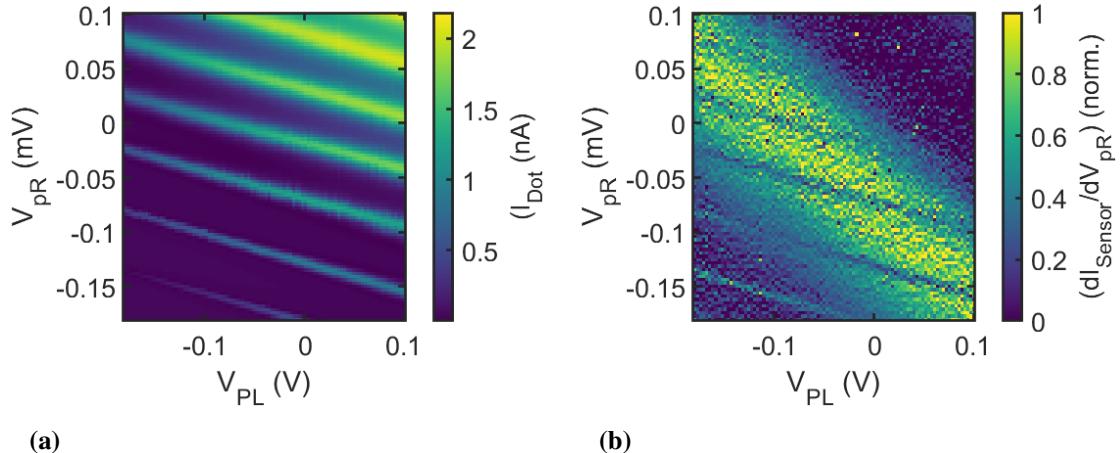

**Figure 2.2: SiGe heterostructure.** Simulation from Floyd Schauer [80]. The simulation shows the potential energy of the conduction band-edge minimum as grey curve, the Fermi energy of the system as dashed purple line and the electron density as blue curve. The heterostructure stack also includes a thick oxide and metal gate layer. The upper panel of the simulation shows the energies without application of a voltage to the TiAu accumulation gate. The lower panel illustrates the configuration for a positive voltage applied to the gate. By applying the gate voltage, the conduction band edge is bent energetically below the Fermi energy resulting in a finite electron density inside the quantum well.

panel of the simulation in Figure 2.2, which was performed by Floyd Schauer [81]. Note, that for the quantum well, the conduction band forms a potential minimum in energy, although silicon intrinsically has a larger band gap. However, as the quantum well is only a thin silicon layer of a few atoms in height, its lattice constant adapts to that of the SiGe barrier, lowering the silicon band gap by the induced strain and resulting in a staggered type II band alignment [77]. Also note, that due to the strain, the sixfold degeneracy of the conduction band minimum is lifted, resulting in an energetic reduction of the 2 valleys along the growth direction [82], which was already indicated by the false

color in Figure 2.1c.

The simulation shows, that the conduction band intrinsically is not populated by electrons, as the Fermi energy lies inside the band gap. To accumulate electrons there are mainly two approaches: On the one hand, a doping layer can be integrated into the heterostructure gate stack of which donor atoms provide electrons to the quantum well. This approach has worked well but has the drawback that ionized donor atoms remain, which lead to scattering of electrons during transport through the quantum well or equivalently can enhance qubit device instability. On the other hand, electrons can be accumulated electrostatically inside the quantum well by a positive electric field provided by a gate electrode. The process is well described in [83] and also in my Master's thesis [75]. Here, only a brief discussion on the consequences of applying a positive electric field to the heterostructure will be given.

We add a metallic gate, isolated by an oxide layer, on top of the heterostructure in Figure 2.2. By applying a positive voltage to this gate, the Fermi energy and the conduction band minimum are bent and lowered electrostatically, as shown in the lower panel of the simulation in Figure 2.2. The band bending results in the band edge being pulled below the Fermi energy inside the silicon quantum well. Consequently, an electron charge density forms in the quantum well. Both simulations in the figure were performed by Floyd Schauer [81]. The situation can be compared in a simplified model to a plate capacitor with the metallic gate on top of the heterostructure stack and the quantum well of the structure being the two corresponding plates.

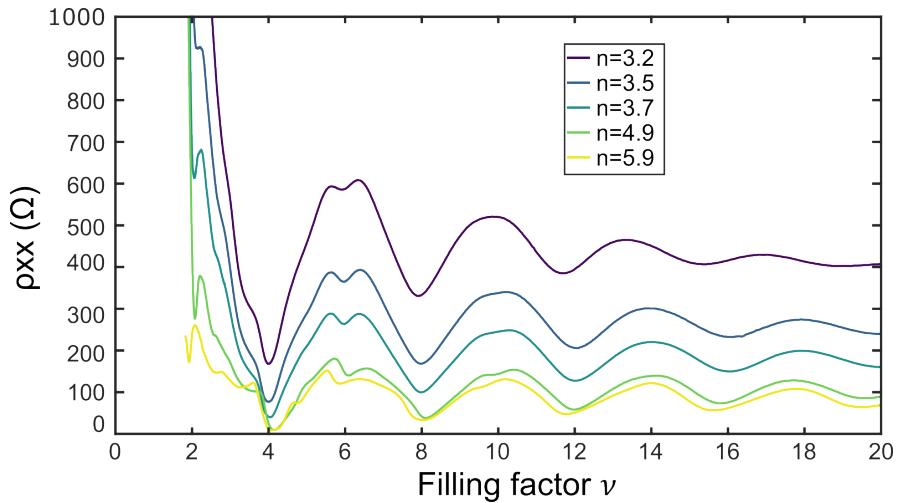

### 2.2.2 Heterostructure analysis by magnetotransport

By band bending electrons can be accumulated in the quantum well and the density of this 2DEG is controlled by the applied gate voltage. By performing transport measurements in a magnetic field and a four-point measurement geometry, we are able to deduce the electron density as well as the mobility of the charge carriers. The following derivations are well described and adapted from the textbooks [83] and [77].

In a low magnetic fields (typically  $< 1$  T) transport is described by the Drude model: The model provides a relation of conductivity, charge carrier density and mobility. By application of a magnetic field, the conductivity tensor obtains a non-zero component perpendicular to the applied current and magnetic field (Hall effect). The relations for the resistivity tensor, the inverted conductivity, are

$$\rho_{xx} = \frac{m^*}{n \cdot e^2 \cdot \mu} \quad (2.1)$$

$$\rho_{xy} = \frac{B}{n \cdot e} \quad (2.2)$$

in which the mobility is defined as  $\mu = \frac{e\tau}{m^*}$ ,  $e$  is the elementary charge, here neglecting the sign for simplicity,  $m^*$  the effective mass and  $n$  the charge carrier density. By measuring both resistivities in a 4-point geometry we can experimentally access both 2DEG characterizing quantities  $n$  and  $\mu$ .

From the spatial confinement along the growth direction ( $z$ ), the electron dispersion is quantized and forms a series of sub-bands with free in-plane motion ( $x, y$ ). Increasing the magnetic field, Landau level quantization steps in: By increasing the perpendicular magnetic field along  $z$ , the states will condense in Landau levels with energy  $\hbar\omega_c(n + \frac{1}{2})$ , independent of the in-plane momentum  $k_x, k_y$ .

We also introduce the filling factor

$$\nu = \frac{h}{e} \cdot \frac{n_{2DEG}}{B} \quad (2.3)$$

counting how many Landau levels are occupied. With increasing magnetic field, the density of states per Landau level increases and hence the filling factor decreases. In this regime, the quantum Hall effect describes the course of the resistivity in a transport measurement and plateaus with  $\sigma_{xx} = 0$  and consequently  $\rho_{xx} = 0$  form for the longitudinal resistance, while the transversal resistance  $\rho_{xy} = \frac{1}{p} \frac{h}{e^2}$  is quantized by integer  $p$ , whenever a Landau level is completely filled. We will measure such quantum Hall effect features in this thesis and also calculate the filling factor  $\nu$ .

While for transport through the 2DEG in the silicon quantum well in the Hall bar a single metallic gate sufficed for accumulating a global electron density, we now aim for isolating single electrons in quantum dots to form our spin qubit. This requires local electron density control and new concepts for a 0-dimensional electron system apply. In the next section we introduce the basic physical principles resulting from such a 0-D confinement of an electron and introduce important concepts for operating a qubit device.

## 2.3 Single-electron physics in Si/SiGe

We now try to modulate the continuous charge carrier density inside the quantum well with the aim of forming a potential minimum for locally trapping electrons. This potential minimum we call quantum dot. In the following description, we do not go into technical or fabrication details about this confinement, but rather highlight the consequences and

how isolated electron spins can be used in a qubit device. All tuning in the following is performed electrostatically by gate voltages. This allows us to form electron reservoirs and tunnel barriers for loading and unloading the quantum dot. More details are provided in section 3.1.3. Here, we focus on the resulting physics when confining electrons in a quantum dot.

### 2.3.1 Coulomb blockade: Single energy states according to electron occupation

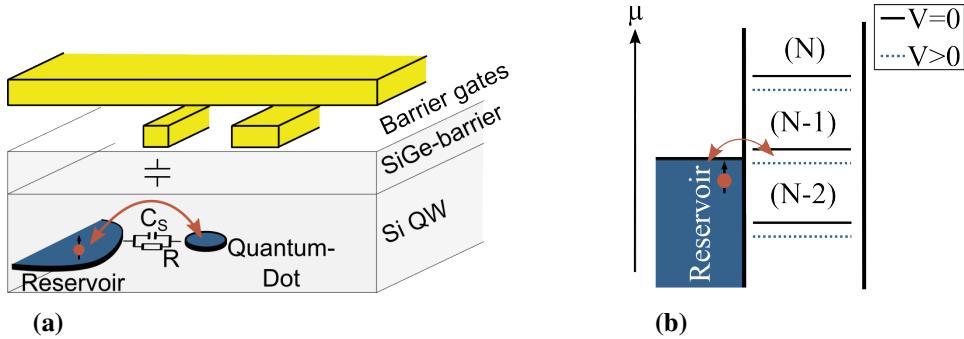

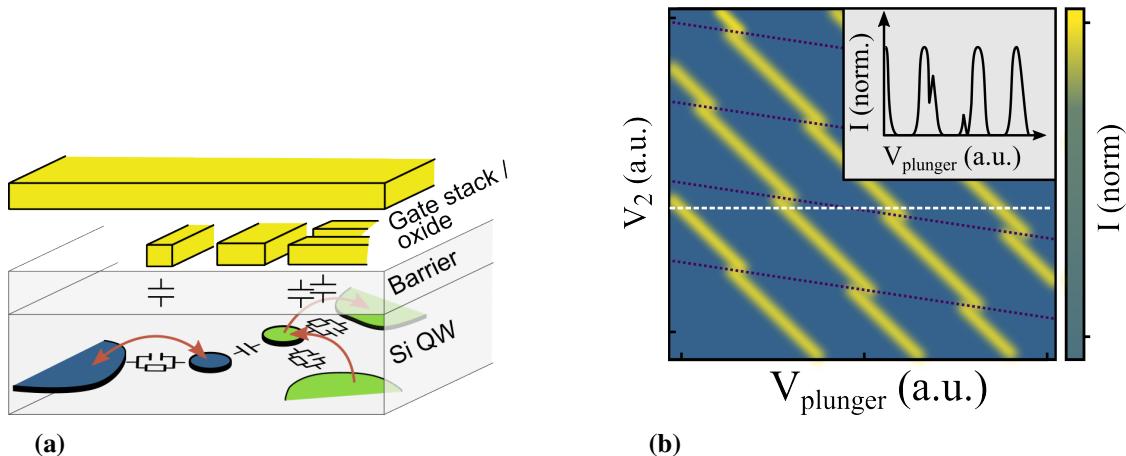

Figure 2.3a shows a very simplified approach towards this goal by introducing a global topgate (TG) and two additional, smaller gates underneath. These two gates screen the positive electric field of the global TG and create a potential minimum in between. In the quantum well underneath accordingly an electron island forms. To the left of the island an electron reservoir is formed where the global accumulation gate is not screened. The island, which we call quantum dot, is tunnel coupled to the reservoir and electron exchange can take place, as indicated by the red arrow. The tunnel barrier is sketched by the equivalent RC connection, which size and tunnel rate may be controlled by the above lying local gate. Therefore we call this gate a barrier-forming gate or just barrier gate, in contrast to the TG.

**Figure 2.3: Electrostatic formation of a quantum dot.** (a) Sketch of the heterostructure and a simplified two-layer metal gate stack. (b) Discrete energy levels of the quantum dot depending on the amount of quantized electron charges stored on the quantum dot.

The resulting energy can be described in a simplified form with a semi-classical ansatz, in which the electrostatic energy of the electron island depends on both, the number of electrons stored on the island as well as the resulting gate voltages, in our sketch mainly the gate voltage of the above lying global TG. As the electron charge is of course

quantized, single energy levels depending on the number of electrons form, as illustrated in Figure 2.3b. The figure shows the chemical potential  $\mu$ , which increases by a discrete amount the more electrons are stored on the island. The potential can be capacitively controlled by the applied gate voltage  $V$ , lowering the potential when increasing the voltage. The charge on the island is in the so-called "Coulomb blockade", so it remains constant, unless the chemical potential of the next state is lower than the Fermi energy set by the electron reservoir. This concept allows also the storage of only a single electron charge on the island by corresponding gate voltage tuning.

### Transport through a quantum dot

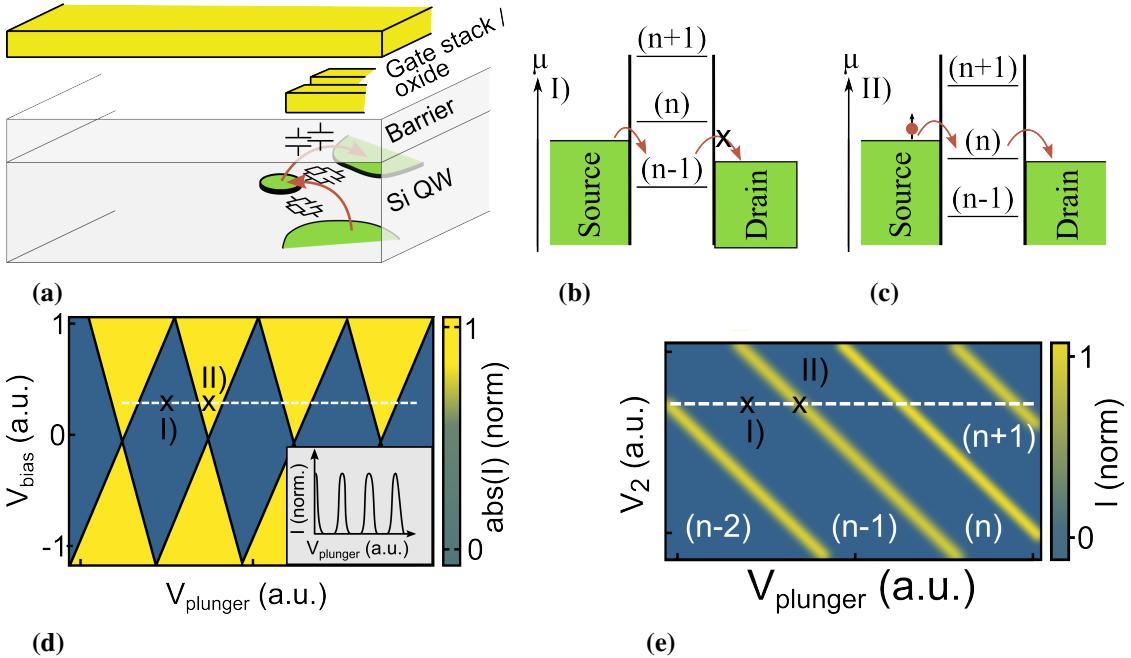

Transport through a single quantum dot is illustrated in Figure 2.4a, which resembles the device of Figure 2.3a, but this sketch shows two reservoirs which are tunnel coupled to a quantum dot in between. We term the reservoirs source and drain and apply a bias voltage to the drain reservoir, shown in the sketches in 2.4b and 2.4c. Due to the Coulomb blockade of the quantum dot, transport via sequential tunneling only sets in, when an energy level is energetically tuned right into the bias window. If no energy level is available, current is blocked. This configuration of a quantum dot coupled to two reservoirs is termed single electron transistor (SET).

A characteristic measurement for this SET is the so-called "Coulomb diamond" measurement, sketched in Figure 2.4d. The figure shows a simplified measurement of the current through this SET, varying the gate voltage (here  $V_{\text{plunger}}$ ) and the bias voltage  $V_{\text{bias}}$ . Only for non-zero bias voltage, the bias window between source and drain opens up and current is allowed, but also only when an energy level is available. The regions in which current is allowed are the yellow triangular shapes, the blockade configurations the blue diamonds. The larger the bias window becomes, the wider the regions, in which current is conducted, grow. Eventually, the bias window becomes as large as the separation of two consecutive energy levels, so no Coulomb blockade occurs any more. A cut through the measurement for a fixed bias voltage is shown in the inset in the bottom right corner, in which peaks in the transported current emerge. Note, that for each peak an additional electron is loaded onto the island.

Figure 2.4e also shows a current measurement of the SET for a constant bias voltage. In this measurement, two gate voltages are varied. Instead of peaks like in the inset before, this measurement shows diagonal lines whenever current through the SET is conducted. Each line corresponds to an energy level inside the bias window and accordingly the SET remains in constant occupation in between two lines, here indicated by the white numbers in brackets. The Coulomb peaks form diagonal lines because of gate cross-coupling of the two varied gates: Increasing one gate for example  $V_{\text{Plunger}}$ , the second gate  $V_2$  has to be decreased to keep the conducting dot level inside the bias window. Note, the

**Figure 2.4: Transport through a single quantum dot.** (a) Sketch of a quantum dot, tunnel coupled to two electron reservoirs. (b),(c) Energy diagram for Coulomb-blocked transport (b) and transport via sequential tunneling (c). (d) Coulomb diamond measurement. Current through the SET is blocked in the blue diamond-shaped configurations. The Inset shows a linecut through the measurement, in which single peaks emerge when current is conducted. (e) Charge stability diagram. Current is conducted for the configuration along the yellow diagonal lines. In between two consecutive lines, the electron occupation of the SET remains constant, indicated by the white numbers.

white horizontal dashed line equals the configuration of the white horizontal line in Figure 2.4d.

### 2.3.2 Readout of a spin qubit via charge sensing

We can use this SET as very sensitive electrometer to perform a charge state readout of a proximal qubit dot. The situation is sketched in Figure 2.5a. The figure shows a device featuring both, a SET on the right hand-side in green and a capacitively coupled quantum dot in blue, which is tunnel coupled to a third reservoir. The current through the SET as function of two voltages  $V_{\text{plunger}}$  and  $V_2$  is shown in

**Figure 2.5: Charge sensing.** (a) Sketch of a device featuring a SET (green) and a second quantum dot that is tunnel coupled to a reservoir (blue). (b) Charge stability diagram. The yellow diagonal transport lines of the SET are chopped by leaps in the gate voltage whenever the second quantum dot changes its electron occupation (dashed purple lines).

Figure 2.5b. Similar to Figure 2.4e, we observe lines along which current through the sensor SET is conducted (yellow diagonal lines) whenever an energy level is tuned into the SET bias window. In contrast to the previous figure, the yellow lines shown here now do have kinks following also parallel lines, indicated by the purple dashed lines. These purple dashed lines originate from the capacitively coupled second quantum dot: Whenever an electron tunnels onto the dot, the electrostatic potential for the SET is slightly lowered, resulting in a voltage jump within the measurement. A line-cut through the measurement along the white dashed line is shown in the upper right insert. In the insert, the voltage jumps emerge as kinks along the Coulomb peaks as a function the single gate voltage.

Via the detection of such kinks in the sensor current we gain insight on the electron occupation of the qubit dot. Crossing one of the purple dashed lines in the measurement is equal to a variation of the second quantum dot occupation by one electron.

Detection of the second dot occupation via this charge sensing is reasonable as soon as we lower its electron occupation down to a few or even a single electron, as in such a configuration direct transport measurements are no longer possible.

Note that also the charge sensing lines have a diagonal slope due to cross coupling of the varied gates. Depending on the geometrical location of sensor and qubit dot, the slopes of transport peaks and charge sensing lines may vary.

### 2.3.3 Spin qubit in a magnetic field

So far we introduced discrete energy levels of the quantum dot which arise due to an occupation of the quantum dot with a discrete charge carrier number. We derived the energy level structure from a semi-classical approach. In this section we now want to analyze the energy structure of a single electron occupation level, considering also quantum mechanical effects.

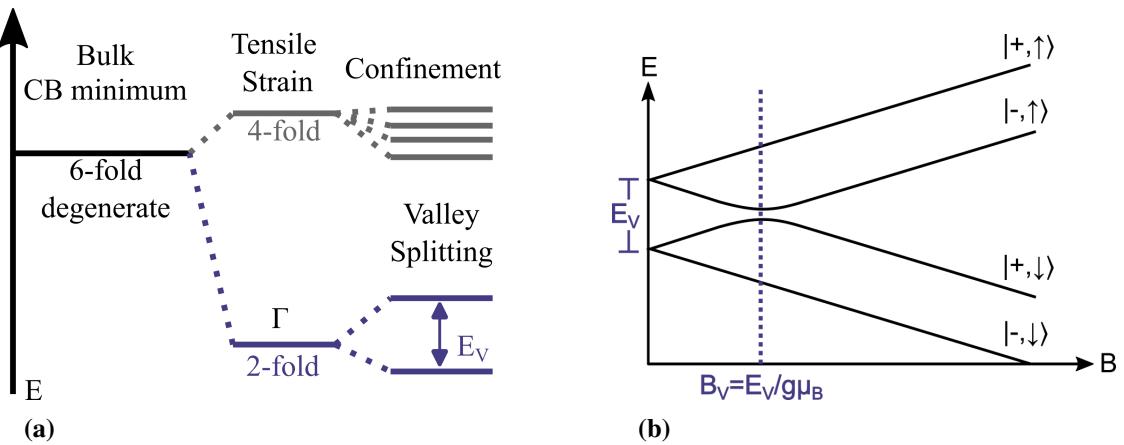

Like mentioned in Figure 2.1c, the sixfold conduction band minimum in silicon along the [100] direction in the Brillouinzone is lifted due to the strained growth of the silicon quantum well, leaving the two lowest-energy valley states along the growth direction lowered in energy. Moreover, the electron wave function is not centered inside the quantum well, but slightly pulled to the upper quantum well interface due to the band bending and the applied positive electric field. As a result, the remaining two-fold degeneracy of the valley states along the growth direction is also lifted. This lifting of the degeneracy is sketched in Figure 2.6a [82]. We denote the energy of the splitting of the lowest two valley states as valley splitting ( $E_V$ ).

**Figure 2.6: Energy states of a spin qubit in a magnetic field.** (a) Lifting of the degeneracy of the silicon conduction band minima. Figure adapted from [82]. (b) Valley and Zeeman splitting as a function of the external magnetic field.

Moreover, also the spin degeneracy is lifted by the application of an external magnetic field. We will use the resulting spin up and spin down states for implementing our two-level system intended for quantum computing. The energies of spin and valley states as a function of the applied magnetic field are shown in Figure 2.6b. The figure marks the crossing point at which the Zeeman splitting matches the valley splitting. Typical values for the valley splitting energies can range from only a few  $\mu\text{eV}$  to more than 200  $\mu\text{eV}$  [58].

Right at the crossing point, a spin up electron can energetically relax very quickly to a spin down electron, so this relaxation hotspot must be avoided in the operation of a qubit device. Typically, a large valley splitting is desired so that quantum computation can be performed at magnetic fields below the crossing point.

We emphasize, that in this description we focused on the ( $n=1$ ) state of the quantum dot. Adding a second quantum electron to the system, the additional electron cannot simply occupy the second lowest spin and valley state, but the charging energy to fill up the next charge-quantized state has to be overcome.

### Spin manipulation via coupling to the electron spin

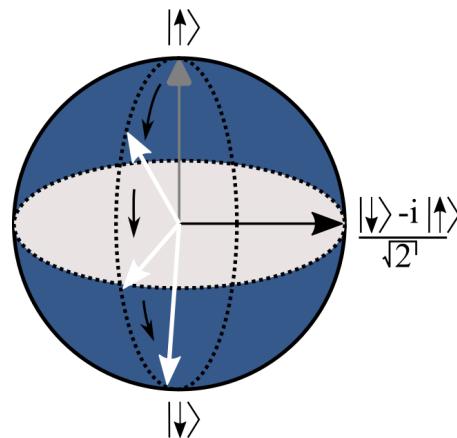

For our qubit implementation we are going to use the two lowest spin-split states of the qubit electron from Figure 2.6b. To visualize the driving of the electron spin, oftentimes the spin rotation is presented in the so-called Bloch sphere as illustrated in Figure 2.7. In this presentation, the surface of the sphere marks all pure spin states and the spin up state is illustrated at the north pole and the spin down state at the south pole. The Figure

**Figure 2.7: Bloch Sphere.** Visualization of Rabi oscillations.

here shows a potential driven rotation between the spin up state and the spin down state, a so-called Rabi oscillation. To drive such a qubit rotation, a coupling to the electron spin is required. As the spin does not directly couple to electric fields, there are different approaches. For systems with large spin orbit coupling (like GaAs or holes in Si), a resonant AC electric field applied to a plunger gate suffices to resonantly wiggle the electron wave function and via spin orbit coupling the electron resonantly sees a varying AC magnetic field modulation. In silicon this large spin-orbit coupling is not given, so we typically incorporate a small magnet into our metal-gate stack, which induces a magnetic

field gradient. Application of an AC electric field can drive electric dipole spin resonance (EDSR) by wiggling the electron wave function in the magnetic field gradient. A second approach is to incorporate a microwave stripline in the gate stack and to directly apply a resonant AC magnetic field next to the qubit dot.

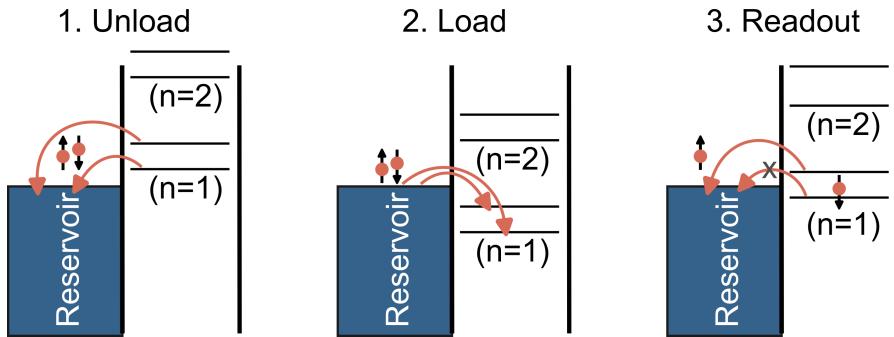

### Single-Shot spin readout

Readout of the qubit spin is challenging as the small magnetic moment of the spin cannot be detected directly. Therefore, we refer to a concept called spin-to-charge conversion [84, 85]: We link the spin orientation to the existence or absence of an electron tunneling event, which we can detect by our SET charge sensor. In our single dot system, we realize this conversion, by tuning the spin-split energy levels such that the lower-energy spin down state is tuned below the Fermi energy of the reservoir during the readout and the spin up state remains higher in energy. An illustration of a complete single-shot spin

**Figure 2.8: Single-shot spin readout.** The measurement sequence consists of three phases: First the qubit is unloaded and subsequently an electron of arbitrary spin orientation is loaded onto the quantum dot. During the readout, spin up and spin down orientation are distinguished as only the spin up electron can tunnel to the reservoir, while a spin down electron remains confined on the qubit dot.

readout measurement cycle is shown in Figure 2.8. The measurement sequence consists of three consecutive phases. In the first phase, the qubit dot is unloaded by pulsing both spin states of the  $(n=1)$  electron above the Fermi energy of the reservoir. In the second phase, both spin states are pulsed below the reservoir energy so that a single electron of arbitrary spin orientation can tunnel onto the qubit. During the readout process, a loaded spin up electron will tunnel out of the dot into the reservoir and eventually gets replaced by a spin down electron. Note, with this technique we can identify the spin orientation of a single electron once at a time. Hence we call this scheme a single-shot readout measurement.

**Qubit initialization and readout: The role of the reservoir**

The reservoir plays a decisive role for the qubit initialization and readout: So far we treated the reservoir as a perfect 2D reservoir with a continuous distribution of states and considered the initialization of an empty dot by 50% spin up and down orientation, respectively. Also the possibility of tunneling to the reservoir during the readout to discriminate spin up and down was considered without restriction, assuming a continuous density of both spin states in the reservoir. The situation however changes when a proximal SET is used as a reservoir and the qubit dot alignment to discrete energy states of the reservoir has to be considered. The role of the density of states within the reservoir will be discussed in the main text of this thesis in more detail.

**Readout of a two-dot system via Pauli spin blockade (PSB)**

The readout scheme may also be implemented differently for the operation of two tunnel coupled qubit dots, both occupied by a single electron. This readout protocol is for example described in the review [9]. Both electron wave functions will entangle, forming singlet and triplet states. When the electrostatic energy is tuned such that both electrons occupy the right quantum dot, the spin singlet  $S(0,2)$  state typically is lower in energy compared to the three triplet states  $T(0,2)$  as due to the Pauli exclusion principle some excitation, like the valley splitting energy, has to be overcome for the symmetric spin triplet states. By the application of a magnetic field, the  $T_+$  and the  $T_-$  triplet states are energetically split off and the neutral  $T_0$  and the singlet state  $S$  form an effective two-level system [56]. A three-phase single-shot spin readout could then be designed by tuning into the  $(0,1)$  state for unloading of the system, followed by random initialization by tuning into the  $(1,1)$  configuration. Tuning the system subsequently into the nominally  $(0,2)$  configuration constitutes the spin readout: Triplet states are blocked to tunnel from the  $(1,1)$  state into the  $(0,2)$  state, called Pauli spin blockade (PSB). The  $S(1,1)$  state however will tunnel into the  $S(0,2)$  state [86, 87].

## 2 Concepts

---

# 3

## Setup and measurement techniques

### 3.1 Fabrication

All measurements presented in this thesis have been performed in undoped silicon/silicon-germanium heterostructures featuring a strained and buried silicon quantum well in which electrons are accumulated in a 2DEG by electrostatically lowering the first accessible conduction band sub-band below the Fermi energy. All experiments are conducted at cryogenic temperatures below 2 Kelvin. Before presenting measurement results in the upcoming chapters, this chapter introduces the technical background of all experiments. First, the heterostructure growth and post-growth processing of the devices will be presented, before subsequently all three cryostat systems, in which the experiments were performed, are introduced. Finally, the focus is directed towards the measurement equipment and the electrical wiring inside our laboratory environment is presented.

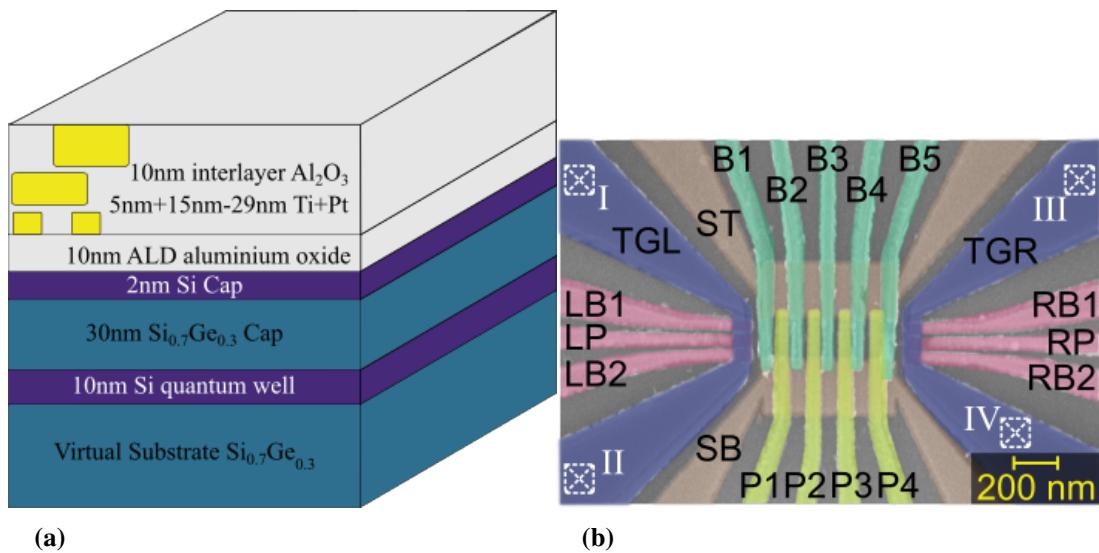

#### 3.1.1 Epitaxial growth of the heterostructure

The heterostructures of all our devices are grown via epitaxial growth: A monocrystalline growth of the semiconductor material under very low background pressure. Two different approaches for growing the material are common in the semiconductor industry and during both processes the alloy concentration of germanium and silicon can be controlled and layers as thin as a single monolayer of the semiconductor can be grown onto the substrate. For the fast industrial chemical vapor deposition (CVD) the semiconductor material comes as a compound with a volatile bond. The deposition is conducted in a vacuum chamber in which the volatile bond diffuses when the compound adsorbs to

### 3 Setup and measurement techniques

---

the surface. At the University of Regensburg we have adopted an alternative epitaxy approach to the CVD growth. In our research group we have the possibility to grow a heterostructure via molecular beam epitaxy (MBE).

#### MBE

The following description has similarly been elaborated during my master's thesis in [75]. For the MBE growth the source material comes as highly purified solid state material and no precursor compound is required. The solid source material is evaporated by an electron beam inside an ultra-highly evacuated chamber. The growth in the ultra-high vacuum chamber and the absence of a precursor ensures a long mean free path of the evaporated atoms or atom clusters and ensures a very low impurity density during the growth. Inside the MBE chamber, the substrate surface is heated and evaporated atoms adsorb to the surface and cluster to begin the horizontal layer growth. Diffusion of atoms on the sample surface suppresses crystal defects. By controlling the source material flux with shutters in front of the effusion cells, mono-atomic layers can precisely be grown and the heterostructure be engineered. Also, isotopically purified source materials of silicon with a residual  $^{29}\text{Si}$  concentration as low as 60 ppm are available at the University of Regensburg. MBE growth details are for example well described in the thesis of Dr. Christian Neumann [88] as well as in the thesis of Dr. Floyd Schauer [81]. Here, only a short overview is given [75].

The heterostructure is grown on a silicon substrate on top of which a relaxed SiGe graded buffer is grown, increasing the germanium concentration from 0% to 30%. The graded buffer is terminated by a constant composition layer. This total SiGe virtual substrate provides a thickness of about 4  $\mu\text{m}$  and by grading the germanium concentration, threading dislocations induced by strain tend to relax towards the side and not vertically. Following the constant composition layer the about 10 nm thick strained silicon quantum well is grown. The heterostructure stack is completed by an additional 35-45 nm SiGe buffer and a 1 nm Si cap to prevent oxidation. A typical cross section of the heterostructure is illustrated in Figure 2.2.

#### 3.1.2 Sample fabrication

The MBE growth at the University of Regensburg is typically performed on 2 inch or 3 inch wafers. To fabricate a fully working qubit device from this heterostructure, additional post-processing steps are required. These routine sample fabrication has also been a larger part of this PhD project and the most important steps are briefly described here.

Ohmic contacts to the quantum well, which is buried by an about 40 nm thick SiGe barrier

under the sample surface, are defined locally by ion implantation of phosphorus atoms at a dose of  $5 \cdot 10^{15}$  atoms/cm<sup>2</sup> at an energy of 20 keV and an angle of 7°. We observed that this ion implantation recipe is sufficient for contacting a quantum well buried as deep as 50 nm and that there is no need for a combination of the phosphorus atoms with larger arsenic atoms for ensuring a continuous contact also through the surface-near barrier. We also observed that a single acceleration voltage suffices and no higher- or lower-energetic ions are required for penetrating different depths in the sample to ensure a continuous electrical connection. Only for extraordinary deeply buried quantum wells changes to the sample recipe may be considered.

Upon implantation the single crystal is destructed. In order to heal crystal defects and simultaneously to integrate dopants into the crystal lattice and to activate these dopants, the implanted samples undergo a rapid thermal anneal (RTA) at a temperature of 700°C for only 15 s with a rapid thermal ramp. This annealing bears the risk of blurring the quantum well edges for a too large thermal budget. We achieved very good results with this short annealing procedure.

There is currently an ongoing development with first promising results in our research cooperation together with the RWTH Aachen University for substituting the thermal anneal with local laser annealing. Results can be found in the Master's thesis of Isabelle Sprave [89]. The idea of the laser annealing procedure is to only locally apply the thermal budget and the quantum well distant to the ion implanted regions remains unaffected.

Following the ion implantation and the crystal annealing, typically a first oxide layer is deposited onto the sample via atomic layer deposition (ALD) at 300°C. The rather high temperature during this ALD process contributes to suppress crystal defects in the oxide, but does not bear the same risk of blurring heterostructure interfaces as the RTA. There are also ongoing projects of growing this first oxide layer in an MBE process, before the heterostructure even leaves the MBE chamber. But this MBE grown oxide is prone to take damage during a regular RTA, so progress relies on a working laser annealing recipe. The metallic gates on top of the sample are lithographically defined, mostly by electron beam lithography and for the fan out towards the sample edge, the structuring is supported by UV lithography. The lift-off process of the lithography is performed in a wet-chemical process. The used recipes and fabrication details are similar to those in the appendix of the thesis of [81, 88].

### **3.1.3 Qubit device: Accumulation vs. depletion mode**

Two main approaches of confining and controlling single electrons in a silicon quantum well heterostructure were present for the design of the metal gate stack on the sample surface at the beginning of this thesis. One approach we will call depleting-mode architecture. This approach has been very successful for the first spin qubit devices. Also

### 3 Setup and measurement techniques

during my master's thesis we extensively measured a depletion-mode device [58, 59, 75]. With the beginning of this thesis, a second approach that we will call accumulation-mode architecture emerged. Both approaches differ in the way the metal stack on the sample surface is designed and the gate voltages are tuned and consequently also differ in the way electrons are accumulated in the quantum well. As both working types are employed during this thesis, they are introduced and discussed in the following.

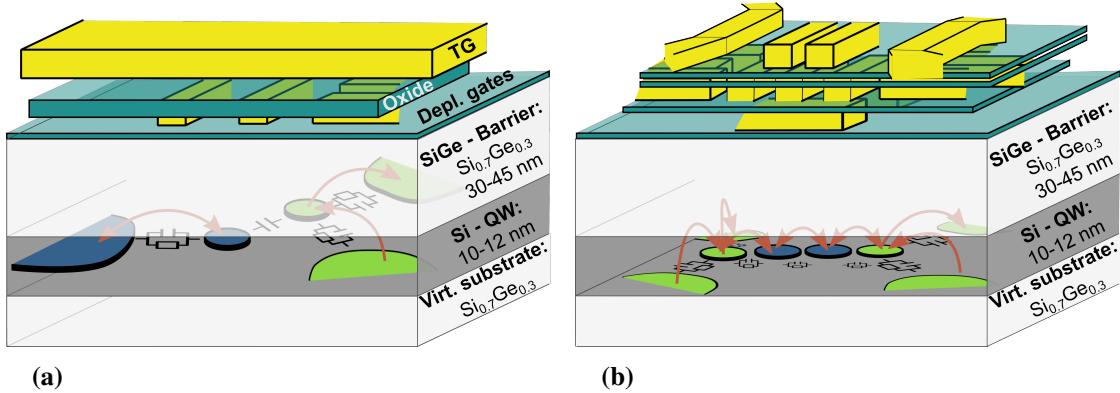

**Figure 3.1: Depletion vs. accumulation type of a qubit sample.** (a) Illustration of a depletion-mode device. A global topgate (TG) for electron accumulation is designed across the whole quantum well, but its electric field is locally screened by an underlying depletion-gate layer. As a result quantum dots are formed in the gaps between the depletion gates. (b) Accumulation-mode type illustration. No global topgate is present in this device. Each resulting quantum dot is defined directly underneath an individual gate, here in the third of three isolated metallic gate layers.

The depletion-mode architecture of qubit samples is sketched in Figure 3.1a. The figure illustrates the quantum well and the upper SiGe-barrier of the heterostructure. For simplicity the Si cap as well as the ion implantation are not drawn here. The figure illustrates a gate stack and two oxide layers fabricated on top of the sample. Characteristic for this depletion-mode architecture is a global topgate (TG) covering the whole active region of the sample and serving for the charge carrier accumulation in the quantum well. The local electron control is realized by the lower lying depletion gate layer. This metal layer screens the positive electric field of the TG locally, forming barriers and only allowing a quantum dot formation in between gaps of this depletion gate layer. Electron reservoirs are therefore formed everywhere, where no depletion gate is positioned directly above. The sketch in the Figure 3.1a is very much simplified as only two quantum dots

are drawn by only four depletion gates. Three depletion gates separate the quantum dots from the respective reservoirs and one depletion gate forms the inter-dot separation. The device is designed here to only allow a capacitive inter-dot coupling but allows tunnel coupling to the respective reservoirs. The green quantum structure forms a SET, which operates as a sensor for the device, while the blue quantum structure may serve as the qubit confining quantum dot and the related reservoir. Note, as all reservoirs are induced by the large TG we expect 2DEGs to form in the reservoirs.

The accumulation-type sample in Figure 3.1b does not feature a global TG. The sketch illustrates a sample with three metallic gate layers, all separated by oxide from each other. Here, each of the two blue quantum dots in the center of the quantum well has an own, dedicated plunger gate in the third metallic gate layer directly above. Also, the two quantum dots at the ends of the sample have a dedicated accumulation gate in the third layer. The second gate layer features gates which are used to form tunnel barriers in between the quantum dots and again each barrier has its own gate directly above. This is characteristic for the accumulation-type of devices. The first gate layer, often called screening layer, consists here of two horizontal and parallel gates, that have a gap in between. These two gates confine the electron accumulation to the channel in between, resulting in quantum dot formation exclusively inside the gap of these screening gates. The accumulation gates for the sensor dots fans out towards the edges of the sample, inducing 2DEGs for the sensor dots' reservoirs. Note, the blue quantum dots no longer feature a separate 2DEG reservoir but are loaded from neighboring quantum dots. This peculiar difference has been introduced in section 2.3.3.

The accumulation-type realization promises better tunability and less crosstalk between gates, but comes with the cost of a more complex fabrication as the pitch between gates becomes smaller and three gate layers compared to the two from the depletion type must be fabricated. For both types working qubit devices have been demonstrated, but the community trends towards employing the accumulation type design.

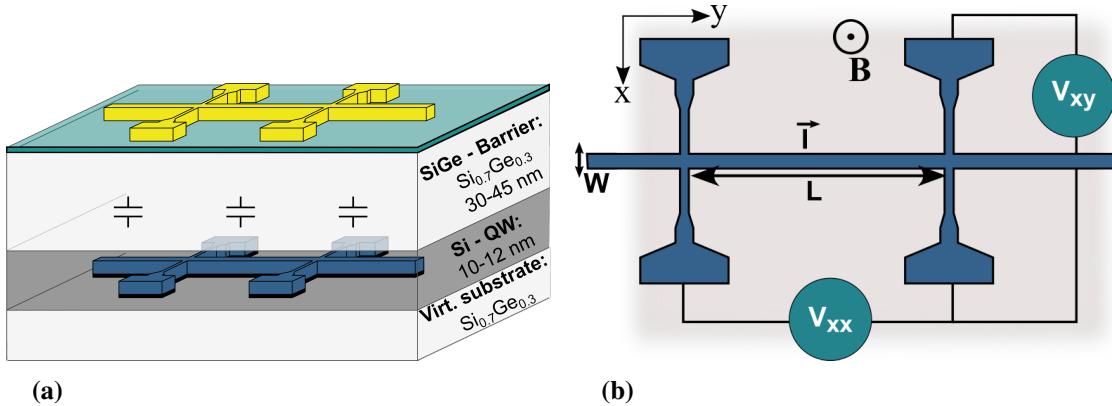

### 3.1.4 Hall bar sample

In contrast, a Hall bar device, which will be used for quantum Hall measurements throughout the thesis, does not require a complex gate stack. For this type of device, we typically fabricate a single gate on top of the sample surface, isolated by a 20 nm thick  $\text{Al}_2\text{O}_x$  layer like shown in Figure 3.2a.

The gate voltage induces a 2DEG in the quantum well in the shape defined by the gate geometry. Here, we drive a current  $I$  along the length of the Hall bar device. This current is indicated in the top view in Figure 3.2b. The geometry has pairwise connections along

### 3 Setup and measurement techniques

**Figure 3.2: Hall bar device.** (a) Single-gate induced 2DEG in Hall bar shape in the quantum well. (b) Top view of the Hall bar geometry. Voltage probes along and perpendicular to the Hall bar channel are indicated.

the Hall bar axis separated by length  $L$  and width  $W$ . If a magnetic field  $B$  is applied perpendicular to the 2DEG plane, the accumulated electron density and mobility can be calculated following the formulas in section 2.2.2, considering the width to length ratio  $W/L$ , which amounts to a factor of 13 in our samples.

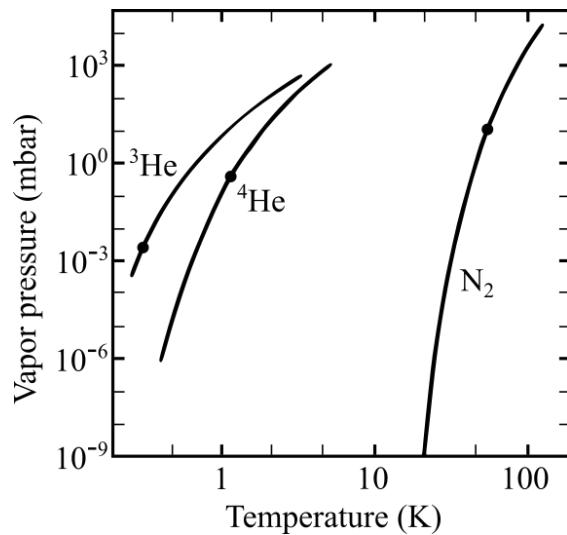

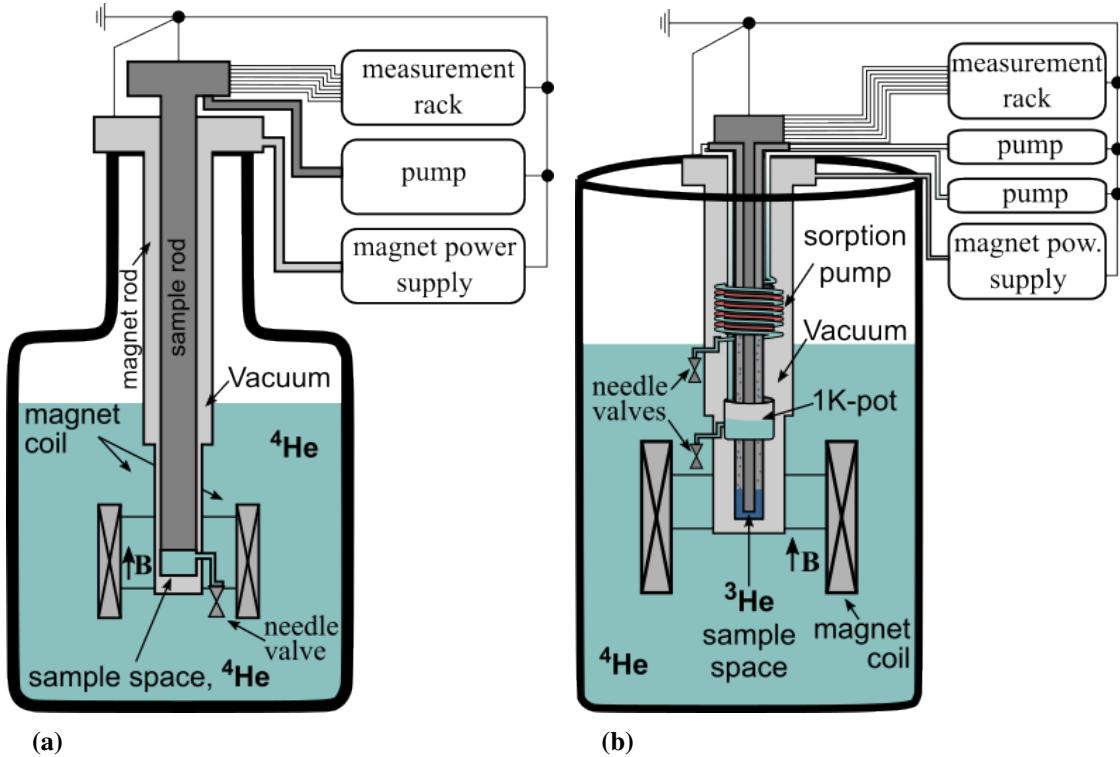

## 3.2 Cryostat

All transport experiments are conducted at temperatures below 2 K, so in a thermal environment in which the thermal noise does not disturb the measurements of quantum mechanical effects like the quantum Hall effect, Coulomb blockade or spin physics. In our laboratory we have three different cryostat systems available, all with different advantages and suitable for different device measurements. This section starts by introducing two cryostats using liquid helium for the sample cooling and then introduces a cryostat that uses a certain phase transition of helium isotopes for cooling to temperatures below 10 mK.

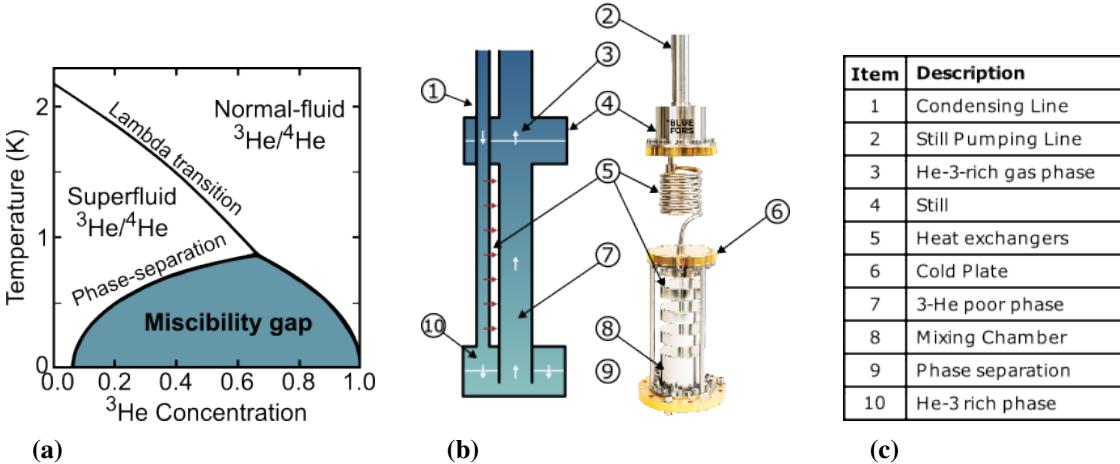

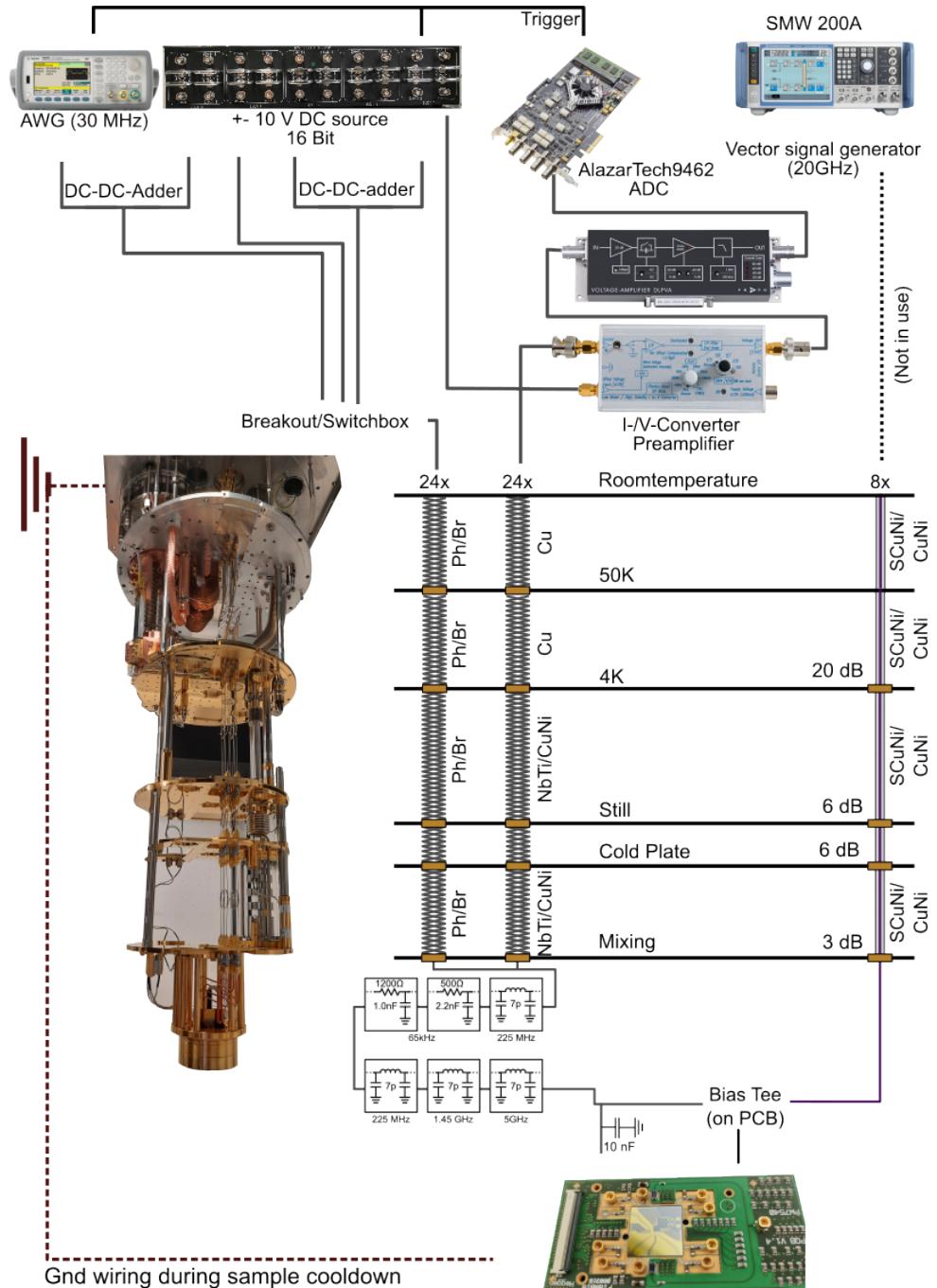

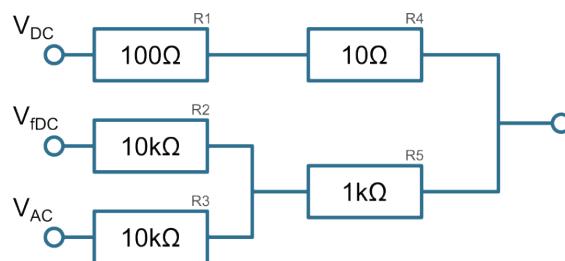

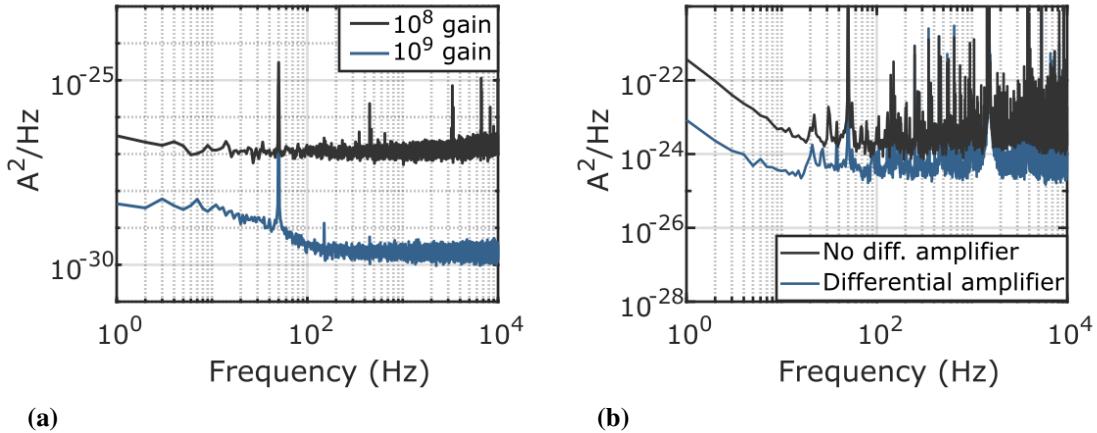

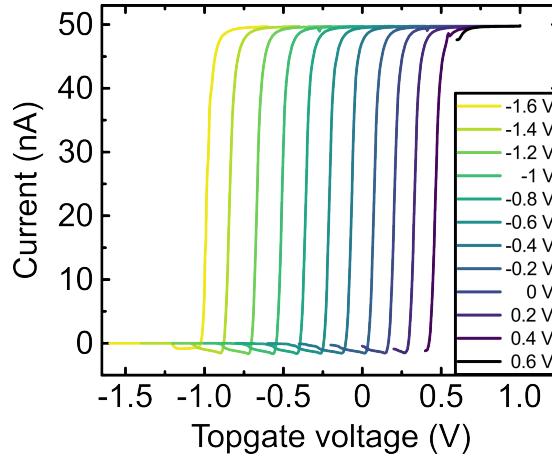

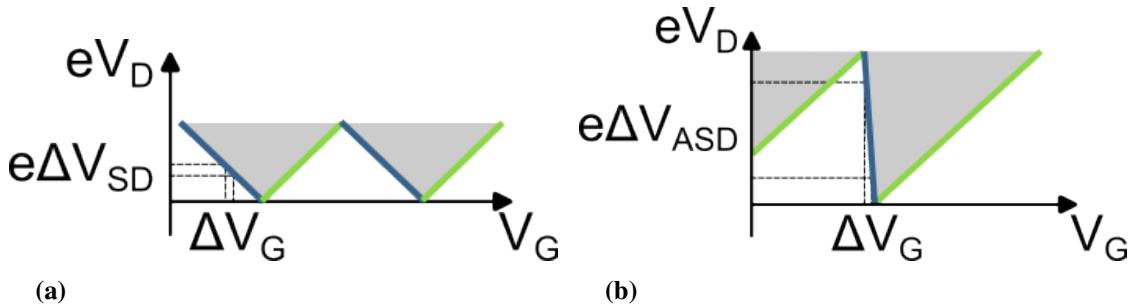

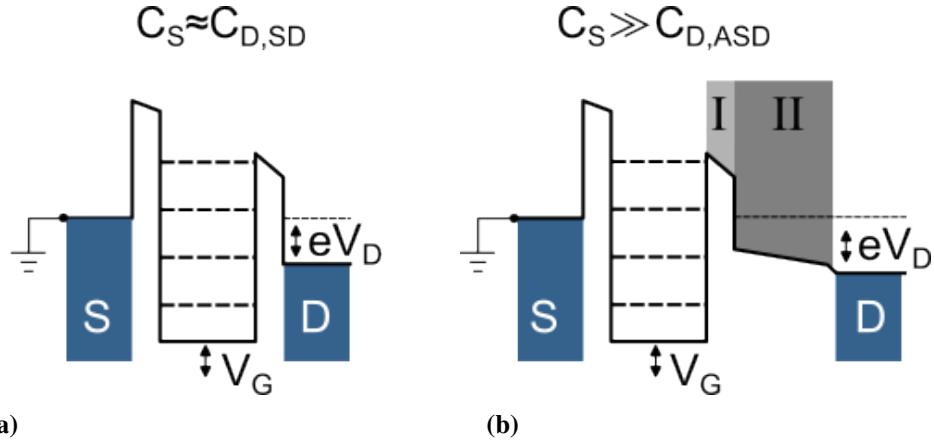

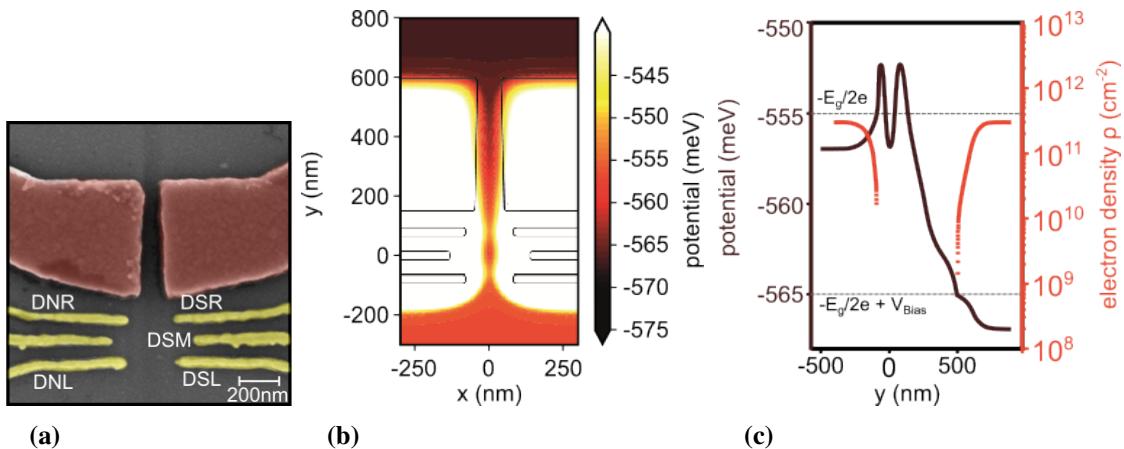

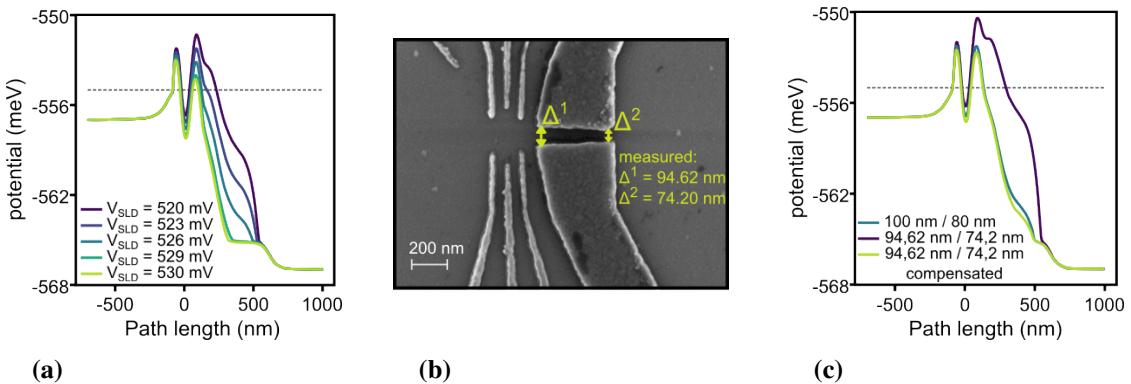

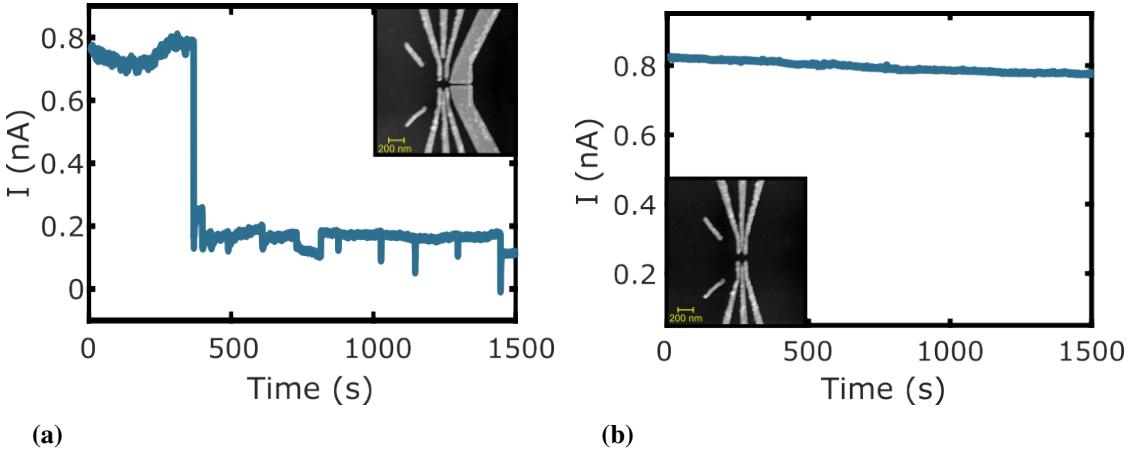

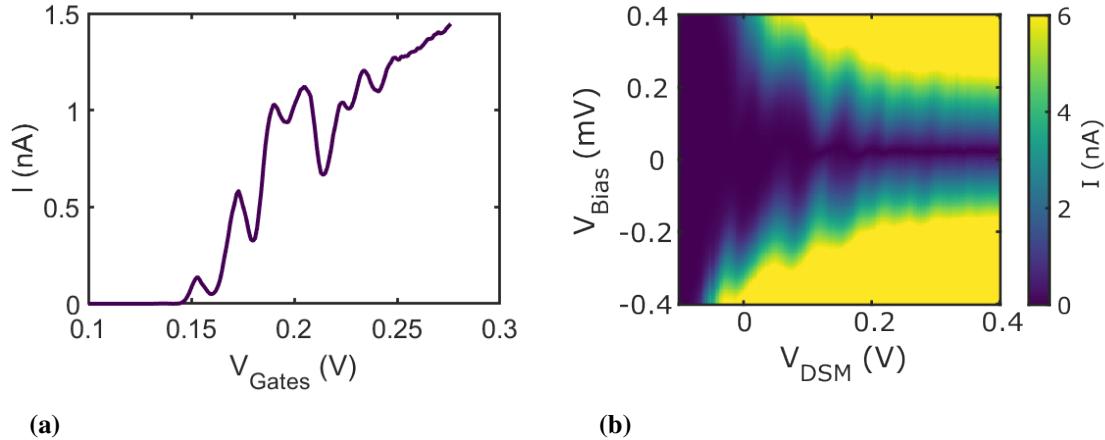

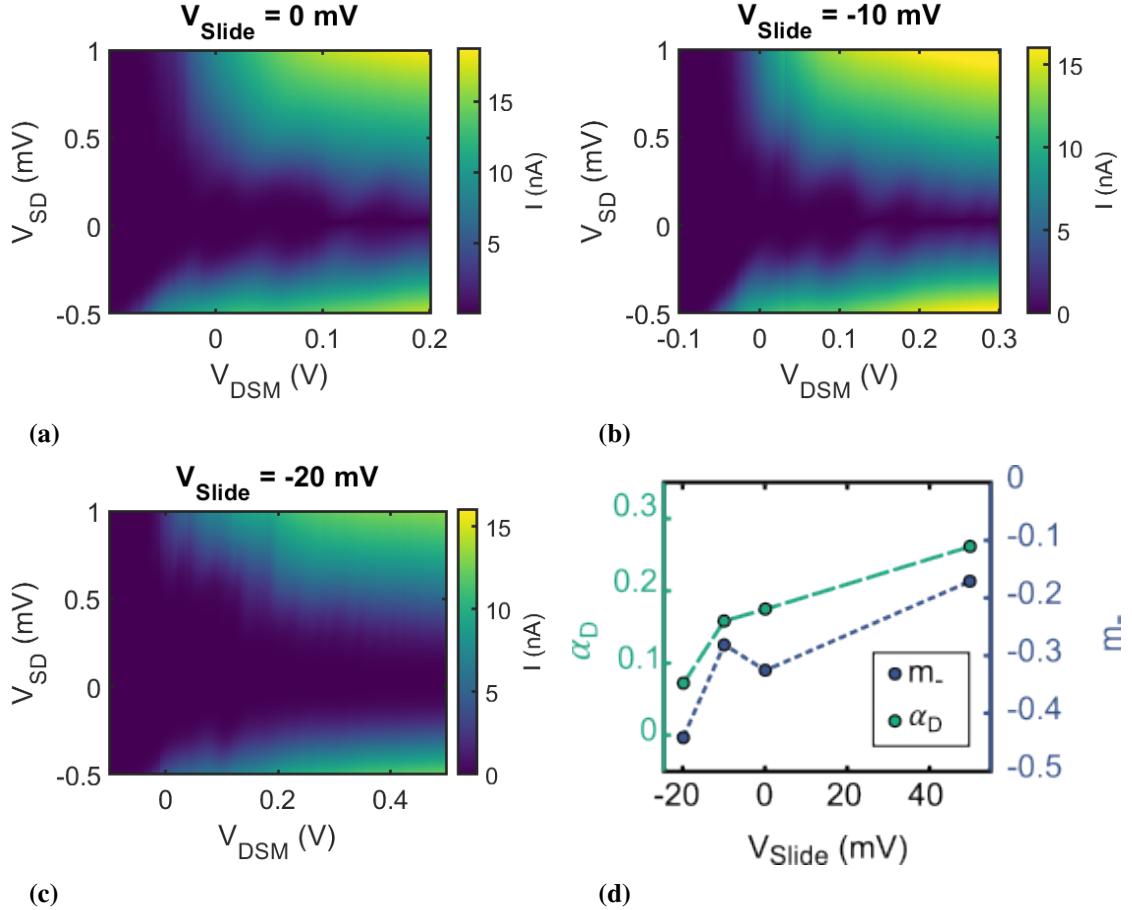

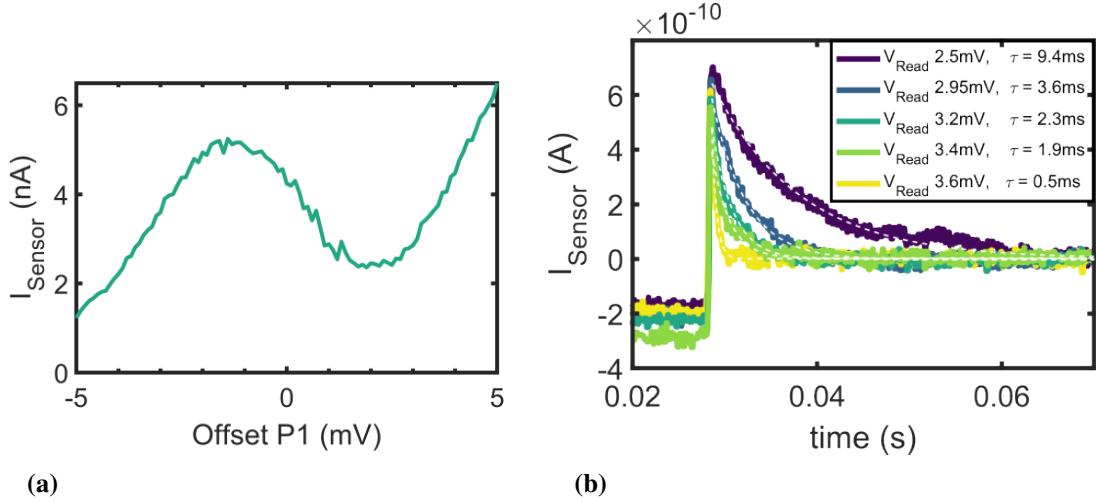

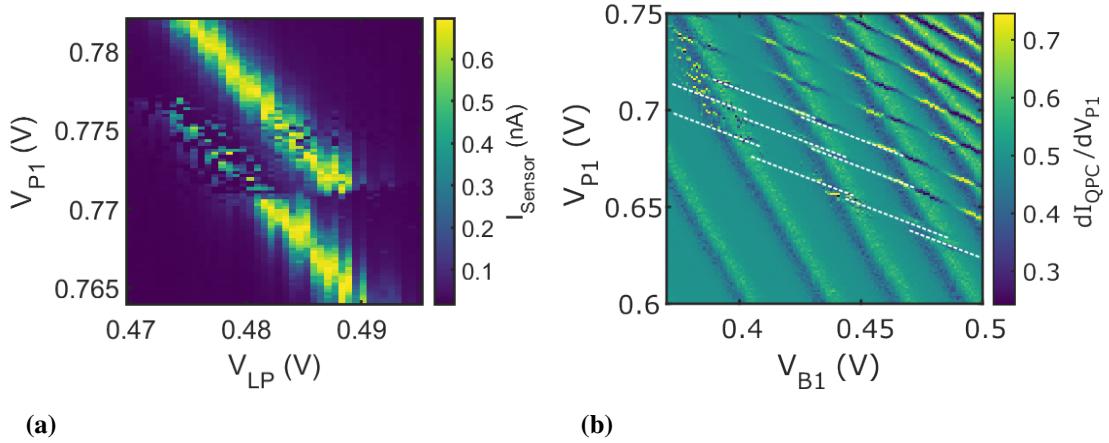

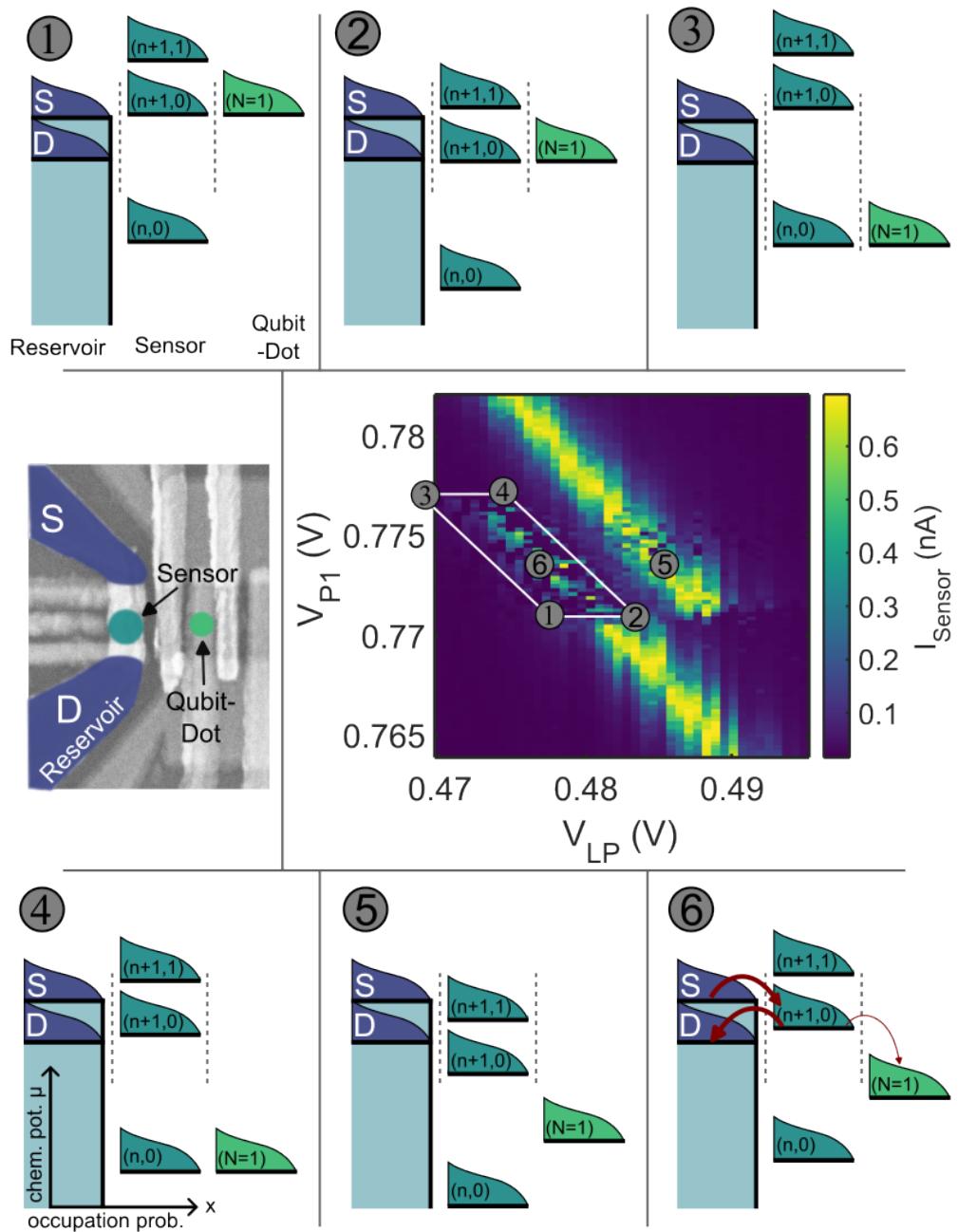

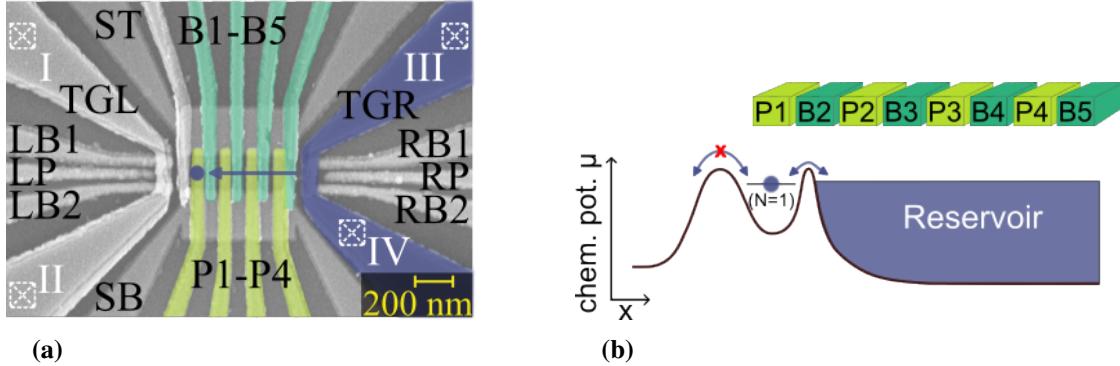

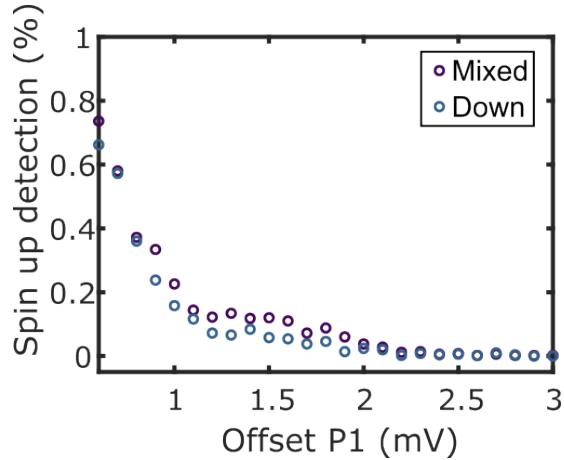

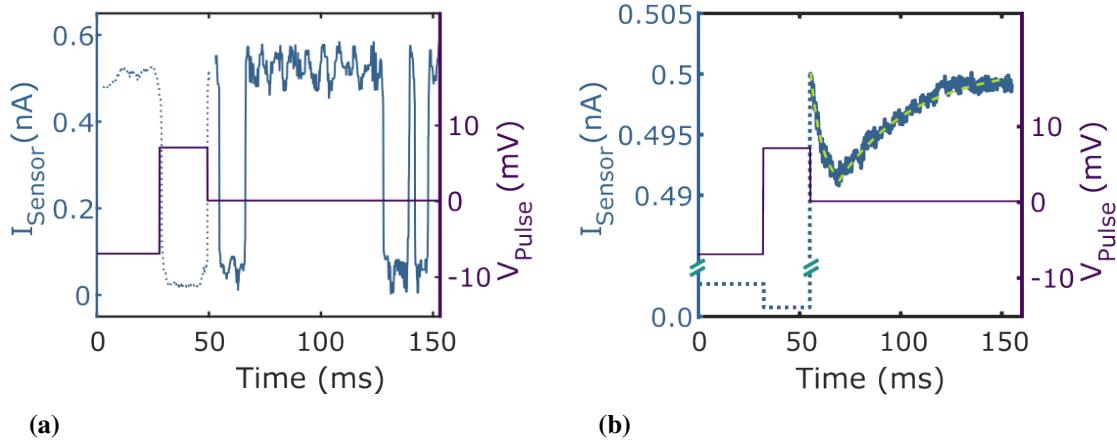

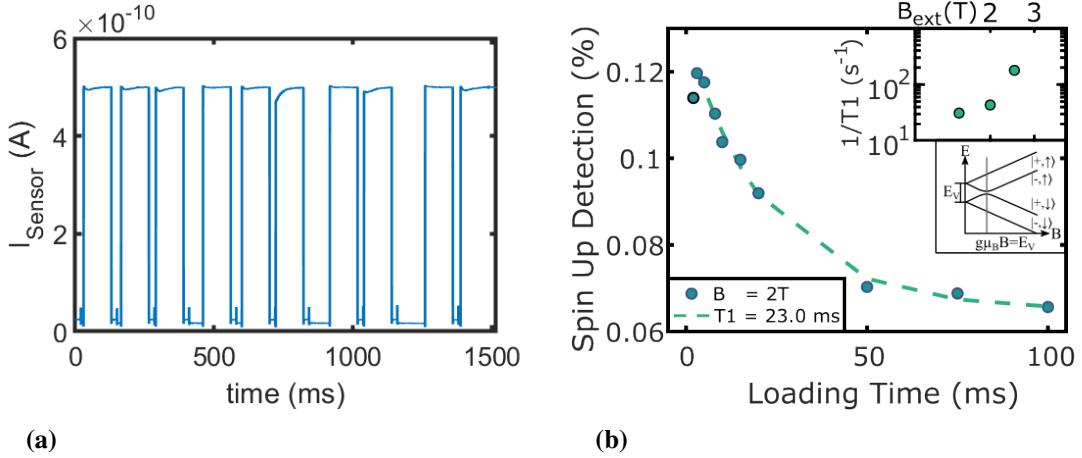

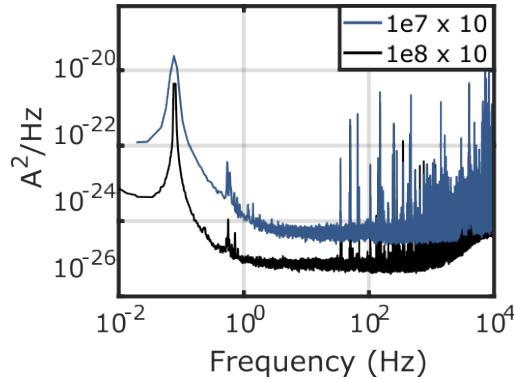

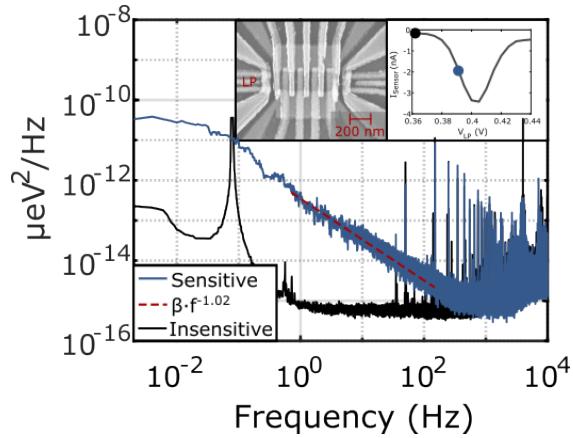

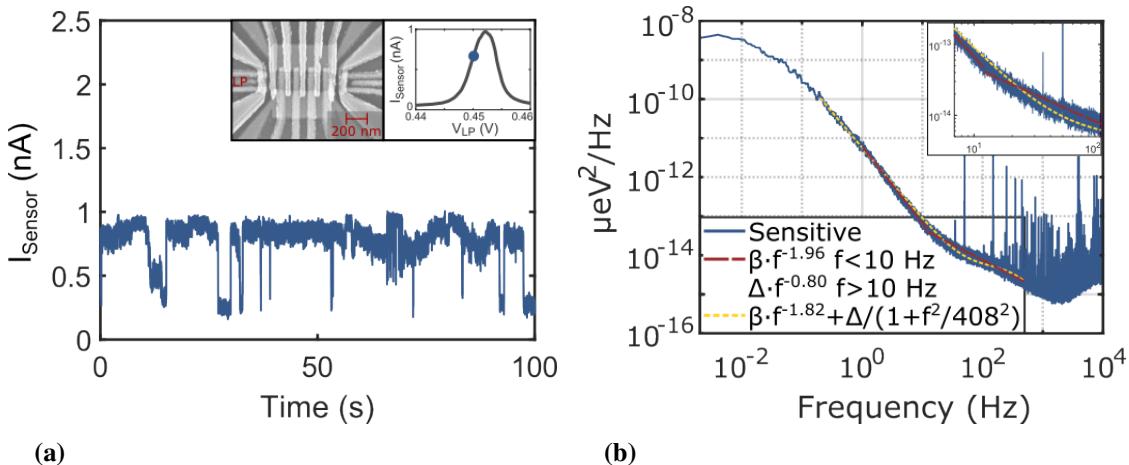

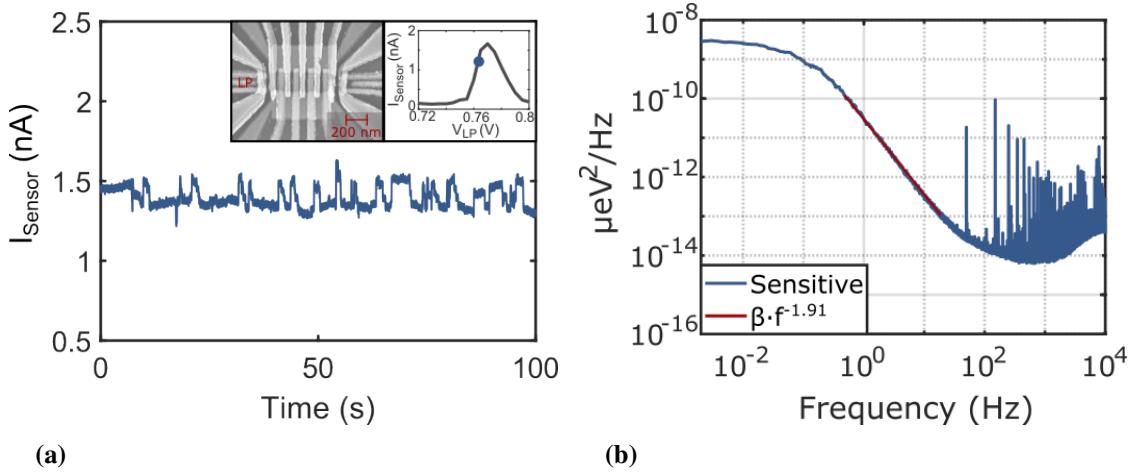

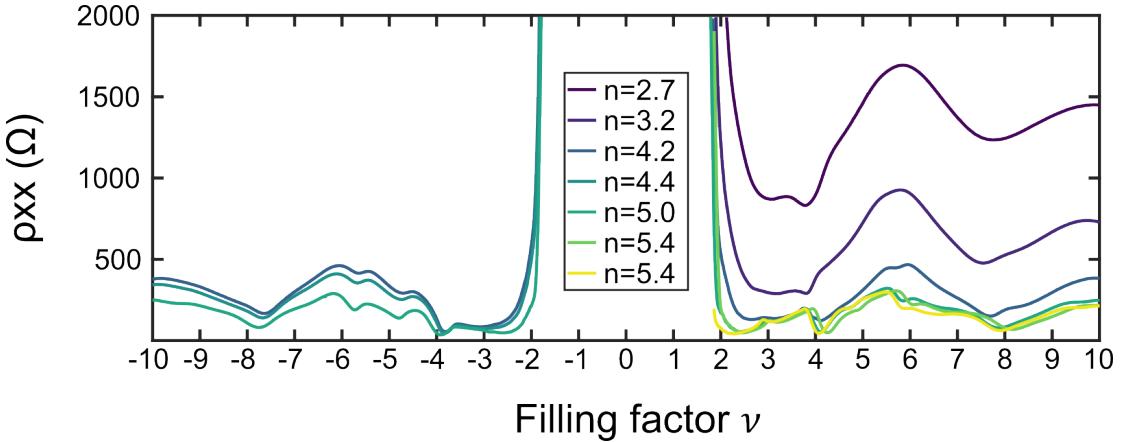

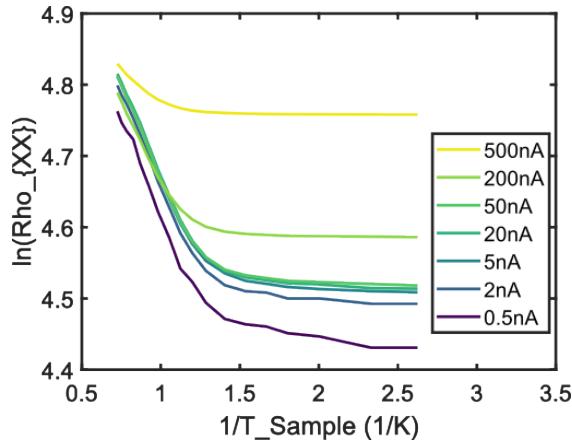

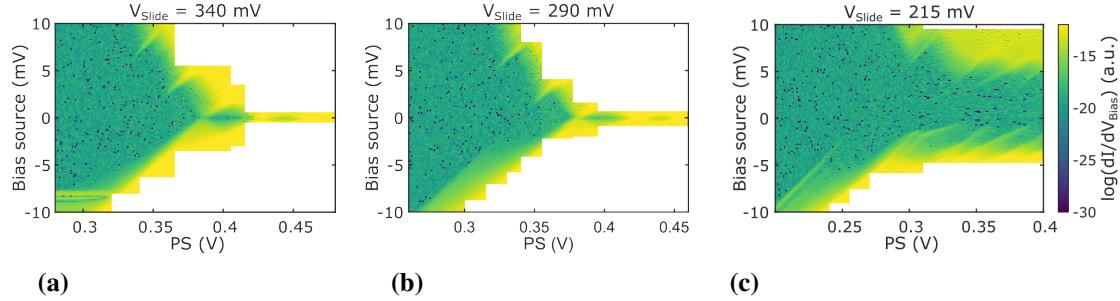

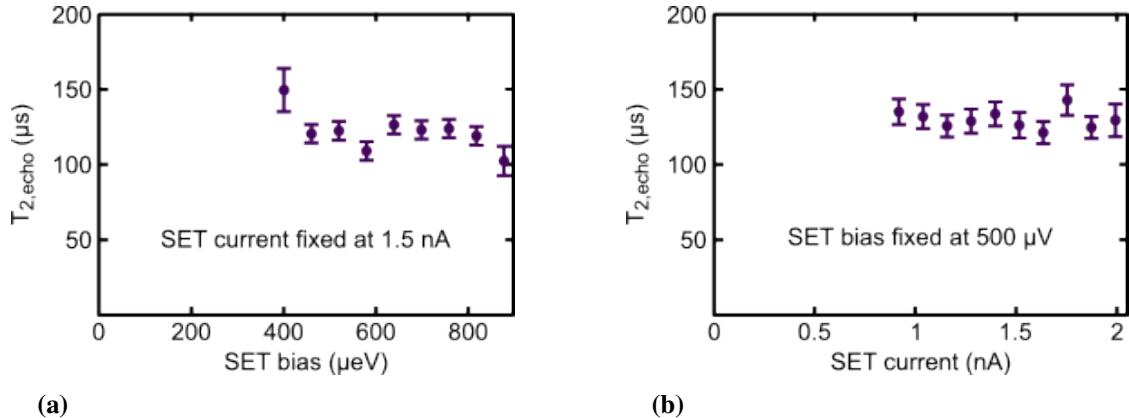

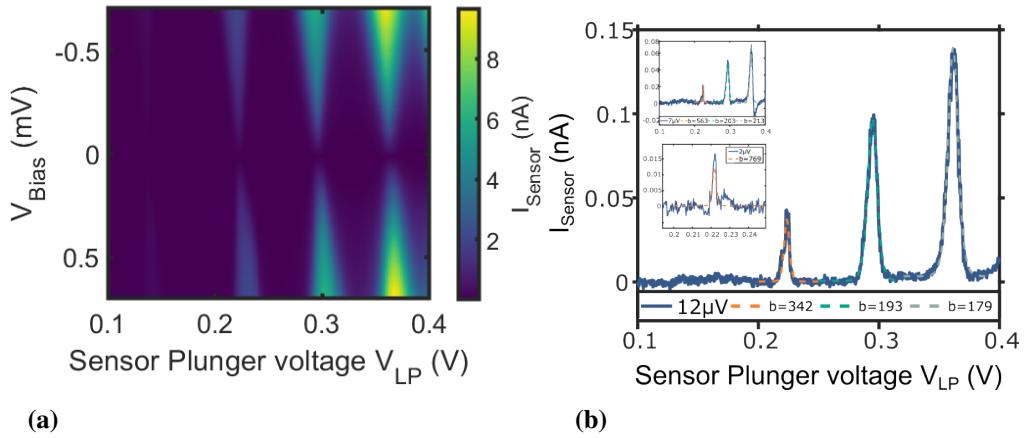

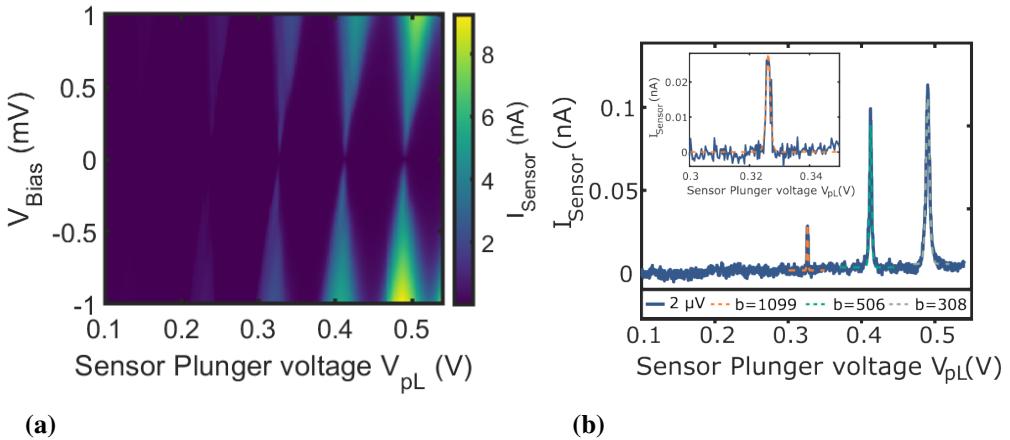

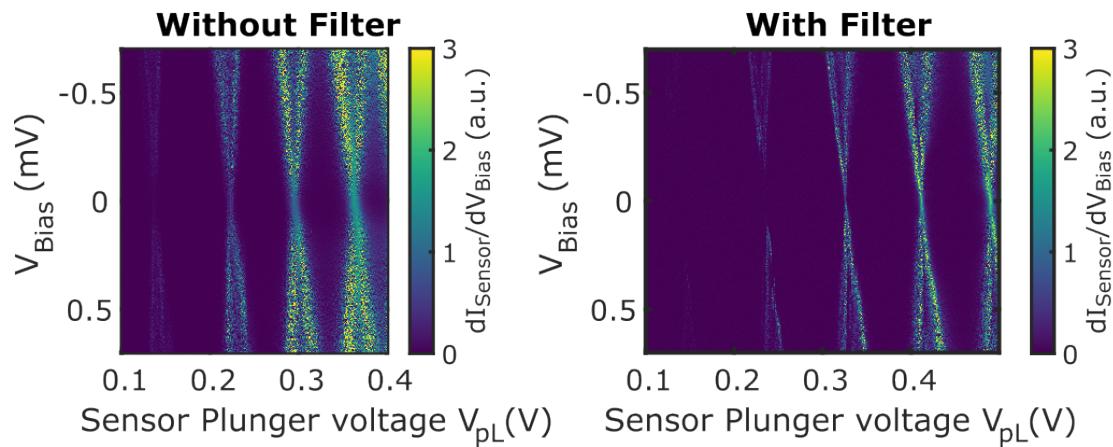

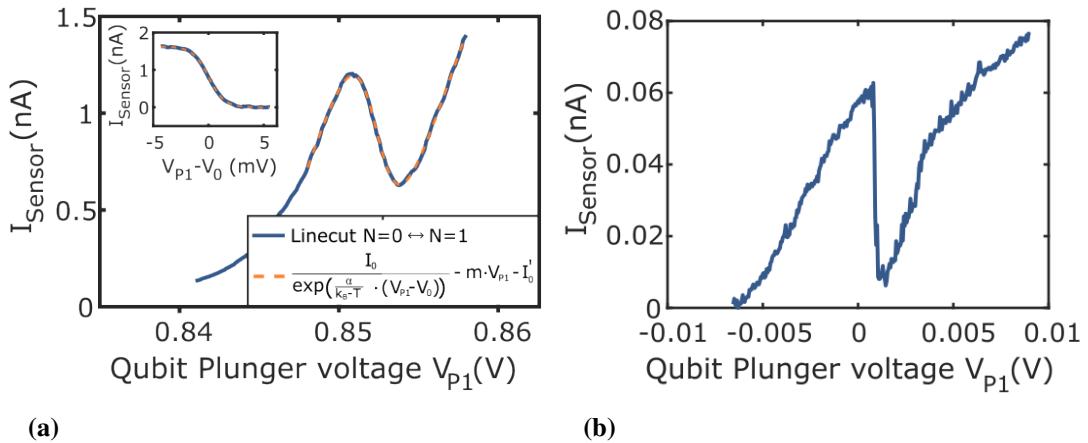

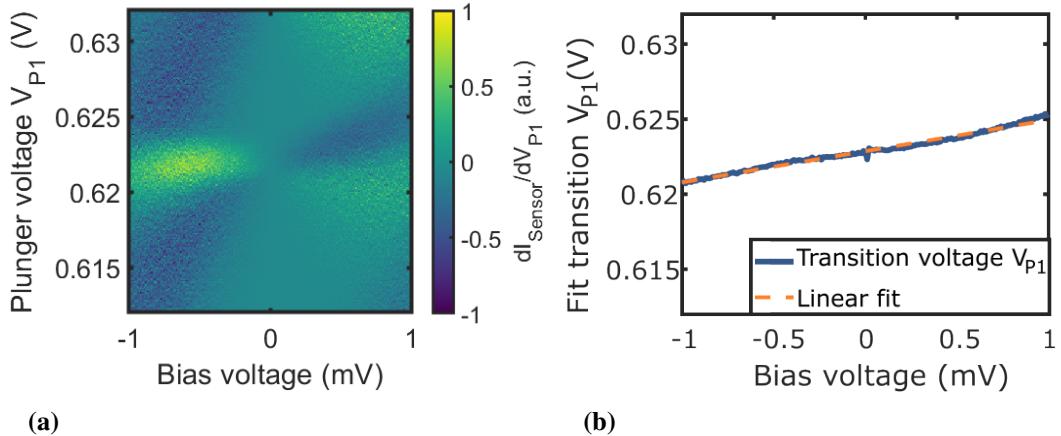

### 3.2.1 Liquid helium cryostats