# 1      The CMOS Pseudo-Thyristor: A Zero-Static Current

## 2      Circuit for Pixelized Detector Front-End Stage

---

3      **X. Wen, <sup>a</sup>D. Gong, <sup>b</sup>X. Huang, <sup>a</sup> T. Liu, <sup>b</sup>P. Gui, <sup>b</sup> and J. Wu, <sup>b,1</sup>**

4      *<sup>a</sup>Southern Methodist University,

5      Dallas, TX 75275, USA.*

6      *<sup>b</sup>Fermi National Accelerator Laboratory,

7      Batavia, IL 60510, USA.*

8      *E-mail: [jywu168@fnal.gov](mailto:jywu168@fnal.gov)*

11     ABSTRACT: A very low power front-end discriminator circuit for pixelized detectors, called

12    pseudo-thyristor is described in this document. It is a positive feedback topology using regular

13    PMOS and NMOS field-effect transistors (FET's) with zero static current. When a small charge

14    is injected into the circuit, it flips rapidly due to the positive feedback and outputs a logic transition

15    for further digitization. Simulation shows that in 65 nm process, it is possible to achieve a

16    detecting threshold of 5 fC while maintain the average power consumption below 10 micro-Watts

17    when the hit occupancy is < 10% for 40 MHz operation.

18     KEYWORDS: Front-end electronics for detector readout; Solid state detectors; Timing detectors

---

<sup>1</sup> Corresponding author.

---

20 **Contents**

|    |                                                        |          |

|----|--------------------------------------------------------|----------|

| 21 | <b>1. Introduction</b>                                 | <b>1</b> |

| 22 | <b>2. Design of the Pseudo-Thyristor Discriminator</b> | <b>2</b> |

| 23 | 2.1 Circuit Diagram                                    | 2        |

| 24 | 2.2 An Application Example                             | 4        |

| 25 | 2.3 Design Considerations                              | 5        |

| 26 | <b>3. Simulation Results</b>                           | <b>5</b> |

| 27 | 3.1 Operations of the pseudo-thyristor discriminators  | 5        |

| 28 | 3.2 Power Consumptions                                 | 6        |

| 29 | <b>4. Conclusion and outlook</b>                       | <b>7</b> |

| 30 |                                                        |          |

| 31 |                                                        |          |

| 32 |                                                        |          |

---

33 **1. Introduction**

34 In contemporary high energy physics detectors, pixelized detectors, either silicon detectors or

35 Low-Gain Avalanche Detectors (LGADs) are widely used for tracking, timing or calorimeters.

36 As the number of detector elements or pixels continues to increases towards the future, much

37 lower power consumption of the front-end circuits is required or desired. In some applications,

38 power consumption as low as 10 micro-Watts per channel is desired. In typical architecture today,

39 the front-end circuits consist of pre-amplifiers and discriminators, each consumes about 1 milli-

40 Watts power for 65-180 nm CMOS fabrication processes and this is a factor of 100 higher than

41 what's desired in the future. To reduce the power consumption by up to two orders of magnitude,

42 new approaches of the front end design are required. The Pseudo-Thyristor proposed here is a

43 novel CMOS circuit with zero static current for LGAD-like frontend electronics with the potential

44 to have ultra-low power consumption.

45 The circuit is a positive feedback topology (which is rarely used in analog frontend circuits)

46 using regular PMOS and NMOS field-effect transistors (FET's). The core of the circuit consists

47 of a pair of PMOS and NMOS FET's with the drain and gate terminals of them cross connected

48 to form a positive feedback loop. When a small amount of electric charges is injected into the

49 NMOS gate, both the NMOS and PMOS FET's are turned from OFF to ON state similar as a

50 thyristor, except that in both ON and OFF states, the static current of the circuit is almost zero

51 (with small leakage currents in deep nanometer fabrication processes) as in most digital CMOS

52 circuits. The circuit converts a signal with a small charge into a logic level transition and later

53 resets from ON to OFF state with a set of MOS FET's.

54 Intrinsically, in typical architecture today, the transistors in the amplifiers and discriminators

55 must operate with a static current so that the transistors are in high conductivity region to follow

56 the input pulse at high speed. The topologies used in amplifiers usually employs deep negative

57 feedback to improve bandwidth and linearity.

58     However, in pixelized detectors, full waveform information is usually not needed because

59     we usually only care about whether a charged particle passed through a given pixel, or we are also

60     interested in the arrival time of the particle. The full waveform information is also not practical

61     due to the limited data link bandwidth. In many cases, single bit hits indicating the coordinates

62     of the passing points of charged particles in a tracking detector are sufficient. Beyond that, one

63     may digitize the arrival times of the particle hits and sometimes digitize the pulse widths for time

64     walk correction. In these situations, the requirement to the front-end circuit is nothing more than

65     to provide a logic flipping. This requirement can be fulfilled using very low power circuits

66     consuming zero static current. Also, since the detector elements produce only one type of charges

67     (negative charges), symmetric topologies in the front-end circuits are not necessary, which further

68     simplifies the circuits and results in lower power consumption.

69     While the circuit can be at least utilized for 1-bit hit detection in tracking pixel detectors,

70     timing walk correction is possible when the 4D detection is demanded, although further

71     simulation and testing are needed..

72     We chose a circuit scheme with positive feedback for fast switching between OFF and ON

73     states that operates like a thyristor. However, unlike a thyristor that needs a static current to

74     maintain the ON state, our front-end circuits consumes zero static currents for both ON and OFF

75     states as in regular CMOS digital circuits. For this reason, we name the circuit as Pseudo-

76     Thyristor Discriminator. In this documents, circuit design of the pseudo-thyristor discriminator

77     is described in Section 2 and simulation results are shown in Section 3, followed with conclusion

78     in Section 4.

79 **2. Design of the Pseudo-Thyristor Discriminator**

80 **2.1 Circuit Diagram**

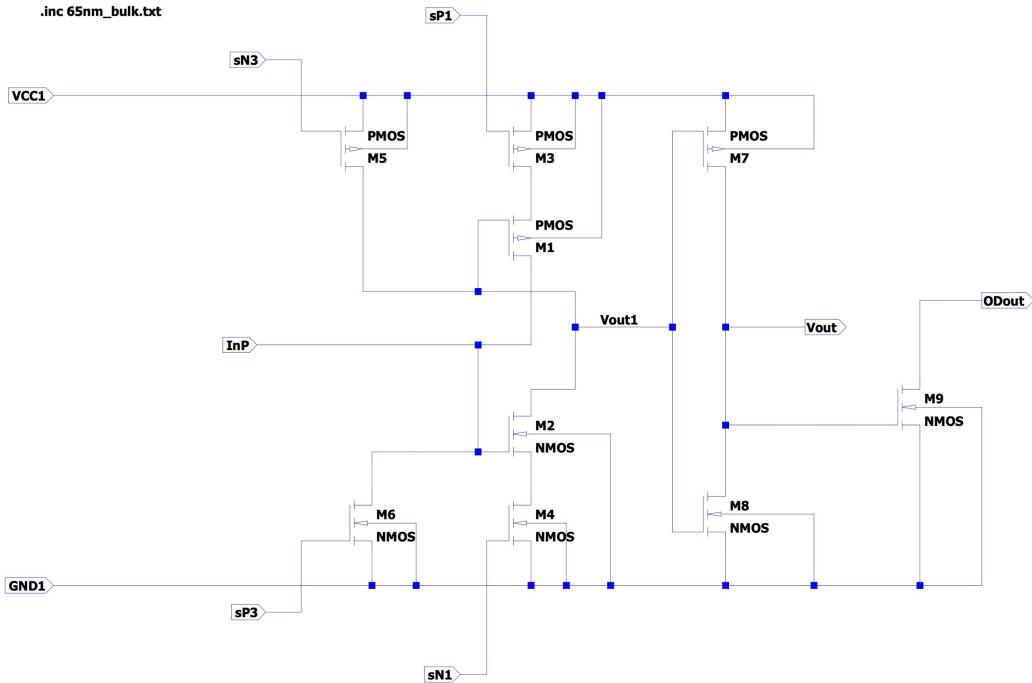

81     Figure 1 illustrates the circuit diagram of the pseudo-thyristor discriminator. The entire circuit is

82     constructed with regular PMOS and NMOS field-effect transistors (FET's) in TSMC 65 nm

83     process.

Figure 1. Circuit diagram of the pseudo-thyristor discriminator

84

85     The core of the circuit consists of a pair of PMOS (M1) and the NMOS (M2) FET's with the

86     drain and gate terminals of them cross connected to form a positive feedback loop. At standby

87     condition, external control signals  $sP1=LO$  and  $sN1=HI$  which cause M3 and M4 in ON state

88     while  $sP3=LO$  and  $sN3=HI$ , causing M6 and M5 in OFF state. After initialization, both M1 and

89     M2 are in OFF state, i.e., the gate of M1 (and the drain of M2) is in HI state while the gate of M2

90     (and the drain of M1) is in LO state. When a small amount of electric charges (typically several

91     femto-Coulombs) is injected via InP port into the NMOS (M2) gate, after the M2 gate is charged

92     beyond the threshold voltage, both the M2 and M1 are turned from OFF to ON state. Due to

93     positive feedback, the switching process is fast with relatively large instantaneous currents that

94     charge the gates of the FET's in a short amount of time. Once in the ON state, both M1 and M2

95     are conductive and the gates of M1 and M2 are kept in the LO and HI voltage level, respectively,

96     which maintain both transistors in ON state until the next reset period.

97     During reset period,  $sP3$  is turned to HI while  $sN3$  is turned to LO causing both M6 and M5

98     becoming ON. The gates of M1 and M2 are discharged to HI and LO voltage levels, respectively,

99     which force both of them to go OFF state. To prevent shorting power rail that cause large current

100    when M5 and M6 become conductive before M1 and M2 are turned OFF, transistors M3 and M4

101    are added and controlled by  $sP1$  and  $sN1$  signals. The  $sP1$  and  $sN1$  are flipped slightly earlier

102    than  $sP3$  and  $sN3$  so that they can cut off current paths before M6 and M5 are turned ON.

103    Therefore, the detailed resetting process takes several small steps: (1) M3 and M4 are turned from

104    ON to OFF, (2) M5 and M6 OFF to ON, (3) M1 and M2 ON to OFF, (4) M3 and M4 OFF back

105    to ON, (5) M5 and M6 ON back to OFF. After resetting, M1 and M2 remain OFF until external

106    charges injected into the gate of M1.

107    The pair of transistors M7 and M8 form a inverting buffer to drive circuits in later stages.

108    The NMOS transistor M9 can be used as an open drain driver.

109 **2.2 An Application Example**

110 An application example of the pseudo-thyristor discriminator interfacing with a negative

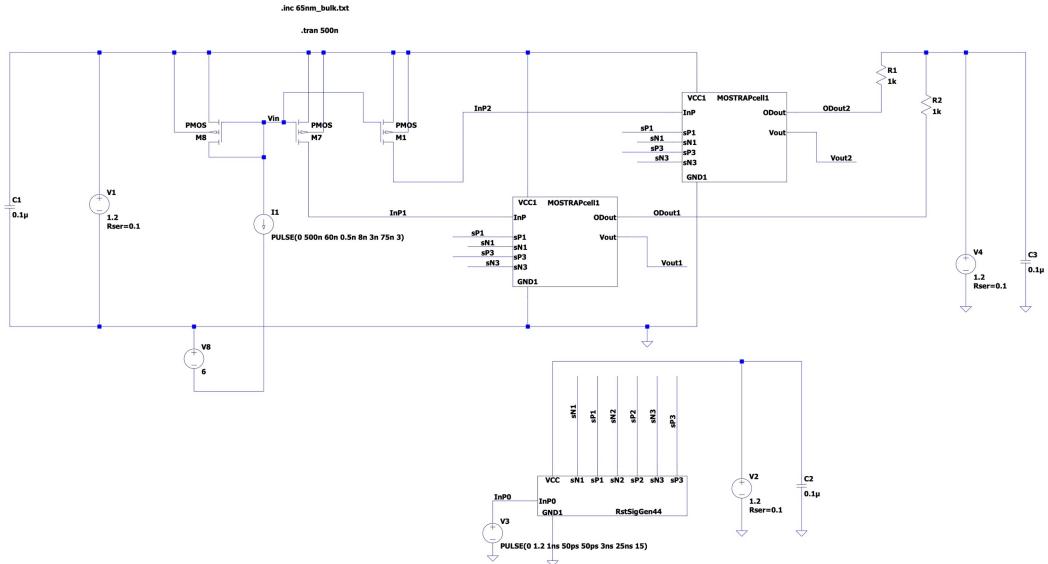

111 current source is studied and the circuit diagram is shown in Figure 2.

**Figure 2.** Circuit diagram of the application of pseudo-thyristor discriminator interfacing with a negative current source.

112

113 The current source I1 emulates the input from a detector element that generate a short (~10

114 ns) negative pulse with total charge approximately 5fC. The input current is amplified with a

115 current mirror structure built with M8, M7 and M1. The outputs from M7 and M1 are fed into

116 two identical pseudo-thyristor discriminators in the subcircuit MOSTRAPcell1 blocks with circuit

117 diagram as shown in Figure 1.

118 The block RstSigGen44 contains a set of inverters and converts the input pulse (InP0) into

119 the control signals sN1, sP1, sN3 and sP3 for reset process as described in previous subsection.

120 In this example, the reset pulse is a 40 MHz periodic signal that emulates resetting the circuits

121 every beam crossing for detectors operating in LHC environment. In fact, the resetting pulse may

122 also be a delayed version of the output logic level, so that the circuit can operate in a self-trigger,

123 self-resetting mode, which we will discuss later.

124 The outputs of the pseudo-thyristor discriminators Vout1 and Vout2 are used to drive later

125 stages and the open-drain outputs ODout1 and ODout2 are used to drive internal wires with pull-

126 up resistors. The voltage supplies V1, V2 and V4 with some internal resistance are bypassed with

127 capacitors. Note that the values of the resistance and capacitance are not realistic and they are

128 chosen solely for the purpose of measuring the power consumptions of different parts of the circuit

129 conveniently.

130 In the current mirror, the widths of M7 and M1 are designed to be different so that their

131 outputs have different gains. The gain difference effectively causing the two pseudo-thyristor

132 discriminators to flip with different thresholds of the input charges. For a given input current

133 pulse, the two output logic levels have different flipping times that reflect the pulse height and the

134 time difference is intended to be utilized for time walk correction. Although the time walk

135 correction is yet to be studied.

136 **2.3 Design Considerations**

137 Cautions must be taken during the design of the pseudo-thyristor discriminators. During the

138 standby condition, M1 and M2 in Figure 1 are both in OFF state. The OFF state leakage current

139 of a transistor may charge the gate of the other one which may cause the transistor pair to go to

140 ON state spontaneously via positive feedback if the one of the gates is charged above the

141 conductive threshold. To prevent the transistor pair from spontaneous state changing, the lengths

142 of M1 and M2 are chosen to be relatively large so that they are turned OFF as completely as

143 possible. The transistors M5 and M6, on the other hand, are designed to provide small OFF state

144 leakage currents to maintain M1 and M2 in OFF state.

145 In standby condition, the transistor M8 is in ON state, leakage current through its gate is not

146 negligible, especially in IC chips fabricated with deep nano-meter processes. The length and

147 width of M8 is chosen to be relatively small and the leakage current of M8 is to be balanced with

148 the OFF state leakage current through the M5 drain.

149 With appropriate sets of the transistor lengths and widths, the circuit is able to remain in

150 standby condition indefinitely. However, for applications in colliders, periodic resetting is still a

151 reasonable operating mode to reduce fake hit rate and reduce variations of the flipping thresholds.

152 **3. Simulation Results**

153 The operations of the pseudo-thyristor discriminators is simulated in schematic-level with TSMC

154 65 nm process technology.

155 **3.1 Operations of the pseudo-thyristor discriminators**

156 The simulation is based on an application in a collider with 40 MHz beam crossing as described

157 in Figure 2. The reset pulses generated by V3 in Figure 2 repeat in 25 ns periods with about 3 ns

158 ON state. The external current input is emulated with current source I1 that produces pulses up

159 to 500 nA for about 10 ns, resulting in a total input charge approximately 5 fC.

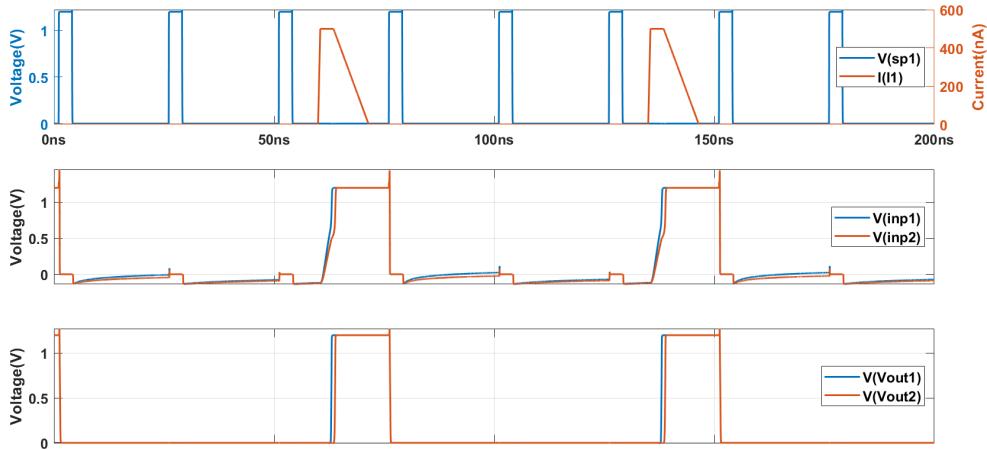

160 The reset pulses and the signal input pulses are plotted in the top pane in Figure 3.

**Figure 3.** Simulation of the operations of the pseudo-thyristor discriminators

161

162 The middle pane shows the voltage at the node InP1 and InP2. The outputs of the current

163 mirrors of the drains of M7 and M1 in Figure 2 charge up the gates of M2 in Figure 1. Since the

164 mirror ratios for these two outputs are different, the charging speeds of these two nodes are

165 different. They reach the threshold at different time and therefore, the two pseudo-thyristor

166 discriminators flip from OFF to ON state at different time. The time difference can be used to

167 estimate the input pulse height and make time walk correction. If the pulse is higher, the time

168 difference becomes smaller given that the two currents from the current mirrors have a constant

169 relative ratio.

170 The two pseudo-thyristor discriminators stay at ON state until the reset at the end of each

171 beam crossing.

172 The bottom pane shows the  $V_{out}$  of the two pseudo-thyristor discriminators. Again the times

173 of their leading edges are different due to different charging threshold for the two branches and

174 their trailing edges are due to reset at the end of beam crossing.

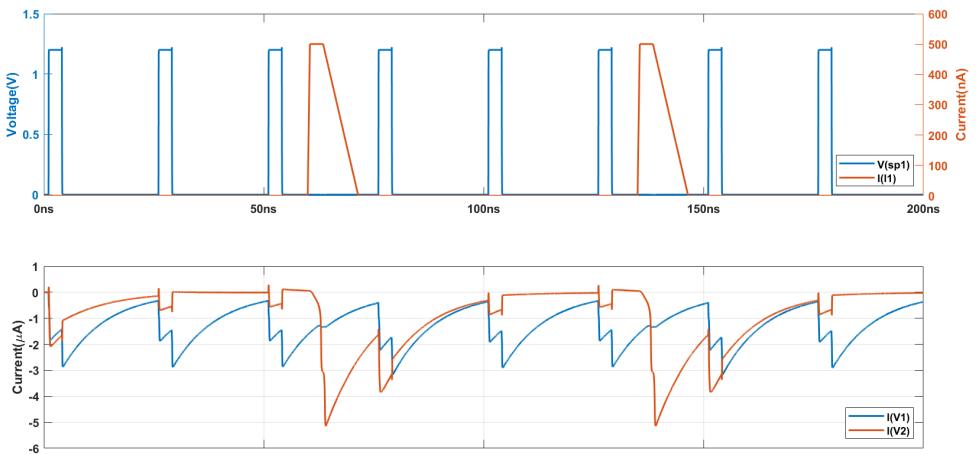

### 175 3.2 Power Consumptions

176 The bottom pane in Figure 4 shows the currents flowing through the voltage supplies  $V_1$  and  $V_2$

177 which reflect the power consumptions in different part of the circuit in schematic-level.

178 In static state, the current flowing through the pseudo-thyristor discriminators and current

179 mirrors is very small as in regular CMOS logic circuits. From the trace of  $I(V_1)$ , the current

180 flowing through power supply  $V_1$ , one can see a large current pulse due to the operations with an

181 input. The peak of  $I(V_1)$  is about  $5 \mu A$  (with the effect of the bypass capacitor and internal

182 resistance), and the average over a short time interval (75 ns in this case) is approximately  $1.1 \mu A$ .

183 The power consumption in this extreme case (33% hit occupancy) is roughly  $1.3 \mu W$ . In real

184 applications with pixelized detector, hit occupancy is typically  $<1\%$  and therefore, the power

185 consumption in this part is very small ( $<1 \mu W$ ).

Figure 4. Simulation of the current of the pseudo-thyristor discriminators

186

187 The trace  $I(V_2)$  is the current through the power supply  $V_2$ , which powers the block

188 `RstSigGen44` that produces pulses for resetting process. The peak of this trace is around  $3 \mu A$

189 and the average is about  $1.3 \mu A$  with an average power consumption of about  $1.6 \mu W$ , which

190 should be acceptable for many applications. Note that this "service" circuit consumes dominating

191 portion of the power in the entire circuit since resetting processes are repeated in all beam

192 crossings.

193 If a self-trigger self-reset scheme is utilized, much lower total power consumption can be

194 anticipated. However, as mentioned earlier, there are advantages for using periodic resetting

195 approach. It is still possible to optimize the reset pulse generating circuit to further reduce the

196 power consumption.

#### 197 **4. Conclusion and outlook**

198 A very low power consumption front end circuit, pseudo-thyristor discriminator is presented in

199 this document. Simulation results show that a power consumption  $< 10 \mu\text{W}/\text{channel}$  is achievable

200 for ASIC chips fabricated with TSMC 65 nm process.

201 The positive feedback employed in the circuit helps reach a fast switching speed with a very

202 simple topology. The CMOS structure ensures current paths are cut off at both ON and OFF state

203 resulting in zero static current, while during the switch process, relative high currents flowing

204 through the transistors bring them into higher conductivity regions to fulfill the speed

205 requirements.

206 It is worth to mention that positive feedback processes are present in amplifications inside

207 natural materials for charged particle detections, such as in gaseous detectors. The frontend circuit

208 utilizing well-controlled positive feedback can be viewed as an extension beyond the interaction

209 of the charged particle with detecting materials.

#### 210 **Acknowledgments**

211 This work has been authored by Fermi Research Alliance, LLC under Contract No. DE-AC02-

212 07CH11359 with the US Department of Energy, Office of Science, Office of High Energy

213 Physics.

#### 214 **References**

- 215 [1] G. Pellegrini et al., *Technology developments and first measurements of low gain avalanche detectors*

216 (*lgad*) *for high energy physics applications*, *Nucl. Instrum. Meth. A* **765** (2014) 12.

- 217 [2] Q. Sun et al., *The Analog Front-end for the LGAD Based Precision Timing Application in CMS ETL*,

218 Presented at [the 22nd Virtual IEEE Real Time Conference](#), zoom, 12 Oct 2020 [[arXiv: 2012.14526](#)].

- 219 [3] W. Zhang et al., *A Low-Power Time-to-Digital Converter for the CMS Endcap Timing Layer (ETL)*

220 *Upgrade*, Presented at [the 22nd Virtual IEEE Real Time Conference](#), zoom, 12 Oct 2020 [[arXiv: 2011.01222](#)].

222 [4]