# **LDPC codes - new methodologies**

by

Jan Broulík

Submitted to the Department of Applied Electronics and

Telecommunications

in fulfillment of the requirements for the degree of

Ph.D.

at the

UNIVERSITY OF WEST BOHEMIA

August 2018

Author .....

Department of Applied Electronics and Telecommunications

24 August 2018

# LDPC codes - new methodologies

by

Jan Broulím

Submitted to the Department of Applied Electronics and Telecommunications

on 24 August 2018, in fulfillment of the

requirements for the degree of

Ph.D. in Electronics

## Abstract

Low Density Parity-Check (LDPC) codes have become very popular because of their near Shannon limit performance when decoded using a probabilistic decoding algorithm. This work proposes several methodologies related to LDPC codes, including design of codes based on optimisation algorithms, mapping LDPC decoders onto parallel architectures, and improving performance of state-of-the-art decoders.

LDPC codes are random-based codes, defined in terms of parity-check matrices or Tanner graphs. Parameters of Tanner graphs, particularly a degree distribution and cycle occurrence, are crucial for probabilistic iterative decoders. Therefore, algorithms for producing good codes are needed. In this work, an algorithm for producing codes of large girth is proposed and evaluated. This algorithm is further utilised for genetic optimization methods accelerated by coarse grained parallelization. The proposed methods are evaluated using different code lengths and redundancies.

The second part of this thesis is devoted to mapping LDPC decoders on parallel systems, which are becoming very popular in modern communications systems. A general method for mapping irregular LDPC codes is proposed and evaluated on GPU platform using OpenCL and CUDA frameworks.

The last main part introduces algorithms for improving performance of LDPC codes. Two main methods are proposed, a method based on backtracking codeword estimations and a method based on using several parity-check matrices. The second method, so called Mutational LDPC (MLDPC), utilises several parity-check matrices produced by slight mutations which run in parallel decoders. Information from all decoders is then used to provide the codeword estimation. The MLDPC is further modified using information entropy and so called radius which provide the additional improvement of the Bit Error Rate.

Thesis Supervisor: Doc. Dr. Vjačeslav Georgiev

Thesis Co-Supervisor: prof. RNDr. Tomáš Kaiser, DSc.

## Acknowledgments

I would thank to my supervisors, Vjaceslav Georgiev and Tomas Kaiser, to take the responsibility of this work and for giving me the opportunity to learn and develop new skills in interesting fields.

I am particularly grateful for the assistance and useful discussions given by Alexander Ayriyan, Stefan Berezny, Nikolaos Boulgouris, Sima Davarzani, Hovik Grigorian, colleagues at the Faculty of Electrical Engineering in Pilsen, Institute of Experimental and Applied Physics in Prague, Joint Institute of Nuclear Research, especially the HybriLIT group, people involved in GBT Project at CERN, and specialists at Brunel Language Centre.

My thanks also go to my family for providing the support during my study.

## Declaration

I hereby declare that this thesis is my original work and that I have not used any sources other than those listed. I further declare that only legal and licensed software has been used. This thesis has not been submitted at any other institution in order to obtain a degree.

.....

# Contents

|          |                                                     |           |

|----------|-----------------------------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>                                 | <b>15</b> |

| <b>2</b> | <b>Error correction coding</b>                      | <b>18</b> |

| 2.1      | History of error correction coding . . . . .        | 18        |

| 2.2      | Shannon model . . . . .                             | 19        |

| 2.3      | Definitions . . . . .                               | 20        |

| 2.3.1    | Generator matrix . . . . .                          | 22        |

| 2.3.2    | Parity-check matrix . . . . .                       | 22        |

| 2.3.3    | Systematic form of coding . . . . .                 | 22        |

| 2.3.4    | Non-binary codes . . . . .                          | 23        |

| 2.3.5    | Communication channel models . . . . .              | 23        |

| <b>3</b> | <b>LDPC codes</b>                                   | <b>25</b> |

| 3.1      | Background . . . . .                                | 25        |

| 3.2      | Encoding . . . . .                                  | 28        |

| 3.3      | Tanner graphs . . . . .                             | 28        |

| 3.4      | Decoding . . . . .                                  | 29        |

| <b>4</b> | <b>Construction of LDPC codes</b>                   | <b>39</b> |

| 4.1      | Generating LDPC matrices with large girth . . . . . | 40        |

| 4.2      | Genetic optimization of LDPC codes . . . . .        | 46        |

| 4.2.1    | Optimization algorithm principle . . . . .          | 46        |

| 4.2.2    | Tanner graph mutations . . . . .                    | 46        |

|          |                                                               |            |

|----------|---------------------------------------------------------------|------------|

| 4.2.3    | Recombination of Tanner graphs . . . . .                      | 47         |

| 4.2.4    | Fitness function . . . . .                                    | 50         |

| 4.2.5    | Parallelization . . . . .                                     | 53         |

| 4.3      | Application of optimization tasks . . . . .                   | 55         |

| 4.3.1    | Sample optimization using mutations . . . . .                 | 55         |

| 4.3.2    | Long run optimization of LDPC (128,64) code . . . . .         | 57         |

| 4.3.3    | Comparison of the optimized LDPC code with the RS code . .    | 59         |

| 4.3.4    | Evaluation of parallelization . . . . .                       | 59         |

| <b>5</b> | <b>Mapping LDPC decoder onto parallel architectures</b>       | <b>62</b>  |

| 5.1      | A general parallelization of LDPC decoders . . . . .          | 63         |

| 5.2      | OpenCL and CUDA implementation . . . . .                      | 65         |

| 5.3      | Experimental evaluation . . . . .                             | 68         |

| <b>6</b> | <b>Improving performance of LDPC decoders</b>                 | <b>72</b>  |

| 6.1      | Belief Propagation Based on Estimation Backtracking . . . . . | 72         |

| 6.1.1    | Algorithm description . . . . .                               | 75         |

| 6.1.2    | Memory requirements . . . . .                                 | 75         |

| 6.1.3    | Complexity requirements . . . . .                             | 77         |

| 6.1.4    | Comprehensive AWGN simulations . . . . .                      | 77         |

| 6.2      | Mutational LDPC decoding . . . . .                            | 81         |

| 6.2.1    | Principle of Mutational LDPC decoding . . . . .               | 82         |

| 6.2.2    | Entropy based algorithm (MLDPCe) . . . . .                    | 84         |

| 6.2.3    | Metric based algorithm (MLDPCr) . . . . .                     | 85         |

| 6.2.4    | Memory and complexity requirements . . . . .                  | 89         |

| <b>7</b> | <b>Conclusions</b>                                            | <b>94</b>  |

| <b>A</b> | <b>On GPU implementation of LDPC decoder</b>                  | <b>96</b>  |

| <b>B</b> | <b>Fully parallel LDPC decoder implementation in FPGA</b>     | <b>99</b>  |

| <b>C</b> | <b>Burst correctability of optimized codes</b>                | <b>105</b> |

|                                                                     |            |

|---------------------------------------------------------------------|------------|

| <b>D On Belief Propagation based on the Estimation Backtracking</b> | <b>107</b> |

| <b>E MLDPC BER simulations</b>                                      | <b>111</b> |

| <b>F Feature based classification</b>                               | <b>113</b> |

# List of Figures

|      |                                                                                                                                                                                                  |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

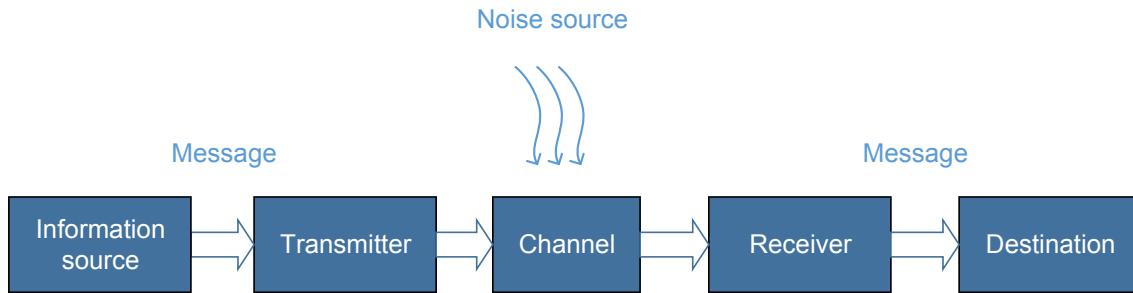

| 2-1  | Shannon's conceptual diagram of the information transmission between the source and the destination. . . . .                                                                                     | 19 |

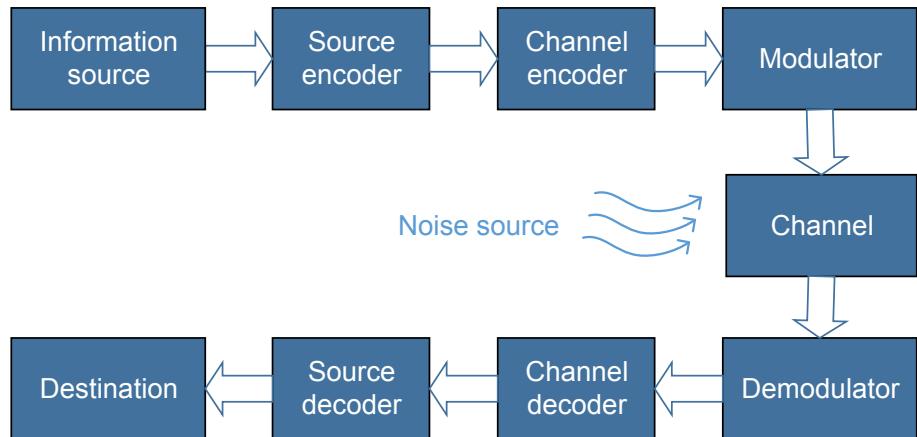

| 2-2  | Extended diagram of the communication chain. . . . .                                                                                                                                             | 19 |

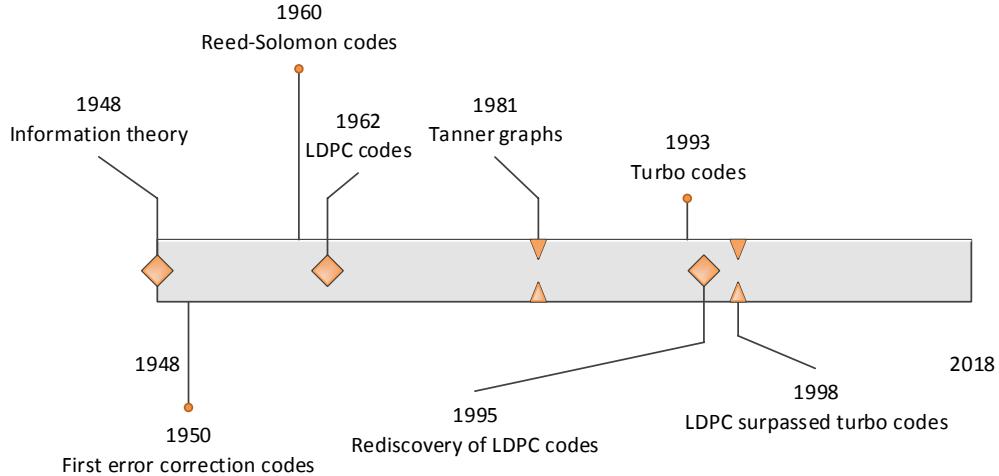

| 2-3  | Historical milestones in coding theory. . . . .                                                                                                                                                  | 20 |

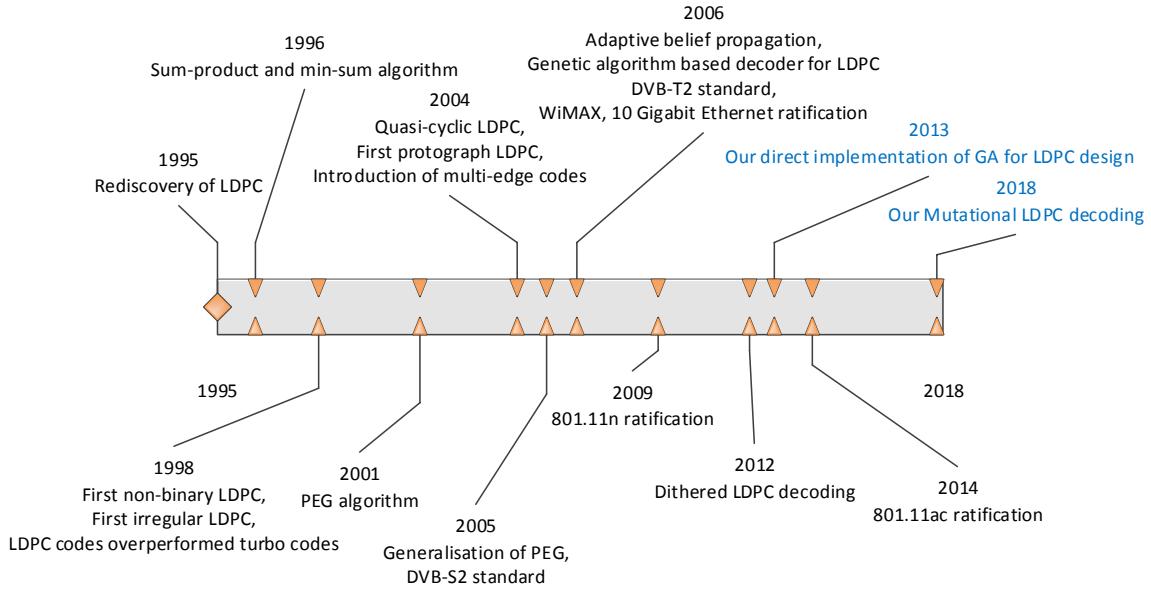

| 3-1  | Historical milestones related to LDPC codes. . . . .                                                                                                                                             | 27 |

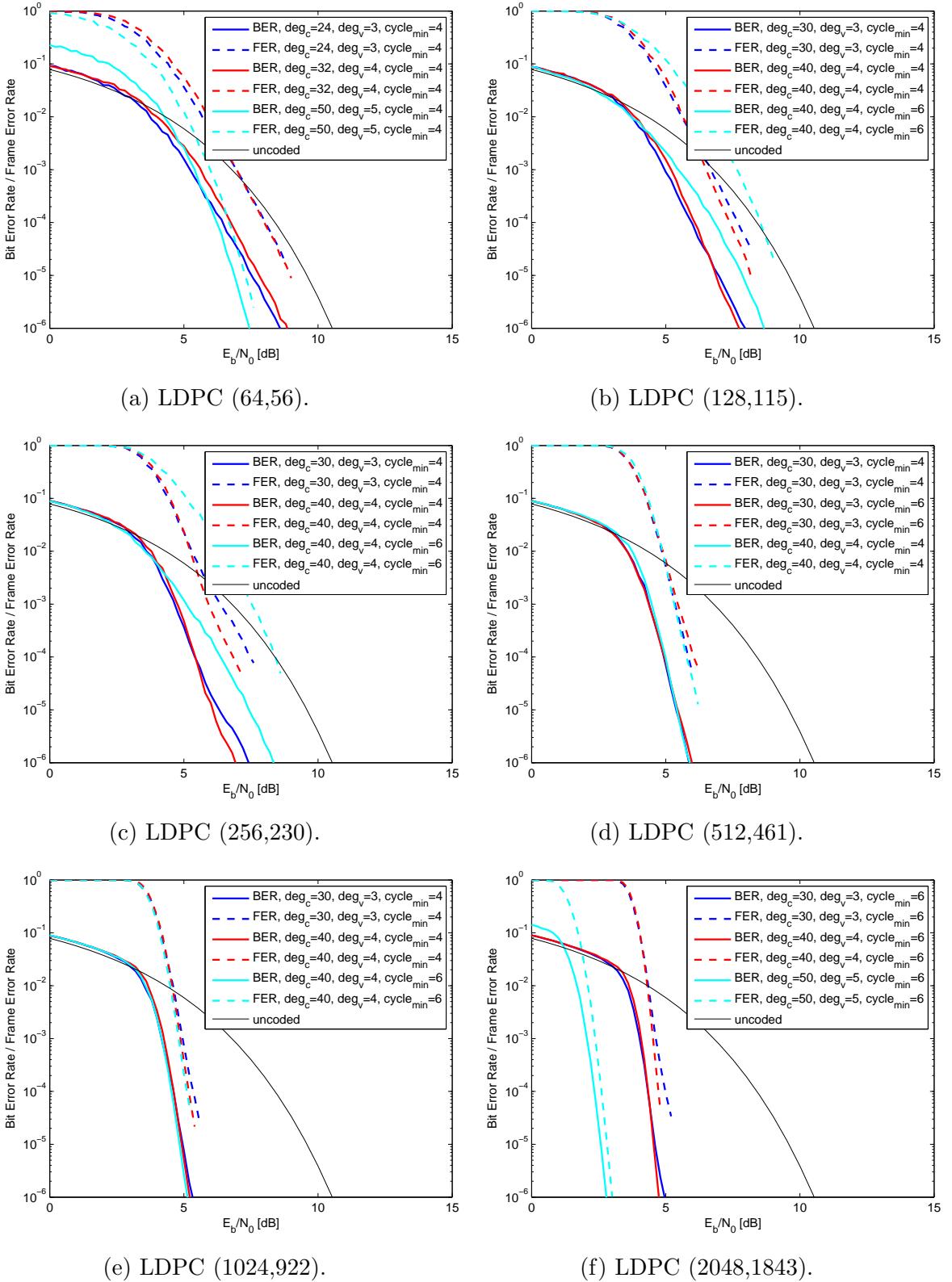

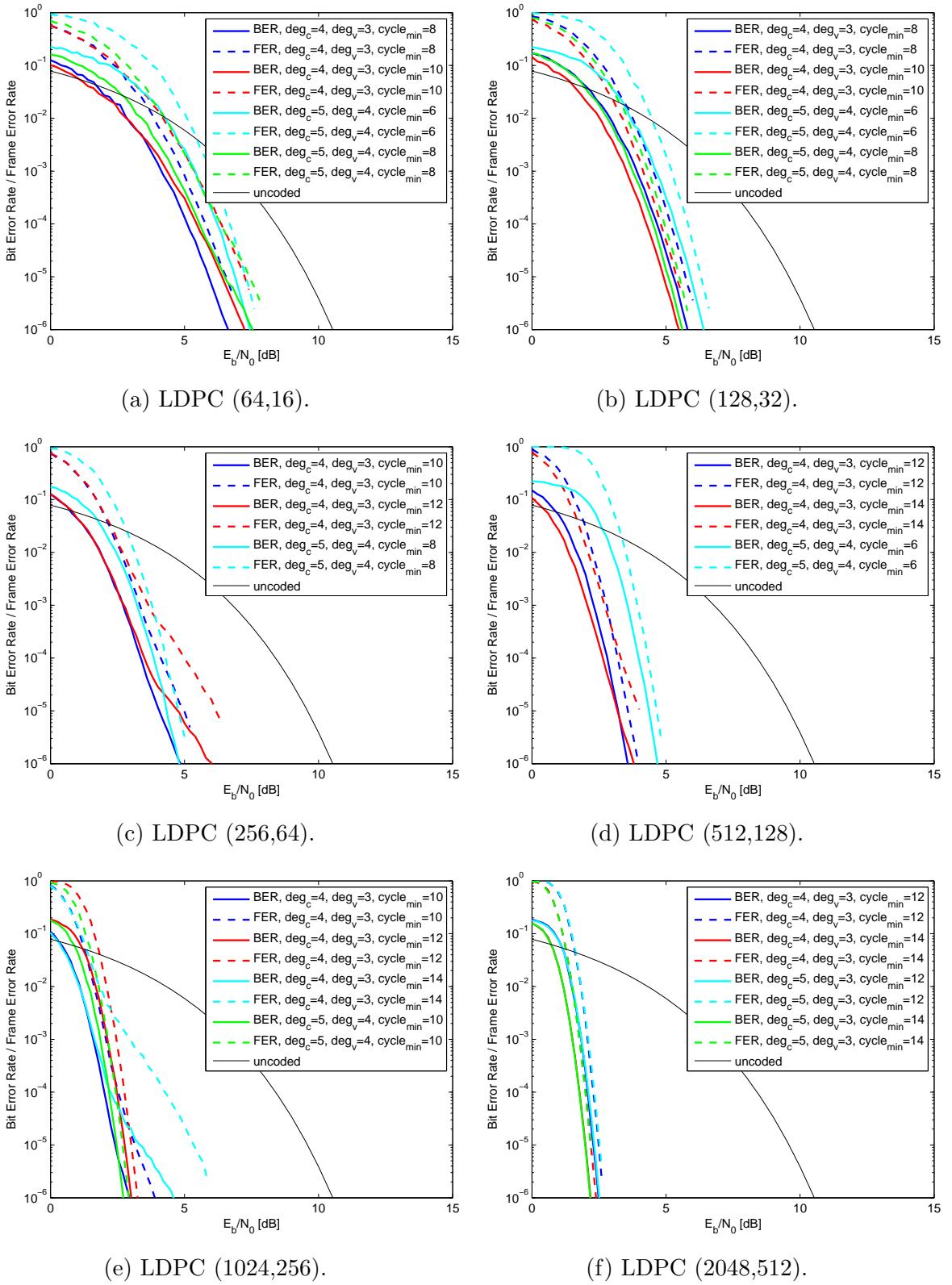

| 4-1  | Correction performance of 10% redundancy codes (12.5% for $n=64$ ). . . . .                                                                                                                      | 42 |

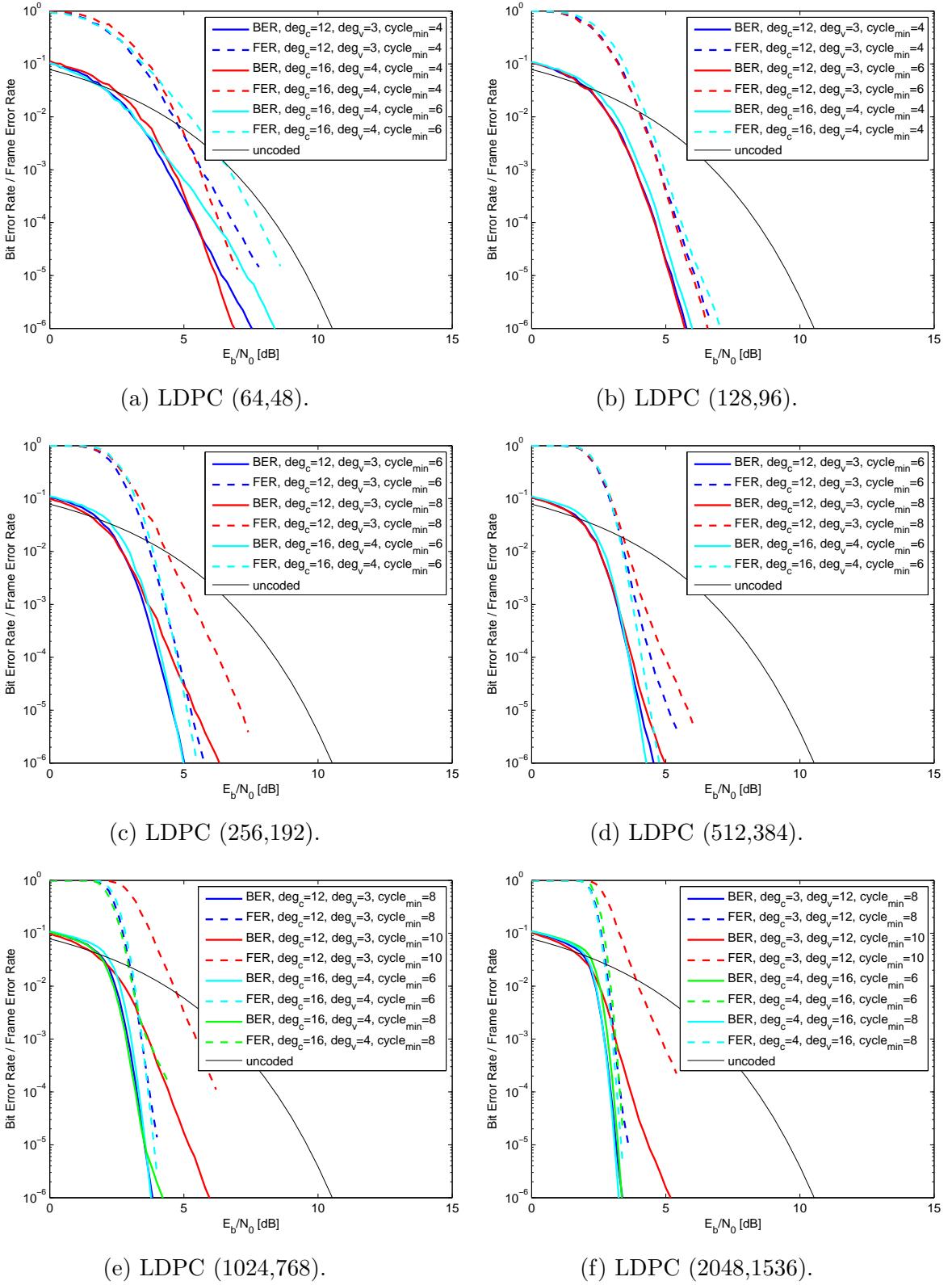

| 4-2  | Correction performance of 25% redundancy codes. . . . .                                                                                                                                          | 43 |

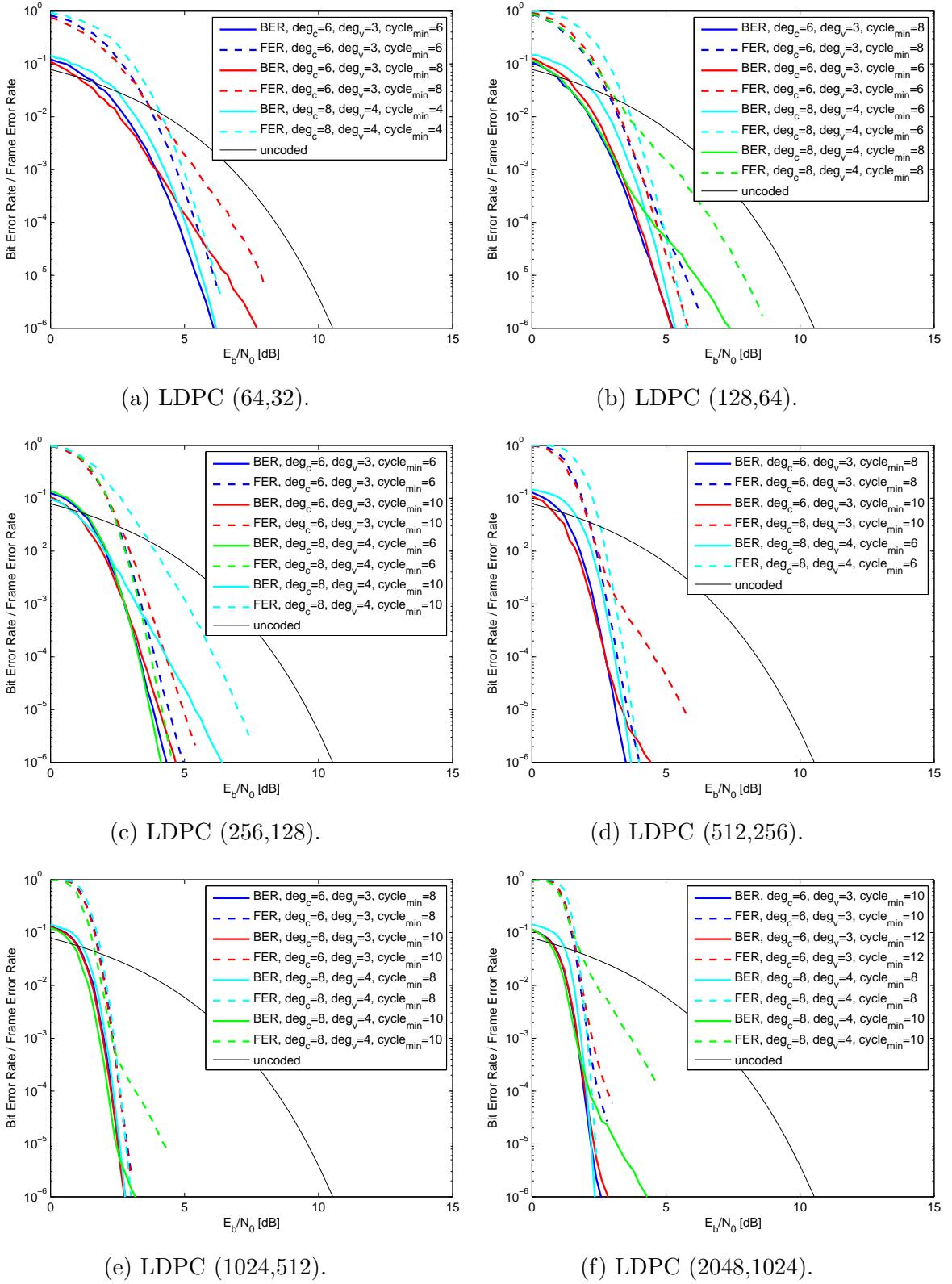

| 4-3  | Correction performance of 50% redundancy codes. . . . .                                                                                                                                          | 44 |

| 4-4  | Correction performance of 75% redundancy codes. . . . .                                                                                                                                          | 45 |

| 4-5  | A diagram of the optimization process. . . . .                                                                                                                                                   | 46 |

| 4-6  | Breaking cycles in the Tanner graph as an example. . . . .                                                                                                                                       | 47 |

| 4-7  | Adding a new edge connected with the node $u : d_G(u) = 1$ as an example. . . . .                                                                                                                | 48 |

| 4-8  | Generating the chromosome. Numbers are node degress corresponding to the selected part of the graph. . . . .                                                                                     | 50 |

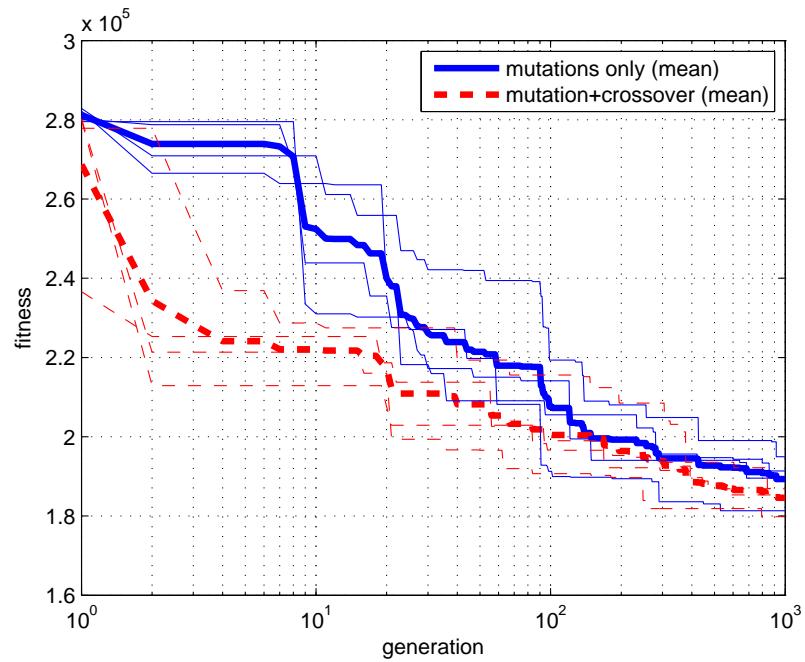

| 4-9  | A demonstrative evolution of the fitness function. The optimization using only mutations is compared to the optimization using the combination of the mutations and crossover operators. . . . . | 54 |

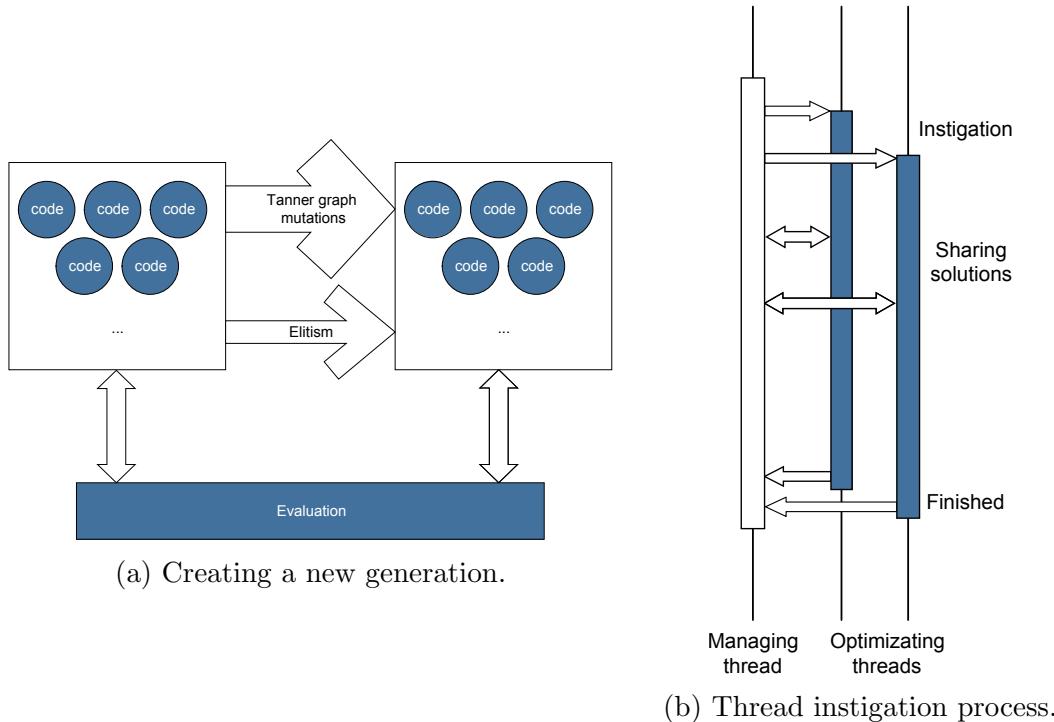

| 4-10 | The principle of the optimization algorithm. . . . .                                                                                                                                             | 54 |

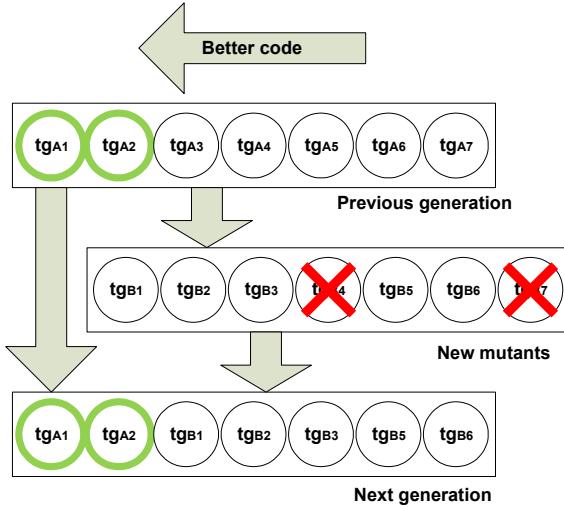

| 4-11 | Reproducing the next generations of Tanner graphs. . . . .                                                                                                                                       | 55 |

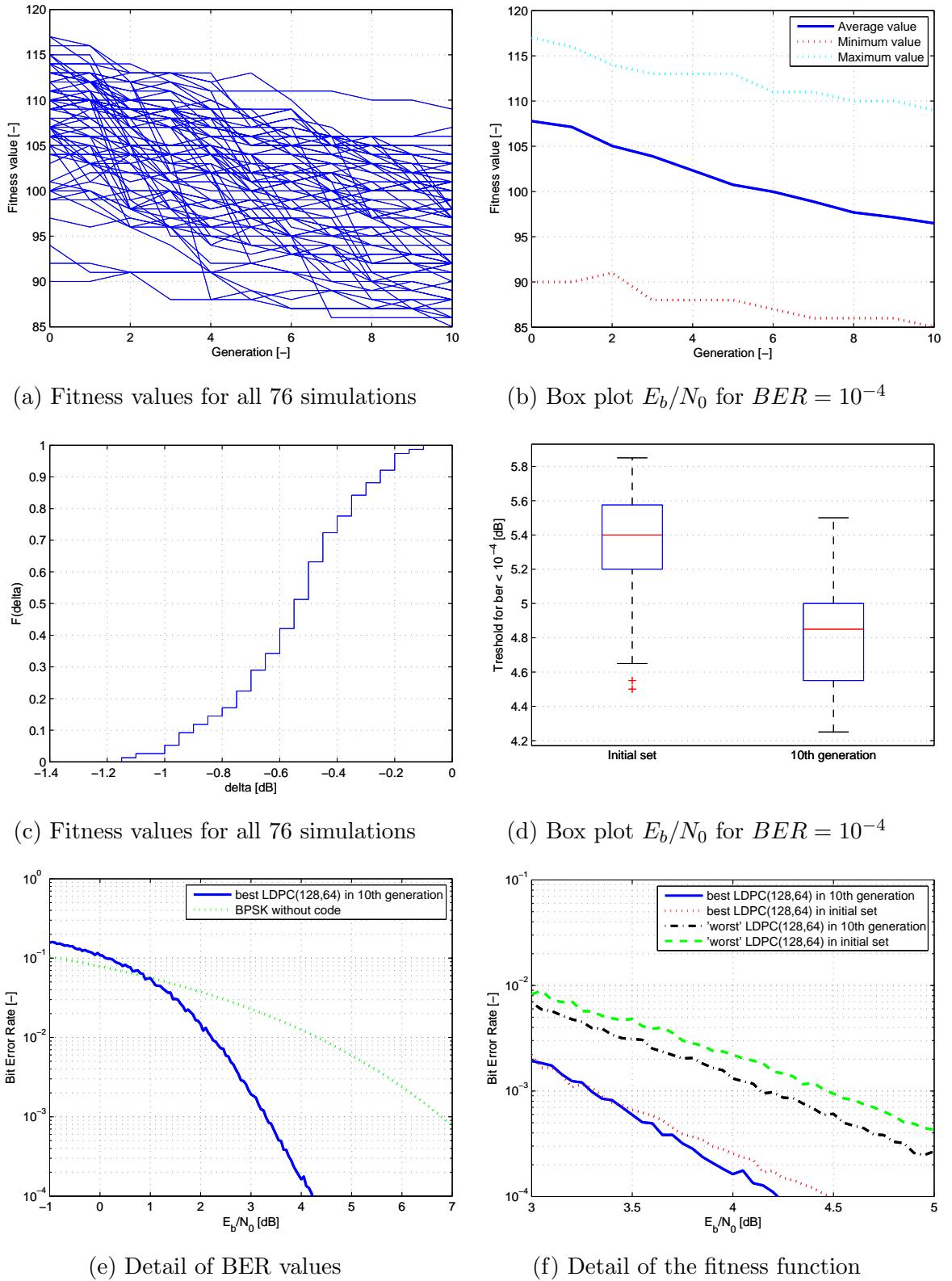

| 4-12 | An optimization task using Tanner graph mutations . . . . .                                                                                                                                      | 56 |

|                                                                                                                                                                                                                                                                                                                              |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

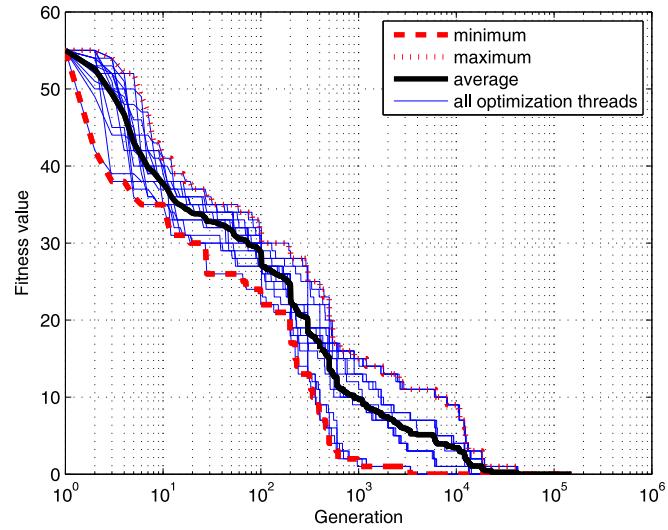

| 4-13 The optimization task run on (128,64) LDPC code to provide the best performance at 10 decoding iterations. The initial population were generated with the use of Algorithm 5. . . . .                                                                                                                                   | 57 |

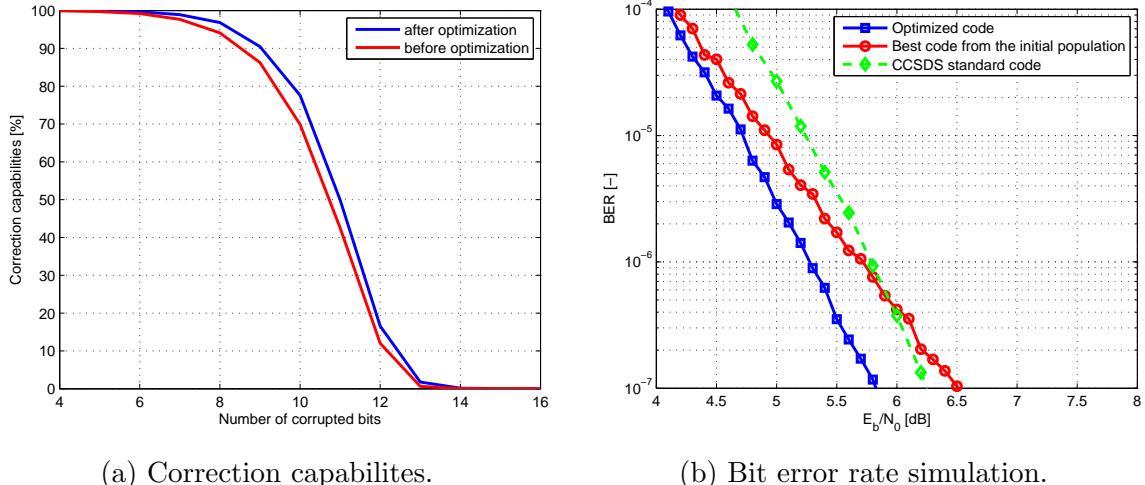

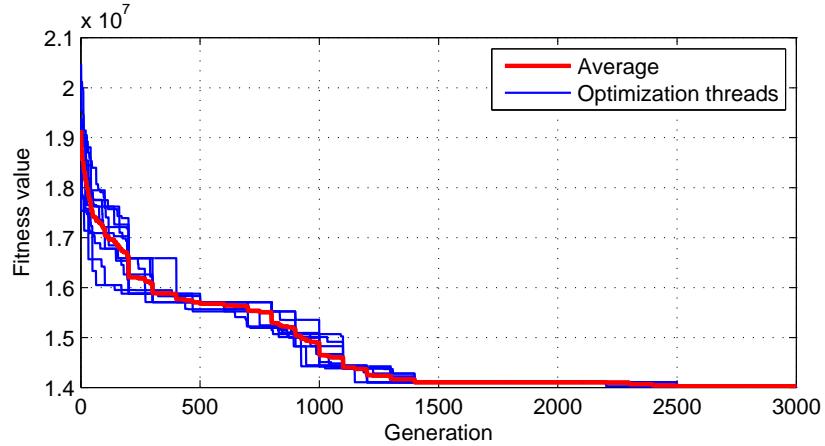

| 4-14 Evolution of fitness value of the optimization task LDPC (128,64), 10 decoding iterations). . . . .                                                                                                                                                                                                                     | 58 |

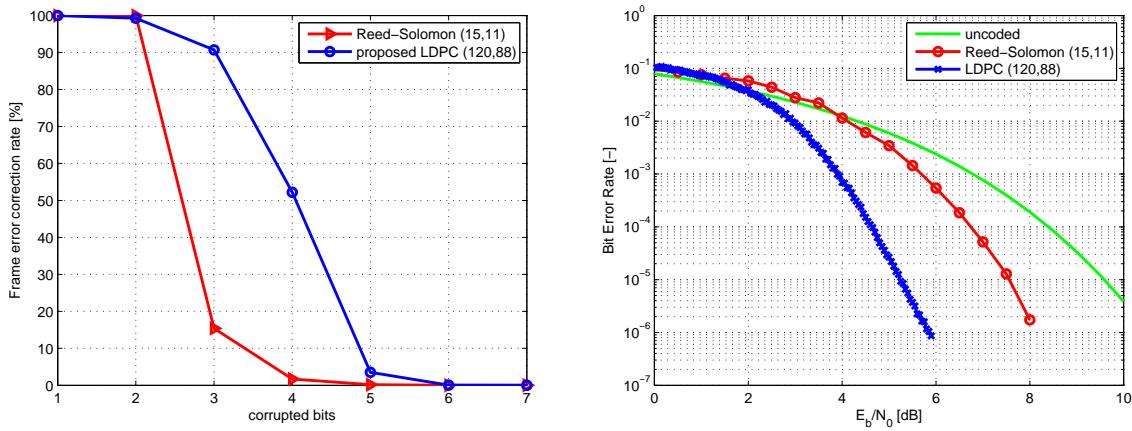

| 4-15 Comparison of the genetically designed LDPC (120,88) with the RS (15,11) code. . . . .                                                                                                                                                                                                                                  | 59 |

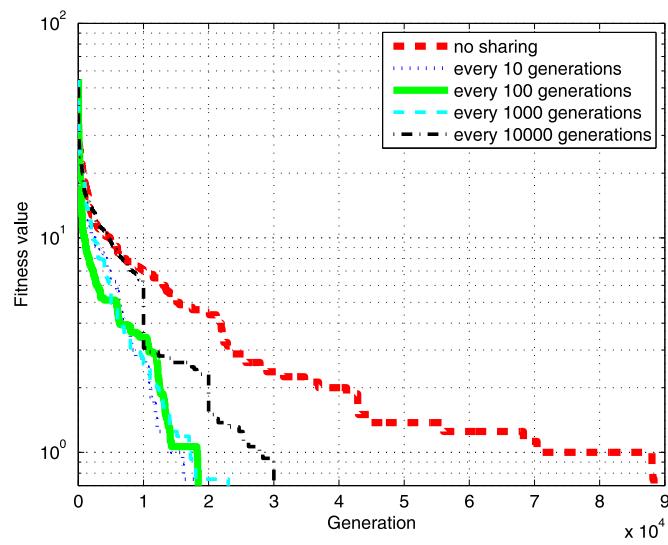

| 4-16 Fitness values for $L = 4$ and $K = 100$ . . . . .                                                                                                                                                                                                                                                                      | 61 |

| 4-17 Fitness values for $L = 4$ and different sharing periods. . . . .                                                                                                                                                                                                                                                       | 61 |

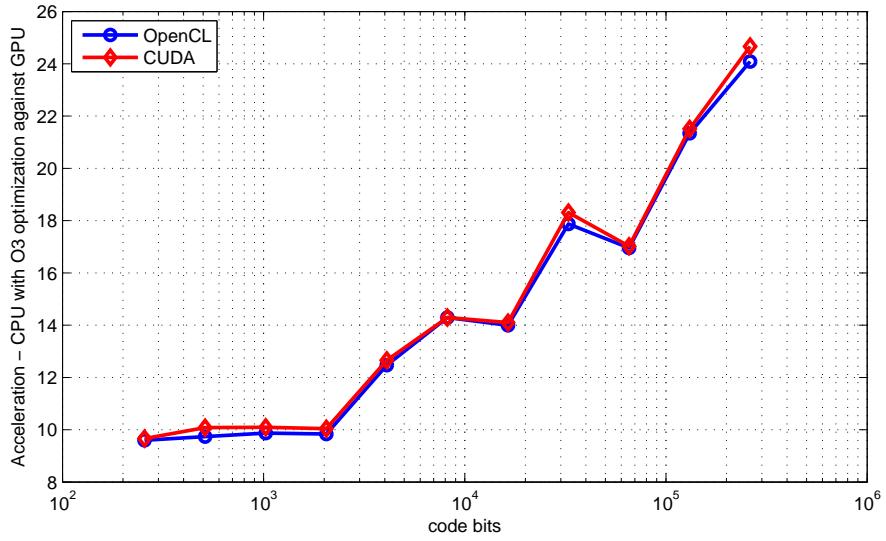

| 5-1 The acceleration dependence on the length of the code. Comparison for OpenCL and CUDA frameworks (local group of 512 threads and 100 decoders working in parallel) against CPU implementation using C++ compiler with O3 optimization. Time was measured for 10000 decoded codewords at $E_b/N_0 = 2\text{dB}$ . . . . . | 70 |

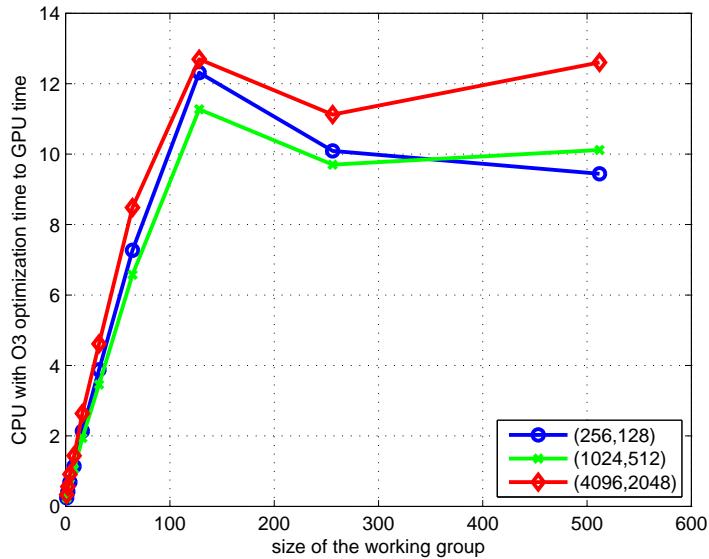

| 5-2 The acceleration dependence on the block (working group) for 100 decoders running in parallel. . . . .                                                                                                                                                                                                                   | 70 |

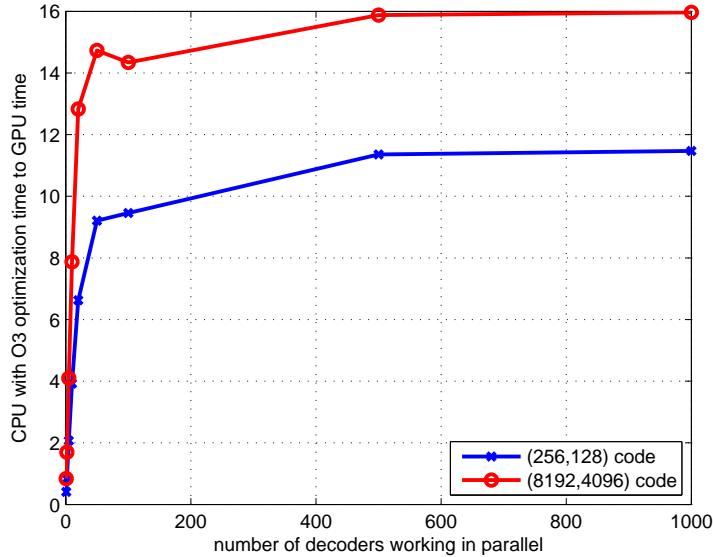

| 5-3 Acceleration dependence on the number of decoders working in parallel when the size of the working group is 512. . . . .                                                                                                                                                                                                 | 71 |

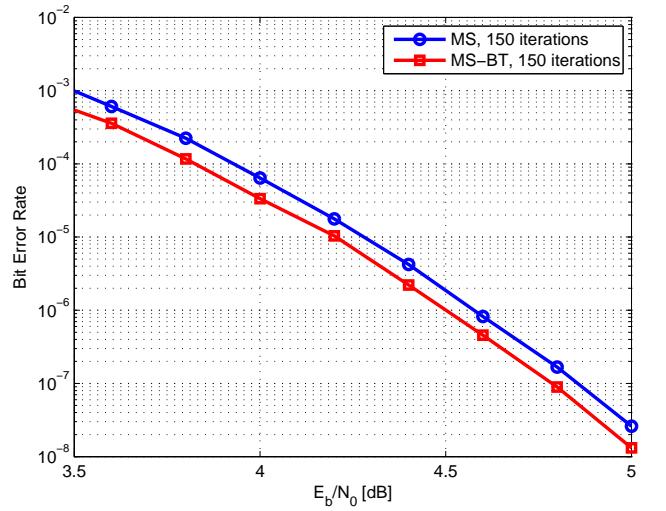

| 6-1 Bit error rate performance simulated on NASA CCSDS (256,128) standard. . . . .                                                                                                                                                                                                                                           | 78 |

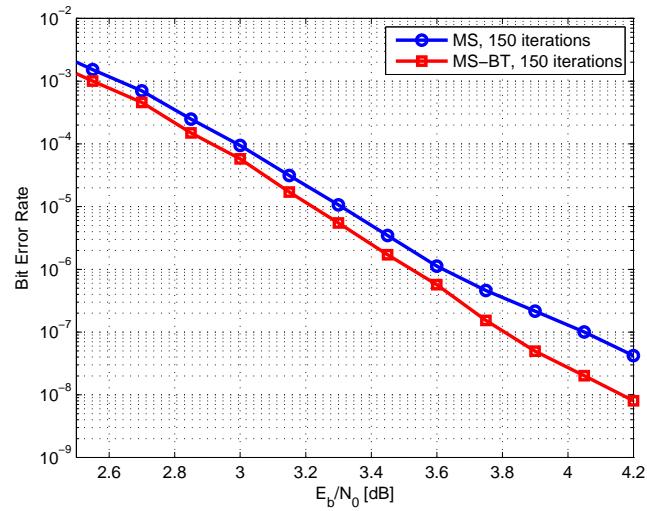

| 6-2 Bit error rate performance simulated on MacKay's (504,252) code. . . . .                                                                                                                                                                                                                                                 | 79 |

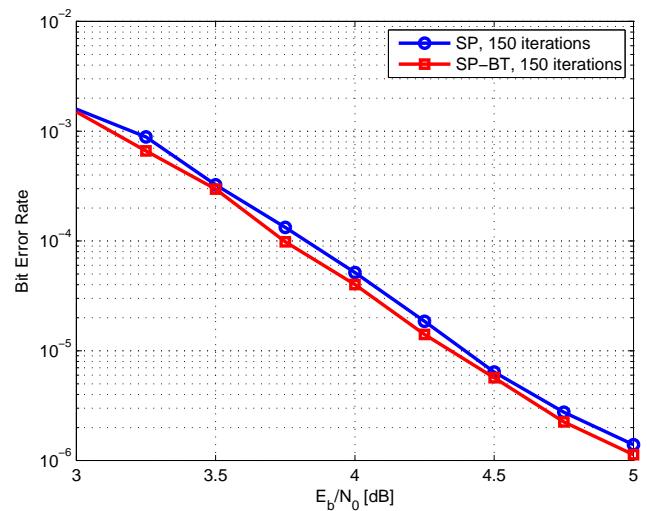

| 6-3 Bit error rate simulated on our irregular LDPC (128,64) code. The original SP algorithm and the improved SP-BT are compared. . . . .                                                                                                                                                                                     | 79 |

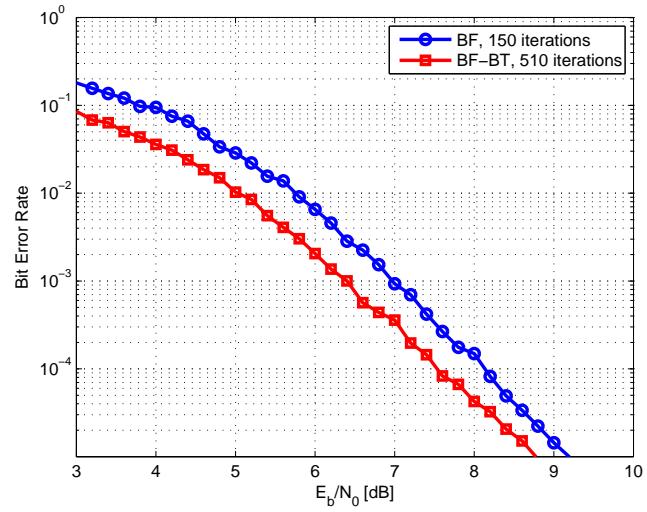

| 6-4 Bit error rate simulated on our irregular LDPC (128,64) code. The original Bit-Flipping algorithm and the improved Bit-Flipping algorithm with backtracking of estimations are compared. . . . .                                                                                                                         | 80 |

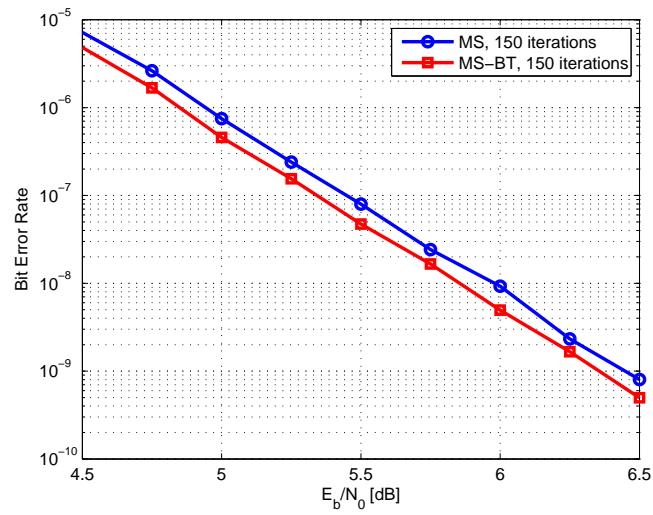

| 6-5 Bit error rate simulated on our irregular LDPC (128,64) code. The original Min-Sum algorithm and improved Min-Sum algorithm with backtracking of estimations are compared. . . . .                                                                                                                                       | 80 |

|      |                                                                                                                                                                                                                                                         |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

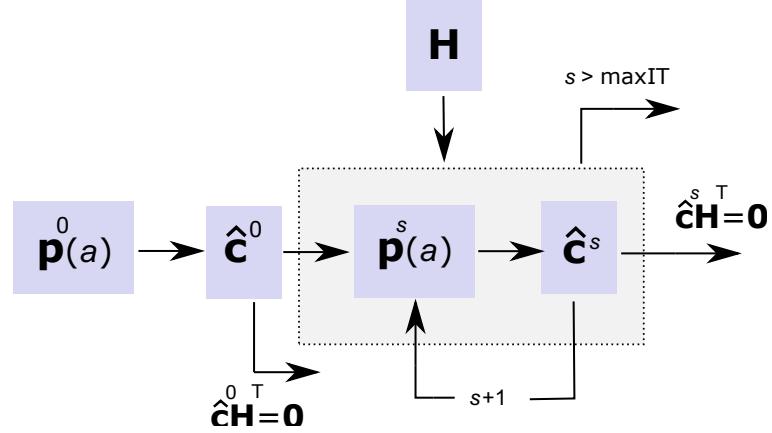

| 6-6  | State-of-the art LDPC decoding scheme. . . . .                                                                                                                                                                                                          | 84  |

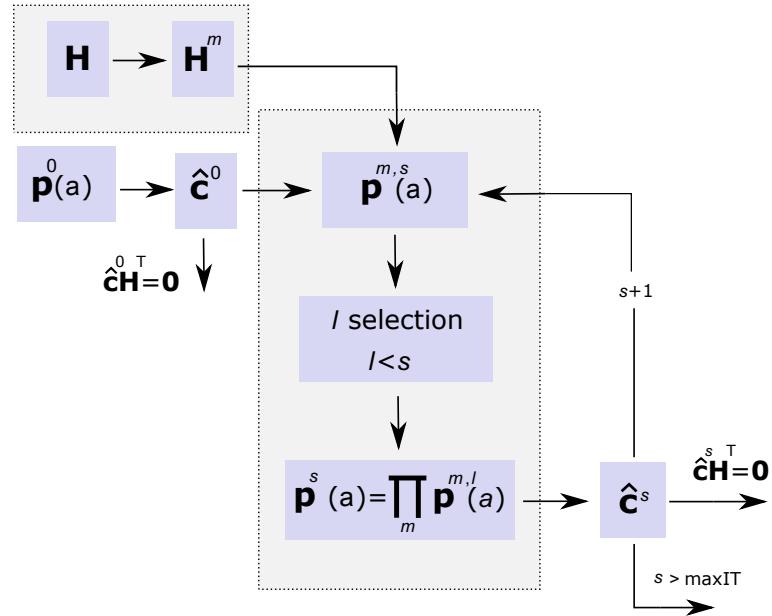

| 6-7  | The proposed MLDPC scheme. . . . .                                                                                                                                                                                                                      | 84  |

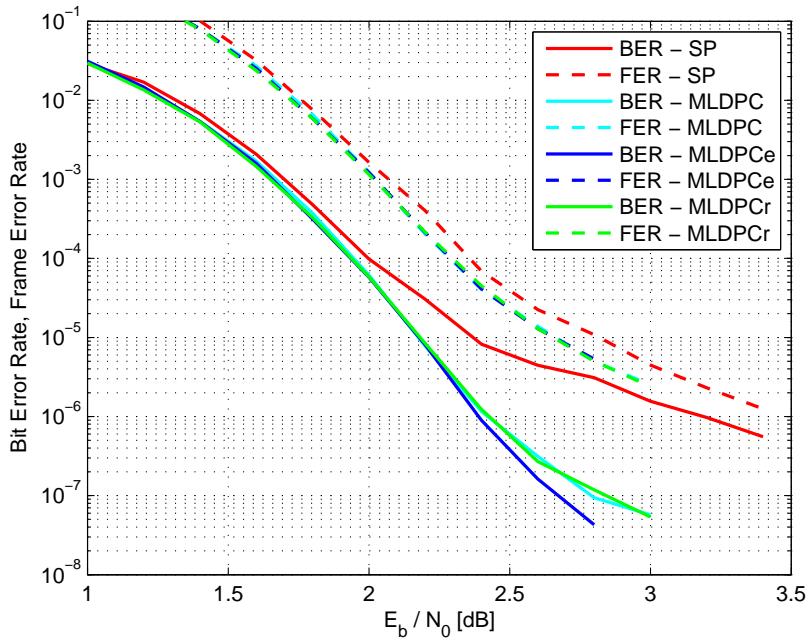

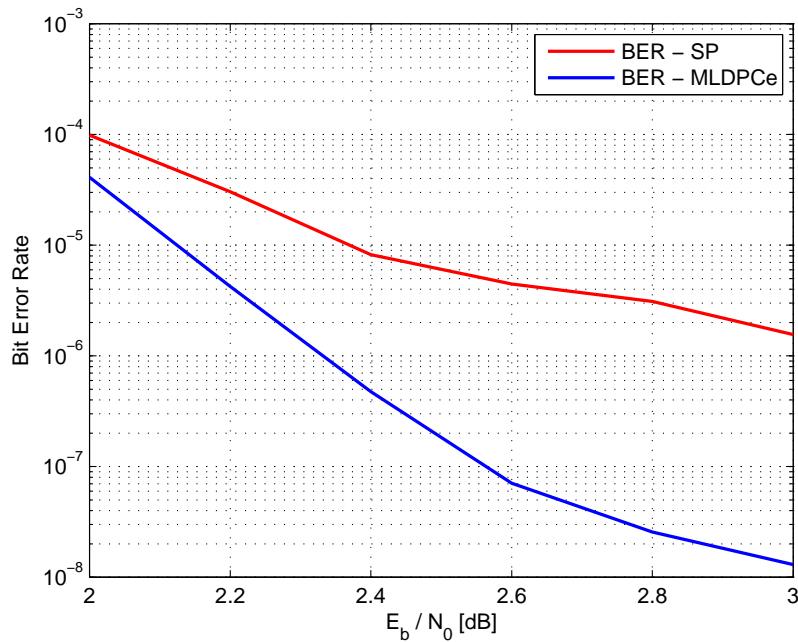

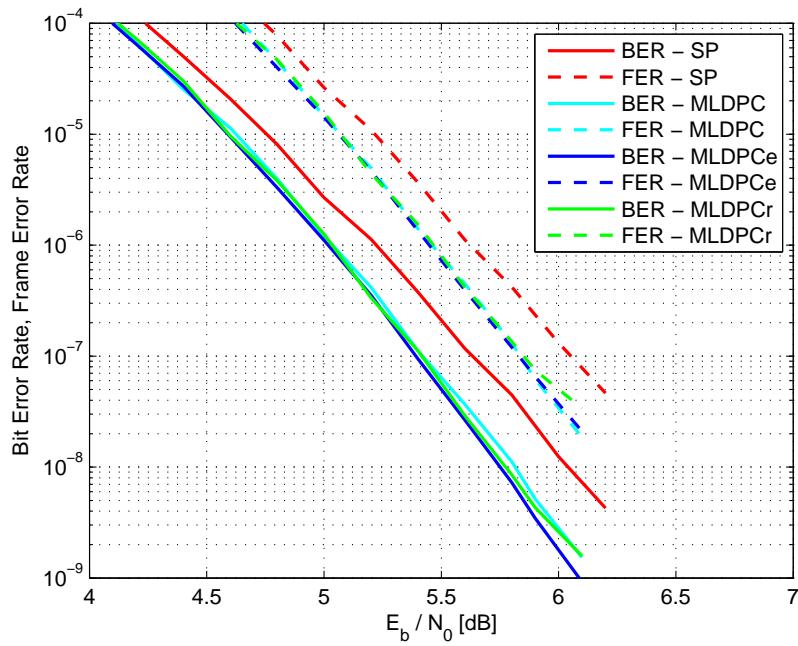

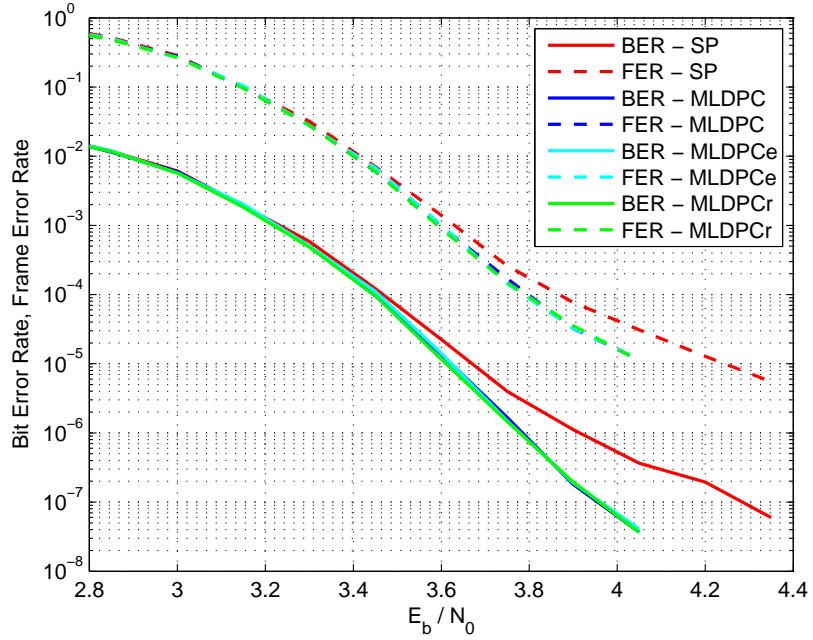

| 6-8  | Simulation on WiMAX 1056 code, 4 additional decoders were used. .                                                                                                                                                                                       | 88  |

| 6-9  | Simulation on WiMAX 1056 code, 19 additional decoders were used. .                                                                                                                                                                                      | 89  |

| 6-10 | Simulation on CCSDS 128 code, 4 additional decoders were used. . .                                                                                                                                                                                      | 89  |

| 6-11 | Simulation on WiMAX 2304 code, 4 additional decoders were used. .                                                                                                                                                                                       | 90  |

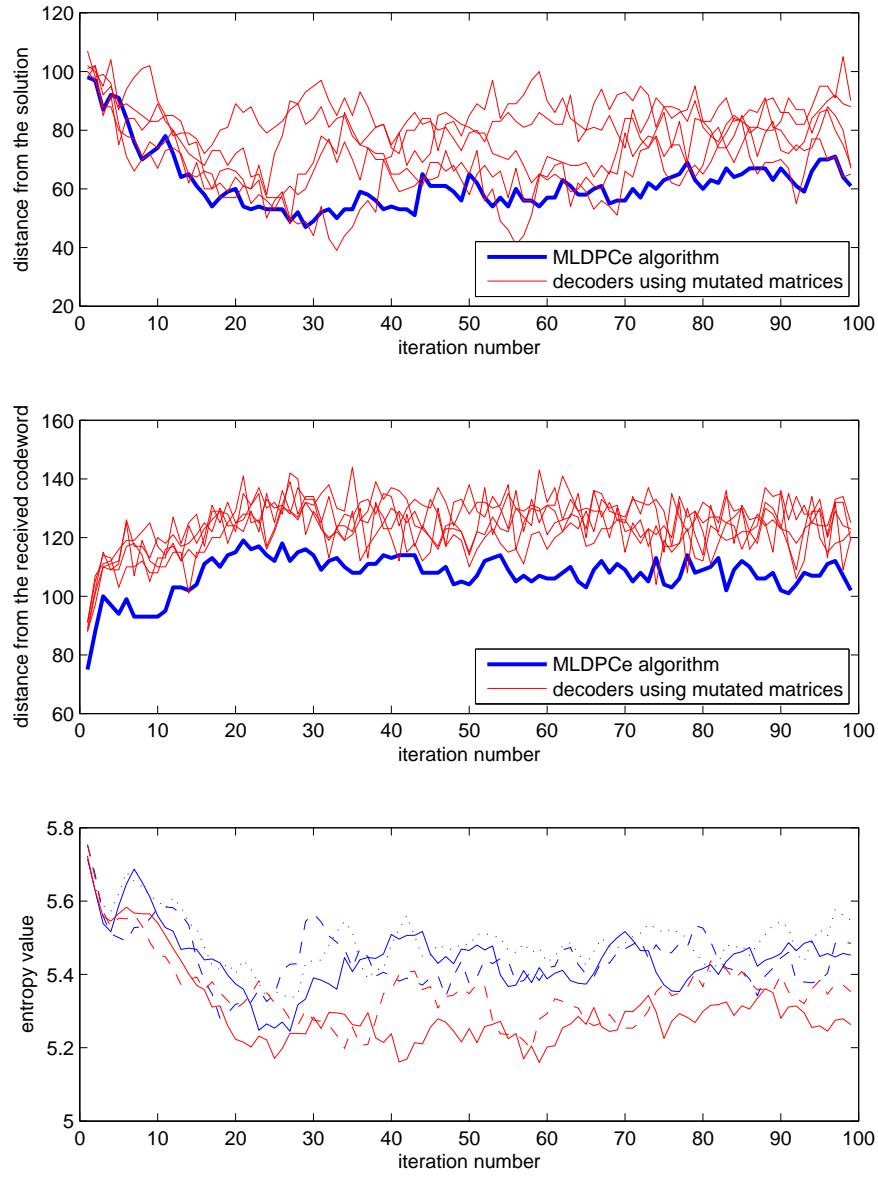

| 6-12 | The Evolution of entropy values and distance values when the decoder fails in the convergency. . . . .                                                                                                                                                  | 91  |

| 6-13 | The Evolution of entropy values and distance values when the decoder oscillates. . . . .                                                                                                                                                                | 92  |

| A-1  | Parity-check matrix divided into pages . . . . .                                                                                                                                                                                                        | 97  |

| A-2  | Parity-check matrix and the principle of the parallelization . . . . .                                                                                                                                                                                  | 97  |

| A-3  | Tanner graph of the LDPC (14,7) code. . . . .                                                                                                                                                                                                           | 97  |

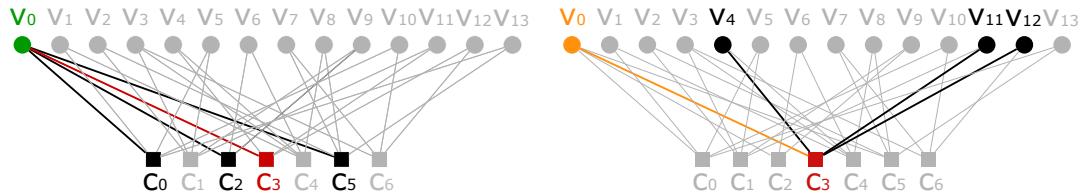

| B-1  | Flowchart of the decoder synthesis. . . . .                                                                                                                                                                                                             | 102 |

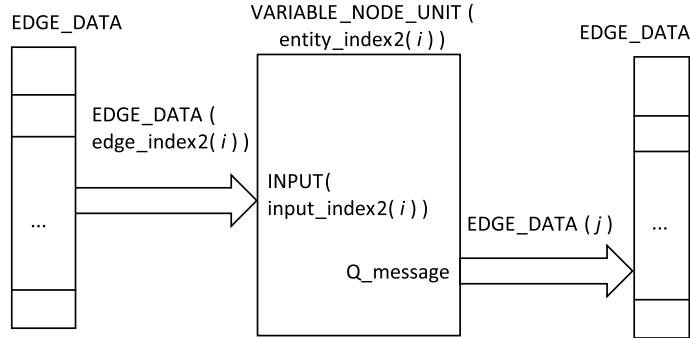

| B-2  | Variable node unit in the relation of message passing, where $i$ is in $0...ctr1 - 1$ , $ctr1$ is the value after running Algorithm 20 and $j$ is in $0...K - 1$ . . . . .                                                                              | 102 |

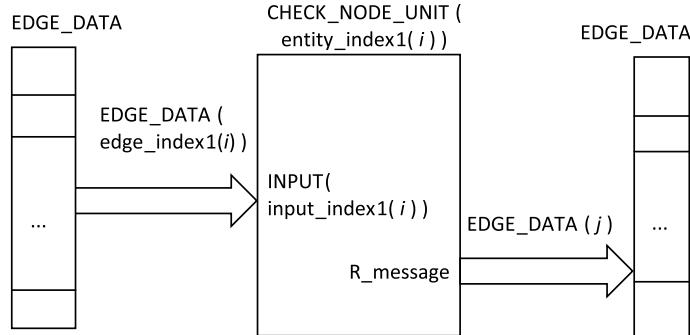

| B-3  | Check node unit in the relation of message passing, where $i$ is $0...ctr2 - 1$ , $ctr2$ is the value after running Algorithm 20 and $j$ is $0...K - 1$ . . .                                                                                           | 102 |

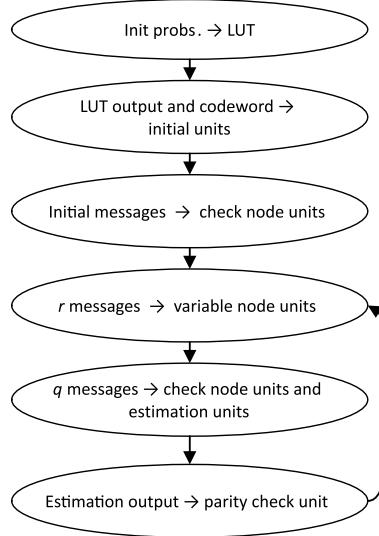

| B-4  | Simplified state diagram of the decoding algorithm. . . . .                                                                                                                                                                                             | 103 |

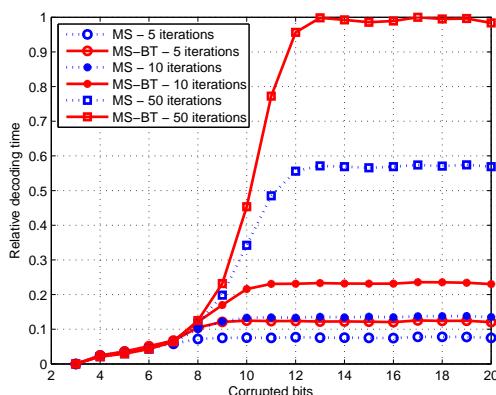

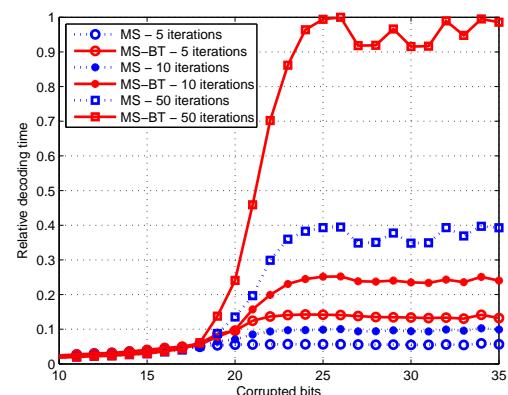

| D-1  | Relative decoding time . . . . .                                                                                                                                                                                                                        | 107 |

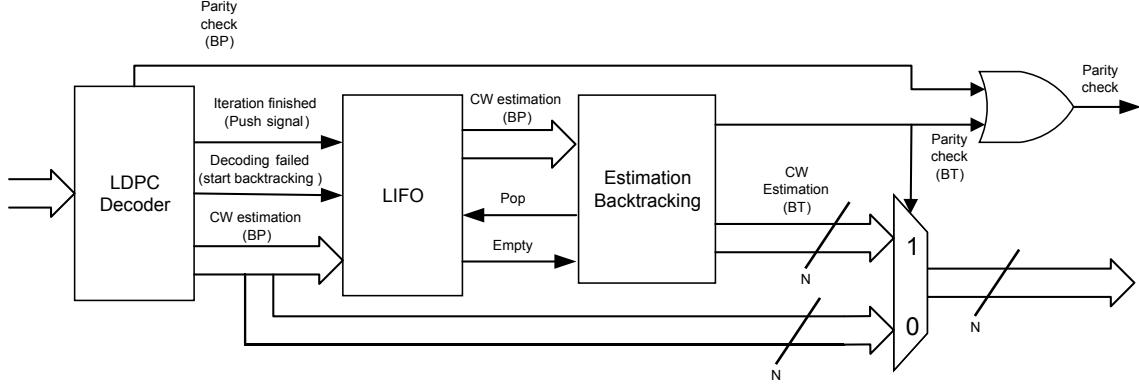

| D-2  | Hardware architecture outline. . . . .                                                                                                                                                                                                                  | 108 |

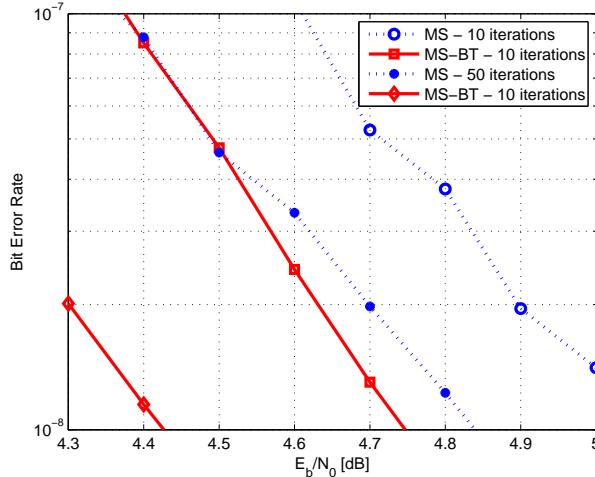

| D-3  | Bit error rate simulated on irregular MacKay's (504,252) code compared for different number of iterations. The values are calculated from 300 codewords for which the iterative decoding algorithm failed at particular Signal-to-Noise Ratios. . . . . | 109 |

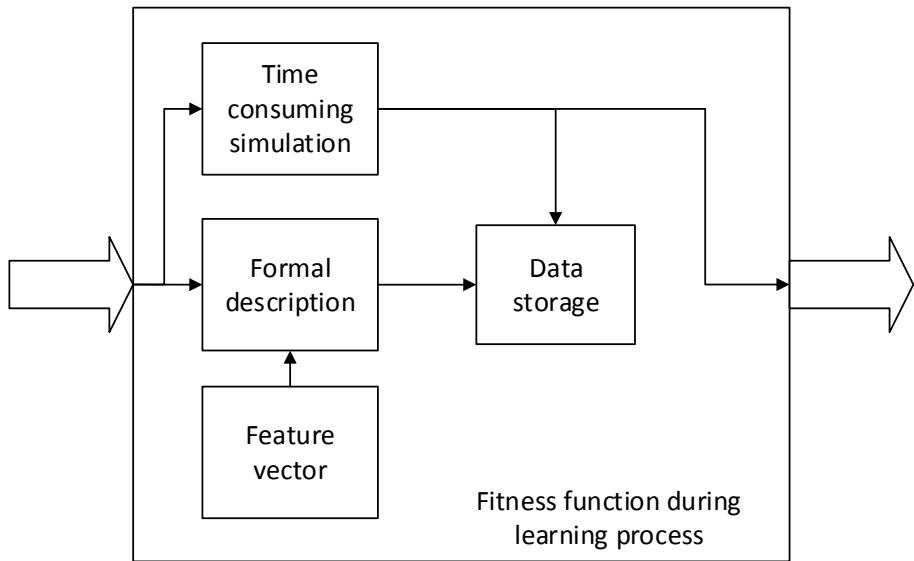

| F-1  | The algorithm of learning a feature based classifier. . . . .                                                                                                                                                                                           | 115 |

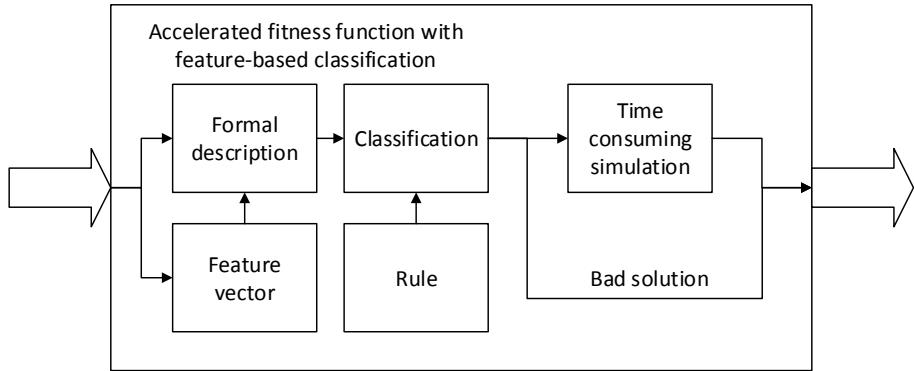

| F-2  | The algorithm for accelerating the evaluation function. . . . .                                                                                                                                                                                         | 115 |

|     |                                                                       |     |

|-----|-----------------------------------------------------------------------|-----|

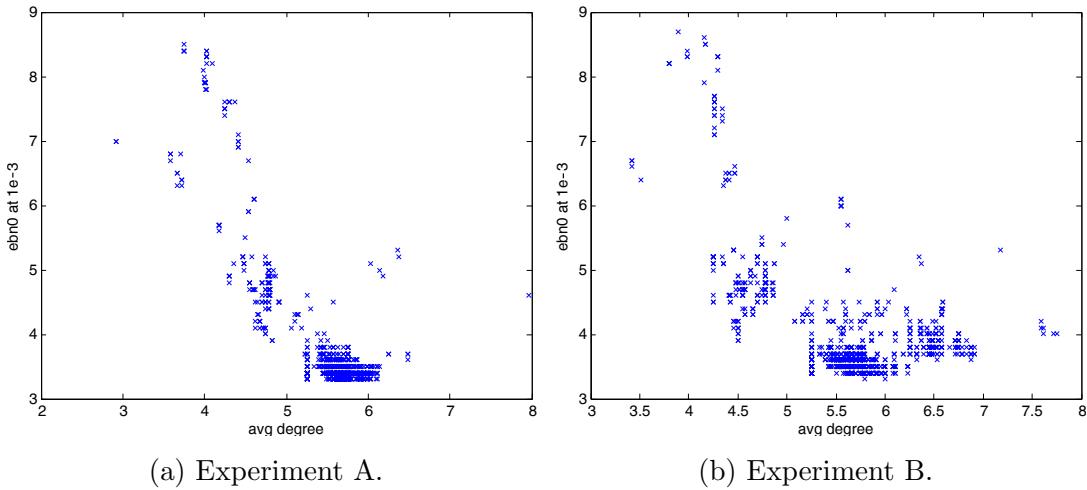

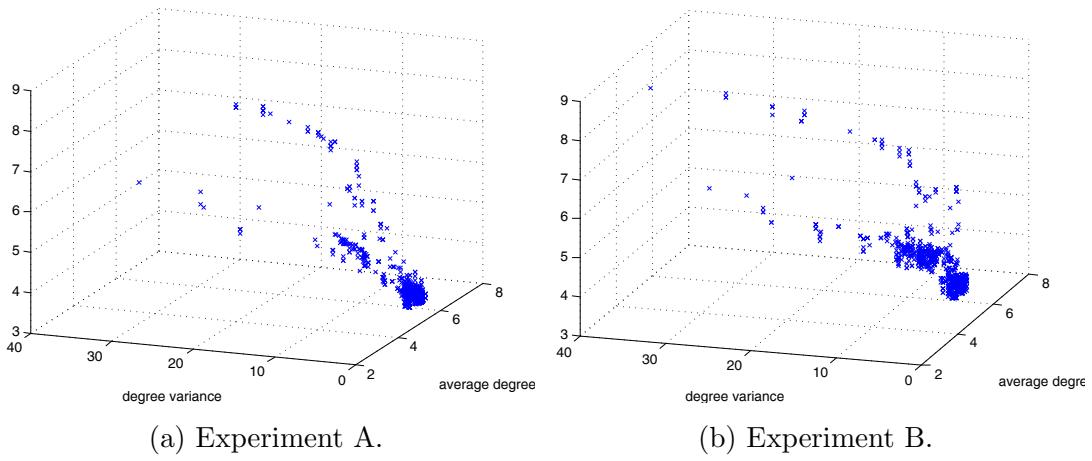

| F-3 | Required Signal to Noise Ratio against average variable node degrees. | 116 |

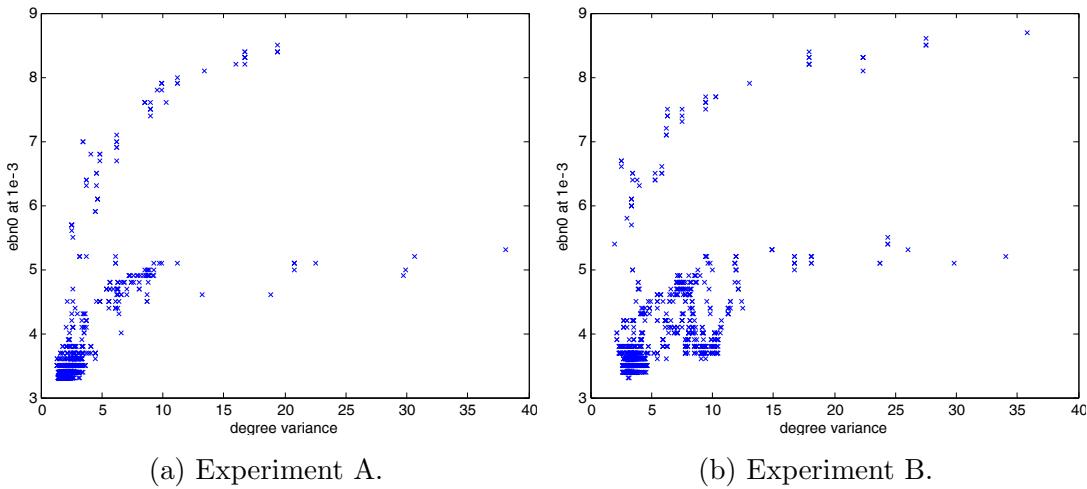

| F-4 | Required Signal to Noise Ratio against average variable node degrees. | 116 |

| F-5 | Required Signal to Noise Ratio against features. . . . .              | 116 |

# List of Tables

|     |                                                                                                                                                                                                                                                                      |    |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Hamming (7,4) code and 4B/5B coding . . . . .                                                                                                                                                                                                                        | 21 |

| 4.1 | Minimum $E_b/N_0$ thresholds for a given $BER = 10^{-4}$ before and after the optimization. . . . .                                                                                                                                                                  | 55 |

| 4.2 | The optimized (128,64) code. The parity-check matrix is listed in the hexadecimal format. . . . .                                                                                                                                                                    | 58 |

| 4.3 | Mean required number of generations for achieving a 100% correction capability of single bit errors. . . . .                                                                                                                                                         | 60 |

| 4.4 | Minimum required number of generations for achieving a 100% correction capability of single bit errors. . . . .                                                                                                                                                      | 60 |

| 4.5 | Median required number of generations for achieving a 100% correction capability of single bit errors. . . . .                                                                                                                                                       | 61 |

| 5.1 | Comparison for OpenCL and CUDA framework (local group of 512 threads and 100 decoders working in parallel) against the CPU implementation using C++ compiler with O3 optimization. Time was measured for 10000 decoded codewords at $E_b/N_0 = 2\text{dB}$ . . . . . | 71 |

| 6.1 | Simulated Bit Error Rate values. There were 4 additional mutational decoders used for simulations. $R = k/n$ is the code rate. Similarly, 4 additional decoding attempts were used for dithered algorithm [32] . .                                                   | 93 |

| A.1 | Addresses used for message calculation outgoing from variable nodes. . . . .                                                                                                                                                                                         | 97 |

| A.2 | Addresses used for message calculation outgoing from check nodes. . . . .                                                                                                                                                                                            | 98 |

| A.3 | Comparison of chosen OpenCL and CUDA syntax rules . . . . .                                                                                                                                                                                                          | 98 |

|     |                                                                                                                 |     |

|-----|-----------------------------------------------------------------------------------------------------------------|-----|

| B.1 | Synthesis results. The number of required ALMs is compared for different code lengths. . . . .                  | 103 |

| B.2 | Addresses used for message calculation outgoing from check nodes. . .                                           | 104 |

| C.1 | Correcting capabilities measured for ultra short block lengths . . . . .                                        | 106 |

| C.2 | Correcting capabilities measured by the ratio of frames which are able to be corrected by the decoder . . . . . | 106 |

| C.3 | Correcting capabilities measured by the ratio of frames which are able to be corrected by the decoder . . . . . | 106 |

| C.4 | Correcting capabilities measured by the ratio of frames which are able to be corrected by the decoder . . . . . | 106 |

| D.1 | Error correcting capability measured on our (128,64) LDPC code. . .                                             | 110 |

| D.2 | Error correcting capability measured on NASA CCSDS (256,128) LDPC code. . . . .                                 | 110 |

| D.3 | Error correcting capability measured on MacKay's (504,252) LDPC code. .                                         | 110 |

| E.1 | Error correcting capability measured o MacKay's (504,252) LDPC code using MLDPC. . . . .                        | 111 |

| E.2 | CCSDS 256, 4 additional decoders. . . . .                                                                       | 111 |

| E.3 | LDPC (128, 64), 4 additional decoders. . . . .                                                                  | 112 |

| F.1 | Comparison of times required for formal description and comprehensive simulation. . . . .                       | 114 |

| F.2 | Comparison of times required for formal description and comprehensive simulation. . . . .                       | 115 |

# List of Symbols

**AWGN** Additive White Gaussian Noise

**BER** Bit Error Rate

**BFS** Breadth-First Search

**BPSK** Binary-Phase Shift Keying

**DVB-S** Digital Video Broadcasting - Satellite

**DVB-T** Digital Video Broadcasting - Terrestrial

**FPGA** Field Programmable Gate Array

**G** Generator matrix

**GPU** Graphics Processing Unit

**H** Parity-Check matrix

**LDPC** Low Density Parity-Check

**MLDPC** Mutational LDPC

**MLDPCe** MLDPC using information Entropy

**MLDPCr** MLDPC using Radius

**SNR** Signal-to-Noise Ratio

*The place where this text has been mostly written :-)*

# Chapter 1

## Introduction

With the increasing development of electronics and telecommunication technologies, there was a need for definitions, new terminology and a generalization of communication processes. The first theoretical contribution to the generalization of a data transmission was made by Shannon's work in 1948 [46], where he defined quantities connected with a new discipline called information theory, established limits for communication processes between a source and a destination and introduced a schematic diagram (Fig. 2-1) of a general communication model.

Since Shannon's work, the topic of error detection and error correction codes, related to channel coding, has seen significant growth. The first serious discussion of error correction codes emerged in Hamming's work in 1950 [22], where Hamming provided a method for the correction of single bit and the detection of double bit errors with minimum redundancy being added to the data transmitted. Since the second half of 20th century, error correction codes have attracted much attention in research work and have been utilized in many applications, including space photography transmission, television broadcasting services, Ethernet, or wireless communication networks.

Since the invention of correction codes and establishment of space programmes, space agencies, i. e. NASA and ESA, have become a common user of these codes. Reed-Muller codes [49],[44] found an application in transmission of Mars photographs in the Mariner spacecraft mission between 1969 and 1977. Reed-Solomon codes [53] and convolutional codes were used on the Voyager 1 space probe mission, whereas

a Golay code [25] was used on the Voyager 2 (both were launched in 1977). The New Horizon spacecraft, currently enroute to Pluto, uses turbo codes [62] for space transmission and Reed-Solomon codes in an internal system.

Although Hamming codes are still used in random access memories, more robust codes are commonly deployed. Reed Solomon codes have become familiar on compact discs, digital versatile discs, Blu-Ray discs, or hard discs. They are also used as a coding technique at CERN for data transmission from detectors or as an outer code to convolutional codes in television broadcasting standards (DVB-T, DVB-S). However, DVB-S2 (ratified in 2005) [88] and DVB-T2 (2006) standards use a combination of BCH [7] and LDPC codes [86]. LDPC codes were further standardized as an option to other coding schemes for communication networks, such as 10 Gigabit Ethernet (10GBASE-T) in 2006, WiMAX (802.16e) in 2006, WiFi (802.11n in 2009 or 802.11ac in 2014 [87]). As can be seen from the number of applications with LDPC codes, which is increasing, these codes have become the very popular coding technique used for an establishment of reliable data transmission. Another interesting coding technique includes polar codes [2]. Also these codes have seen growing interest because of their low coding complexity.

Low Density Parity-Check (LDPC) codes were introduced by Gallager [24] in 1962. Since MacKay's rediscovery [37] in 1995, the past two decades have seen increasingly rapid advances in the field of LDPC codes. There is a growing number of applications with LDPC codes and Sum-Product (SP) decoding [70]. Recently, the Progressive-Edge Growth (PEG) [74] construction has been becoming popular. It was said, "The PEG construction creates matrices with very large girth. This construction has proved to produce the best known Gallager codes." (MacKay, 2008). Moreover, LDPC codes can be constructed in a wide variety of block lengths or redundancies, and the decoder is able to report that the block has been incorrectly decoded, which is not a common behavior of all decoders associated with different types of codes.

This text is organized as follows. Chapter 2 provides general ideas of error correction coding. Chapter 3 presents LDPC codes in terms of their history, principles of construction, encoding and decoding. Chapter 4 introduces innovative construction

methods, applied in combination with genetic optimization algorithms. A performance of the proposed methods is evaluated and new codes are compared to the codes of the same length. Chapter 5 proposes a general method for the parallelization of irregular LDPC codes. Benchmarks are performed using GPU platform. In Chapter 6, several methodologies improving performance of decoders are proposed and the performance is compared to the state-of-the art decoders using the same LDPC code.

# Chapter 2

## Error correction coding

### 2.1 History of error correction coding

Since Hamming reported the first generalized correction codes there has been an increasing amount of interest in this field. In 1954, D. Muller published a paper on the application of Boolean algebra to electrical circuits and error detection [44], where he established the minterm terminology. Working independently of Muller, I. Reed reported codes with bit error correctability greater than two [49]. Codes that came from their work are currently known as Reed-Muller. In 1955, P. Elias introduced convolutional codes [17] and later, in 1957, E. Prange introduced cyclic codes [48]. This trend was followed by BCH and Reed-Solomon codes in 1960 [7], [53]. The first mention of LDPC codes appeared in Gallager's work in 1962 [24], but this work did not have a considerable impact for several decades. Afterwards, in 1993, there was a revolution with the introduction of turbo codes [62], whose decoding performance was significantly closer to Shannon's bound than any other codes published previously. In 1995, MacKay and Neal rediscovered Gallager's LDPC codes [37], which had been neglected for over 30 years (few mentions by Zyablov, Pinsker and Tanner [85], [56]). MacKay's rediscovery of LDPC codes in 1995 [37] has heightened the need for other studies on those codes. In 1998, Davey and MacKay proposed non-binary LDPC codes, which outperformed turbo codes [14], [15]. Spielman also showed that binary LDPC codes using heuristic construction can surpass turbo codes in terms of

correction capability [54].

## 2.2 Shannon model

The Shannon model (Fig. 2-1) divides the communication process into separate blocks with specific functions. Data provided by an information source are transmitted and passed through a noisy channel to a receiver, where they are processed and transferred to a destination. Today, the transmitter is often divided into the source encoder and the channel encoder, according to the theory introduced by Shannon. Additionally, a modulator can be located between the channel encoder and the channel if it is not considered as a part of the channel encoder. Similarly, the receiver can be divided into a demodulator, a channel decoder, and a source decoder (Fig. 2-2).

Figure 2-1: Shannon's conceptual diagram of the information transmission between the source and the destination.

Figure 2-2: Extended diagram of the communication chain.

Figure 2-3: Historical milestones in coding theory.

## 2.3 Definitions

Alphabet  $\mathcal{A}$  is said to be the set of  $q$  symbols, usually considered that  $\mathcal{A}$  forms a field.

A block code over an alphabet  $\mathcal{A}$  is a set of  $q^k$  vectors (codewords) of length  $n$ .

A block code  $C$  is a linear  $(n,k)$  code if and only if its  $q^k$  codewords form a  $k$ -dimensional vector subspace of the vector space  $\mathcal{F}_q^n$  over a field  $\mathcal{F}_q$ , where  $\mathcal{F}_q^n$  is a space of  $q^n$  vectors. The number  $n$  is the length of the code and the number  $k$  is the dimension of the code. The examples of linear and nonlinear codes can be seen in Table 2.1.

The Hamming distance  $d$  between vectors  $\mathbf{x}$  and  $\mathbf{y}$  of equal length ( $|\mathbf{x}|=|\mathbf{y}|$ ) is the number of positions where the corresponding elements are different,

$$d(\mathbf{x}, \mathbf{y}) = \sum_{n=1}^{|\mathbf{x}|} d_i \quad (2.1)$$

$$d_i = \begin{cases} 0 & \text{for } x_i = y_i \\ 1 & \text{for } x_i \neq y_i \end{cases} \quad (2.2)$$

The minimum distance  $d_{min}$  of a block code  $C$  is the smallest Hamming distance between any two codewords in the code  $C$ .

Table 2.1: Hamming (7,4) code and 4B/5B coding

| message $\mathbf{m}$ | codeword $\mathbf{c}$ |       |

|----------------------|-----------------------|-------|

|                      | Hamming (7,4)         | 4B/5B |

| 0000                 | 0000000               | 11110 |

| 0001                 | 0001111               | 01001 |

| 0010                 | 0010110               | 10100 |

| 0011                 | 0011001               | 10101 |

| 0100                 | 0100101               | 01010 |

| 0101                 | 0101010               | 01011 |

| 0110                 | 0110011               | 01110 |

| 0111                 | 0111100               | 01111 |

| 1000                 | 1000011               | 10010 |

| 1001                 | 1001100               | 10011 |

| 1010                 | 1010101               | 10110 |

| 1011                 | 1011010               | 10111 |

| 1100                 | 1100110               | 11010 |

| 1101                 | 1101001               | 11011 |

| 1110                 | 1110000               | 11100 |

| 1111                 | 1111111               | 11101 |

$$d_{min} = \min_{\mathbf{c}_1, \mathbf{c}_2 \in \mathcal{C} \wedge \mathbf{c}_1 \neq \mathbf{c}_2} d(\mathbf{c}_1, \mathbf{c}_2), \quad (2.3)$$

The Hamming weight  $w(\mathbf{c})$  of a codeword  $\mathbf{c}$  is the number of nonzero elements of the codeword.

The entropy  $H(X)$  is a measure of the amount of uncertainty (average amount of self-information) associated with a discrete random variable  $X$ . For a source  $X$  with probabilities  $P(X = x_i)$ , where  $x_i \in \{x_1 \dots x_N\}$ , the entropy is:

$$H(X) = - \sum_{i=1}^N (P(x_i) \log_2 P(x_i)) \quad [\text{Sh}]. \quad (2.4)$$

The information rate  $R$  of code  $\mathcal{C}$  is given by:

$$R = \frac{\log_q |\mathcal{C}|}{n}, \quad (2.5)$$

where  $q$  is the number of symbols in the alphabet and  $n$  is the length of the

codeword.

For a block code  $\mathcal{C} = (n, k)$  the information rate becomes:

$$R = \frac{\log_q |q^k|}{n} = \frac{k}{n}, \quad (2.6)$$

where  $k$  is the length of the information message.

The redundancy  $r$  of the code is the difference between the length of the codeword and the length of the information message,  $r = n - k$ .

### 2.3.1 Generator matrix

Every linear block code  $\mathcal{C}$  can be described in terms of the  $k$  by  $n$  generator matrix  $\mathbf{G}$ . The rows of  $\mathbf{G}$  generate  $\mathcal{C}$ . The codeword  $\mathbf{c}$  can be represented as a linear combination of the row vectors of  $\mathbf{G}$ . The information vector (message) is denoted as  $\mathbf{m}$ . Then,

$$\mathbf{c} = \mathbf{m}\mathbf{G}. \quad (2.7)$$

### 2.3.2 Parity-check matrix

A parity check matrix  $\mathbf{H}$ , associated with a linear block code  $\mathcal{C}$ , is a matrix satisfying the formula:

$$\mathbf{G}\mathbf{H}^\top = \mathbf{0}. \quad (2.8)$$

Any vector  $\mathbf{v}$  of length  $n$  is a codeword if and only if it meets the following condition:

$$\mathbf{v}\mathbf{H}^\top = \mathbf{0}. \quad (2.9)$$

A product of the multiplication  $\mathbf{v}\mathbf{H}^\top$  is called the syndrome  $\mathbf{s}$ .

### 2.3.3 Systematic form of coding

Consider information symbols (elements of  $\mathbf{m}$ ) as the elements of the information vector  $\mathbf{m}$ . When the systematic form of coding is applied, information symbols are

then written in the same order both in the codeword and in the original message. The systematic form of the generator matrix is the following:  $\mathbf{G} = [\mathbf{P} \mid \mathbf{I}]$  or  $[\mathbf{I} \mid \mathbf{P}]$ , where  $\mathbf{I}$  is the  $k$  by  $k$  identity matrix and  $\mathbf{P}$  is a part of  $\mathbf{G}$  matrix.

### 2.3.4 Non-binary codes

So far, only binary representations of the generator and a parity check matrix have been considered. Linear block codes can be generalized using finite field arithmetic, which is illustrated in following paragraphs.

The modular arithmetic with congruence modulo  $n$  relation is considered. If  $n$  is a prime, such an arithmetic generates a field, which can be utilized for computations with linear block codes. Because of the binary channels generally used in communications, Galois fields (GF) of  $2^p$  polynomials are generally utilized. Such a field is created by any irreducible polynomial.

### 2.3.5 Communication channel models

There are two groups of mathematical models of communication channels, analogue and digital. Analogue channels, including Additive White Gaussian Noise (AWGN) or Rayleigh fading model, work with analogue messages being transmitted. Digital channel models, involving Binary Symmetric Channel (BSC) or Binary Erasure Channel (BEC), consider the messages as digital variables. The capacity associated with the channel is a measure first used by Shannon [46]. The definition in terms of entropy is the following:

The channel capacity  $C$  is the upper bound on the information being transmitted between the input and output (maximum mutual information),

$$C = \max \{I(X, Y)\} = \max \{H(Y) - H(Y|X)\}, \quad (2.10)$$

where  $H(Y)$  is the destination entropy,  $H(Y|X)$  is the conditional entropy, and  $I(X, Y)$  is the mutual information. If  $H(Y|X) = 0$ , there are no errors in the transmission and the capacity is maximum. As the symbol duration  $T_s$  is known, the

maximum bandwidth in bits per second can be determined by:

$$C' = \frac{C}{T_s} \quad [\text{bit/s, Sh/s}]. \quad (2.11)$$

For BSC, the capacity is given:

$$C = 1 - H = 1 + p \log_2 p + (1 - p) \log_2 (1 - p) \quad [\text{Sh}] \quad (2.12)$$

Related to the AWGN channel, the maximum rate of transmitted information is given by the Shannon-Hartley theorem, which can be written in the following formula:

$$C = B \log_2 \left( 1 + \frac{P_S}{P_N} \right) \quad [\text{bit/s}], \quad (2.13)$$

where  $B$  is the bandwidth,  $P_S$  is the power of the signal,  $P_N$  is the power of the noise.

# Chapter 3

## LDPC codes

Low Density Parity-Check (LDPC) codes are defined in terms of sparse parity check matrices (described in Section 2.3.2). Suppose a parity-check matrix  $\mathbf{H}$  associated with the linear block code  $\mathcal{C}$ . If the matrix  $\mathbf{H}$  is sparse, the code  $\mathcal{C}$  is said to be the LDPC code. If the column weights in the matrix  $\mathbf{H}$  are all the same and row weights are all the same, the LDPC code is regular. If not, it is irregular. It has been shown that irregular codes perform better [35].

LDPC construction, encoders, decoders, and historical milestones are outlined in the following chapter.

### 3.1 Background

Although only the regular form of the parity-check matrix was considered by Gallager, irregular constructions have become familiar because of their better performance. The first report on irregular codes was published by Luby, Mitzenmacher, Shokrollahi and Spielman in 1998 [35], followed by MacKay, Wilson and Davey in 1999 [38]. In 2001, a powerful code design, which is based on appropriate degree distribution in a Tanner graph, was presented by Richardson, Shokrollahi and Urbanke [50]. However, regular codes have been studied comprehensively in MacKay's work [39]. In 2003, Fossorier studied Quasi-Cyclic (QC) codes, based on circulant permutation matrices [21]. Later, in 2004, Vasic showed several combinatorial constructions of parity-check

matrices [64], and Tian, Jones, Villasenor and Wesel studied an effect of the graph connectivity on the correction capability [61]. Probably still the best known code was identified in the work of Chung, Forney, Richardson and Urbanke [13]. Further, in 2004, Thorpe, Andrews, Dolinar proposed the construction of LDPC codes based on protographs [60]. Hu, Eleftheriou and Arnold, discovered in 2001 and generalized in 2005 an algorithm (the Progressive Edge-Growth (PEG)) based on a Tanner graph construction in terms of a tree structure [73], [74]. During the past ten years, this algorithm has become a general standard for the design of good codes. Numerous studies have attempted to modify PEG construction in order to achieve better performance. In 2010, Zheng, Lau and Tse presented a PEG modification improving performance at the error floor region [84]. Uchoa, Healy, de Lamare and Souza [63] introduced PEG techniques for fading channels in 2011. Our work on LDPC codes started in 2012 [10] with the utilization in a microcontroller and it was followed with probably the first direct application of genetic optimization methods on code construction in 2013 [11]. This work has led to results pointed out in Section 4.2. Furthermore, the genetic construction can be naturally optimized to all possible channels and decoding algorithms, where it outperforms state-of-the art solutions

Decoding algorithms used for LDPC codes are suboptimal and the convergence to the minimum distance codeword is not guaranteed. Thus, the correction performance depends both on the code and the decoding algorithm used. Several decoding methods, which differed in the performance and required number of operations, were presented in the literature. Soft-decision algorithms working on Tanner graphs were introduced by Wiberg [70]. Nonbinary and Fast Fourier Transform (FFT) versions were pointed by Davey in 1999 [16] and later, in 2004, log-domain FFT decoding was described by Byers and Takawira [9]. The work of Yedidia, Freeman and Weiss from 2001 contributed to generalization of Belief Propagation (BP) algorithms [76], including the decoding algorithms above.

Recently, researchers have shown an increased interest in the connection of neural networks and LDPC codes. A relationship between message passing and continuous Hopfield networks was revealed by Ott and Stoop in 2007 [47]. In 2009 Karami, Attari

and Tavakoli presented perceptron neural networks for LPDC decoders [27] and later, in 2013, Anton, Ionescu, Tutanescu, Mazare and Serban presented an application with parallel Hopfield networks [1].

However, far too little attention has been paid to the multi-edge codes discovered by Richardson and Urbanke in 2004 [52]. This work was followed by Liva and Chiani [34] in 2007, where they provided a novel extrinsic information transfer analysis for protograph and multi-edge codes. Obata, Yung-Yih, Kasai and Pfister showed properties of multi-edge codes on binary erasure channels in 2013 [45].

Several patents have been granted for encoding or decoding implementations in hardware for special purposes (e.g. US 7,543,212 B2 or US 7,499,490 B2 in 2009) and several hardware implementations have been published [67], [80]. Nevertheless, very few studies have examined scalable implementations of decoders for irregular codes in Field-Programmable Gate Arrays (FPGA) (e.g. [57]). Important milestones covering LDPC codes are presented in the work of Bonello, Chen and Hanzo in 2011 [8]. The selected milestones are pointed out in Fig. 3-1

Figure 3-1: Historical milestones related to LDPC codes.

## 3.2 Encoding

The encoding of LDPC codes is performed by the multiplication of an information vector  $\mathbf{m}$  with the generator matrix  $\mathbf{G}$ . Because LDPC codes are often defined by a parity-check matrix  $\mathbf{H}$  solely, there is a need for finding the generator matrix  $\mathbf{G}$ , which satisfies Eq. 2.8. This can be done by the principle described below.

It is assumed that the parity-check matrix  $\mathbf{H}$  is in the systematic form  $\mathbf{H} = [\mathbf{P} \mid \mathbf{I}]$ . A relation between  $\mathbf{G}$  and  $\mathbf{H}$  is given by:

$$\mathbf{G} = [\mathbf{I} \mid -\mathbf{P}^\top] \iff \mathbf{H} = [\mathbf{P} \mid \mathbf{I}], \quad (3.1)$$

where  $\mathbf{I}$  is the  $k$  by  $k$  identity matrix.

## 3.3 Tanner graphs

The Tanner graph is a graph representation of linear block codes, which provides a support for decoding algorithms of LDPC codes. A parity-check matrix  $\mathbf{H}$  of a linear block code  $\mathcal{C}$  is considered as a part of an adjacency matrix of a bipartite undirected graph (Fig. 3.2). Nodes associated with columns of  $\mathbf{H}$  are said to be the variable nodes, symbol nodes, or bit nodes, whereas nodes associated with rows of  $\mathbf{H}$  are called the check nodes. Edges occur between these nodes. The edges are being used for passing messages between two sets of nodes. Note that the full adjacency matrix of the Tanner graph has the form:

$$\mathbf{A} = \begin{bmatrix} 0 & \mathbf{H} \\ \mathbf{H}^\top & 0 \end{bmatrix}. \quad (3.2)$$

The set of all edges in the Tanner graph is defined by:

$$E \triangleq \{\{c_i, v_j\} : \mathbf{H}_{i,j} \neq 0\}, \quad (3.3)$$

or in terms of node indices:

$$\mathcal{E} \triangleq \{(i, j) : \{c_i, v_j\} \in E\}. \quad (3.4)$$

A degree distribution function describes a distribution of degrees in a graph. Associated to Tanner graphs, an ensemble of irregular codes is specified by two degree distributions,  $\lambda(x)$  and  $\rho(x)$ ,

$$\lambda(x) = \sum_{i=2}^{d_{vmax}} \lambda_i x^{i-1}, \quad (3.5)$$

$$\rho(x) = \sum_{j=2}^{d_{cmax}} \rho_j x^{j-1}, \quad (3.6)$$

where  $\lambda_i$  is the fraction of edges that belongs to degree- $i$  variable nodes,  $\rho_j$  is the fraction of edges that belong to degree- $j$  check nodes,  $d_{vmax}$  is the maximum variable node degree, and  $d_{cmax}$  is the maximum check node degree.

## 3.4 Decoding

The decoding of LDPC codes is usually performed by iterative Belief Propagation (BP) algorithms [70], [76] which work on the Tanner graph [56]. There are two groups of algorithms - hard decision and soft decision, which performs better in terms of correction capabilities. The soft decision decoding is described in the following sections.

### Sum-Product algorithm

The Sum-Product (SP) algorithm is the algorithm based on probabilistic iterative decoding of LDPC codes. The algorithm works in several steps : Initialization, Iterative process, and Termination.

The first step of the algorithm is the initialization, when the decoder receives a possibly corrupted codeword from a communication channel. During the iterative

process, message passing through edges is being performed. Values sent from variable nodes to check nodes are denoted as  $q_{ij}$ , values outgoing from check nodes to variable nodes are denoted as  $r_{ij}$ . The algorithm is terminated when the corrected codeword is achieved or after a certain number of iterations is reached. If the algorithm is interrupted after the specific number of iterations, the decoding is considered as unsuccessful.

Two sets of node indices are given,  $\mathcal{M}_j$  and  $\mathcal{N}_i$ .  $\mathcal{M}_j$  is the set of all check node indices that are connected with the variable node  $j$ , while  $\mathcal{N}_i$  is the set of all variable node indices that are connected with the check node  $i$ .

$$\begin{aligned}\mathcal{M}_j &\triangleq \{i : (i, j) \in \mathcal{E}\}, \\ \mathcal{N}_i &\triangleq \{j : (i, j) \in \mathcal{E}\}.\end{aligned}\tag{3.7}$$

Consider the codeword sent into the channel to be denoted as  $\mathbf{c}$  and the possibly corrupted message received from the channel as  $\mathbf{y}$ . Bits in these vectors are denoted as  $c_j$  and  $y_j$ , where  $j = 1 \dots n$ . In the initialization step, conditional probabilities  $P(c_j | y_j)$  are calculated and these values are sent to check nodes.

The conditional probabilities are defined as:

$$p_j(0) \triangleq P(c_j = 0 | y_j),\tag{3.8}$$

$$p_j(1) \triangleq P(c_j = 1 | y_j),\tag{3.9}$$

after the calculation, these values are sent to check nodes as messages  $q_{ij}$ ,

$$q_{ij}(0) = p_j(0), q_{ij}(1) = p_j(1).\tag{3.10}$$

The calculation of conditional probabilities for several channels, Binary Symmetric Channel (BSC), Binary Erasure Channel (BEC), Binary Symmetric Channel with Errors and Erasures (BSEC), and AWGN channel with Binary-Phase Shift Keying (BPSK), can be performed using the formulas below.

For BSC channel, we can express the initial messages as:

$$p_j(0) = \begin{cases} 1 - p, & \text{for } y_j = 0 \\ p, & \text{for } y_j = 1 \end{cases}, \quad (3.11)$$

$$p_j(1) = 1 - p_j(0) = \begin{cases} p, & \text{for } y_j = 0 \\ 1 - p, & \text{for } y_j = 1 \end{cases}, \quad (3.12)$$

where  $p \in [0, 1]$  is the crossover probability (probability of an error) and  $y_j \in \{0, 1\}$  is the received symbol.

For BEC, the probabilities are given as:

$$p_j(0) = \begin{cases} 0, & \text{for } y_j = 1 \\ 1, & \text{for } y_j = 0 \\ 1/2, & \text{for } y_j = e \end{cases}, \quad (3.13)$$

$$p_j(1) = \begin{cases} 1, & \text{for } y_j = 1 \\ 0, & \text{for } y_j = 0 \\ 1/2, & \text{for } y_j = e \end{cases}, \quad (3.14)$$

where  $y_j \in \{0, 1, e\}$  is the received symbol.

Calculation of the probabilities of BSEC is the following:

$$p_j(0) = \begin{cases} 1 - p, & \text{for } y_j = 0 \\ p, & \text{for } y_j = 1 \\ 1/2 \text{ for } y_j = e \end{cases}, \quad (3.15)$$

$$p_j(1) = 1 - p_j(0) = \begin{cases} p, & \text{for } y_j = 0 \\ 1 - p, & \text{for } y_j = 1 \\ 1/2 \text{ for } y_j = e \end{cases}. \quad (3.16)$$

AWGN channel with BPSK modulation, which is often used in simulations:

$$p_j(0) = \frac{1}{1 + e^{2y_j/\sigma^2}}, \quad (3.17)$$

$$p_j(1) = 1 - p_j(0) = \frac{1}{1 + e^{-2y_j/\sigma^2}}, \quad (3.18)$$

where  $y_j \in \mathbb{R}$  is the received symbol.

---

**Algorithm 1** Message passing - Sum Product algorithm

---

1: **procedure** VALUES TO CHECK NODES

▷ First half on an iteration

**Input:**  $\mathbf{p}, \mathbf{r}$

**Output:**  $\mathbf{q}$

```

2:   for all  $j \in [0, |\mathcal{M}|)$  do

3:     for all  $i \in [0, |\mathcal{N}|)$  do

4:        $q_{i,j}(0) = p_j(0)$

5:        $q_{i,j}(1) = p_j(1)$

6:       for all  $i' \in \mathcal{M}_j \setminus i$  do

7:          $q_{i,j}(0) = q_{i,j}(0)r_{i',j}(0)$

8:          $q_{i,j}(1) = q_{i,j}(1)r_{i',j}(1)$

9:       end for

10:      end for

11:    end for

12:  end procedure

```

13: **procedure** VALUES TO VARIABLE NODES

▷ Second half on an iteration

**Input:**  $\mathbf{q}$

**Output:**  $\mathbf{r}$

```

14:   for all  $j \in [0, |\mathcal{M}|)$  do

15:     for all  $i \in [0, |\mathcal{N}|)$  do

16:        $r_{i,j}(0) = 1$

17:        $r_{i,j}(1) = 1$

18:       for all  $j' \in \mathcal{N}_i \setminus j$  do

19:          $r_{i,j}(0) = r_{i,j}(0)(1 - 2q_{i,j'}(1))$

20:       end for

21:        $r_{i,j}(0) = 1/2 + 1/2r_{i,j}(0)$

22:        $r_{i,j}(1) = 1 - r_{i,j}(0)$

23:     end for

24:   end for

25: end procedure

```

---

The values of  $p_j$  are passed to check nodes as  $q_{ij}$  messages. After passing  $q_{ij}$ ,

---

**Algorithm 2** Soft-decision decoding

---

```

1: procedure DECODEAWGN                                 $\triangleright$  SP algorithm

Input:  $\mathbf{y}$  – output from a demodulator

ITERATIONS – maximum number of iterations

$\sigma$  – variance of the channel

Output:  $\hat{\mathbf{c}}$

2:    $\mathbf{q}$  =Initialize( $\mathbf{p}, \sigma$ )                       $\triangleright$  See Algorithm 3

3:    $\mathbf{r}$  =Values to Variable Nodes( $\mathbf{q}$ )             $\triangleright$  See Algorithm 1

4:    $\hat{\mathbf{c}}$  =Calculate Estimation( $\mathbf{r}$ )             $\triangleright$  See Algorithm 4

5:   if  $\hat{\mathbf{c}}\mathbf{H}^\top = \mathbf{0}$  then return  $\hat{\mathbf{c}}$

6:   end if

7:   for  $it \in (0, \text{ITERATIONS})$  do

8:      $\mathbf{q}$  =Values to Check Nodes( $\mathbf{r}$ )           $\triangleright$  See Algorithm 1

9:      $\mathbf{r}$  =Values to Variable Nodes( $\mathbf{q}$ )           $\triangleright$  See Algorithm 1

10:     $\hat{\mathbf{c}}$  =Calculate Estimation( $\mathbf{r}$ )           $\triangleright$  See Algorithm 4

11:    if  $\hat{\mathbf{c}}\mathbf{H}^\top = \mathbf{0}$  then return  $\hat{\mathbf{c}}$

12:    end if

13:   end for

14: end procedure

```

---

**Algorithm 3** Soft-decision decoding - initialization

---

```

1: procedure INITIALIZE                                 $\triangleright$  Probabilities for AWGN

Input:  $\mathbf{y}, \sigma$

Output:  $\mathbf{q}$

2:   for all  $y_j \in \mathbf{y}$  do

3:      $p_j = 1.0 / (1 + \exp(-2y_j / \sigma^2))$

4:   end for

5:   for all  $j \in [0, |\mathcal{M}|)$  do

6:     for all  $i \in [0, |\mathcal{N}|)$  do

7:        $q_{i,j} = p_j$

8:     end for

9:   end for

10: end procedure

```

---

values  $r_{ij}$  are calculated and passed back to the variable nodes, as follows:

$$r_{ij}(0) = \frac{1}{2} + \frac{1}{2} \prod_{j' \in \{\mathcal{N}_i \setminus j\}} (1 - 2q_{ij'}(1)), \quad (3.19)$$

$$r_{ij}(1) = 1 - r_{ij}(0) \quad (3.20)$$

---

**Algorithm 4** Soft-decision decoding - estimation

---

```

1: procedure CALCULATE ESTIMATION

Input:  $\mathbf{p}, \mathbf{r}$

Output:  $\hat{\mathbf{c}}$

2:   for all  $j \in [0, |\mathcal{M}|)$  do

3:      $Q_{i,j}(0) = p_j(0)$

4:      $Q_{i,j}(1) = p_j(1)$

5:     for all  $i \in \mathcal{M}_j$  do

6:        $Q_{i,j}(0) = Q_{i,j}(0)r_{i,j}(0)$

7:        $Q_{i,j}(1) = Q_{i,j}(1)r_{i,j}(1)$

8:     end for

9:     if  $Q_{i,j}(0) > Q_{i,j}(1)$  then  $\hat{c}_j = 0$

10:    else  $\hat{c}_j = 1$

11:    end if

12:   end for

13: end procedure

```

---

After the variable nodes receive the values of  $r_{ij}$ , a new estimation  $\hat{\mathbf{c}}$  of the codeword  $\mathbf{c}$  is calculated.

$$Q_j(0) = K_j \cdot p(0) \cdot \prod_{i \in \mathcal{M}_j} r_{ij}(0), \quad (3.21)$$

$$Q_j(1) = K_j \cdot p(1) \cdot \prod_{i \in \mathcal{M}_j} r_{ij}(1), \quad (3.22)$$

the constant  $K_j$  is chosen to satisfy  $Q_j(0) + Q_j(1) = 1$ ,

$$\hat{c}_j = \begin{cases} 1, & \text{for } Q_j(1) > Q_j(0) \\ 0, & \text{otherwise} \end{cases}. \quad (3.23)$$

If  $\hat{\mathbf{c}}$  is a codeword of the code (the product of  $\hat{\mathbf{c}}\mathbf{H}^\top$  is equal to the zero vector), the decoding is stopped. If not, the decoding process continues with the next iteration. Then, values  $q_{ij}$  are calculated as follows:

$$q_{ij}(0) = K_{ij}p(0) \prod_{i' \in \{\mathcal{M}_j \setminus i\}} r_{i'j}(0), \quad (3.24)$$

$$q_{ij}(1) = K_{ij} p(1) \prod_{i' \in \{\mathcal{M}_j \setminus i\}} r_{i'j}(1), \quad (3.25)$$

where  $K_{ij}$  is the normalization constant to satisfy:  $q_{ij}(0) + q_{ij}(1) = 1$ .

These values are sent to check nodes and the second half of the iteration continues to Eq. 3.19 and 3.20.

### Log-domain decoding

In order to decrease the number of multiplications being used in the decoding process, the log-domain decoding has been proposed. Assume the surjective function  $L$ ,

$$L : L(x, y) = \ln \frac{x}{y}. \quad (3.26)$$

Consider this function applied on initial probabilities and messages being passed through the Tanner graph,

$$L(p_j) \triangleq L(p_j(0), p_j(1)) = \ln \frac{p_j(0)}{p_j(1)}, \quad (3.27)$$

$$L(r_{ij}) \triangleq L(r_{ij}(0), r_{ij}(1)) = \ln \frac{r_{ij}(0)}{r_{ij}(1)}, \quad (3.28)$$

$$L(q_{ij}) \triangleq L(q_{ij}(0), q_{ij}(1)) = \ln \frac{q_{ij}(0)}{q_{ij}(1)}. \quad (3.29)$$

For AWGN channel, the initial probability is given by:

$$L(p_j) = -\frac{2y_i}{\sigma^2}. \quad (3.30)$$

For Rayleigh fading channel, the initial probabilities can be expressed as (e. g. [28]):

$$L(p_j) = -\frac{2y_i}{\sigma^2} \alpha, \quad (3.31)$$

where  $\alpha$  is the normalized Rayleigh fading factor with  $E[\alpha^2] = 1$  and probability density function  $p(\alpha) = 2\alpha e^{-\alpha^2}$ , and  $y_j \in \mathbb{R}$  is the received symbol.

If no channel state information is available, we can calculate with the approxima-

tion:

$$L(p_j) = -\frac{2y_i}{\sigma^2} E[\alpha]. \quad (3.32)$$

It can be derived that  $L(r_{ij})$  values are determined as:

$$\phi(x) \triangleq -\ln \left( \tanh \frac{x}{2} \right) = \ln \frac{e^x + 1}{e^x - 1}, \quad (3.33)$$

$$L(r_{ij}) = \prod_{j' \in \{\mathcal{N}_i \setminus j\}} \text{sign}(L(q_{ij'})) \cdot \phi \left( \sum_{j' \in \{\mathcal{N}_i \setminus j\}} \phi |L(q_{ij'})| \right). \quad (3.34)$$

The precise calculation of  $\phi$  can consume a prohibitively long time. In order to decrease the number of operations, the following simplification is often applied:

$$L(r_{ij}) \approx \prod_{j' \in \{\mathcal{N}_i \setminus j\}} \text{sign}(L(q_{ij'})) \cdot \min |L(q_{ij'})|. \quad (3.35)$$

The algorithm using the equation above is usually referred as the Min-Sum algorithm [70].

Values of  $L(q_{ij})$  are calculated by the summation:

$$L(q_{ij}) = L(p_j) + \sum_{i' \in \{\mathcal{M}_j \setminus i\}} L(r_{ij}), \quad (3.36)$$

and the estimation  $\hat{\mathbf{c}}$  is given by:

$$L(Q_j) = L(p_j) + \sum_{i \in \mathcal{M}_j} L(r_{ij}), \quad (3.37)$$

$$\hat{c}_j = \begin{cases} 1, & \text{for } L(Q_j) < 0 \\ 0, & \text{otherwise} \end{cases}. \quad (3.38)$$

### Sum-Product algorithm for non-binary codes

The SP algorithm for non-binary LDPC codes was generalized by Davey's and Mackay's work [14]. Their non-binary LDPC codes [15] were the first LDPC codes that surpassed turbo codes at decoding performance.

The values of  $r_{ij}(a)$  are calculated as follows:

$$r_{ij}(a) = \sum_{\mathbf{c}: c_j = a \wedge \mathbf{c} \cdot \mathbf{h}_i^\top = 0} \left( \prod_{j' \in \{\mathcal{N}_i \setminus j\}} (q_{ij'}(c_{j'})) \right), \quad (3.39)$$

which is the sum over all codewords which have the symbol  $a$  at the position  $j$  and satisfy the  $i$ -th parity check, and  $\mathbf{c} \in \mathcal{C}$ . The probability that the symbol at  $j$ -th position is equal to  $a$  is determined by this formula. The vector  $\mathbf{h}_i$  denotes the  $i$ -th row of the parity-check matrix.

The values of  $q_{ij}(a)$ , which are being passed from the variable to the check nodes, are determined by:

$$q_{ij}(a) = K_{ij} \cdot p(a) \cdot \prod_{i' \in \{\mathcal{M}_j \setminus i\}} r_{i'j}(a), \quad (3.40)$$

The constant  $K_{ij}$  is chosen to satisfy  $\sum_{a \in \mathcal{A}} q_{ij}(a) = 1$ .

The estimation is realized by:

$$\hat{x}_j = \operatorname{argmax}_a \left( p(a) \prod_{i \in \{\mathcal{M}_j\}} r_{ij}(a) \right). \quad (3.41)$$

The initial probabilities are calculated proportional to the channel properties. For the AWGN channel using BPSK modulation, it is:

$$p_j(a) = p(y_j | c_j = a) \propto \prod_{i=1}^k e^{\frac{((y_j \text{BIN})_k - (-1)^{t_i})^2}{2\sigma^2}}, \quad (3.42)$$

$t_i^a$  is chosen with respect to  $a$  and  $i$ .

## Adaptive decoding, modifications

One of the most perspective methods of improving the correction performance of the decoder is the usage of an adaptive technique of decoding, firstly presented in [29], and tested on LDPC codes by Mobini in 2011 [40]. In this method, the outgoing messages are replaced by:

$$q'_{ij} = \alpha q_{ij} e^{-\beta |q_{ij}|}. \quad (3.43)$$

where  $\alpha \in (0, 1]$  and  $\beta \in [0, \infty)$  are chosen by solving an optimization task for particular codes.

### Gallager's construction

This is the original Gallager's construction of regular  $\mathbf{H}$  matrix. The weight of row vectors of the parity-check matrix is denoted as  $k$ , the weight of column vectors of the parity-check matrix is denoted as  $j$ , and the length of a codeword is denoted as  $n$ .

Considering the matrix  $\mathbf{A}_0$ ,

$$\mathbf{A}_0 = \begin{bmatrix} 1 & 1 & 1 & 1 \\ & 1 & 1 & 1 & 1 \\ & & 1 & 1 & 1 & 1 \\ & & & 1 & 1 & 1 & 1 \end{bmatrix} \quad (3.44)$$

of the dimension  $n/k$  by  $n$ , the matrix  $\mathbf{H}$  is then given as:

$$\mathbf{H} = \begin{bmatrix} \pi_1(\mathbf{A}_0) \\ \pi_2(\mathbf{A}_0) \\ \vdots \\ \pi_j(\mathbf{A}_0) \end{bmatrix} \quad (3.45)$$

where  $\pi_i$  are random column permutations of  $\mathbf{A}_0$ . However, irregular forms of  $\mathbf{H}$  matrices perform better under the SP decoding. Some construction methods are summarized in the following chapter and methods based on large girth construction and genetic optimization algorithms are proposed in this work.

# Chapter 4

## Construction of LDPC codes

Numerous studies have been focused on construction algorithms of LDPC codes during past decades. In general, these algorithms create the parity-check matrices, which define LDPC codes and associated Tanner graphs. The construction of a parity-check matrix can be performed either in structured (e.g. geometry based methods) and unstructured ways (e.g. PEG [73] or by Gallager's construction (Section 3.4)).

Kou, Lin and Fossorier summarized the construction of LDPC codes based on finite geometries [30] in 2001. Large-girth construction based on graphical models was presented in work of Zhang and Moura [81] in 2003. Later, in 2004, Moura, Lu and Zhang summarized structured construction methods [43] and Vasic and Milenkovic introduced several combinatorical construction methods in [65]. Significant family of structured codes are Quasi-Cyclic (QC) LDPC codes [21], constructed by Fossorier in 2004.

In 2001, Richardson, Shokrollahi and Urbanke introduced a powerfull construction algorithm working with degree distributions in the Tanner graph [50]. In 2003, the algorithm using a new metric called Extrinsic Message Degree (EMD) in order to avoid short cycles was proposed by Tian, Jones, Villasenor and Wessel [58].

The Progressive Edge Growth (PEG) algorithm, firstly presented in 2001 [73] a summarized in 2005 [74], outperformed codes constructed by the methods above. Several modifications of PEG was published [84], [63]. Good degree distributions might by designed using the density evolution method [33], [13], [51] and passed as

an input of the PEG algorithm.

This chapter proposes methodologies for designing LDPC codes and associated Tanner graphs of large girths, and direct application of genetic optimization algorithms.

## 4.1 Generating LDPC matrices with large girth

The proposed algorithm for generating Tanner graphs is based on sequential usage of Breadth-First Search (BFS) and addition of edges with avoidance of short cycles. The diversity of candidate solutions can be tuned by parameters  $\sigma_v$ ,  $\sigma_c$ , and cycle lengths, as can be seen in Algorithm 5.

The algorithm progressively iterates over nodes and calculates distances (denoted as  $d(c, v)$ ) between nodes. If any distance is higher than a given *cycle* parameter and a degree is lower than the desired degree, a new edge is added between the nodes  $c$  and  $v$ . The parameter *cycle* is being changed from the value  $cycle_{start}$  to  $cycle_{stop}$  and it is decreasing.

The proposed algorithm can be used solely for a construction of large girth graphs or as a part of genetic optimization tasks. The performance evaluation of codes produced by this algorithm is also presented. For genetic optimization tasks, this algorithm is used for producing the initial population, as described in the following sections.

---

**Algorithm 5** Large girth graph construction

---

1: **procedure** GENERATE GRAPH

**Input:**  $v_{req}$  - requested variable nodes,

$c_{req}$  - requested check nodes,

$cycle_{start}$  - length of the longest cycle in the first iteration

$cycle_{stop}$  - length of the longest cycle in the last iteration

$d_{v0}$  - design degree of the variable nodes

$d_{c0}$  - design degree of the check nodes

$\sigma_v$  - standard deviation of variable node degrees

$\sigma_c$  - standard deviation of check node degrees

**Output:** (CN,VN)-bipartite graph  $G$

```

2:   for  $cycle = cycle_{start}$  down to  $cycle_{stop}$  do

3:      $d_v = d_{v0} + \sigma_v r, r \in \mathcal{N}(0, 1)$

4:      $d_c = d_{c0} + \sigma_c r, r \in \mathcal{N}(0, 1)$

5:     for all  $v \in VN$  do

6:       for all  $c \in CN$  do

7:         if  $deg(v) < d_v$  and  $deg(c) < d_c$  then

8:           if  $d(c, v) > cycle$  then

9:             | add  $e = (c, v)$  to the set  $E$

10:            | end if

11:          | end if

12:        | end for

13:      | end for

14:    | end for

15:    for all  $v \in VN$  do

16:      if  $deg(v) < 2$  then

17:        |  $e = (c : (c \in G, \max\{k|v \rightarrow^k c\}), v)$

18:        | add  $e$  to the set  $E$

19:      | end if

20:    | end for

21:    for all  $v \in CN$  do

22:      if  $deg(c) < 2$  then

23:        |  $e = (c, v : (v \in G, \max\{k|c \rightarrow^k v\}))$

24:        | add  $e$  to the set  $E$

25:      | end if

26:    | end for

27: end procedure

```

---

Figure 4-1: Correction performance of 10% redundancy codes (12.5% for  $n=64$ ).

Figure 4-2: Correction performance of 25% redundancy codes.

Figure 4-3: Correction performance of 50% redundancy codes.

Figure 4-4: Correction performance of 75% redundancy codes.

## 4.2 Genetic optimization of LDPC codes

### 4.2.1 Optimization algorithm principle

Considering a linear block code  $\mathcal{C} = (n, k)$  as a candidate solution of an optimization problem and the objective function  $f_0 : \mathcal{C} \rightarrow \mathbf{R}$ , the goal is to find the optimal solution  $C^*$  such that  $f_0(C^*) \leq f_0(C)$  as a local minimum  $\|C - C^*\| \leq \delta$ , where  $\delta$  determines the subspace size. According to the parameters of the algorithm and the optimization problem, the local minimum can be equal to the global minimum. A constraint function  $g_i(\mathcal{C}) \leq b_i, i = 1, \dots, m$  can be also considered.

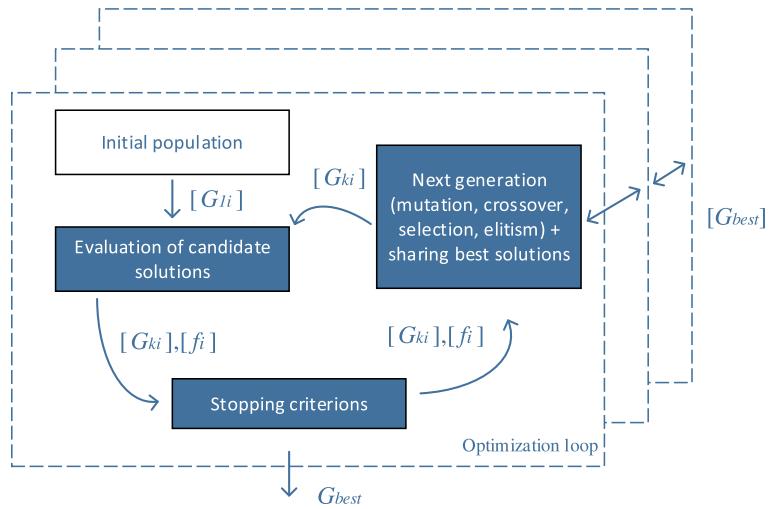

Figure 4-5: A diagram of the optimization process.

The genetic optimization algorithm requires generating the initial population, mutation and crossover operators, and methods used for selection and evaluation candidate solutions. The proposed operators and methods are described in the following sections.

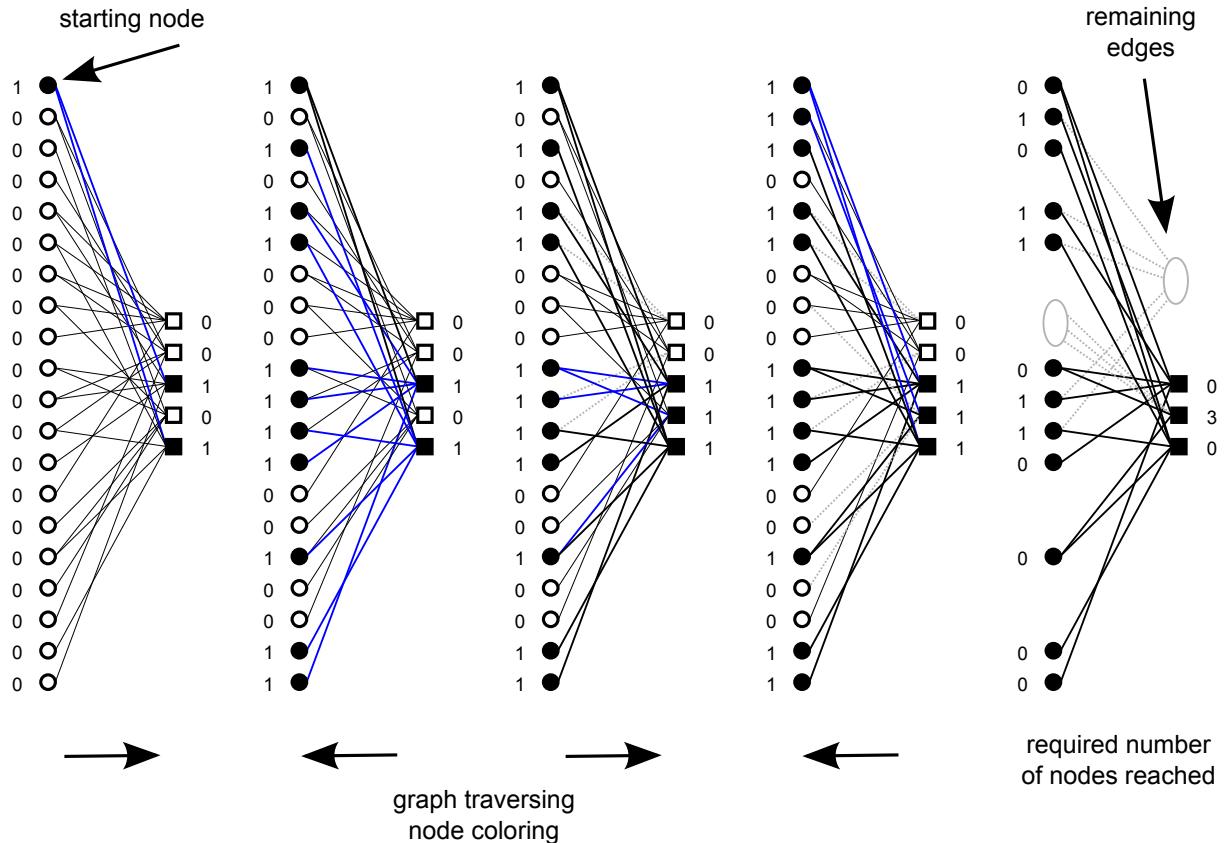

### 4.2.2 Tanner graph mutations

For reproducing the next generations of candidate solutions in the optimization process, operators performing mutations or crossover are needed. A mutation of the Tanner graph is reproduced with the use of the following operations:

- Addition of  $R$  random edges,

- Erasure of  $R$  random edges,

- Addition of an edge connected to a chosen node  $u \in G$  and some node  $v \in G$ :  $d(u, v) > M$  and  $d(u, v) \equiv 1 \pmod{2}$  (connection of two distant nodes),

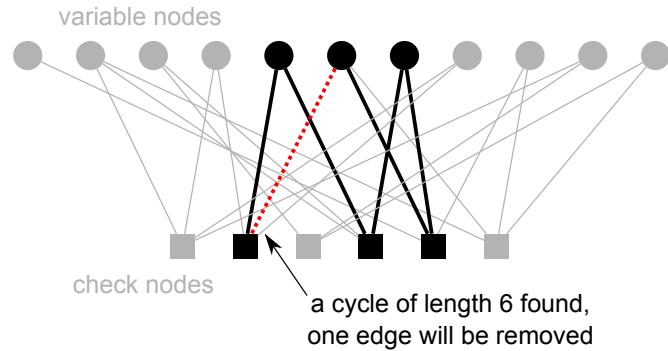

- Erasure of an edge in order to break a cycle of length  $l < Q$ ; the example can be seen in Fig. 4-6,

- Addition of an edge between nodes  $u, v \in G$ :  $(d_G(u) = 1 \wedge d_G(v) = 1)$  and  $d(u, v) \equiv 1 \pmod{2}$  (connection of nodes with a degree equal to one),

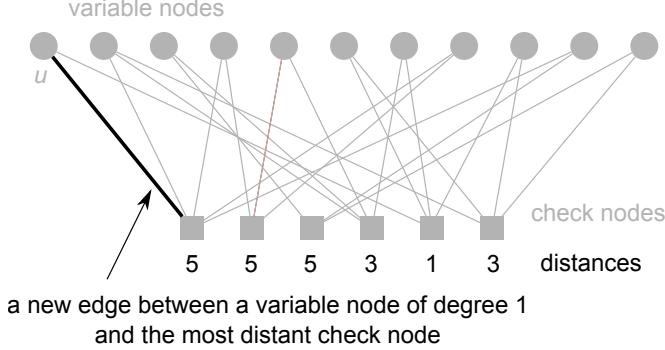

- Addition of an edge between nodes  $u, v \in G$ :  $d_G(v) = 1$  and  $d(u, v) = \max\{d(u, v) | d(u, v) \equiv 1 \pmod{2}\}$ ; the example can be seen in Fig. 4-7,

where  $G$  is the Tanner graph,  $E$  are edges of the graph  $G$ , and parameters  $R, M, Q$  are chosen randomly with regard to the Tanner graph size (it is convenient to tune them experimentally for each optimization task). The operation performed for reproducing one mutant is also chosen randomly. The operator works with graph search algorithms for finding cycles in the Tanner graph.

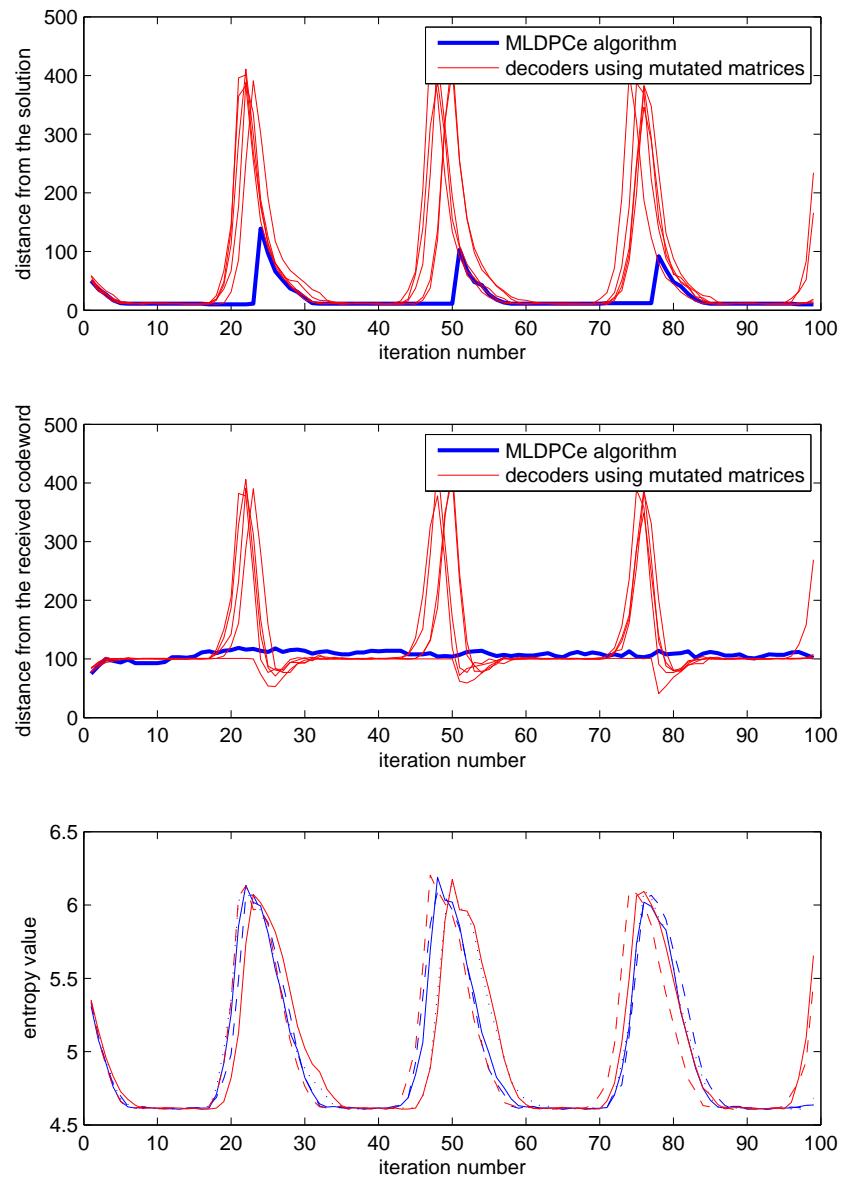

Figure 4-6: Breaking cycles in the Tanner graph as an example.

### 4.2.3 Recombination of Tanner graphs

Supposing  $(VN, CN)$  - bipartite graph  $G$  as the Tanner graph of the LDPC code  $\mathcal{C}$ , a coloured subgraph  $H^\beta$  (called the chromosome), such  $H \subseteq G$ , we define algorithms

Figure 4-7: Adding a new edge connected with the node  $u : d_G(u) = 1$  as an example.

to combine chromosomes  $H_i^\beta$  in order to create a new Tanner graph  $G_{TG}$ ,

$$G_{TG} = \left( U = \bigcup U_i, E = \left\{ \bigcup E_i, \{E_j\} \right\} \right), \quad (4.1)$$

where  $E_i$  are edges of chromosomes  $H_i$ ,  $E_j$  are edges ensuring that graph  $G_{TG}$  is connected.  $U_i$  are node chromosomes.

A vertex colouring function  $\alpha$ ,

$$\alpha : v \in G \rightarrow [0, 1], \quad (4.2)$$

is used to mark nodes which are included in the chromosome  $H$ . The algorithm implementing the vertex colouring works with 3 parameters,  $v_{req}$  (the number of requested variable nodes),  $c_{req}$  (the number of requested check nodes), and  $v_{start}$  (the node where the colouring function starts). The nodes of the graph  $G$  are selected with the use of the Breadth-First Search (BFS) starting at  $v_{start}$  and terminated when the number of selected nodes reaches the values  $v_{req}$  and  $c_{req}$ , as can be seen in Algorithm 6. The algorithm partly keeps the degree distribution and other parameters, e. g. cycle occurrence, of the graph  $G$ . The reproduced chromosome  $H^\beta$  uses vertex colouring function  $\beta$ ,

$$\beta : v \in H \rightarrow [0, \max(d_{vmax}, d_{cmax})], \quad (4.3)$$

where  $d_{cmax}$  is the maximum check node degree and  $d_{vmax}$  is the maximum variable

node degree, as the difference between the original node degree and the node degree in the chromosome  $H$ , as defined in Algorithm 7. These values are then applied in the recombination function for edge addition to connect the input chromosomes  $H_i$  among each other, as described in Algorithm 8. The recombination function reproduces a new Tanner graph  $G_{TG}$ , consisting of chromosomes  $H_{set} = \{H_i^\beta\}$ ,  $i = 1, \dots, k$ .

The colouring algorithm implements BFS in order to partly keep the distribution of cycles in the resulting chromosome  $H$ . By combining several graphs together in the optimization process, we can get codes with interesting correction capabilities measured by the fitness function.

---

**Algorithm 6** Node colouring

---

1: **procedure** COLOUR NODES

**Input:**  $v_{req}$  - requested variable nodes,

$c_{req}$  - requested check nodes,

$(VN, CN)$  - bipartite graph  $G$ ,

$v_{start} \in G$  - starting node for traversing

**Output:** coloured graph  $G^\alpha$

```

2:   for all  $u \in G$  do

3:      $\alpha(u) = 0$

4:   end for

5:    $\alpha(v_{start}) = 1$

6:   for  $k = 0$  to  $(v_{req} + c_{req})$  do

7:     for all  $u \in \{v | v_{start} \rightarrow^k u\}$  do

$\triangleright$  Implemented via BFS algorithm

8:       if  $u \in VN$  and  $|\{u | \alpha(u) = 1\}| < v_{req}$  then

9:          $\alpha(u) = 1$

10:      end if

11:      if  $u \in CN$  and  $|\{u | \alpha(u) = 1\}| < c_{req}$  then

12:         $\alpha(u) = 1$

13:      end if

14:      if  $|\{u \in CN | \alpha(u) = 1\}| = c_{req}$

and  $|\{u \in VN | \alpha(u) = 1\}| = v_{req}$  then

15:        return  $(G, \alpha)$

16:      end if

17:    end for

18:  end for

19: end procedure

```

---

---

**Algorithm 7** Generating chromosome

---

```

1: procedure CHROMOSOME GENERATION

Input:  $(VN, CN)$ -bipartite coloured graph  $G^\alpha$

Output: chromosome graph  $H^\beta$

2:    $U_H = \{\forall u \in G^\alpha : \alpha(u) = 1\}$

3:    $E_H = \{\forall e = (u, v) \in G^\alpha : \alpha(u) = 1 \wedge \alpha(v) = 1\}$

4:   for all  $u \in U_H$  do