# Lattice QCD Optimization and Polytopic Representations of Distributed Memory

Michael Kruse

## ► To cite this version:

Michael Kruse. Lattice QCD Optimization and Polytopic Representations of Distributed Memory. Distributed, Parallel, and Cluster Computing. Paris-Sud XI, 2014. English. <tel-01078440>

HAL Id: tel-01078440

<https://hal.inria.fr/tel-01078440>

Submitted on 29 Oct 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# UNIVERSITÉ PARIS-SUD

ÉCOLE DOCTORALE D'INFORMATIQUE DE PARIS-SUD

INRIA SACLAY ÎLE-DE-FRANCE/LABORATOIRE DE RECHERCHE EN

INFORMATIQUE

DISCIPLINE : INFORMATIQUE

## THÈSE DE DOCTORAT

Soutenue le 26 Septembre 2014 par

**Michael Kruse**

## Lattice QCD Optimization and Polytopic Representations of Distributed Memory

**Directeur de thèse :** Mme. Christine Eisenbeis Directrice de Recherche (INRIA, LRI, Université Paris-Sud XI)

**Composition du jury :**

Rapporteurs :

M. Philippe Clauss Professeur (Université de Strasbourg)

M. Jagannathan Ramanujam Professeur (Louisiana State University)

M. Sid Touati Professeur (Université Nice Sophia Antipolis)

M. Paul Feautrier Professeur émérite (ENS Lyon)

M. Sylvain Conchon Professeur (Université Paris-Sud XI)

M. Olivier Pène Directeur de Recherche retraité (CNRS, LPT Orsay)

M. Gilbert Grosdidier Directeur de Recherche retraité (CNRS, LAL Orsay)

Examinateurs :

Invités :

## Abstract

Motivated by modern day physics which in addition to experiments also tries to verify and deduce laws of nature by simulating the state-of-the-art physical models using large computers, this thesis explores means of accelerating such simulations by improving the simulation programs they run. The primary focus is Lattice Quantum Chromodynamics (QCD), a branch of quantum field theory, running on IBM newest supercomputer, the Blue Gene/Q.

In a first approach, the source code of tmLQCD, a Lattice QCD program, is improved to run faster on the Blue Gene machine. Its most performance-relevant operation is a 8-point stencil in 4 dimensional space. Two different optimization strategies are pursued: One with the prioritizing spatial and temporal locality, and a second making use of the hardware's data stream prefetcher. On Blue Gene/Q the first strategy reaches up to 20% of the peak theoretical floating point operation performance of that machine. The second strategy with up to 54% of peak is much faster at the cost of using 4 times more memory by storing the data in the order they will be used in the next stencil operation, duplicating data where necessary.

Other techniques exploited are direct programming of the messaging hardware (called MUSPI by IBM), a low-overhead work distribution mechanism for threads, explicit data prefetching of data (using dcbt instructions) and manual vectorization (using QPX; width-4 SIMD instructions). Hardware-based list prefetching and transactional memory – both distinct and novel features of the Blue Gene/Q system – did not improve the program's performance.

The second approach is the newly-written LLVM compiler extension called *Molly* which optimizes the program itself, specifically the distribution of data and work between the nodes of a cluster machine such as Blue Gene/Q. Molly represents arrays using integer polyhedra and uses another already existing compiler extension Polly which represents statements and loops using polyhedra. When Molly knows how data is distributed among the nodes and where statements are executed, it adds code that manages the data flow between the nodes. Molly can also permute the order of data in memory.

Molly's main task is to cluster data into sets that are sent to the same target into the same buffer because single transfers involve a massive overhead. We present an algorithm that minimizes the number of transfers for unparametrized loops using anti-chains of data flows. In addition, we implement a heuristic that takes into account how the programmer wrote the code. Asynchronous communication primitives are inserted right after the data is available respectively just before it is used. A runtime library implements these primitives using MPI.

Molly manages to distribute any code that is representable by the polyhedral model, but does so best for stencils codes such as Lattice QCD. Compiled using Molly, the Lattice QCD stencil reaches 2.5% of the theoretical peak performance. The performance gap is mostly because all the other optimizations are missing, such as vectorization. Future versions of Molly may also effectively handle non-stencil codes and use make use of all the optimizations that make the manually optimized Lattice QCD stencil so fast.

## Résumé

La physique actuelle cherche, à côté des expériences, à vérifier et déduire les lois de la nature en simulant les modèles physiques sur d'énormes ordinateurs. Cette thèse explore comment accélérer ces simulations en améliorant les programmes qui les font tourner. L'application de référence est la chromodynamique quantique sur réseaux (LQCD pour "Lattice Quantum Chromodynamics"), une branche de la théorie quantique des champs, tournant sur le plus récent des supercalculateurs d'IBM, le Blue Gene/Q.

Dans un premier temps, on améliore le code source de tmLQCD, un programme de LQCD, dont l'opération clef pour la performance est un stencil à 8 points en dimension 4. On étudie deux stratégies d'optimisation différentes : la première se donne comme priorité d'améliorer la localité spatiale et temporelle ; la seconde utilise le préchargement matériel de flux de données. Sur le Blue Gene/Q, la première stratégie permet d'atteindre 20% de la performance crête théorique. La seconde, avec jusqu'à 54% de la performance crête est bien meilleure mais utilise 4 fois plus de mémoire car elle stocke les résultats dans l'ordre où les utilise le stencil suivant, ce qui requiert de dupliquer des données.

Les autres techniques exploitées sont la programmation directe du système de communication (appelé MUSPI chez IBM), un mécanisme allégé de gestion des threads, le préchargement explicite de certaines données (à l'aide de l'instruction dcbt) et la vectorisation manuelle (en utilisant les instructions SIMD de largeur 4; appelé QPX par IBM). Le préchargement de liste et la mémoire transactionnelle - deux nouveaux mécanismes du Blue Gene/Q - n'améliorent pas les performances.

Dans un second temps, on présente la réalisation d'une extension appelé *Molly* au compilateur LLVM, pour optimiser automatiquement le programme, et plus précisément la distribution des données et des calculs entre les nœuds d'un cluster tel que le Blue Gene/Q. Molly représente les tableaux par des polyèdres entiers et utilise l'extension existante Polly qui représente les boucles et les instructions par des polyèdres. Partant de la spécification de la distribution des données et de l'emplacement des calculs, Molly ajoute le code qui gère les flots de données entre les nœuds de calcul. Molly peut aussi permute l'ordre des données en mémoire.

La tâche principale de Molly est d'agrégner les données dans des ensembles qui sont envoyés dans le même tampon au même destinataire, pour éviter l'overhead des transferts trop petits. Nous présentons un algorithme qui minimise le nombre de transferts pour des boucles non-paramétrées, basé sur les antichaînes du flot des données. De plus, nous implementons une heuristique qui tient compte de la manière dont le programmeur a écrit son code. Les primitives de communication asynchrone sont insérées juste après que les données soient disponibles – respectivement juste avant qu'elles soient utilisées. Une bibliothèque runtime implémente ces primitives en utilisant MPI.

Molly gère la distribution pour tout code représentable dans le modèle polyédrique, mais fonctionne mieux pour du code à stencil tel LQCD. Compilé avec Molly, le code LQCD atteint 2,5% de la performance crête. L'écart de performance est surtout dû au fait que les autres optimisations ne sont pas faites, par exemple la vectorisation. Les versions futures de Molly pourraient aussi gérer efficacement les codes non à stencil et exploiter les autres optimisations qui ont rendu le code LQCD optimisé à la main si rapide.

## Zusammenfassung

Zusätzlich zur Experimentalphysik versucht die moderne Naturwissenschaft auch Naturgesetze durch Computersimulationen auf Großrechnern herzuleiten und zu verifizieren. Hierdurch motiviert, untersucht diese Arbeit Möglichkeiten zur weiteren Beschleunigung durch das Verbessern der darauf laufenden Programme. Der Schwerpunkt liegt auf das Optimieren von Anwendungen für Gitter-Quantenchromodynamik (Lattice QCD) für IBMs neuestem Großrechner, Blue Gene/Q.

Der erste Ansatz besteht aus dem Anpassen des Quelltextes von tmLQCD, einem Programm für Lattice QCD-Simulationen, an den Blue Gene Rechner. Seine für die Geschwindigkeit wichtigste Operation ist ein 8-Punkt-Stencil in 4 Dimensionen. Dabei werden zwei verschiedene Optimierungsstrategien verfolgt : Eine zur Verbesserung der zeitlichen und örtlichen Nähe und eine Zweite um der Hardware das Vorausladen der Datenströme zu ermöglichen. Auf dem Blue Gene/Q erreicht die erste Strategie bis zu 20% der theoretisch möglichen Geschwindigkeit für Gleitkommaoperationen. Die zweite Strategie ist mit bis zu 54% derselben deutlich erfolgreicher, mit dem Nachteil eines bis zu 4x höherem Speicherverbrauchs durch eine Umsortierung der Daten in Lesereihenfolge inklusive Duplizierung mehrfach gelesener Werte.

Weitere genutzte Techniken beinhalten sind der direkte Zugriff auf die Kommunikationseinheit des Blue Gene/Q (von IBM auf den Namen MUSPI getauft), ein schneller Mechanismus für die Thread-Arbeitsverteilung, explizites Vorausladen von in kürze benötigter Daten und manueller Vektorisierung mittels 256-Bit SIMD-Instruktionen (QPX genannt). Transaktionaler Speicher sowie Hardware List Prefetching – beides neue und einzigartige Funktionen des Blue Gene/Q-Prozessors – führten leider nicht zu einer Geschwindigkeitsverbesserung.

Der zweite Ansatz ist eine Erweiterung für den LLVM-Compiler mit dem Namen Molly welche Programme selbstständig parallelisiert, speziell für die Systeme mit verteiltem Speicher wie dem Blue Gene/Q. Molly stellt Arrays mit Hilfe von Polyedern dar und benutzt die bereits existierende Erweiterung Polly welche Anweisungen und Schleifen als Polyeder darstellt. Bei gegebener Datenverteilung zwischen den Knoten eines Clusters kann Molly den zur Datenfluss notwendigen Anweisungen generieren. Molly kann auch Daten im Speicher eines Einzelknotens umordnen.

Mollys Hauptaufgabe ist das Zusammenstellen von Daten zum selben Ziel zu einer Nachricht weil einzelne Übertragungen zu lange benötigen würden. Wir stellen einen Algorithmus mittels Antiketten vor welcher die Anzahl der Übertragungen minimiert wenn die Schleifen unparametrisiert sind. Eine Heuristik, die in Molly implementiert ist, orientiert sich stattdessen an der Quelltextstruktur. Anweisungen für asynchrone Datenkommunikation werden an der Stelle eingefügt, an dem die zu übertragenen Daten verfügbar sind, sowie kurz bevor sie auf dem Ziel benötigt werden. Eine Laufzeitbibliothek übersetzt diese Anweisungen in MPI-Aufrufe.

Molly kann prinzipiell jeden das Polytopmodell darstellbare Quelltexte parallelisieren, funktioniert aber am besten für Stencilcodes wie Lattice QCD. Mittels Molly kompiliert erreicht es 2.5% der theoretisch möglichen Gleitkommageschwindigkeit. Der Unterschied zur manuell optimierten Version kommt hauptsächlich durch das Fehlen anderer Optimierungen wie der Vektorisierung zustande. Zukünftige Versionen von Molly könnten auch andere Codes effektiv parallelisieren und ebenfalls die noch fehlenden Optimierungen anwenden wegen derer die erste Strategie so erfolgreich war.

# Contents

|                                                                         |           |

|-------------------------------------------------------------------------|-----------|

| <b>List of Figures</b>                                                  | <b>9</b>  |

| <b>List of Tables</b>                                                   | <b>10</b> |

| <b>List of Algorithms</b>                                               | <b>11</b> |

| <b>Listings</b>                                                         | <b>12</b> |

| <b>1 Introduction</b>                                                   | <b>13</b> |

| 1.1 Motivation . . . . .                                                | 14        |

| 1.2 Contributions of this Thesis . . . . .                              | 15        |

| 1.3 Thesis Structure . . . . .                                          | 16        |

| <b>I Optimization of Lattice QCD for the Blue Gene/Q</b>                | <b>17</b> |

| <b>2 Lattice Quantum Chromodynamics</b>                                 | <b>19</b> |

| 2.1 Quantum Chromodynamics . . . . .                                    | 19        |

| 2.2 Lattice QCD . . . . .                                               | 21        |

| 2.3 Iterative Solver . . . . .                                          | 25        |

| 2.4 Wilson-Dirac Operator Stencil . . . . .                             | 26        |

| 2.5 Domain Decomposition . . . . .                                      | 30        |

| 2.6 tmLQCD . . . . .                                                    | 31        |

| <b>3 The Blue Gene/Q Supercomputer</b>                                  | <b>33</b> |

| 3.1 Blue Gene/Q Architecture . . . . .                                  | 33        |

| 3.2 The Processor . . . . .                                             | 34        |

| 3.3 Memory . . . . .                                                    | 37        |

| 3.4 Network . . . . .                                                   | 40        |

| <b>4 Manual Optimizations</b>                                           | <b>43</b> |

| 4.1 Separation of Even and Odd Elements . . . . .                       | 43        |

| 4.2 Floating-Point Instruction Vectorization . . . . .                  | 44        |

| 4.3 Load-Store Vectorization . . . . .                                  | 48        |

| 4.4 Lattice Linearization and Iteration Order . . . . .                 | 50        |

| 4.5 Precision . . . . .                                                 | 60        |

| 4.6 Layout Selection at Runtime . . . . .                               | 60        |

| 4.7 Cache Management . . . . .                                          | 61        |

| 4.8 Assembly-Level Optimizations . . . . .                              | 64        |

| 4.9 Symmetric Multiprocessing and Simultaneous Multithreading . . . . . | 66        |

| 4.10 Elementwise Operations . . . . .                                   | 68        |

---

|                                                                  |            |

|------------------------------------------------------------------|------------|

| 4.11 Reductions . . . . .                                        | 68         |

| 4.12 Messaging Unit System Programming Interface . . . . .       | 69         |

| <b>5 Results</b>                                                 | <b>71</b>  |

| 5.1 Fullspinor Layout . . . . .                                  | 72         |

| 5.2 Halfspinor Layout . . . . .                                  | 76         |

| <b>6 Discussion</b>                                              | <b>81</b>  |

| 6.1 Summary . . . . .                                            | 81         |

| 6.2 Conclusions . . . . .                                        | 82         |

| 6.3 Further Possibilities for Optimizations . . . . .            | 83         |

| 6.4 Related Work . . . . .                                       | 86         |

| <b>II Representing Memory Layout in the Polyhedral Model</b>     | <b>89</b>  |

| <b>7 The Polyhedral Model</b>                                    | <b>91</b>  |

| 7.1 Polyhedra . . . . .                                          | 91         |

| 7.2 Static Control Parts . . . . .                               | 98         |

| 7.3 Example: 2D Jacobi . . . . .                                 | 105        |

| <b>8 Distributed Memory Parallelism and the Polyhedral Model</b> | <b>111</b> |

| 8.1 Data Distribution . . . . .                                  | 111        |

| 8.2 Work Distribution . . . . .                                  | 113        |

| 8.3 Data Transfers . . . . .                                     | 114        |

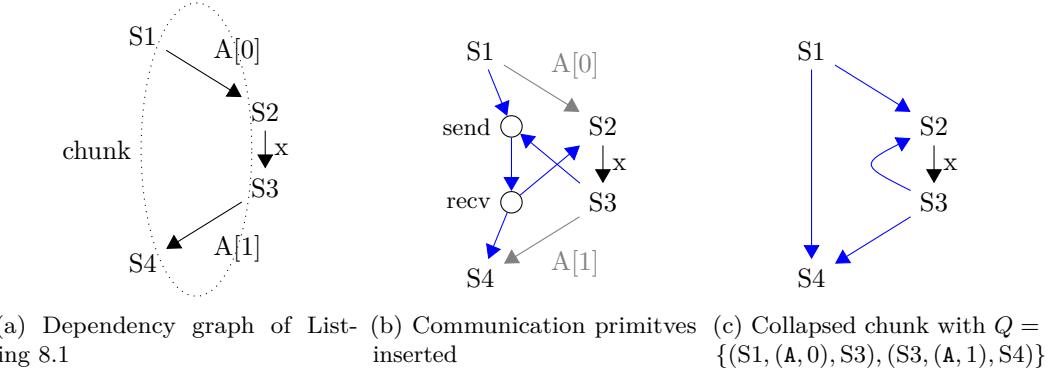

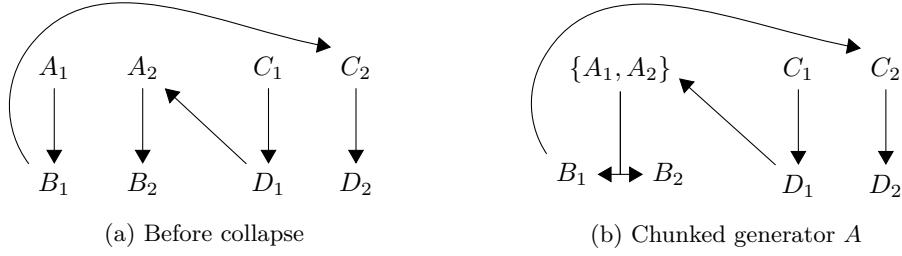

| 8.4 Chunking . . . . .                                           | 115        |

| 8.5 Example: 2D Jacobi . . . . .                                 | 126        |

| <b>9 Molly</b>                                                   | <b>131</b> |

| 9.1 C++ Language Extensions . . . . .                            | 131        |

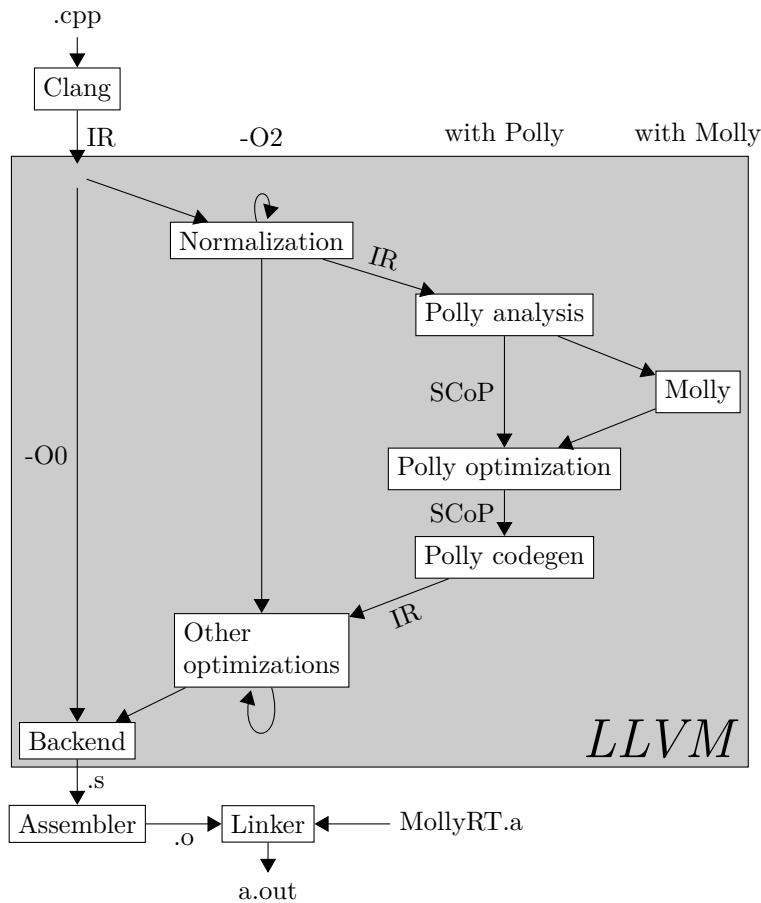

| 9.2 The Toolchain . . . . .                                      | 134        |

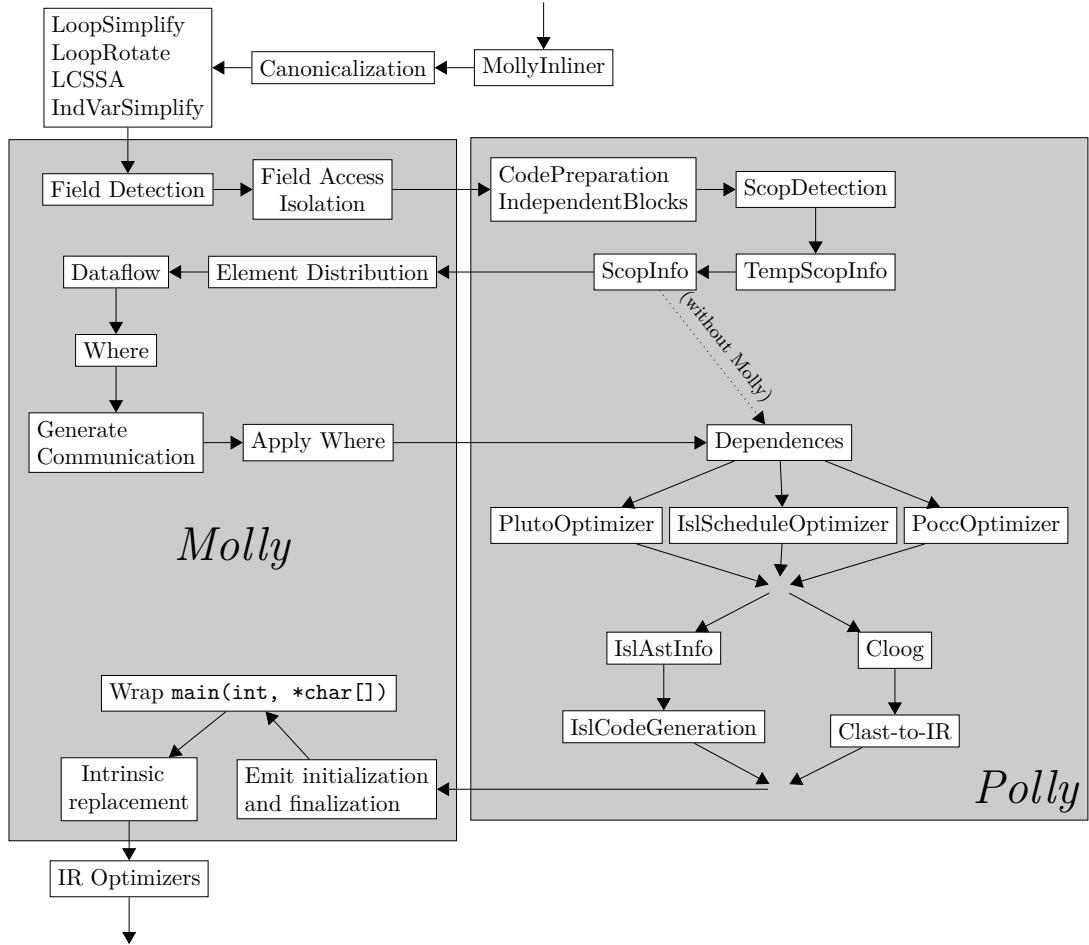

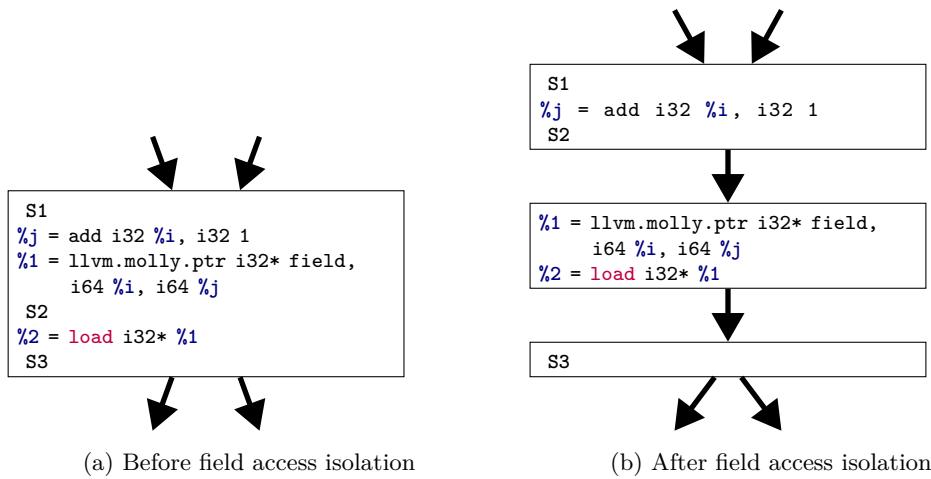

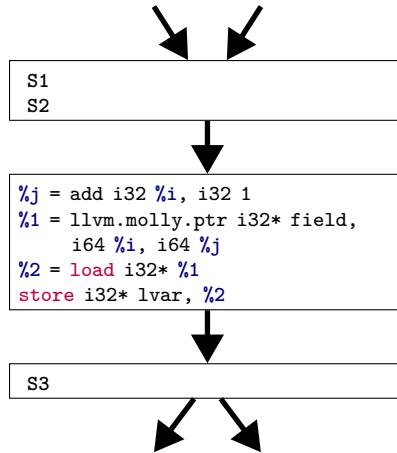

| 9.3 The Molly Pass . . . . .                                     | 139        |

| 9.4 MollyRT . . . . .                                            | 148        |

| <b>10 Results</b>                                                | <b>151</b> |

| 10.1 Jacobi 2D . . . . .                                         | 151        |

| 10.2 Lattice QCD . . . . .                                       | 155        |

| 10.3 Game of Life . . . . .                                      | 160        |

| <b>11 Discussion</b>                                             | <b>163</b> |

| 11.1 Summary . . . . .                                           | 163        |

| 11.2 Conclusions . . . . .                                       | 164        |

| 11.3 Future Work . . . . .                                       | 165        |

| 11.4 Related Work . . . . .                                      | 167        |

| <b>A Original Hopping Matrix Source</b>                          | <b>169</b> |

| <b>B Symbol Summary</b>                                          | <b>175</b> |

| B.1 Sets, Relations and Functions . . . . .                      | 175        |

| B.2 Typical Placeholder and Constant Names . . . . .             | 177        |

# List of Figures

|      |                                                                                    |     |

|------|------------------------------------------------------------------------------------|-----|

| 2.1  | Discretized space-time . . . . .                                                   | 22  |

| 2.2  | 4D neighbors . . . . .                                                             | 23  |

| 2.3  | Dirac operator stencil data flow . . . . .                                         | 27  |

| 2.4  | Flow in the Dirac stencil with projection . . . . .                                | 29  |

| 2.5  | Domain Decomposition . . . . .                                                     | 31  |

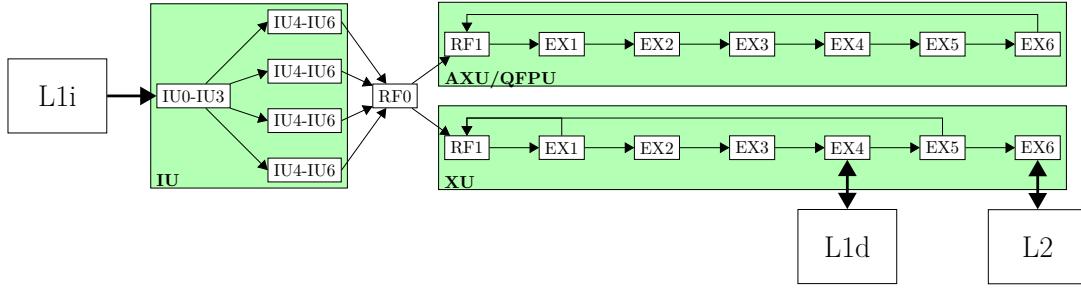

| 3.1  | A2 processor pipeline . . . . .                                                    | 35  |

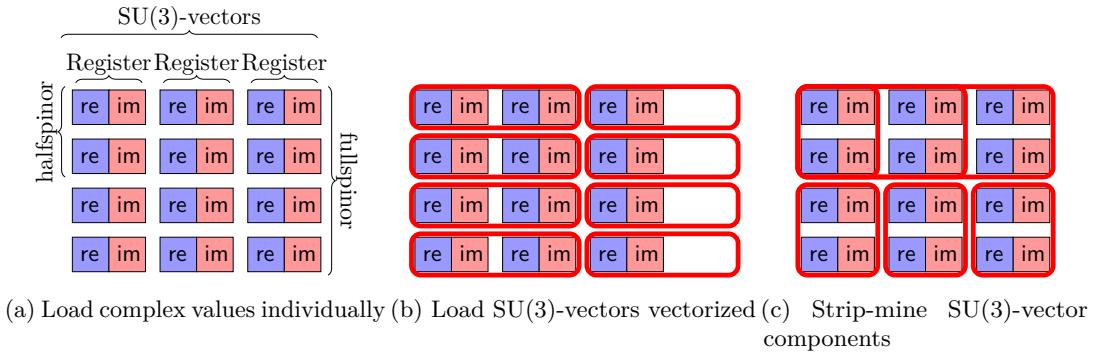

| 4.1  | Choices of combining two complex values . . . . .                                  | 49  |

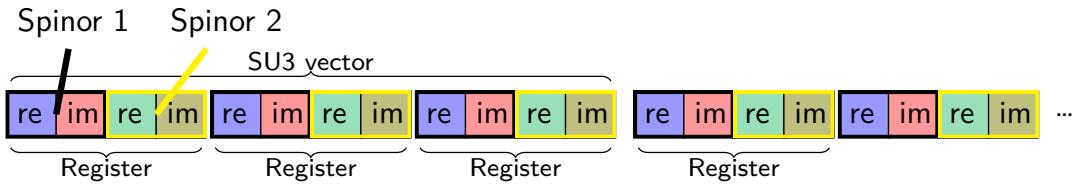

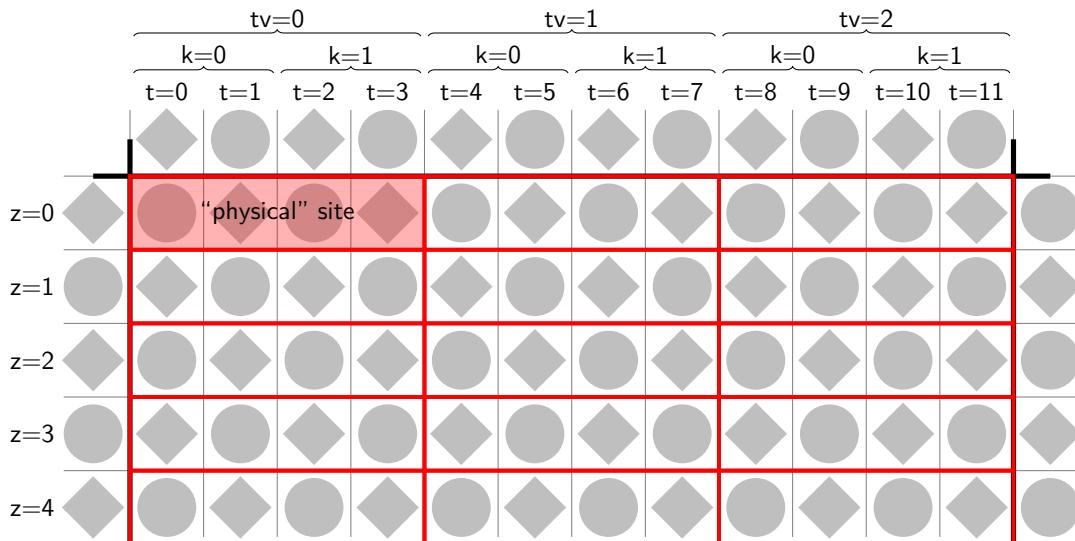

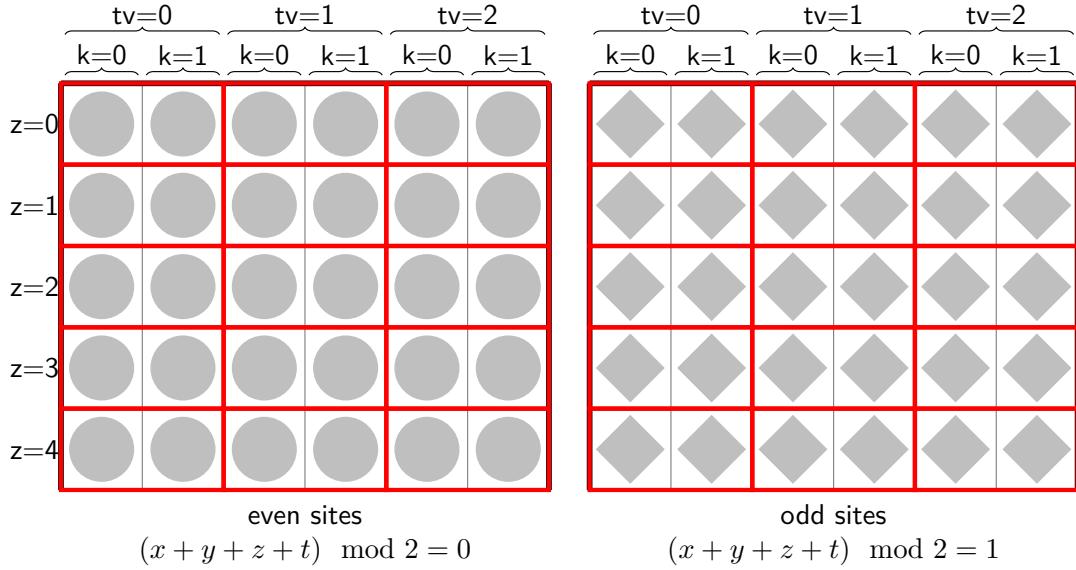

| 4.2  | Data ordering of physical site . . . . .                                           | 50  |

| 4.3  | Coordinates of physical sites . . . . .                                            | 51  |

| 4.4  | Storing sites with even and odd coordinates in different arrays . . . . .          | 52  |

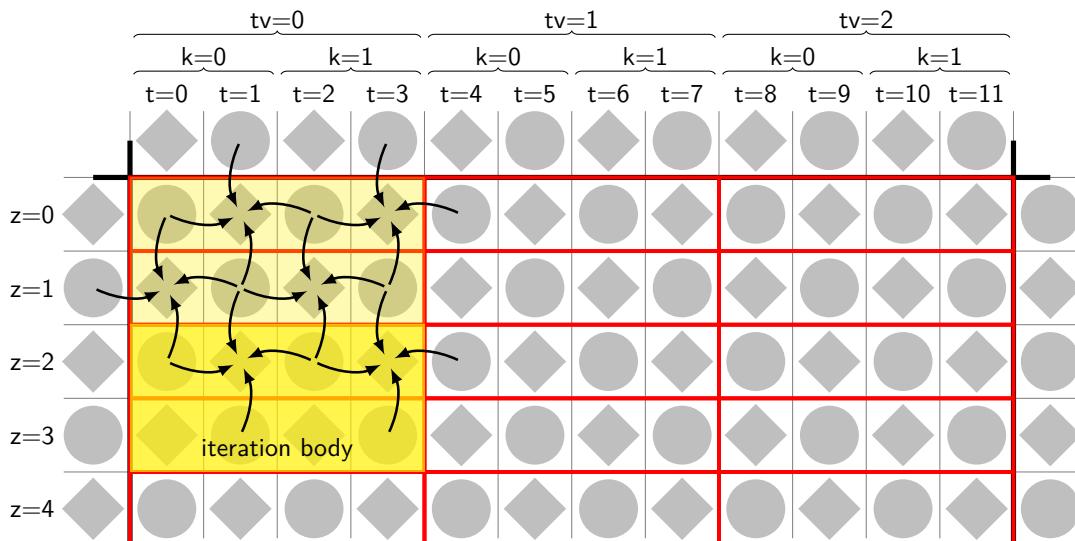

| 4.5  | Element reuse while iterating through the field . . . . .                          | 53  |

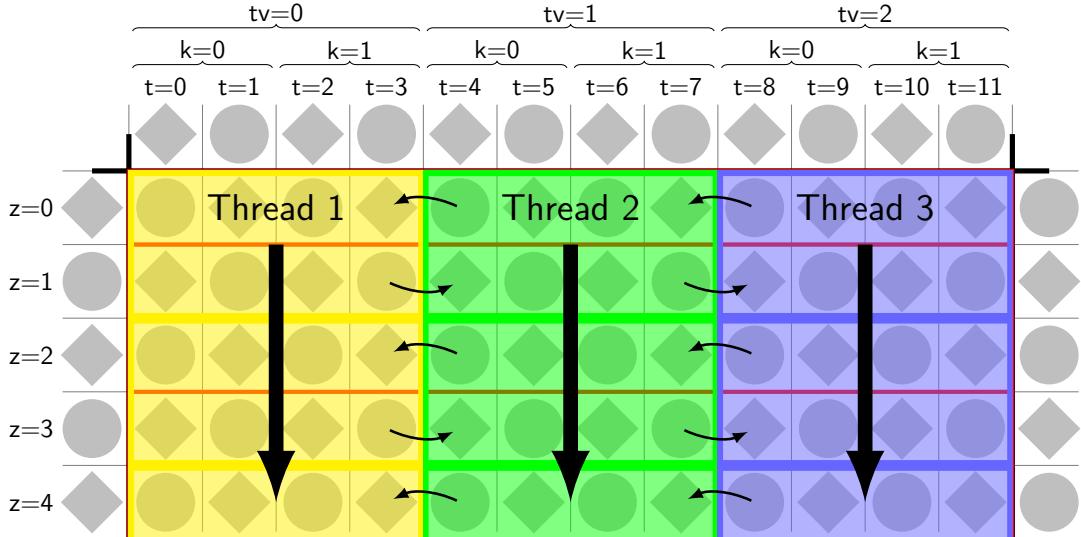

| 4.6  | Wavefronting with multiple threads . . . . .                                       | 54  |

| 4.7  | Alternative shape of physical sites . . . . .                                      | 54  |

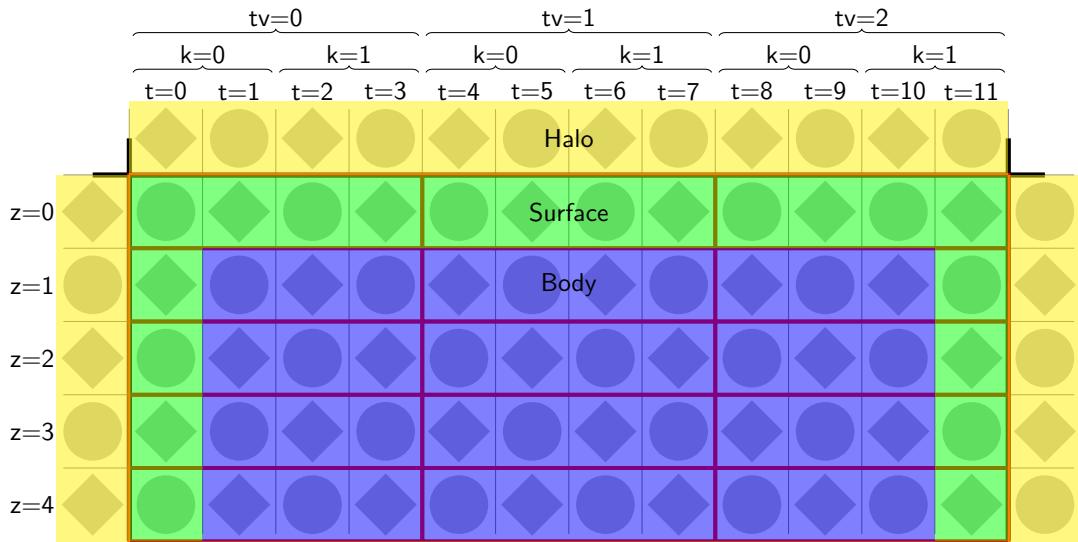

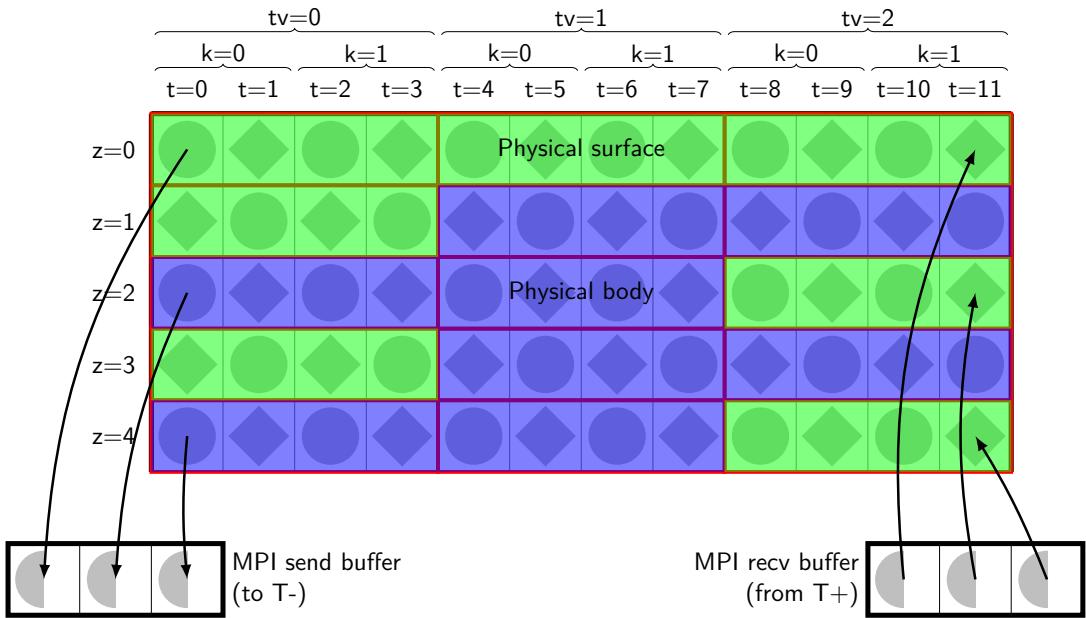

| 4.8  | Body, surface and halo . . . . .                                                   | 55  |

| 4.9  | Physical body and surface . . . . .                                                | 56  |

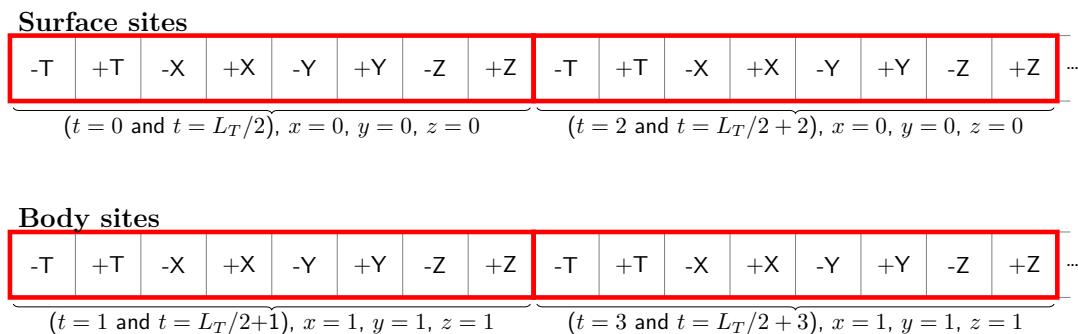

| 4.10 | Halfspinor layout for even sites . . . . .                                         | 57  |

| 4.11 | Stencil and inverse stencils . . . . .                                             | 58  |

| 4.12 | Reduction schema . . . . .                                                         | 69  |

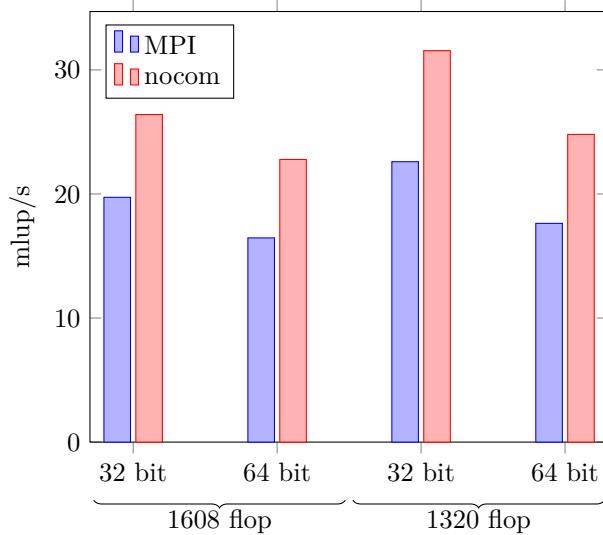

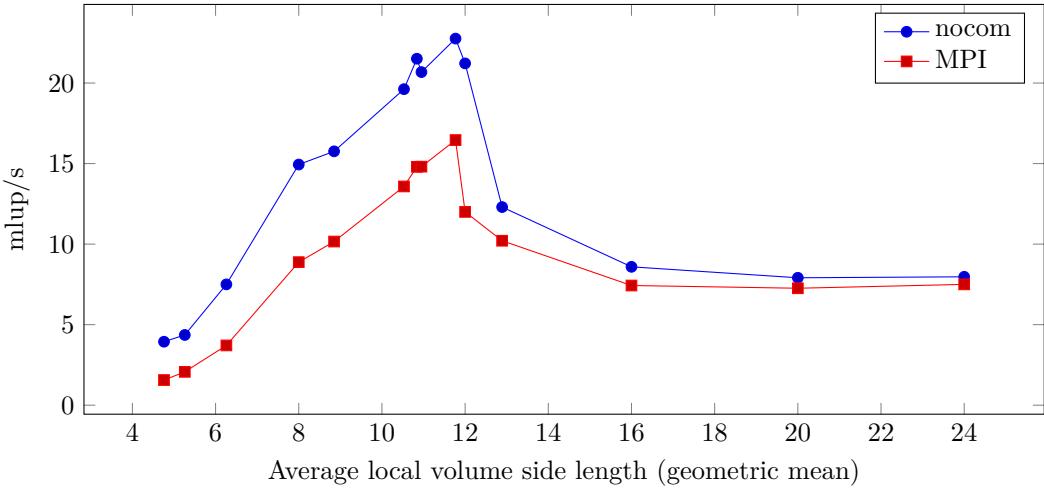

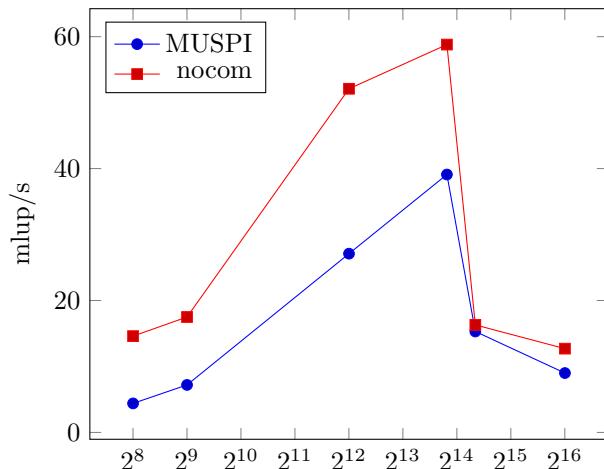

| 5.1  | Visualization of Table 5.1 . . . . .                                               | 73  |

| 5.2  | Visualization of Table 5.3 . . . . .                                               | 75  |

| 5.3  | Visualization of Tables 5.5 and 5.6 . . . . .                                      | 77  |

| 5.4  | Visualization of Table 5.8 . . . . .                                               | 78  |

| 8.1  | Illustration of chunking function (8.1) . . . . .                                  | 116 |

| 8.2  | Counterexample . . . . .                                                           | 121 |

| 9.1  | Molly toolchain interior . . . . .                                                 | 135 |

| 9.2  | Molly pass internals . . . . .                                                     | 140 |

| 9.3  | Field access isolation . . . . .                                                   | 141 |

| 9.4  | After IndependentBlocks . . . . .                                                  | 142 |

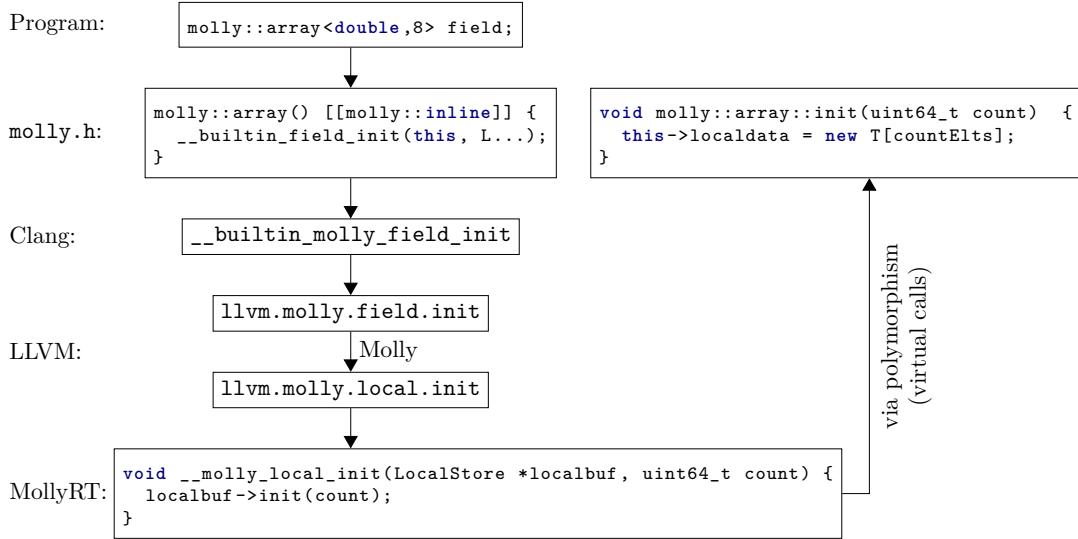

| 9.5  | Simplified transformation/call sequence for local storage initialization . . . . . | 149 |

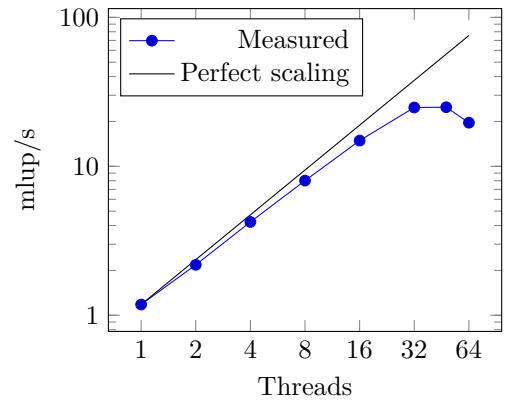

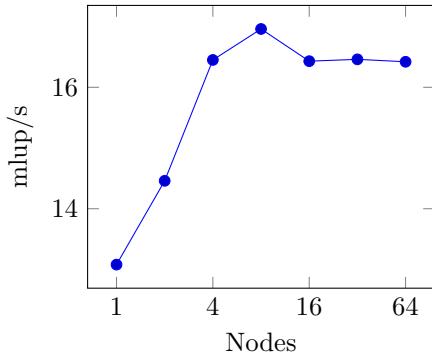

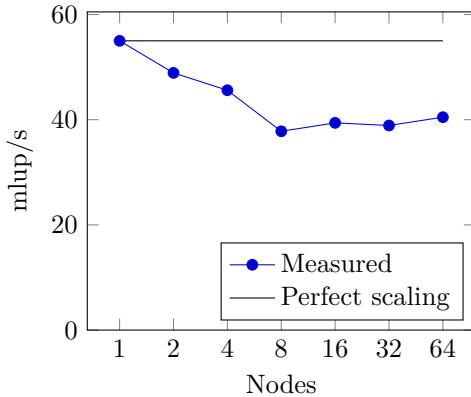

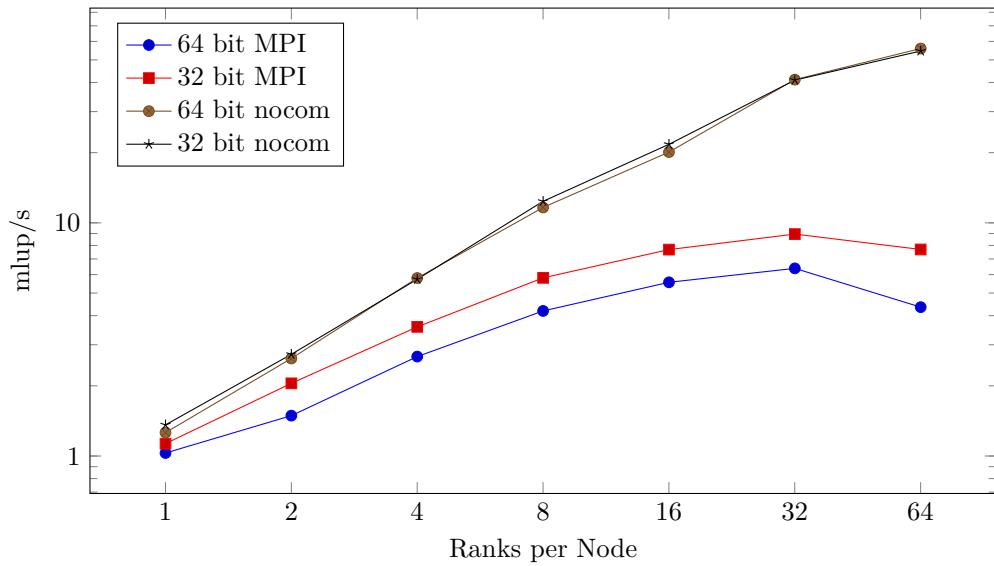

| 10.1 | Visualization of Table 10.1 . . . . .                                              | 153 |

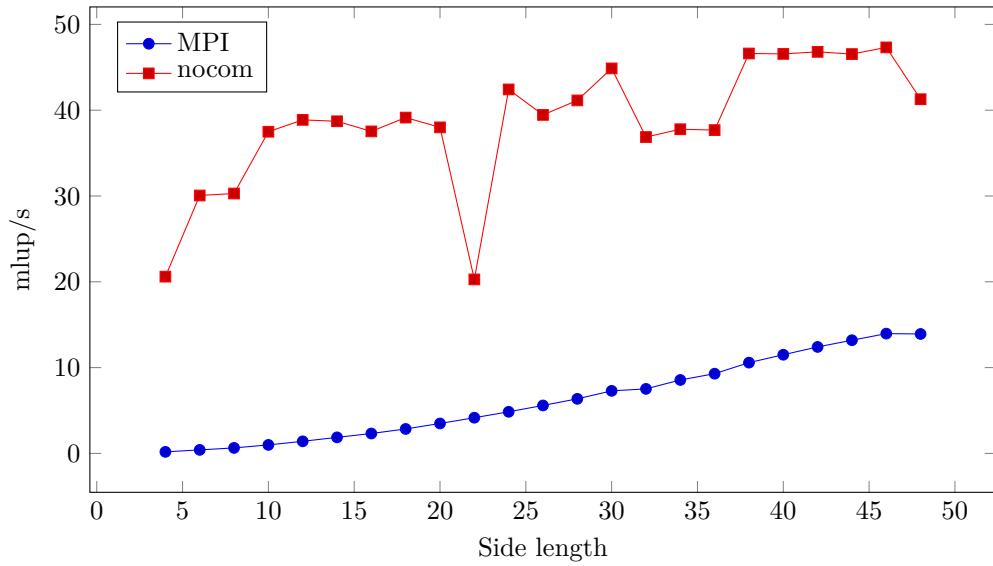

| 10.2 | Visualization of Table 10.2 . . . . .                                              | 154 |

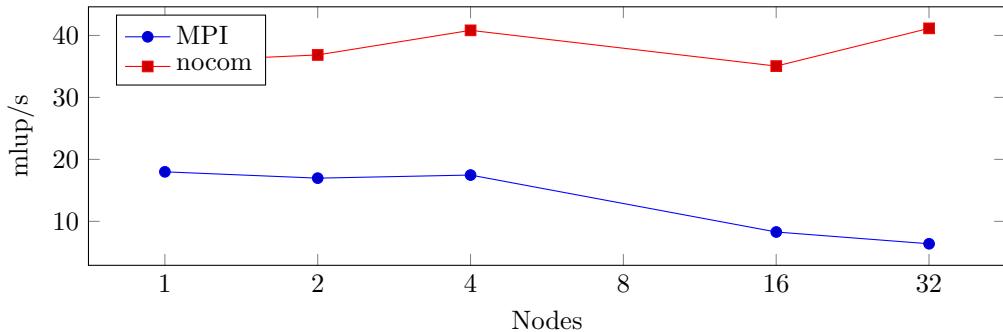

| 10.3 | Visualization of Table 10.3 . . . . .                                              | 154 |

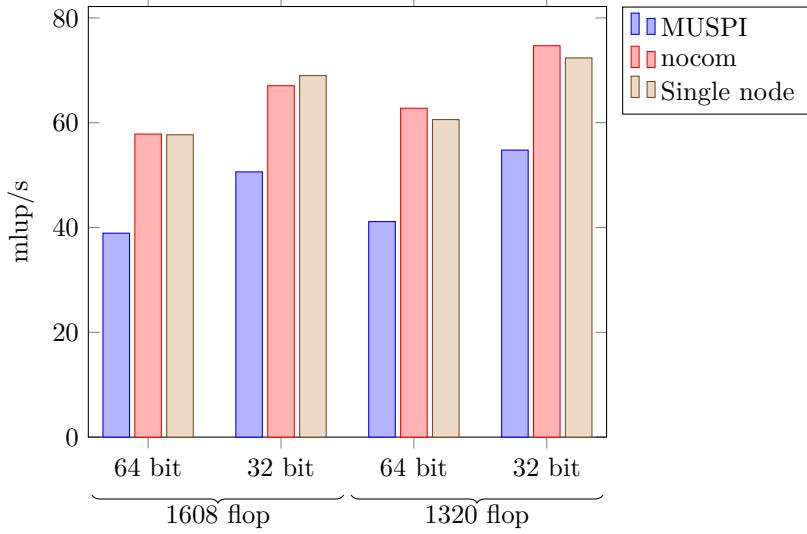

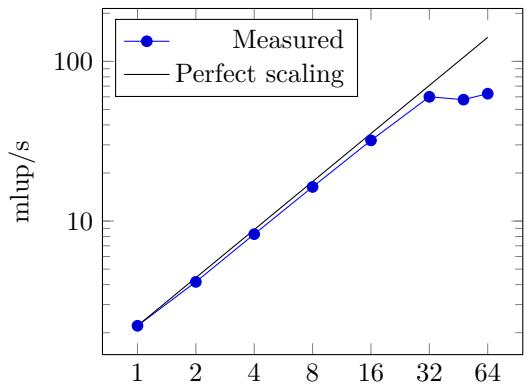

| 10.4 | Visualization of Table 10.4 . . . . .                                              | 156 |

# List of Tables

|      |                                                           |     |

|------|-----------------------------------------------------------|-----|

| 2.1  | Computational complexity of a single stencil . . . . .    | 30  |

| 2.2  | Field element sizes . . . . .                             | 30  |

| 2.3  | Bytes of memory access per stencil execution . . . . .    | 30  |

| 3.1  | Small Blue Gene/Q job sizes . . . . .                     | 40  |

| 3.2  | QCDOC and Blue Gene family comparison . . . . .           | 42  |

| 4.1  | Cache lines occupied by elements . . . . .                | 61  |

| 5.1  | Featured fullspinor layout results . . . . .              | 72  |

| 5.2  | Varying number of threads . . . . .                       | 74  |

| 5.3  | Varying local volume . . . . .                            | 74  |

| 5.4  | Weak scaling . . . . .                                    | 75  |

| 5.5  | Featured halfspinor layout result . . . . .               | 76  |

| 5.6  | Single node results . . . . .                             | 76  |

| 5.7  | Varying number of threads . . . . .                       | 77  |

| 5.8  | Varying local volume . . . . .                            | 78  |

| 5.9  | Weak scaling . . . . .                                    | 79  |

| 9.1  | Data flow categories . . . . .                            | 143 |

| 9.2  | Overview on communication primitives . . . . .            | 144 |

| 9.3  | Selected intrinsics and their replacements . . . . .      | 146 |

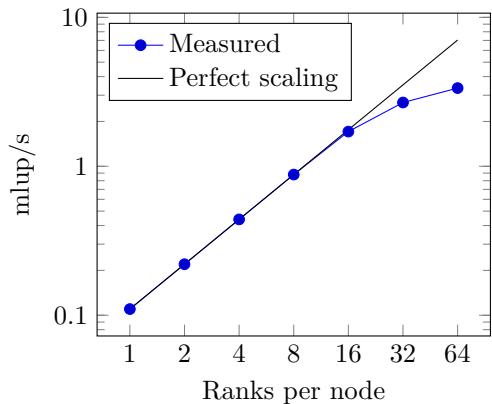

| 10.1 | Jacobi 2D ranks per node execution times . . . . .        | 152 |

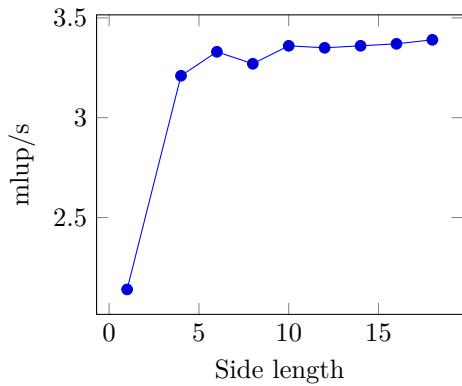

| 10.2 | Jacobi 2D varying subvolumes . . . . .                    | 153 |

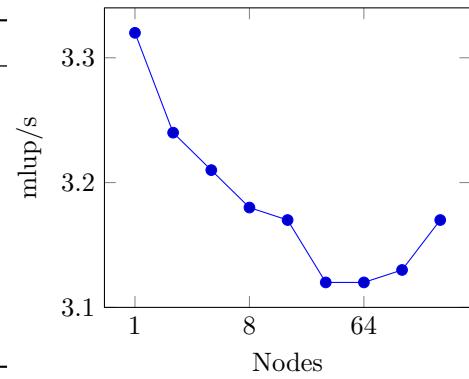

| 10.3 | Jacobi 2D weak scaling . . . . .                          | 154 |

| 10.4 | Lattice QCD featured results . . . . .                    | 156 |

| 10.5 | Lattice QCD results with varying ranks per node . . . . . | 157 |

| 10.6 | Lattice QCD results with varying subvolumes . . . . .     | 157 |

| 10.7 | Lattice QCD weak scaling results . . . . .                | 158 |

| 10.8 | Conway’s Game of Life results . . . . .                   | 161 |

# List of Algorithms

|     |                                          |     |

|-----|------------------------------------------|-----|

| 2.1 | Conjugate Gradient (CG) iterative solver | 25  |

| 4.1 | Explicit prefetch                        | 64  |

| 8.1 | Antichain chunking                       | 118 |

| 8.2 | Schedule-dependent chunking heuristic    | 120 |

# Listings

|      |                                                                               |     |

|------|-------------------------------------------------------------------------------|-----|

| 4.1  | First phase of Hopping Matrix: Multiplication and send . . . . .              | 58  |

| 4.2  | Second phase of Hopping Matrix: Receiving and reconstruction . . . . .        | 59  |

| 4.3  | Master/worker algorithm (in C-like pseudocode) . . . . .                      | 67  |

| 4.4  | Worker callee . . . . .                                                       | 68  |

| 7.1  | Example of a Static Control Part . . . . .                                    | 98  |

| 7.2  | Example of a SCoP with structure parameter $N$ . . . . .                      | 99  |

| 7.3  | Jacobi example code . . . . .                                                 | 106 |

| 8.1  | Program to illustrate invalid chunking . . . . .                              | 116 |

| 8.2  | Example program showing the underdefined result of the chunking heuristic . . | 120 |

| 9.1  | Different methods to clear arrays . . . . .                                   | 132 |

| 10.1 | Lattice QCD program for <i>Molly</i> . . . . .                                | 159 |

| 10.2 | Conway's Game of Life . . . . .                                               | 160 |

# 1

## Introduction

In 1974 the physicist Kenneth Geddes Wilson published a theory on how to approximate one of the four fundamental forces in continuous space-time using a finite number of representative measurement points [1]. The points are arranged in an equidistant mesh, also called a *lattice*. The force he described this way was the strong force that pulls quarks to each other. The theory about this strong force is also known as *Quantum Chromodynamics* (QCD), hence the discretized theory is known as *Lattice Quantum Chromodynamics* (Lattice QCD, or just LQCD).

Field theories are different from other physics theories in that these are not about explicit objects that interact and move in space or space-time, like Newtonian gravity. Instead, space-time is understood as having a value at each coordinate in space and time. The value most often is a scalar (a single number like temperature in Kelvin) or a vector (like gravity; the direction of the vector is the direction an object with mass is pulled to and its length is the “strength” of the pull), but Lattice QCD uses mathematical objects called *spinors* instead. As space and time are continuous, there are infinitely such coordinates and therefore cannot be numerically computed, but the discretized approximation introduced by Wilson can.

The computers in 1972 were not yet powerful enough to do such computations, but became stronger over time. With every generation of computers higher lattice density become more and more feasible and therefore it is hoped that the approximation becomes closer and closer to reality.

These simulations are used to derive observable physical constants. Those constants can also be measured experimentally, but confirming them using a second method derived solely from the physical model describing them increases the confidence in the model’s correctness. In case the simulations do not match the observed reality, either the simulation has to be refined or current physics is incorrect. Being falsifiable is a quality of a theory. In this case a new theory deduced from the simulations can advance physics by giving new insights. Moreover, knowing that same physical constants can be derived from others (like electric permeability in vacuum  $\epsilon_0$  from speed of light and magnetic susceptibility) reduces arbitrariness from the theory and therefore simplifies it. Some results of such simulations are presented in [2].

Today lattice simulations run on some of the fastest computers pursuing better approximations by increasing the density of the mesh that results from the discretization of space-time. It increases the number of measurement points and therefore the computational effort. The principle is simple: The more lattice points are simulated the more accurate results can be expected. Simulations on relatively small lattice sizes can be done on every personal computer, we cannot expect new discoveries on this scale.

Computers on large scale are cluster computers – lots of individual compute nodes with a fast connection between them. This implies that every node has its own memory that is not directly accessible from the other nodes, hence such machines are also called *Distributed Memory Machines* (DMMs). A single global memory does not scale to the size of these machines.

Unfortunately, to achieve such computation speed, programming such computers in an efficient manner is more complicated. Just buying a faster computer is not enough, the programs running on it has to be adapted to the specific machine for maximal speed.

## 1.1 Motivation

The program suite *tmLQCD* [3] is a software one can use for such Lattice QCD simulations. It has been written by the ETMC, a high energy physics research collaboration. Like in nearly any software, some parts are executed more often than others; the most executed code is referred to as hotspots, critical parts or kernels. *tmLQCD* already includes an optimization for IBM's *Blue Gene/Q*.

The successor of the *Blue Gene/P* has been introduced in late 2012, named *Blue Gene/Q*. Naturally, one also wants to support this architecture as some computing centers replaced their *Blue Gene/P* machine with the new generation. To continue fast Lattice QCD simulations, the kernels have to be optimized to the new machine as well. The plain C version also works, but is comparatively slow as it does not use many of the hardware features that make the *Blue Gene/Q* fast.

Compared to *Blue Gene/P*, the new machine has some different characteristics that need to be taken into account, as well as new features that did not exist in the previous generation. Straightforward translation of an optimized kernel to the new architecture does not yield the best performance. For optimal performance even the way data is stored in memory needs to be changed. Unfortunately, a lot of code in *tmLQCD* assumes a specific way the data is stored. Changing it, required those parts to be rewritten, even if they do not belong to a hotspot.

Some optimizations are contradictory. One can optimize access patterns or reduce required bandwidth, but generally not both at the same time. One may also try to find a tradeoff between optimization goals, but which choice results in the fastest program is hard to predict. There is usually only one way to find out: Implement both optimizations and measure their execution time. Which version is faster may also depend on what the program's input. In the case of Lattice QCD the size of the lattice has a huge impact on what the bottleneck – the speed-limiting factor – is and therefore there is no single optimal, always-fastest way to optimize a program.

Finding the sweet-spot of optimizations for specific cases is a big task that involves trial-and-error, one that is tackled in this thesis. For each experiment, some code parts must be written and re-written again. Normally in software engineering, the different optimization aspects would be abstracted into different layers such that each of them can be modified independently. For speed optimizations this is not viable because every such abstraction will slow down the application. If lucky, the compiler may remove the abstraction in the compiled program, for instance by inlining a function. This works for relatively easy cases, but generally compilers keep abstractions out of fear to break some special case and/or to limit compile time. In extreme cases, one even has to write the assembler code manually because the compiler does not find the machine code one had in mind. Hence, the optimized hotspots have to be written to closely reflect the output machine code.

This means a lot of repetitive work when trying out a different optimization. Want to change the iteration order? Have to rewrite all the hotspot loops. This is unfortunate since there exists a mathematical model that can cope with many classes of such reorderings. Its research community calls it the *polyhedral model*. Some compilers make use of this model for loop transformations, but their implementations usually lack maturity, and to the programmer it is not visible what the compiler is doing or why not. Dedicated source-to-source transformation tools seem more successful, partly because the user has more control and on average better understanding of what the tool is supposed to do.

The math behind the polyhedral model can also be applied to the element ordering in

memory, something no mainstream compiler does yet. The combination of both may take the bulk from the programmer when doing such speed optimizations. Different versions of the same kernels become unnecessary, replaced by either the compiler knowing what the best reordering is for the platform, or by per-platform annotations chosen by the programmer. It decreases the maintenance cost of existing code since less code needs to be maintained.

Such an evolution already happened with other compiler optimizations. For instance, in the early days of C the only ways to avoid a function call overhead was to “declare” the function as a preprocessor macro. Today’s compilers can inline function if annotated with the `inline` keyword or if the compiler thinks it is advantageous to do so. The general advice is to leave this decision to the compiler, avoiding premature optimization<sup>1</sup>. Actually, assuming a specific reordering is best without measurements *is* premature optimization, especially if those require a rewrite of the non-hotspot parts. The compiler being able to apply reorderings encourages trying out different program transformations.

## 1.2 Contributions of this Thesis

This thesis explores the two main ways of parallelization and general program speed optimizations<sup>2</sup> that do not involve changing the hardware: manual optimization of the source code and optimization by the compiler. Any optimization can be implemented in source – if necessary by going down to assembly level. But new transformations in the compiler must work for the general case, ensure that any well-defined source code does not change its meaning and as far as possible also never runs slower than without such changes. The reward is that the transformation is then applicable to any program automatically.

The use case is Lattice QCD on the Blue Gene/Q supercomputer. First, we change the source code of the tmLQCD program suite, searching for the best transformation for this architecture. Using this experience, we modify a compiler, enabling it to apply some of those optimizations automatically.

The following list describes the work done in the first part of the thesis.

- Adding Blue Gene/Q-optimized versions of the kernels to tmLQCD

- Experimenting with different memory layouts

- Optimization of assembly code generated by IBM’s *IBM XL compiler* [5] (XLC) compiler, especially, *SIMD* instructions

- Reduction of multi-threading overhead

- Implement inter-node communication using low-level hardware commands (*Message Unit System Programming Interface* (MUSPI) instead of *Message Passing Interface* (MPI))

In the second part contributes the following items.

- Development of a model for polyhedral reordering of data in memory and between distributed memory nodes

- Implementing an extension called *Molly* to the *Clang* [6] compiler that does such transformations

---

<sup>1</sup>“There is no doubt that the grail of efficiency leads to abuse. Programmers waste enormous amounts of time thinking about, or worrying about, the speed of noncritical parts of their programs, and these attempts at efficiency actually have a strong negative impact when debugging and maintenance are considered. We should forget about small efficiencies, say about 97% of the time: premature optimization is the root of all evil. Yet we should not pass up our opportunities in that critical 3%” (*Donald Knuth*) [4]

<sup>2</sup>Optimization in this thesis is used in the sense of improving a program’s execution speed. It is not meant to find the fastest (“optimal”) program possible.

- Evaluation of the transformations done by Molly

The Blue Gene/Q-optimized version of tmLQCD is not the fastest possible (“optimal”) implementation of Lattice QCD on Blue Gene/Q. Also, Molly has been prototyped with this single purpose in mind. It is not a ready-to-use implementation for any program, but could be extended that way.

### **1.3 Thesis Structure**

Following the two different kinds of optimizations, this thesis consists of two parts. The first Part starting at Page 19 copes with the manual optimization of tmLQCD for the Blue Gene/Q computer. Part II at Page 91 and onward is about the implementation of Molly, the compiler extension for data layout transformations using the polyhedral model.

Part I starts with a brief overview of the theoretical physics behind Lattice QCD in Chapter 2. Chapter 3 explains the Blue Gene/Q platform and its hardware details that are important for program optimizations and Chapter 4 presents the various optimizations applied to tmLQCD. The experimental results using different combinations of optimization are shown in Chapter 5. The part ends with a summary, more optimization ideas, and related work in Chapter 6.

The second Part begins with an introduction to the polyhedral model in Chapter 7. The following Chapter presents how the same theory can be applied to reordering data in local memory and between nodes of a distributed memory computer. Chapter 9 goes on presenting how it has been implemented as Molly, the extension to the Clang compiler. Experimental results of how well the Molly-optimized programs perform are shown in Chapter 10. The thesis finishes with a summary of this part, similar work by other researchers and ideas for improving Molly in Chapter 11.

## Part I

# Optimization of Lattice QCD for the Blue Gene/Q

# 2 Lattice Quantum Chromodynamics

The current physics standard model knows four fundamental forces that attract or repel particles: Gravity, electromagnetism, the weak force and the strong force. The latter three can be described using *Quantum Field Theories* (QFTs). For instance, the QFT of electromagnetism is called QCD. Finding a QFT of gravity would be a major breakthrough for today's physics, a big step towards a *unified field theory* which would unify all 4 forces into a single theory.

Field theories are a mathematical model in continuous space and time (Euclidean or Minkowski space). It assigns a value to the fields to each point in this space. Particles – themselves expressible as excitation in a field – are influenced by the value of the space-time coordinate they occupy, but the particles may influence the field as well.

In QFT, all the dynamic variables are fields. Considering for example *Quantum Electrodynamics* (QED), there are fields for electrons and positrons, which annihilate or create electrons/positrons from/to the vacuum. There are also photon fields which create or annihilate photons. QFT is more complex to solve. In the case of QED the small coupling of the electron to the photon allows for an analytical computational technique called “Feynman diagrams”, but QCD which corresponds to strong interactions cannot be solved analytically anymore. Numerical simulation using a computer would be an option, but also impossible because space-time is a continuum. A computer simply cannot store values for infinitely many space-time coordinates. Space-time must be discretized first, with the necessary consequence that such a numerical solution is only an approximation of reality.

## 2.1 Quantum Chromodynamics

The force between color charged particles is mediated by exchange particles called *gluons* which exist in 8 different colors. Although hadrons are always white and therefore in principle do not attract or repel each other, they still influence each other when in direct proximity. This is why electric positively charged protons are kept together in a nucleus. It can be explained by residue forces – color charges not evenly distributed inside the hadrons. Merely, color charge is distributed in a quantum field. The spin of gluons is 1, which makes them bosons like the other exchange particles (photons, etc.).

QCD field theory has two main space-time fields. First, there is the quark field<sup>1</sup> describing the charge distribution. For every point in time and space it defines a Dirac 4-spinor of color vectors. Such an element consists of 4 SU(3)-vectors, i.e. an element of  $\mathbb{C}^{4 \times 3}$ . One can define such a 4-spinor for multiple of the 6 quark flavors (up, down, strange, charm, top, bottom) but in the thesis we assume just one flavor. The three complex components of the SU(3) vector represent the amount of charge per color. There are four of them because of the four components of relativistic spinors (Dirac spinors). They are represented as linear combinations

---

<sup>1</sup> Alternative names: fermion field, spinor field, Grassmann field

of the 4 gamma matrices (or Dirac matrices) in the four-dimensional space of Dirac spinors. Spinor fields are typically denoted using the Greek letter  $\psi$ .

The second field is the gluon field<sup>1</sup>. It assigns a  $SU(3)$  ( $3 \times 3$  complex) matrix to each point in space-time and euclidean dimension, i.e. a subset of  $\mathbb{C}^{4 \times 3 \times 3}$ . It characterizes the exchange of color charges into the euclidean direction, by right-multiplying an  $SU(3)$  vector with the matrix. In the following, the capital letter  $A$  denotes a gluon field(s) for the 8 flavors.  $\mu$  stands for one of the 4 space-time dimensions. By convention,  $\mu = 0$  identifies the time dimension whereas 1, 2, 3 are the x, y and z space dimensions respectively.

The influence of all fields can be described using an *action functional*  $\mathcal{S}$ . Typically, it is the path-integral of a Lagrangian or Hamiltonian. Such an action maps a path through space and time to a scalar. In the case of classical field theory the principle of least action now states that the path with the smallest result is the one that is observed in reality, or at least is the one with highest probability. For instance, the Lagrangian of a particle of mass  $m$ , velocity  $v$  and potential energy  $V(t, x)$  at time  $t$  and position  $x$  is

$$\mathcal{L} = \frac{1}{2}mv^2 - V(t, x)$$

and the action functional becomes

$$\mathcal{S}[\phi] = \int_{\phi} \mathcal{L}(\phi(t, x)) dt d^3x = \int_{\phi} \left( \frac{1}{2}m(\partial_t \phi(t, x))^2 - V(\phi(t, x)) \right) dt d^3x .$$

In classical field theory one chooses the path, the trajectory  $\phi(t, x)$ , which minimizes  $\mathcal{S}[\phi]$ . In QFT, all trajectories are taken into account and interfere with each other, and one defines a partition function  $Z$  as

$$Z = \int \mathcal{D}\phi e^{\frac{i}{\hbar} \mathcal{S}[\phi]}$$

where  $\phi$  represents generically all the fields and  $\int \mathcal{D}\phi$  is a continuous sum over all possible values of the fields on all possible paths in space-time. An observable quantity is defined via a given functional of the fields which, say  $\mathcal{O}(\phi)$ . The expected value of the observable  $\mathcal{O}$  is given by

$$\langle \mathcal{O}(\phi) \rangle = \int \mathcal{D}\phi \mathcal{O}(\phi) e^{\frac{i}{\hbar} \mathcal{S}[\phi]} / Z .$$

The observable corresponds to the probability of a path being observed in the quantum-mechanical sense. That is, a measurement and therefore a wave function collapse have to happen in order to get a probability density of events.

The Lagrangian of continuum QCD is

$$\mathcal{L} = \underbrace{\sum_q \bar{\psi}_q [\gamma_{\mu}(\partial_{\mu} - igA_{\mu}) + m_q] \psi_q}_{\text{fermionic action}} + \underbrace{\frac{1}{4} F_{\mu\nu}^2}_{\text{gauge action}} . \quad (2.1)$$

Here  $\mu$  and  $\nu$  are one of the 4 space-time dimensions,  $q$  one of the 6 quark flavors (up, down, strange, charm, bottom, top),  $g$  is the strong force coupling constant,  $m_q$  is the quark's mass,  $A$  is the gluon field,  $\phi_q$  the flavor's quark field and  $\bar{\psi}_q$  ( $= \psi^{\dagger} \gamma_0$  for relativistic quantum mechanics [7]). We will just assume a single flavor in the following. The field strength tensor is

$$F_{\mu\nu}(x) = \partial_{\mu} A_{\nu}(x) - \partial_{\nu} A_{\mu}(x) + ig[A_{\mu}(x), A_{\nu}(x)] .$$

---

<sup>1</sup>Alternative names: gauge field, color space

The fermionic action describes the interaction between gluons and quarks (fermions) and the gauge action is the self-interaction of gluons since these also carry a color charge. The QCD Lagrangian is a function of quark- and gluon-field.

The fermionic part in (2.1) can be simplified with the introduction of the *Dirac operator* defined as

$$D = (\partial_\mu - igA_\mu) - m , \quad (2.2)$$

also called the covariant derivative, and using the Feynman-slash notation

$$\not{D} = \gamma_\mu D = \gamma_\mu (\partial_\mu - igA_\mu) - m \quad (2.3)$$

(written out: *Dslash* operator) such that the Lagrangian simplifies to

$$\mathcal{L} = \bar{\psi} \not{D} \psi + \frac{1}{4} F_{\mu\nu}^2 .$$

The gamma matrices  $\gamma_\mu$  are constant and must obey the euclidean Clifford algebra

$$\gamma_\mu \gamma_\nu = \begin{cases} -\gamma_\nu \gamma_\mu & \text{if } \mu \neq \nu \\ I & \text{if } \mu = \nu \end{cases}$$

with  $I$  being the identity matrix. The corresponding  $\gamma$  matrices in the representation used by tmLQCD is

$$\begin{aligned} \gamma_0 &= \begin{pmatrix} 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \\ 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \end{pmatrix} & \gamma_1 &= \begin{pmatrix} 0 & 0 & 0 & i \\ 0 & 0 & i & 0 \\ 0 & -i & 0 & 0 \\ -i & 0 & 0 & 0 \end{pmatrix} \\ \gamma_2 &= \begin{pmatrix} 0 & 0 & 0 & 1 \\ 0 & 0 & -1 & 0 \\ 0 & -1 & 0 & 0 \\ 1 & 0 & 0 & 0 \end{pmatrix} & \gamma_3 &= \begin{pmatrix} 0 & 0 & i & 0 \\ 0 & 0 & 0 & -i \\ -i & 0 & 0 & 0 \\ 0 & i & 0 & 0 \end{pmatrix} \end{aligned} \quad (2.4)$$

There is also a fifth gamma matrix, historically named  $\gamma_5 = i\gamma_0\gamma_1\gamma_2\gamma_3$ . With the gamma basis above:

$$\gamma_5 = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & -1 & 0 \\ 0 & 0 & 0 & -1 \end{pmatrix} .$$

## 2.2 Lattice QCD

Lattice QCD is a numerical approach to QCD by discretization of space-time which is then simulated on a computer. Such simulations typically consist of two parts. To begin, a gluon field is generated using a probability process [8]. The second step is to compute a *quark propagator*. Operationally, this is the inversion of the Dirac operator in Equation (2.2) and with the generation of the gluon field the computationally most intensive part.

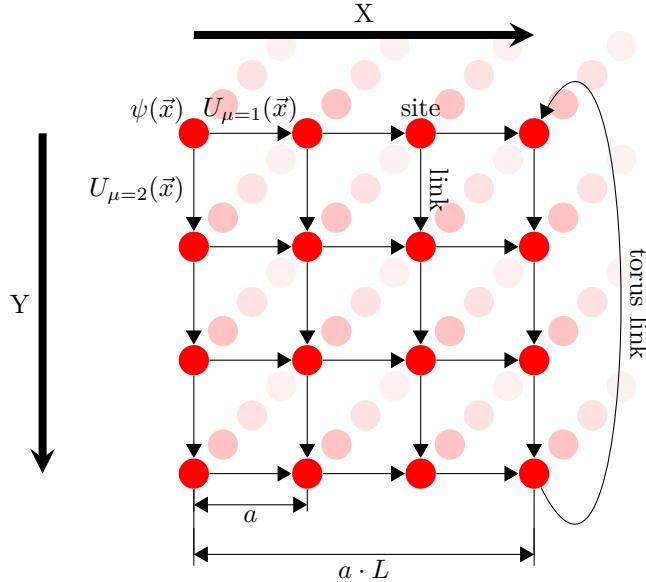

Figure 2.1: Discretized space-time (only 2 dimensions shown, a third one hinted)

The lattice version of QCD splits space and time into a Cartesian grid with interval distance  $a$ , as in Figure 2.1. Typical values for  $a$  are in the scale of a tenth of a femtometer ( $10^{-16}m$ ) in space and  $a/c = 3.3 \cdot 10^{-25}$  seconds in time dimension. The number of sites per dimension are  $L_t$ ,  $L_x$ ,  $L_y$  and  $L_z$ , or as a vector:

$$\vec{L} = \begin{pmatrix} L_t \\ L_x \\ L_y \\ L_z \end{pmatrix}.$$

Often the number of sites in the space dimensions are the same and identified with capital letter  $L$  and  $T = L_t$  for the time dimension. The total volume covered therefore is  $(aL)^3$ . A site in the lattice is identified by four coordinates  $(t, x, y, z)$  or a 4-vector  $\vec{x}$  for brevity. Each site holds a spinor  $\psi(\vec{x})$  just as in the continuous version.

The gluon field is represented by connections between the sites. Only paths to direct neighbors – called links – exist in this model. Other paths must be constructed transitively. The boundary condition is periodic, i.e. borders are connected to each other such that the geometry of space-time is a torus. This is to reduce the impact of a hard border which does not exist in reality. tmLQCD also gradually shifts phases between sites such that walking around the torus results in a different phase when arriving at the same site again. Expressed as a formula, this is [9]

$$\psi(\vec{x}) = e^{i\theta_\mu \pi} \psi(\vec{x} + a\vec{L}) . \quad (2.5)$$

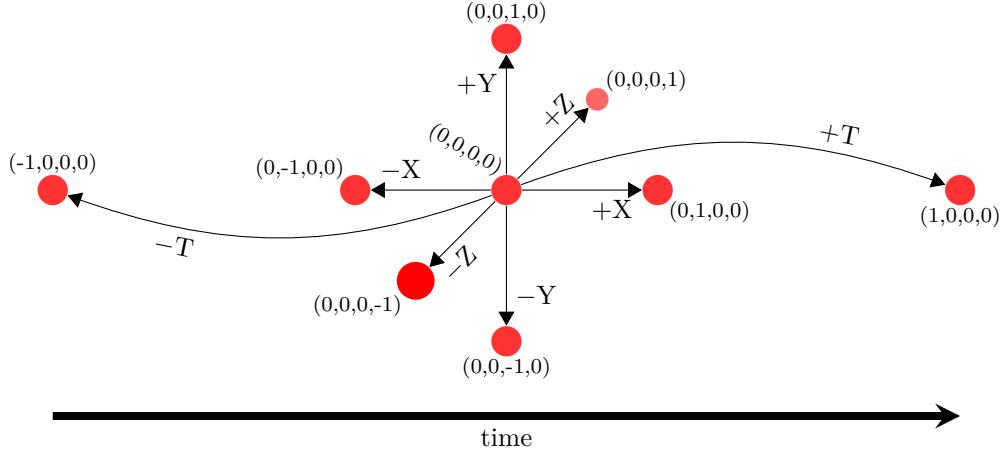

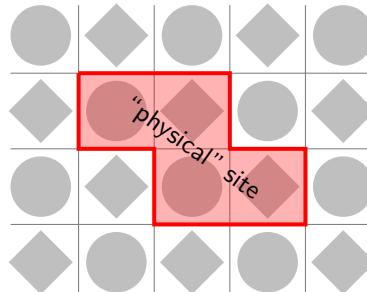

Figure 2.2: 4D neighbors

The directions from an origin vector are shown in Figure 2.2. The eight directions are named by the dimension and sign. Positive directions point to coordinates with increasing coordinate components whereas negative direction point to the opposite.

The links are annotated by the effect of the gluon field on a color charge when traversing them, which is a  $SU(3)$  matrix. This is a *link variable*  $U_\mu$  instead of a description of gluons  $A$  in the continuum version. The relation between the two is

$$U_\mu(\vec{x}) = \mathcal{P} e^{-i \int_{\vec{x}}^{\vec{x}+a\hat{\mu}} g A_\mu(\vec{y}) d\vec{y}} \quad (2.6)$$

where  $\mathcal{P}$  signifies a path-ordered product. In this notation  $\hat{\mu}$  is one of canonical vectors in dimension  $\mu \in \{0, 1, 2, 3\}$ , namely

$$\mu_0 = \begin{pmatrix} 1 \\ 0 \\ 0 \\ 0 \end{pmatrix} \quad \mu_1 = \begin{pmatrix} 0 \\ 1 \\ 0 \\ 0 \end{pmatrix} \quad \mu_2 = \begin{pmatrix} 0 \\ 0 \\ 1 \\ 0 \end{pmatrix} \quad \mu_3 = \begin{pmatrix} 0 \\ 0 \\ 0 \\ 1 \end{pmatrix}.$$

The field  $A_\mu$  hereby becomes unimportant and we continue to work on the gauge field  $U$  only. That is, we replace the description of gluon charges  $A$  with their effect on quark charges  $U$ .

This integral of Equation (2.6) is commonly approximated using

$$U_\mu(\vec{x}) = U(\vec{x}, \vec{x} + a\hat{\mu}) = e^{-i a g A_\mu(\vec{x} + \frac{a}{2}\hat{\mu})}.$$

This is the effect for going into positive direction. The effect of going into negative direction is the inverse of coming from the target site and therefore

$$U(\vec{x}, \vec{x} - a\hat{\mu}) = (U(\vec{x} - a\hat{\mu}, \vec{x}))^{-1} = U(\vec{x} - a\hat{\mu})^\dagger$$

( $\dagger$  = complex conjugate) because the gauge matrices are unitary.

### 2.2.1 Discrete Fermionic Action

There are various approaches on how to design a discretized version of the action of Equation (2.1). We cover the fermionic part first. The main difficulty is the derivative of the Dirac operator in Equation (2.2).

The classic replacement of the Dirac operator as suggested by Wilson himself [1, 9] – self-suggestively called the Wilson-Dirac operator  $D_W$  – is

$$\not{D}_W = \underbrace{\frac{1}{2} \sum_{\mu} \gamma_{\mu} (\nabla_{\mu} + \nabla_{\mu}^*)}_{\text{Naïve discretization}} - \underbrace{\frac{a}{2} \sum_{\mu} \nabla_{\mu} \nabla_{\mu}^*}_{\text{Wilson correction term}} + m$$

with

$$\begin{aligned} \nabla_{\mu} \psi(\vec{x}) &= \frac{1}{a} (U(\vec{x}, \vec{x} + a\hat{\mu}) \psi(\vec{x} + a\hat{\mu}) - \psi(\vec{x})) \\ \nabla_{\mu}^* \psi(\vec{x}) &= \frac{1}{a} (\psi(\vec{x}) - U(\vec{x} - a\hat{\mu}, \vec{x}) \psi(\vec{x} - a\hat{\mu})). \end{aligned}$$

$\nabla_{\mu} \psi(\vec{x})$  and  $\nabla_{\mu}^* \psi(\vec{x})$  are known as the forward gauge covariant difference operator, respectively the backward gauge covariant difference operator. The correction term is intended to eliminate doubler poles (an artifact from discretization) and vanishes for  $a \rightarrow 0$ , although it may be very large for finite  $a$ . The difference operators are the “slopes” of the lines between two lattice sites; the center point and one Cartesian neighbor. When inserted into `cref:diracwilson`, the contribution of the center point vanishes:

$$\frac{1}{2a} \sum_{\mu} \gamma_{\mu} (U(\vec{x}, \vec{x} + a\hat{\mu}) \psi(\vec{x} + a\hat{\mu}) - U(\vec{x} - a\hat{\mu}, \vec{x}) \psi(\vec{x} - a\hat{\mu})) . \quad (2.7)$$

Alternatively, there is the Wilson-Twisted Mass formulation that has one more correction term:

$$\not{D}_{text{ttm}} = \frac{1}{2} \sum_{\mu} \gamma_{\mu} (\nabla_{\mu} + \nabla_{\mu}^*) - \frac{a}{2} \sum_{\mu} \nabla_{\mu} \nabla_{\mu}^* + m + i\mu_q \gamma_5 \begin{pmatrix} 1 & 0 \\ 0 & -1 \end{pmatrix}$$

with the twisted mass parameter  $\mu_q \in \mathbb{C}$ . The matrix multiplying the  $\gamma_5$  term acts in the doublet isospin space : the up- and down-quarks. The additional term also reduces the error due to discretization. Normally, the discretization artifact is in the scale of  $O(a)$  and is reduced to  $O(a^2)$  when using a set of parameters called “maximal twist”.

### 2.2.2 Discrete Gauge Action

The gluons also carry charge and therefore also influence the gauge field themselves. Its gluon-gluon influence on the total action manifests in the gauge action term of Equation (2.1).

Wilson discretized the gauge action by summing up the closed loop walks (walk along links that starts and ends at the same point) on the lattice. The walk must be non-trivial (i.e. following at least one link) and not traveling links twice. The smallest such loop walks along 4 links on a square. It is called a *plaquette*. The SU(3) matrix effect collected on such a walk is

$$U_{\mu\nu}(\vec{x}) = U(\vec{x}, \vec{x} + a\hat{\mu}) U(\vec{x} + a\hat{\mu}, \vec{x} + a\hat{\mu} + a\hat{\nu}) U(\vec{x} + a\hat{\mu} + a\hat{\nu}, \vec{x} + a\hat{\nu}) U(\vec{x} + a\hat{\nu}, \vec{x})$$

The *Wilson Gauge Action* is the sum over all plaquettes, but not going in reverse, starting at a point  $\vec{x}$ :

$$\frac{6}{g^2} \sum_{\mu < \nu} \left( 1 - \frac{1}{6} \text{Tr} (U_{\mu\nu}(\vec{x}) U_{\mu\nu}^\dagger(\vec{x})) \right)$$

This thesis’ focus is on the fermionic action, not the gauge action, for the sole reason that in practice programs spend more time on the Dirac operator. Optimizing it therefore saves more computation time than by putting the same effort into optimizing plaquettes.

## 2.3 Iterative Solver

Arguably the most computationally intensive part in tmLQCD and any Lattice QCD application is the evaluation of the Dirac operator of Equation (2.7). It is applied again and again for instance when inverting  $D$  represented as matrix. It is actually not finding  $D^{-1}$  but a solution  $\psi$  of the equation  $\not{D}\psi = \phi$ . Solving this equation system is already hard enough, even storing  $\not{D}^{-1}$  explicitly in memory is not possible with today's computers and typical lattice sizes such as  $128 \times 64^3 \approx 33.6$  million elements. This squared yields up to  $1.1 \times 10^{15}$  elements to be stored for an explicit representation.

Direct solvers such as Gaussian elimination, LU/Cholesky-decomposition etc. are also not preferred as they require  $O(n^3)$  operations ( $\sim 3.8 \times 10^{22}$  for typical lattice sizes). Iterative solvers are preferable here. These typically have a complexity of  $O(kn^2)$  where  $k$  is the number of iterations which varies between iterative algorithms, but in practice  $k$  is asymptotically smaller than  $n$ .

*Conjugate gradient* (CG, Algorithm 2.1) is the “gold standard” used in Lattice QCD. Other algorithms are typically compared to CG. Without rounding errors it is guaranteed to return the exact result at most  $k = n$  iterations. However, the result is not needed with exact precision and therefore the algorithm can abort when the solution is close enough to the optimal solution, defined by an  $\epsilon$ -limit of the residual ( $r = Ax - b$  in Algorithm 2.1). The number of iterations is typically sub-linear and therefore a solution can be found quicker than with a direct method.

---

**Algorithm 2.1:** Conjugate Gradient (CG) iterative solver

---

```

Input:  $n \in \mathbb{N}$ ,  $b \in \mathbb{K}^n$ ,  $A \in \mathbb{K}^{n \times n}$

Result:  $x \in \mathbb{K}^n$  such that  $Ax \approx b$

$x \leftarrow \vec{0}$ ; // Initial guess

$r \leftarrow b$ ;

$p \leftarrow r$ ;

$n_r \leftarrow \|r\|^2$ ;

while ( $n_r \geq \epsilon$ ) do

$p' \leftarrow Ap$ ;

$\alpha \leftarrow \frac{n_r}{\langle p | p' \rangle}$ ;

$x \leftarrow x + \alpha p$ ; // Next guess

$r \leftarrow r - \alpha p'$ ;

$n_{r1} \leftarrow \|r\|^2$ ;

$\beta \leftarrow \frac{n_{r1}}{n_r}$ ;

$p \leftarrow r + \beta p$ ;

$n_r \leftarrow n_{r1}$ ;

end

$x = Ax - b$ ;

```

---

For CG to be applicable,  $A$  must be hermitian ( $A^\dagger = A$ ) and positive definite which unfortunately is not the case for the Dirac operator. However, the matrices  $A^\dagger A$  and  $AA^\dagger$  have both properties and their solutions provided by CG can be used to calculate the solutions of the original systems. These variants are called *Conjugate Gradient Normal Residual* (CGNR) and *Conjugate Gradient Normal Equation* (CGNE) respectively.

Per iteration there is one application of the matrix, one scalar products, one norm, three vector additions/subtractions and three scalar-vector multiplications. The matrix-vector multiplication here is not implemented using dense matrix-vector multiplication, but a function call that applies the Dirac operator. This function is discussed in the next section. Because of its computational complexity and memory access pattern it is also the dominant part in every iteration.

## 2.4 Wilson-Dirac Operator Stencil

As already stated, the Dirac operator (Equation (2.7)) is one of the most important kernels of any Lattice QCD program. The operator is also called *Dslash*, D standing for Dirac and using the Feynman-slash notation  $\not{D} = \sum_\mu \gamma_\mu D_\mu$  (compare Equation (2.3)). The function applying it is called *Hopping Matrix* within tmLQCD. We will use the same name in this thesis, and explore its properties in this section.

Equation (2.7) does not include all the complexities necessary. E.g. the twisted boundary of Equation (2.5) is missing. The actual Wilson twisted mass Dirac operator as implemented in tmLQCD is [9]

$$\begin{aligned} (\not{D}\psi)(\vec{x}) = & (m_0 + 4 + i\mu_q \gamma_5) \psi(\vec{x}) \\ & - \frac{\kappa}{2} \sum_\mu \left( e^{i\pi\theta_\mu/L_\mu} U(\vec{x}, \vec{x} + a\hat{\mu}) (1 + \gamma_\mu) \psi(\vec{x} + a\hat{\mu}) \right. \\ & \left. + e^{-i\pi\theta_\mu/L_\mu} U(\vec{x}, \vec{x} - a\hat{\mu}) (1 - \gamma_\mu) \psi(\vec{x} - a\hat{\mu}) \right) \end{aligned}$$

The coefficient  $\kappa \in \mathbb{R}$  is a constant and depends on the quark's mass. One may think of a weight relative to  $\psi(\vec{x})$ .

### 2.4.1 Optimizing the Formula

For the hardware, accesses to  $\psi(\vec{x})$  are faster to execute than accesses to neighbor cells. Separating them makes the same-cell access hardware-predictable and also reduces the working set of the neighbor accesses (see Section 4.4). The split-up Dirac operator is

$$\begin{aligned} (\not{D}\psi)(\vec{x}) = & (m_0 + 4 + i\mu_q \gamma_5) \psi(\vec{x}) - (\not{D}'\psi)(\vec{x}) \quad (2.8) \\ (\not{D}'\psi)(\vec{x}) = & \frac{\kappa}{2} \sum_\mu \left( U(\vec{x}, \vec{x} + a\hat{\mu}) e^{i\pi\theta_\mu/L_\mu} (1 + \gamma_\mu) \psi(\vec{x} + a\hat{\mu}) \right. \\ & \left. + U(\vec{x}, \vec{x} - a\hat{\mu}) e^{-i\pi\theta_\mu/L_\mu} (1 - \gamma_\mu) \psi(\vec{x} - a\hat{\mu}) \right). \end{aligned}$$

We simplify  $D'$  further by

- merging the coefficients  $\frac{\kappa}{2}$  and  $e^{i\pi\theta_\mu/L_\mu}$  into a coefficient  $\kappa_\mu$  per dimension and therefore remove one multiplication

- exploiting the relation  $U(\vec{x}, \vec{x} - a\hat{\mu}) = U^\dagger(\vec{x} - a\hat{\mu}, \vec{x})$

- shortening  $U(\vec{x}, \vec{x} + a\hat{\mu})$  to  $U_\mu(\vec{x})$ ; with the previous rule  $U(\vec{x}, \vec{x} - a\hat{\mu}) = U_\mu^\dagger(\vec{x} - a\hat{\mu})$

such that we gain

$$(D'\psi)(\vec{x}) = \sum_\mu \left( \kappa_\mu U_\mu(\vec{x}) (1 + \gamma_\mu) \psi(\vec{x} + a\hat{\mu}) + \bar{\kappa}_\mu U_\mu^\dagger(\vec{x} - a\hat{\mu}) (1 - \gamma_\mu) \psi(\vec{x} - a\hat{\mu}) \right).$$

In this formulation the tensor products are hidden. A written-out formulation of the same formula is

$$\begin{aligned} (\not{D}'\psi)(\vec{x}) = & \sum_\mu \left( \kappa_\mu (\mathbb{1}_4 \otimes U_\mu(\vec{x})) ((\mathbb{1}_4 + \gamma_\mu) \otimes \mathbb{1}_3) \psi(\vec{x} + a\hat{\mu}) \right. \\ & \left. + \bar{\kappa}_\mu (\mathbb{1}_4 \otimes U_\mu^\dagger(\vec{x})) ((\mathbb{1}_4 - \gamma_\mu) \otimes \mathbb{1}_3) \psi(\vec{x} - a\hat{\mu}) \right) \end{aligned}$$

where

$\mathbb{1}_n \in \mathbb{C}^{n \times n}$  are the identity matrices

$\otimes$  is the tensor product:  $A = (a_{ij}) \in \mathbb{C}^{m \times n}$ ,  $B \in \mathbb{C}^{o \times p}$

$$A \otimes B = \begin{pmatrix} a_{11}B & \dots & a_{1n}B \\ \vdots & \ddots & \\ a_{m1}B & & a_{mn}B \end{pmatrix} \in \mathbb{C}^{mo \times np}$$

$\vec{x} \in \mathbb{R}^4$  is a space-time coordinate on the lattice

$\mu \in \{0, 1, 2, 3\}$  is a dimension (0=time; 1,2,3=space)

$U_\mu$  is the lattice link field in positive direction

$\gamma_\mu \in \mathbb{C}^{4 \times 4}$  are the gamma matrices (Equation (2.4))

$\kappa_\mu \in \mathbb{C}$  are coefficients as defined above

$\psi$  is the spinor field

In computer science this structure is commonly known as a stencil: An operator that is applied on each coordinate of a field and depends on data with constant offset to that coordinate. In this case, it is a 8-point stencil for each of the neighbor spinors  $\psi(\vec{x} \pm a\bar{\mu})$ . Including the diagonal part of Equation (2.8), it actually is a 9-point stencil, which we keep separate out of efficiency reasons. Including the gauge field it even is a 16 point stencil.

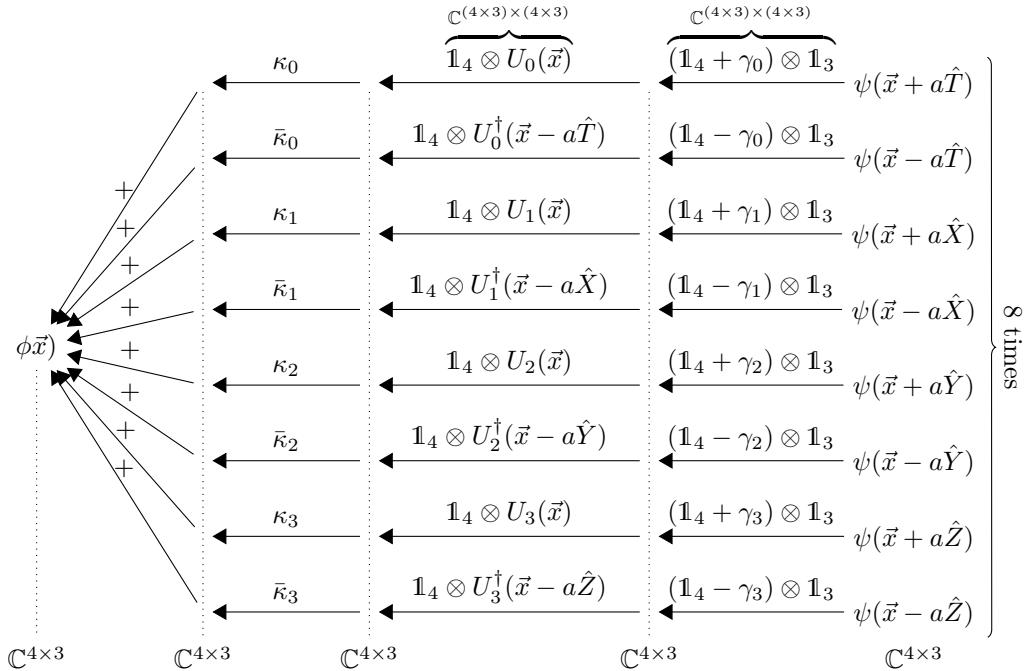

If directly implemented as a function, its data flow would resemble Figure 2.3. Every source stencil point has a computation path until the result is accumulated and stored in the target buffer  $\phi$ . One cannot overwrite the source spinor field  $\psi$  as the original value might be used in stencil for the neighbor site.

Figure 2.3: Dirac operator stencil data flow

The gauge field does not change during the execution of CG. The constant  $\kappa$  therefore can be multiplied in advance into the gauge field  $U$ .

$$U_\mu(\vec{x}) \rightarrow \kappa_\mu U_\mu(\vec{x})$$

$$U_\mu^\dagger(\vec{x}) = U_\mu(\vec{x} - a\hat{\mu}) \rightarrow \kappa_\mu U_\mu(\vec{x} - a\hat{\mu}) = \kappa_\mu U_\mu(\vec{x})^\dagger = \bar{\kappa}_\mu U_\mu^\dagger(\vec{x})$$

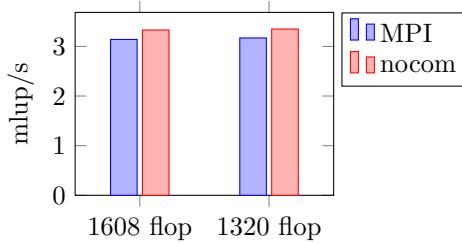

This has not been done in tmLQCD. Performance is usually measured in floating point operations per seconds, but with the additional  $\kappa$ -multiplication, more floating point operations are executed than with the optimized version without doing more work. In this thesis, we therefore provide performance numbers for both versions.

### 2.4.2 Spin Projection

The third and fourth line of the matrices ( $\mathbb{1}_4 \pm \gamma_\mu$ ) are factors of the first and second line. We can use the linear dependency by removing the redundant lines, applying any (linear) operation  $f$  on the remaining lines and then reconstructing the other lines. For instance with  $\mu = 0$ :

$$(\mathbb{1}_4 \otimes f)(\mathbb{1}_4 + \gamma_0) = \begin{pmatrix} 1 & 0 & 1 & 0 \\ 0 & 1 & 0 & 1 \\ 1 & 0 & 1 & 0 \\ 0 & 1 & 0 & 1 \end{pmatrix} = \begin{pmatrix} 1 & 0 \\ 0 & 1 \\ 1 & 0 \\ 0 & 1 \end{pmatrix} (\mathbb{1}_2 \otimes f) \begin{pmatrix} 1 & 0 & 1 & 0 \\ 0 & 1 & 0 & 1 \end{pmatrix}$$

$$= ((\mathbb{1}_4 + \gamma_\mu) P^T)(\mathbb{1}_2 \otimes f)(P(\mathbb{1}_4 + \gamma_\mu))$$

$$(\mathbb{1}_4 \otimes f)(\mathbb{1}_4 - \gamma_0) = \begin{pmatrix} 1 & 0 & -1 & 0 \\ 0 & 1 & 0 & -1 \\ -1 & 0 & 1 & 0 \\ 0 & -1 & 0 & 1 \end{pmatrix} = \begin{pmatrix} 1 & 0 \\ 0 & 1 \\ -1 & 0 \\ 0 & -1 \end{pmatrix} (\mathbb{1}_2 \otimes f) \begin{pmatrix} 1 & 0 & -1 & 0 \\ 0 & 1 & 0 & -1 \end{pmatrix}$$

$$= ((\mathbb{1}_4 - \gamma_\mu) P^T)(\mathbb{1}_2 \otimes f)(P(\mathbb{1}_4 - \gamma_\mu))$$

The matrix  $P$  is the projection matrix that only keeps the first two rows.  $P$  and its left-inverse  $P^T$  are representable by the following matrices.

$$P = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \end{pmatrix} \quad P^T = \begin{pmatrix} 1 & 0 \\ 0 & 1 \\ 0 & 0 \\ 0 & 0 \end{pmatrix}$$

Therefore just half of the operations following are unnecessary. There are only 2 instead of 4 evaluations of  $f$ . In the case of the Dirac operator,  $f$  is the multiplication with the  $SU(3)$  gauge matrix and  $\kappa$ . A 2-component spinor may also be called *halfspinor*, 2-spinor or Weyl-spinor, in contrast to the full 4-component spinor that we call *fullspinor*, 4-spinor or Dirac-spinor. The original  $4 \times 4$  matrix can be reconstructed by (in this example) negating the first respectively second line. More generally, the reconstruction matrix is built by throwing away the last two columns of the gamma matrix, or equivalently by right-multiplication by transposed  $P$ .

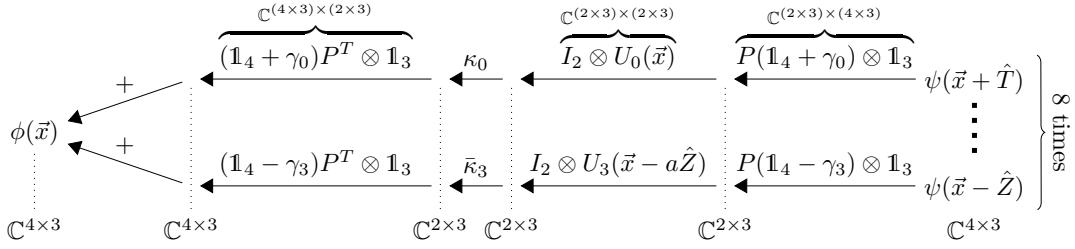

Incorporating this projection and reconstruction, the Dirac stencil becomes

$$(\mathcal{D}'\psi)(\vec{x}) = \sum_\mu \left( ((\mathbb{1}_4 + \gamma_\mu) P^T \otimes \mathbb{1}_3) \kappa_\mu (\mathbb{1}_2 \otimes U_\mu(\vec{x}))(P(\mathbb{1}_4 + \gamma_\mu) \otimes \mathbb{1}_3) \psi(\vec{x} + a\hat{\mu}) \right. \\ \left. + ((\mathbb{1}_4 - \gamma_\mu) P^T \otimes \mathbb{1}_3) \bar{\kappa}_\mu (\mathbb{1}_2 \otimes U_\mu^\dagger(\vec{x}))(P(\mathbb{1}_4 - \gamma_\mu) \otimes \mathbb{1}_3) \psi(\vec{x} - a\hat{\mu}) \right)$$

whose data flow is illustrated in Figure 2.4.

Figure 2.4: Flow in the Dirac stencil with projection

### 2.4.3 Number of Floating-Point Operations per Stencil

A spinor has  $4 \times 3 = 12$  complex values, which makes a total of  $8 \times 12 = 96$  values to read. The next step is to apply the spin projector per direction. Every projector matrix has 2 non-zero entries per row, each non-zero entry either 1,  $-1$ ,  $i$  or  $-i$ . We do not consider multiplication by such a constant as an operation because it can be implemented trivially. For instance, instead of negating a value the next operation may be a subtraction instead of an addition. What remains is the sum of the two non-zero entries, i.e.  $8 \times 2 \times 3 = 48$  complex additions.

The multiplication by the SU(3) matrices is done on both of the halfspinor vectors, each involving 6 complex additions and 9 multiplications. In total,  $8 \times 2 \times 6 = 96$  additions and  $8 \times 2 \times 9 = 144$  multiplications. Therefore, it is the computationally most costly part.

Multiplication by the complex number  $\kappa_\mu$  is done individually on all (half-)spinor components, i.e.  $8 \times 2 \times 3 = 48$  multiplications.

The re-expansions of the halfspinors to spinors again is trivial as every coefficient involved is either 1,  $i$  or their negatives. Summing up the results from all directions is more expensive though and done elementwise. In total  $7 \times 4 \times 3 = 84$  additions take place.

The sum of one stencil operation is  $48 + 96 + 84 = 228$  complex additions and  $144 + 48 = 192$  complex multiplications. However, we do not compute complex numbers directly, but must be lowered to real number calculation. Every complex addition has the equivalent of 2 real additions:

$$\begin{pmatrix} a_r \\ a_i \end{pmatrix} + \begin{pmatrix} b_r \\ b_i \end{pmatrix} = \begin{pmatrix} a_r + b_r \\ a_i + b_i \end{pmatrix}$$

An implementation of complex multiplication needs 2 real additions and 4 real multiplications:

$$\begin{pmatrix} a_r \\ a_i \end{pmatrix} \begin{pmatrix} b_r \\ b_i \end{pmatrix} = \begin{pmatrix} a_r b_r - a_i b_i \\ a_r b_i + a_i b_r \end{pmatrix}$$

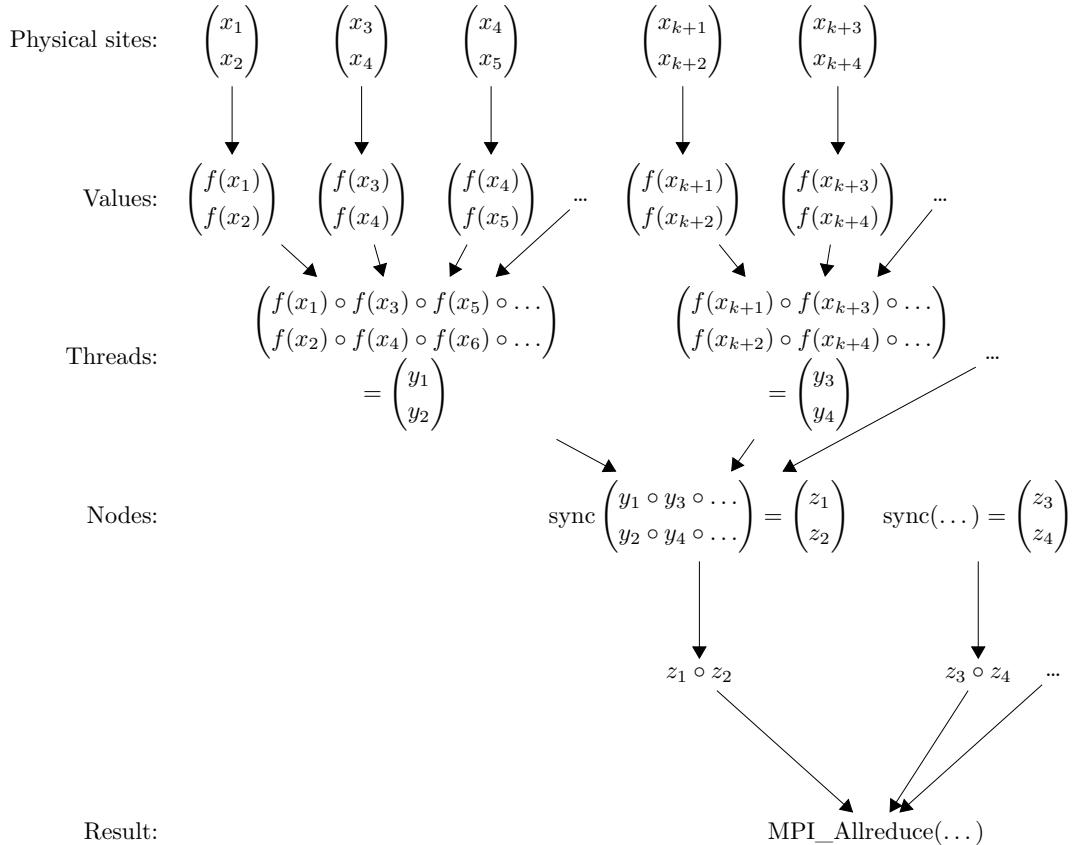

Therefore,  $2 \times 228 + 2 \times 192 = 840$  real additions and  $4 \times 192 = 768$  real multiplication are required, i.e. 1608 total floating-point operations.

If  $\kappa$  is integrated into the gauge field, some arithmetic operations are saved. The remaining number of floating-point operations is  $2 \times 212 + 2 \times 144 = 712$  additions and  $4 \times 144 = 576$  multiplications, i.e.  $744 + 576 = 1320$  floating-point operations. This is the most often cited number in terms of complexity of Lattice QCD.

The Tables 2.1 and 2.2 give an overview on the required number of operations per stencil and the memory required per element to store element in memory. Table 2.3 also contains the amount of memory that is to be read and written for every execution of the stencil.

The computational complexity is the ratio between floating-point operations and bandwidth. As seen from the tables there are 3.93 respectively 4.79 operations (with  $\kappa$  multiplication) per floating-point to load. Hence, depending on whether we use single or double precision, the computational complexity of Hopping Matrix is between 0.49 and 1.2 operations per byte.

| Operation        | Complex |           | Real      |           | Flops       |

|------------------|---------|-----------|-----------|-----------|-------------|

|                  | Adds    | Muls      | Adds      | Muls      |             |

| Spin projection  | 48      |           | 96        |           | 96          |

| SU(3) mul        | 96      | 144       | 480       | 576       | 1056        |

| $\kappa_\mu$ mul |         | 48 (0)    | 96 (0)    | 192 (0)   | 288 (0)     |

| Spinor sum       | 84      |           | 168       |           | 168         |

| Total            | 228     | 192 (144) | 840 (744) | 768 (576) | 1608 (1320) |

Table 2.1: Computational complexity of a single stencil

| Structure  | Mathematical representation                                                | Floats | Bytes in precision |        |

|------------|----------------------------------------------------------------------------|--------|--------------------|--------|

|            |                                                                            |        | single             | double |

| Gauge      | $SU(3) (\subset \mathbb{C}^{3 \times 3})$                                  | 18     | 72                 | 144    |

| Fullspinor | $\mathbb{C}^3 \times \mathbb{C}^3 \times \mathbb{C}^3 \times \mathbb{C}^3$ | 24     | 96                 | 192    |

| Halfspinor | $\mathbb{C}^3 \times \mathbb{C}^3$                                         | 12     | 48                 | 96     |

Table 2.2: Field element sizes

## 2.5 Domain Decomposition

The more sites the lattice has the more reliable the results. The size of a lattice easily grows larger than today's shared-memory computer systems can store. The amount of memory can be increased but with larger lattices one also wants to add more processors to the system. The more processors there are the more problematic their concurrent access to the same memory regions becomes.

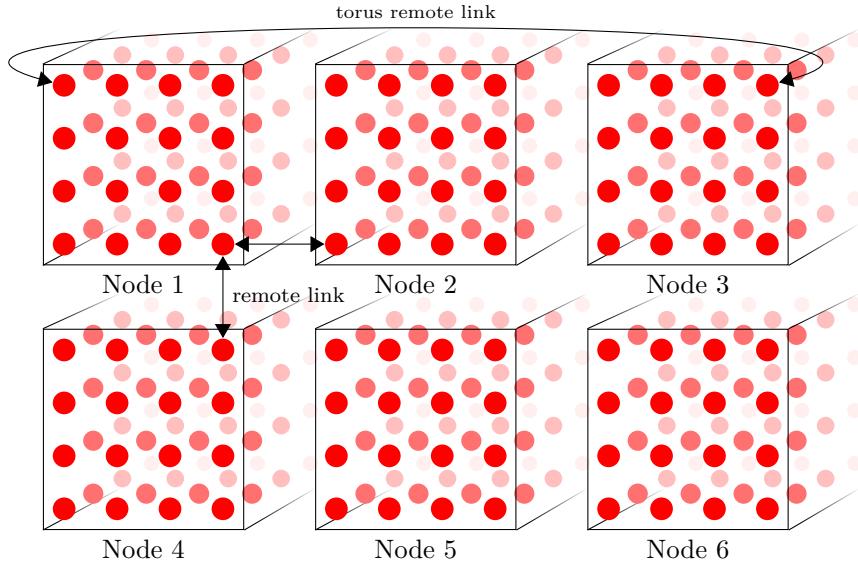

Therefore the use of processors with distinct memories – called nodes – becomes unavoidable. The data must be split between all the nodes and every node computes just a part of the global lattice. The data split-up is done using the domain decomposition method. Every node is assigned a rectangular sublattice of the global lattice. The split may happen in any of the 4 dimensions, Figure 2.5 for instance shows a decomposition in two dimensions into an array of  $3 \times 2$  nodes. The difficult part is the data exchange between the nodes when such as the Dirac operator stencil when a neighbor site is not on the local node, but a remote neighbor node.

tmLQCD uses MPI to exchange the neighbor elements between nodes. Elements in the fields are ordered such that all the elements that have to go to a remote node are in a single contiguous block of memory. When data is needed from the remote nodes, these blocks are transferred and received from the 8 neighbor nodes. The calculation requiring that data can continue when all the data has been received.

| Element of       | Elements per stencil | Bandwidth for precision |                  |

|------------------|----------------------|-------------------------|------------------|

|                  |                      | single                  | double           |

| Read gauge       | 8                    | 576                     | 1152             |

| Read fullspinor  | 8                    | 768                     | 1536             |

| Write fullspinor | 1                    | 96                      | 192              |

| Total            |                      | 1344 (write 96)         | 2688 (write 192) |

Table 2.3: Bytes of memory access per stencil execution

Figure 2.5: Domain decomposition of a  $12 \times 8 \times L_z$  lattice with 6 nodes in a  $3 \times 2$  cluster

## 2.6 tmLQCD

As already mentioned we base our optimization in tmLQCD. Next to a version written in plain C that works with any architecture for which there is a C compiler available, tmLQCD also has specialized versions optimized for specific computer architectures. The optimized architectures include x86 (with SSE2 or SSE3), NVIDIA GPUs and IBM Blue Gene/P. A more recent addition to tmLQCD is a straightforward optimization for Blue Gene/P without memory layout changes.

The original and general (not specific to any platform) source code for Hopping Matrix is shown in Appendix A. It is the base for all platform-specific versions including the one developed for this thesis.

# 3 The Blue Gene/Q Supercomputer

The Blue Gene supercomputer family from IBM has been primarily constructed for protein folding, hence the name. *Blue* for IBM's corporate identity color and *Gene* for the genomes that encode the 20 amino acids proteins are made of. But its architecture originates from *QCDOC* (QCD-On-a-Chip, [10]), a cluster computer dedicated to Lattice QCD.

Hence the Blue Gene series features everything that is also essential to Lattice QCD: Multidimensional torus network, high bandwidth links, homogeneous nodes, high memory data rate and fast a double precision floating point unit. The first product of the family, the *Blue Gene/L*, featured a width-2 vector floating point unit called *Double Hummer*. The two double precision values can be interpreted as a complex value with corresponding instructions, making it very suitable for scientific computing. The next generation, Blue Gene/P was mostly more of the same. More cores per node, slightly higher CPU frequency, faster interconnection, etc., but also introduced shared memory threading (*Symmetric Multi-Processing (SMP)/OpenMP*) that the predecessor did not support because it did not ensure cache coherency.

The most recent generation – Blue Gene/Q – features some characteristics that have not been available in previous commercial/off-the-shelf computers. One of the most noteworthy is transactional memory, but also the list prefetch algorithm. The processor switched to 64 bit *PowerPC* which is capable of *Simultaneous Multi-Threading (SMT)*. Otherwise, Blue Gene/Q also provides “more of the same”, i.e. doubled clock frequency, memory, bandwidth and the SIMD vector has been increased to 4 double precision floating point values. The new floating point unit is called *Quad Processing Extension (QPX)*. Table 3.2 summarizes the technical differences between the generations.

A noteworthy point from the manufacturing perspective is that its processor is produced with 18 physical cores, but one of the cores is used as spare part in case one other is defect. It is similar Intel's and AMD's 3-core processors: Presumably these are 4-core processors with one defect, therefore disabled core, sold for a lower price than the 4 core version. In contrast, IBM's design always has one deactivated core even if it is perfectly working.

QCDOC has been designed for and only for Lattice QCD. The Blue Gene family follows the same design, although the primary purpose has changed to protein folding. The design decisions that make these platform good for Lattice QCD are high-throughput double precision floating point unit suitable for complex math, high memory and network bandwidth and a torus-shaped network that allows static workload distribution on the lattice.

## 3.1 Blue Gene/Q Architecture

The Blue Gene family follows the maxim of a homogeneous architecture. That is, every processing unit is equal in nature, in contrast to accelerator-based machines that offload most work from the CPU, most often to a *GPGPU* (General Purpose Graphics Processing Unit) or Intel's *MIC* (Many Integrated Cores). The major disadvantage of such heterogeneous

architectures is that they are more difficult to program. Indeed, one of the design goals was simple programmability. It still get complicated if seeking maximal performance.