Università degli Studi di Genova

Facoltà di Ingegneria

Dipartimento di Ingegneria Meccanica, Energetica, Gestionale e dei Trasporti

Tesi di Dottorato in INGEGNERIA MECCANICA

XXVIII ciclo

Micro-fabricated Silicon Devices for Advanced

Thermal Management and Integration of

Particle Tracking Detectors

Giulia Romagnoli

Tutor: Prof. Ing. Carla Gambaro

Supervisor of Doctoral Program: Ing. Paolo Petagna

## Abstract

Since their first studies targeting the cooling of high-power computing chips, micro-channel devices are proven to provide a very efficient cooling system. In the last years micro-channel cooling has been successfully applied to the cooling of particle detectors at CERN. Thanks to their high thermal efficiency, they can guarantee a good heat sink for the cooling of silicon trackers, fundamental for the reduction of the radiation damage caused by the beam interactions. The radiation damage on the silicon detector is increasing with temperature and furthermore the detectors are producing heat that should be dissipated in the supporting structure. Micro-channels guarantee a distributed and uniform thermal exchange, thanks to the high flexibility of the micro-fabrication process that allows a large variety of channel designs. The thin nature of the micro-channels etched inside silicon wafers, is fulfilling the physics requirement of minimization of the material crossed by the particle beam. Furthermore micro-channels are well suited to be fabricated in silicon, as the same material of the detector they need to cool, and in this way mechanical stresses due to thermal gradients and different Coefficients of Thermal Expansion are minimized in the structure.

The silicon micro-channel device fabrication starts with the etching of the channels in a silicon wafer, followed by the bonding of a cover wafer in silicon (or in Pyrex for testing purposes) to close the channels, and ends with the etching of the fluidic apertures for the fluid circulation. The fluid circulating inside can be in single phase or two phase flow and the flow parameters like pressure, temperature or mass flow, can vary following each detector requirements. After the micro-fabrication of the cooling devices, thermal and fluidic tests are done to validate the channels performances before integrating them in the detector structure. The mechanical integration inside the detector starts with the equipment of the device with fluidic connectors for the fluid circulation, is followed by the gluing of the detector on the micro-channels surface, and ends with the mechanical jigs and supports needed to integrate the cooling in the detector structure.

The first High Energy Physics experiment pioneering micro-channel cooling was the NA62 detector who chose to cool its three GTK stations with a micro-channel plate circulating  $C_6F_{14}$  in liquid flow. The LHCb VELO detector has chosen a  $CO_2$  evaporative flow in micro-channels for its upgrade in 2018. The ATLAS and ALICE detectors are evaluating the possibility of adopting a cooling system based on two-phase cooling in micro-channels using  $CO_2$  and  $C_4F_{10}$  fluids respectively.

Starting with the first application of micro-channel cooling, this novel cooling system applied to particle detector at CERN is fully analysed in this thesis. The four micro-channels cooling applications currently developed at CERN, are analysed in different fields: the micro-fabrication of the cooling plates, the structural properties of silicon to understand the maximum pressure a device can hold, the thermal exchange and fluid circulation to evaluate the cooling performances and, in the last part, the mechanical integration of the silicon cooling plate inside the detector infrastructure.

# TABLE OF CONTENTS

---

|       |                                                                  |    |

|-------|------------------------------------------------------------------|----|

| 1     | Introduction .....                                               | 1  |

| 1.1   | CERN .....                                                       | 1  |

| 1.2   | Silicon Tracking Detectors .....                                 | 3  |

| 1.2.1 | Cooling of Tracking Detectors .....                              | 5  |

| 1.3   | Silicon Micro-channel Cooling of Tracking Detectors .....        | 6  |

| 1.4   | Silicon Micro-channel Cooling at CERN .....                      | 9  |

| 1.4.1 | NA62 GTK .....                                                   | 9  |

| 1.4.2 | Proposal for ALICE ITS Upgrade .....                             | 10 |

| 1.4.3 | LHCb VELO Upgrade .....                                          | 12 |

| 1.4.4 | Studies on ATLAS FEI4 cooling .....                              | 13 |

| 2     | Micro-fabrication of Silicon Micro-channel Cooling Systems ..... | 15 |

| 2.1   | Why Silicon? .....                                               | 15 |

| 2.2   | Micro-channels Fabrication .....                                 | 17 |

| 2.2.1 | Silicon .....                                                    | 18 |

| 2.2.2 | Patterning – Photolithography .....                              | 19 |

| 2.2.3 | Etching the Channels .....                                       | 22 |

| 2.2.4 | Bonding of Cover Wafer .....                                     | 25 |

| 2.2.5 | Anodic Bonding .....                                             | 26 |

| 2.2.6 | Direct Bonding .....                                             | 29 |

| 2.2.7 | Wafer Thinning .....                                             | 32 |

| 2.2.8 | Metal Deposition .....                                           | 34 |

| 2.2.9 | Dicing of the Device .....                                       | 37 |

| 3     | Silicon Pressure Tests .....                                     | 39 |

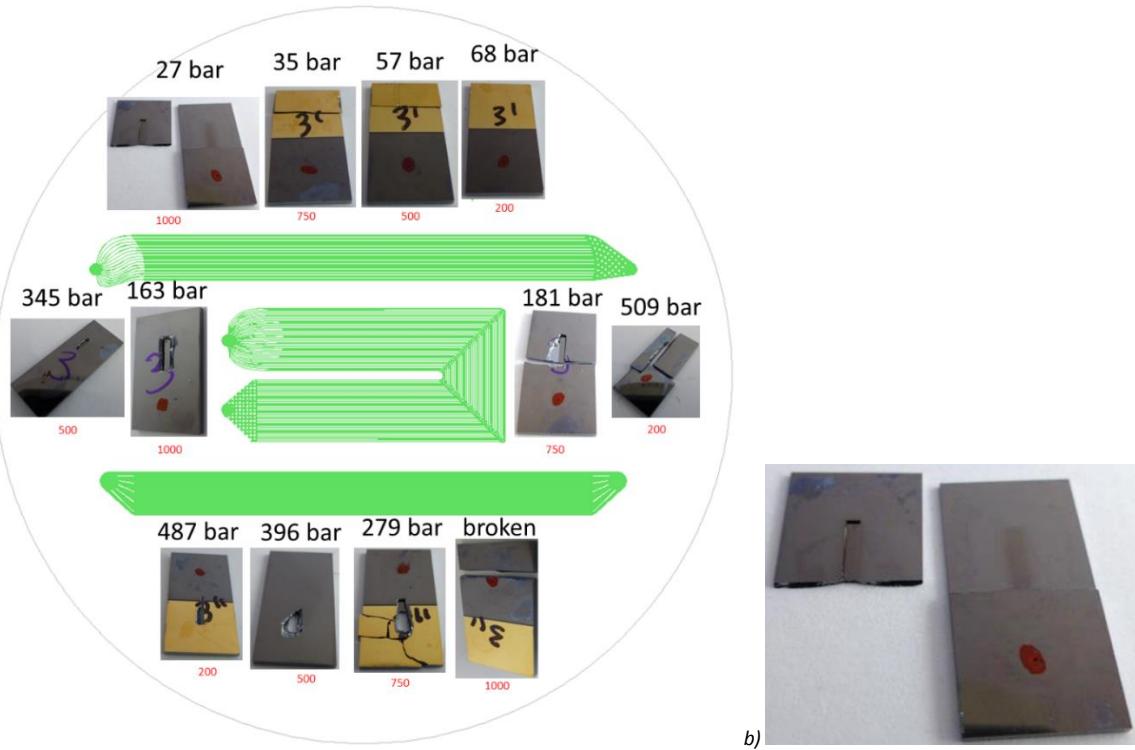

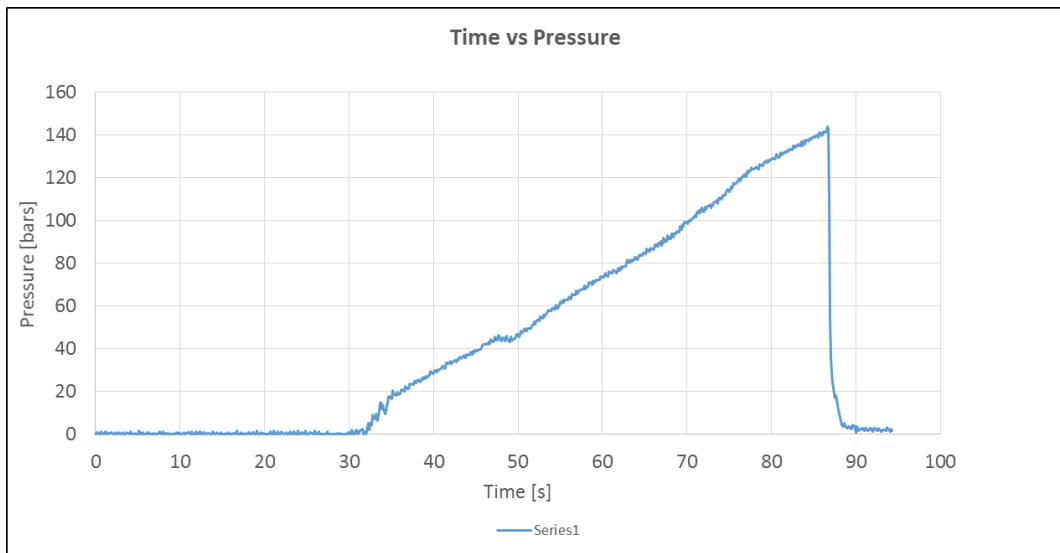

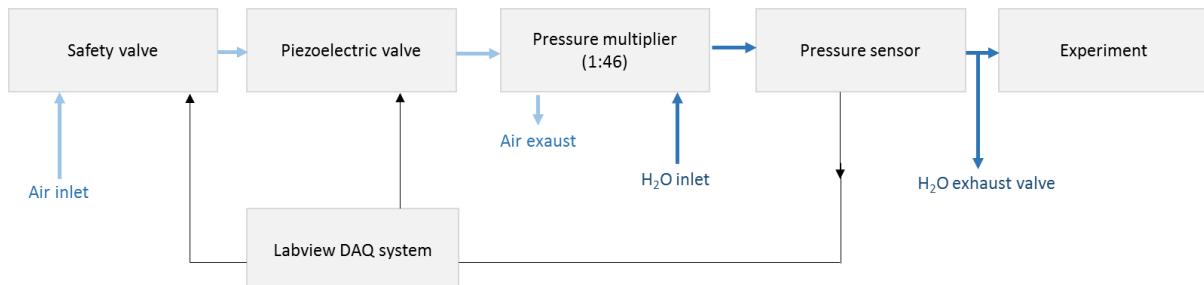

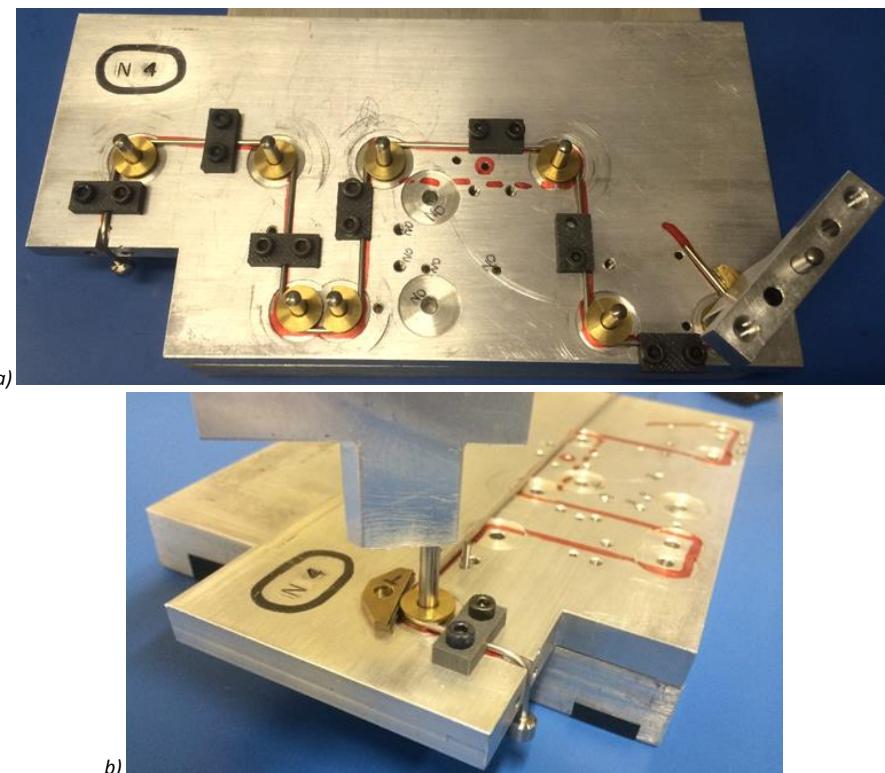

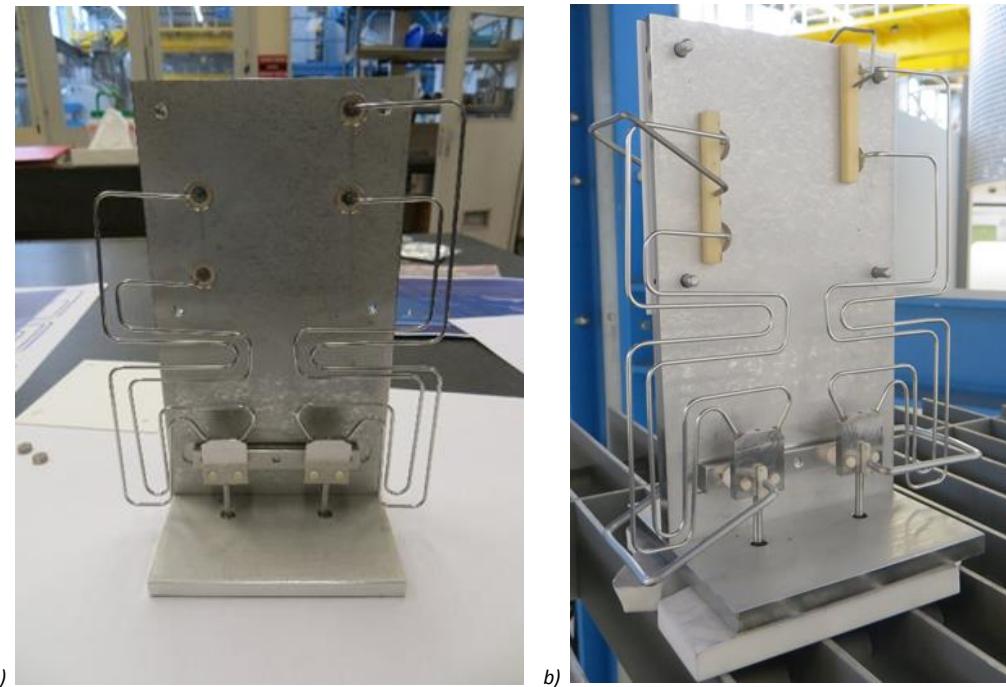

| 3.1   | Test Setup .....                                                 | 40 |

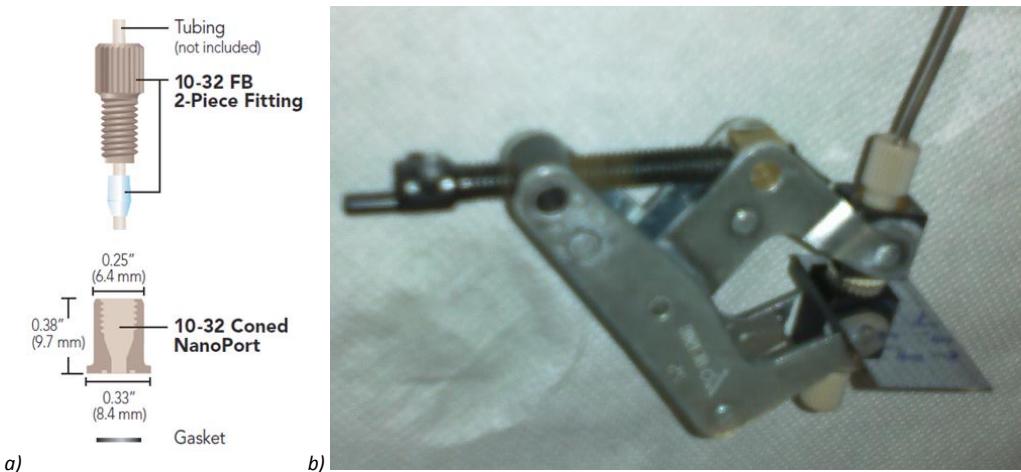

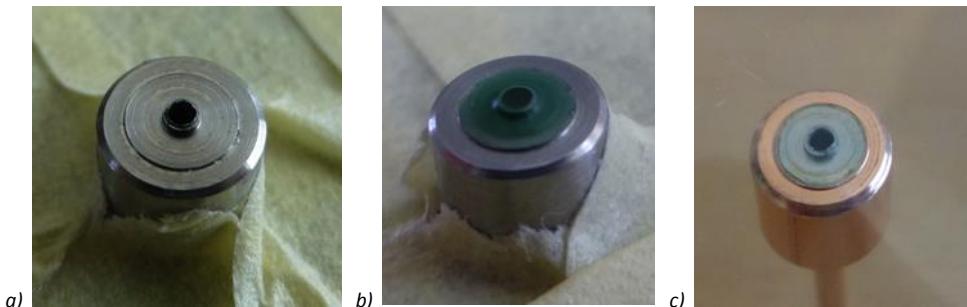

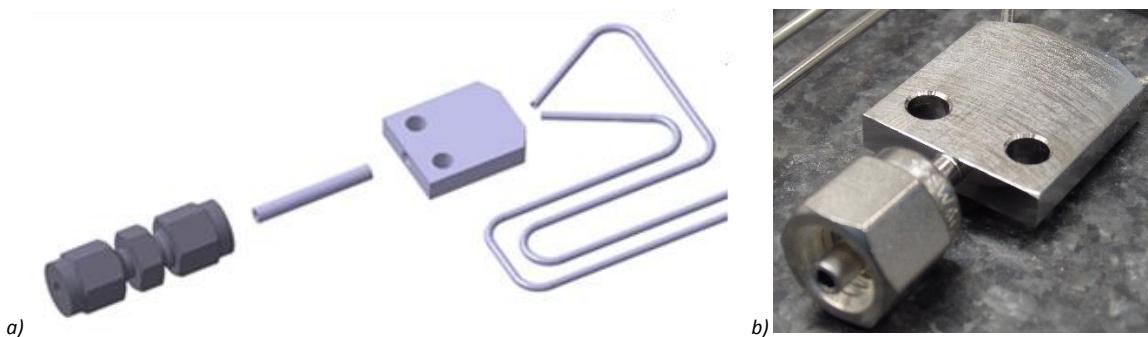

| 3.2   | Pressure Tests Connectors .....                                  | 41 |

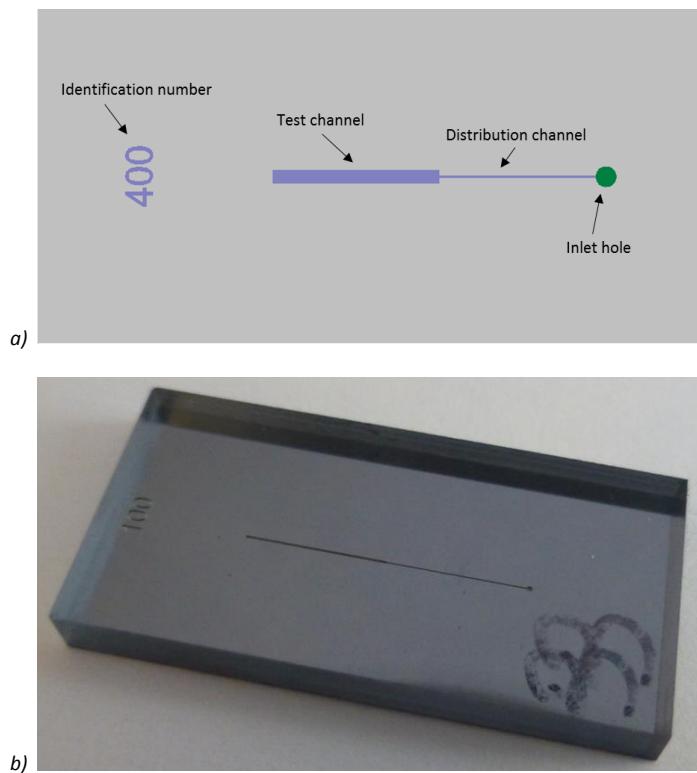

| 3.3   | Single-channel Test Structures .....                             | 45 |

| 3.3.1 | Single-channels Silicon/Pyrex .....                              | 45 |

| 3.3.2 | Single-channels Silicon/Silicon .....                            | 49 |

| 3.4   | Multi-channels Test Structures .....                             | 51 |

| 3.5   | Circulating Test Devices .....                                   | 53 |

| 4     | Fluidic and Thermal Tests .....                                  | 57 |

| 4.1   | NA62 GTK Liquid C <sub>6</sub> F <sub>14</sub> Flow .....        | 57 |

| 4.2   | ALICE C <sub>4</sub> F <sub>10</sub> Evaporative Flow .....      | 67 |

|       |                                                                |     |

|-------|----------------------------------------------------------------|-----|

| 4.3   | CO <sub>2</sub> Evaporative Flow.....                          | 69  |

| 4.3.1 | ATLAS FEI4 Cooling with CO <sub>2</sub> Evaporative Flow ..... | 70  |

| 4.3.2 | LHCb Velo Cooling with Evaporative CO <sub>2</sub> Flow .....  | 76  |

| 4.4   | CO <sub>2</sub> Two-phase Flow Studies.....                    | 77  |

| 5     | Microchannel Device Interfaces .....                           | 83  |

| 5.1   | Fluidic Connectors.....                                        | 84  |

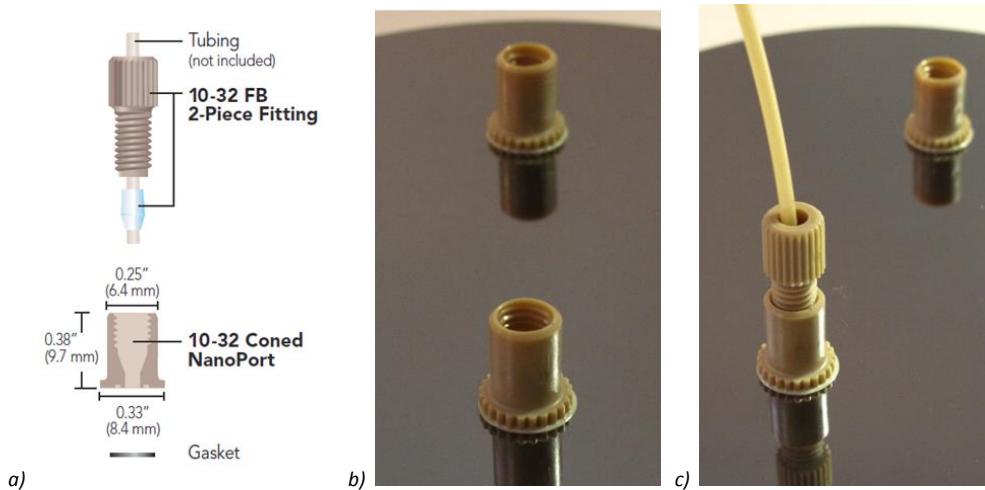

| 5.1.1 | NanoPort Peek Connectors.....                                  | 84  |

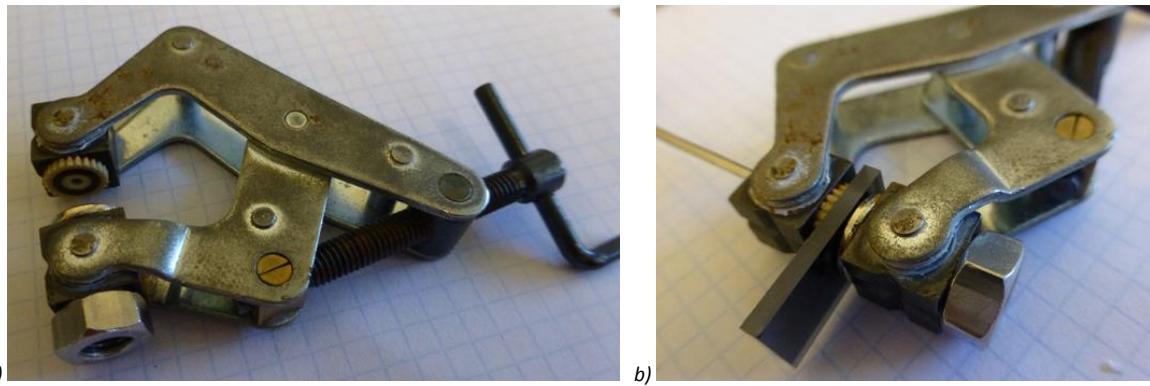

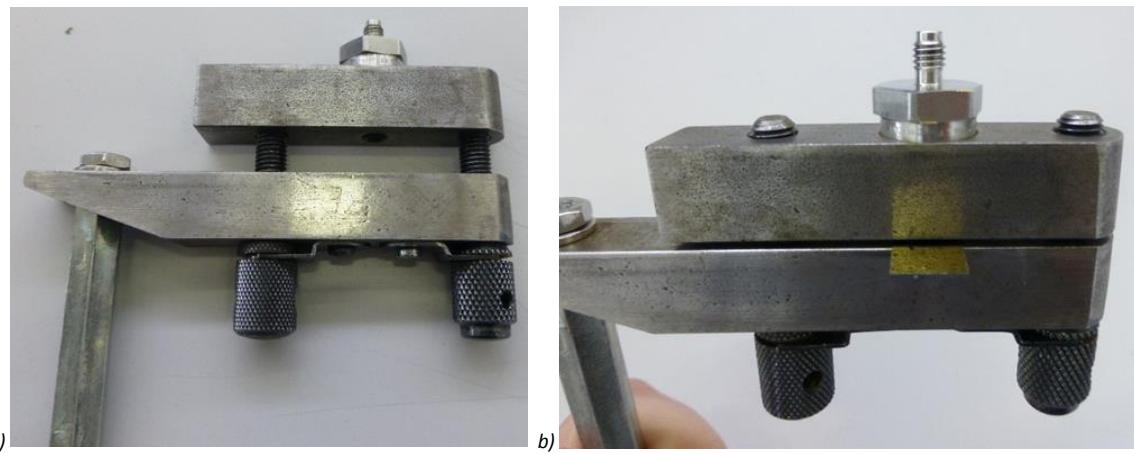

| 5.1.2 | Mechanical Clamping Connectors.....                            | 86  |

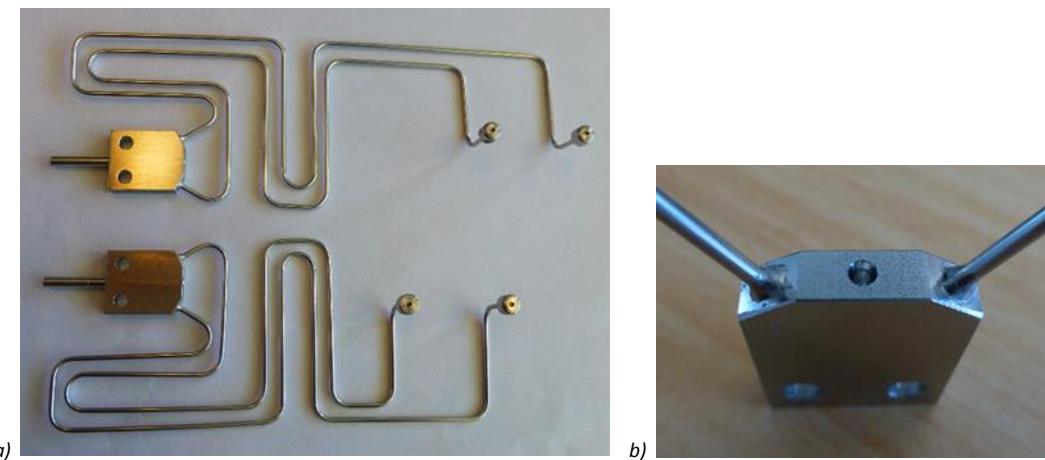

| 5.1.3 | Soldered Brass Ferrules.....                                   | 87  |

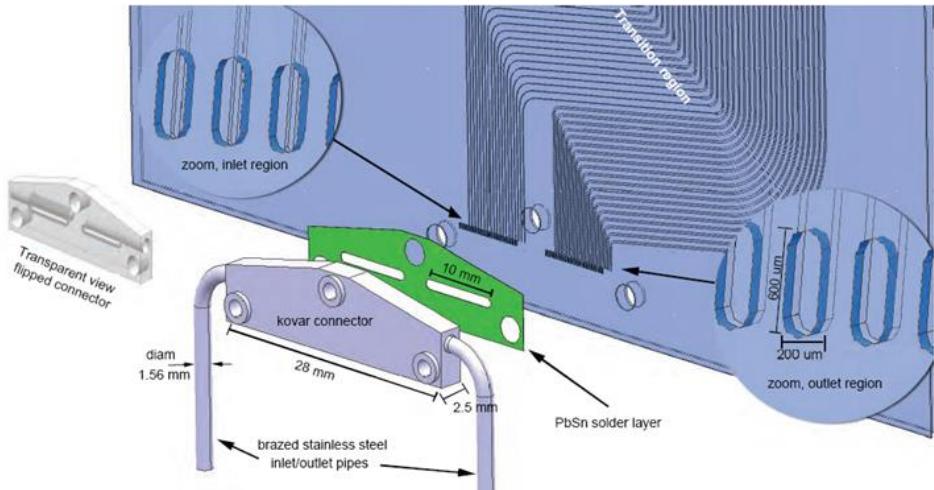

| 5.1.4 | Kovar Connectors .....                                         | 88  |

| 5.1.5 | LHCb Upgrade Connector.....                                    | 96  |

| 5.1.6 | 3D-Printed Connectors and Micro-channels.....                  | 97  |

| 5.1.7 | In-Plane Connectors .....                                      | 100 |

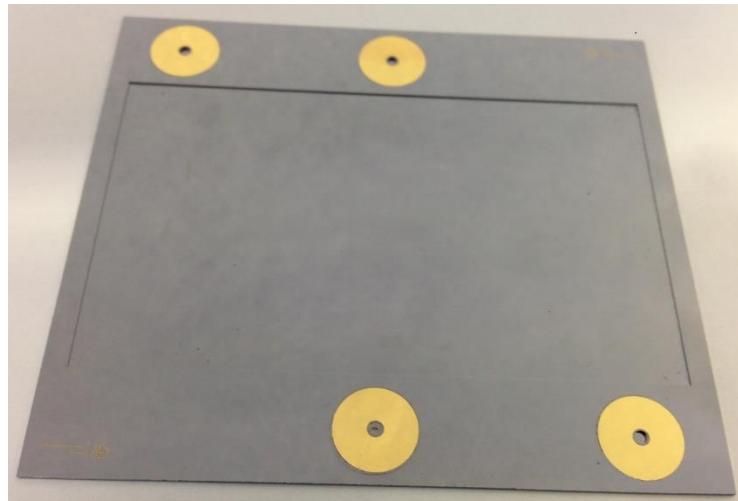

| 5.2   | Detector Gluing.....                                           | 101 |

| 5.2.1 | NA62 Glue Choice .....                                         | 102 |

| 5.2.2 | ATLAS Glue Choice .....                                        | 110 |

| 5.3   | Integration with Other Components .....                        | 110 |

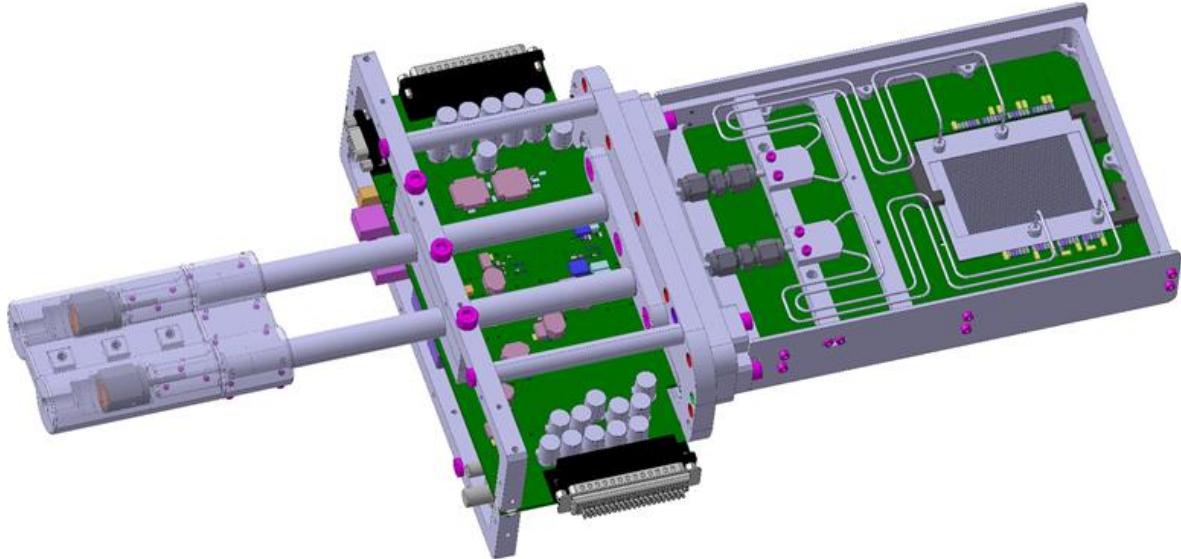

| 6     | Integration of the Cooling Device in the NA62 GTK Module ..... | 113 |

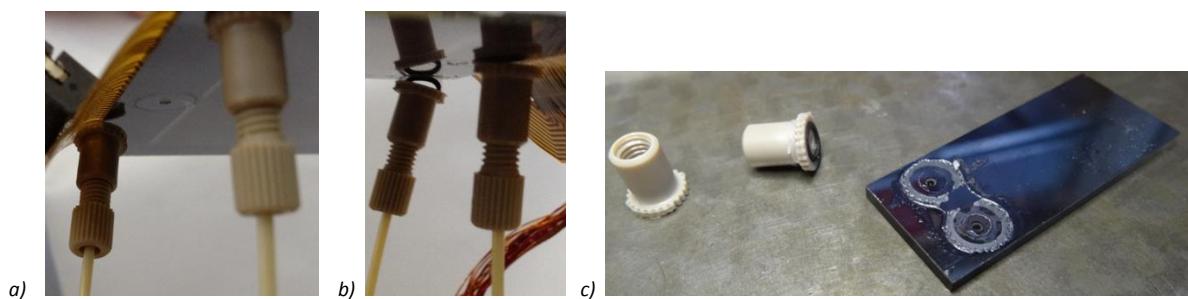

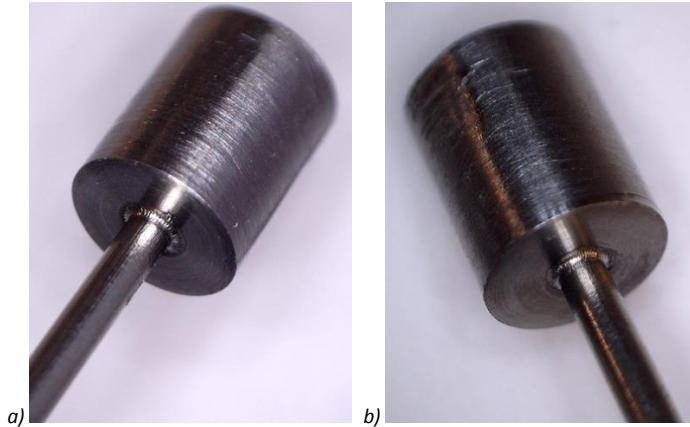

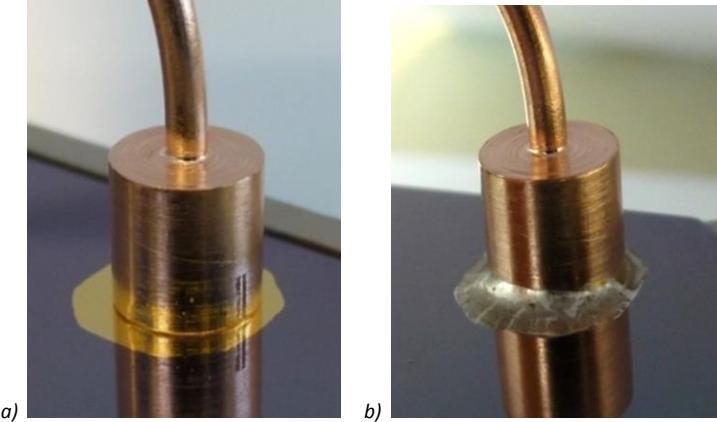

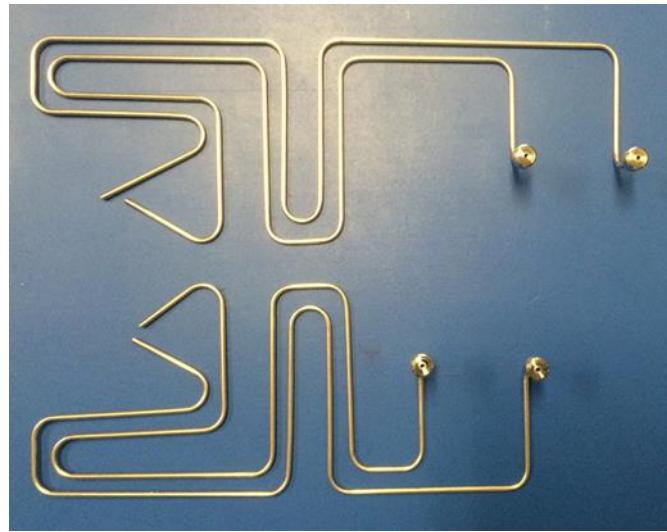

| 6.1   | Tubes Preparation.....                                         | 113 |

| 6.2   | Connector Soldering .....                                      | 116 |

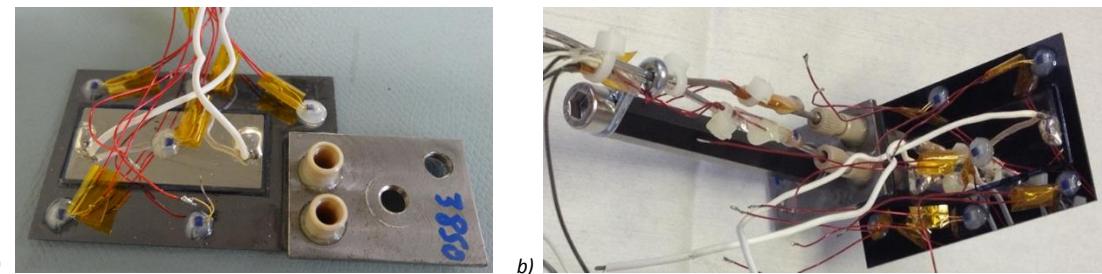

| 6.3   | PCB-Cooling Plate Interface .....                              | 118 |

| 6.4   | Detector Gluing.....                                           | 125 |

| 6.5   | PCB Aligning and Wire-bonding .....                            | 126 |

| 7     | Conclusions .....                                              | 129 |

| 8     | Bibliography .....                                             | 133 |

# 1 INTRODUCTION

## 1.1 CERN

CERN, the European Organization for Nuclear Research [1], is the world largest research centres in particle physics. It was founded in 1954 by 12 member states, in Geneva across the border between France and Switzerland. Nowadays it has 21 member states and scientists and physicists from more than 100 countries work there.

At CERN the fundamentals particles and the composition of the universe, are studied. The physics particles are studied with accelerators and detectors. The accelerators bring the particles to high energies and speeds and make them colliding between each other or with a fix target. The detectors analyse the results of these collisions.

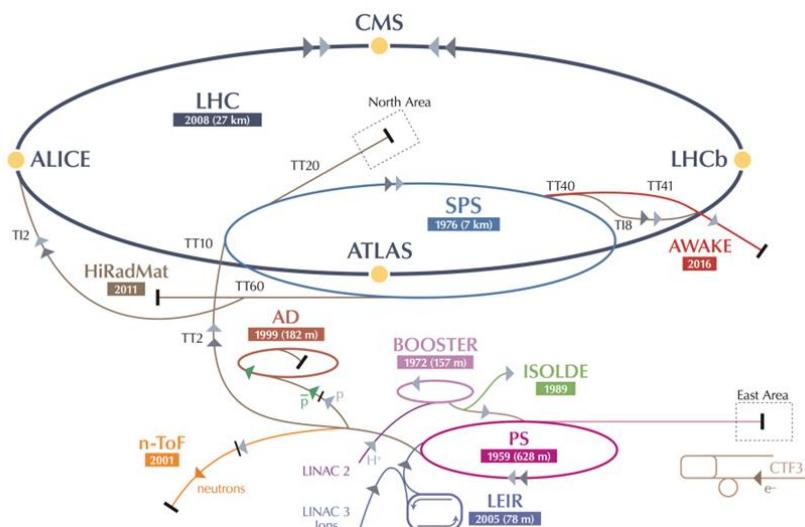

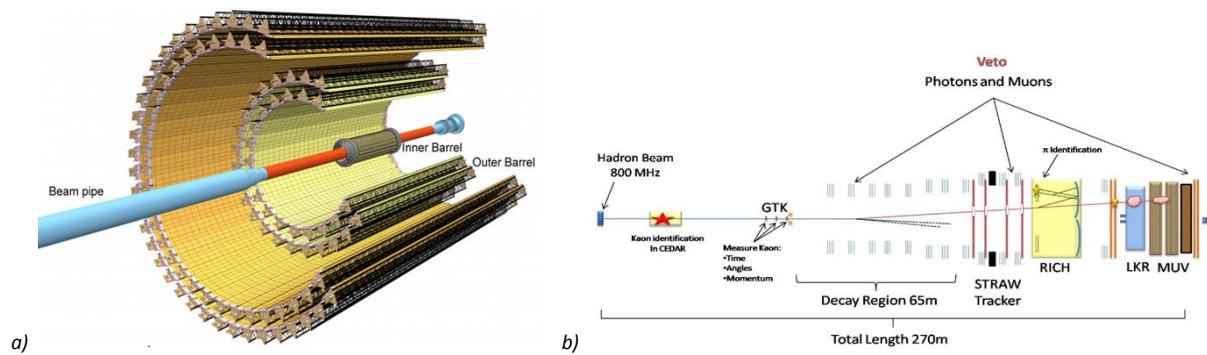

In order to increase the speed and the energy of the particles, the accelerator is a circular tunnel in which the particles are bended and focused together in a small beam using magnets while they are accelerated with radiofrequency cavities. The accelerated particles are mainly protons, extracted from a simple bottle of hydrogen gas. Quadrupole magnets are used to focalize the particle beam, while dipole magnets are used to bend the protons and make them following a circular trajectory. The protons are accelerated by the radiofrequency cavities that are hollow bodies in which the beam is passing. Inside the cavity an electric field that changes polarity with a very high frequency, is created. When the positive sign is oriented towards the incoming protons, they are attracted inside the cavity while, when the electric field changes, the protons are pushed away from the cavity with higher speed. In order to reach speeds close to the speed of light and very high energies, CERN hosts an accelerator complex with a succession of one accelerator following the other. The last accelerator of the chain is the biggest and more powerful CERN accelerator, the Large Hadron Collider (LHC). In *Figure 1.1* is shown the CERN accelerator complex scheme.

Figure 1.1: The CERN accelerator complex scheme.

The detectors instead are experiments placed at specific spots along the accelerators length that detect and analyse the results of the particle collisions. A detector usually tries to understand the nature of a particle by studying its momentum, energy, mass and charge. The structure of a detector is organized in layers of subdetectors each of them looking at a particular property of the particle or to a specific particle type.

A detector can be a ‘fix target experiment’ if it is analysing the result of a beam collision on a fix target. In this case the detector is built in a line-structure with the subdetectors placed one after the other along the particles trajectories. Contrary, the detector analysing the collision of two particle beams, is a ‘colliding beam experiment’ where the subdetectors are organized in a cylindrical structure around the collision point.

The four biggest colliding beam experiments at CERN are placed on the LHC ring and they analyse the results of the LHC colliding beams turning with a speed very close to the speed of light and with an energy of around 7 TeV. Between the four, ATLAS (A Toroidal LHC ApparatuS) and CMS (Compact Muon Solenoid) are general purpose detectors in charge of analysing all collisions of the two beams. The other two detectors, ALICE (A Large Ion Collider Experiment) and LHCb (LHC-beauty) are more specific detectors studying respectively heavy-ion collisions and CP violation in the interactions of b-hadrons.

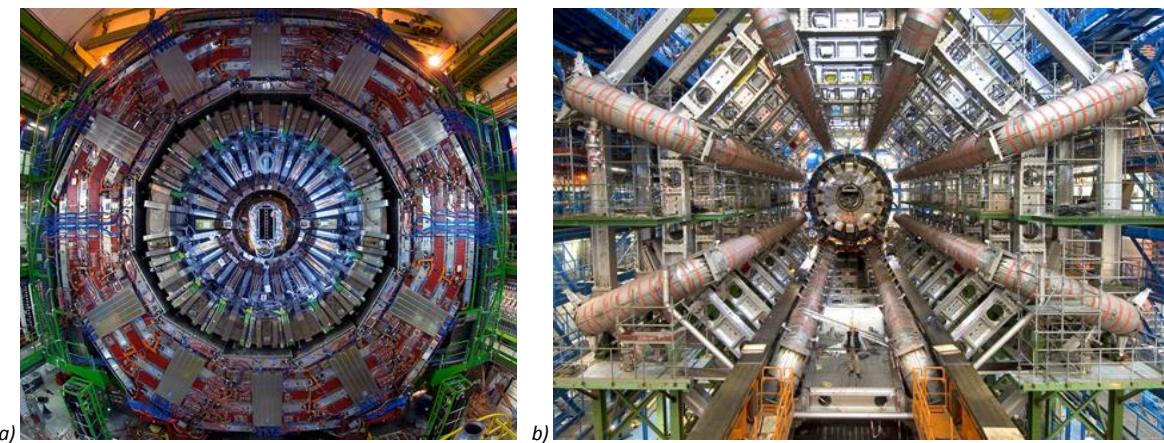

The particle beam of the SPS (Super Proton Synchrotron) accelerator has an energy of 450 GeV. The SPS is suppling several experiments, among them fix target experiments are present like the NA62 (North Area 62) or the COMPASS (Common Muon and Proton Apparatus for Structure and Spectroscopy) experiments. In *Figure 1.2* two pictures of the CMS and ATLAS colliding beam particle detectors can be seen.

Figure 1.2: Front pictures of CMS (a) and ATLAS (b) experiments at CERN.

Normally particles, after collision, travel in straight lines, but the presence of a magnetic field inside the detector make them bending according to their charge. From the curvature of the particle path, the particle momentum can be calculated that is a clue on the particle identity.

Among all detectors, tracking detectors can identify the path of a particle, while calorimeters can stop, absorb and measure a particle energy. A big range of techniques is then used by the identification detectors to understand a particle identity.

## 1.2 SILICON TRACKING DETECTORS

A fundamental component of a particle detector is the tracking detector used to identify the path of a particle after the collisions with another particle or with the fix target. The particle path is a fundamental information to understand the particle identity by discovering the particle momentum. During the tracking process the particle trajectory should be disturbed as less as possible. This leads to a minimization of the physical material of the detector structure. In order to identify the particle position on one layer and then, layer after layer, the particle trajectory, a suitable substance has to be crossed by the particle and an electrical signal is left on each layer. The particle has enough energy to ionize the substance that is crossing and so the detector has to find the ionization trail left behind. A particle creates ionization by detaching electrons and ions in an atom or in a molecule of the crossed substance. The detached ions and electrons cause a current flow that can be measured.

According to the different substance that the particles have to traverse the most used tracking detectors are: gaseous detectors, scintillator detectors and solid state detectors.

In gaseous detectors, the used substance is a gas, in which the atoms or molecules are ionized by the passing particles. In scintillator detectors the material used is a scintillator that absorbs the particle energy and scintillates by re-emitting the absorbed energy in the form of light. The detector is then coupled to a scintillator counter like a photomultiplier tube, a photodiode or a silicon multiplier to identify the particle position. The solid state detectors [2], also called semiconductor detectors, use a solid crystal material as detecting medium. When a particle passes, a current pulse is created by the ionization thanks to the internal structure of the semiconductor. The current is measured and the particle position is known.

The detecting medium usually used in solid state detectors is a semiconductor material like silicon or germanium. The internal structure of a semiconductor is connected to two electrodes, so when an ionizing particles traverse the semiconductor, the amount of free electrons and holes (the electron-deficient sites) creates a current that starts flowing in the material. The current amount is directly proportional to the particle energy.

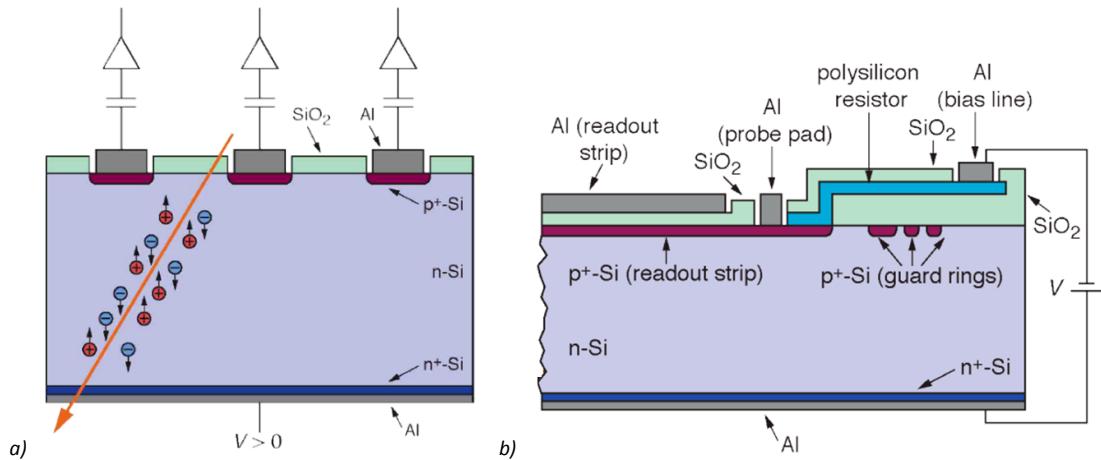

Silicon, as a detector material, can be fabricated in two forms: n-type, with a surplus of electrons in the structure, and p-type, with a deficit of electrons. The silicon *strip* detectors, in use at the LHC experiments, consist of n-type body material on which the back side has an aluminium layer while on the front side there are deposited strips of p-type material, in the middle of which a small strip of aluminium is deposited (*Figure 1.3 a*). The aluminium strips are separated from the p-type strips from a thin layer of insulator. By applying in the detector material an electric field between the p-type material and the back aluminium face, when a particle passes through it, it creates ionisation in the body material. The free electrons move to the positive back aluminium side, while the vacancies left by the electrons move towards the negative p-type strips. When the vacancies reach the p-type, they induce a measurable charge on the aluminium strips that are connected to the read-out channels. The electronics read-out components are placed at the end of the sensor on one side of the strips (*Figure 1.3 b*). By reading which aluminium strip collected the charge is possible to know where the particle passed. If a similar detection system is applied in the other direction is possible to see the x-y coordinates of where the particle passed.

Figure 1.3: Internal structure of a strip detector: transversal section (a) and longitudinal section (b).

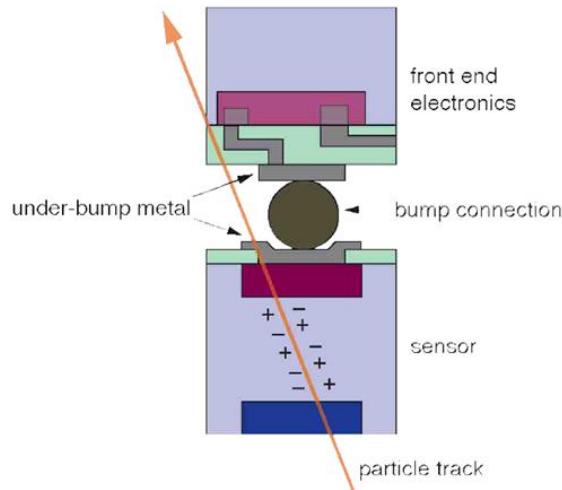

Another type of silicon detectors is the *pixel* detector. This time the p-type material is not present as a strip but as a small square, a pixel. The working principle is the same, but this time the electronics to collect the charge information is not placed at the end of the sensor but below. Each pixel is connected to the electronics through a metal ball, thanks to a process called bump-bonding, to the corresponding electronic path. In Figure 1.4 is possible to see a cross section of a single pixel with the corresponding electronics. Thanks to its structure, the pixel detector is, in terms of precision and efficiency, better than strip detector. In the strip detectors the electrical signal is slower since it has to cross the complete detector before delivering the signal and furthermore the pixel structure allows a more precise resolution detecting more particles.

Figure 1.4: Internal cross section of a pixel detector (Ref. [4]).

The sensitivity of these detectors is increased at low temperature. With the increase of temperature the conductivity of the semiconductor material increases meaning that the number of electrons and holes increases for the temperature effect and not due to particle crossing. Also the leakage current (uncontrolled parasitic current flowing in the semiconductor not due to crossing particles) starts to increase with temperature and so the detector sensitivity decreases.

Particle detectors, and in particular silicon trackers, are exposed to high intensity particle beams and this can cause severe radiation damage that degrades the sensor performances. The intense particle beam can cause severe damages in the semiconductor detector structure and consequently in the

detectors performances [3]. These damages are temperature dependent and with the increase of temperature the radiation damage is more and more important in the detector, and the detector work life is significantly reduced. For all these reasons it is necessary to keep the detector at low temperature integrating in the detector structure also a cooling system.

### 1.2.1 Cooling of Tracking Detectors

In addition to the reasons just explained for the silicon detectors, the tracker detectors need an efficient cooling system to remove the heat produced by the electronics from the small and compact mechanical volume typical of these structures [4]. From the physics point of view a good pixel detector has to be hermetic within the cover range, as transparent as possible to particle (the material of the detector must be minimized to not disturb the particle tracks) and stable to a few microns to obtain better results. Furthermore, as explained before, the detector must be operated at low temperatures (below 0 °C), therefore it has to be kept in dry atmosphere to avoid condensation. All these requirements are translated in a set of specifications for the mechanical structure of a detector. The detector structure has to be lightweight to minimize the material crossed by the particles, stiff to guarantee the stability of the detector, stable by using materials with the same coefficient of thermal expansion (CTE) to avoid thermal deformations and stresses, radiation hard and with an efficient cooling system. The cooling system should use a coolant fluid stable, non-flammable, non-toxic, electrical insulator.

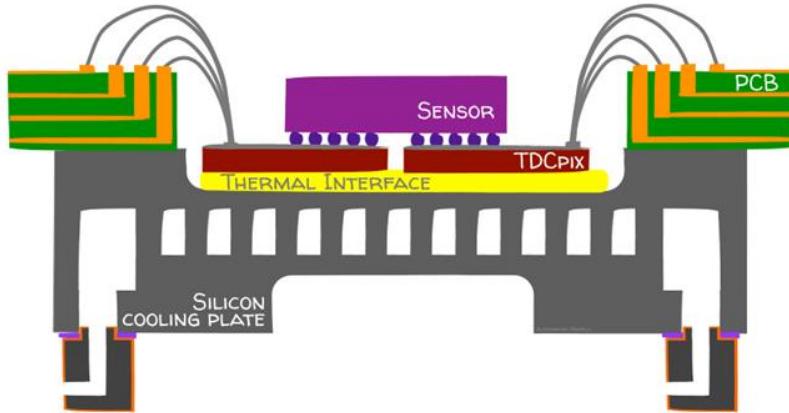

A pixel detector is usually composed by the silicon sensor, sensitive to the particle passing, by the electronic chips, to collect and read the information of the sensor, and by the hybrid circuit, usually build on a printed circuit board (PCB), connected to the read-out chips housing the chip control module and providing the optical, data and power cables. All these components should be integrated together in the detector structure and they should be coupled to the cooling system.

The heat is produced mainly in the electronic read-out chips and it has to be transferred to the coolant fluid. One of the detector requirements in term of cooling system is a good temperature uniformity over the detection area to minimize any possible mechanical stress and to let all the detector pixels react at the same way. A low temperature difference between the cooling fluid and the silicon detector is also needed to avoid really low cooling temperatures that would require higher technical problems and costs.

The three main components that have to be assembled together by fulfilling all the detector requirements are the detector module, the mechanical support and the cooling channels.

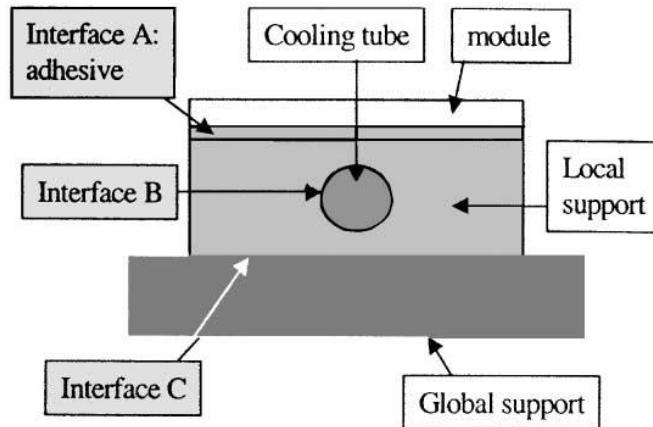

When the new generation of pixel detectors was described in 2001 in the review of M. Olcese [5], the best mechanical structure of a detector and the most efficient cooling system, were presented for the CERN experiments ALICE, ATLAS and CMS and for the Fermilab BTeV pixel detector. The detector scheme is presented in *Figure 1.5* where three interfaces are visible. The three interfaces should minimize the CTE mismatches between the different materials and they should introduce a flexible joint between them. The first interface (A in the picture) is the interface between the detector module and the support structure; this is a critical point not only for the stability of the detector but also for the thermal coupling of the detector. Interface A should guarantee a good thermal contact while minimizing mechanical actions on the module due to CTE mismatches. Interface B is the coupling of the cooling tube to the support structure and it should also guarantee an efficient heat transfer. Interface C instead is just a structural interface between the local and the global detector support.

The first generation of cooling systems for the pixel detectors was using carbon fibre support structures glued to the modules, cooled with stainless steel or aluminium tubes connected to the

module through thermal paste. The coolant fluids used were fluorocarbon fluids either in mono or two-phase flows.

Figure 1.5: Thermal stability: relevant interfaces (Ref. [5]).

### 1.3 SILICON MICRO-CHANNEL COOLING OF TRACKING DETECTORS

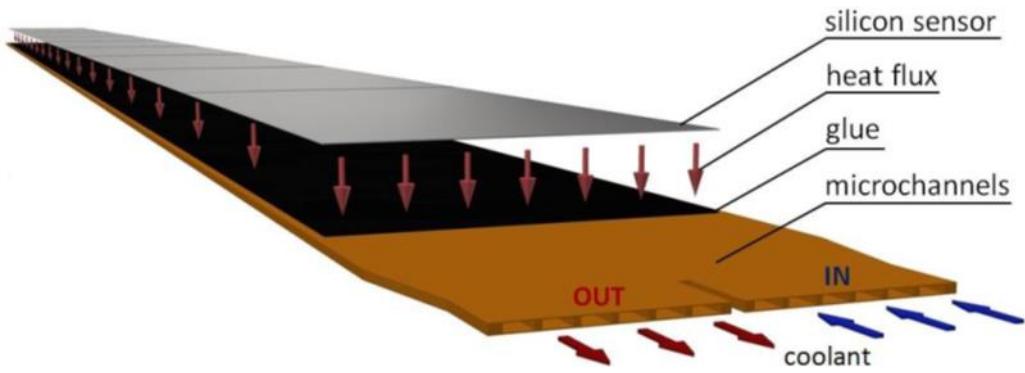

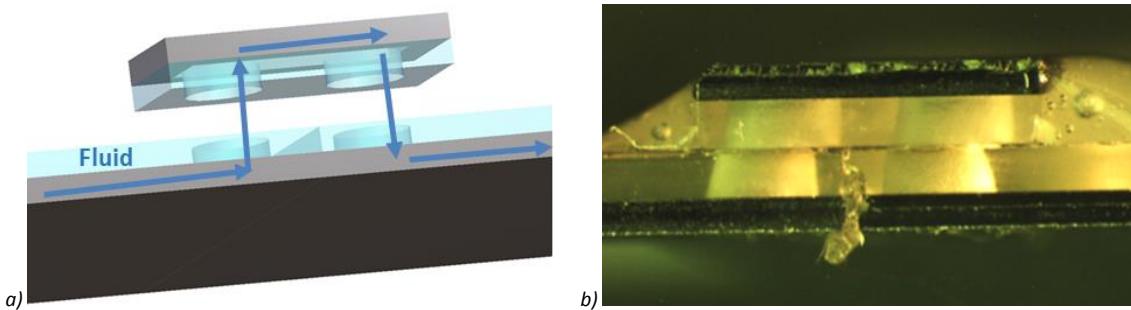

In the last years, the PH-DT (Physics Department, Detector Technologies) group at CERN [6] proposed a new system for the thermal management of particle tracking detectors using a micro-channel fluidic circuit [7],[8]. The micro-channel circuit is embedded in a silicon wafer that is then glued through a thermal interface to the detector module. In the micro-channels a coolant fluid is circulate to dissipate the heat produced by the electronics.

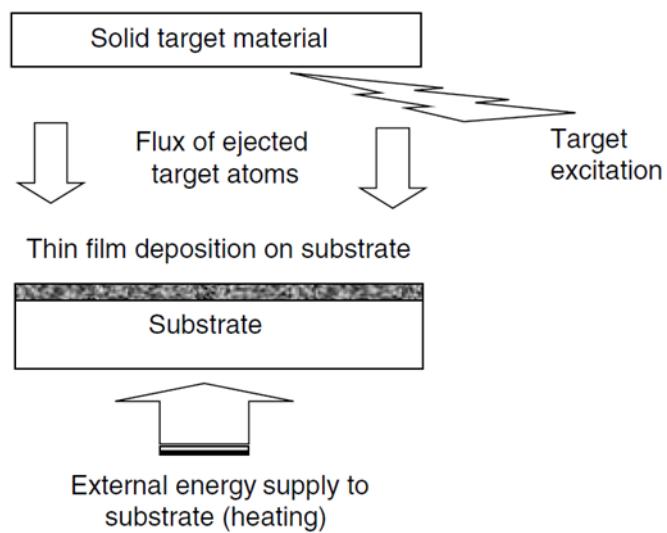

The first idea of liquid cooling using micro-channel instead of air cooling was presented by Tuckerman and Pease in 1981 [9]. The advent of more and more high-speed, high-density and very large scale integrated circuits was demanding an effective and compact system for heat removal. The authors investigated a new cooling system for planar integrated circuit based on liquid cooling. The theory of a system based on convective heat transfer with a laminar flow in micro-channels was discussed in the paper. They then designed and tested a first prototype by etching micro-channels inside a silicon wafer and closing the channels by anodic bonding with a Pyrex wafer. They deposited on the silicon surface a thin layer of metal to simulate the heat produced by the integrated circuit and they circulated deionized water at 23 °C inside. The maximum allowed temperature increase for the integrated circuits was between 50 and 100 °C above the fluid inlet temperature. Power densities up to the values of 790 W/cm<sup>2</sup> were proven to be cooled by the 1 cm<sup>2</sup> area of the prototype.

Since this work, the micro-channel cooling of electronic chip both in single-phase and two-phase flow, has been extensively studied and several exhausting reviews have been recently published [10], [11], [12], [13], [14].

The first micro fabricated fluidic devices applied to particle physics were scintillation particle detectors based on microfluidics [15]. The scintillation detector consists in a single microfluidic channel filled with liquid scintillator. The channel is designed to reproduce an array of scintillating waveguides each coupled to a photodetector. When the particle is passing in a specific part of the channel, that waveguide scintillates and the photodetector is able to know the exact particle position. A particle detector prototype was built using an SU-8 resin and tested with electrons from a radioactive source. After this first application of microfluidics in particle detectors, the micro-channels were evaluated as an alternative technique for cooling the electronics modules of tracking detectors.

The micro-channel cooling system presents a very efficient solution for the cooling of particle detectors. In

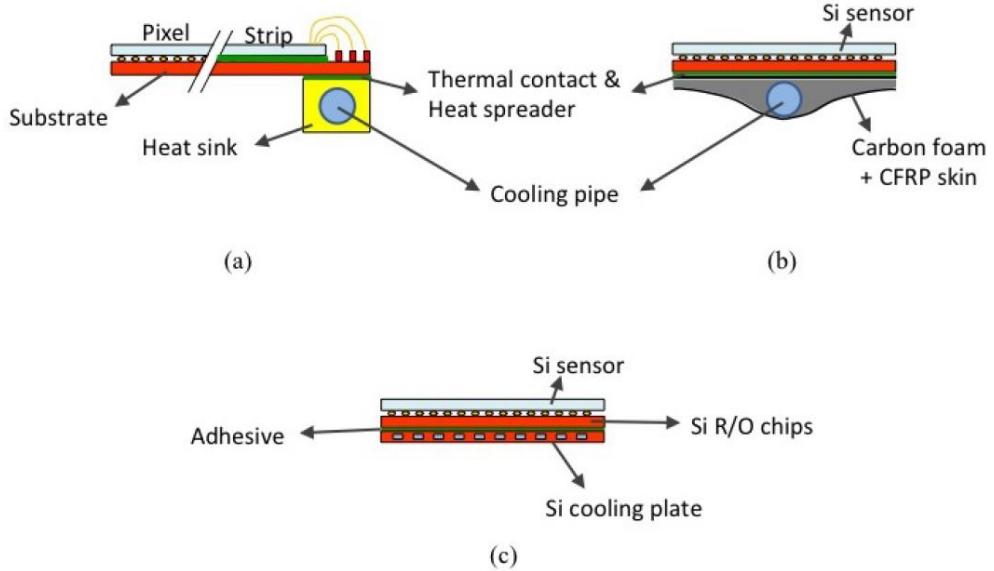

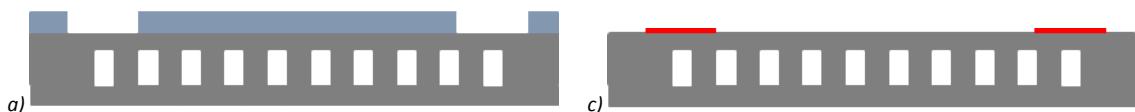

*Figure 1.6* it is possible to see a comparison between the standard cooling systems adopted for the pixel detectors and the novel micro-channel based system.

*Figure 1.6: Cooling configurations for tracking detectors (Ref. [7]).*

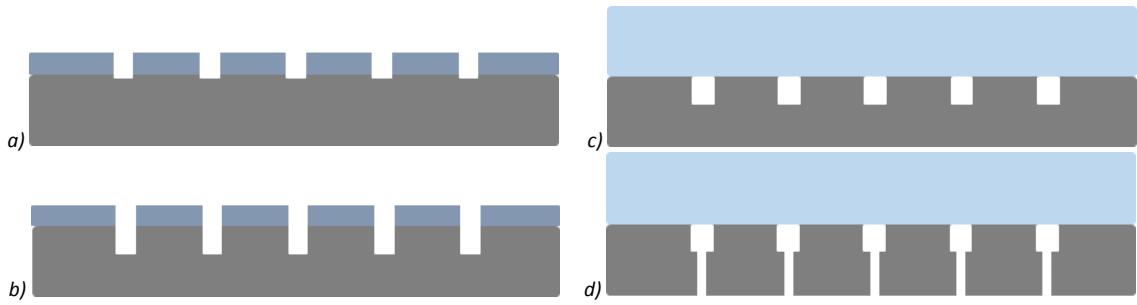

The standard thermal management techniques (*Figure 1.6 a,b*), as previously discussed, present a cooling system based on a high thermal conductivity structure with a cooling pipe embedded inside that removes the heat produced by the detector module.

The first solution (*Figure 1.6 a*) is referring to a standard cooling scheme adopted in the first generation of silicon trackers at LHC, both for strip and pixel detectors [16]. The sensor modules are connected with a thermal interface to a heat sink in a lateral position. For the CMS tracker, for instance, the cooling tube is a metal tube circulating a fluorocarbon fluid,  $C_6F_{14}$ . The tube is bonded to two CFRP (Carbon Fibre Reinforced Polymers) blades that are holding the silicon modules. The internal space between the two blades is filled with a foamed material to guarantee rigidity and the thermal conductivity. In this solution the lateral cooling pipe brings important mechanical stresses due to the non-uniform thermal gradient across the module. Furthermore the small thermal contact area between the module and the heat sink and the long chain of thermal resistances, increase the thermal gradient across the module, inducing mechanical stresses in the structure and increasing the TFoM. The Thermal Figure of Merit (TFoM) is defined as the ratio between the temperature difference between the sensor and the fluid, over the power density. The TFoM is an indicator of the efficiency of a thermal management system because it defines, for a given power density, how cold the cooling fluid has to be, in order to keep the sensor to the target temperature.

In order to improve the thermal uniformity over the module area, in the second solution is possible to see how the cooling pipes is placed at the centre of the structure to allow a more uniform thermal flux. The solution presented in *Figure 1.6 b* was used for the ATLAS IBL (Insertable B-Layer) pixel detector in the phase I upgrade [17]. The IBL is the innermost part of the ATLAS detector, and it is composed by fourteen local supports for the silicon modules arranged cylindrically around the beam line called staves. The staves are tilted in order to have an overlap between them and cover the all area. The stave structure is built in carbon foam material that provides a thermal path for the heat generated in the sensor and in the electronics. The titanium cooling pipe is strongly bonded to the

structure with a thermally conductive epoxy resin. The coolant fluid used is CO<sub>2</sub>. The rigidity of the stave is provided by a CFRP skin, the Omega, that surrounds the carbon foam. The CTE difference between all materials involved in the stave structure is considerable and it induces a non-negligible mechanical deformation in the stave. The largest deformation occurs when the stave is cooled while the detector modules are not powered, and the corresponding bow in the stave reaches a maximum of 0.15 mm. These problems were taken into account during the detector design and construction and the minimum gap between one stave and the other was 1 mm in order to leave enough space to avoid interferences and clashes.

An innovative solution, shown in *Figure 1.6 c*, takes advantage of the high cooling power of micro-channels to improve all aspects of the thermal management of the pixel detectors. The micro-channel circuit is embedded in a silicon wafer and it is then glued to the detector module. All the material involved in the structure is silicon; the CTE of the cooling part is exactly the same as the one of the detector modules and so mechanical stresses due to CTE mismatches are avoided. The thermal gradient across the detector is uniform since the channels are designed to be equally distributed along the module area. The thermal flux is flowing in the vertical direction from the electronics and sensor, to the channels. The interface between the cooling pipe and the support structure is eliminated since the silicon device acts as support structure and as cooling pipe at the same time. The use of micro-fabrication techniques allows the production of very thin cooling devices, thus minimizing the amount of material to be crossed by the particles.

One crucial point in the three configuration shown in *Figure 1.6*, is the thermal interface between the silicon modules and the detector structure. This thin layer should provide a perfect and uniform thermal contact without air bubbles or defects, while being also radiation resistant. It should be as light as possible to minimize the material crossed by the particles and, for the solutions of *Figure 1.6 a,b*, it should also be enough flexible to absorb the CTE mismatches in the whole structure. Several studies will be presented in *Chapter 5* to select the best suitable adhesive.

The critical point of the correct thermal interface between the cooling structure and the detector modules can be avoided in the future thanks to the silicon micro-channels. The micro-channels are etched in a silicon wafer as well as the detector modules, in a future it can be imagined to etch the channels on the backside of the same wafer of the detector. In this way a monolithic structure could be obtained, avoiding the thermal interface between the two parts.

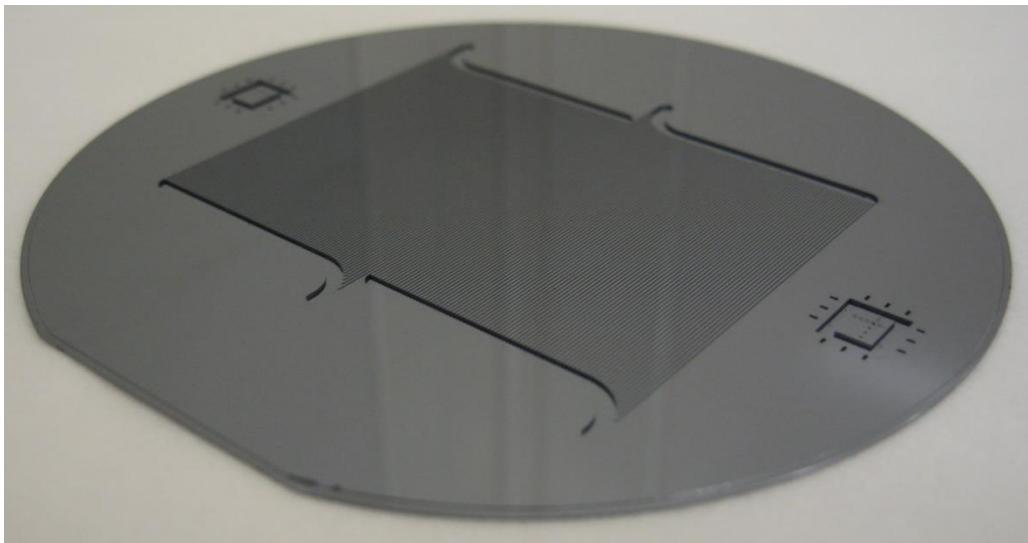

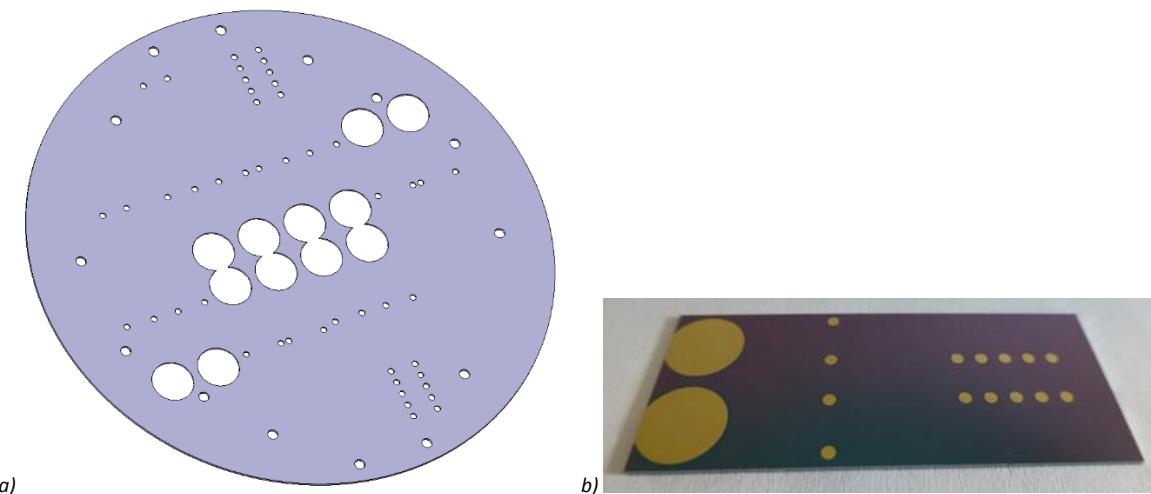

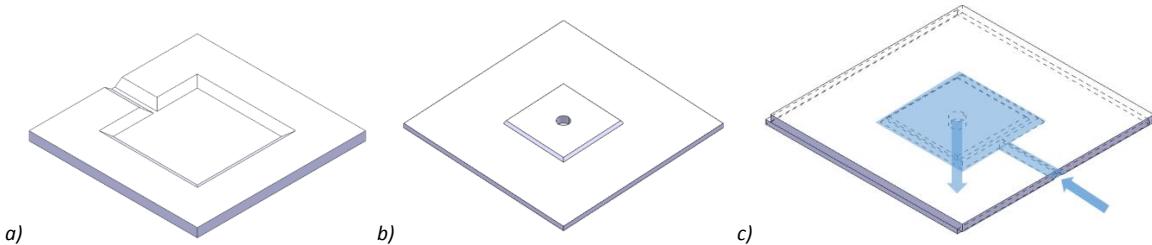

A silicon micro-channel cooling device is fabricated using standard micro-fabrication techniques inside cleanrooms. The device fabrication starts with the photolithography mask fabrication to be able to transfer, on the silicon wafer surface, the design of the cooling circuit. The micro-channels are plasma etched on the silicon surface using a resin mask. The micro-channels are then sealed by a cover wafer that can be of Pyrex material with an anodic bonding technique, or again in silicon using a direct bonding process. Usually silicon-Pyrex devices are used in a preliminary phase due to the simpler anodic bonding technique compared to the direct bonding process. Pyrex, thanks to its transparency, is also used for visualizing the flow in the channels. In a second time, for final prototyping and for the insertion of the cooling system in the detector assembly, only silico-silicon devices are used. The final step of the fabrication is the etching of the openings for the inlet and the outlet of the fluid. Depending on the detector structure a very final step of localized thinning can be applied to minimize the material in the detecting area. In *Figure 1.7* is possible to see a simple design example for a silicon-Pyrex wafer fabrication. More details on the micro-fabrication will follow in *Chapter 2*.

Figure 1.7: Micro-channel simple design for a silicon-Pyrex device.

## 1.4 SILICON MICRO-CHANNEL COOLING AT CERN

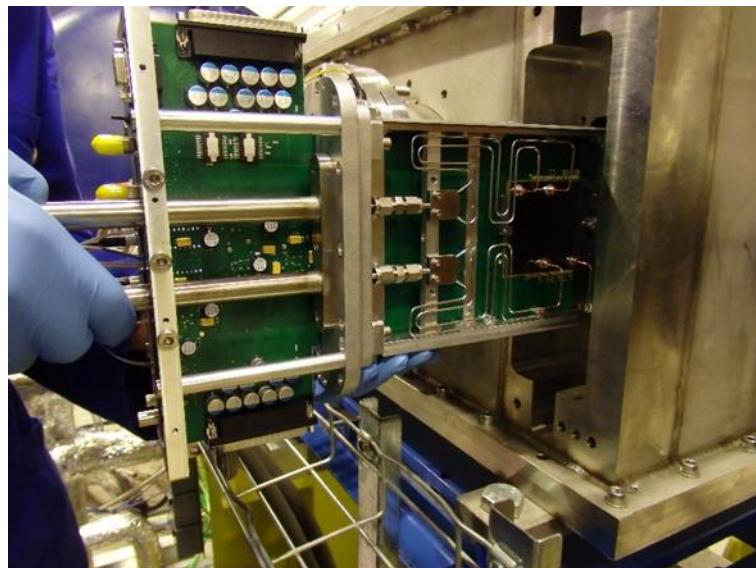

The application of micro-channel cooling systems to particle physics is gaining more and more success. The first micro-channels cooling system was installed in 2014 for the thermal management of the NA62 GTK (GigaTracKer) stations at CERN [18]. The three GTK stations are cooled by a micro-channel silicon device circulating  $C_6F_{14}$ , in liquid flow. The LHCb VELO (Vertex Locator) detector has adopted a micro-channels based cooling system for its upgrade in 2018 [19]. The cooling fluid in the VELO detector will be  $CO_2$  circulating in two-phase flow. A micro-channel cooling system is the backup solution for the ALICE ITS (Inner Tracking System) upgrade [20]. The silicon micro-channels circulate in this case  $C_4F_{10}$ , in evaporative flow. Very preliminary studies are also going on for the cooling of an ATLAS FEI4 chip, cooled with  $CO_2$  evaporative flow, for a future integration in the upgrade of the ATLAS pixel detector.

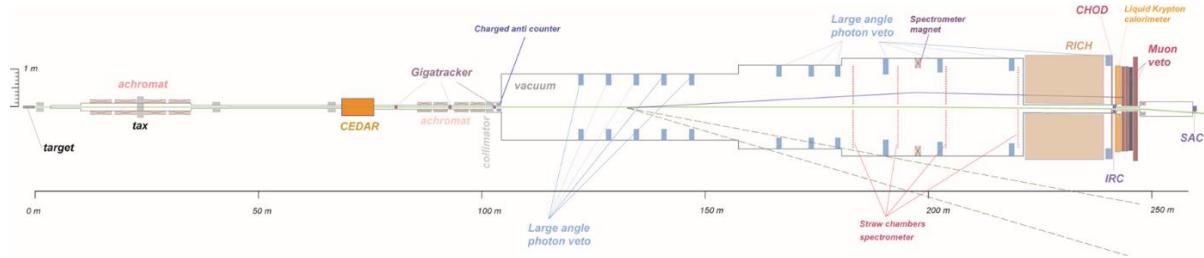

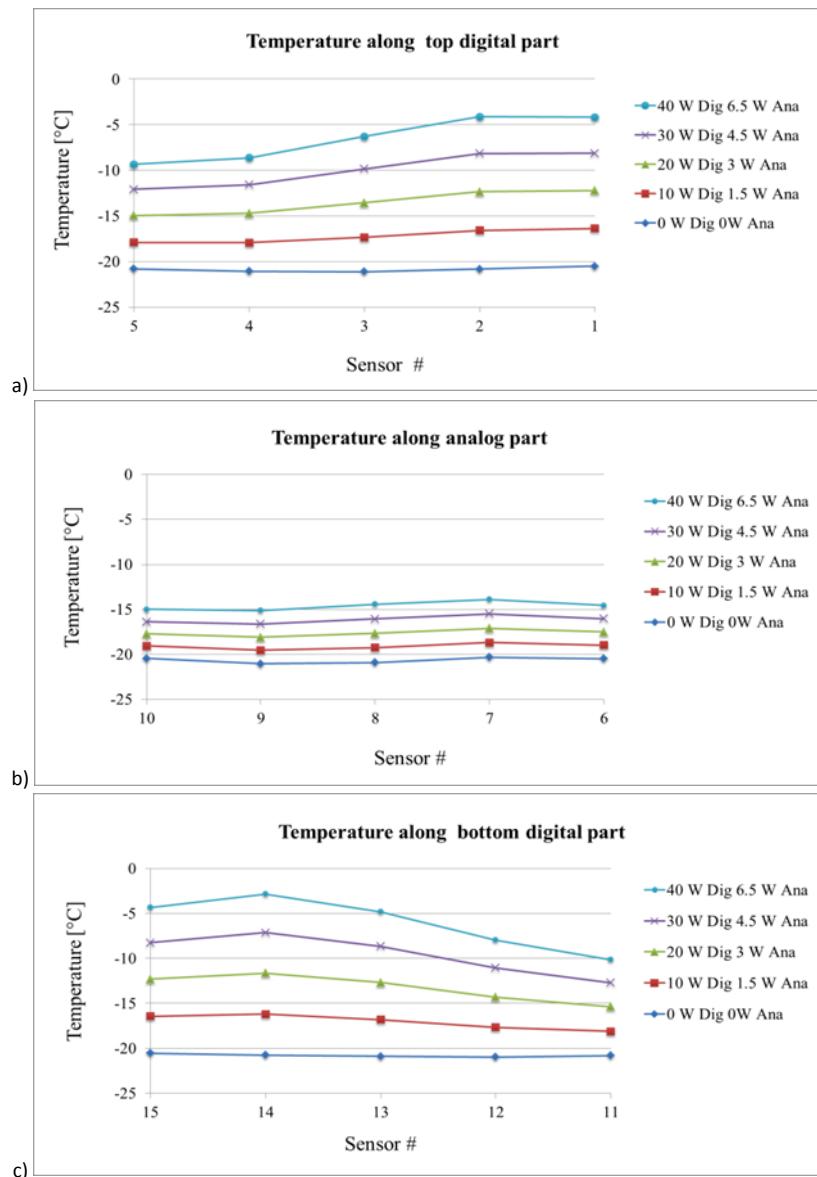

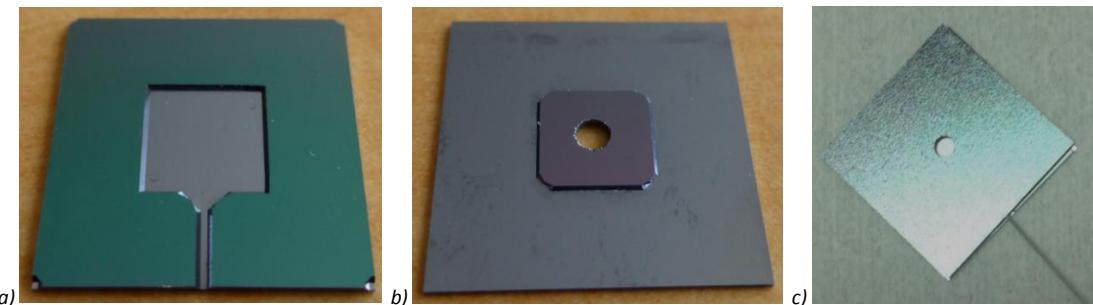

### 1.4.1 NA62 GTK

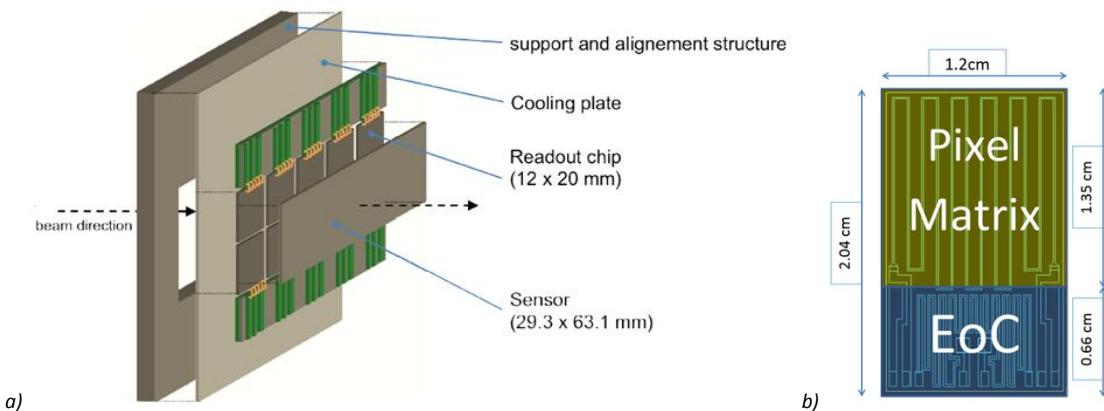

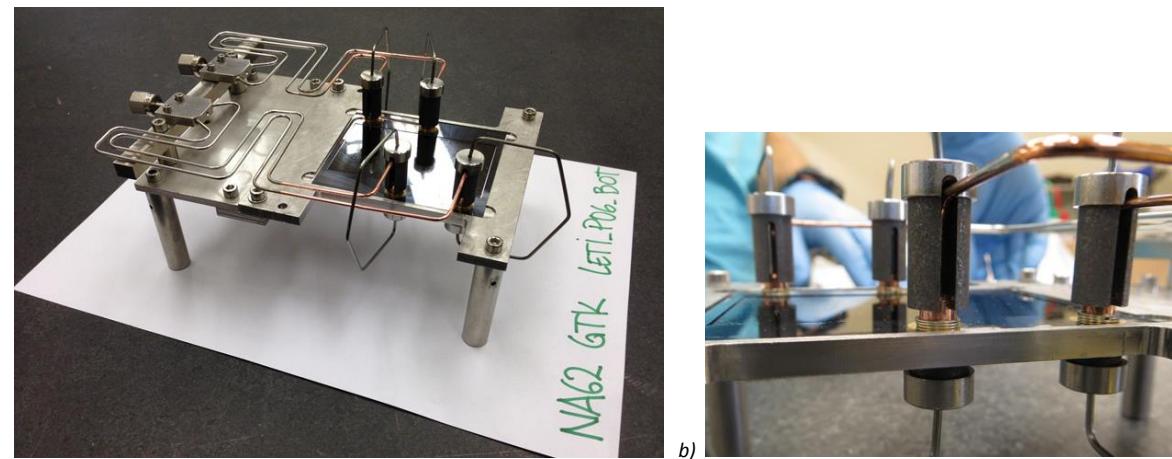

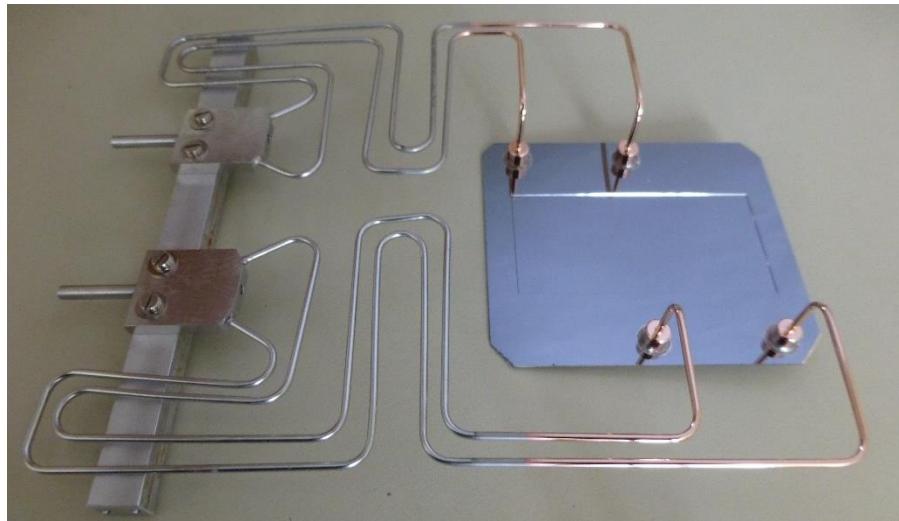

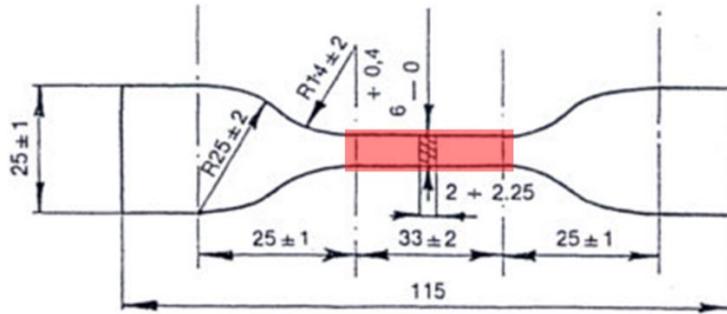

The NA62 GTK detector was the pioneer in evaluating micro-channel cooling for the thermal management of its three stations. The NA62 detector [21] is a fix target detector of the SPS accelerator, focused on the rare decay of charged kaons. It started physics data taking in 2015. The three GTK stations provide precise measurement of momentum, time and angle of the incoming particle beam. The detector layout consists in a silicon sensor 63x29 mm bump-bonded to ten 12x20 mm read-out chips. The power dissipation foreseen is  $2.5 \text{ W/cm}^2$  for the analog part of the chip and  $0.4 \text{ W/cm}^2$  for the central digital part, for a total maximum power of 48 W per station. The detector requirements are to keep the sensor surface at a temperature below  $-10^\circ\text{C}$  and a maximum temperature gradient of  $5^\circ\text{C}$  along the sensor area.

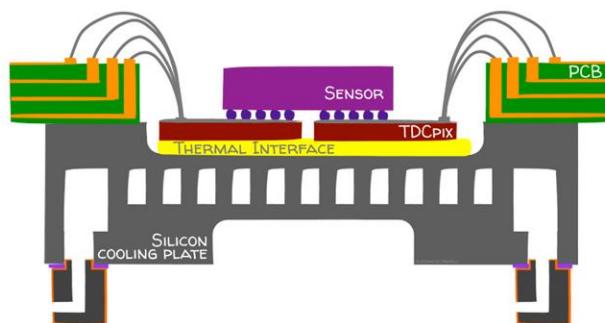

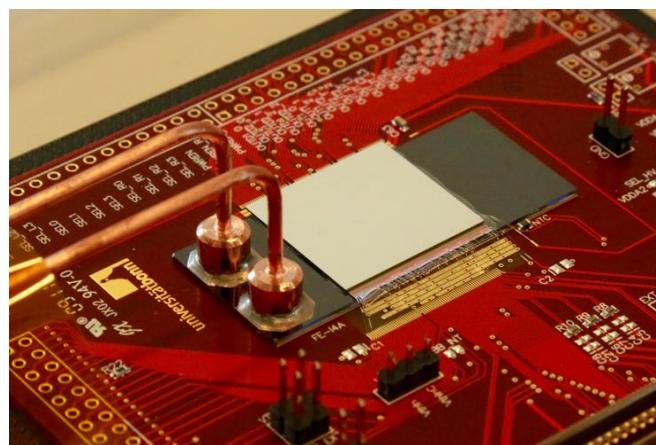

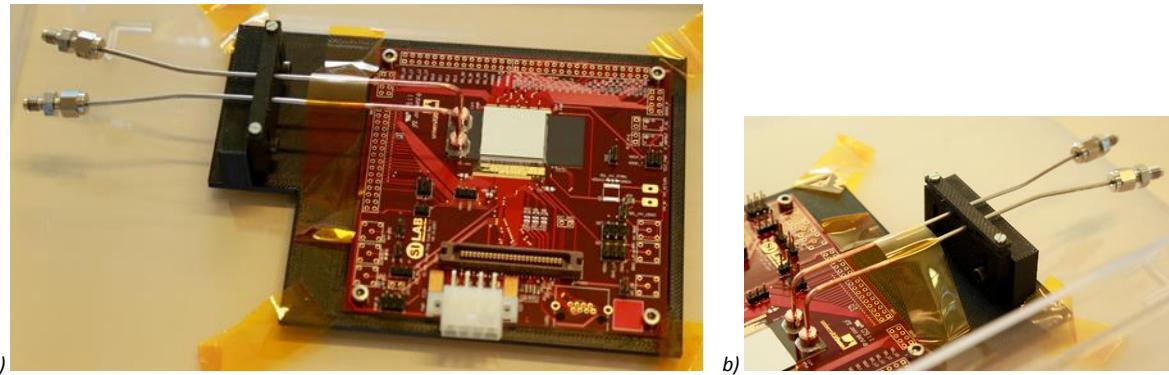

The micro-channel device foreseen for this application is a 480  $\mu\text{m}$  thick silicon wafer with a localised thinning in the central part, in order to minimize the material crossed by the particles in the sensor area. In the central part the micro-channels device is 150  $\mu\text{m}$  thick. The detector assembly of the silicon sensor bump-bonded to the ten read-out chips is glued onto the thinned part of the micro-channel plate with a thermal interface. The external parts of the chips are then wire-bonded to the PCB for data transfer. A cross section scheme is shown in *Figure 1.8*.

Figure 1.8: Cross section concept of the micro-channel cooling for the NA62 experiment.

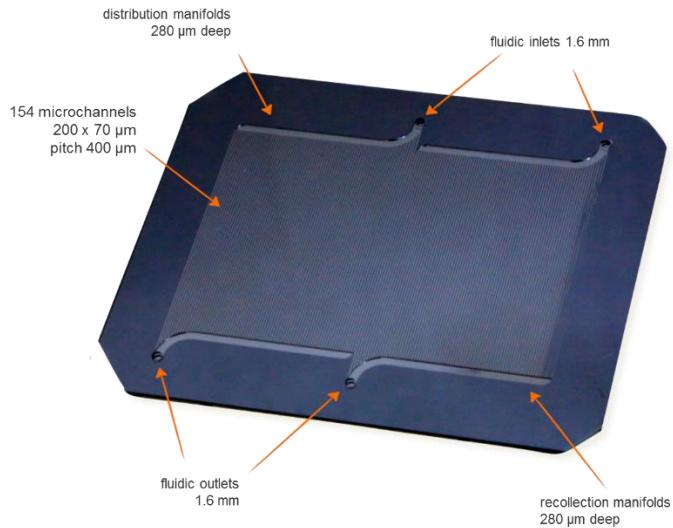

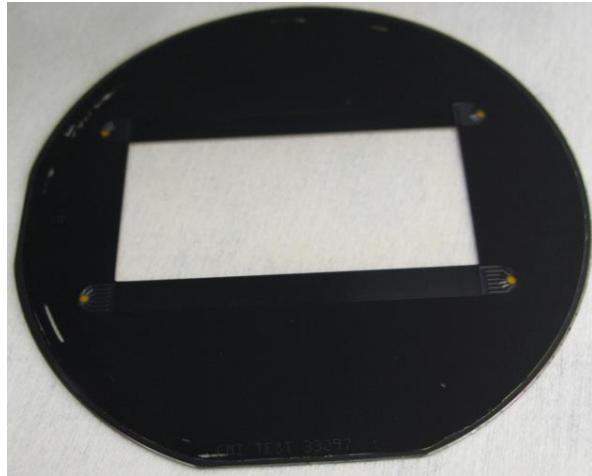

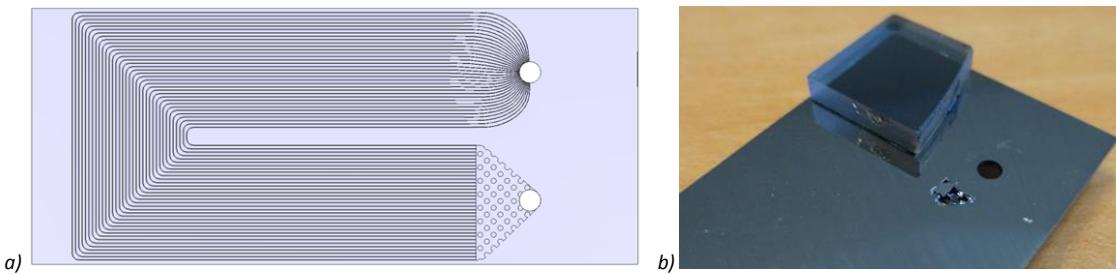

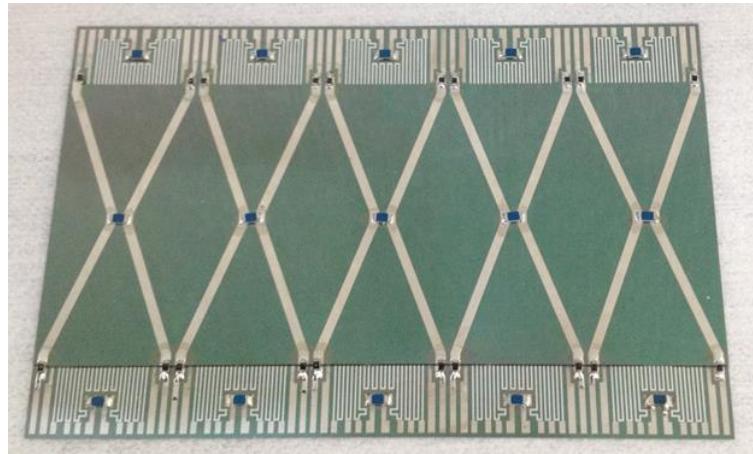

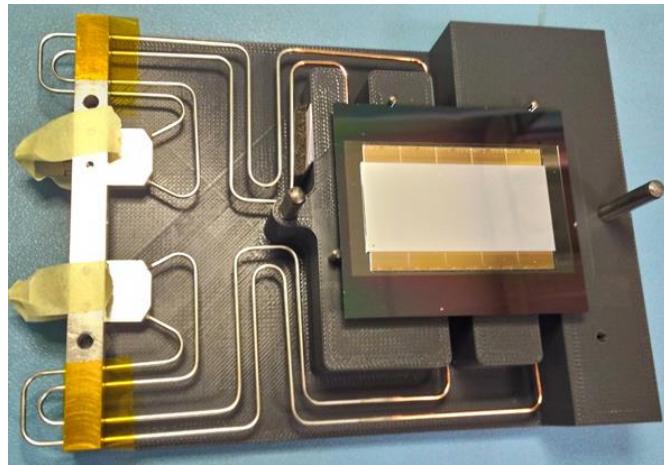

The micro-channel design consist in two parallel circuits for the  $C_6F_{14}$  liquid flow. The 154 micro-channels of the device are  $200 \mu m$  wide and  $70 \mu m$  deep, separated by  $200 \mu m$  walls. The two fluidic circuits start with an inlet hole and a distribution manifold from where the fluid is distributed in the channels; the circuits end with a recollection manifold where the fluid from the channels is collected before leaving the device from the outlet hole. In Figure 1.9 it is possible to see a picture of a micro-channel device designed for NA62 with the transparent front Pyrex wafer.

Figure 1.9: Micro-channel design for the NA62 experiment.

Test devices have been fabricated in the CMi (Center of Micronanotechnology) EPFL (École Polytechnique Fédérale de Lausanne) class 100 cleanroom [22]. After thermal, mechanical and structural tests conducted at CERN on test devices fabricated in silicon and Pyrex, the design is validated. The micro-cooling devices installed in the experiment since 2014 are full silicon devices fabricated by the Leti 3S [23] at CEA-Leti in Grenoble [24].

#### 1.4.2 Proposal for ALICE ITS Upgrade

During the long LHC shutdown scheduled in 2018, also the ITS detector of the ALICE experiment is planned to be upgraded [25]. The existing detector will be replaced by seven new layers of pixel

detectors. The ITS detector is responsible of the high precision tracking and momentum identification of the incoming particles. For this reason the material minimization is quite crucial in this case. The new pixel detectors are expected to dissipate between 0.1 and 0.3 W/cm<sup>2</sup>. The maximum allowed temperature on the detector surface is 30°C and the minimum is 15°C, to avoid condensation on the electronics surface. The allowed maximum temperature difference over the chip area is 5°C.

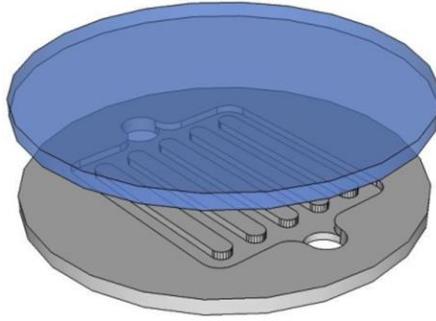

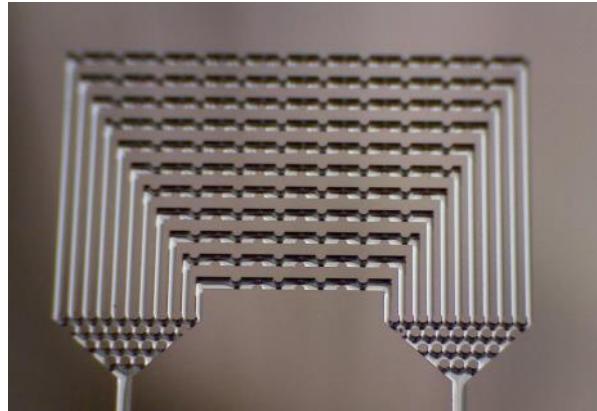

Micro-channels cooling is studied as backup cooling option for the ITS upgrade. In order to minimize the material of the cooling system a frame design is investigated: the micro-channels are present only at the edges of the chip to avoid additional material in the central part. In *Figure 1.10* it is possible to see a picture of a first prototype of a silicon frame with the Pyrex cover wafer.

*Figure 1.10: Micro-channel frame design for the ALICE ITS upgrade (Ref. [20]).*

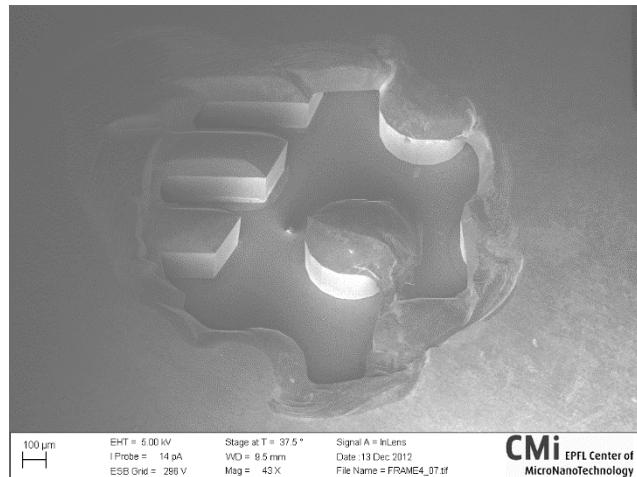

While for NA62 a liquid flow is used, since the heat transfer coefficient of C<sub>6</sub>F<sub>14</sub> in single phase is fulfilling the detector requirements, for the ALICE ITS studies currently on-going at CERN, an evaporative flow has been chosen. The fluid is entering the micro-channel device in sub-cooled liquid state. At the inlet of the circuit the channels present a much narrower cross section than in the entire circuit. The length of these narrow capillary parts is dimensioned to induce the desired pressure drop and to bring the fluid in the saturation conditions at the end of the capillaries. The sudden increase of the channels width favours the onset of boiling by flash evaporation. In the specific case of ALICE ITS, due to the reduced pressure budget provided by the C<sub>4</sub>F<sub>10</sub> saturation properties at room temperature, a large distribution manifolds acts as a plenum and, in order to stabilize the flow when it enters in the micro-channels and to avoid back flow, short inlet restrictions are foreseen. In *Figure 11* the inlet restrictions for the ALICE ITS micro-channel device are shown.

*Figure 1.11: SEM image of the ALICE inlet restrictions.*

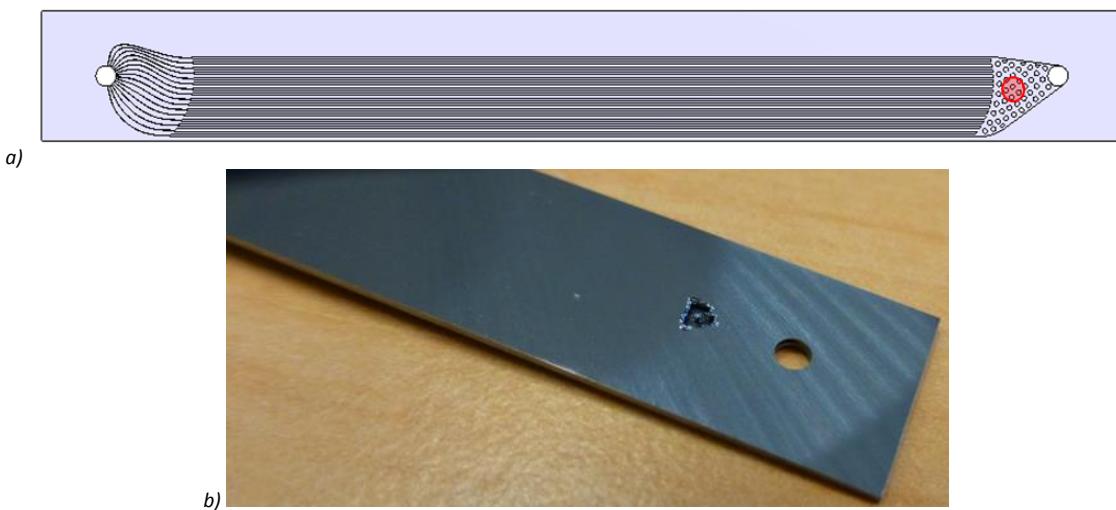

The ITS detector staves are 270 mm long, making it impossible to have a single micro-channel cooling device that covers the entire area. Standard wafer sizes are too small to cover in a single piece this length. For this reason it is foreseen to use several micro-channels devices in chain one after the other.

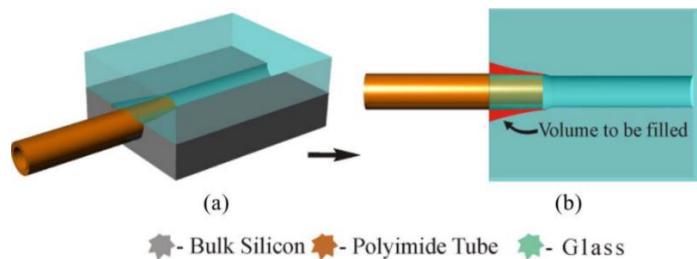

It is so necessary to study a fluidic interconnection between one wafer and the other. The ITS geometry requires minimal mechanical structure and out-of-plane solutions should be avoided. The first tested prototype was a “bridge” connection where a small piece of silicon with a small microchannel is connecting one frame to the following one [26]. Further studies are on-going to find the best solution.

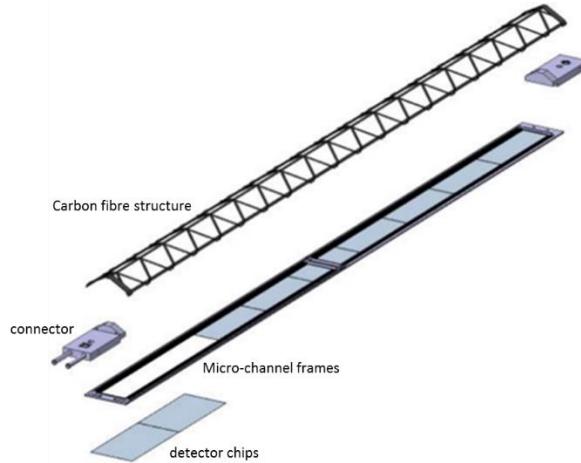

### 1.4.3 LHCb VELO Upgrade

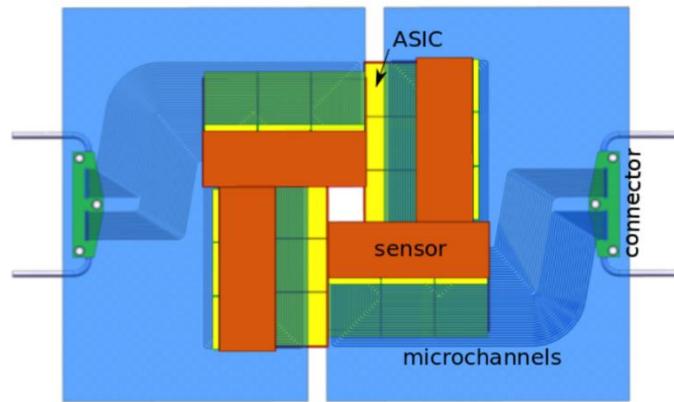

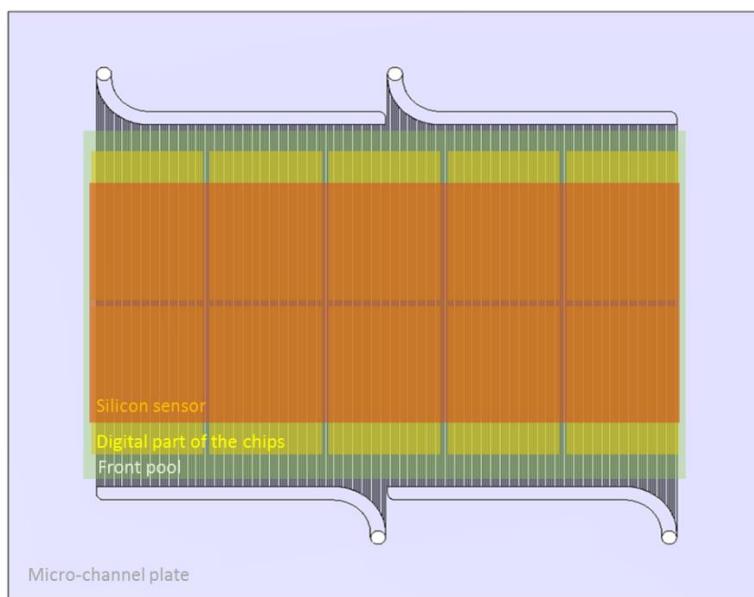

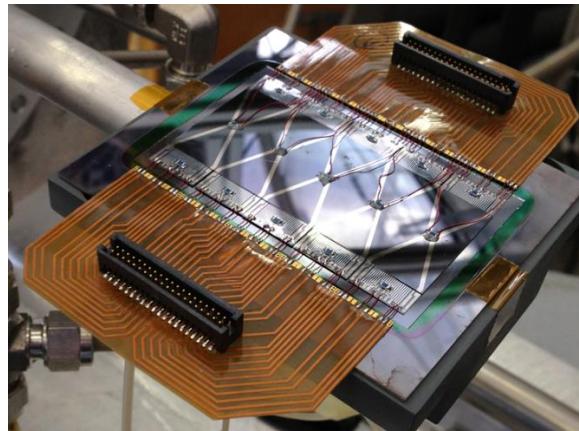

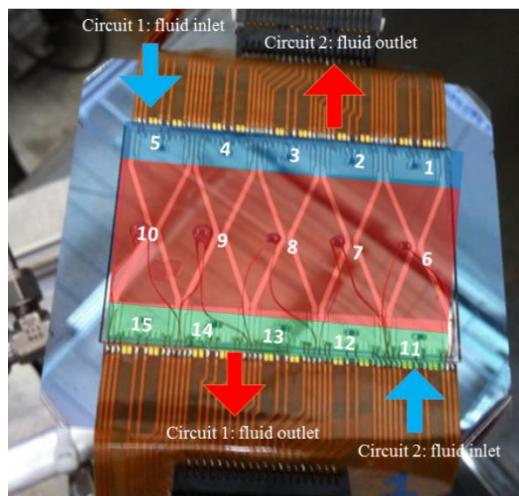

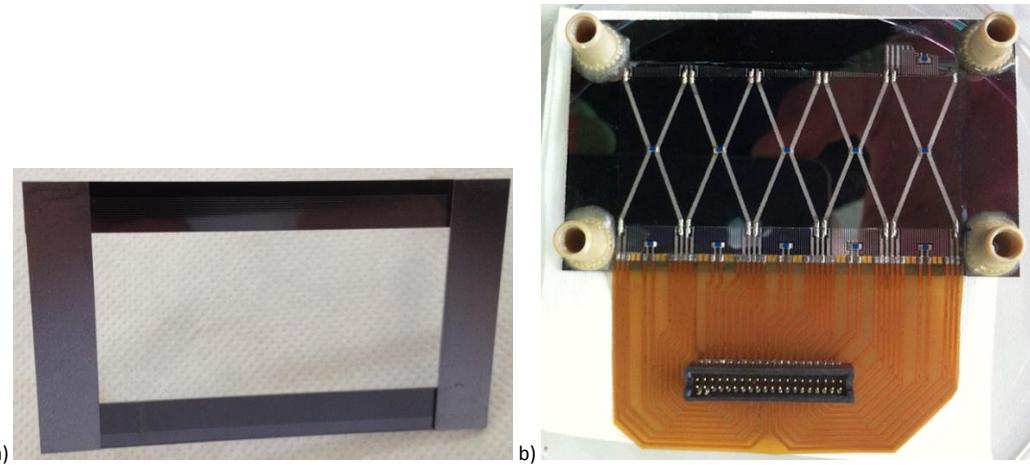

The VELO tracker is the closest LHCb detector to the interaction point, it was a pioneer in the use of the evaporative CO<sub>2</sub> cooling since its first installation in 2007 [27]. The VELO experiment will be upgraded in 2018 to run at higher luminosities and with higher speeds. The upgraded detector will work also in higher radiation environment and it will see the silicon strip technology substituted by silicon pixels. This, bringing much higher power distributed on the whole sensor surface, requires innovative thermal management techniques to keep the silicon sensor temperature below -20°C. In 2013 silicon micro-channels cooling was selected as the basic solution for the upgrade. The new VELO detector will be composed of 26 stations of two silicon micro-channel modules facing each other around the beam. The layout of one station is available in *Figure 1.12*. On each micro-channel module two sensor and chip assemblies, will be glued, one on the front side and one on the back side. A silicon pixel sensor (orange in *Figure 1.12*) will be bump-bonded to three ASICs (Application Specific Integrated Circuit) chips (yellow in *Figure 1.12*). The expected power densities are around 1.5 W/cm<sup>2</sup> that means about 36 W per module.

*Figure 1.12: Micro-channel cooling station or the LHCb VELO upgrade (Ref. [28]).*

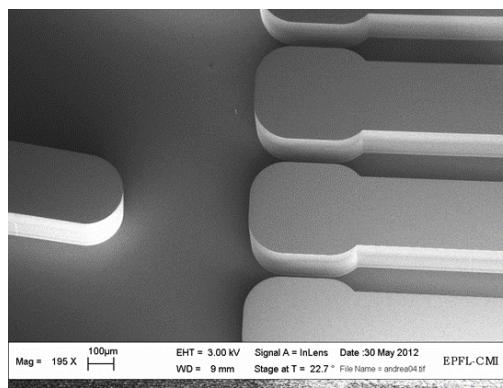

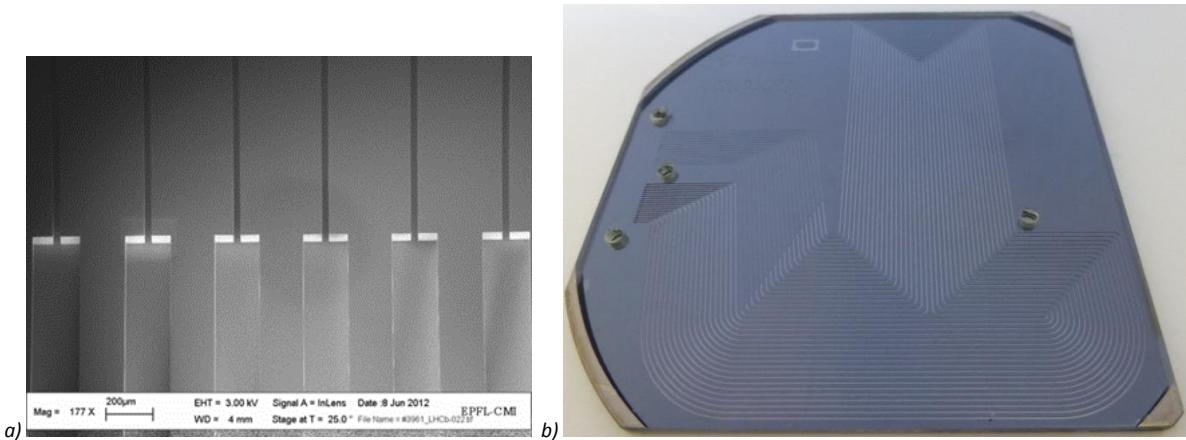

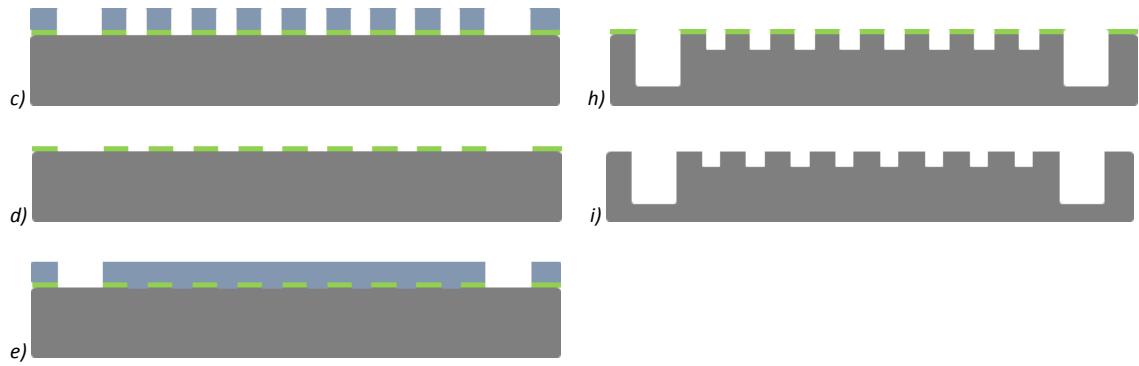

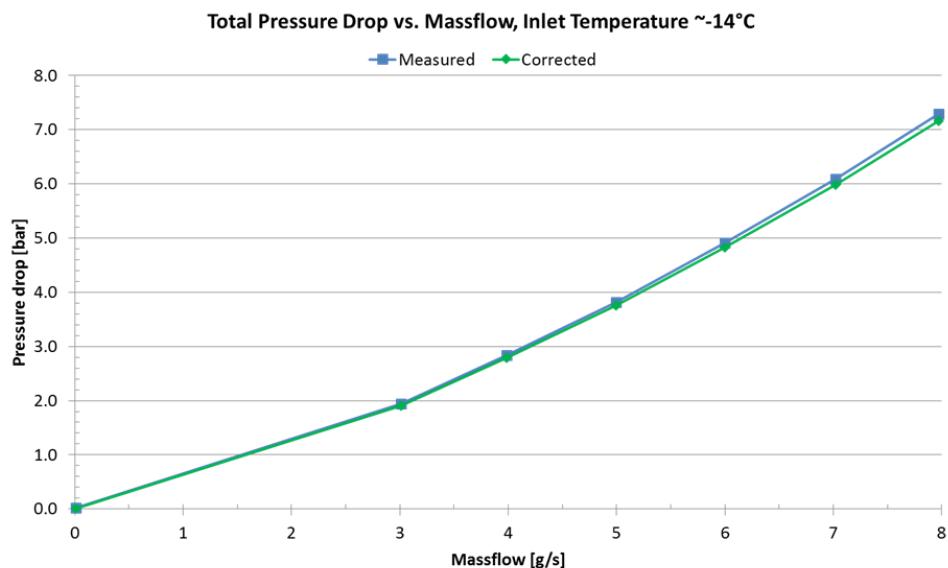

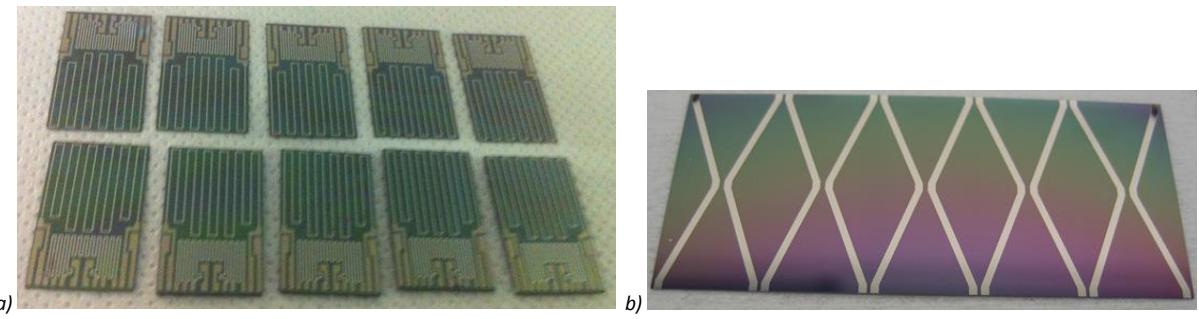

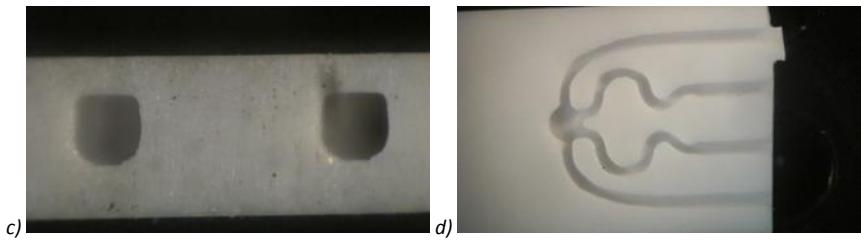

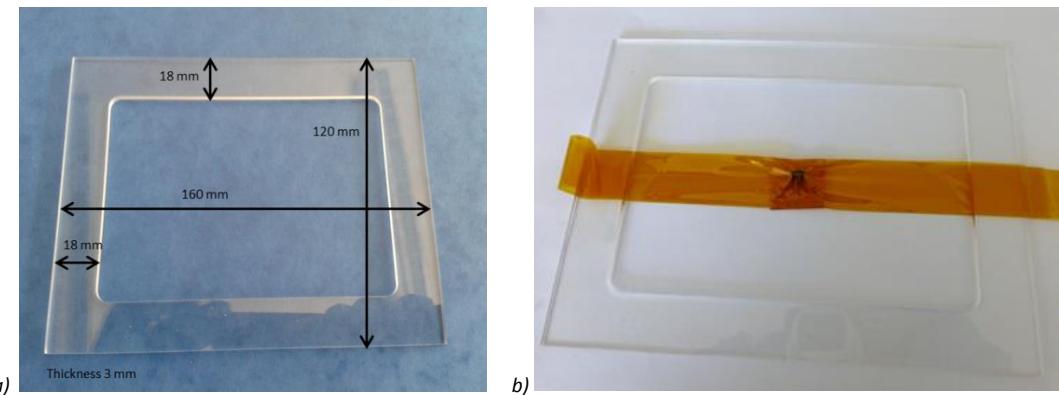

The micro-channel design will consist of a 400 μm thick silicon device with 19 parallel micro-channels, 200 μm wide and 120 μm deep, separated by walls of 500 μm. Each channel has a fluidic inlet and a fluidic outlet and the fluid distribution occurs inside a specific connector soldered on the silicon surface. Taking advantage from the high pressure of CO<sub>2</sub> flow, subcooled liquid is distributed in each micro-channel from the fluidic connector. The liquid enters a long capillary (60 μm wide and 60 μm deep), where it is brought in saturation conditions at the entrance of the micro-channels. A SEM image of the change of size between capillaries and micro-channels is shown in *Figure 1.13 a*. The final dimension of a micro-channel module will be 80x104 mm, fabricated starting from a 6 inches wafer. In order to validate the design with thermal and mechanical tests, a smaller prototype was built inside the CMI EPFL cleanroom with a silicon 4 inches wafer bonded to a Pyrex 2 mm thick wafer. A picture of the fabricated test device can be seen in *Figure 1.13 b*.

Figure 1.13: SEM picture of restrictions (a) and micro-channel test prototype for the VELO cooling (b).

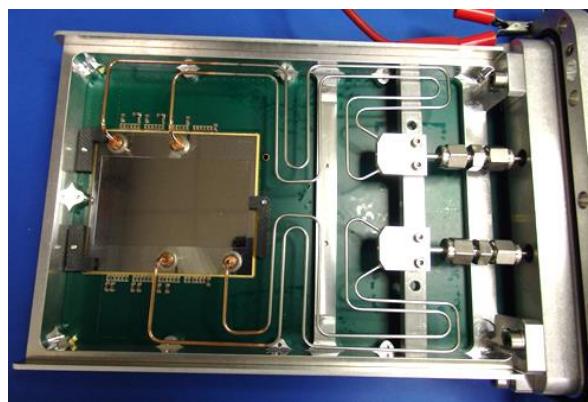

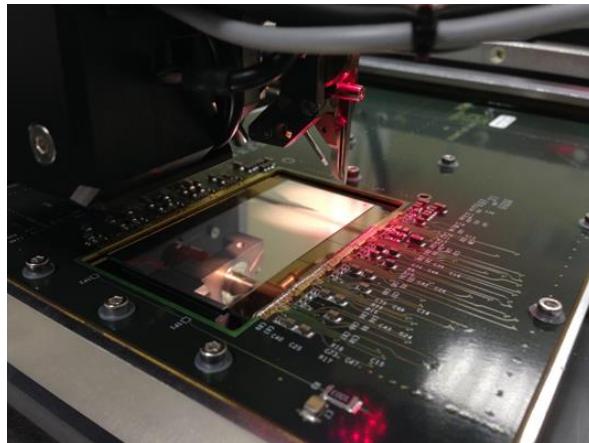

#### 1.4.4 Studies on ATLAS FEI4 cooling

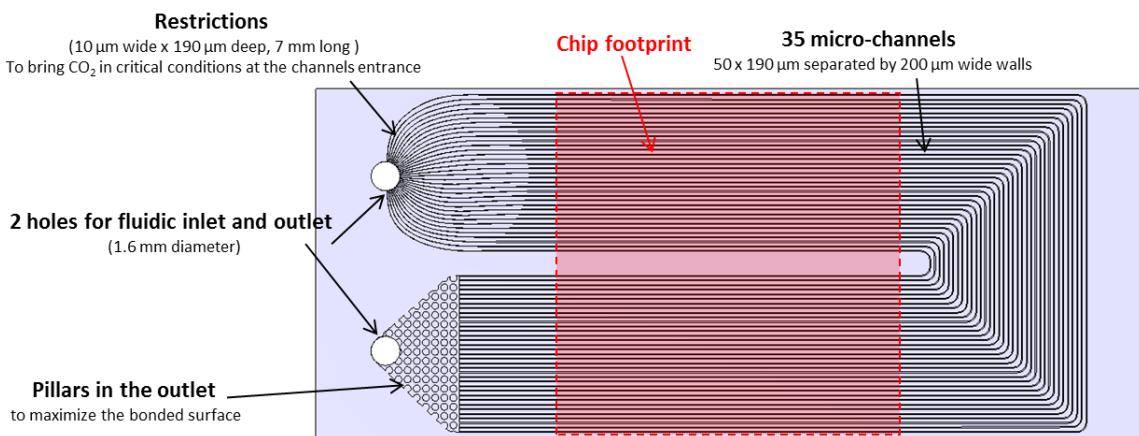

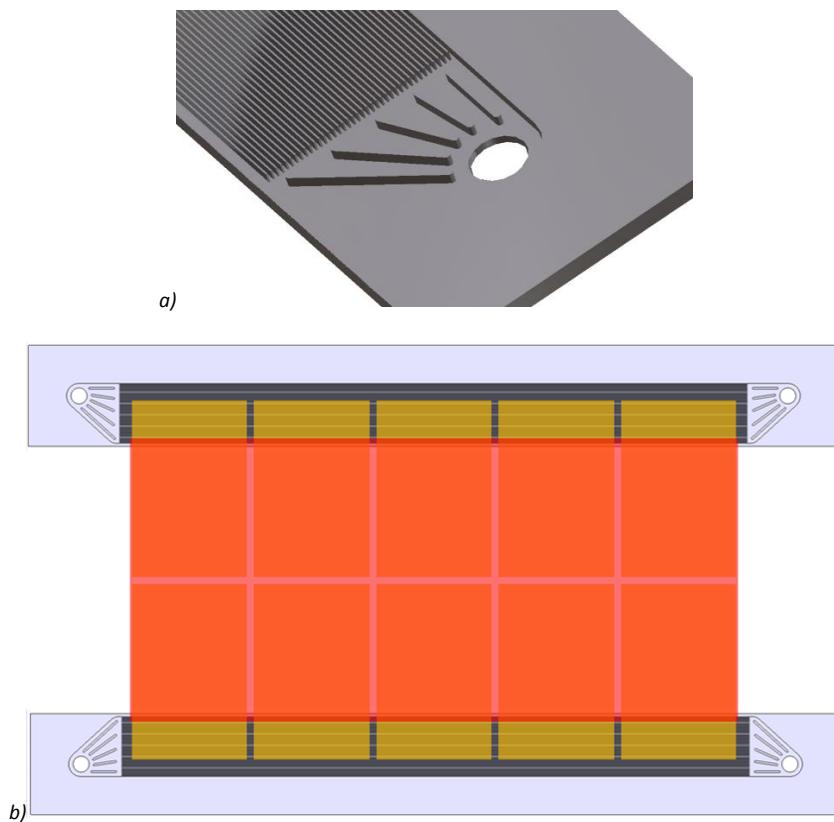

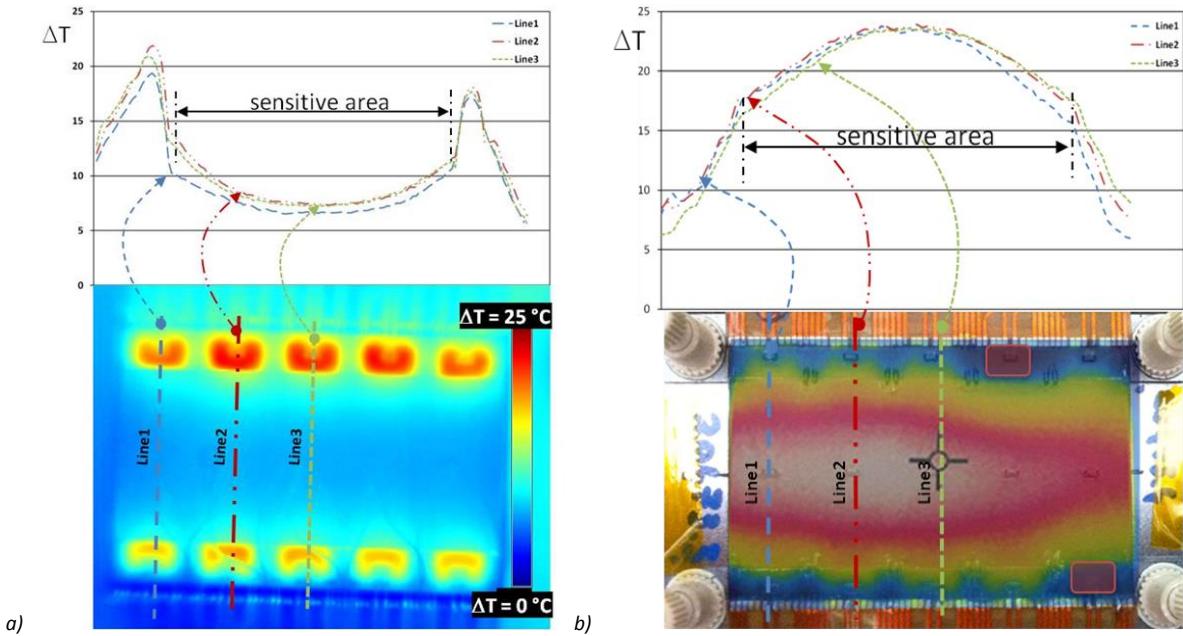

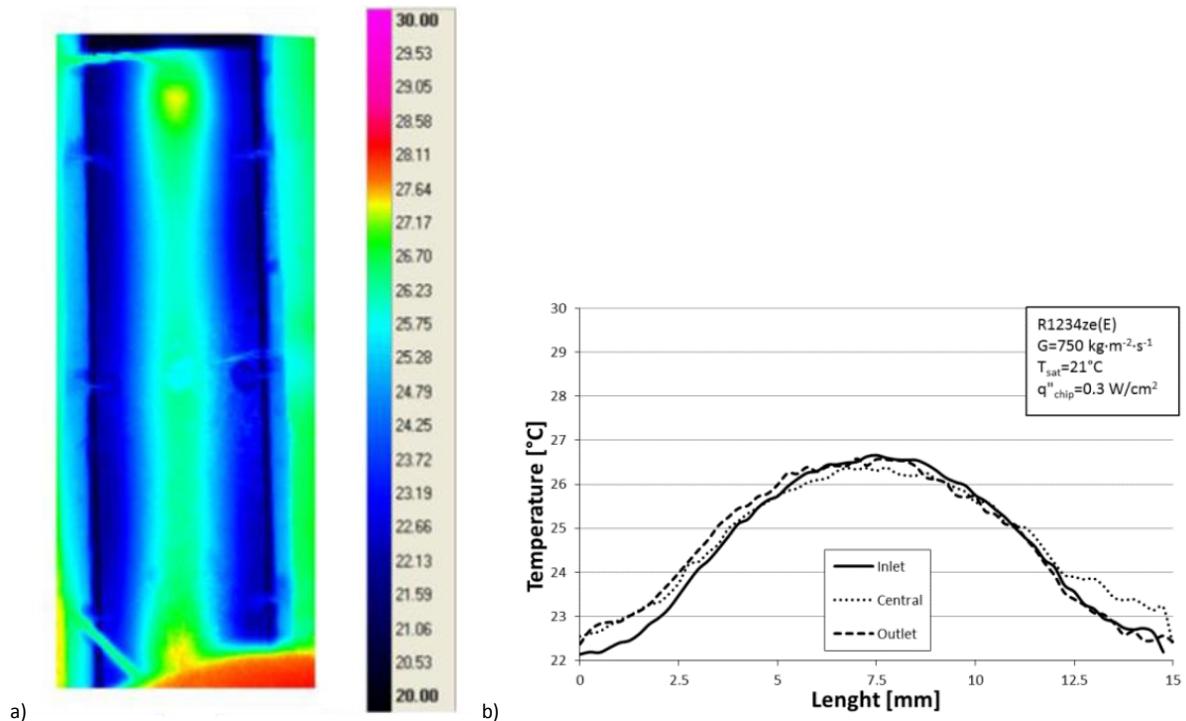

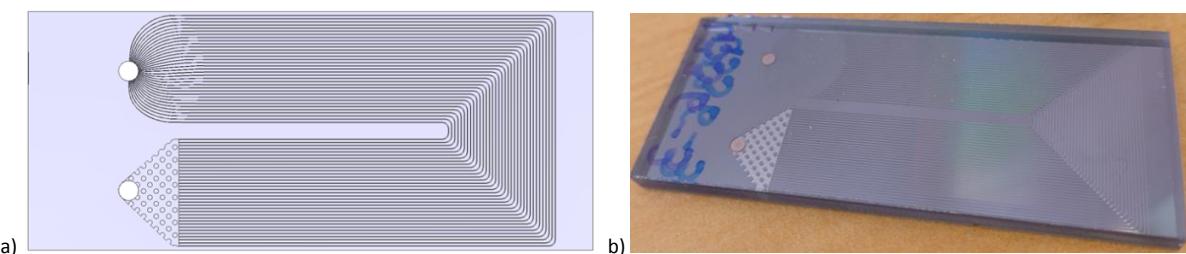

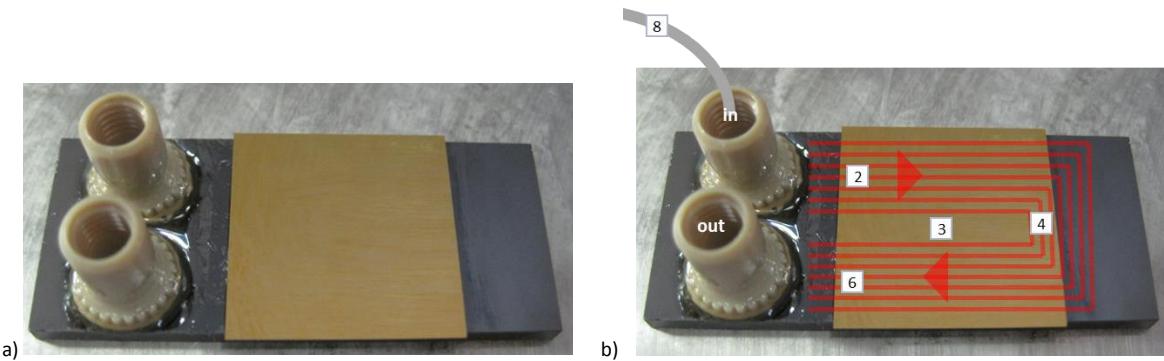

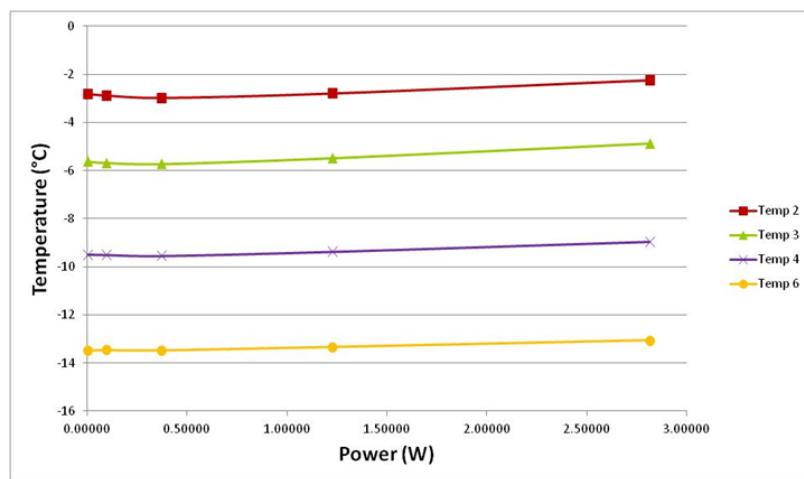

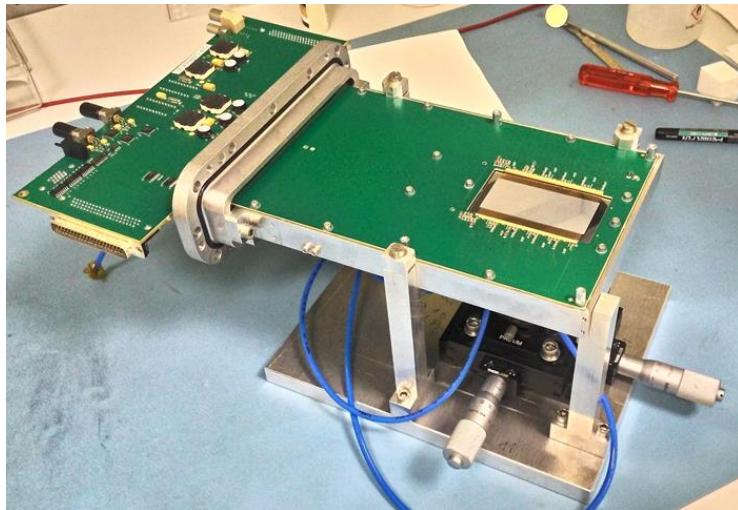

Preliminary studies are also done with micro-channel cooling for the cooling of an FEI4 chip of the ATLAS IBL experiment. The chip is 20x20 mm and it is supposed to dissipate a power density of 0.376 W/cm<sup>2</sup>, so a total power in the chip of 1.5 W. The requirement is to keep the detector surface at -15°C to minimize radiation damages on the chip structure. The proposed micro-channel solution is to use a silicon micro-channel device circulating CO<sub>2</sub> in evaporative flow. The first prototype of micro-channels device is 760 μm thick with a total area of 20x40 mm. The design is based on the LHCb solution, with 35 parallel micro-channels 50 μm wide and 190 μm deep. From the inlet hole, the fluid is distributed into the 10 μm wide capillaries, and then is evaporating in the channels under the chip area. The outlet manifold is collecting the fluid from the channels and it is filled with structural pillars to avoid a mechanical failure of the region due to high internal pressure. In *Figure 1.14* is possible to see a design of the micro-channels with the FEI4 footprint.

Figure 1.14: Micro-channel design for the ATLAS FEI4 chip cooling.

## 2 MICRO-FABRICATION OF SILICON MICRO-CHANNEL COOLING SYSTEMS

### 2.1 WHY SILICON?

As discussed in the first chapter micro-channel cooling is gaining lot of attention for the detector cooling of silicon trackers. The high thermal efficiency of micro-channels is strongly pushing in this direction. Furthermore, compared to the standard cooling approaches, the micro-channels give the possibility to spread the local heat sink in a planar array of channels uniformly distributed under the sensor area, in direct contact with the heat source. Different micro-channel cooling techniques are being studied in the last years for the cooling of particle detectors.

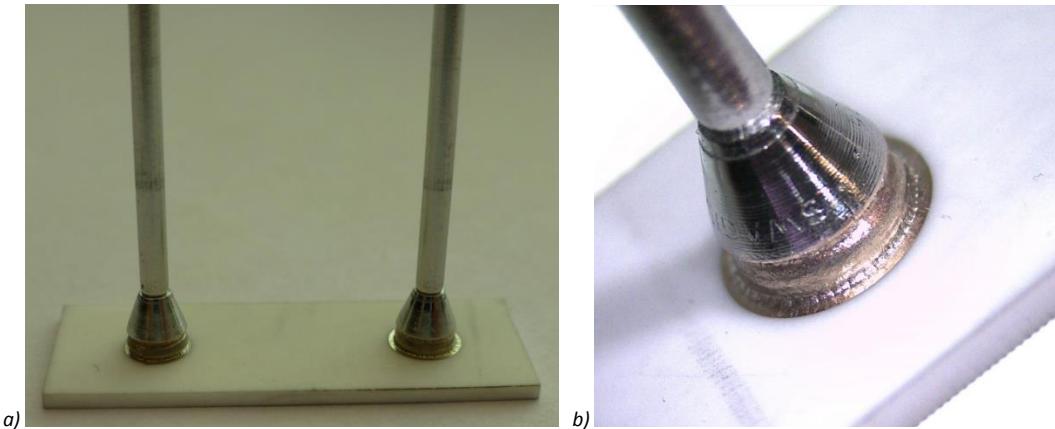

One of the alternatives that are being explored for the cooling of the ALICE ITS upgrade is a polyimide micro-channels cooling system [29]. The polyimide micro-channel structure is a system of parallel micro-channels with rectangular cross-section manufactured by deposition of epoxy walls on a polyimide substrate, then glued to the silicon detector (*Figure 2.1*). The heat flux generated by the electronics is transferred firstly to the polyimide substrate and then is dissipated by the cooling fluid flowing inside. Two studies were conducted using single-phase demineralized water and single phase  $C_6F_{14}$  fluid. Indeed the thin polyimide covers have a very poor structural properties and they cannot stand internal pressure in the channels: the system is only suited for liquid circulation in sub-atmospheric pressure. The foreseen channels were 16 per stave with a cross section of  $200 \times 800 \mu m$ . Successful thermal tests were conducted using a kapton heater with a heat power production between 0.1 and  $0.5 \text{ W/cm}^2$  as foreseen for the ALICE ITS detector [30].

Figure 2.1: Sketch of the polyimide cooling system (Ref. [29]).

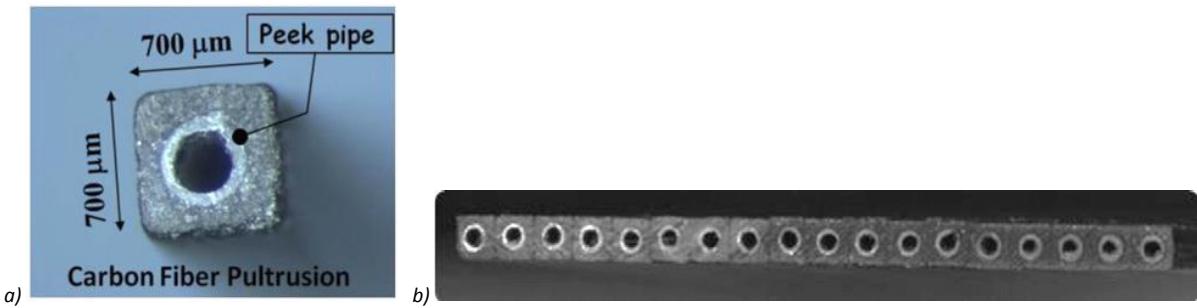

Another relevant work about micro-channel technology is the study by F. Bosi and others [31], for the cooling of the SuperB Layer0 Vertex Detector. The proposed solution is an array of PEEK capillaries with  $50 \mu m$  thick walls, encapsulated in a protruded carbon fiber. A single unit is a  $700 \times 700 \mu m$  square cross-section micro-tube with at the centre the PEEK pipe and the carbon fiber all around (*Figure 2.2 a*). The single units are glued together with epoxy glue Araldite 2011 (*Figure 2.2 b*). The micro-channels are 130mm long as the total length of the detector. The prototype was tested using as coolant a mixture of water and ethylene glycol.

Figure 2.2: Single unit cross section (a) and full module support cross section (b) (Ref. [31]).

All these methods of micro-channel cooling benefits from the heat spread aspect and from the short thermal path between the heat sink and the heat source. Unfortunately for both polyimide and carbon fiber, the CTE values are not matching with the one of silicon, and possible stresses due to thermal gradient can occur on the detector modules.

W. E. Cooper in his work [32], lists the most used materials in tracker detectors structures. He is dividing the materials into three groups according to their CTE values or their FOM (Figure Of Merit). One of the most fundamental parameters in thermal exchange, is the thermal impedance, defined as the ratio of the temperature gradient to the heat transferred. The FOM is the inverse of the thermal impedance. According to Cooper's classification, inside the group of the standard material for silicon structures (together with carbon-carbon composites, glass epoxy composites, aluminium nitride, ...), also silicon is present. The thermal conductivity of silicon is good compared to the other materials, and moreover the CTE is the same of the one of the sensor module. The possible use of silicon as a structural element should be taken in account.

Following this idea, the BELLE II detector upgrade is designed using the silicon material of the sensor as structural material [33]. The BELLE II detector is built using DEPFET (Depleted-Field Effect Transistor) modules. The DEPFET technology allows to realize very thin sensors, even to thicknesses down to 50 μm. In this concept the read-out electronics is located outside the sensitive area, which contributes to the minimization of the material to be crossed by the particles. The sensor itself produce very little power in such a way that gas injection cooling is sufficient to dissipate the heat there generated. The detector module is so fabricated starting from the same substrate with a localised thinning in the central part with the sensor and with an outer thick frame for the electronics. The thicker part is in contact with a cooling block in non-magnetic metal material cooled down with evaporative CO<sub>2</sub> flow at around -30 °C.

The method proposed in the PH-DT group of using silicon micro-channels for the cooling of particle detector, seems to gather all the advantages of the previous technologies reported. The micro-channels guarantee the spread cooling system below the sensor area and the small thermal path between the heat sink and the heat source. Furthermore the silicon itself is used as a structural material and so the CTE mismatch is not affecting the structure.

Another fundamental reason to choose silicon as the material of the micro-channels, is related to the fabrication method. In the last years MEMS (MicroElectroMechanical Systems) fabrication techniques for silicon electronic devices were largely developed: standard and well controlled processes can be used to fabricate micro-channels devices in silicon.

Based on the projects currently under study at CERN for the cooling of tracker detectors, also the DEPFET collaboration is investigating the possibility to use silicon micro-channel cooling for the new ILC (International Linear Collider) detectors [34]. Contrary to the Belle II detector, where the support

and cooling structure can be placed outside the sensitive area, for the future ILC detector the detector material has to be kept at minimum in the whole volume. Very preliminary studies are carried out on the possibility of inserting the micro-channels in the thick frame of the DEPFET detector and to circulate a forced gas flow. In *Figure 2.3* is possible to see a tentative layout of the micro-channel cooling part in the thick frame of the detector.

*Figure 2.3: Tentative micro-channel circuit design for the gas cooling of the DEPFET new ILC detectors (Ref. [34]).*

## 2.2 MICRO-CHANNELS FABRICATION

As previously anticipated, among the benefits of choosing a silicon micro-channel cooling system, there is the controlled and highly reproducible fabrication done using the standard and well known MEMS processes inside cleanrooms.

For the studied micro-cooling projects at CERN, after the channels dimensioning, the micro-channel designs for the different experiments have been prototyped and tested before the design validation. The test devices production takes place in the class 100 cleanroom of the CMi (Center of Micronanotechnology) at EPFL (École Polytechnique Fédérale de Lausanne) [22], while the thermodynamic tests are done at CERN inside the PH-DT laboratory. In a second time, the micro-channel devices for the final application in the experiments, are purchased from high qualified micro-technology companies that develop a series production of the devices.

Thanks to a collaboration between the PH-DT group at CERN and the CMi centre in Lausanne, it is possible for the PH-DT personnel, after a training period, to have access to the CMi cleanroom and to perform the micro-fabrication of the test devices. The CMi is a university cleanroom where typical micro-fabrication processes are taking place in a temperature and humidity controlled environment, principally on silicon wafers but also on other substrates. In order to avoid the contamination of the high sensitive processes done in the cleanroom, there is a driven laminar air flow inside the room, flowing from the ceiling to the floor, to evacuate possible pollution particles through the holes present in the floor. Furthermore the cleanroom users have to wear a cleanroom suit to minimize the pollution of the working environment.

The micro-fabrication of the test devices starts with the process flow definition in order to decide all the working steps with the correct parameters necessary to reach the targeted device. Often the micro-fabrication processes done in the CMi cleanroom for the test prototypes, and the processes done in the external companies for the final realisation of the micro-channel devices, present some differences due to the complexity of the processes.

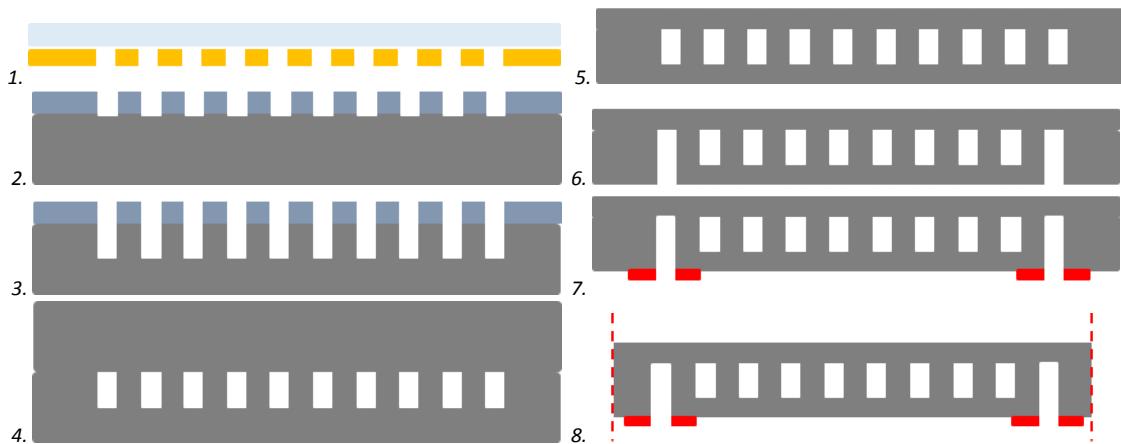

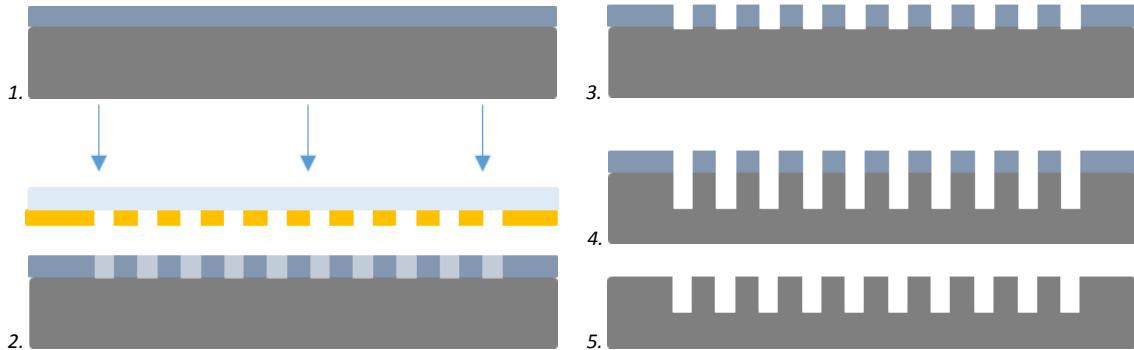

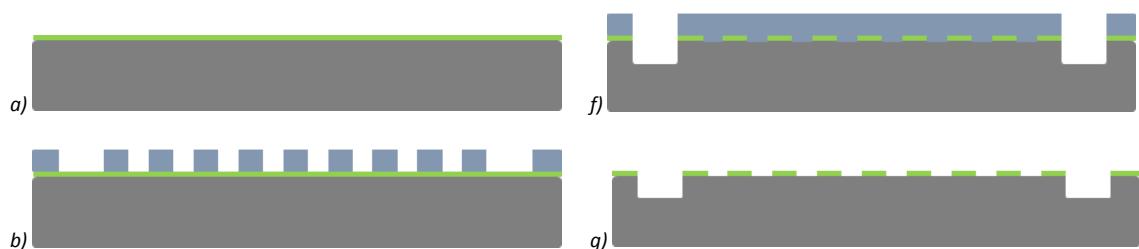

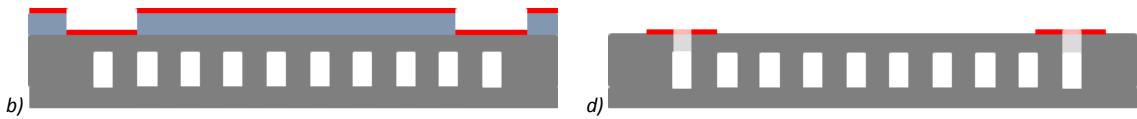

In Figure 2.4 is possible to see, in a simplified form, a complete standard process flow for a micro-cooling device fabrication. The process starts from a silicon wafer. The channel design is transferred on a chromium/glass photolithography mask (Figure 2.4 1). After a photolithography process (Figure 2.4 2), the micro-channel circuit is etched on the wafer surface with a DRIE (Deep Reactive Ion Etching) etching process (Figure 2.4 3). The wafer is well cleaned from all the impurities and the cover wafer is bonded on top of the etched one. The cover wafer can be a Pyrex wafer or another silicon wafer. The bonding process is an anodic bonding, if the cover wafer is Pyrex, otherwise it is a silicon-silicon direct bonding process (Figure 2.4 4). A wafer thinning, localized or applied to the whole wafer surface, is then performed on the wafer to minimize the amount of material to be crossed by the particles (Figure 2.4 5). The fluidic inlets and outlets are then etched in the cover wafer or in the bottom wafer (Figure 2.4 6). If required from the device application, a metal deposition is done at this point on the wafer surface for the soldering of the fluidic connectors or for temperature measurements (Figure 2.4 7). The last step of the process flow is to dice the wafer to have the single devices ready for testing (Figure 2.4 8).

Figure 2.4: Simplified process flow for the micro-channels fabrication in cleanrooms.

In the next section each single step of the process flow is analysed and explained from the point of view of the micro-channel device fabrication. The description is done showing the problems found during the fabrication and underlining the differences between the production in the CMi cleanroom and in the external companies.

### 2.2.1 Silicon

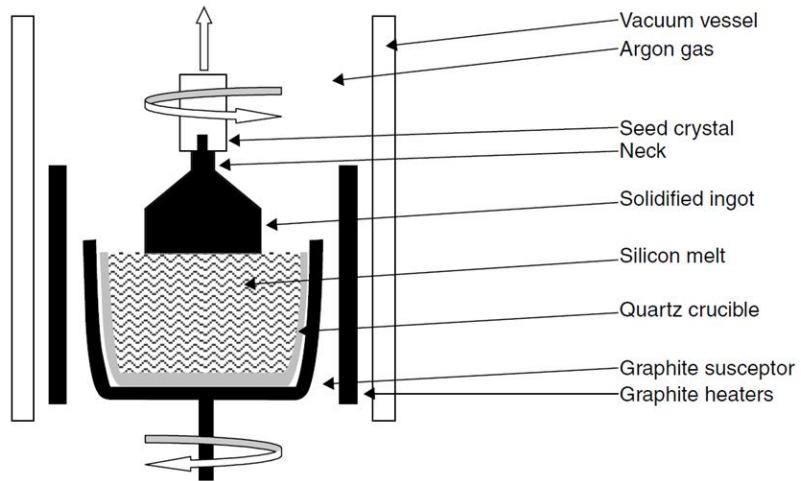

The first time that silicon was considered suitable for a microfabrication process was with the first silicon transistor in 1952 [35]. But it became even more interesting with the discovery of the good insulation properties of silicon dioxide. Silicon is processed in the micro-fabrication machines starting from circular thin substrates of monocrystalline silicon called *wafers*. The silicon-wafer manufacturing is a multistep process, usually based on the so called Czochralski process that starts with the sand purification and ends with the wafer inspection. The silica sand, with the correct amount of dopants, is heated up in a quartz crucible under vacuum, to 1420 °C to melt the silicon. A single-crystalline seed of known orientation is dipped in the bath. The seed is gently pulled outside the bath and the silicon solidify around the seed following its orientation. A small neck is created at the beginning of the ingot for the high temperature difference and then the resulting ingot increases diameter with the decreasing of the pulling rate. During the process the crucible and the ingot are rotated in different

directions (Figure 2.5). Since the silicon ingot is not mechanically strong enough at 1400°C, a graphite susceptor is providing the mechanical strength to the silicon.

Figure 2.5: Czochralski process to create wafers from a silica crucible (Ref [35]).

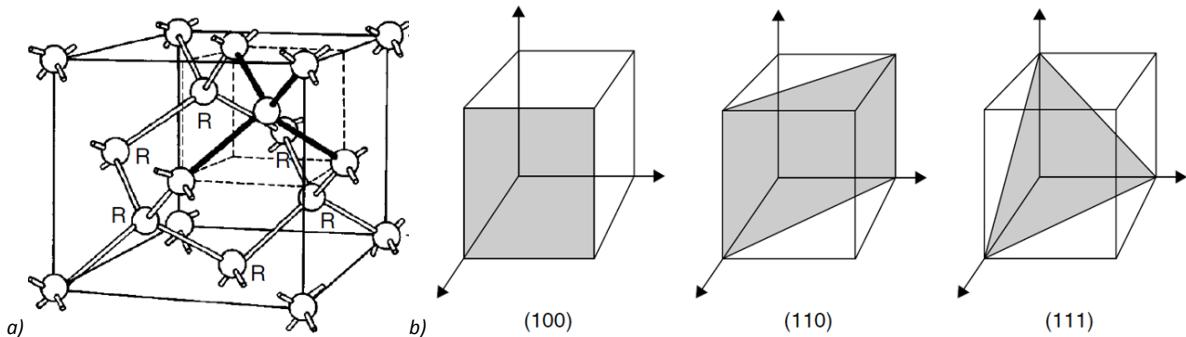

Silicon has a cubic diamond lattice structure (Figure 2.6 a). Miller indices define the planes of the crystal (Figure 2.6 b). The indices are the reciprocals of the intersections of the plane with the three axis, for example the front plane in Figure 2.6 b is the (1 0 0).

Figure 2.6: Silicon lattice structure (a) and important silicon planes with Miller indices (Ref [35]).

The silicon ingots are then transformed into silicon wafers through a long thermal, mechanical and chemical process. A flat part is cut from the cylindrical shape of the ingot to indicate the crystal plane orientation of the resulting wafers. At the end the wafer is sawed in slices. Each slice is thinned and polished with mechanical and chemical processes to the desired thickness and roughness. The silicon wafers can be of different sizes, from less than 100 mm of diameter to more than 300 mm. For the micro-fabrication inside the CMi the standard wafer size is 4 inches wafers while in the external companies that collaborated with PH-DT the fabrication is done typically on 6 or 8 inches wafers.

## 2.2.2 Patterning – Photolithography

Lithography is the technique to transfer copies of a master pattern on a solid surface like a silicon wafers. Photolithography is the lithography done using the UV light to transfer the pattern from a mask onto the wafer surface.

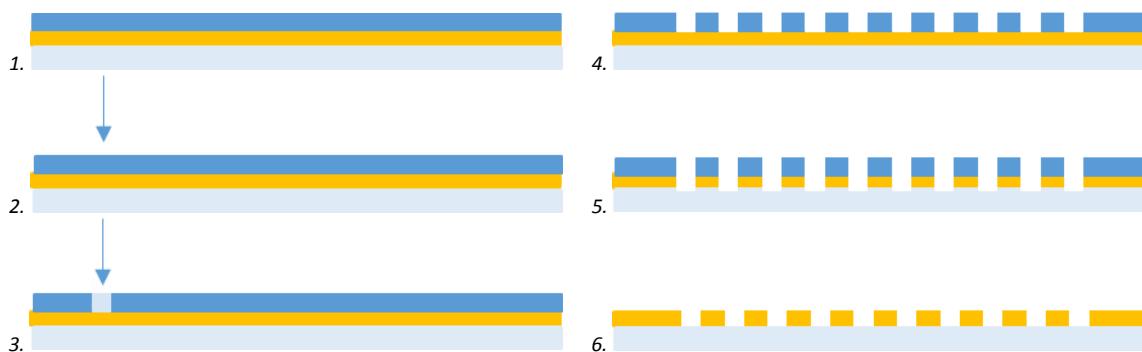

The first step is to realize the photolithography mask used as the master to reproduce the design on all the wafers. The most commonly used photolithography masks are made of chromium coated glass. The masks are prepared and the chromium is etched in order to obtain the desired pattern design. The scheme of the photolithography mask production done inside the CMi cleanroom is shown in *Figure 2.7*. The glass mask (light blue in *Figure 2.7 1*) is chromium coated on one side (orange in *Figure 2.7 1*) and a resist layer is deposited on top of the chromium (dark blue in *Figure 2.7 1*). The resist is exposed to a laser beam that scans the whole mask surface and illuminates the parts that have to be etched (*Figure 2.7 2*). The third step is to start developing the resist where it has been illuminated by the laser (*Figure 2.7 3*), and after the complete development the result is like in *Figure 2.7 4*. The wafer is now dipped in an etching bath to remove the chromium parts to be etched (*Figure 2.7 5*). Finally the resist on the mask is removed and the photolithography mask is ready to be used (*Figure 2.7 6*).

*Figure 2.7: Mask fabrication process flow.*

The photolithography process to transfer the channels design on the wafer surface is very similar to the one used to fabricate the mask. The wafer is coated with a photoresist and then the resist is exposed to UV light using the photomask just fabricated. In *Figure 2.8* all the steps of the process are shown. The standard resists used in micro-fabrication are organic polymers sensitive to UV light. One of the most common processes to deposit the resist on the wafer surface, is by spin-coating. The liquid resist is deposited in the centre of the wafer and after a while the wafer is accelerated to high rotational speed to let the resist spread on the wafer surface (*Figure 2.8 1*). The amount of resist to deposit is a critical parameter for the good outcome of the process. Too less resist may leave uncovered areas, while too much resist results in ridges, wrinkles and defects on the wafer surface. The resist is sensitive to UV light and so the next step is to illuminate the wafer surface through the photolithography mask to let the light passing where the chromium has been etched (*Figure 2.8 2*). The exposure time, the light energy and the others parameters are calculated on the base of the resist type and thickness. An important parameter to consider during the photolithography process is the thickness of the resist mask. The thickness is usually determined by the etching step following the photolithography. After the patterning of the resist deposited on the wafer, the portion of silicon non-protected by the mask is attacked by the etching agent selected. Nevertheless also the mask is etched during the process through with a slower etching rate. The ratio between the etching rates of the two materials, silicon and the resist, is called selectivity of the resist. The resist thickness is so calculated depending on the silicon depth to be etched and the selectivity of the resist.

The wafer is then dipped in a solvent bath where the resist is developed and the areas exposed to UV light are dissolved (*Figure 2.8 3*). Now the resist mask is ready to be used for the next step that can be for example the etching of the wafer surface (*Figure 2.8 4*). As last step of the photolithography process the resist mask is removed with a dry or wet process (*Figure 2.8 5*). The dry stripping of the

resist is done with an oxygen plasma beam while the wet process is done by dipping the wafer in a solvent bath that dissolves the unexposed resist.

Figure 2.8: Photolithography process.

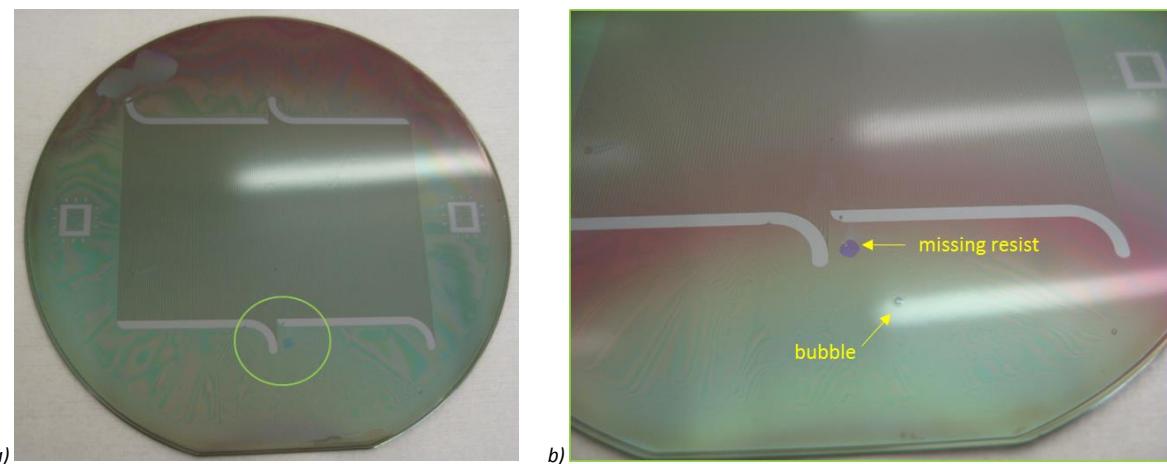

A picture of a wafer with the resist mask ready to be etched is shown in *Figure 2.9 a*. The channel design on the wafer is the one chosen for the NA62 project with two distribution manifolds at the inlet and two collection manifolds at the outlet. The mask in the picture is the one used to etch just the manifolds that have a different depth of the channels according to the circuit design.

Sometimes during the resist deposition and developing, a local defect can appear due to problems during the process. In *Figure 2.9 b* is possible to see a zoom of the green circle in *Figure 2.9 a*, where a defect is present on the resist mask. The defects can be due to a different air condition during deposition (temperature and humidity out of range in the cleanroom environment), or to internal defect of the resist. Another cause of defects in the resist mask can be the direct contact with the photomask during the UV exposition. In order to obtain the highest precision, the distance between the mask and the wafer is to be minimized up to the “direct contact” exposition. The contact can cause defects on the resist mask because, if the photomask is not perfectly cleaned, parts of resist can stick to the mask. In *Figure 2.9 b* is possible to see a small bubble in the resist, probably due to the presence of a contaminant particle, and also a missing part of resist on the wafer surface maybe due to the wafer and mask hard contact. In the resist hole is possible to see the wafer surface with the blue colour characteristic of the silicon oxide, below the resist.

Figure 2.9: Photoresist mask deposited on a NA62 wafer before the etching of the manifolds.

### 2.2.3 Etching the Channels

A lithography usually precedes an additive or a subtractive process. Materials are either added or removed from the wafer surface in a selective way following the pattern created with the lithography. In the silicon micro-channel fabrication, the next step in the process flow is to etch the channels on the wafer surface, which is a subtractive process. Usually the etching is done using the DRIE (Deep Reactive Ion Etching) process. DRIE etching is a dry etching technique, contrary to the wet etching where the wafer is dipped in an acid bath.

The dry etching is done in a vacuum chamber by a plasma hitting the wafer surface. The plasma etching is the result of an excited and ionized reactive gas that is mechanically and chemically attacking the wafer surface. The resulting profile of this etching process is an anisotropic etching with almost vertical sidewalls. Normally the etching process, as soon as the channels depth is growing, is affecting also the sidewalls by bouncing of the ions in the bottom of the channel.

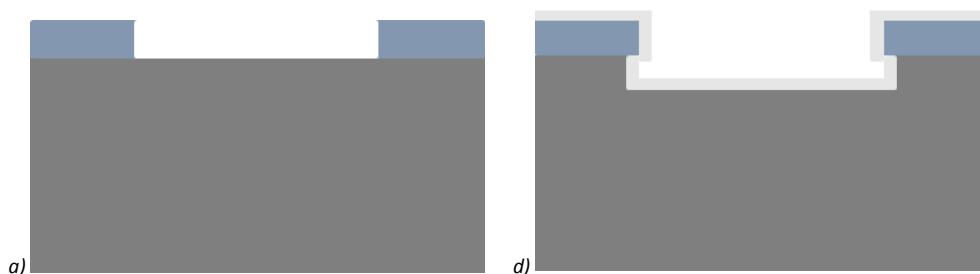

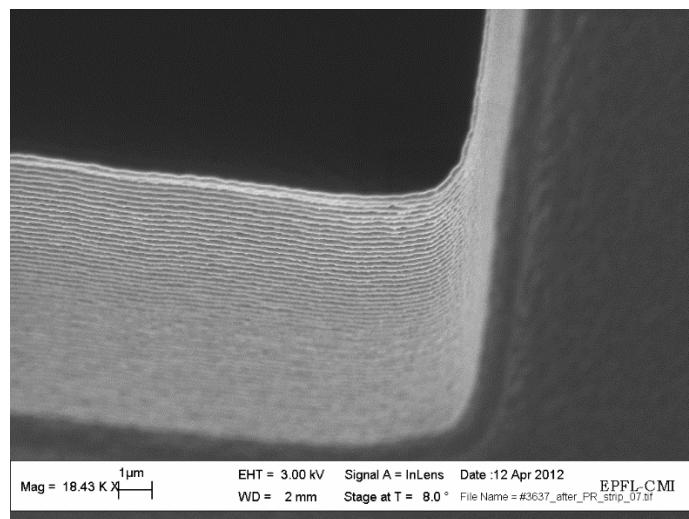

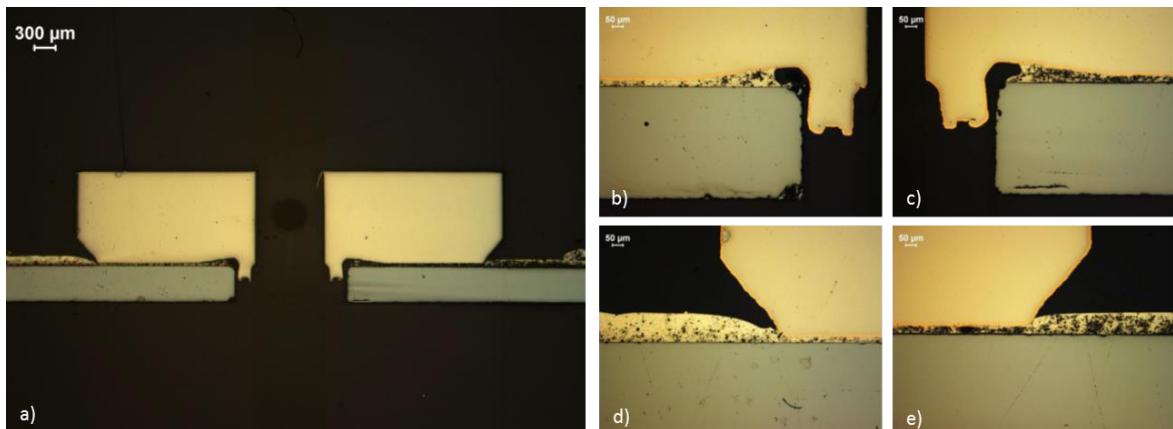

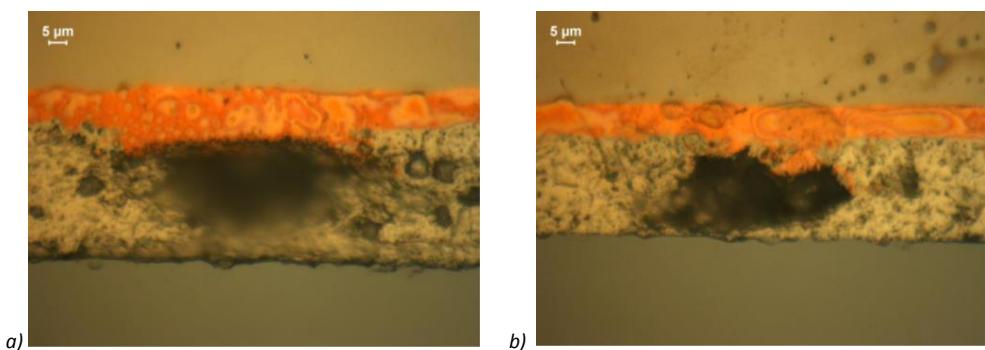

The DRIE etching process, named also Bosch process, guarantees vertical sidewalls thanks to two alternating phases, an etching phase and a passivation phase (*Figure 2.10*). Two gases are alternatively pulsed in the vacuum chamber (*Figure 2.10 a*). An etching gas is bombarding the wafer surface and it starts to increase the channel depth (*Figure 2.10 b*). After a while, the ion particles start attaching also the sidewalls inducing an under-etching effect (*Figure 2.10 c*). To stop this behaviour the second gas is pulsed in the chamber and a thin polymer layer is deposited on the wafer surface and inside the channel (*Figure 2.10 d*). During the following phase the polymer in the bottom of the channel is etched immediately from the plasma and the channel depth is increased, while the polymer on the sides is protecting the walls from the bounce of the ions and the lateral etching is minimized (*Figure 2.10 e*). As soon as also the lateral polymer starts to be etched, a second passivation phase takes place and the polymer layer is redeposited on the wafer surface. At the end of the etching process the wall surface finishing is the resulting of the succession of the two phases, and it presents an indented profile with a chain of small circular arcs (*Figure 2.10 f*). This profile is called “scalloping” and it is shown in detail in the SEM image in *Figure 2.11* where is possible to see a tilted top view of a channel design for the LHCb micro-channel device. Varying the parameters of the two phases and varying the mask design can lead to different etched profiles (*Figure 2.12*). Normally with the same etching time, the wider profiles are deeper while the thinner profiles are less deep, due to side effects.

Using this Bosch process not only pure silicon can be etched, but it is also possible to etch silicon oxide or silicon nitride layers used during the micro-fabrication flow as insulating layers or hard masks to etch silicon.

Figure 2.10: DRIE etching process steps.

Figure 2.11: DRIE etching process scalloping effect on the sidewalls of a channel.

Figure 2.12: DRIE etching profiles obtained in the CMi EPFL cleanroom (Ref [22]).

In order to obtain different etching depths on the same wafer, for example for the channels and for the distribution manifolds, two photolithography steps are necessary. Since the sputtering of the resist on a wafer with already etched structures is almost impossible due to the non-uniform surface, two masks have to be present on the wafer surface at the same time. The first mask will be a hard mask done with an oxide layer while the second one will be a standard resist mask. The mask are then used in reverse order of how they are deposited on the wafer surface.

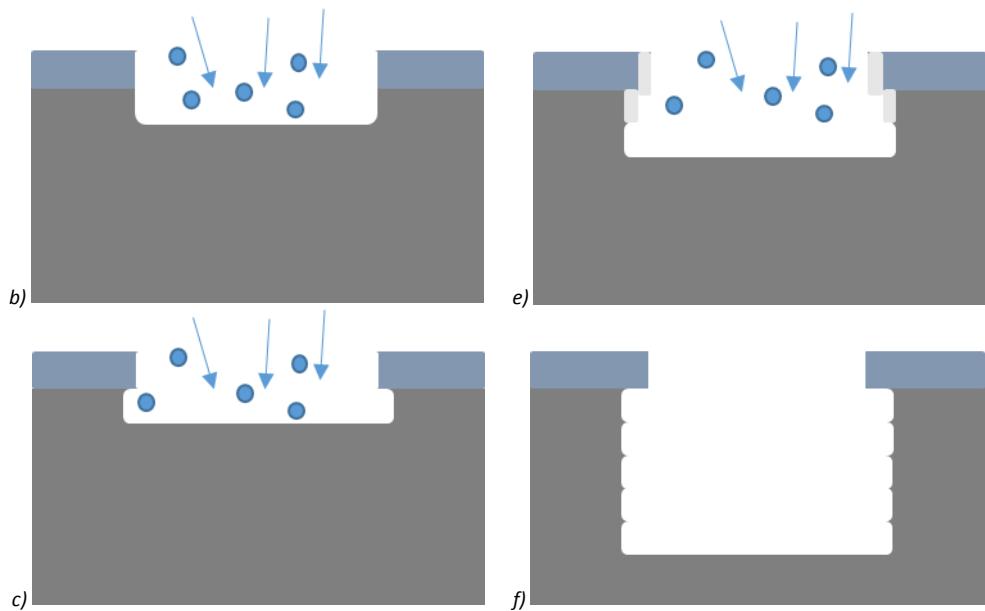

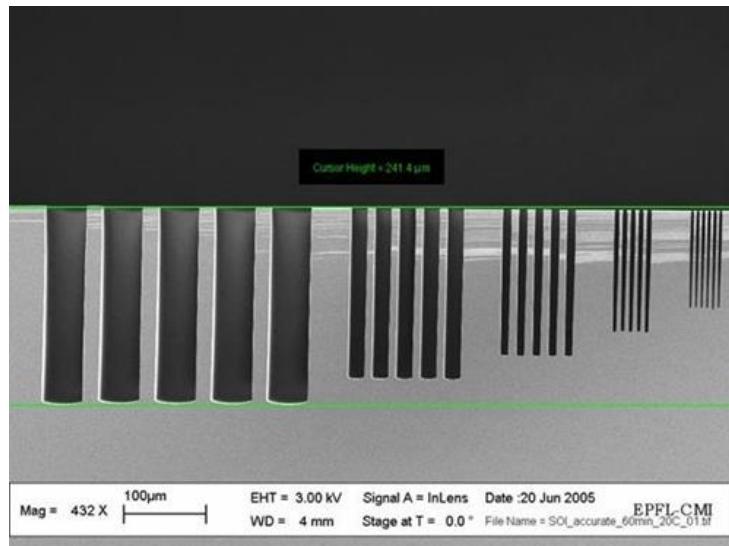

In Figure 2.13 it is possible to see a small process flow of how to realize different depths on the same wafer surface. A standard resist photolithography mask is created on the wafer surface, using as support an oxide layer previously grown on the silicon surface (Figure 2.13 a). In this first resist mask both depths (the channels and the manifolds designs) are present (Figure 2.13 b). The first etching step is to etch the oxide layer on the silicon wafer (Figure 2.13 c). The resist mask is removed and the hard oxide mask is patterned on the silicon surface and it is ready to be used (Figure 2.13 d). A second resist mask is then created this time only with the deeper structure that is going to be realized, like the distribution manifolds (Figure 2.13 e). The etching of the silicon wafer starts with the depth corresponding to the difference between the two depths to be realized (Figure 2.13 f). Once this depth is reached, the resist mask is removed from the wafer surface (Figure 2.13 g). The oxide mask is ready to be used to perform the second etching step with the total depth of the less deep between the two structures (Figure 2.13 h). Since the two structures are present on this mask the less deep one, will be etched of the targeted amount, while the deeper one will be etched as the sum of the two etching steps. At the end of the process is possible to remove the oxide mask with a selective plasma etching or with a wet etching inside an acid chemical bath (Figure 2.13 i).

Figure 2.13: Process flow to realize two different etching depths on the same wafer.

A two-depths etching process is used for the final micro-channel device installed in the NA62 experiment. The 280  $\mu\text{m}$  deep distribution and collection manifolds are etched in the bottom wafer (380  $\mu\text{m}$  thick wafer), while the cooling channels are only 70  $\mu\text{m}$  deep in the central area of the device. In *Figure 2.14* it is possible to see a picture of a NA62 test device processed in the EPFL cleanroom after the etching on the channels and the manifold before the bonding with the cover wafer.

Figure 2.14: NA62 test device realized in the EPFL cleanroom with two etching depths.

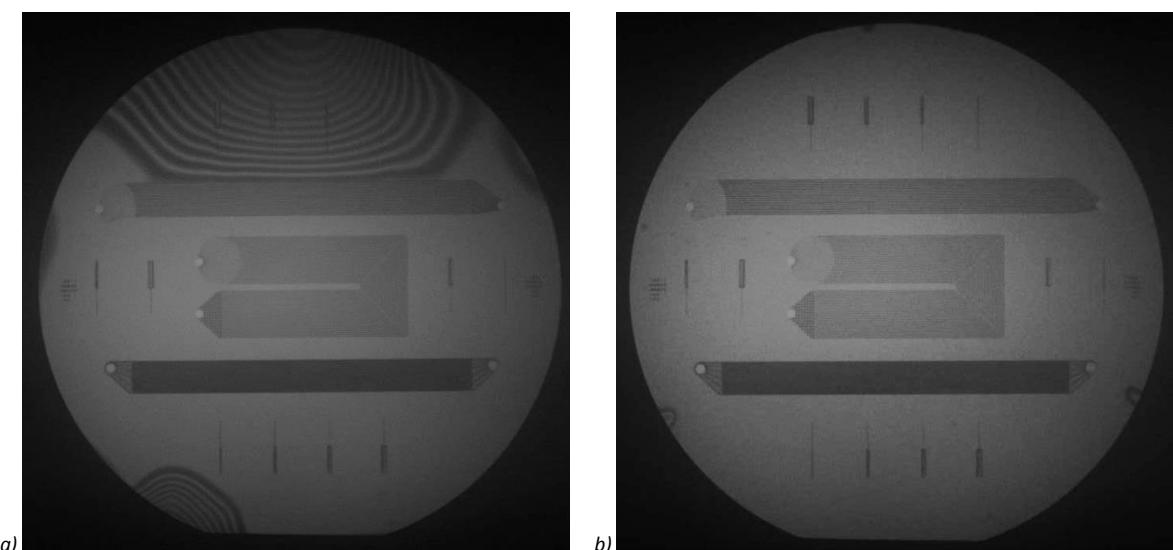

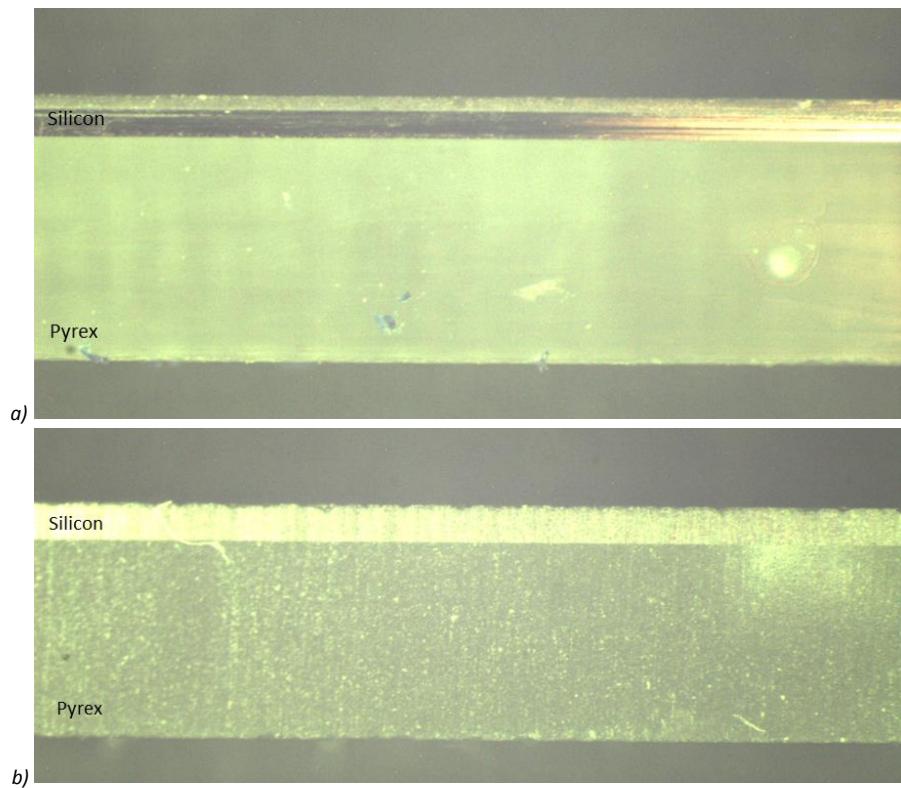

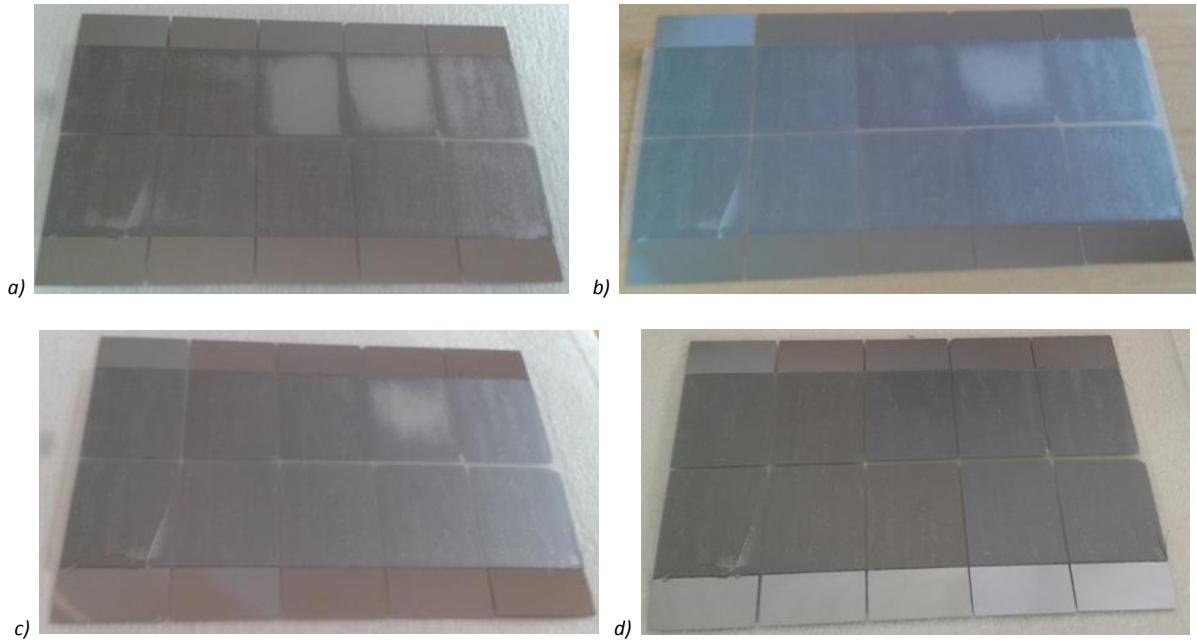

#### 2.2.4 Bonding of Cover Wafer

The next step in the micro-channel process flow is the bonding of the cover wafer. The cover wafer can be a Pyrex wafer or a silicon wafer. For the final installation in the detectors, a full silicon device (silicon cover wafer) is required for the CTE properties, for the transparency to particles and for the mechanical properties. Structural tests have been conducted evaluating the maximum pressure that can be sustained by a given amount of material on top of a micro-channel (see *Chapter 3*). Results show how a silicon membrane is holding much more pressure than a Pyrex one. For this reason, with the same fluid pressure, a full silicon device can be thinner than a silicon-Pyrex one, helping to minimize the material in the beam area. For testing purposes a Pyrex-silicon device is usually chosen because of the easier bonding technique and for the possibility offered of flow observation in the channels through the transparent wafer.

Both bonding processes (silicon on silicon and silicon on glass) belong to the “direct bonding” category [36]. A direct bonding is when two substrates are bonded together without using an intermediate adhesive layer. Contrary to the direct bonding, the indirect bonding involves the use of an intermediate layer that acts as adhesive agent. It can be made of different materials like metals, polymers or glass.

In theory two wafers of every materials can be bonded together at room temperature using the Van der Waals intermolecular forces. This type of bonding requires the wafer surfaces to be perfectly clean, flat and smooth but the bonding strength of the resulting bond is not very high. In order to obtain a stronger bond, the two wafer surfaces are placed in contact and then a driving force is acting to perform the bonding between the two. The driving force in bonding can be temperature, an electric field or a combination of the two. The silicon-Pyrex bonding process takes the name of *anodic bonding* while the silicon-silicon bonding is called *fusion or silicon direct bonding*.

The standard phases to obtain a direct bonding process start with the surface cleaning and wafer preparation, followed by the joining of the two surfaces at room temperature. At this point the bonding driving force is applied.

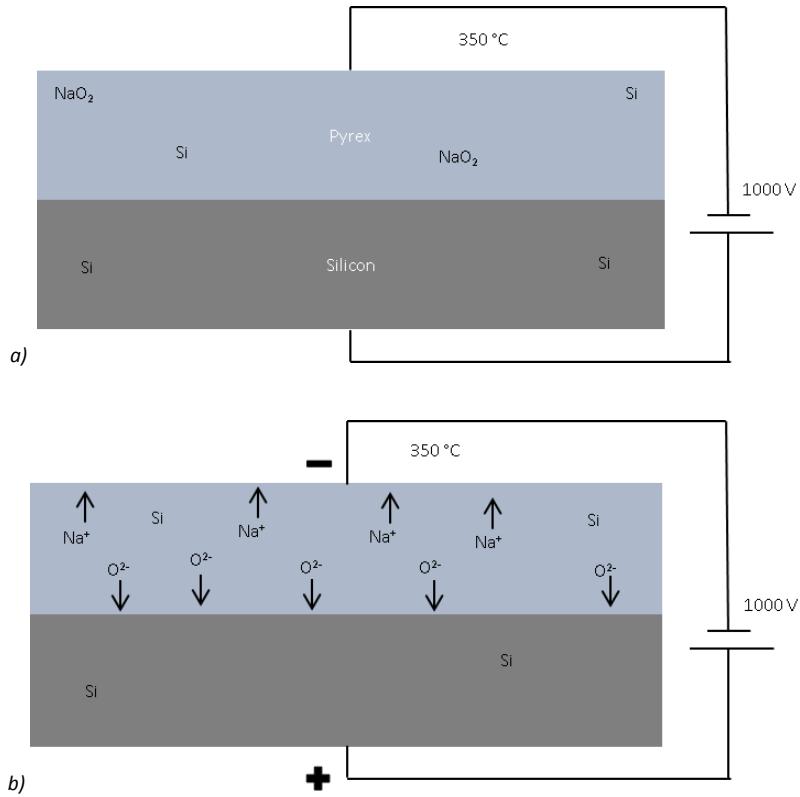

## 2.2.5 Anodic Bonding

The anodic bonding technique as sealing method between glass and silicon, was firstly presented by G. Wallis and D. I. Pomerantz in 1969 [37]. In the paper they present a new method to bond glass to metals and semiconductors. The setup used is based on a hot plate or a furnace in which the wafers are heated to the sealing temperature and then an electric field is applied to the wafer assembly. Starting from a test on the sealing of Pyrex (Corning 7740) to silicon, they selected the best temperature (300 – 600 °C) and voltage (200 – 2000 V) ranges. Temperature plays an important role in the anodic bonding since it increases the mobility of the ions in the glass. Based on this work and the works of others [38], [39], the selected temperature and voltage for the bonding of micro-channel wafers at CMi, were respectively 350 °C and 1000 V.

The anodic bonding process for the realization of the micro-channels test devices at EPFL, is done using a small controlled oven and two brass electrodes. The oven is set to 350 °C and, after the temperature is reached, a waiting time of at least 30 minutes is applied to let all the assembly be at a constant temperature. Once the temperature is set, the bonding voltage is applied. The glass wafer is connected to the anode while the silicon wafer is connected to the cathode. In *Figure 2.15 a* it is possible to see a scheme of the ion mobility during the bonding process. At high temperature the sodium oxide ( $NaO_2$ ) molecules present in the Pyrex, decompose into sodium and oxygen ions. As soon as the voltage is applied the positive sodium ions ( $Na^+$ ) start to migrate towards the anode glass surface while the negative oxygen ions ( $O^{2-}$ ) are attracted by the negative silicon and migrate towards the two wafers interface (*Figure 2.15 b*). When the ions start to move, the current is flowing in the wafer, and during the process, when the ions start reaching the top surface or the interface between the two wafers, the current is decreasing. When the current reaches the 10% of its starting value, the anodic bonding is considered finished. The movement of the ions creates a depletion layer without the presence of free charge carriers. The electrostatic force in the assembly pulls the silicon and glass together. The negative oxygen ions at the interface react with the silicon and create a silicon oxide layer that, being insulator avoid further flow of the current.

Figure 2.15: Anodic bonding scheme procedure.

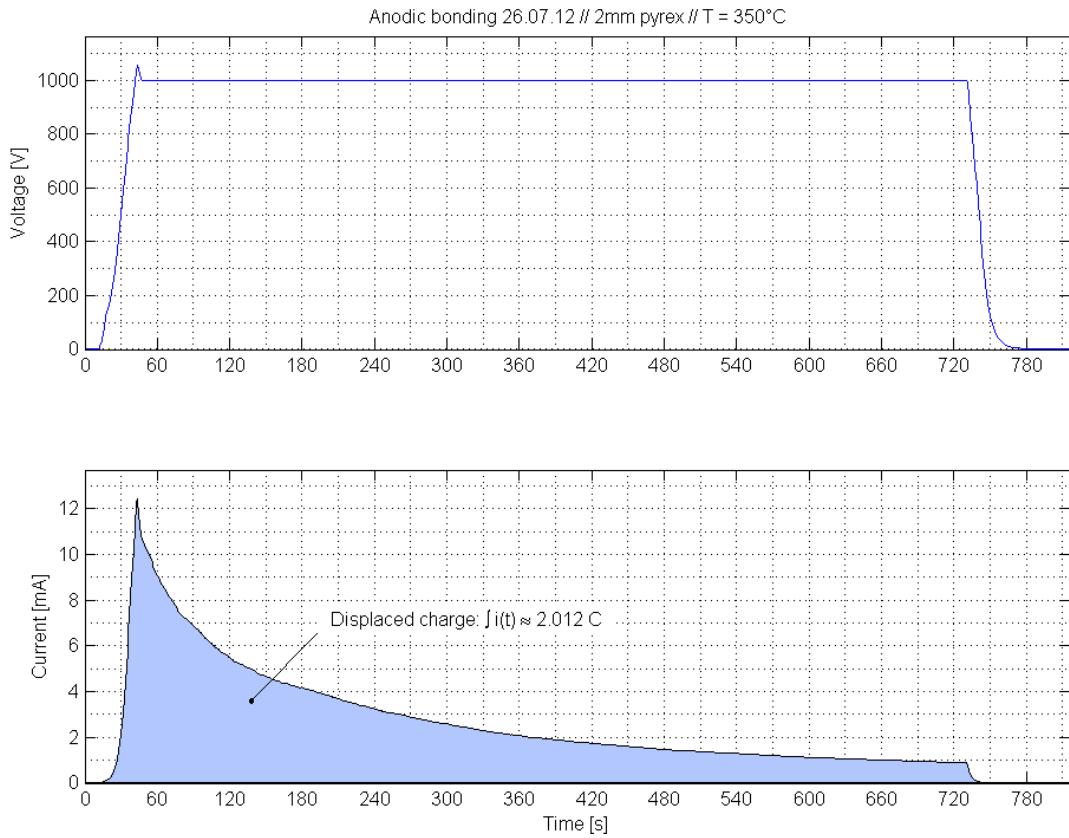

In order to understand better the voltage and current behaviour during the bonding process, the values have been recorded during a bonding between a 2 mm thick Pyrex wafer and a 380  $\mu\text{m}$  thick silicon wafer. The bonding was done at 350 °C with an applied voltage of 1000 V. In the graphs of *Figure 2.16* it is possible to see the voltage and current behaviours during the process. After setting the full voltage, the current reaches its maximum value of 12.5 mA and then start to decrease. At 0.8 mA (less than 10 % of the peak value) the voltage was removed and the bonding process was completed after around 13 minutes. By calculating the amount of current flowed in time is possible to see the total displaced charge inside the wafers during the entire process. The displaced charge can be used as an indicator for the bonding quality and the bond strength [40].

Figure 2.16: Anodic bonding current and voltage monitoring in EPFL.

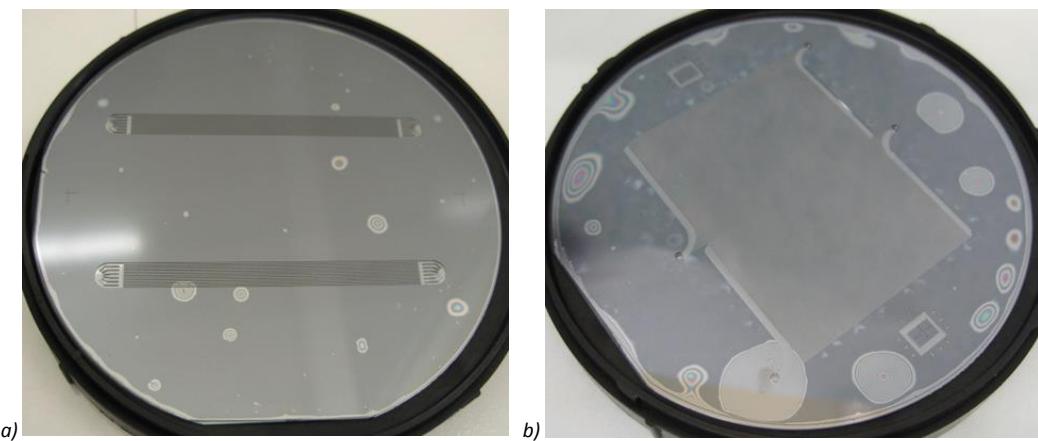

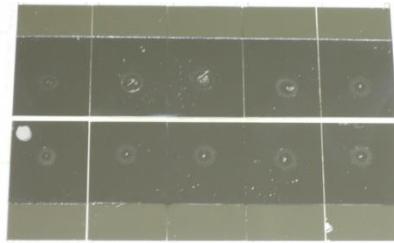

In the anodic bonding process the quality inspection of a good bonding process is easy, since the defects are visible at the interface between the two wafers from the Pyrex side. The well bonded areas are dark while the defects appear in a lighter colour. In *Figure 2.17* it is possible to see bonded wafers with many defects at the interface. Both wafers were done as a test for the NA62 experiment. Bonding defects can be due to the presence of dust particles in the interface, to defects in the wafer surface, to roughness and others. In *Figure 2.17 b* the Pyrex wafer has been previously machined and four holes have been drilled inside it. This leads to the presence of bonding defects next to the drilled areas caused by the particles and the damages surface next to the hole.

Figure 2.17: Anodic bonding tests done at EPFL for the NA62 experiment.

Cleaning is one of the key parameters for a good quality of anodic bonding. As suggested in different works [41], several cleaning ways and surface preparation have been tested. A cleaning method used was an oxygen plasma process with high power before the anodic bonding. Another test was done using the cleaning bath with the so-called “piranha solution”:  $\text{H}_2\text{SO}_4$  acid boiling at 100 °C with  $\text{H}_2\text{O}_2$  added at high temperature. For higher cleaning purposes also the combination of the two methods, “piranha” and oxygen plasma, was tested. Another tested bath was the RCA cleaning procedure with a mixture of different acids bath  $\text{NH}_4\text{OH}$ , HF, HCl at high temperatures. For the surface treatment a CMP (Chemical Mechanical Polishing) procedure was done on the silicon bonding surface followed by a RCA treatment. At the end of the test campaign the “piranha solution” was chosen as best cleaning method for the anodic bonding procedure in the EPFL CMi cleanroom.

## 2.2.6 Direct Bonding

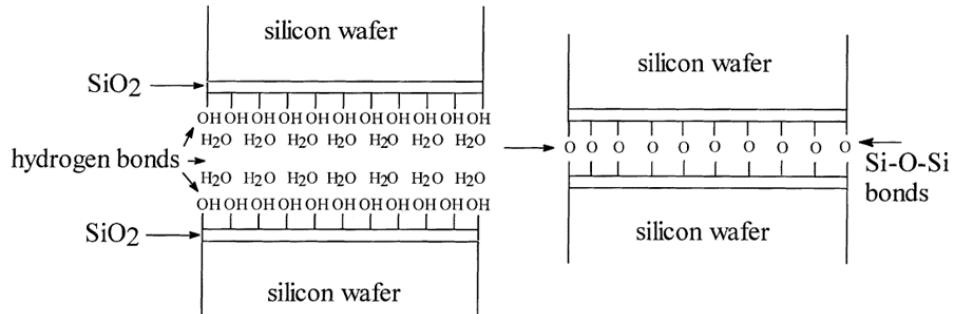

In the direct bonding procedure, also called fusion bonding, two silicon wafers, with mirrored surfaces, are placed in direct contact without an intermediate layer. The bonding is the result of chemical reactions among the OH groups present on the wafer surface. Direct bonding can be performed at room temperature or low temperature [42], but usually a high annealing temperature (more than 800 °C) is applied to increase the interface energy and so the bonding strength. More than for the anodic bonding, the wafer cleaning is a very critical step in fusion bonding. During the cleaning of the wafer also a surface activation takes place. Two different bonding types are possible: the hydrophilic bonding [43] and the hydrophobic bonding [44]. In the hydrophilic process, at the bonding interface a thin layer of silicon dioxide is present while, in the hydrophobic bonding, no intermediate layer is used and just Si-Si bonds are present. For the hydrophilic type, the RCA cleaning leaves on the wafer surface a large number of silanol groups (Si-OH) responsible of the wafer bonding. For the hydrophobic instead the wafers are cleaned in HF solution to leave on the surface Si-H groups. In *Figure 2.18* and *Figure 2.19* it is possible to see in detail the chemical bonds present at the interface of the hydrophilic and hydrophobic bonding before and after the annealing step.

Figure 2.18: Direct bonding chemical bonds for the hydrophilic process before and after annealing (Ref [42]).

Figure 2.19: Direct bonding chemical bonds for the hydrophobic process before and after annealing (Ref [42]).

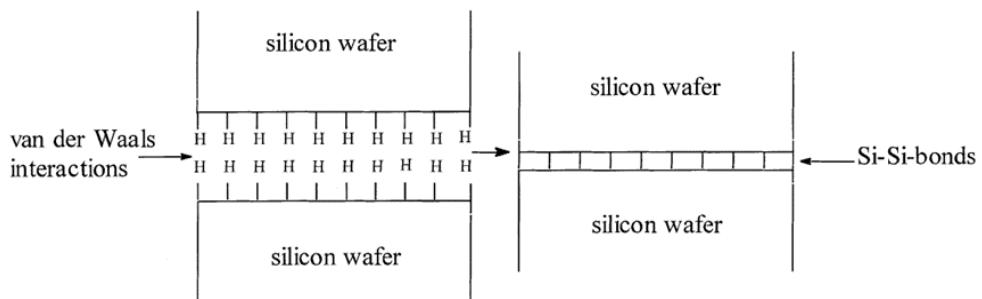

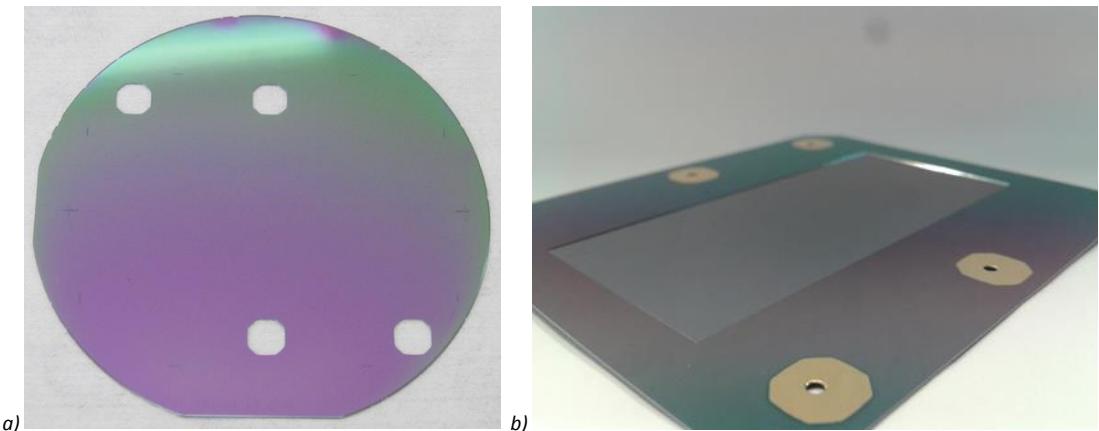

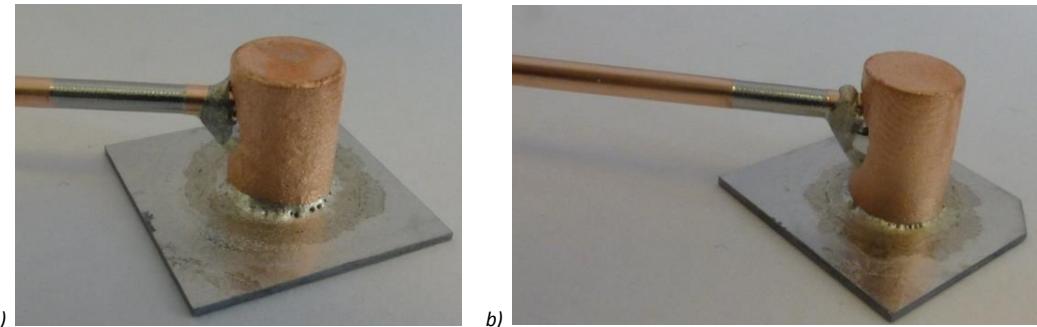

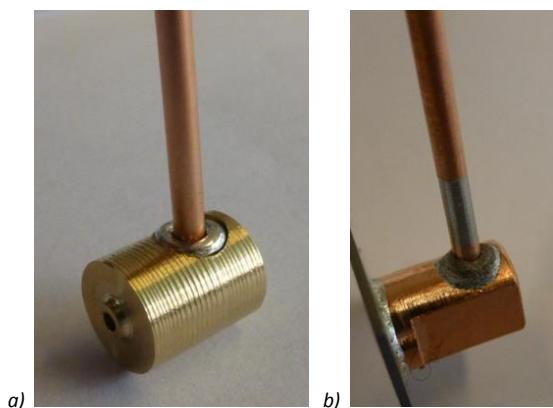

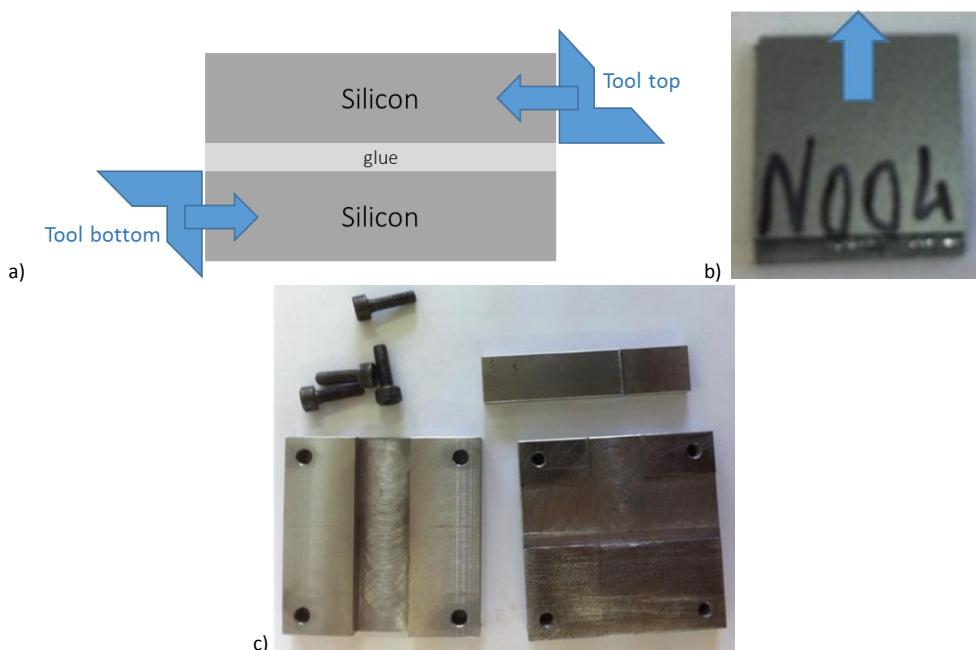

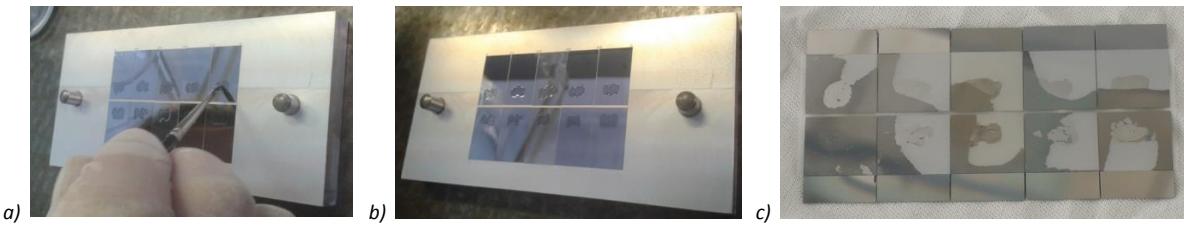

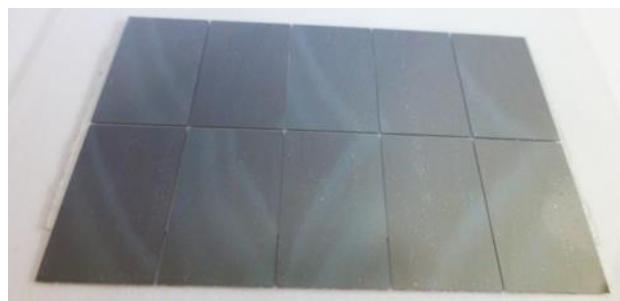

Due to the high cleaning requirements, inside the EPFL cleanroom the direct bonding process was never successful. Thanks to a collaboration between CERN and CSEM (Centre Suisse d'Electronique et de Microtechnique) [45] in Neuchatel, it was possible to process, inside the CMi cleanroom, 4" silicon wafers until the bonding step and then send them to bond to CSEM. The final quality inspection is more complicated for the direct bonding than for the anodic bonding, since the interface is not visible. To test the bond quality, at CSEM infra-red images were done. In Figure 2.20 is possible to see two examples of infra-red images done on the 4" wafer to see the bonding interface. In the first wafer (Figure 2.20 a) it is possible to see how the top part of the wafer is un-bonded, while for the second test (Figure 2.20 b) only small defects are visible far from the micro-channels area.

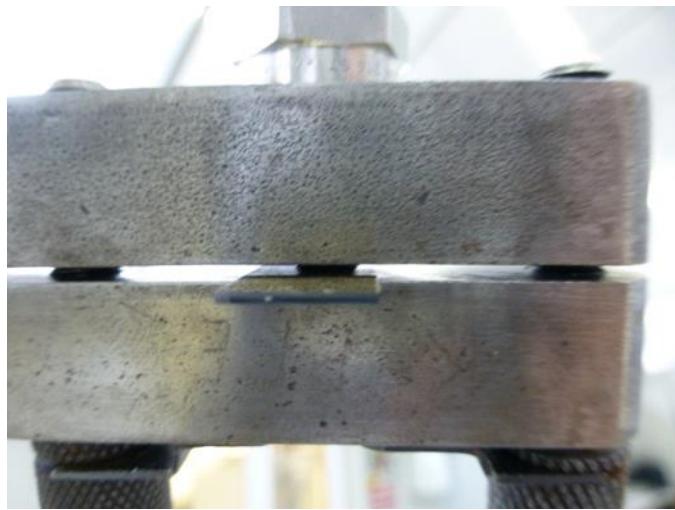

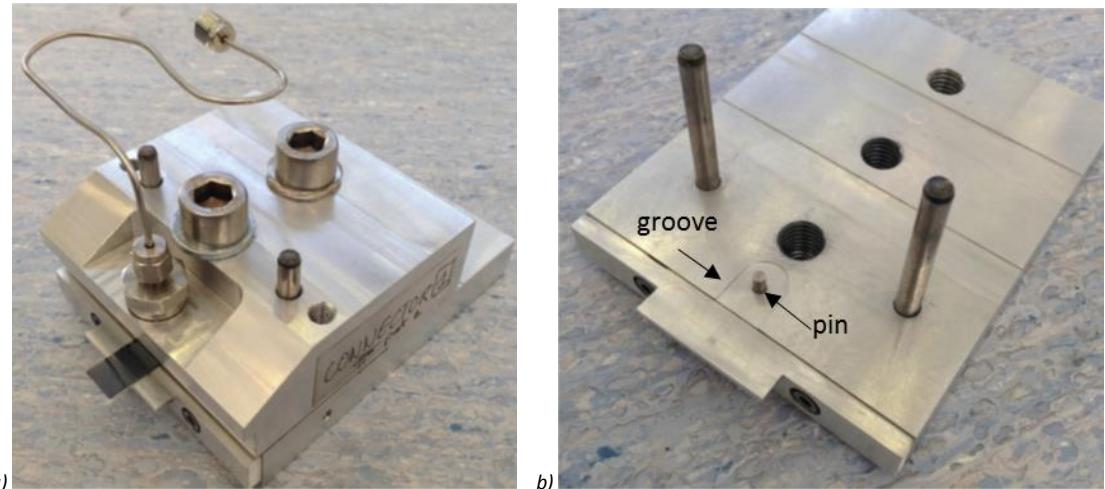

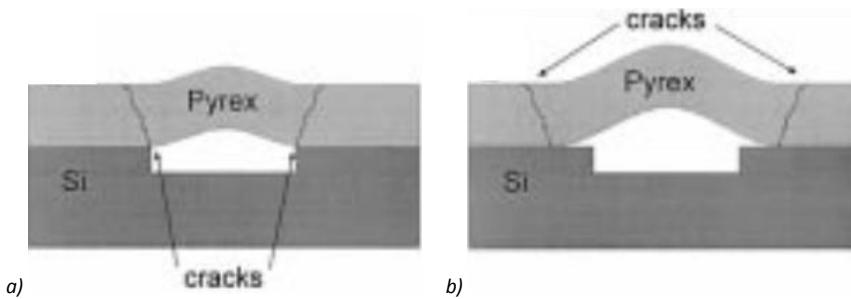

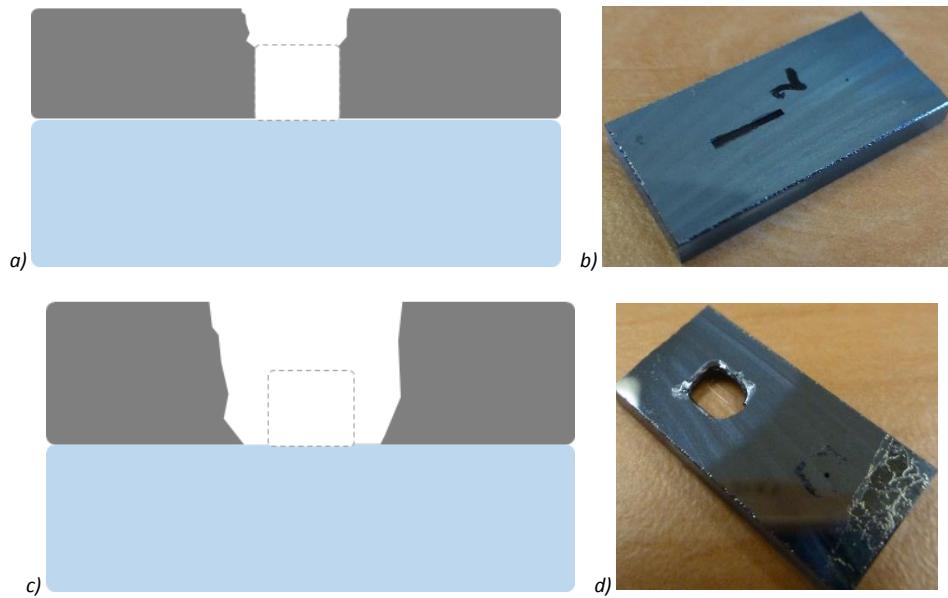

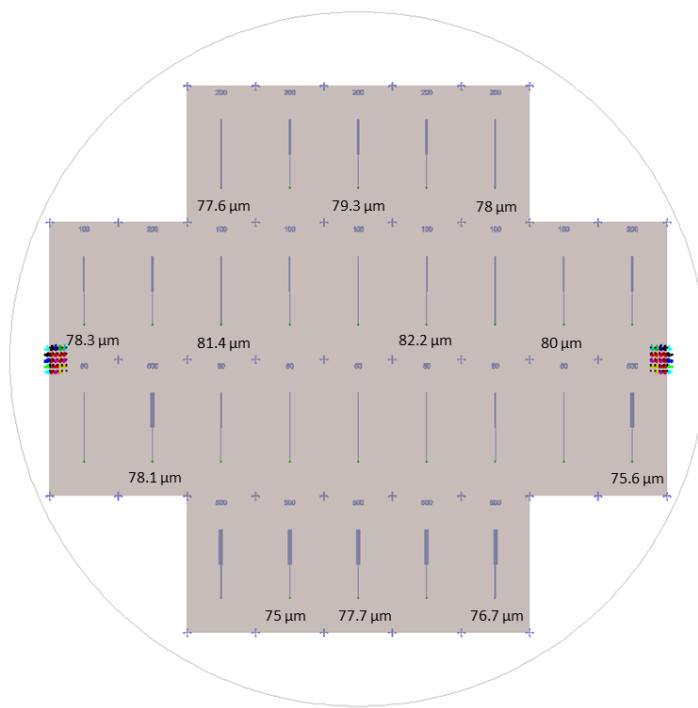

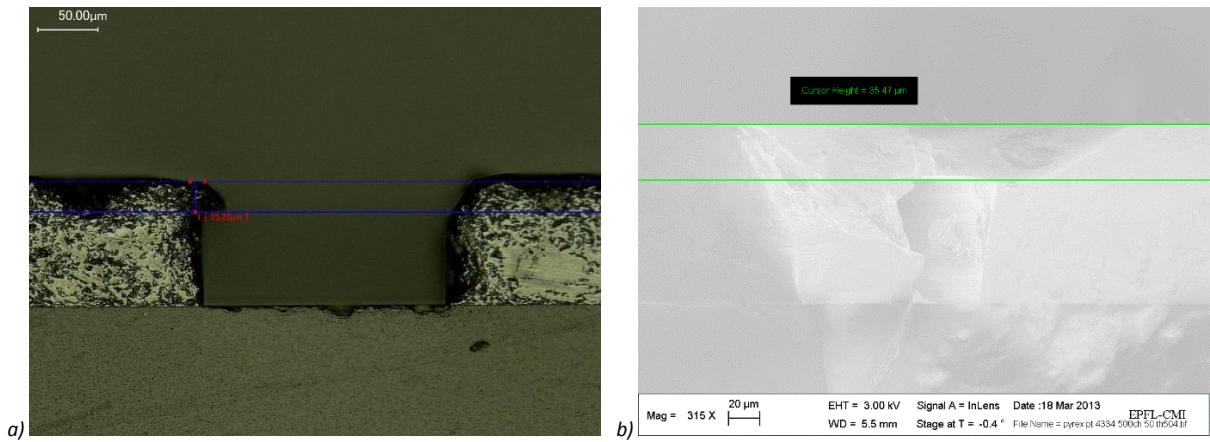

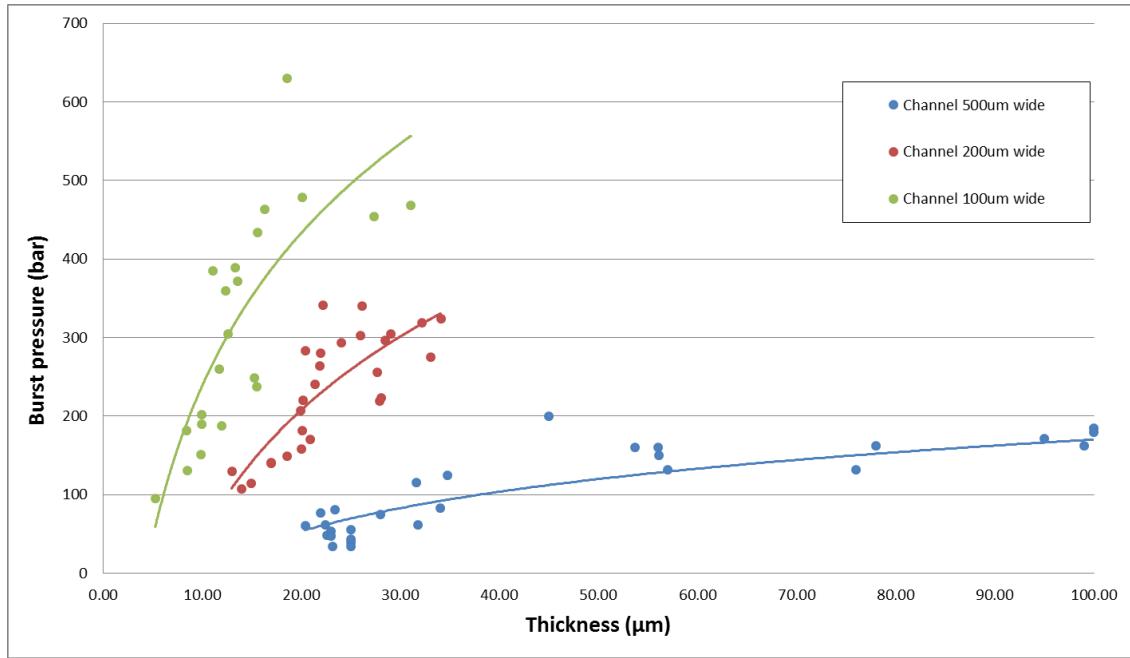

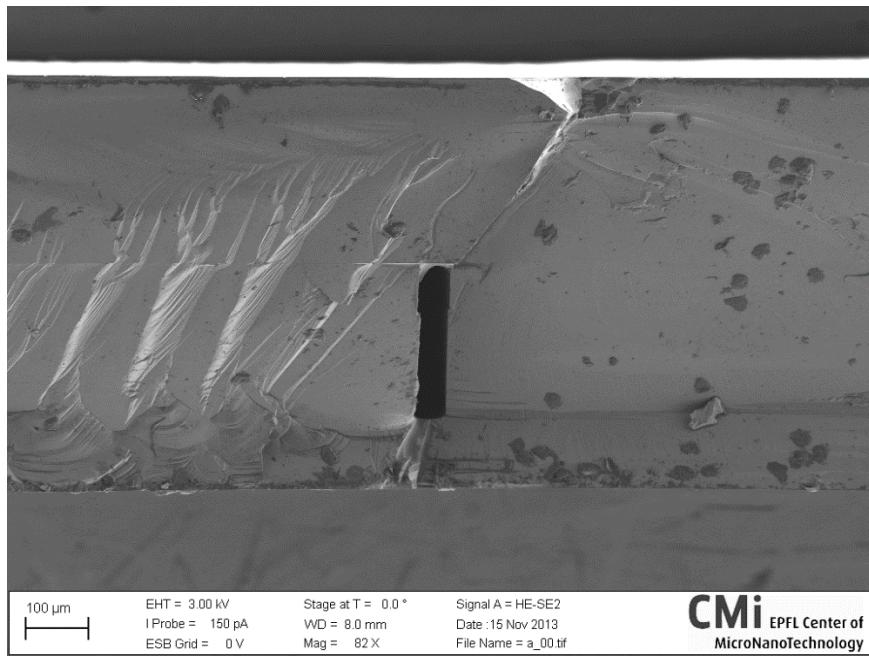

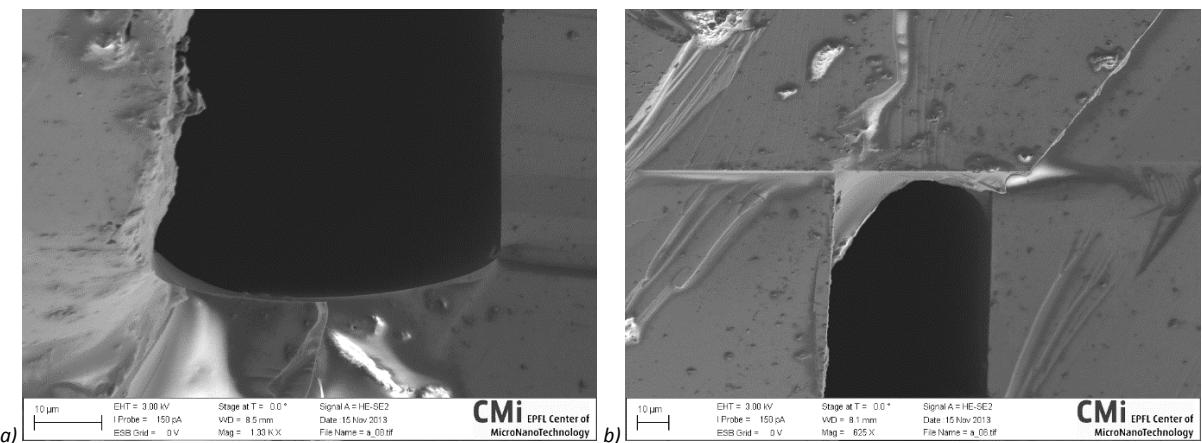

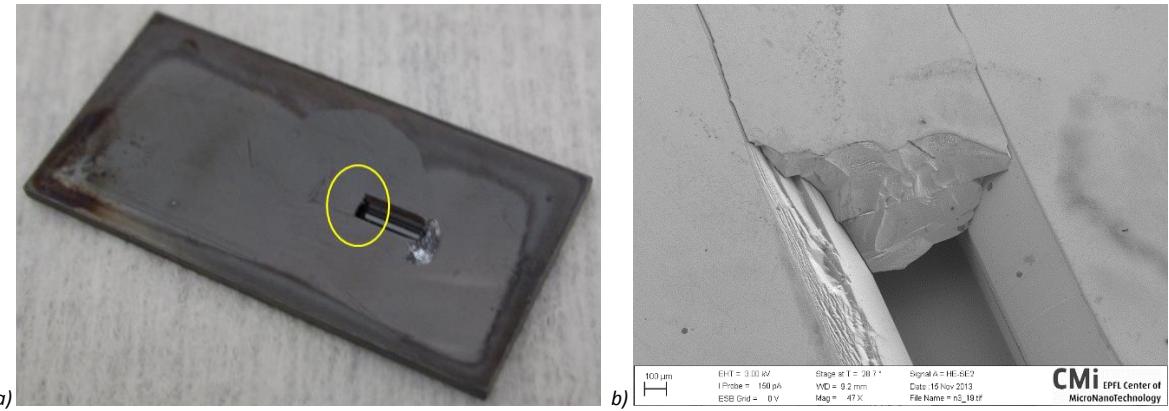

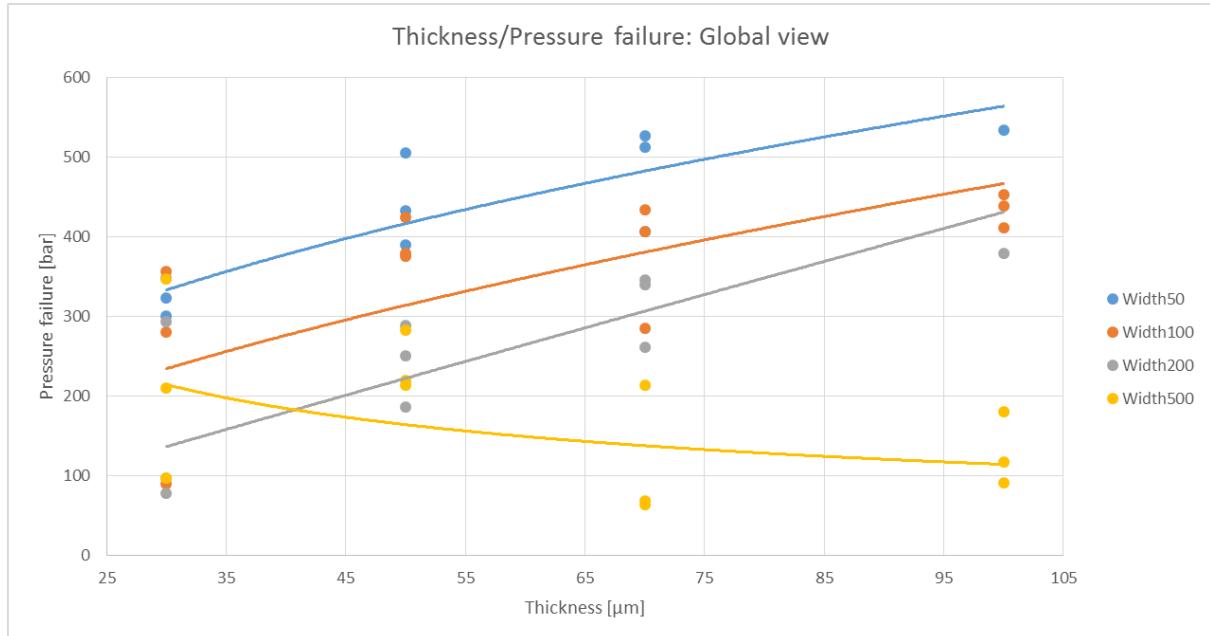

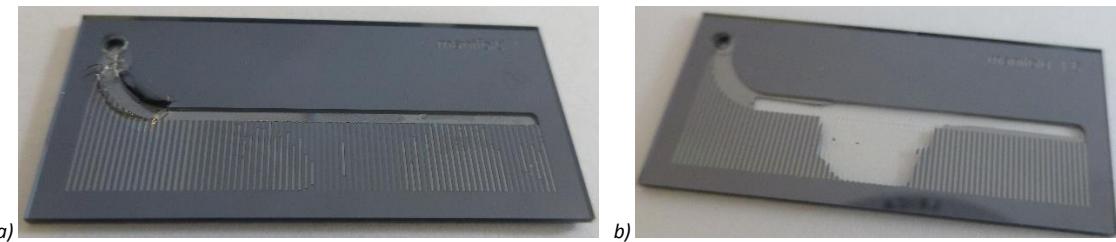

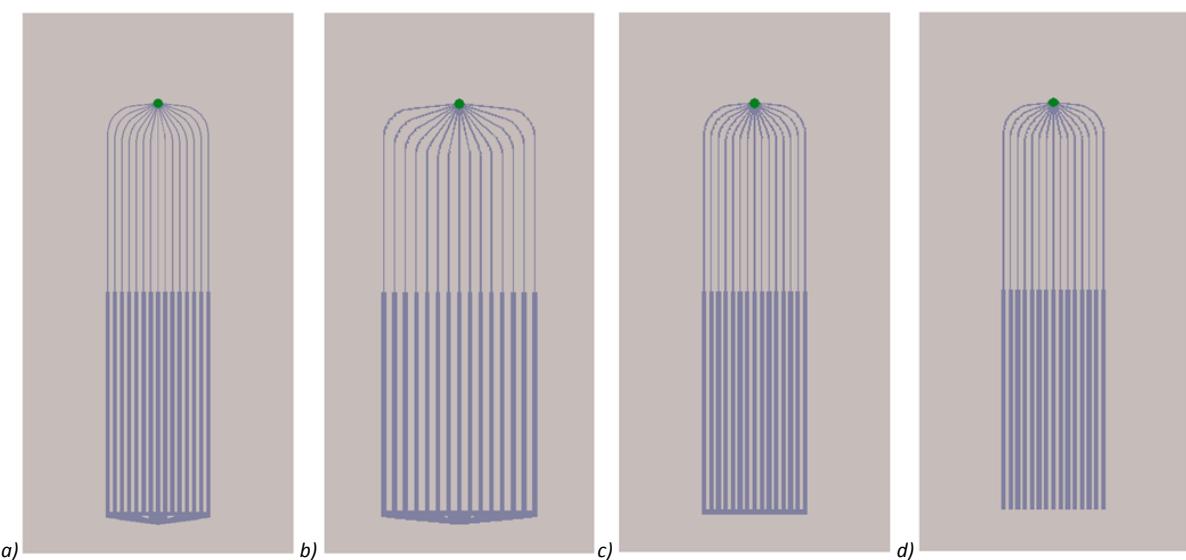

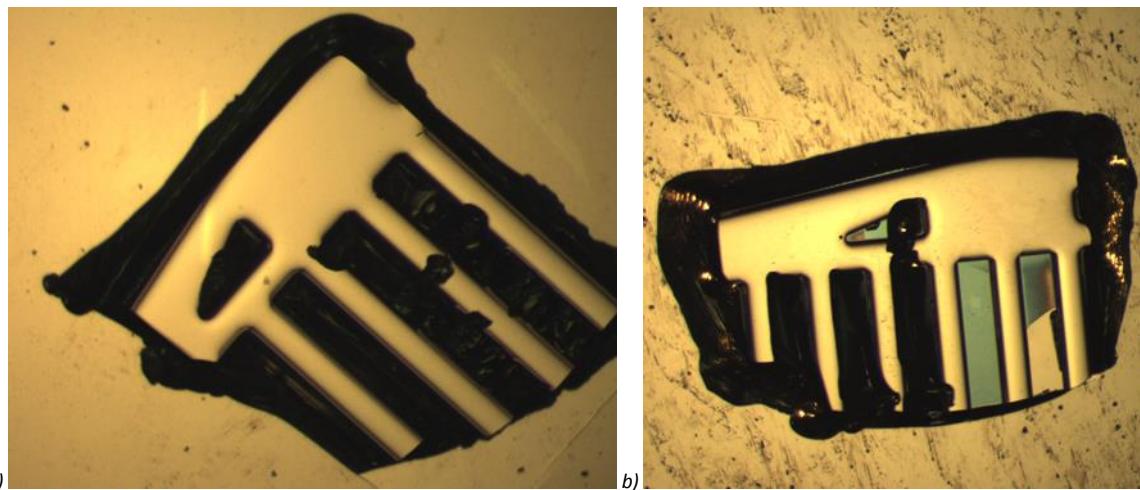

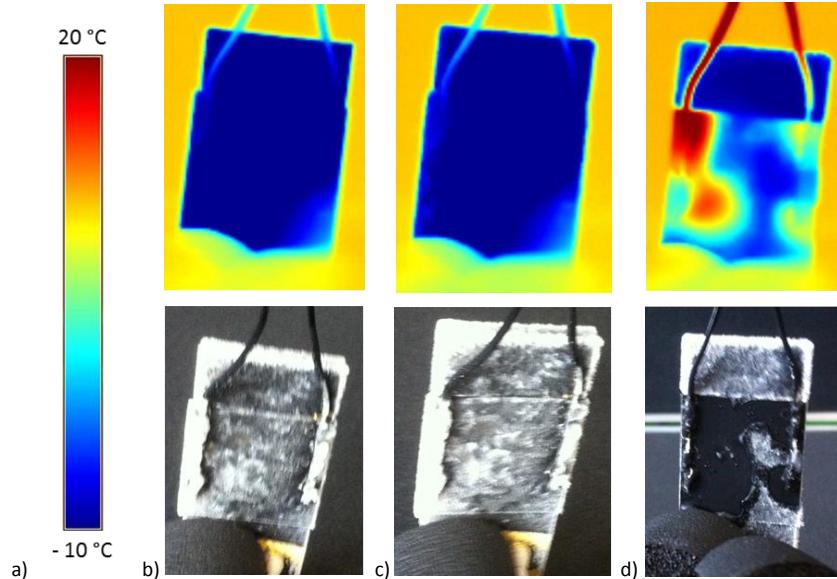

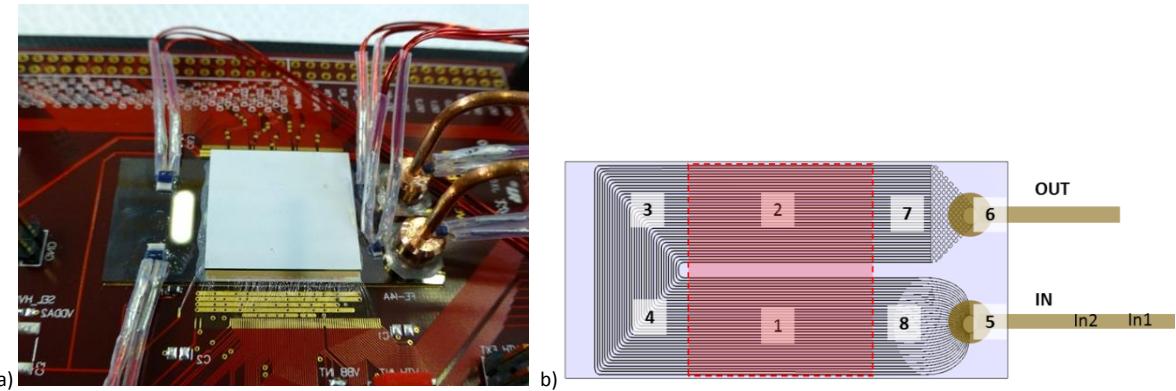

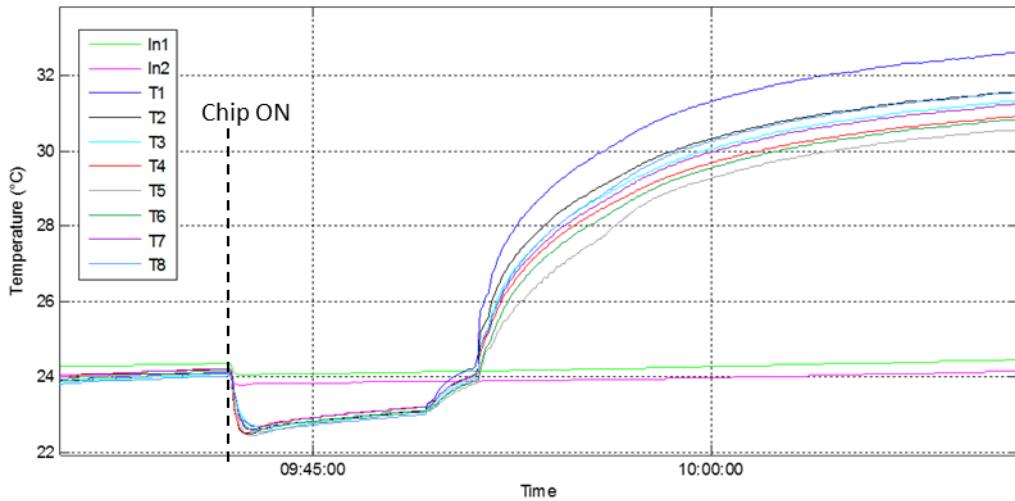

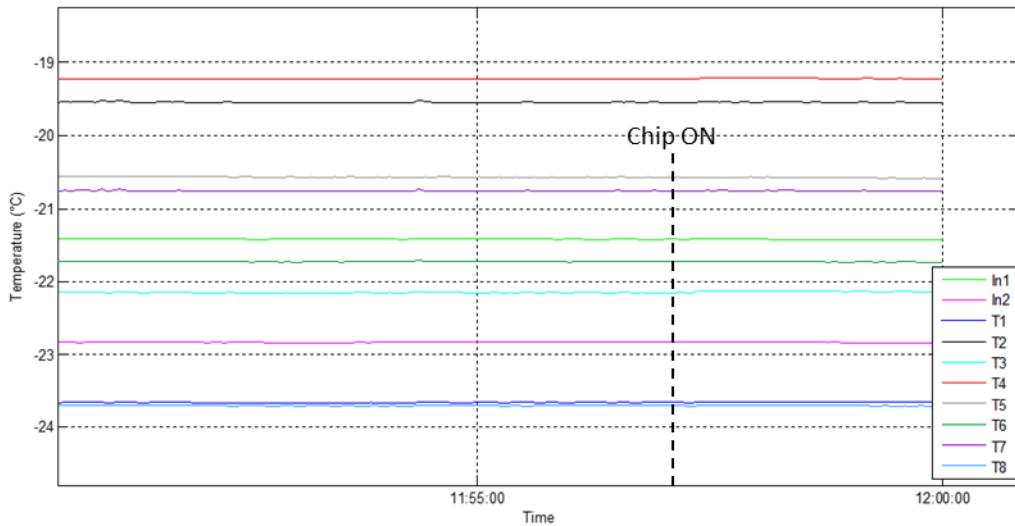

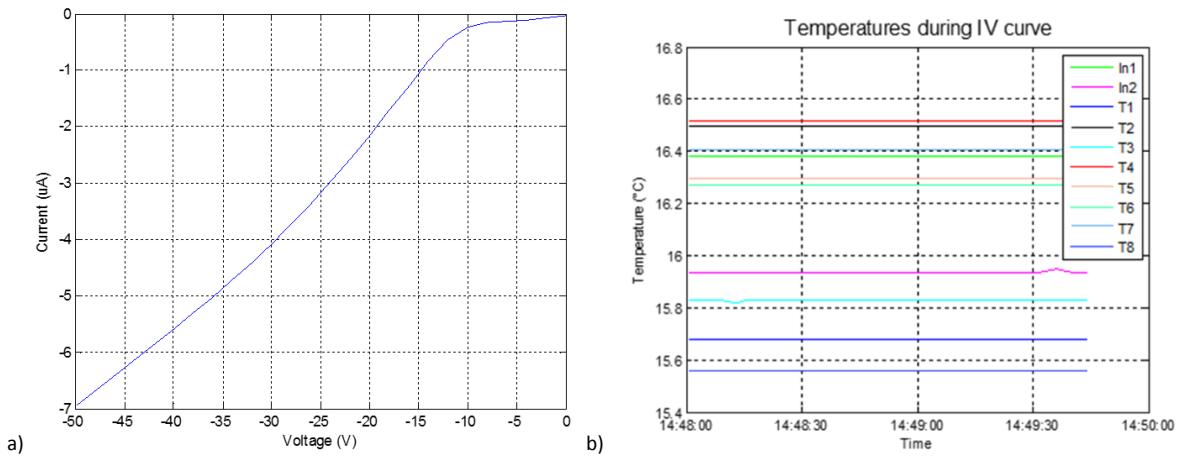

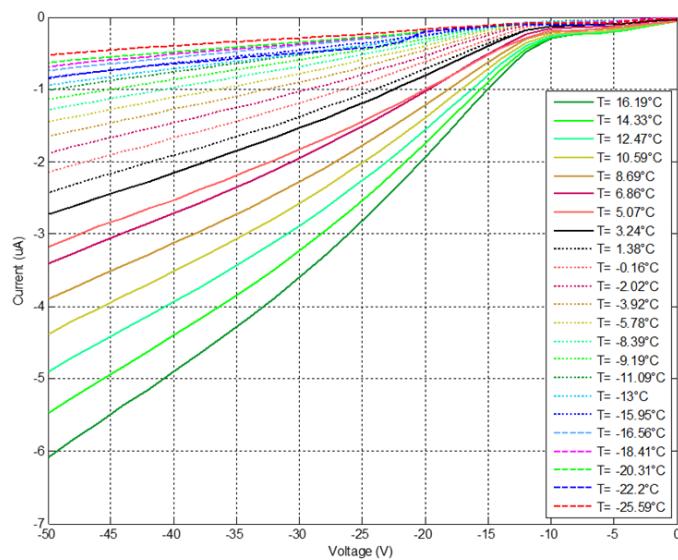

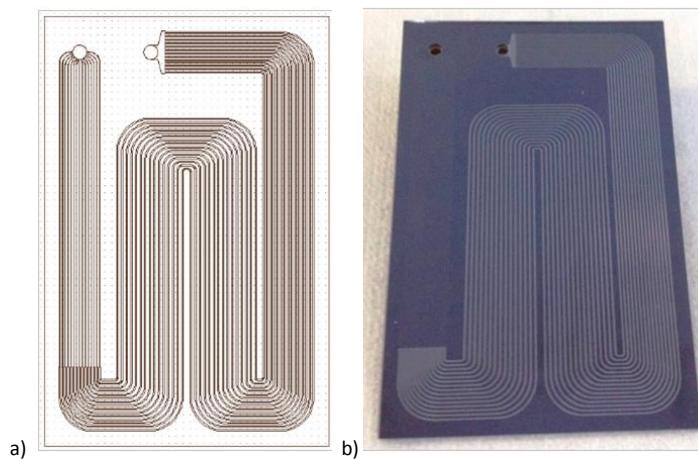

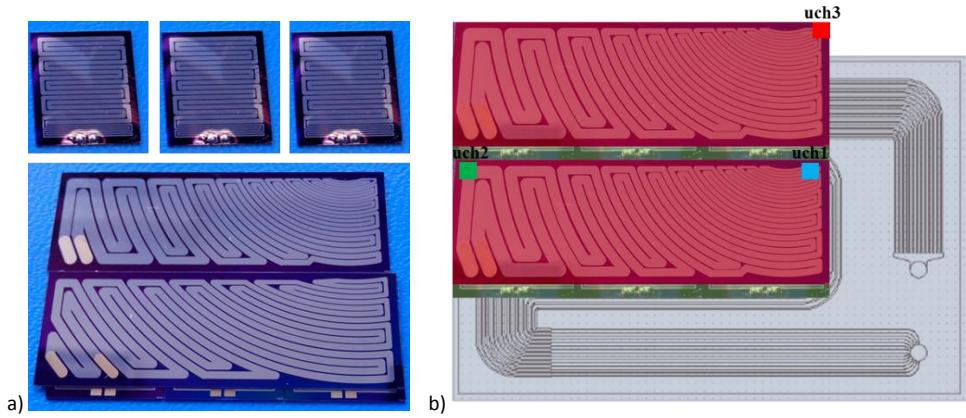

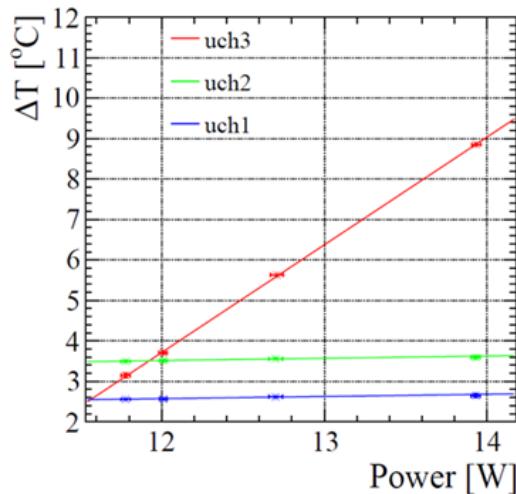

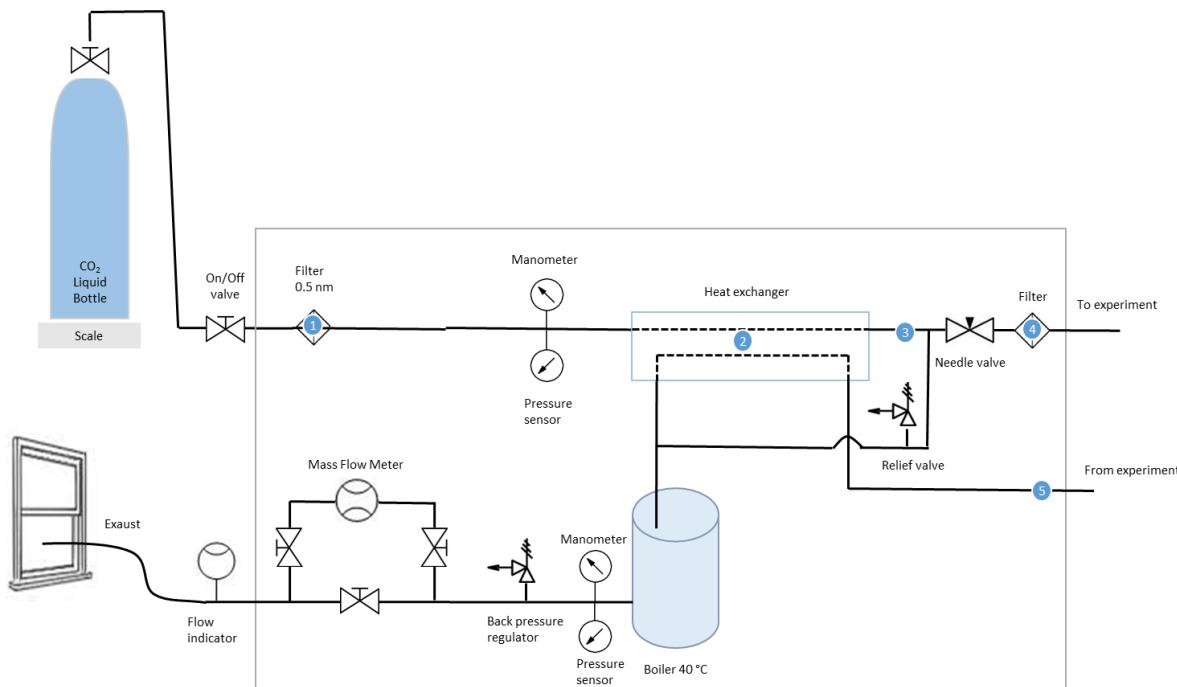

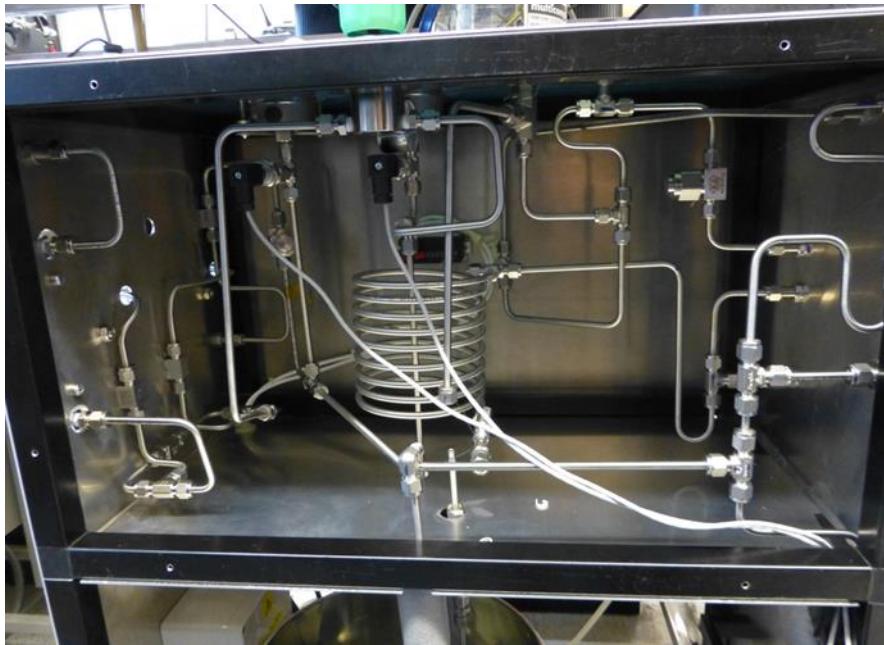

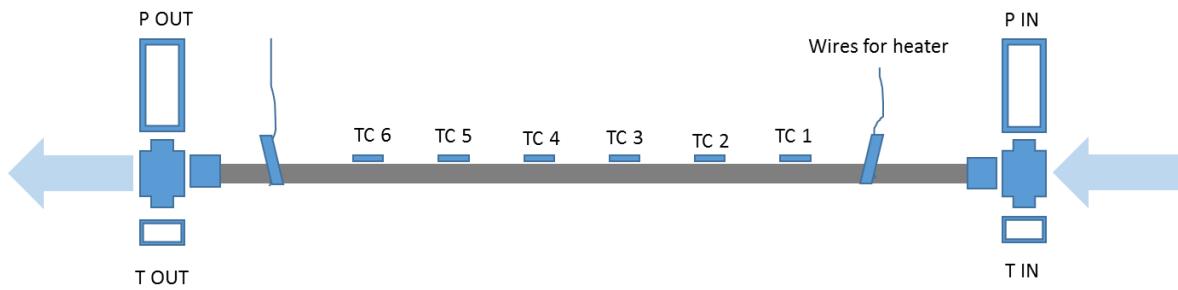

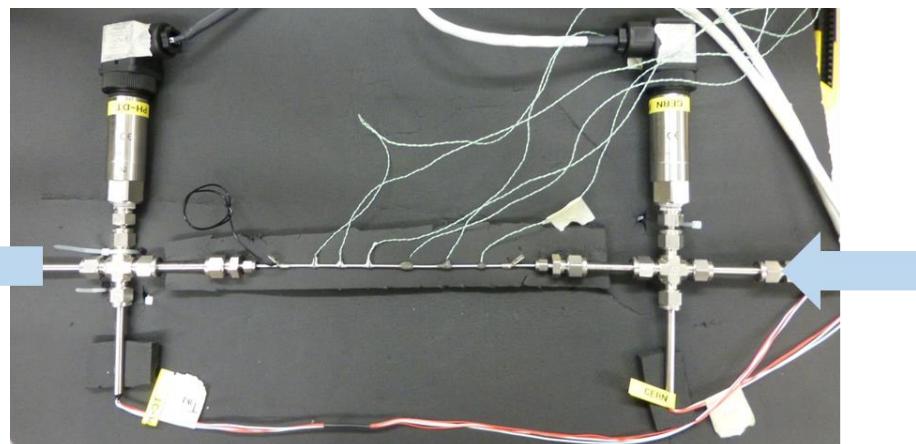

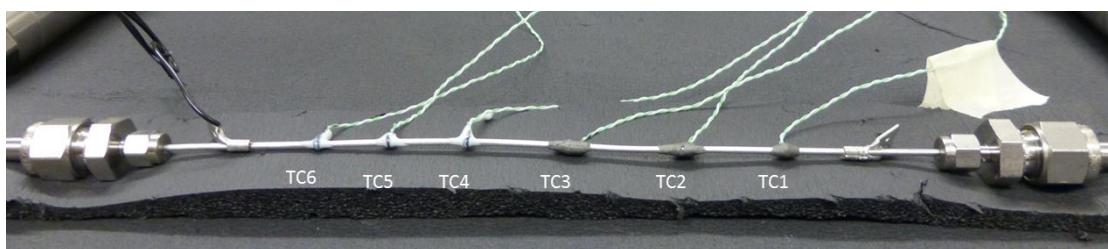

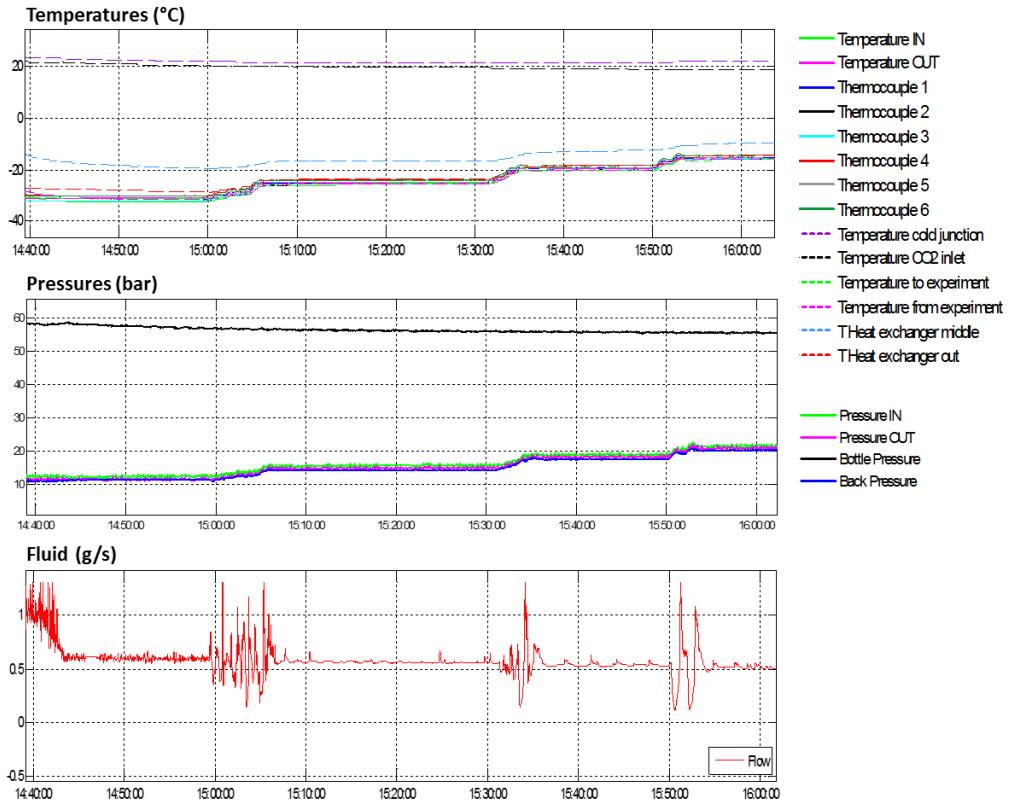

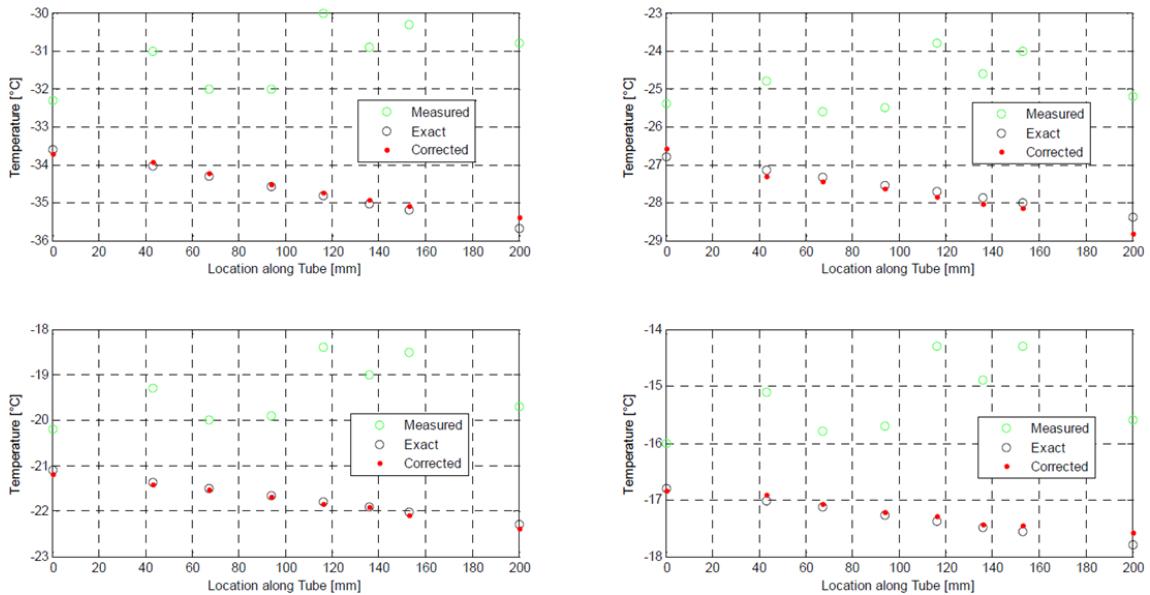

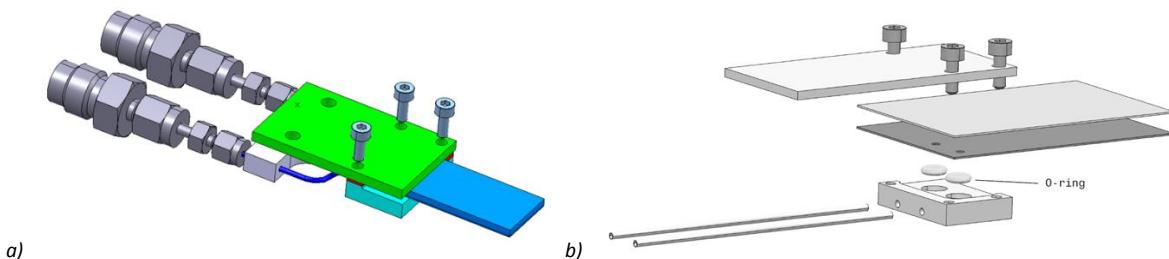

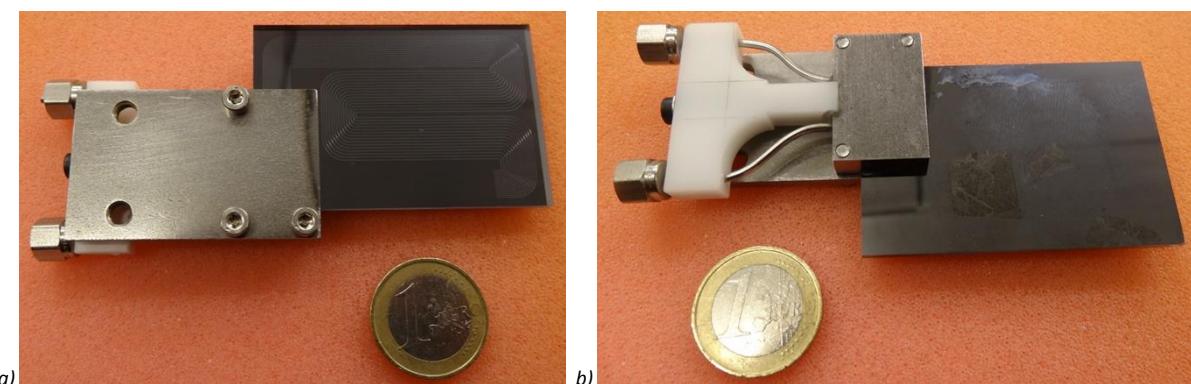

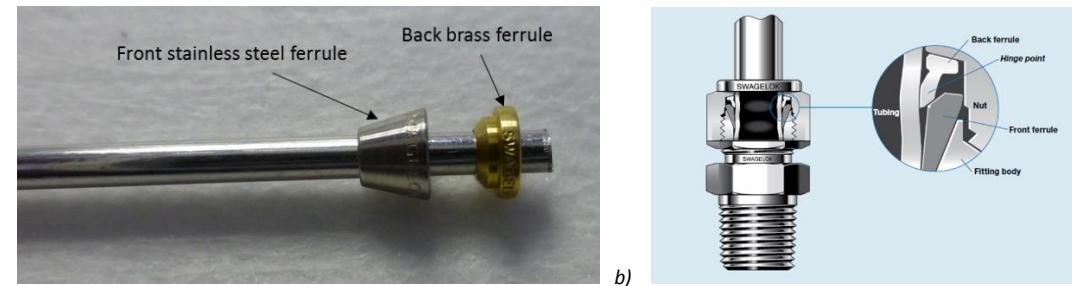

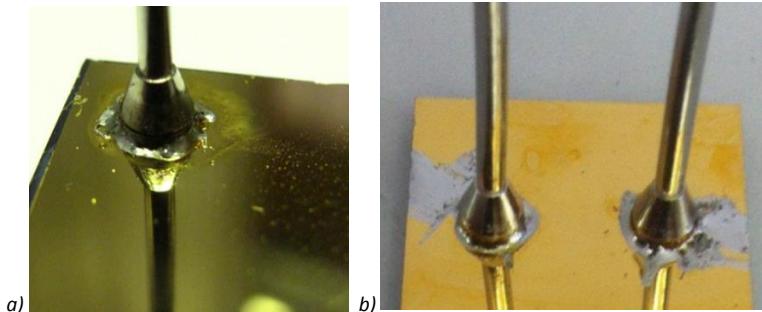

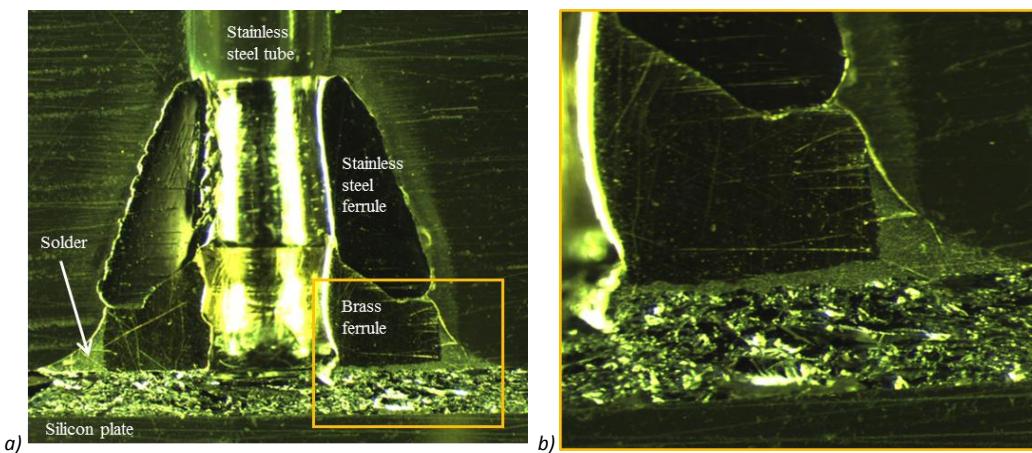

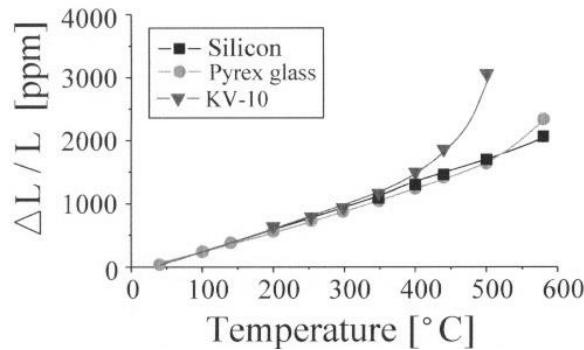

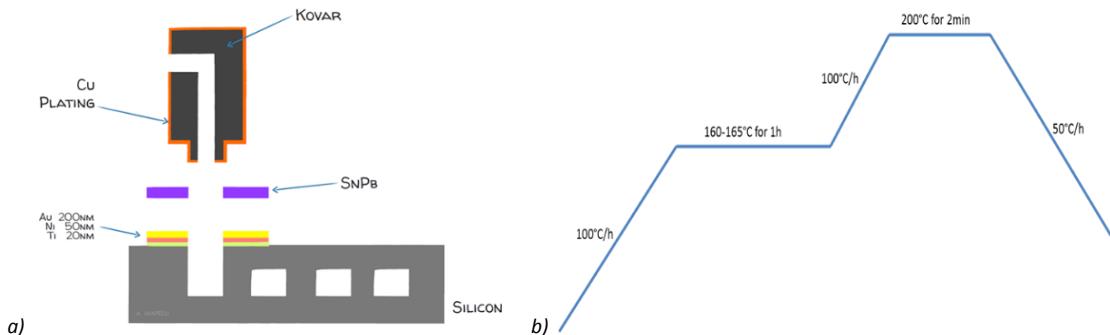

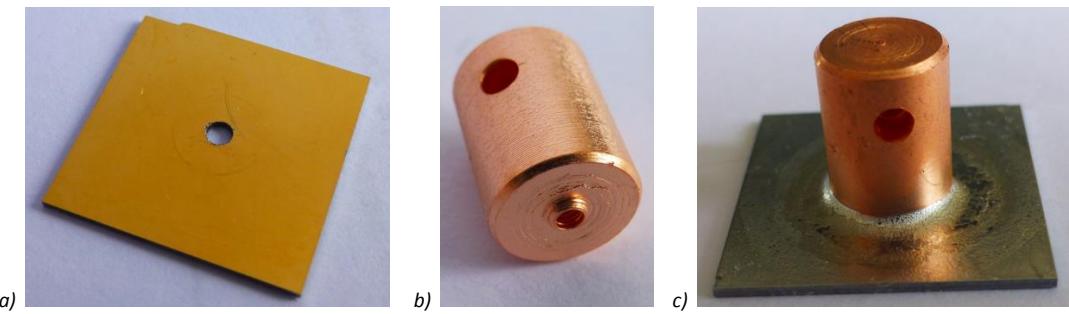

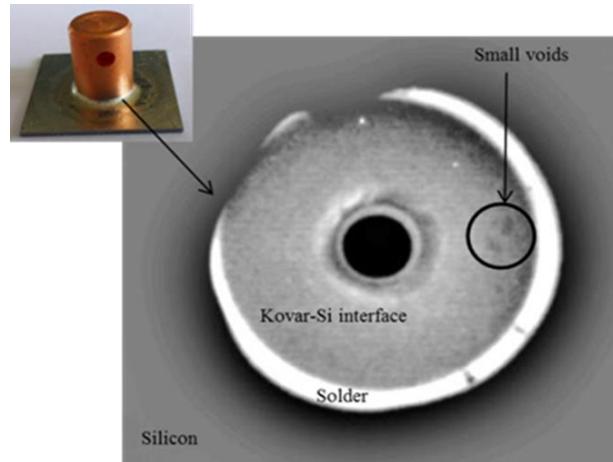

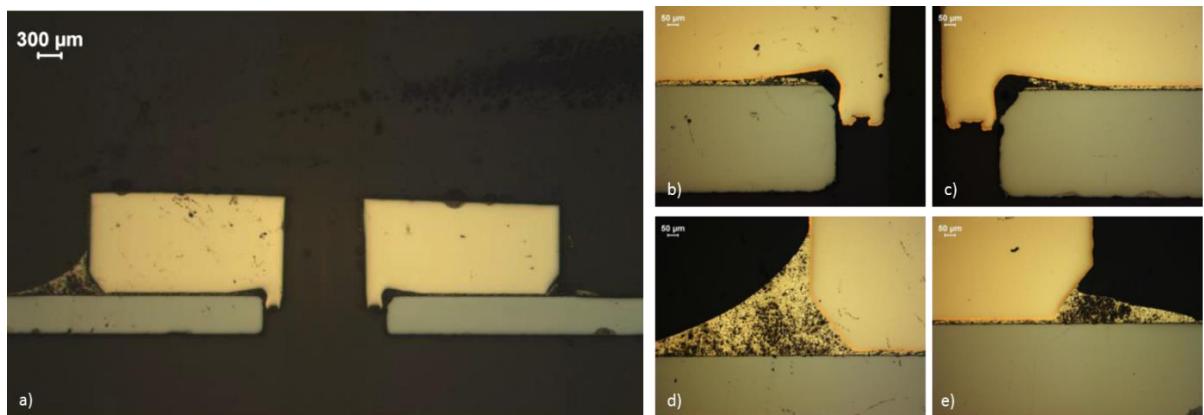

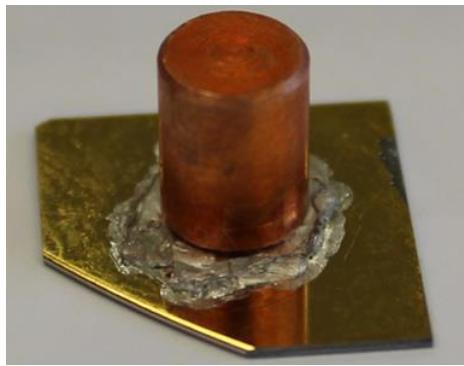

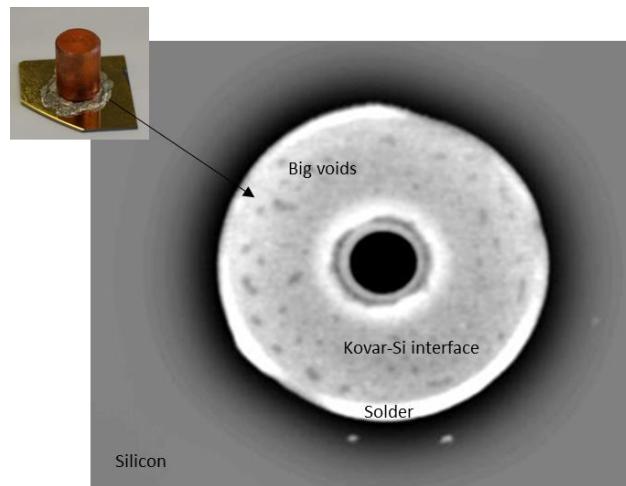

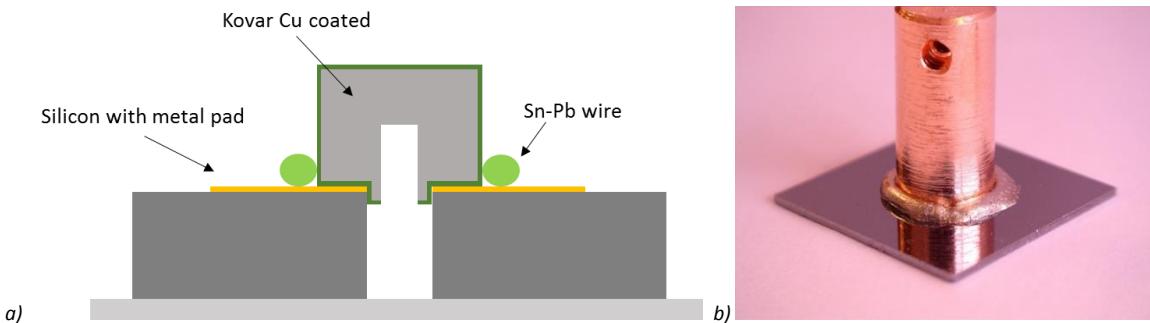

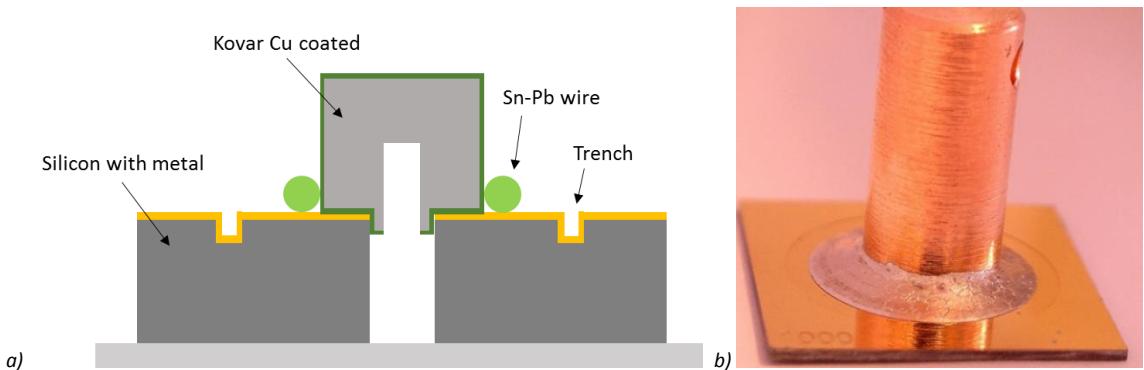

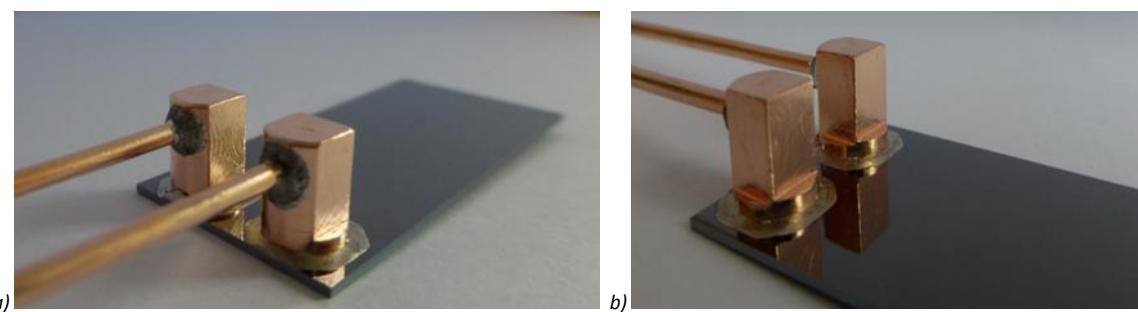

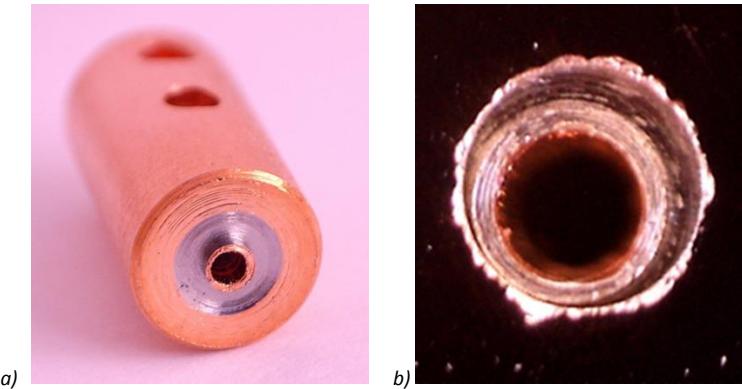

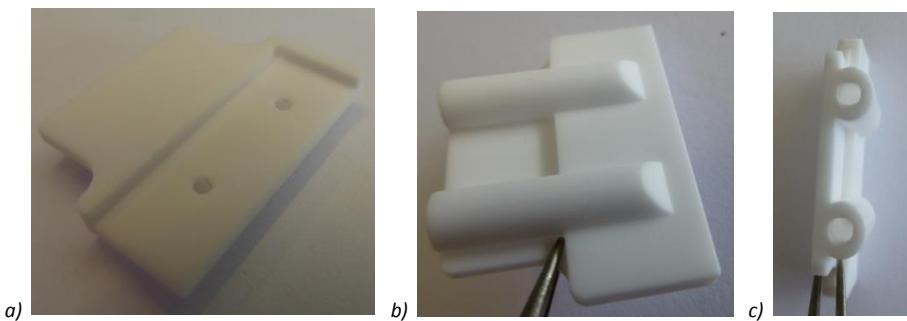

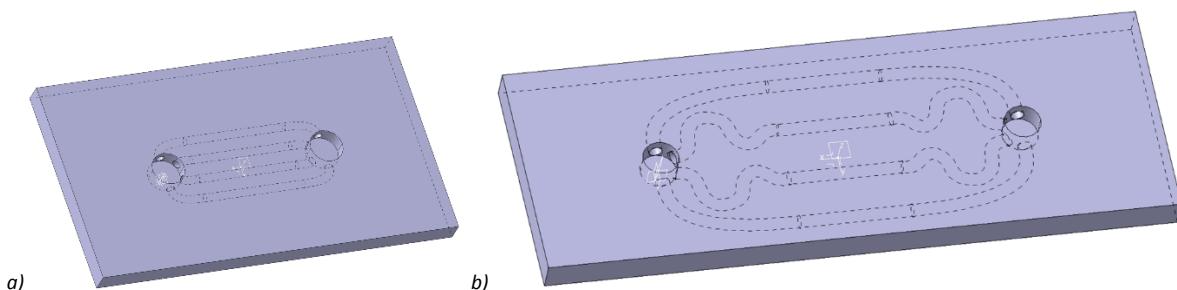

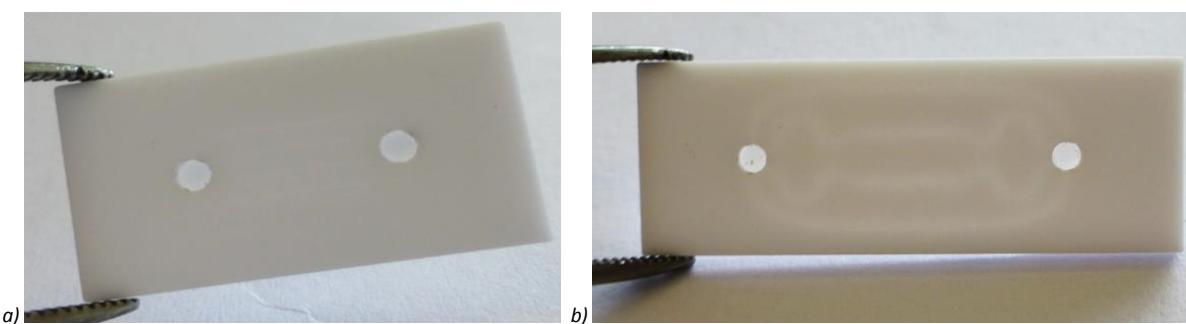

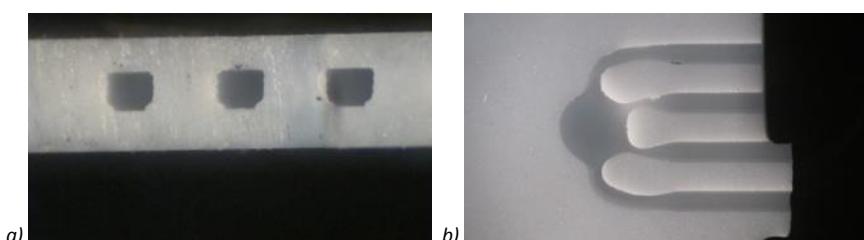

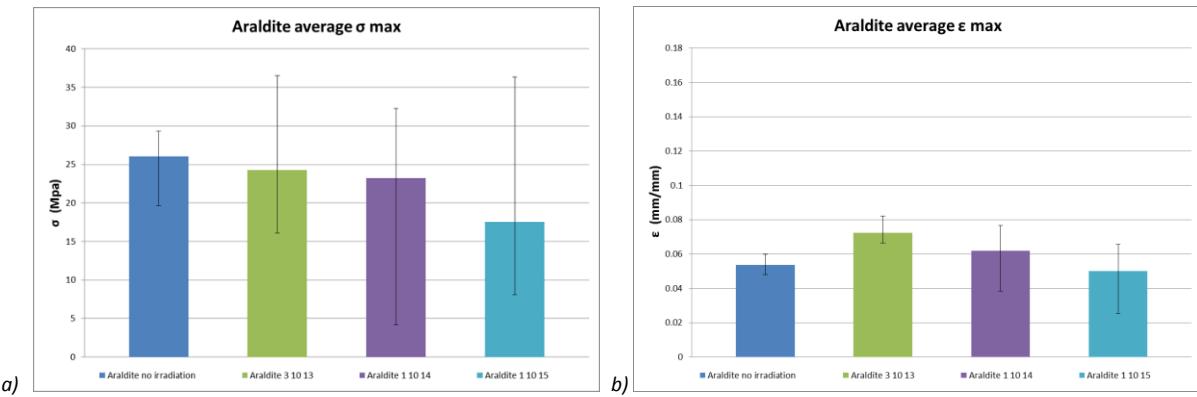

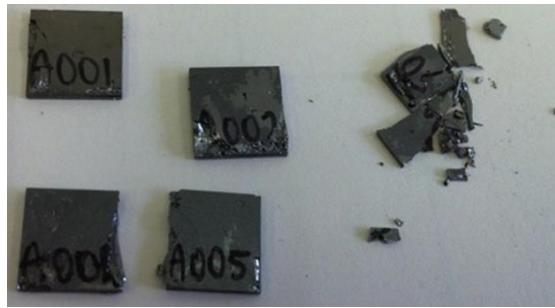

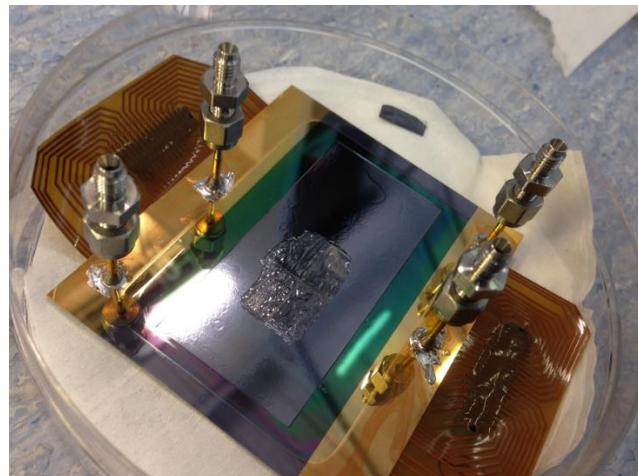

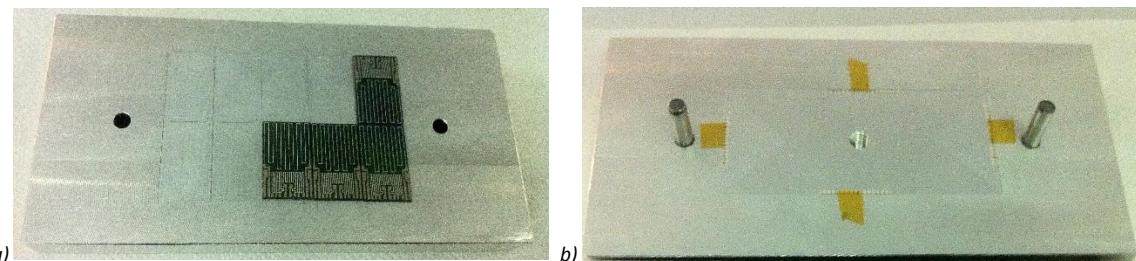

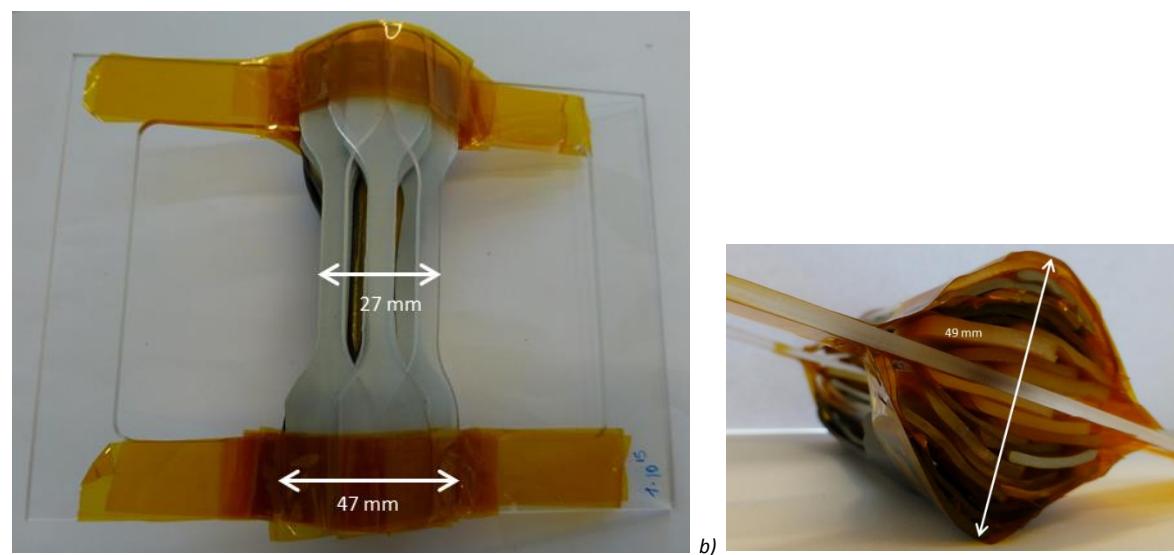

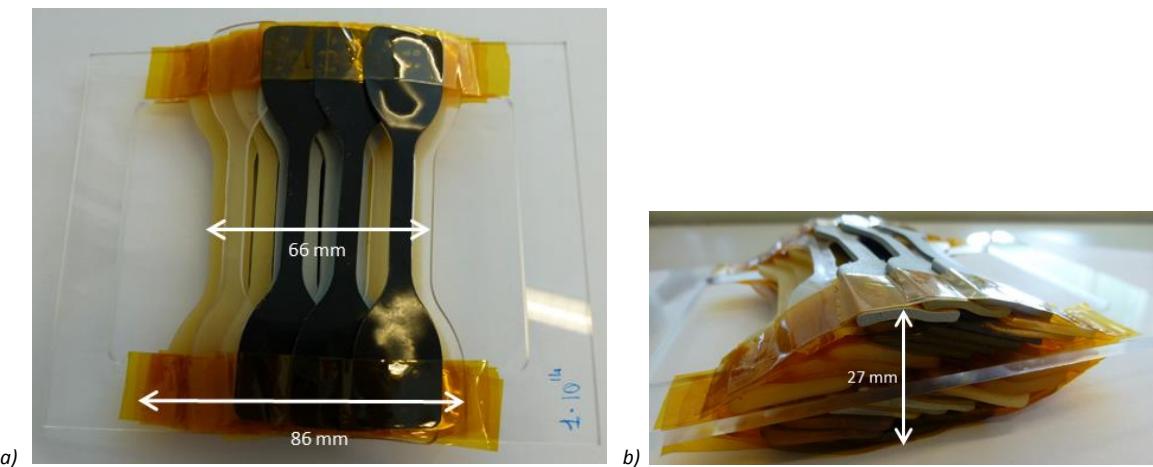

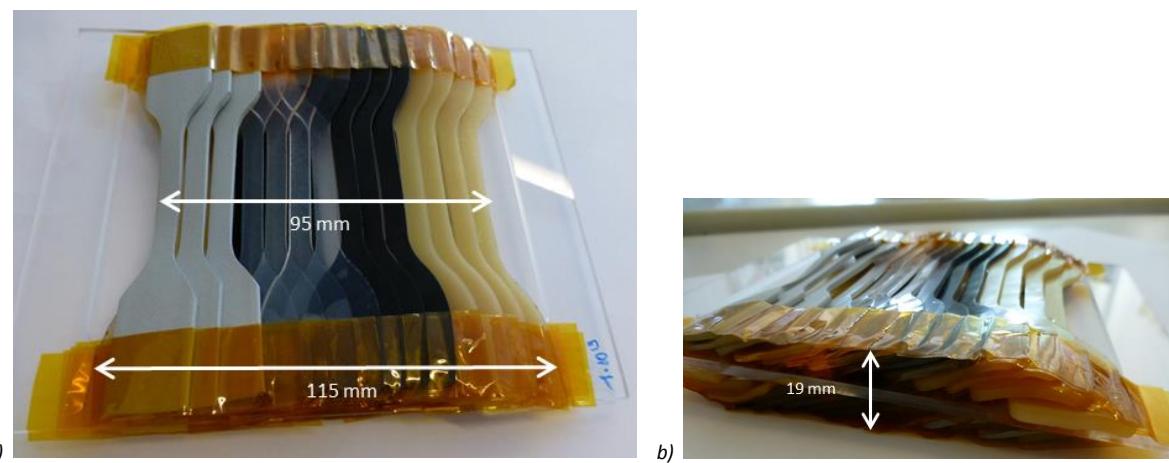

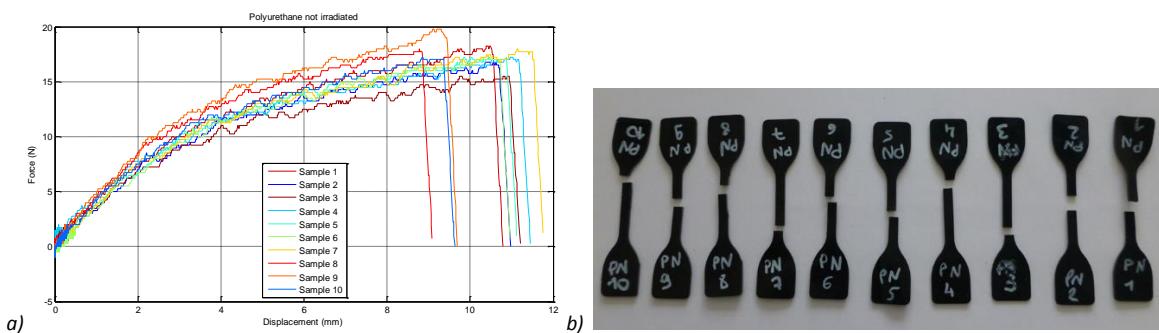

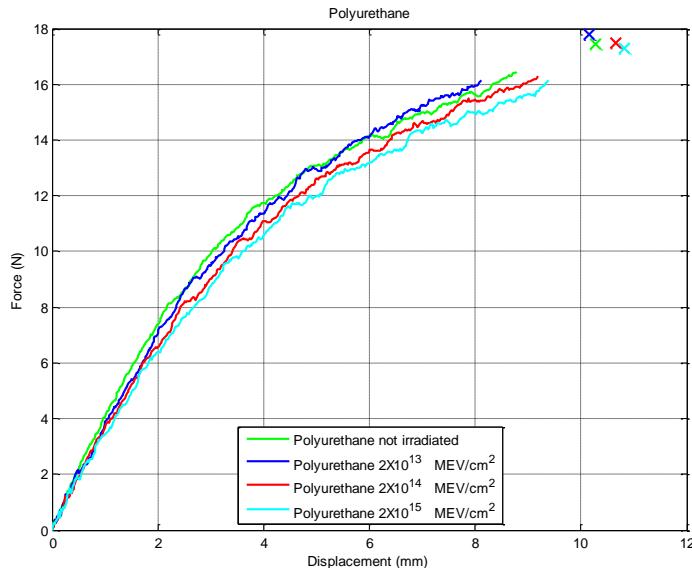

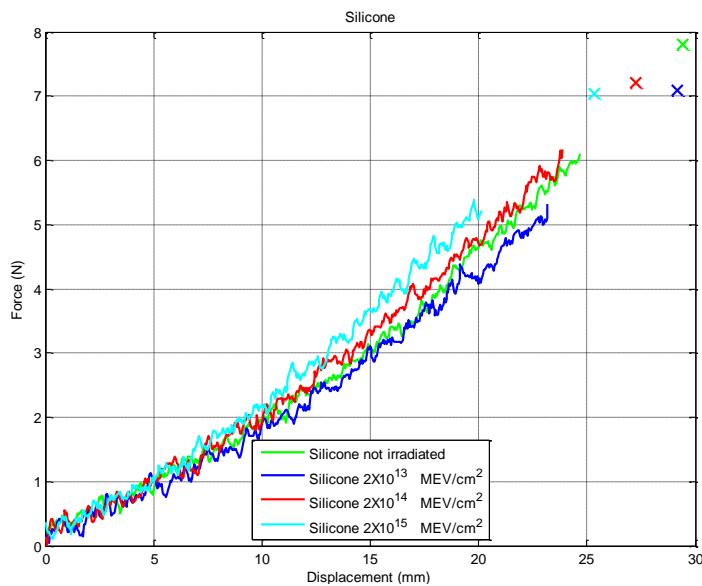

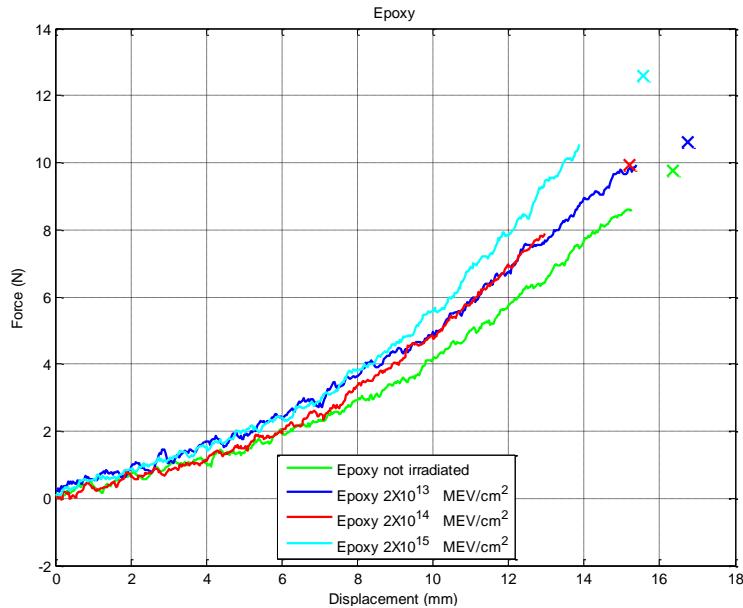

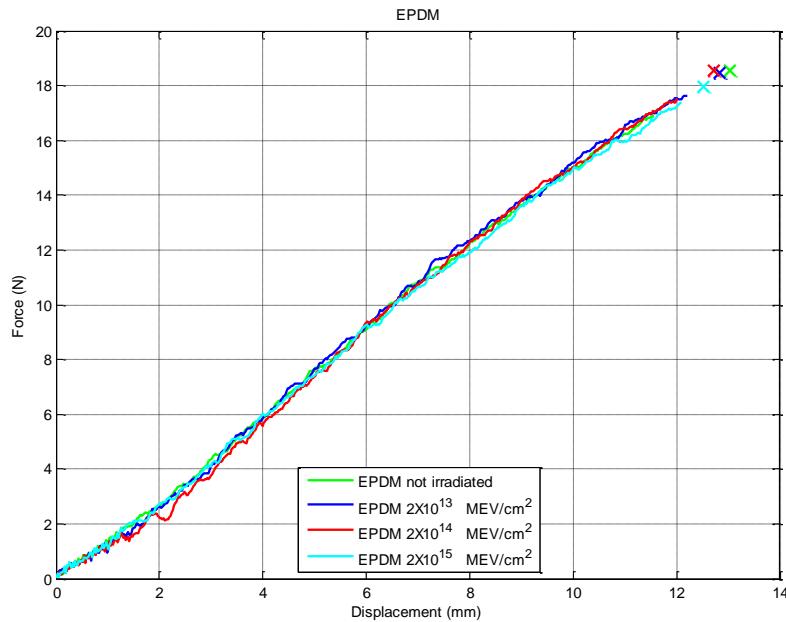

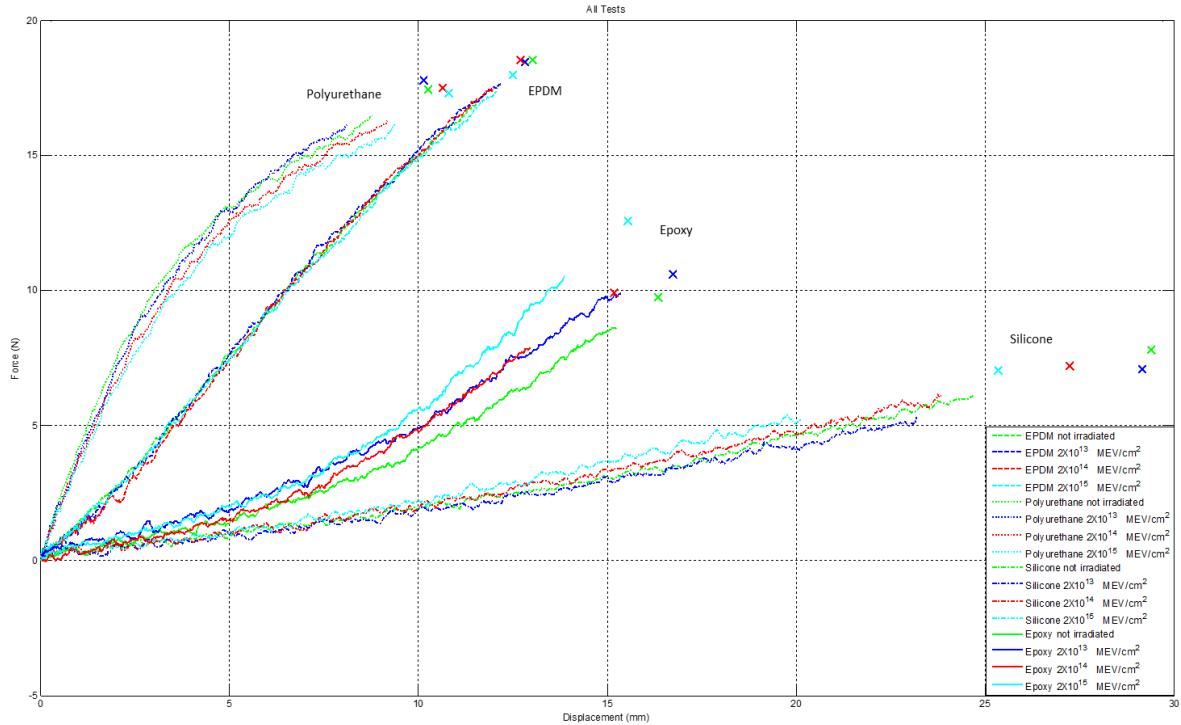

Figure 2.20: Direct bonding infra-red images of wafer processed inside the EPFL cleanroom and bonded by CSEM.