# **Data acquisition for an SiPM based muon detector**

Von der Fakultät für Mathematik, Informatik und Naturwissenschaften der

RWTH Aachen University zur Erlangung des akademischen Grades eines

Doktors der Naturwissenschaften genehmigte Dissertation

vorgelegt von

**Lukas Middendorf

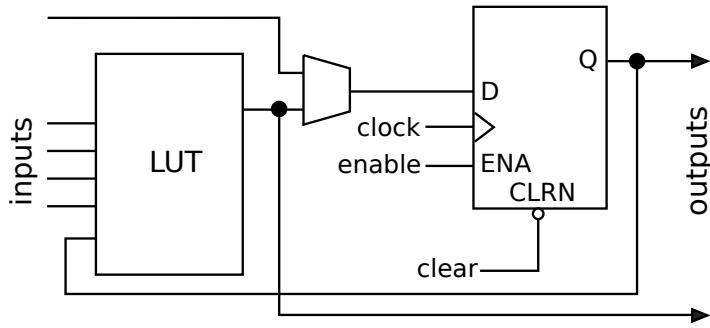

M.Sc. RWTH**

aus

**Bocholt**

Berichter: Univ.-Prof. Dr. rer. nat. Thomas Hebbeker

apl. Prof. Dr. rer. nat. Stefan Roth

Tag der mündlichen Prüfung: 29.05.2018

Diese Dissertation ist auf den Internetseiten der Universitätsbibliothek verfügbar.

# Abstract

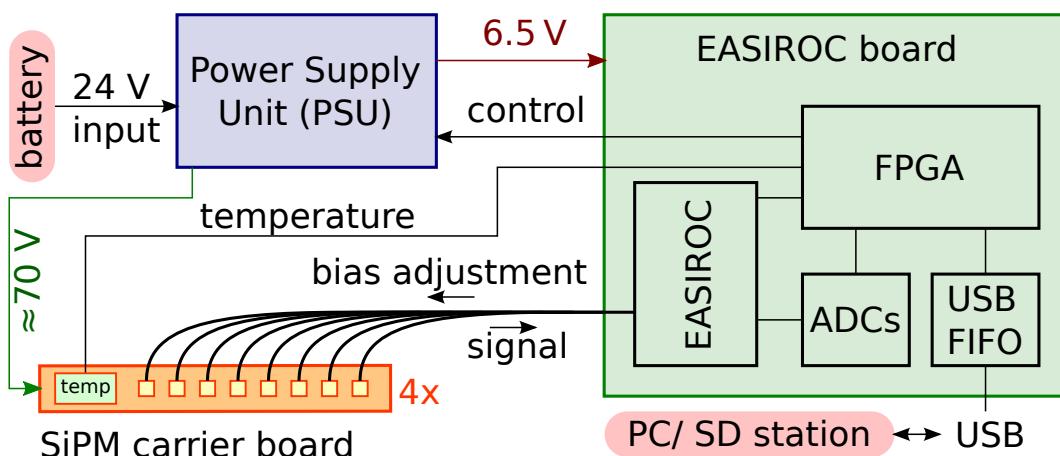

To measure cosmic rays at the highest energies, ground based detectors sparsely covering an area of several thousand square kilometers to detect cosmic ray induced air showers are used. One of those experiments is the Pierre Auger Observatory, which is currently being upgraded for a better determination of the muonic component in the showers to allow a better identification of the type of primary particle. For this upgrade multiple different detector concepts and designs were proposed. One of those proposals is the Aachen Muon Detector (AMD), which is a tiled scintillator detector with silicon photomultipliers (SiPMs) as light sensors. To digitize the SiPM signals the EASIROC chip is used, which allows to read out 32 SiPMs and adjusting of their supply voltage with a low power consumption. The complete readout electronics, including the power supply unit as well as the firmware and software needed for operation, are described in this thesis. Furthermore, characterization measurements of the electronics and first measurements with the detector system are presented.

# Zusammenfassung

Um die kosmische Strahlung bei den höchsten Energien zu messen, werden boden-gestützte Detektoren verwendet. Sie decken Flächen von einigen tausend Quadratkilometern ab, um durch kosmische Strahlung induzierte Luftschaue zu detektieren. Eines dieser Experimente ist das Pierre Auger-Observatorium, das derzeit für eine bessere Bestimmung der myonischen Komponente in den Schauern erweitert wird, um eine verbesserte Identifizierung der Art des Primärteilchens zu ermöglichen. Für dieses Upgrade wurden mehrere verschiedene Detektorkonzepte und Designs vorgeschlagen und untersucht. Einer dieser Vorschläge ist der Aachen Muon Detector (AMD), ein kachelbasierter Szintillatordetektor mit Silizium-Photomultipliern (SiPMs) als Lichtsensoren. Zur Digitalisierung der SiPM-Signale wird der EASIROC-Chip verwendet, der es erlaubt, 32 SiPMs auszulesen und deren Versorgungsspannung mit geringem Stromverbrauch anzupassen. In dieser Arbeit wird die komplette Ausleseelektronik des AMD einschließlich der Spannungsversorgung und der für den Betrieb notwendigen Firmware und Software beschrieben. Weiterhin werden Charakterisierungsmessungen der Elektronik und erste Messungen mit dem Detektorsystem vorgestellt.

# Contents

|                                                       |           |

|-------------------------------------------------------|-----------|

| <b>1. Introduction</b>                                | <b>9</b>  |

| <b>2. Cosmic rays</b>                                 | <b>11</b> |

| 2.1. Nature and origin . . . . .                      | 11        |

| 2.1.1. Energy spectrum . . . . .                      | 11        |

| 2.1.2. Production mechanisms . . . . .                | 12        |

| 2.1.3. Source candidates . . . . .                    | 13        |

| 2.1.4. Propagation . . . . .                          | 15        |

| 2.1.5. Composition . . . . .                          | 15        |

| 2.2. Cosmic ray induced air showers . . . . .         | 17        |

| 2.2.1. Hadronic component . . . . .                   | 17        |

| 2.2.2. Electromagnetic component . . . . .            | 19        |

| 2.2.3. Muonic component . . . . .                     | 19        |

| 2.2.4. Neutrino component . . . . .                   | 20        |

| 2.2.5. Detection principles . . . . .                 | 21        |

| 2.2.5.1. Fluorescence light detection . . . . .       | 21        |

| 2.2.5.2. Particle detection at ground level . . . . . | 21        |

| 2.2.5.3. Radio detection . . . . .                    | 22        |

| 2.2.5.4. Hybrid approaches . . . . .                  | 22        |

| <b>3. The Pierre Auger Observatory</b>                | <b>23</b> |

| 3.1. The Surface Detector . . . . .                   | 23        |

| 3.2. The Fluorescence Detector . . . . .              | 25        |

| 3.3. Existing enhancements and upgrades . . . . .     | 28        |

| 3.3.1. AMIGA . . . . .                                | 28        |

| 3.3.2. HEAT . . . . .                                 | 28        |

| 3.3.3. AERA . . . . .                                 | 28        |

| 3.4. AugerPrime . . . . .                             | 29        |

| 3.4.1. Upgrade of the SD electronics . . . . .        | 29        |

| 3.4.2. Proposals for a new muon detector . . . . .    | 30        |

| 3.4.3. SSD . . . . .                                  | 30        |

| <b>4. Scintillators for particle detection</b>        | <b>33</b> |

| 4.1. Plastic scintillators . . . . .                  | 35        |

| 4.2. Photon collection and detection . . . . .        | 36        |

| 4.3. Wrapping of scintillators . . . . .              | 37        |

|                                                             |           |

|-------------------------------------------------------------|-----------|

| <b>5. Silicon Photomultipliers – SiPMs</b>                  | <b>39</b> |

| 5.1. Structure . . . . .                                    | 39        |

| 5.1.1. Readout . . . . .                                    | 42        |

| 5.2. Characteristics . . . . .                              | 43        |

| 5.2.1. Pulse form and time behavior . . . . .               | 43        |

| 5.2.2. Photon detection efficiency . . . . .                | 43        |

| 5.2.3. Gain . . . . .                                       | 44        |

| 5.2.4. Noise phenomena . . . . .                            | 44        |

| 5.2.4.1. Dark noise . . . . .                               | 44        |

| 5.2.4.2. Crosstalk . . . . .                                | 45        |

| 5.2.4.3. Afterpulsing . . . . .                             | 45        |

| 5.2.5. Dynamic range . . . . .                              | 46        |

| 5.2.6. Temperature dependence . . . . .                     | 46        |

| 5.3. Comparison to other photon detection methods . . . . . | 47        |

| <b>6. FPGAs</b>                                             | <b>49</b> |

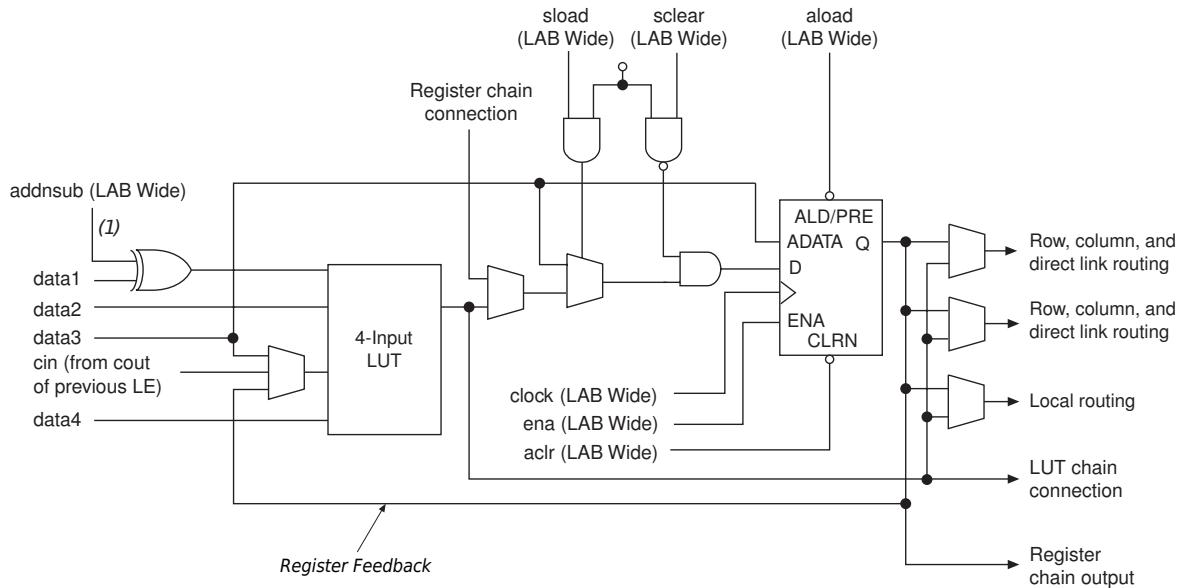

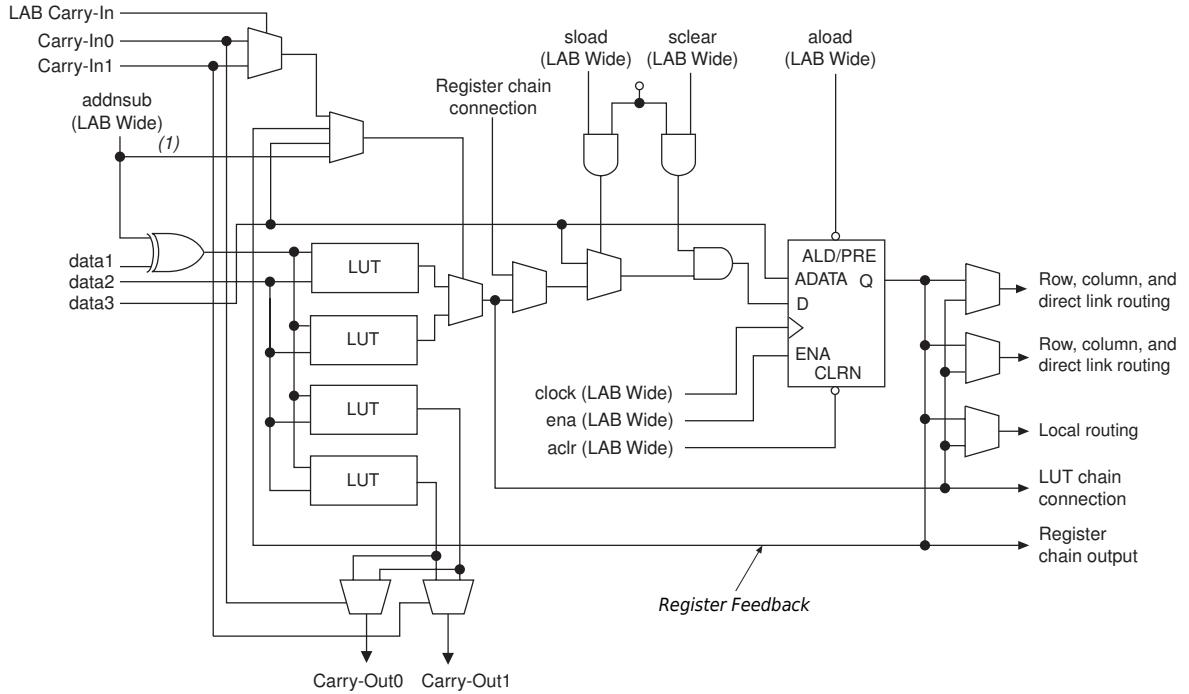

| 6.1. Hardware . . . . .                                     | 49        |

| 6.1.1. Altera Cyclone family . . . . .                      | 51        |

| 6.2. Configuration . . . . .                                | 54        |

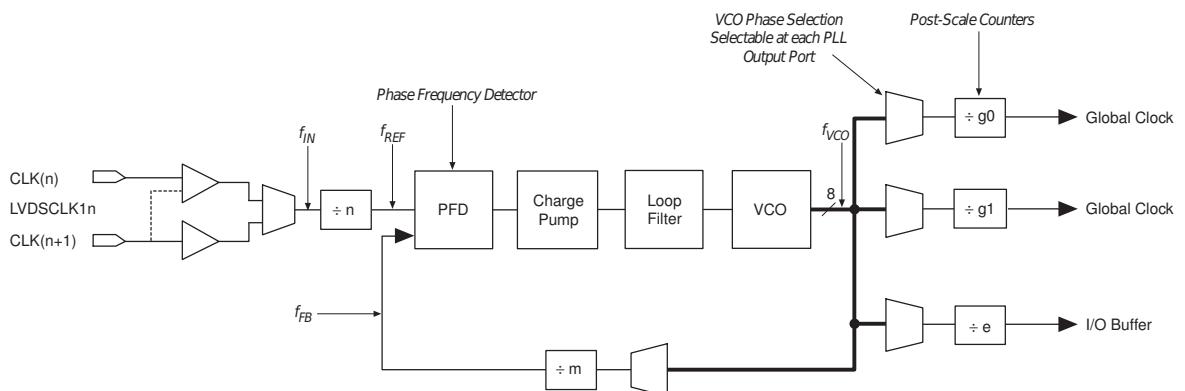

| 6.2.1. Timing . . . . .                                     | 55        |

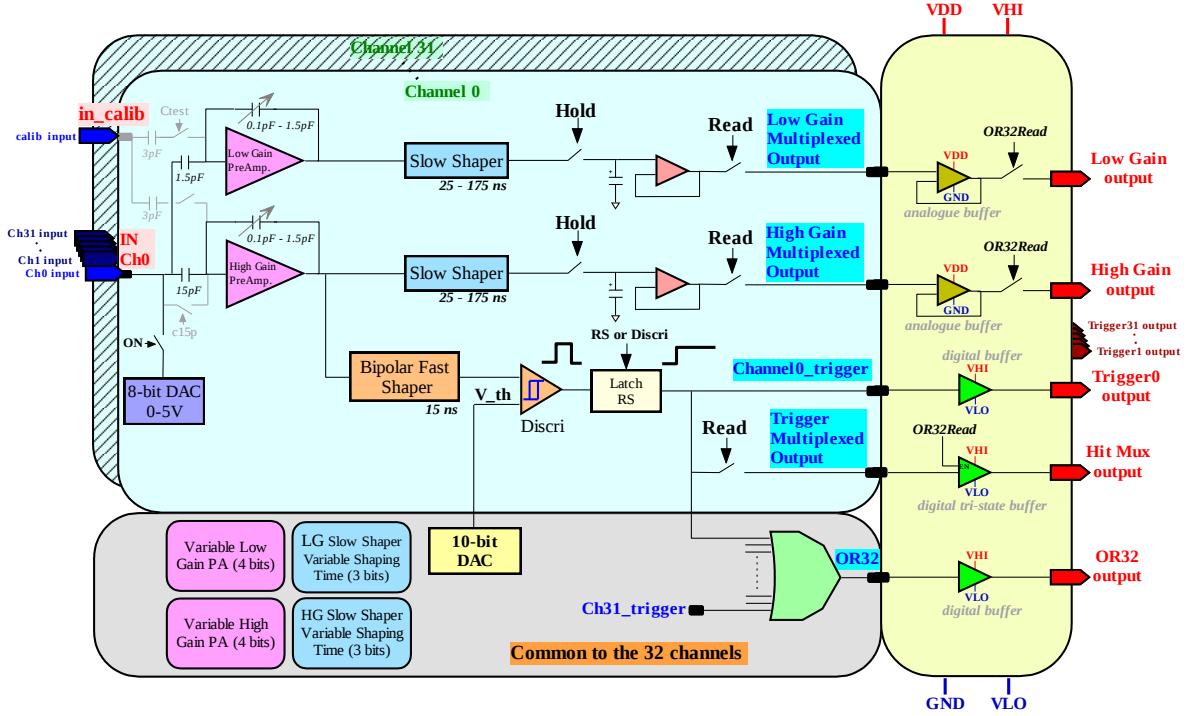

| <b>7. The EASIROC ASIC for SiPM readout</b>                 | <b>57</b> |

| <b>8. The Aachen Muon Detector – AMD</b>                    | <b>61</b> |

| 8.1. Motivation . . . . .                                   | 61        |

| 8.2. Detector concept . . . . .                             | 61        |

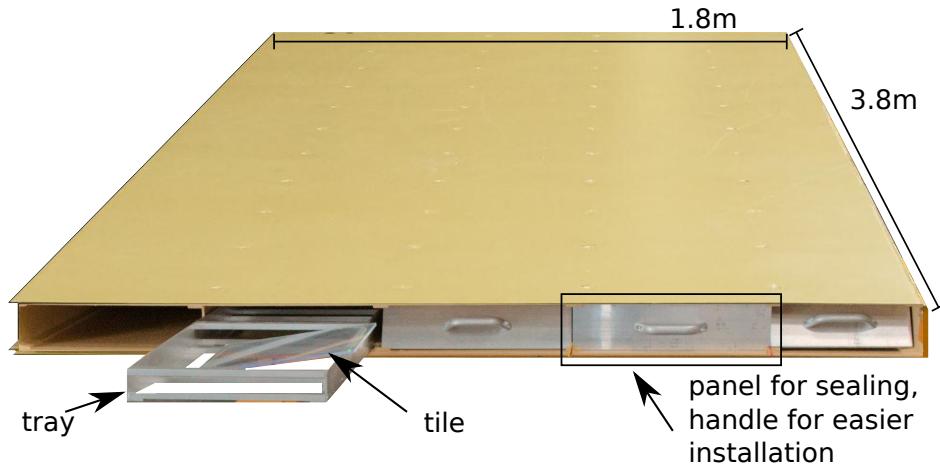

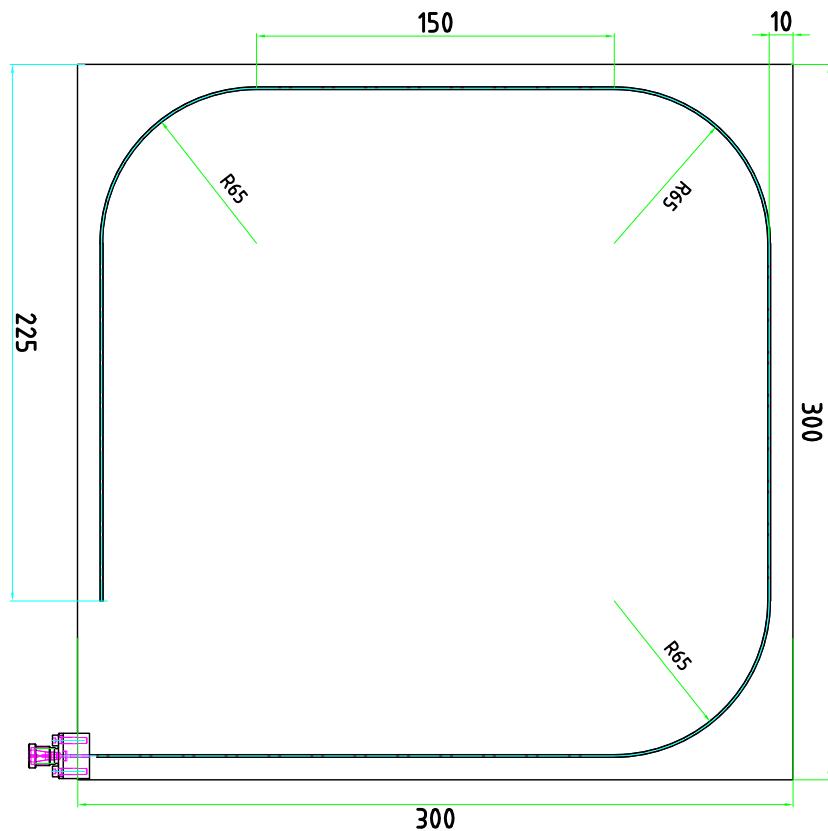

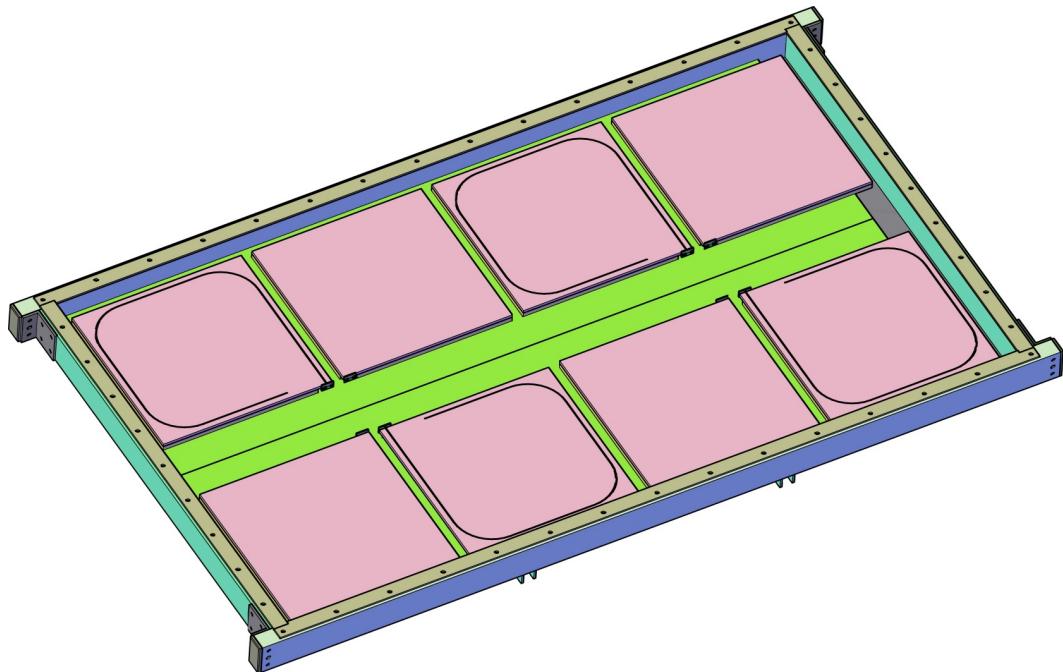

| 8.3. Mechanical description . . . . .                       | 63        |

| 8.4. DAQ . . . . .                                          | 66        |

| 8.5. (Expected) performance . . . . .                       | 66        |

| 8.6. Applications of AMD technology . . . . .               | 68        |

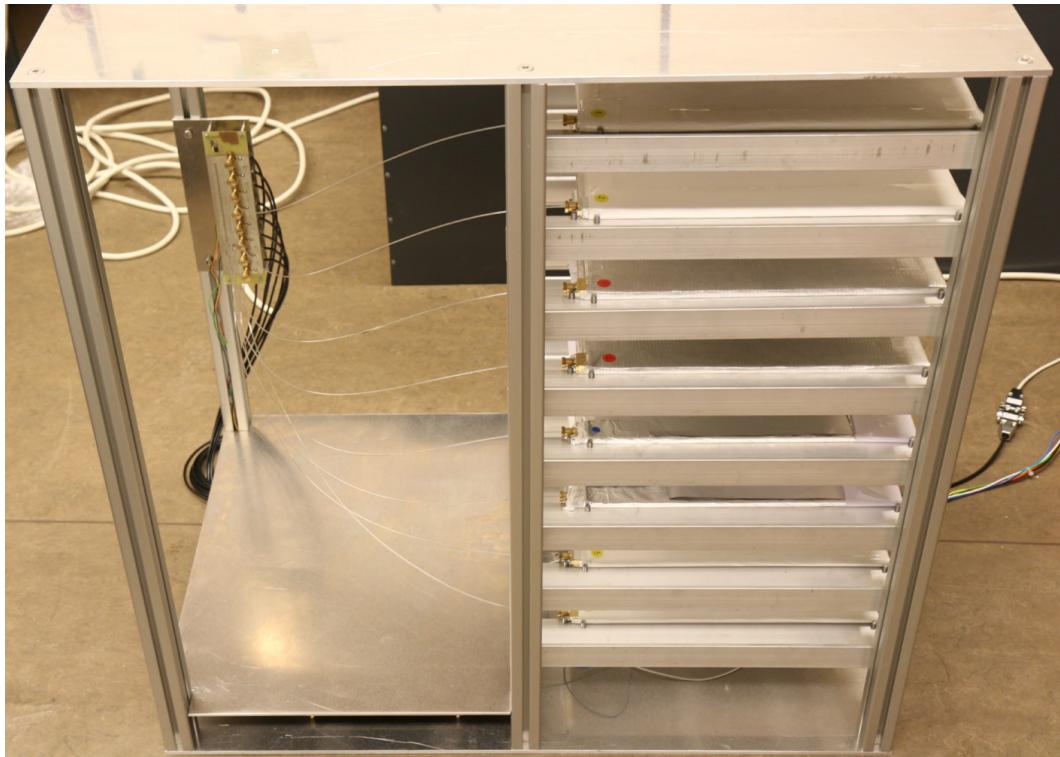

| 8.6.1. The AMD tile container . . . . .                     | 68        |

| 8.6.2. The AMD shelf . . . . .                              | 69        |

| 8.6.3. AMD tiles as muon trigger . . . . .                  | 71        |

| 8.6.4. MiniAMD . . . . .                                    | 71        |

| <b>9. The DAQ of the AMD</b>                                | <b>73</b> |

| 9.1. Hardware . . . . .                                     | 73        |

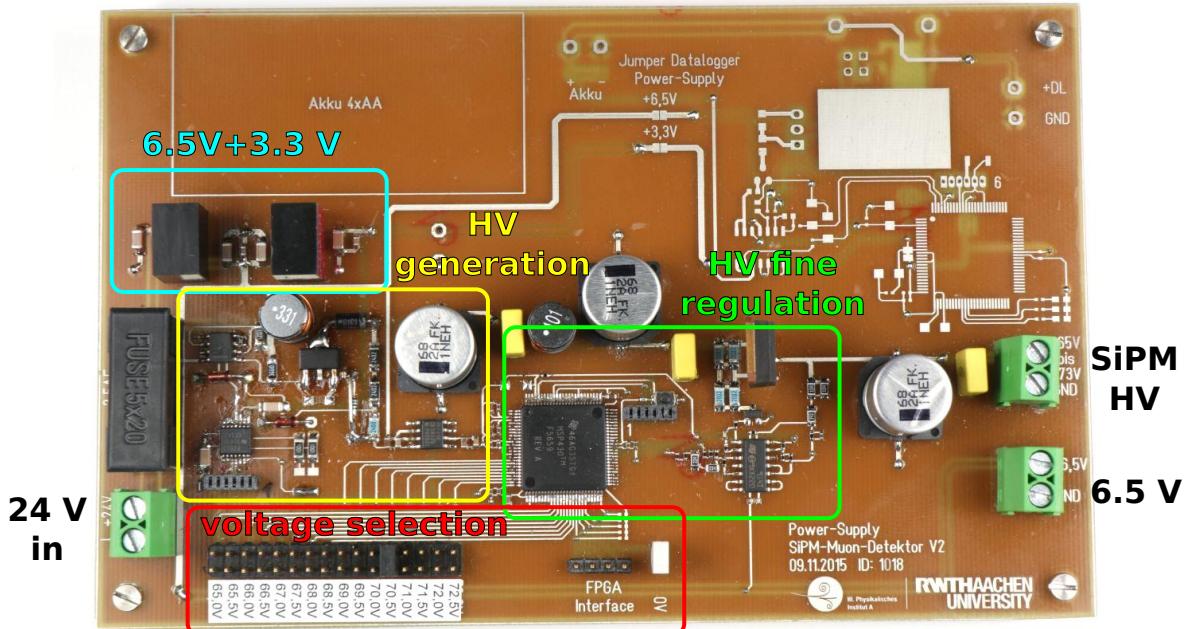

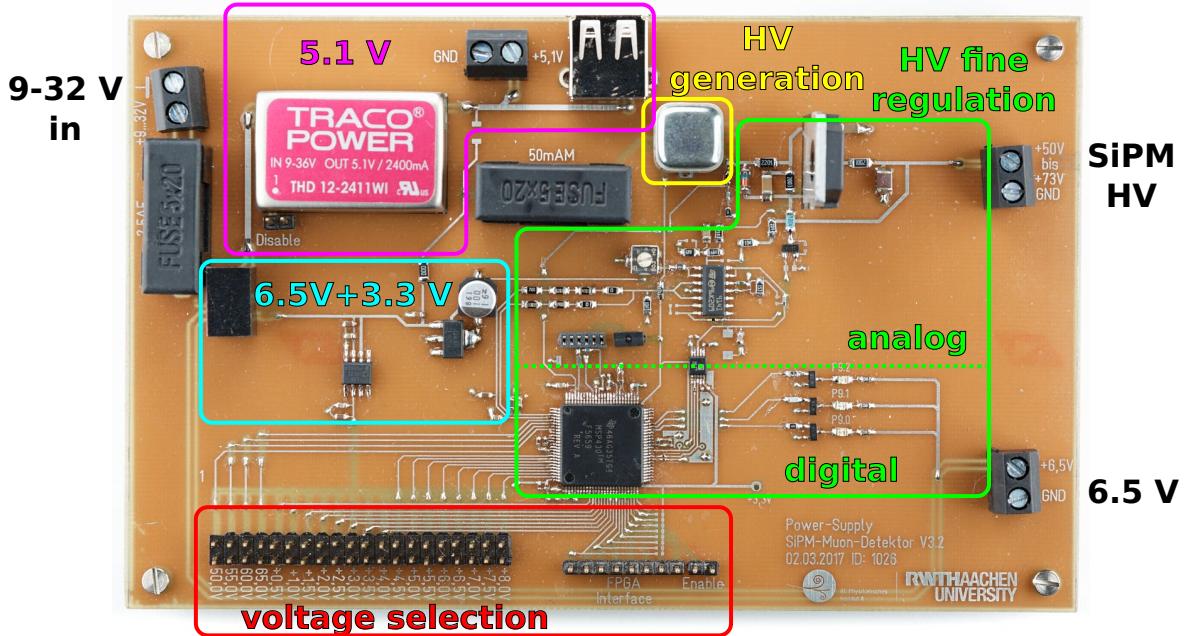

| 9.1.1. The Power Supply Unit – PSU . . . . .                | 74        |

| 9.1.1.1. Version 1 . . . . .                                | 74        |

| 9.1.1.2. Version 2 . . . . .                                | 75        |

| 9.1.1.3. Version 3 . . . . .                                | 78        |

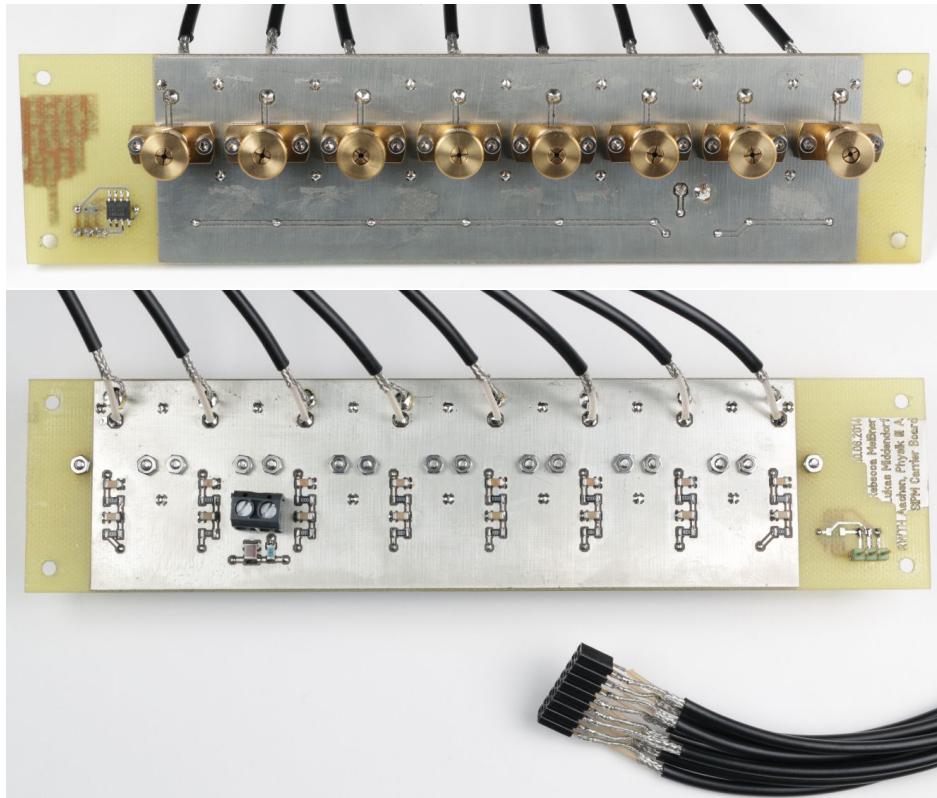

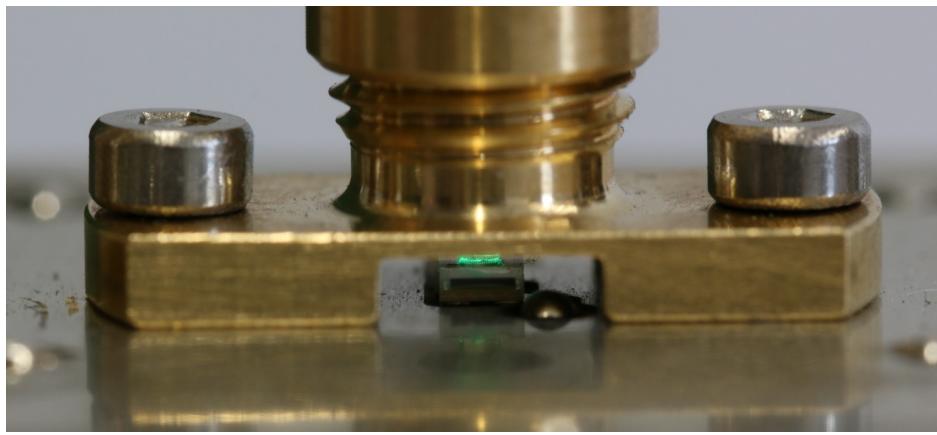

| 9.1.2. SiPM carrier board . . . . .                         | 80        |

| 9.1.2.1. SiPM carrier board for the MiniAMD . . . . .       | 81        |

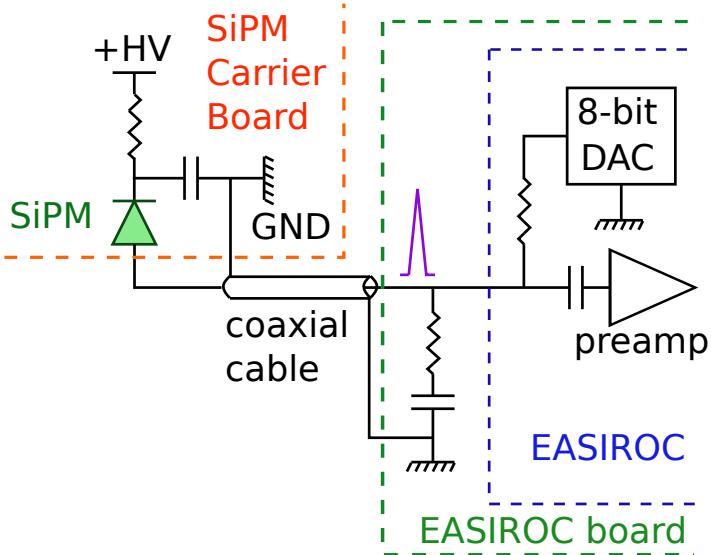

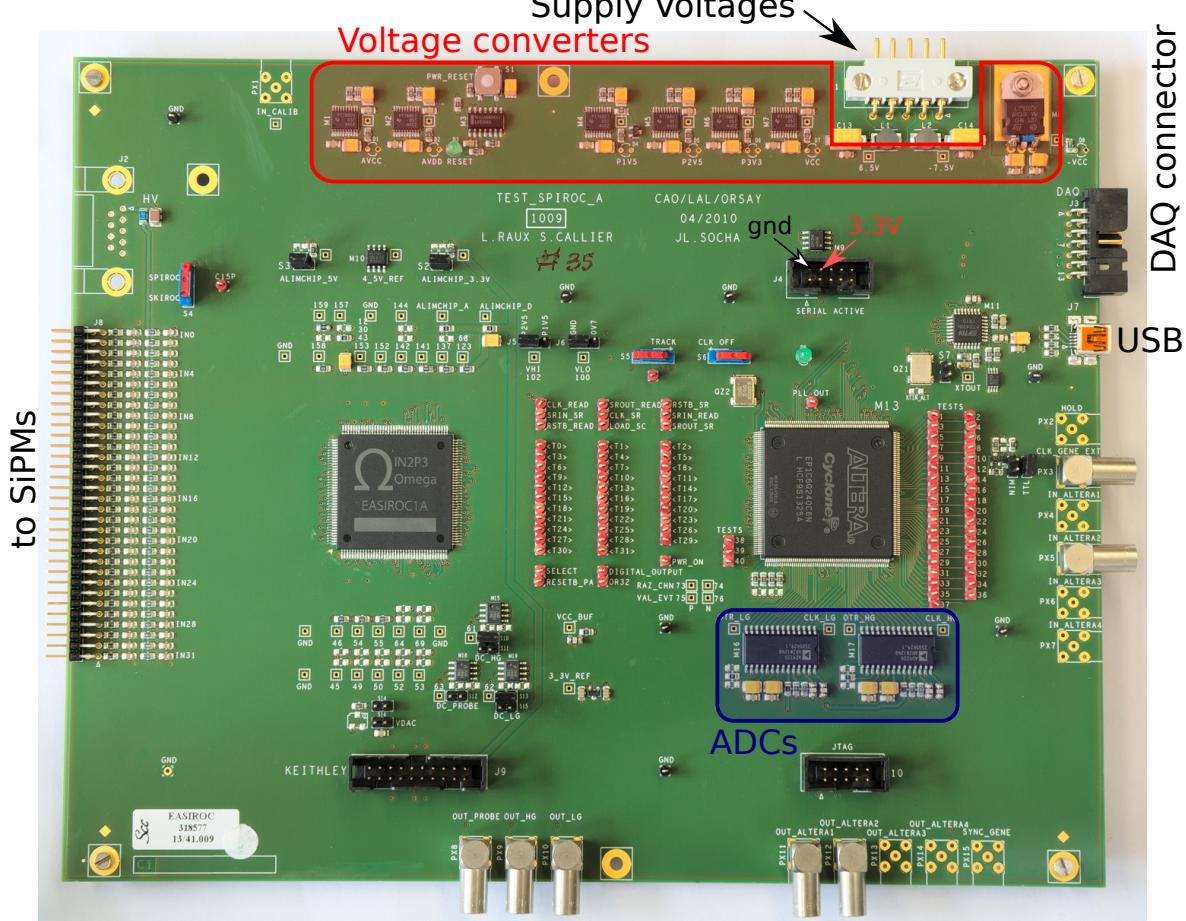

| 9.1.3. EASIROC board . . . . .                              | 83        |

|            |                                                                 |            |

|------------|-----------------------------------------------------------------|------------|

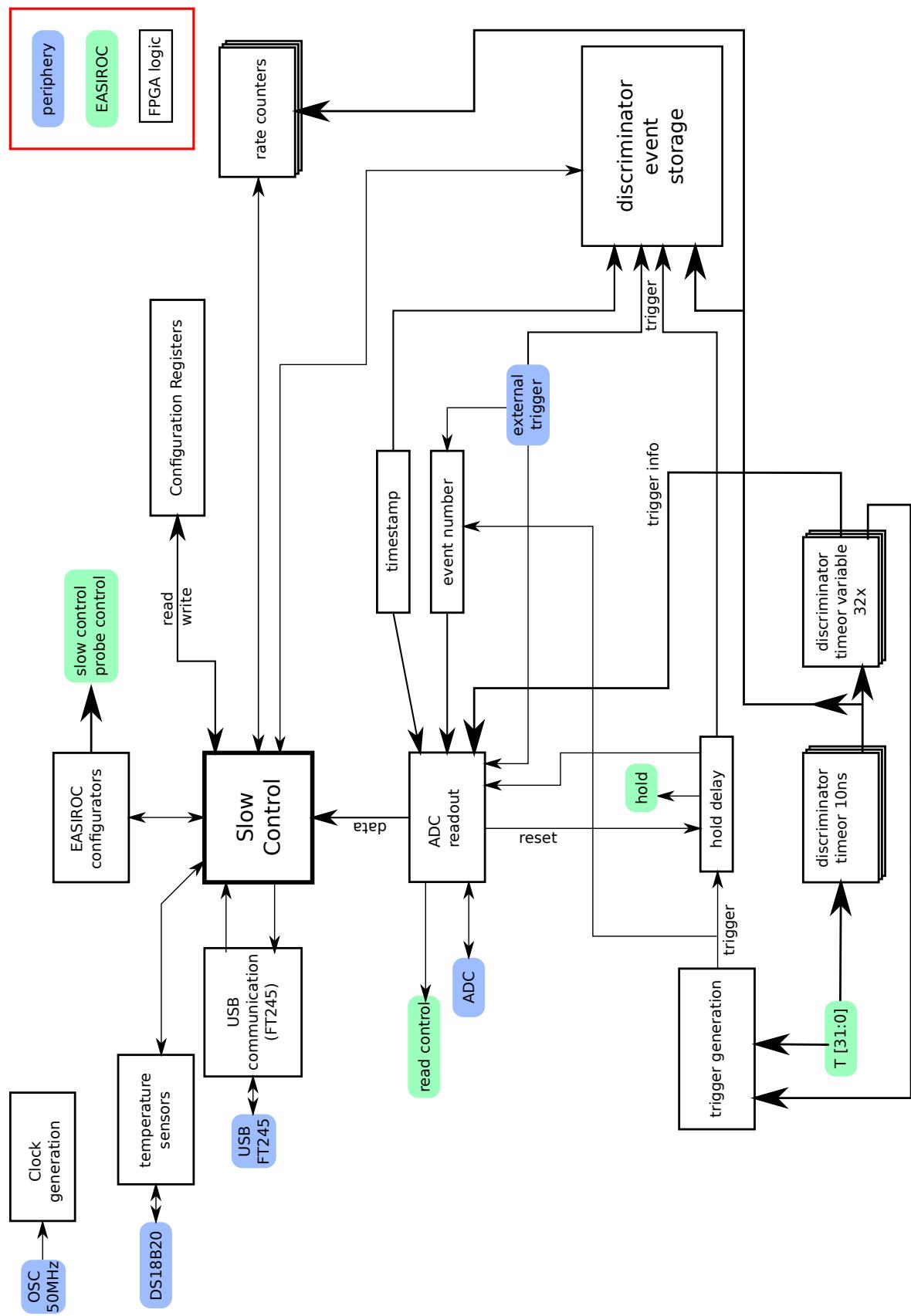

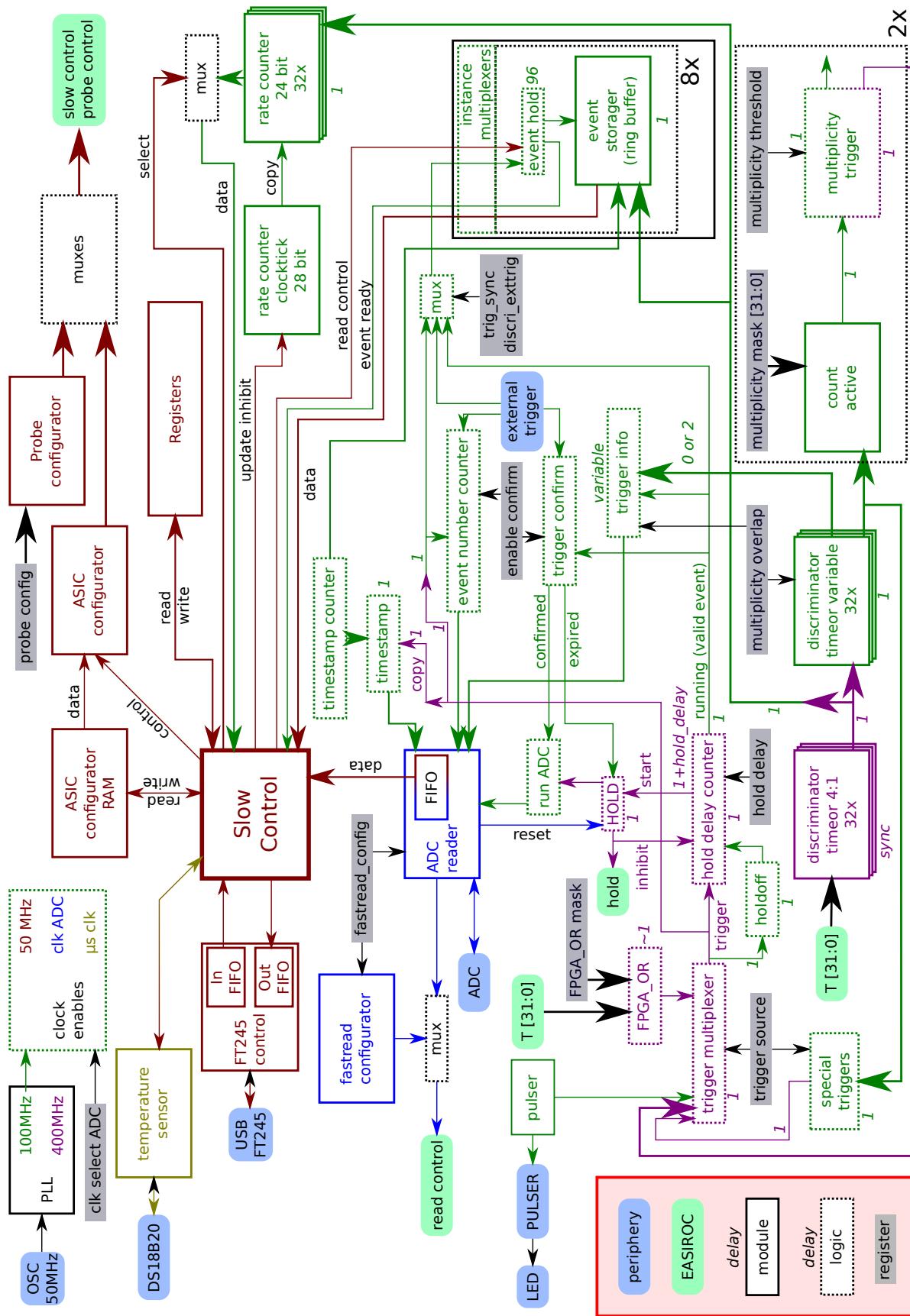

| 9.2.       | Firmware                                                        | 86         |

| 9.2.1.     | General structure                                               | 86         |

| 9.2.2.     | Clock system                                                    | 90         |

| 9.2.3.     | Communication via USB                                           | 91         |

| 9.2.3.1.   | The high level communication protocol                           | 92         |

| 9.2.3.2.   | The slow control module                                         | 96         |

| 9.2.4.     | Configuration of the firmware functions                         | 96         |

| 9.2.5.     | Configuration of the EASIROC                                    | 97         |

| 9.2.6.     | Temperature sensors                                             | 98         |

| 9.2.7.     | Discriminator input handling                                    | 99         |

| 9.2.8.     | Single channel trigger rates measurement                        | 100        |

| 9.2.9.     | Event trigger handling                                          | 101        |

| 9.2.10.    | Event number                                                    | 103        |

| 9.2.11.    | Timestamp                                                       | 103        |

| 9.2.12.    | ADC readout                                                     | 104        |

| 9.2.12.1.  | ADC event structure                                             | 104        |

| 9.2.13.    | Time trace of discriminator status                              | 105        |

| 9.2.14.    | Timing constraints                                              | 106        |

| 9.2.15.    | Reset logic                                                     | 107        |

| 9.2.16.    | Other functionality                                             | 108        |

| 9.3.       | Software                                                        | 108        |

| 9.3.1.     | The LibLAB                                                      | 109        |

| 9.3.2.     | Driver for communication with the firmware                      | 110        |

| 9.3.3.     | Measurement programs                                            | 110        |

| 9.3.3.1.   | The shelf program                                               | 110        |

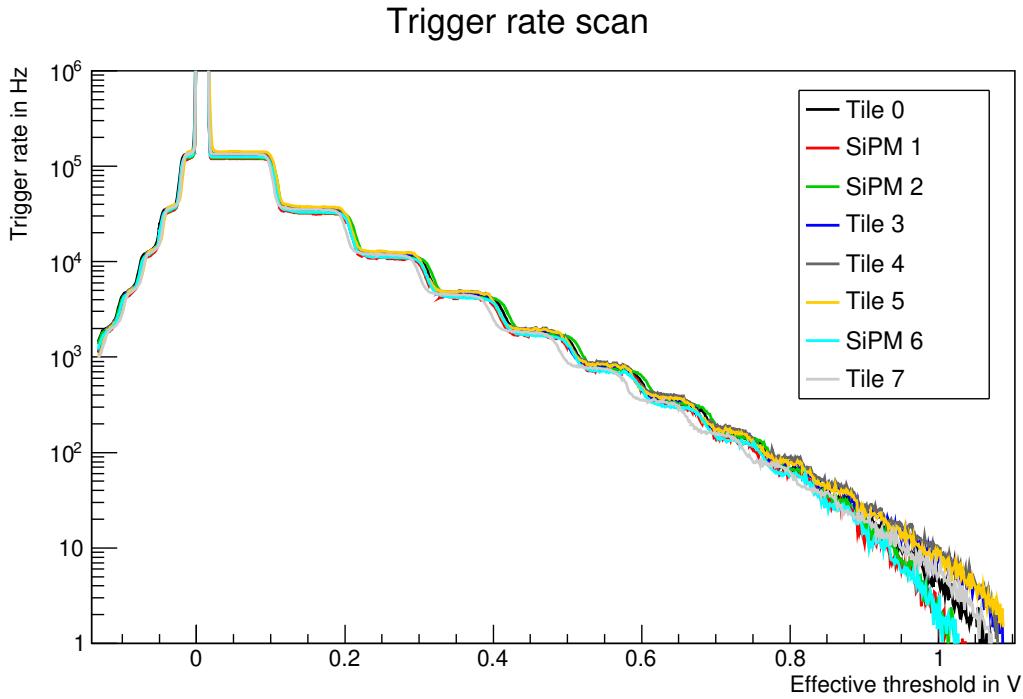

| 9.3.3.2.   | Trigger rate scan                                               | 113        |

| 9.4.       | Further plans                                                   | 114        |

| <b>10.</b> | <b>First characterization measurements with the AMD</b>         | <b>117</b> |

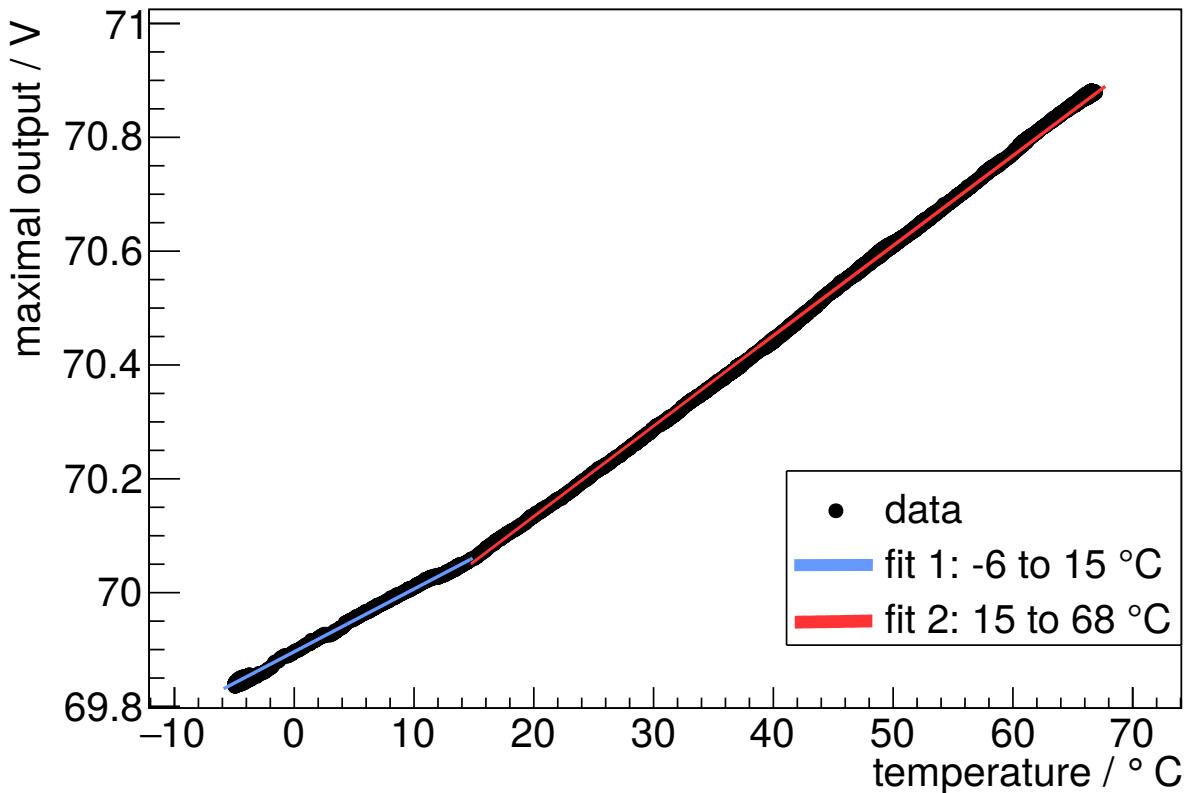

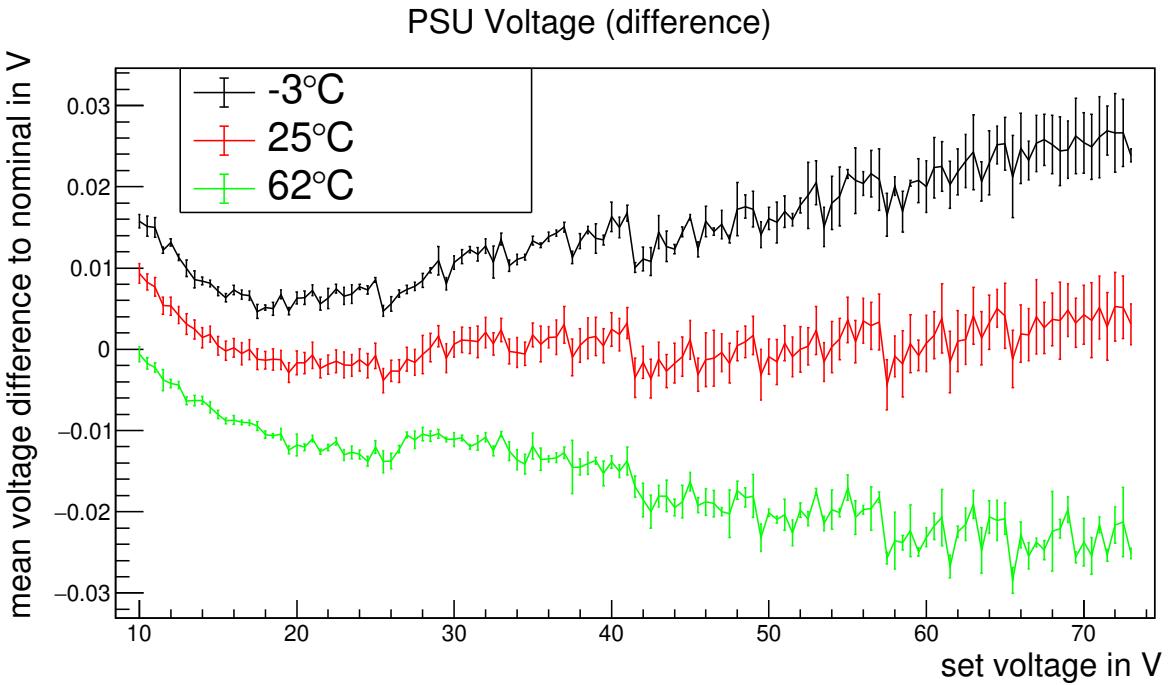

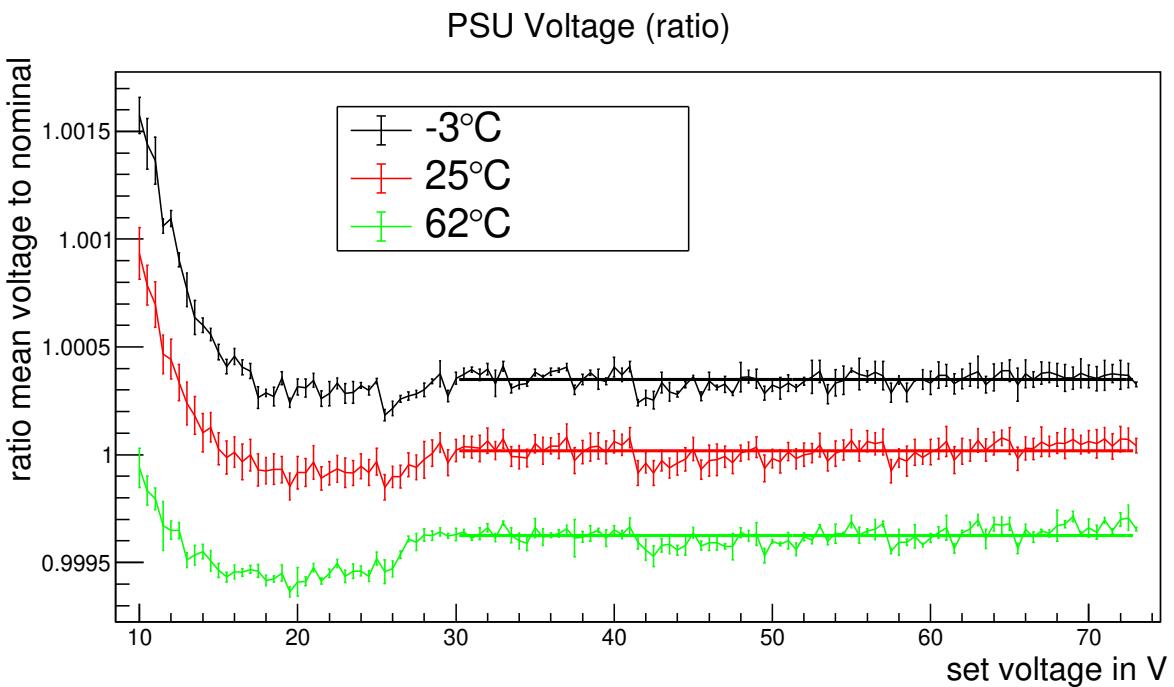

| 10.1.      | Characterization of the Power Supply                            | 118        |

| 10.2.      | Characterization of the EASIROC ASIC                            | 123        |

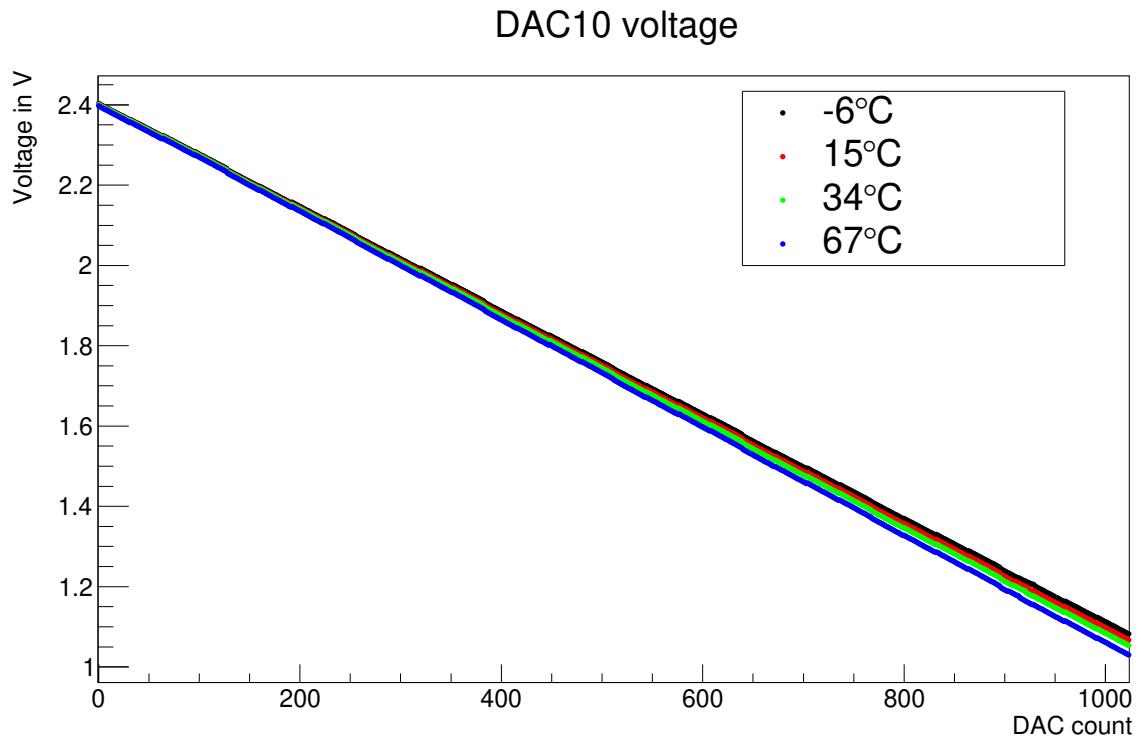

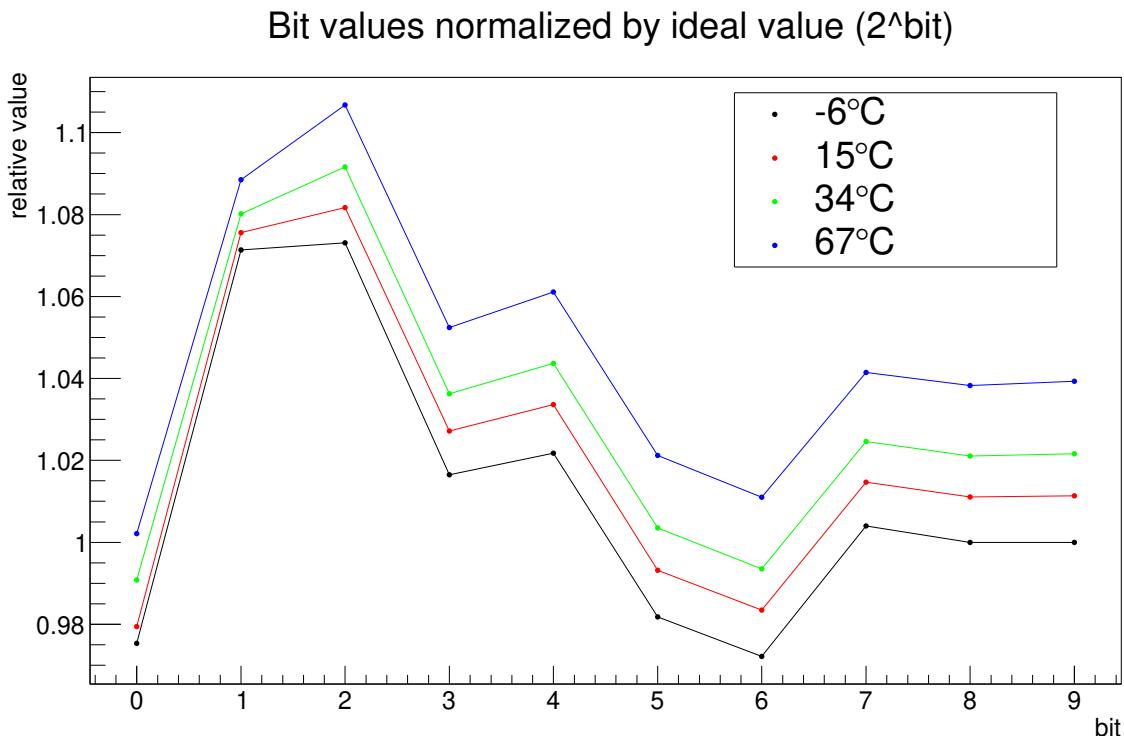

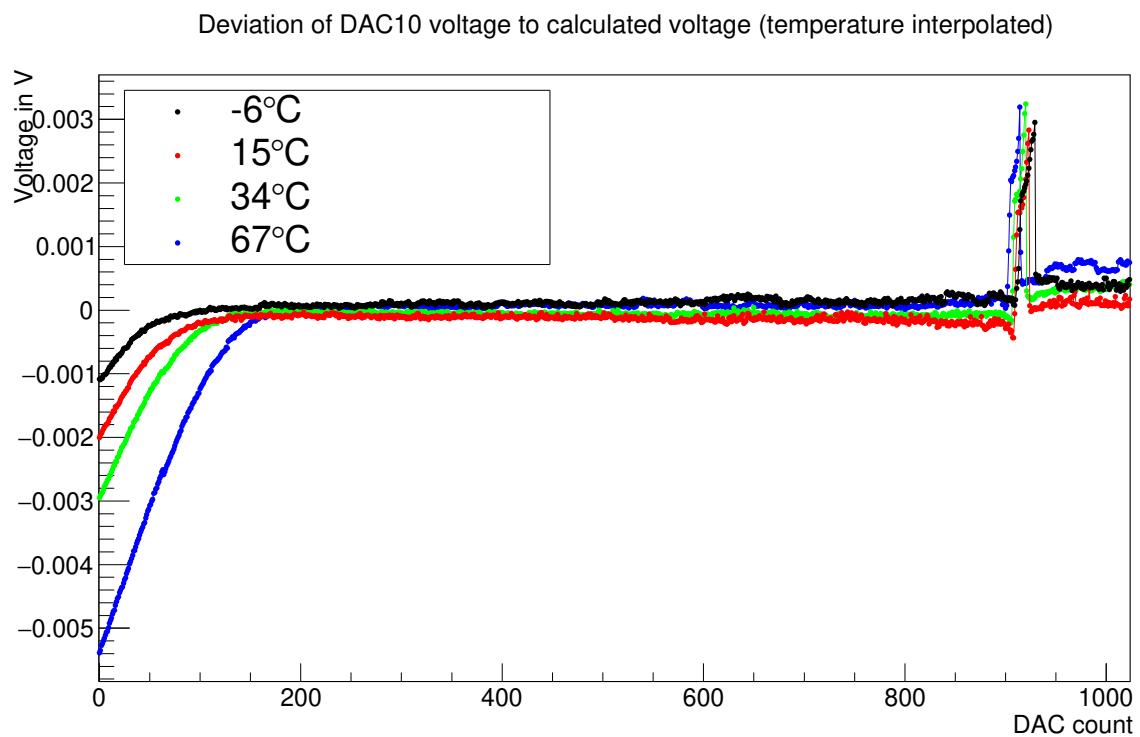

| 10.2.1.    | Characterization of DACs                                        | 123        |

| 10.2.2.    | Input DACs                                                      | 125        |

| 10.2.3.    | Threshold DAC and discriminators                                | 127        |

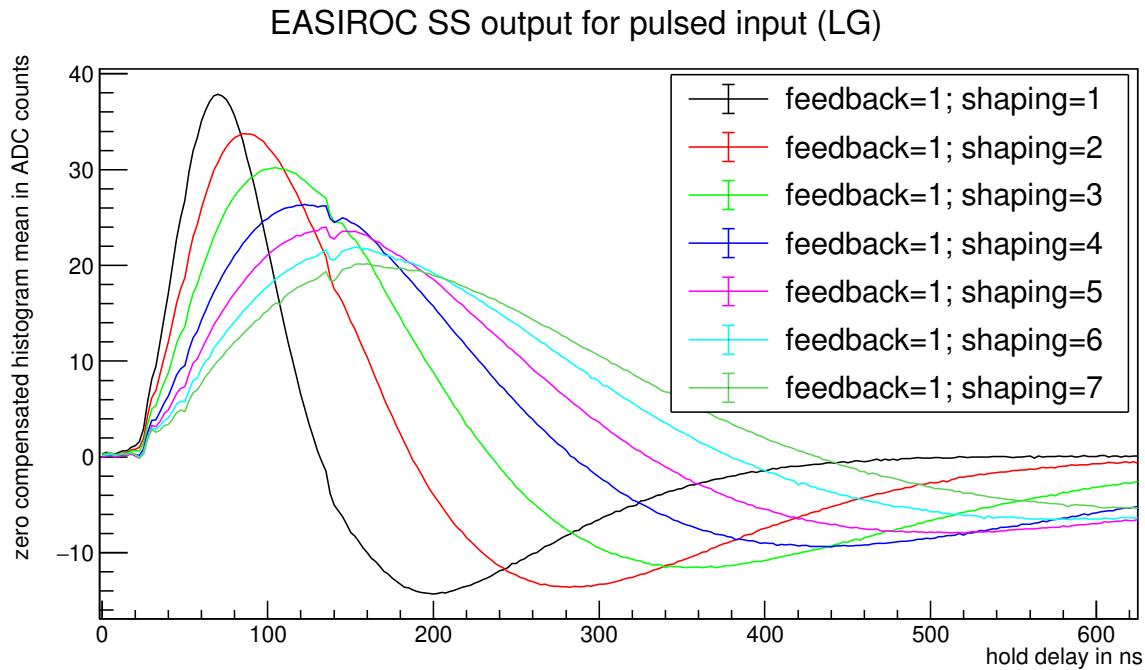

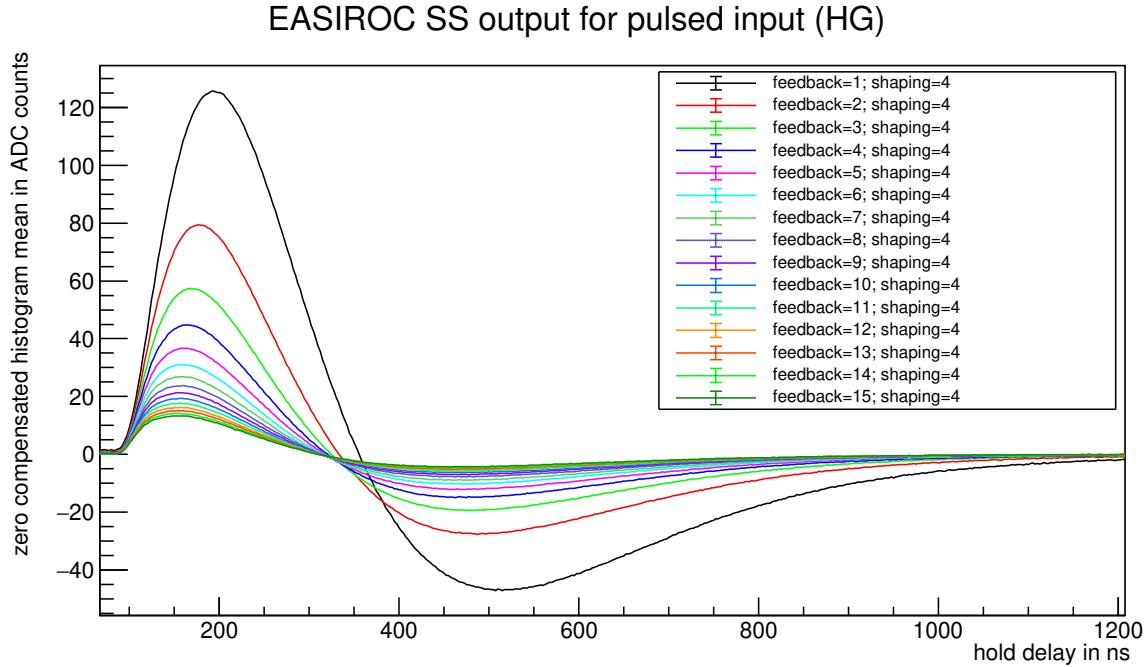

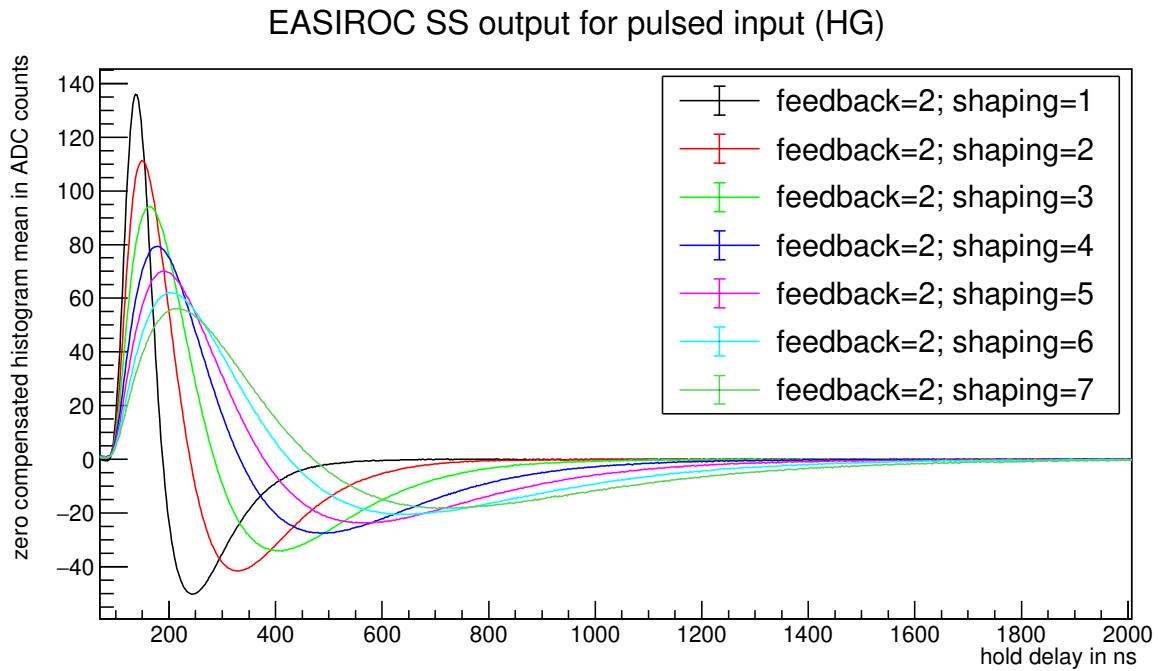

| 10.2.4.    | Slow Shapers                                                    | 131        |

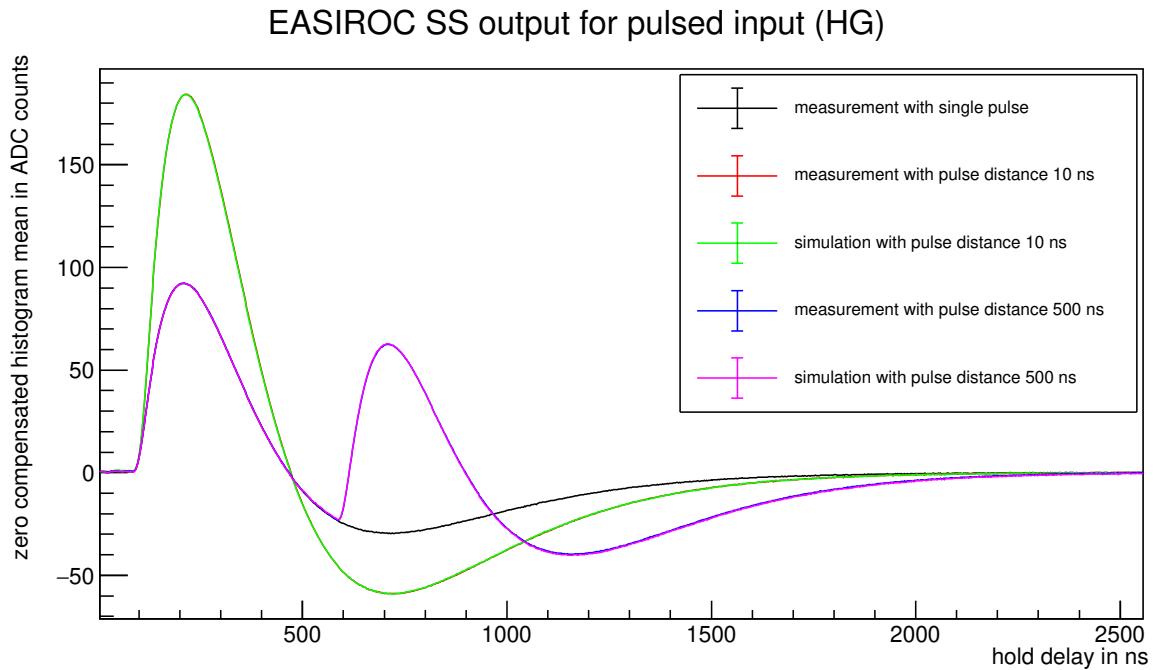

| 10.2.4.1.  | Shaper electronics simulation model                             | 136        |

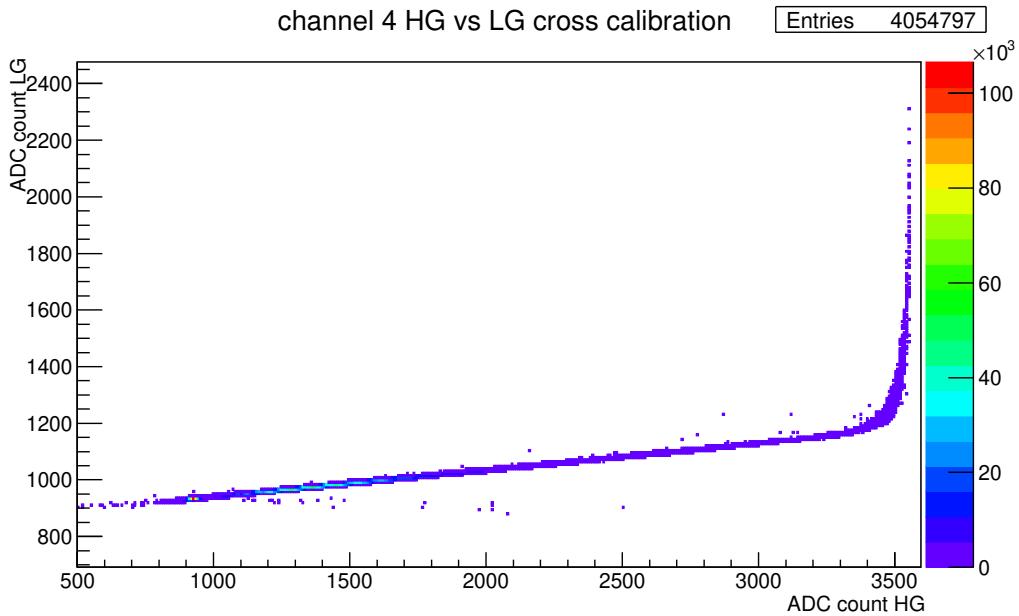

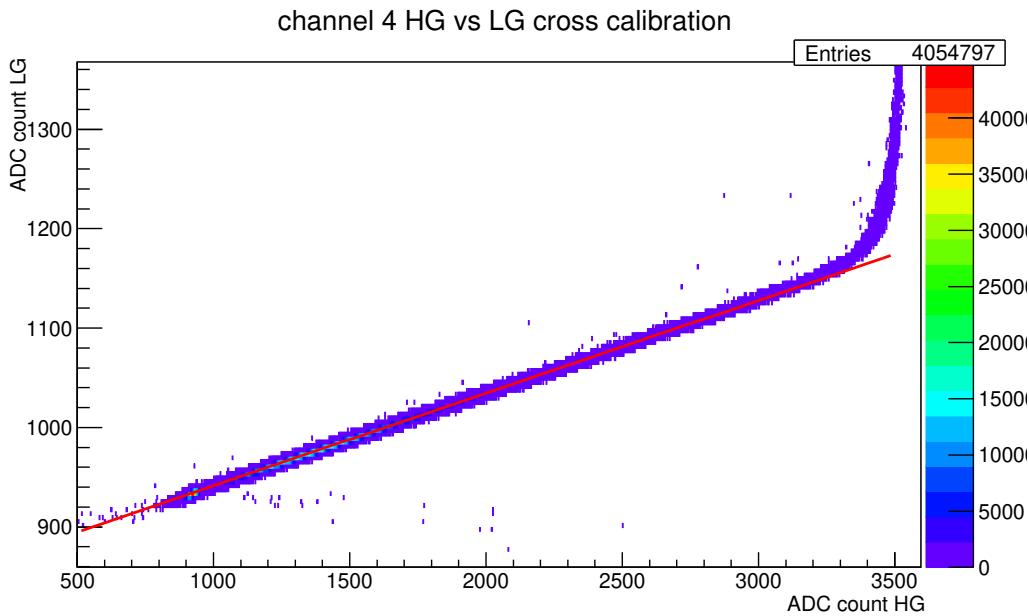

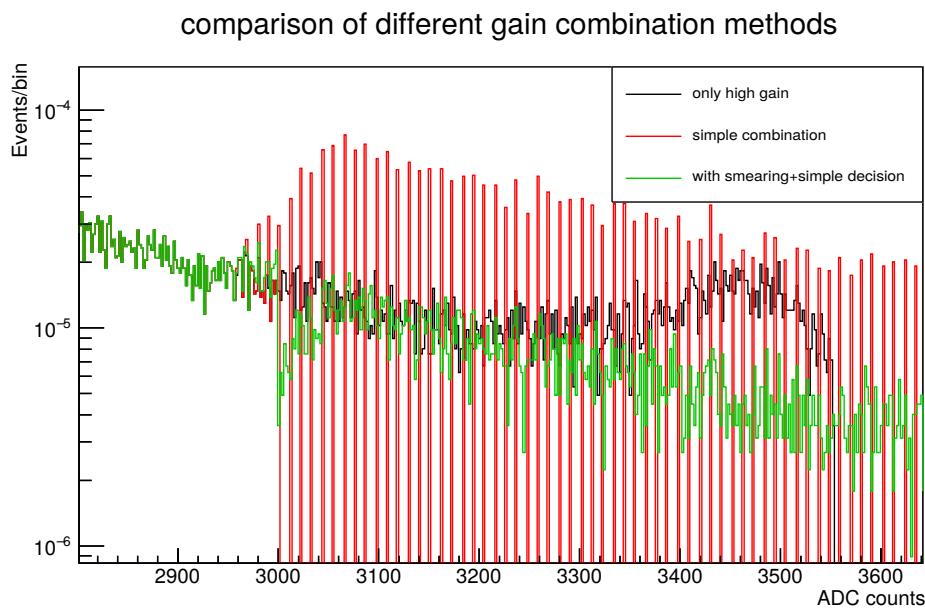

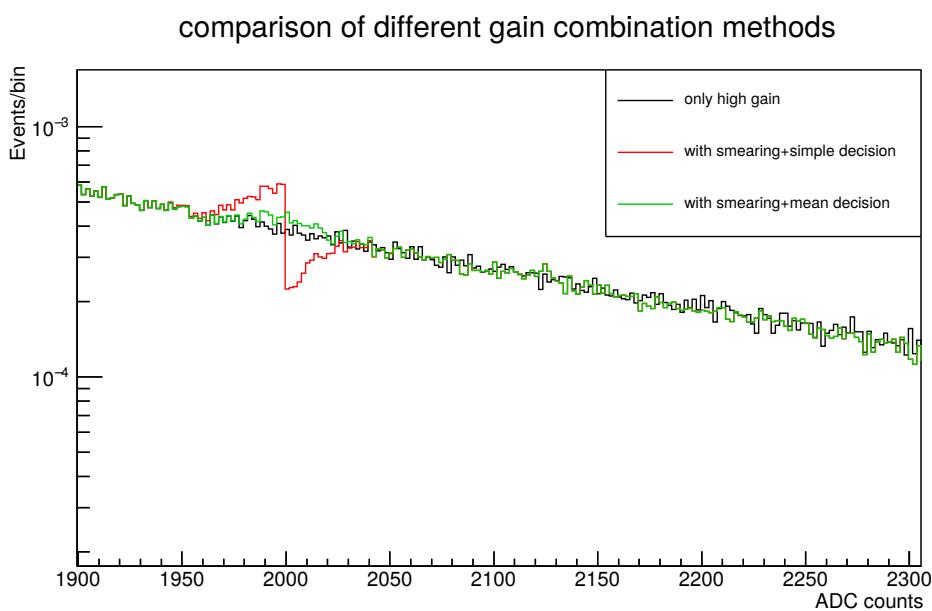

| 10.2.4.2.  | High-gain - Low-gain cross calibration                          | 137        |

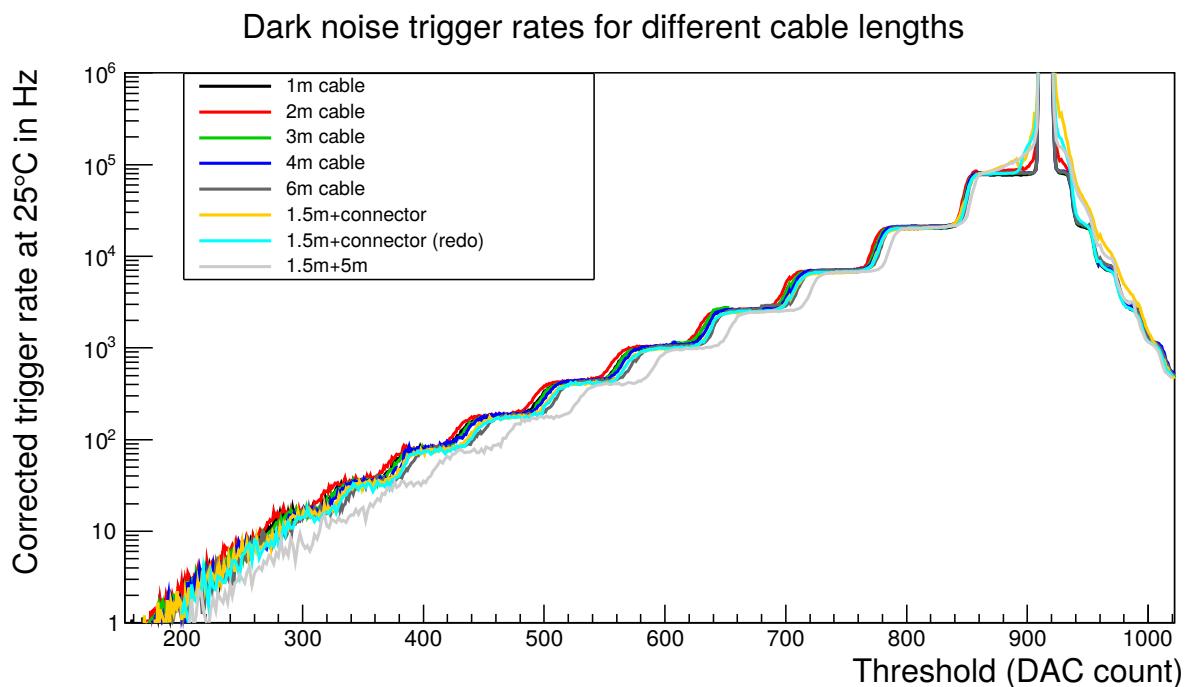

| 10.2.5.    | Study of different signal cable lengths                         | 140        |

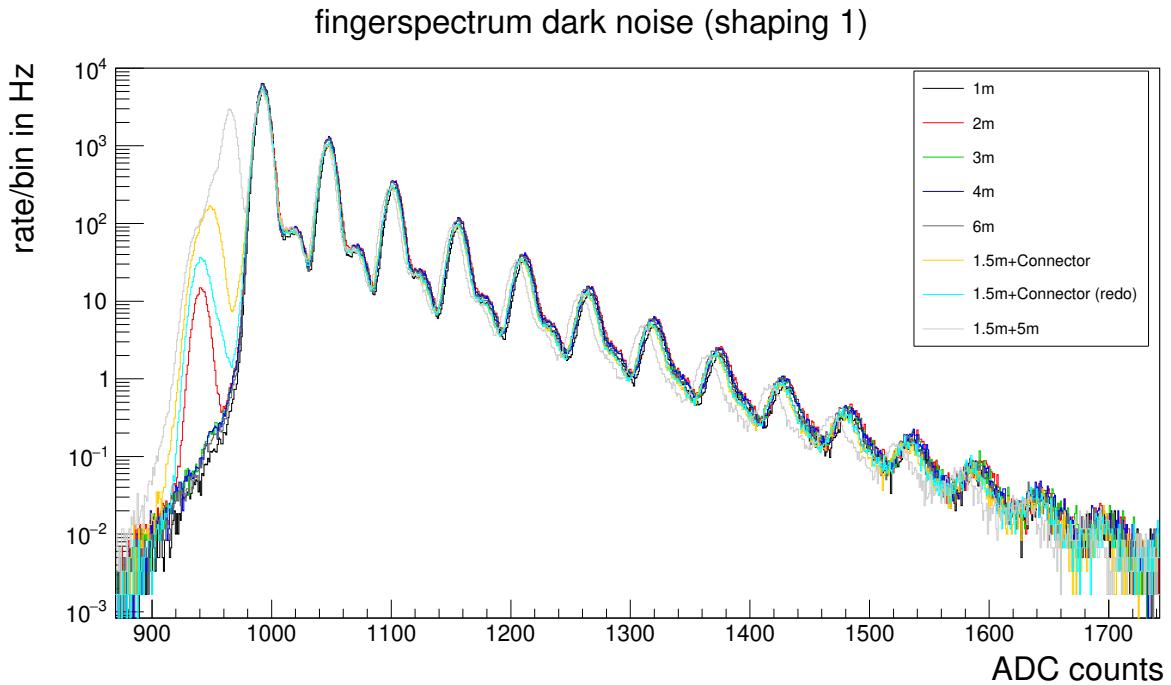

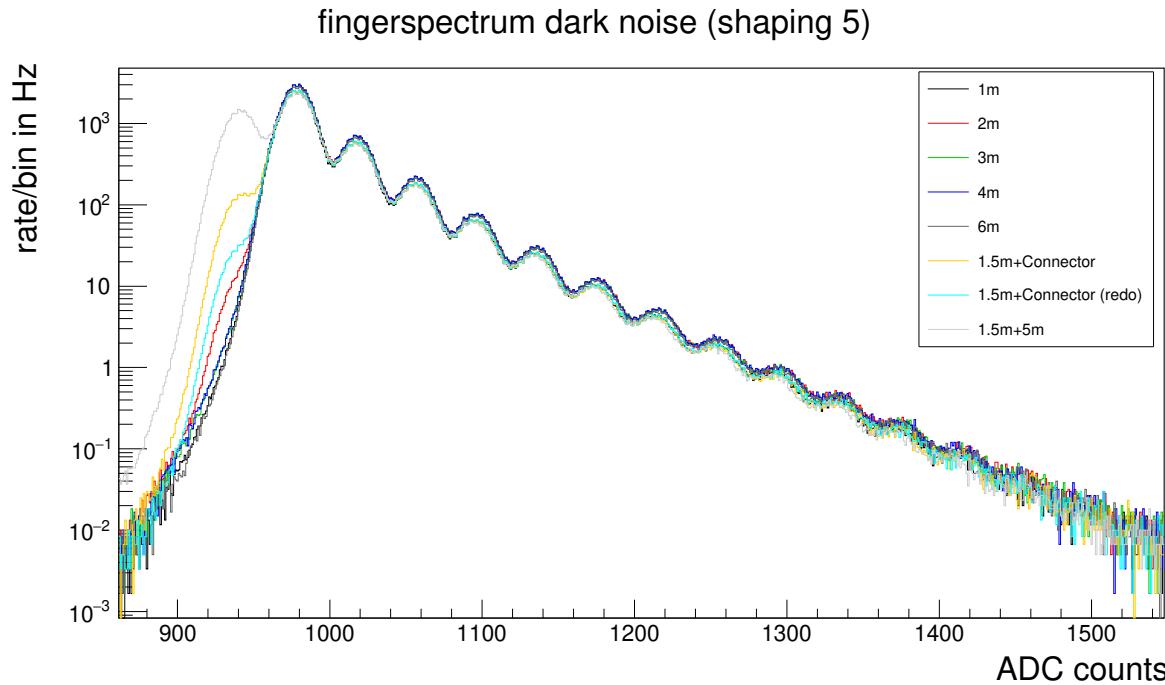

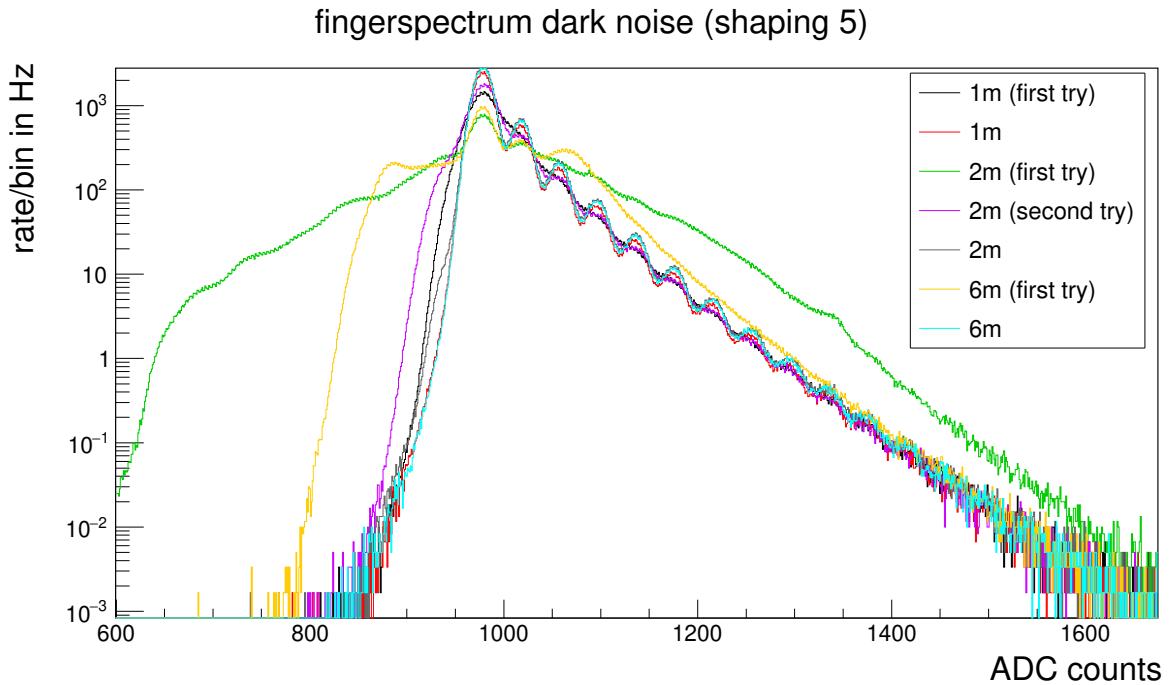

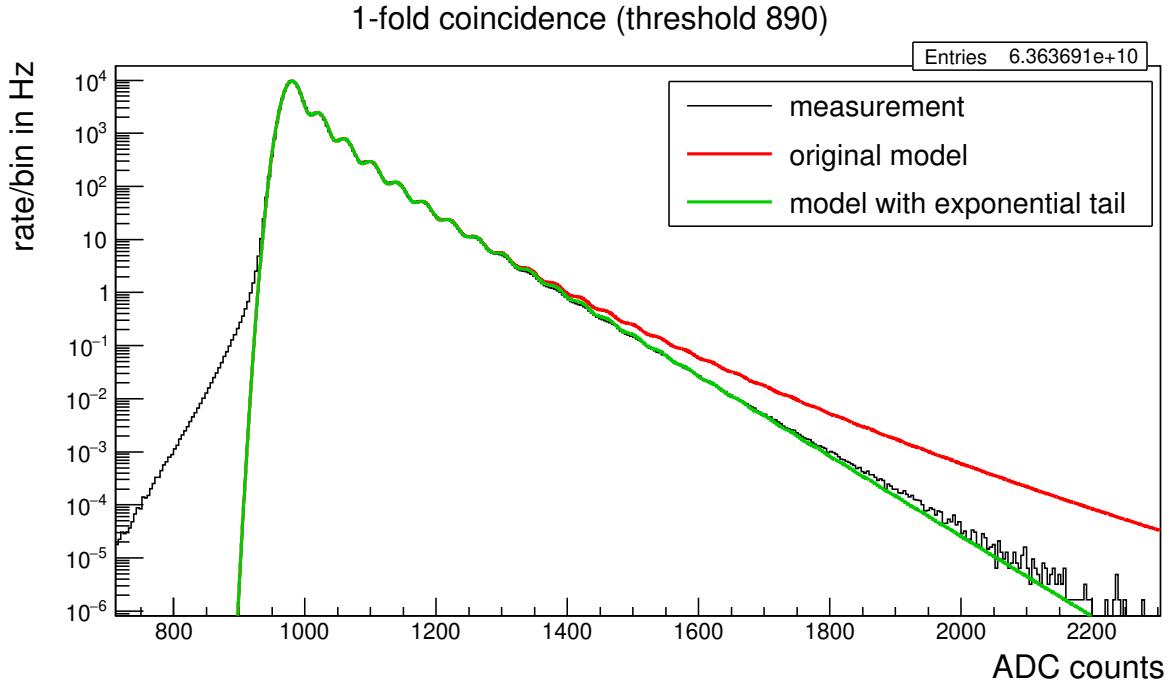

| 10.2.6.    | SiPM dark noise spectrum                                        | 147        |

| 10.3.      | Measurement of atmospheric muons with an AMD test configuration | 150        |

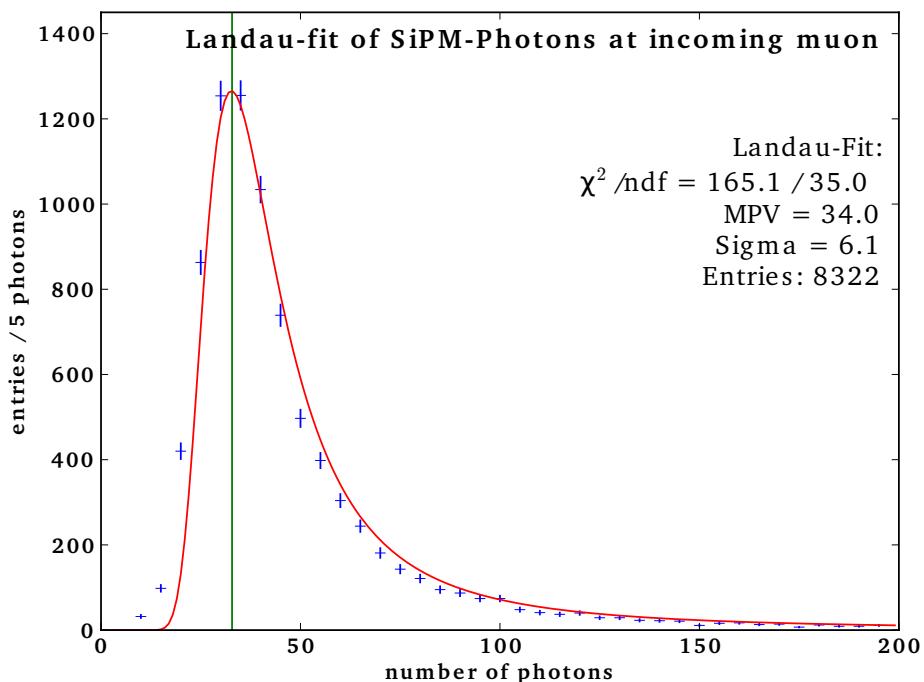

| 10.3.1.    | Photon yield of the AMD tiles                                   | 152        |

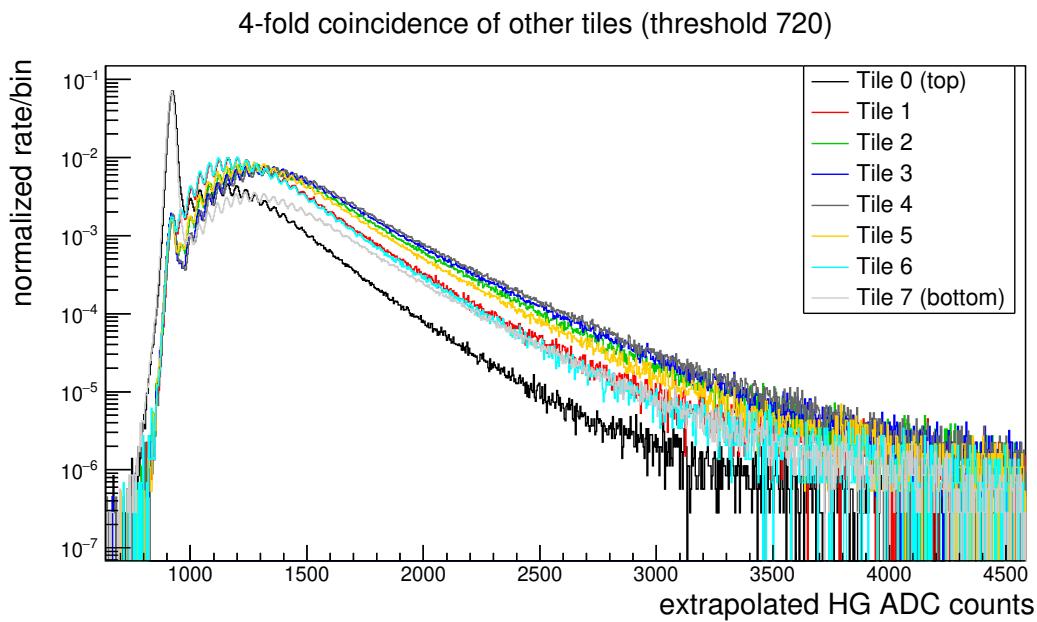

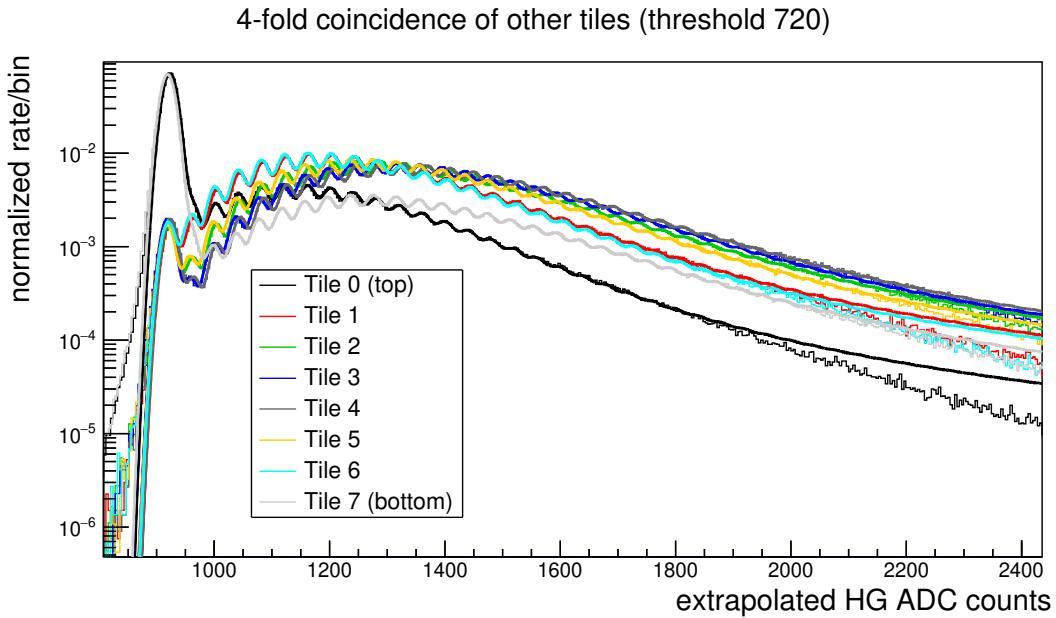

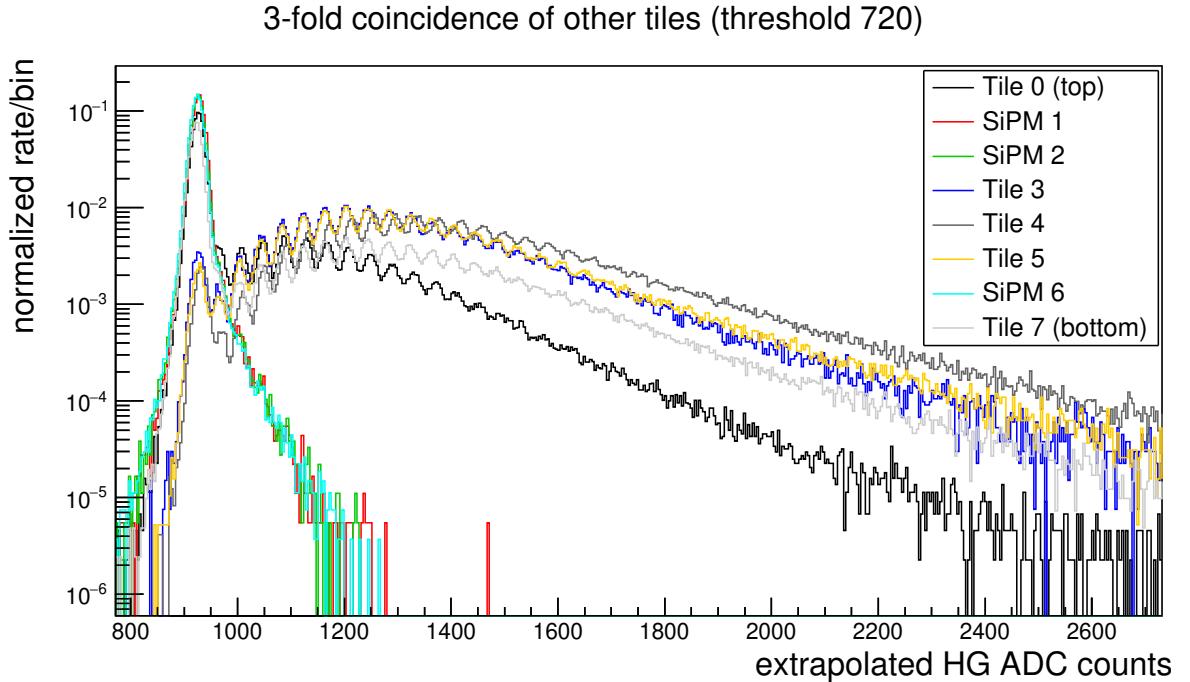

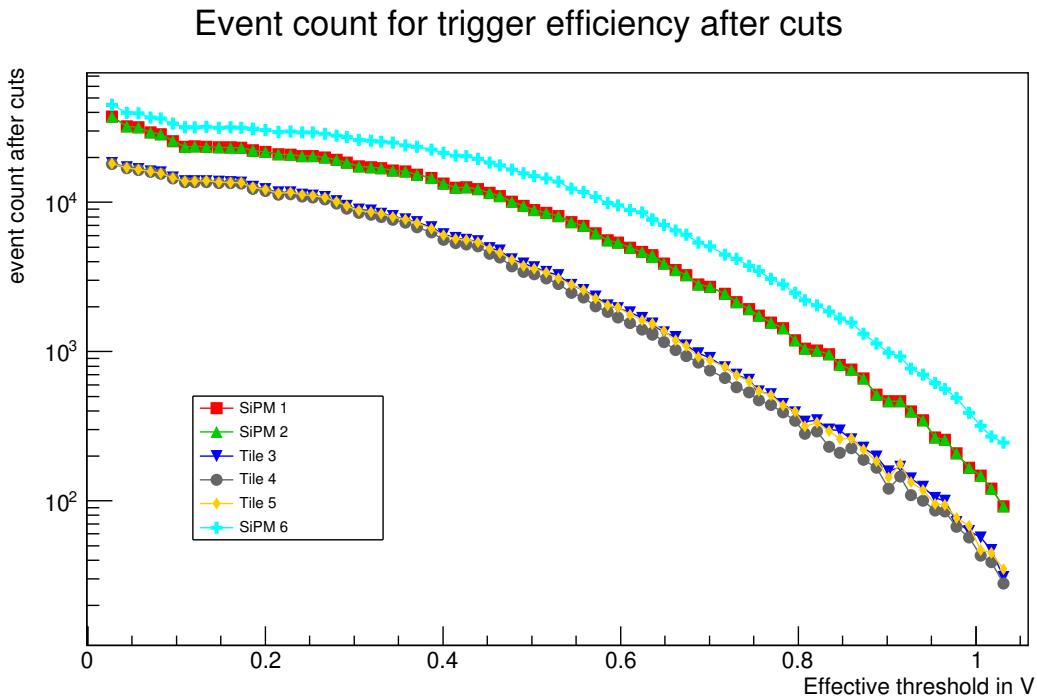

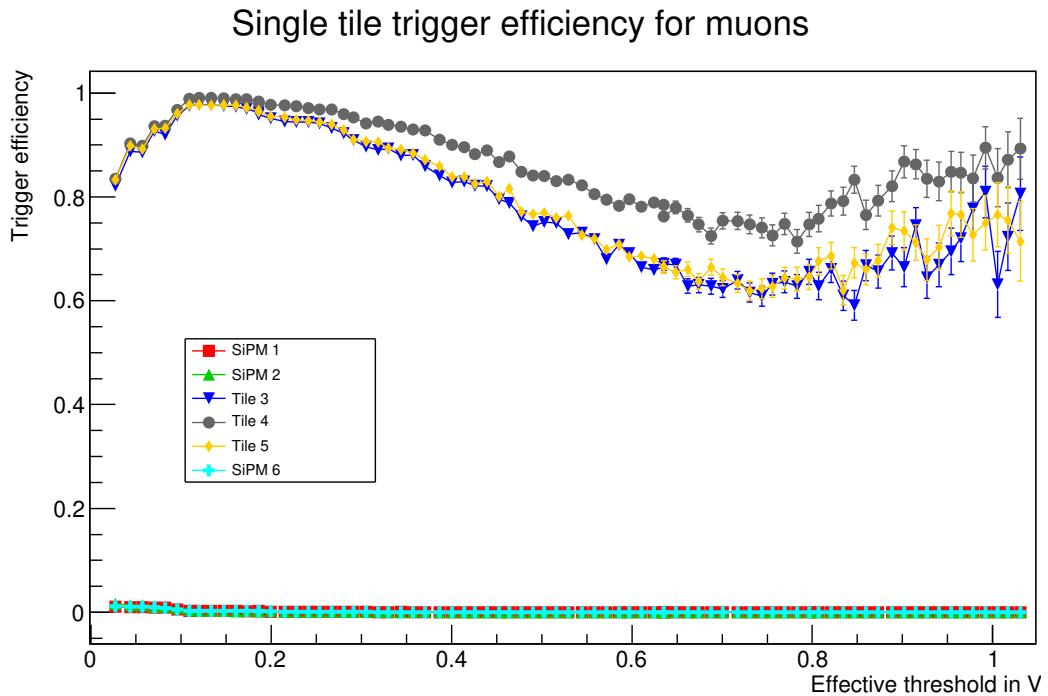

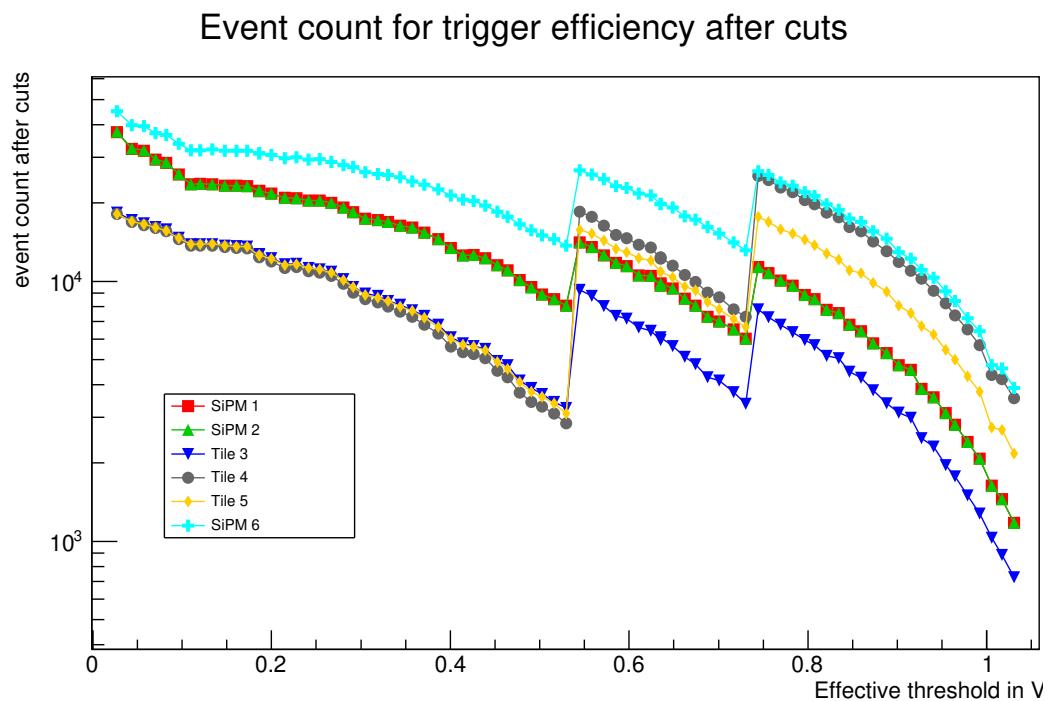

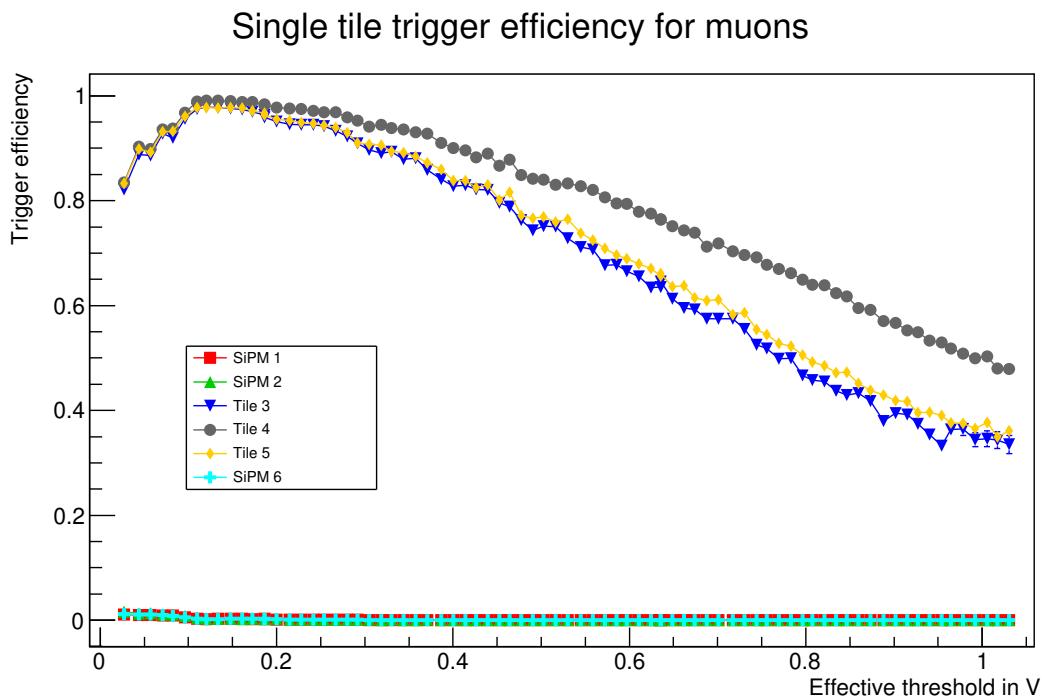

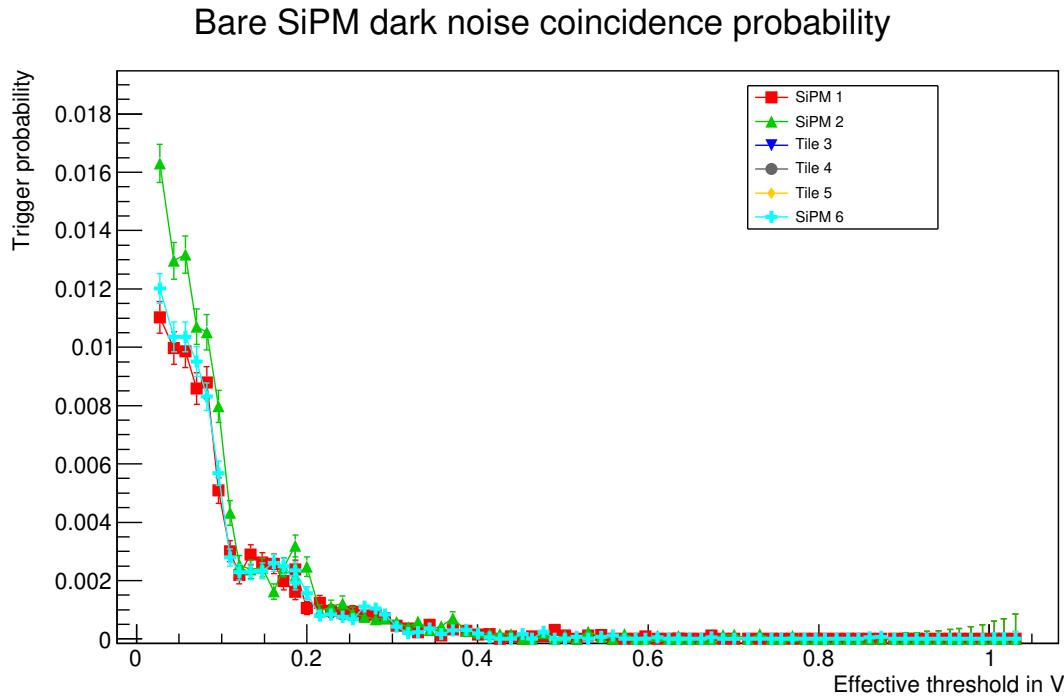

| 10.3.2.    | Trigger efficiency for single muons                             | 156        |

|                                                                        |            |

|------------------------------------------------------------------------|------------|

| <b>11. Summary and Outlook</b>                                         | <b>167</b> |

| 11.1. Outlook . . . . .                                                | 168        |

| <b>Bibliography</b>                                                    | <b>169</b> |

| <b>A. Firmware register description</b>                                | <b>179</b> |

| A.1. 0x00: probe config . . . . .                                      | 179        |

| A.2. 0x01: hold delay . . . . .                                        | 179        |

| A.3. 0x02: fastread config . . . . .                                   | 179        |

| A.4. 0x03: config A . . . . .                                          | 180        |

| A.5. 0x04: OR_maskA . . . . .                                          | 180        |

| A.6. 0x05: OR_maskB . . . . .                                          | 180        |

| A.7. 0x06: OR_maskC . . . . .                                          | 181        |

| A.8. 0x07: OR_maskD . . . . .                                          | 181        |

| A.9. 0x08: multiplicity threshold . . . . .                            | 181        |

| A.10. 0x09: multi_maskA . . . . .                                      | 181        |

| A.11. 0x0a: multi_maskB . . . . .                                      | 181        |

| A.12. 0x0b: multi_maskC . . . . .                                      | 181        |

| A.13. 0x0c: multi_maskD . . . . .                                      | 182        |

| A.14. 0x0d: DAQ outputs . . . . .                                      | 182        |

| A.15. 0x0e: DAQ inputs . . . . .                                       | 182        |

| A.16. 0x0f: firmware revision . . . . .                                | 182        |

| A.17. 0x10: multiplicity overlap . . . . .                             | 182        |

| A.18. 0x11: configB . . . . .                                          | 183        |

| A.19. 0x12: configC . . . . .                                          | 184        |

| A.20. 0x13: trigger holdoff . . . . .                                  | 184        |

| A.21. 0x14: stack threshold . . . . .                                  | 184        |

| A.22. 0x15: stack mask . . . . .                                       | 185        |

| A.23. 0x17: reset . . . . .                                            | 185        |

| A.24. 0x18: multiplicity threshold 2 . . . . .                         | 185        |

| A.25. 0x19: multi_mask2A . . . . .                                     | 185        |

| A.26. 0x1a: multi_mask2B . . . . .                                     | 185        |

| A.27. 0x1b: multi_mask2C . . . . .                                     | 186        |

| A.28. 0x1c: multi_mask2D . . . . .                                     | 186        |

| A.29. 0x1f: scratch . . . . .                                          | 186        |

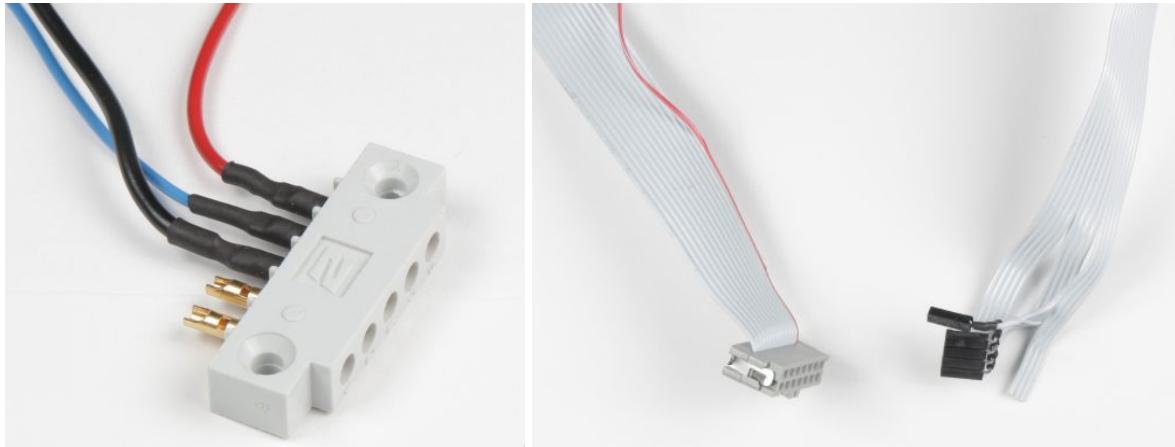

| <b>B. Cabling</b>                                                      | <b>187</b> |

| <b>C. Detailed description of firmware modules</b>                     | <b>191</b> |

| C.1. Detailed description of the ADC readout . . . . .                 | 191        |

| C.1.1. Configuration of fastread . . . . .                             | 192        |

| C.1.2. The read_ADC module . . . . .                                   | 192        |

| C.2. Detailed description of the disrievents firmware module . . . . . | 193        |

| C.2.1. The disrievent_storage module . . . . .                         | 194        |

|                                                                    |            |

|--------------------------------------------------------------------|------------|

| <b>D. Driver for communication with the EASIROC board firmware</b> | <b>197</b> |

| D.1. Additional classes . . . . .                                  | 200        |

# 1. Introduction

The atmosphere of the earth is constantly bombarded by a multitude of cosmic ray particles. Victor Hess first discovered this fact during his now famous balloon flights in 1912. This flux of cosmic ray particles consists of various different types of particles, most prominently photons, electrons, positrons and nuclei including protons. When traversing the atmosphere, the particles initiate a cascade of secondary particles upon colliding with a nucleus of the air. These cascades of particles, called extensive air showers, can be observed by ground-based observatories. This is done either by detecting the secondary particles reaching the ground, or by observing their longitudinal development through fluorescence light, which is emitted when excited nitrogen molecules in the path of the shower deexcite to their ground state. The arrival directions and energies of the primary particles as well as their particle types can be deduced from the shower observables. The largest observatory for extensive air showers induced by ultra high energy cosmic rays (UHECRs) at energies above around  $10^{16.5}$  eV is the Pierre Auger Observatory in the Pampa Amarilla in Argentina. Here both observation methods (Fluorescence Detector (FD) and Surface Detector (SD)) are combined for optimal precision and cross calibration.

Even though there are various models and theories of particle acceleration in astrophysical sources, no clear source of UHECRs has been identified until today. Most exotic top-down scenarios, where the decay of e.g. relic particles from the big bang might produce ultra-high energy cosmic rays, are by now severely constrained by the lack of an observation of photons at ultra-high energies. The recent observation of a dipole anisotropy in the arrival direction of cosmic rays at the highest energies by the Pierre Auger Observatory is a strong indication of an extragalactical source [31]. Due to their deflection in galactic and intergalactic magnetic fields, the arrival direction of charged cosmic rays does not directly point back to their point of production. At the highest energies of around  $10^{20}$  eV however, at least for particles with only a small charge (mainly protons), the deflections are sufficiently small to attempt source identification.

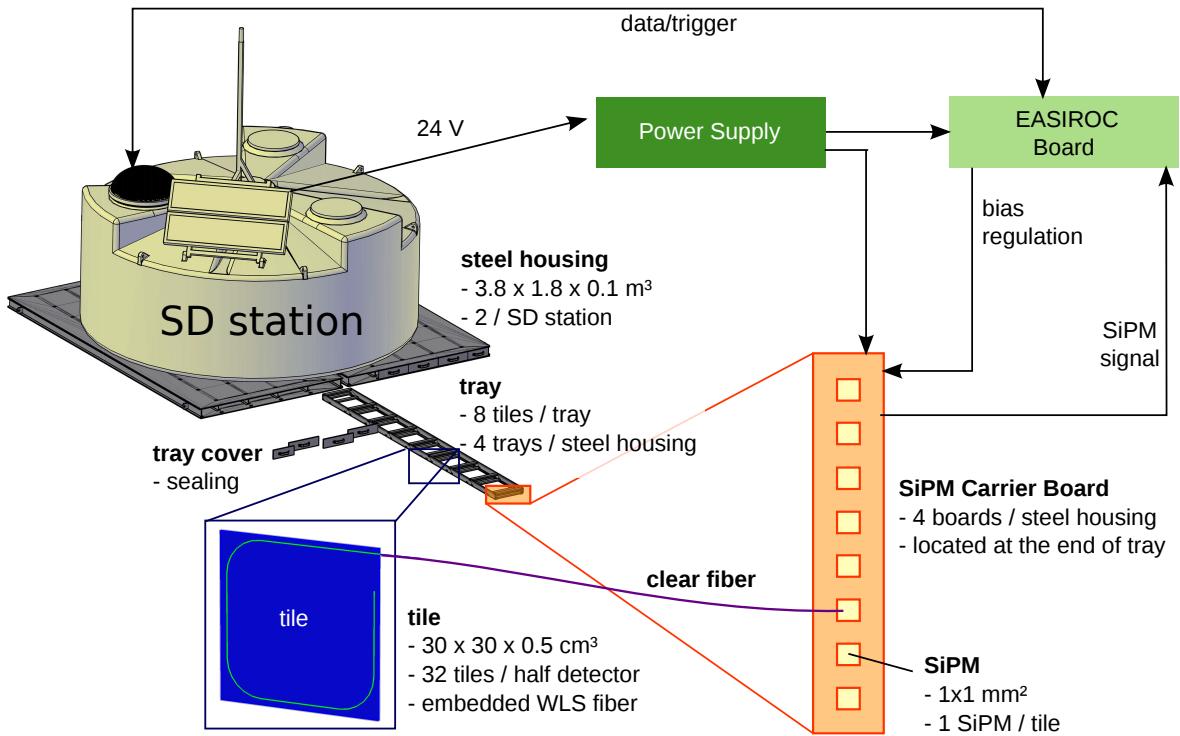

To improve its separation between the different types of primary particles, the Surface Detector Pierre Auger Observatory is currently in the process of being upgraded. A scintillator module called Scintillating Surface Detector (SSD) is placed on top of each detector station as a second detector type to better distinguish between secondary electrons and muons. Different detector upgrades were proposed with the Aachen Muon Detector (AMD) being one of them.

The Aachen Muon Detector is a scintillator detector placed under the Auger SD sta-

tions and read out by silicon photomultipliers (SiPM). The digitization of the signals is performed by an application specific integrated circuit (ASIC) for SiPM readout called *EASIROC*, which is optimized for low power applications. To relay and buffer the digitized signals and to do triggering, a field programmable gate array (FPGA) is needed and has to be programmed.

Even though the AMD was not selected as the final upgrade for the Pierre Auger Observatory, work on the AMD prototype was continued to understand the behavior of the detector components and to apply the developed techniques to other detector designs. The performance of the detector parts is characterized and evaluated to confirm applicability for the foreseen application. One detector design that is based on the AMD components is the MiniAMD which uses an only slightly modified DAQ with a heavily modified mechanical design. It is a lightweight, flexible and modular muon detector which will be used for characterization measurements and quality control of detector modules for the SSD.

You are currently reading chapter 1. In chapter 2 a short overview over cosmic rays is given, including an introduction to extensive air showers in section 2.2. In chapter 3 the Pierre Auger Observatory and its upgrade *AugerPrime* is presented. This is followed by a short introduction to the device technologies used in this thesis for the construction of the AMD: SiPMs in chapter 5, FPGAs in chapter 6, and the EASIROC ASIC in chapter 7. Then the Aachen Muon Detector is introduced (chapter 8) with a special focus on its DAQ system and the FPGA firmware (chapter 9). Finally characterization measurements of the DAQ and first measurements with the complete AMD readout chain to validate the AMD performance are presented in chapter 10.

## 2. Cosmic rays

Cosmic ray particles constantly hit our atmosphere. This was first discovered by Victor Hess during his famous balloon flights in 1912 [44]. These particles have a broad energy range from a few MeV up to at least a few  $10^{20}$  eV [21]. With rising energy, the flux of the particles decreases steeply and covers more than 20 orders of magnitude. The charged cosmic rays mainly consist of charged nuclei and electrons. The neutral part of the cosmic rays is dominated by photons, neutrinos and neutrons.

It is not possible to cover the complete span of energies and flux of particles with a single detector or experiment. Particles up to an energy of about  $10^{15}$  eV, which have a high flux and therefore need only small detectors to reach a sufficient event rate, can be detected directly by satellites or balloon experiments. At higher energies, larger detectors on the ground with areas up to multiple thousand square kilometers, observing cosmic ray induced air showers, are used. While this allows a much greater effective detector area, the energy and particle type reconstruction becomes very challenging.

This chapter is only a very short introduction with a special focus on the highest energies. For a more complete introduction, see for example [25].

### 2.1. Nature and origin

#### 2.1.1. Energy spectrum

The flux of cosmic rays decreases from  $\sim 10^3 \text{ m}^{-2} \text{s}^{-1}$  at a few GeV to  $\sim 1 \text{ km}^{-2}$  per century at  $10^{20}$  eV [25]. The energy spectrum of cosmic rays mostly follows a broken power law

$$\frac{dN}{dE} \propto E^{-\gamma} . \quad (2.1)$$

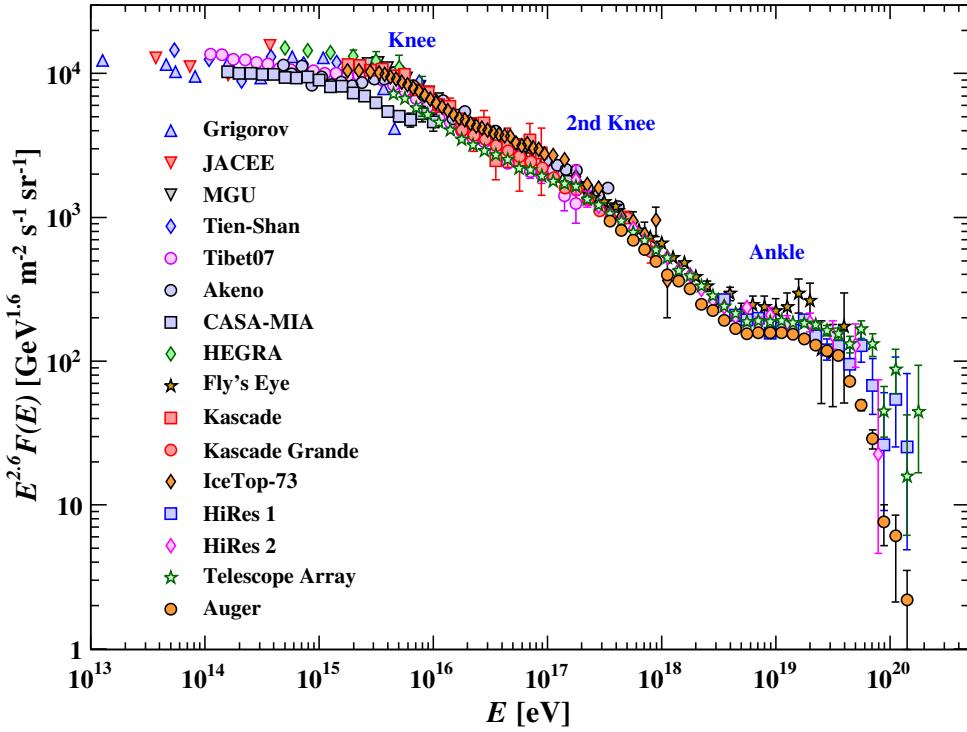

Broken means that the spectral index  $\gamma$  changes slightly at specific energies, which are given special names, breaking the spectrum into segments. The first break occurs at the *knee* at  $E \approx 6 \cdot 10^{15}$  eV. Below, the spectral index is approximately  $\gamma = 2.7$ , at higher energies it is  $\gamma \approx 3.1$ . A slight further steepening occurs at the *second knee* at  $E \approx 4 \cdot 10^{17}$  eV, while at the *ankle* at  $E \approx 4 \cdot 10^{18}$  eV, the spectrum flattens again with a spectral index  $\gamma \approx 2.7$ . The energy of  $E \approx 5 \cdot 10^{19}$  eV marks the onset of an even more rapid decline [82]. The spectrum is shown in figure 2.1, with the flux multiplied by  $E^{2.6}$  to enhance visibility of the aforementioned features.

Figure 2.1.: The cosmic ray flux spectrum (all particle types) as a function of the particle energy from air shower measurements. Multiplied by  $E^{2.6}$  to enhance visibility of features. Original and references in [63, chap 28].

There are different proposed explanations for the knee and the ankle, for example the transition from galactic to extragalactic cosmic ray sources, propagation effects or features in single sources. The two knees can be explained by the same effect occurring at different energies for different particles, e.g. at the same energy per nucleon for protons and iron nuclei. The final drop off coincides with the predicted GZK<sup>1</sup> effect (see section 2.1.4), but might also originate in an energy limit of the sources of cosmic rays.

### 2.1.2. Production mechanisms

Even though the production mechanisms and sources of ultra-high energy cosmic rays (UHECRs) are still unknown, there are many theories to explain their creation.

The currently favored models are acceleration models [53]. According to most of these models, acceleration of charged particles occurs in multiple steps. The so-

---

<sup>1</sup>Greisen-Zatsepin-Kuzmin

called *shock acceleration* occurs when particles are scattered in and around relativistic shock waves by turbulent magnetic fields. For each passing through the shock wave, the particles gain an energy of

$$\frac{\Delta E}{E} \propto \beta \quad , \quad (2.2)$$

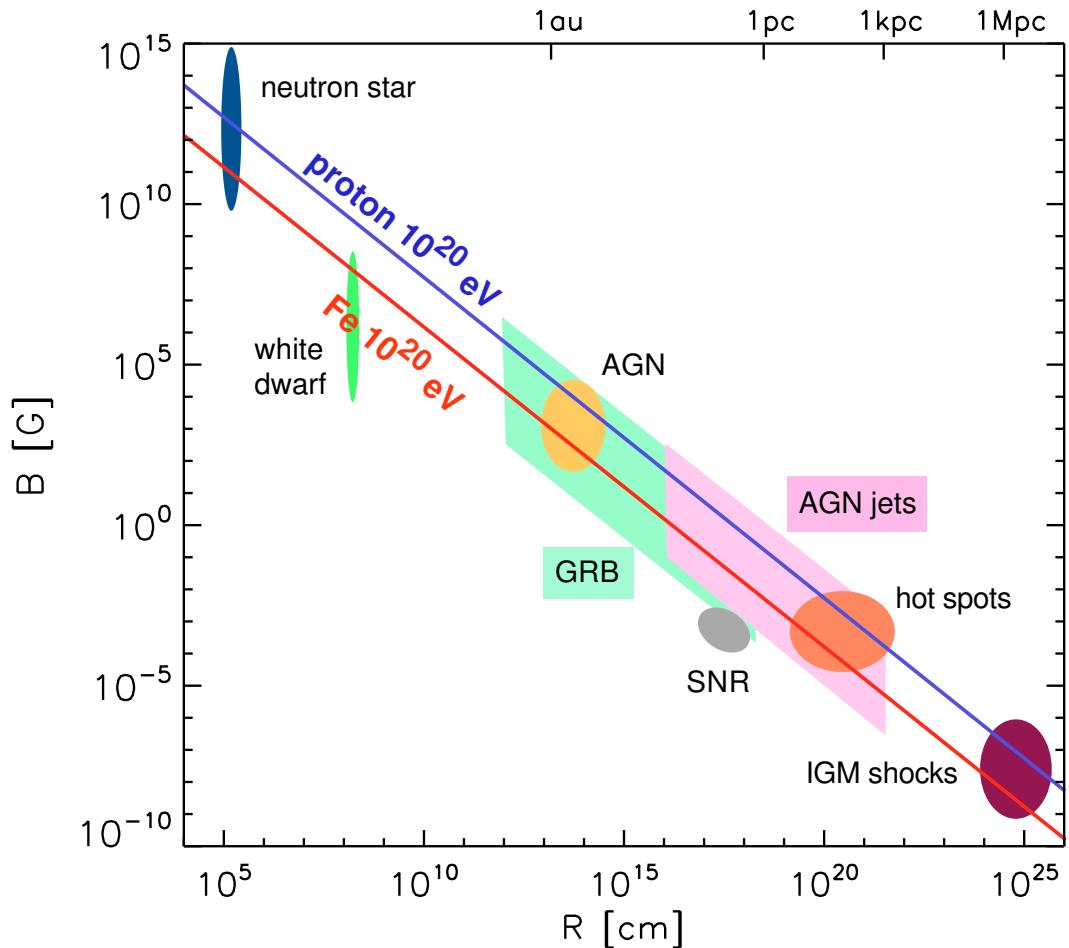

where  $E$  is the current particle energy,  $\Delta E$  is the energy gain and  $\beta = v/c$  is the velocity of the shock wave. Multiple acceleration passes result in a high particle energy, which quite naturally follows a power law spectrum in accordance with the observed energy spectrum. Candidates for this form of acceleration are *Active Galactic Nuclei* (AGNs) and their jets and hot spots, *Gamma Ray Bursts* (GRBs) and shocks in the intergalactic medium (IGM). There are however still many uncertainties especially regarding the exact configuration of the magnetic fields, leading to a continuing evolution of acceleration models.

In other models rapidly changing magnetic fields, for example near young neutron stars (pulsars), can produce electric fields strong enough to accelerate charged particles to the highest energies in one shot.

Also “top-down” models, which explain the generation of UHECRs through the decay of ultra-heavy exotic particles produced in the big bang (e.g. [18], for a broad overview see [19]), were proposed. These models however also predict a high UHE photon flux, which has not been observed, and therefore are now strongly disfavored by the current limits on UHE photons [22].

### 2.1.3. Source candidates

Not all relativistic shock waves can accelerate particles to above  $10^{20}$  eV. During acceleration, the magnetic fields in the source region have to keep the particles contained. The maximum possible energy  $E_{\max}$  of a particle can be estimated [45]:

$$\frac{E_{\max}}{10^{15} \text{ eV}} \approx \frac{1}{2} \cdot \beta \cdot Z \cdot \frac{B}{\mu\text{G}} \cdot \frac{R}{\text{pc}} \quad (2.3)$$

Here  $Z$  is the charge of the particle,  $\beta$  is the velocity of the shock wave,  $B$  is the magnetic field strength and  $R$  the size of the source region.

This relation is visualized by the so-called *Hillas plot* [45], which is shown as an updated<sup>2</sup> version in figure 2.2. With it size and magnetic field of possible accelerators of cosmic rays are compared. Diagonal lines indicate constant possible  $E_{\max}$ , which are obviously different for different particle types. A confirmation that the measured UHECRs originate in any of the proposed sources is still pending. The recent observation of a dipole anisotropy in the arrival direction of cosmic rays at the highest energies by the Pierre Auger Observatory is a strong indication of an extragalactical source [31].

<sup>2</sup>Knowledge about magnetic fields in the universe advanced in the last decades.

Figure 2.2.: An updated *Hillas plot* from [53]. Diameter  $R$  and magnetic field strength  $B$  of cosmic ray accelerator candidates are given with their uncertainties. Objects below the diagonal lines can not contain the specified particle during acceleration.

### 2.1.4. Propagation

It is not possible to directly infer the sources of charged cosmic rays from their arrival directions, since these particles are strongly deflected in the galactic and extragalactic magnetic fields. The gyroradius  $r$  of a charged particle being deflected in a magnetic field is proportional to  $E/Z$ , with the particle energy  $E$  and its charge  $Z$ . This leads to different deflections for different energies and particle types, and together with the non-homogeneity of the magnetic fields to an almost perfectly isotropic distribution of arrival directions below some  $10^{19}$  eV. Only uncharged particles (photon, neutrino and neutrons), for which very stringent observational limits exist at energies above  $10^{18}$  eV [22], are not affected by deflections in magnetic fields. For protons at energies above a few  $10^{19}$  eV, it might be possible to observe a significant correlation between the sources of UHECRs and their arrival directions in the future [4].

In addition to deflection, also energy loss and a change of particle type can occur during propagation. Unstable particles like muons and neutrons can decay. The Hubble expansion of the universe causes an adiabatic energy loss. Due to interactions with background photons  $\gamma_B$  from star light or the cosmic microwave background (CMB) heavy nuclei can experience photodisintegration. Ultra high energy photons  $\gamma$  can undergo pair production:

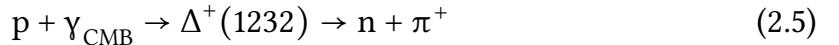

For protons the GZK<sup>3</sup> effect ([40] and [85]) is the name for the resonant pion production with photons of the cosmic microwave background:

The resulting proton or neutron has a lower energy than the original proton. The so-called GZK cutoff is expected to occur at energies at which the production of  $\Delta^+(1232)$  becomes possible. At lower energies energy loss due to direct  $e^+e^-$  pair production

can occur [24].

The main energy loss effect for electrons is synchrotron radiation in magnetic fields, which at ultra high energies reduces their energy rapidly and also prevents their direct acceleration.

### 2.1.5. Composition

While at lower energies a variety of different particle types is observed, at ultra high energies only charged nuclei have been observed until now. Other particle types

<sup>3</sup>Greisen-Zatsepin-Kuzmin

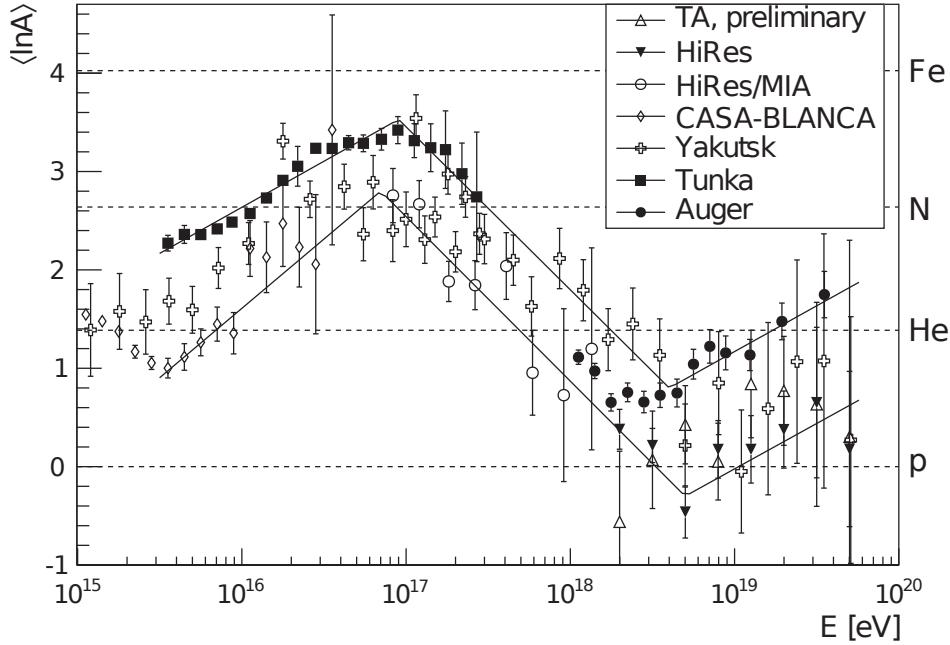

Figure 2.3.: Average logarithmic mass number of cosmic rays as a function of energy derived from measurements with fluorescence telescopes. Simulations using the hadronic interaction model QGSJetII have been used to convert the measured  $X_{\max}$  values (see section 2.2.1) to atomic masses. Different interaction models change the absolute mass number scale but not the general trend. The lines are an estimate of the experimental systematic uncertainties. Taken from [48].

either can not reach the earth at those energies (electrons) or have very stringent limits on their flux (neutrons [72], photons and neutrinos [22]).

In figure 2.3 the evolution of the average mass number of the cosmic rays at energies above  $10^{15}$  eV can be seen. Above the knee the composition becomes heavier, while above the second knee it becomes lighter only to become heavier again above the ankle. These measurements are compatible with a particle-dependent cutoff occurring for protons at a few  $10^{15}$  eV and for iron at higher energies of about  $10^{17}$  eV. At the energy cutoff at about  $10^{20}$  eV the measurement uncertainties are still too large to draw a conclusion.

## 2.2. Cosmic ray induced air showers

When cosmic rays enter the atmosphere, the interactions result in *extensive air showers* (EAS). This fact was first discovered in 1938 by Pierre Auger through measurements of a high coincidence rate between particle detectors up to 300 meters apart, which can be explained by multiple particles from the same EAS triggering the different detectors [17].

During the first interaction, mostly with nuclei of nitrogen or oxygen, multiple secondary particles are produced which do further interactions themselves. The increasing number of particles from the secondary interactions form a cascade of particles, the extensive air shower. The secondary particles still travel roughly in the same direction as the primary particle at a speed close to the speed of light, which results in a slightly curved disc of particles with a thickness in the order of one meter and a lateral extension of a few kilometers when reaching the ground [8]. The exact dimensions of the shower, like its lateral distribution of particles and the curvature of the shower front, depend on the energy and type of the primary particle and undergo statistical fluctuations.

To characterize and describe the longitudinal development of extensive air showers, not a usual length or depth in the atmosphere is used but the slant depth  $X$ , which is the integral over the traversed air density, given in units of  $\text{g cm}^{-2}$ :

$$X(x) = \int_x^{\infty} \rho(x') \, dx' \quad (2.8)$$

where  $x$  is the (conventional) distance from the ground and  $\rho$  is the air density. It has to be taken into account that the integral follows the path of the shower, which in general is not vertical and leads to a slant depth which for inclined showers is bigger than for vertical showers at the same height above ground.

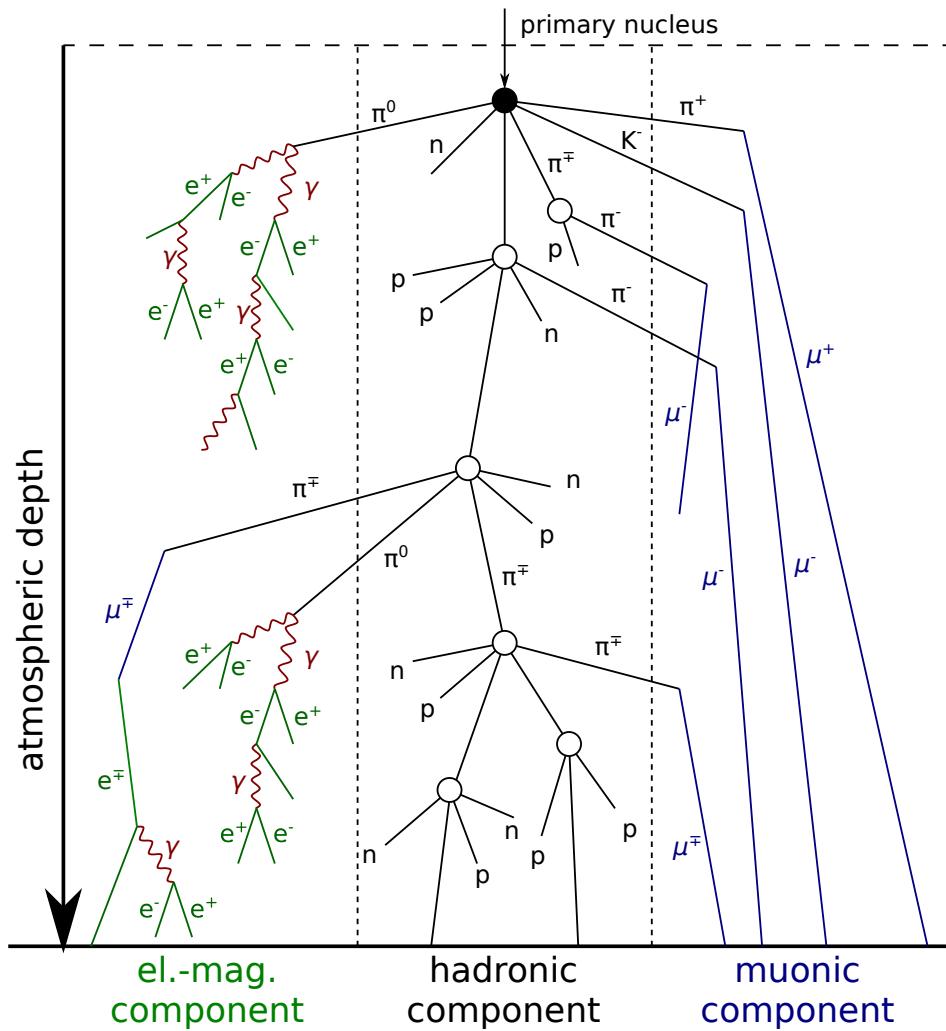

The secondary particles of a shower can be divided into hadronic, electromagnetic ( $e^{\pm}$  and  $\gamma$ ) and muonic components (see figure 2.4).

### 2.2.1. Hadronic component

Especially for hadronic primary particles, the interactions with air nuclei produce mainly charged and uncharged mesons (pions, kaons) and nucleons (protons, neutrons). The secondary hadronic particles can either do further scattering processes with nuclei or decay (e.g.  $\pi^0 \rightarrow \gamma + \gamma$ ), which often leads to further contributions to other shower components.

The Gaisser-Hillas-Formula [39] is often used to phenomenologically parameterize the longitudinal evolution of the number of shower particles (for  $X > X_1$ ):

$$N(X) = N_{\max} \left( \frac{X - X_1}{X_{\max} - X_1} \right)^{\frac{X_{\max} - X_1}{\lambda}} \exp \left( -\frac{X - X_{\max}}{\lambda} \right) \quad (2.9)$$

Figure 2.4.: Schematic view of the components in an extensive air shower. The spatial separation is just for illustrative purposes.

Here  $X_{\max}$  is the slant depth of the shower maximum where  $N_{\max}$  secondary particles exist,  $X_1$  is the slant depth of the first interaction.  $\lambda$  appears as an effective free path length (slant depth), it is actually just a shape parameter without a clear physical equivalent. Up to  $X_{\max}$  the energy of the particles is distributed onto an increasing number of particles, but at  $X_{\max}$  the critical energy for the particles is reached, particles are being stopped and the shower dies out.  $X_{\max}$  can be used as a mass-sensitive observable. Heavier primary nuclei on the one hand have a bigger cross section for the first interaction and therefore (on average) a smaller  $X_1$ . On the other hand they produce more particles (each with lower energy) in the first interaction, resulting in a shower development similar to multiple simultaneous lower energy proton-induced showers after the first interaction.

### 2.2.2. Electromagnetic component

The electromagnetic component of extensive air showers develops mainly from photons resulting from the decay of neutral pions, but to a lesser degree also electrons produced by decaying muons or particles scattering directly with the electrons of the air atoms. Through this the electromagnetic component is permanently renewed by and coupled to the hadronic component. The photons in the electromagnetic component mainly undergo pair production of  $e^+e^-$  pairs, which then produce further photons due to bremsstrahlung. Also contributions to the hadronic component are possible with photonuclear interactions. Through an excitation of nitrogen molecules in the air, fluorescence light with an intensity proportional to the energy deposit and therefore to the number of  $e^\pm$  is produced [15].

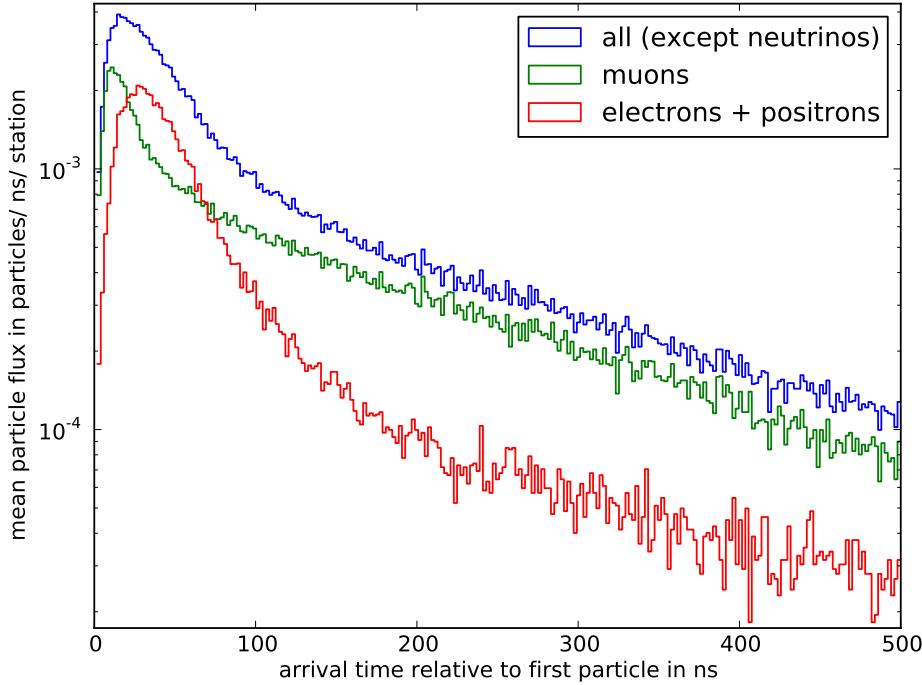

### 2.2.3. Muonic component

Charged mesons  $K^\pm$  and  $\pi^\pm$  mostly decay into muons and the corresponding neutrinos. This leads to a muonic component which is strongly coupled to the hadronic component. The muons undergo only limited scattering in the atmosphere and at their relativistic velocities also have a lifetime long enough to often reach the ground without decaying into electrons. Due to this, their trajectories often point back directly to their point of production and they are usually the first particles of the shower to arrive at the ground.

The total number of muons produced depends on the mass number  $A$  of the primary with energy  $E_0$ . Again, for higher mass numbers the showers can be seen as a superposition of  $A$  proton-induced showers, each with an energy of  $E = E_0/A$ .

This can be made plausible by assuming a simplified Heitler-like model, in which the hadronic cascade continues until the charged particles decay into muons when they reach the critical energy  $E_c$ . More cascade steps

$$N_{\text{steps}}(E) = \log_N(E/E_c)$$

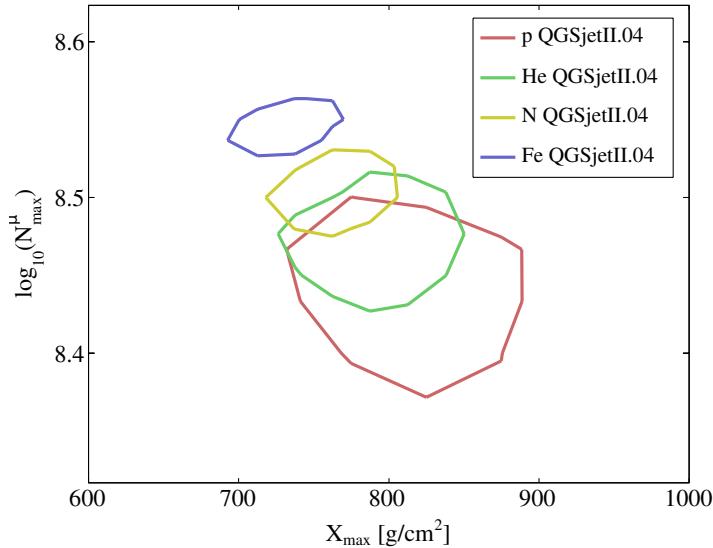

Figure 2.5.: Simulated  $1\sigma$  contour lines of the distributions of  $X_{\max}$  and  $N_{\max}^{\mu}$ , which is the number of muons at the maximum of the muonic shower development, for different primary particles. Air showers induced by primary particles with  $E = 5 \times 10^{19}$  eV and zenith angle  $\theta = 38^\circ$ . Taken from [4].

(where  $N$  is the number of particles produced in each step) happen for higher energies. For each interaction in the hadronic cascade, a fraction  $p_0$  of the energy is carried by  $\pi^0$ , which decay into photons and are therefore removed from the hadronic cascade and can no longer produce muons, while only the fraction  $p = 1 - p_0$  of the energy continues in the cascade. It can be deduced that

$$N_{\mu} \propto E_0 \cdot p^{N_{\text{steps}}(E)} ,$$

which means that the number of muons  $N_{\mu}$  increases slower than linear with the primary proton energy  $E = E_0/A$  and therefore primaries with a higher mass number  $A$  produce a higher number of muons

$$N_{\mu} \propto E_0 \cdot p^{N_{\text{steps}}(E_0/A)} .$$

As can be seen from the air shower simulations shown in figure 2.5, the number of muons can be used to discriminate different primary particle types even better than  $X_{\max}$ , with a combination of both observables preferable.

## 2.2.4. Neutrino component

During decay and production of muons also neutrinos are produced to balance the lepton number. Even though they can not normally be measured, the fact that they withdraw energy from the shower (*invisible energy*) has to be corrected for.

## 2.2.5. Detection principles

Extensive air showers can be detected using different methods. The most important principles are the detection of the fluorescence light produced by the electromagnetic component, through which the longitudinal shower development can be observed, and the measurement of the lateral distribution of particles at the ground level.

### 2.2.5.1. Fluorescence light detection

*Fluorescence telescopes* are used to observe the longitudinal shower development by measuring fluorescence light. The fluorescence light produced by nitrogen molecules in the air is strongly related to the energy deposit by the electromagnetic component. It therefore allows a calorimetric energy measurement if the fluorescence light yield and the amount of invisible energy" is known. The longitudinal measurement of the shower profile also allows a direct determination of  $X_{\max}$ . A major inherent limitation of this detection principle is the fact that it only works in dark nights with decent weather<sup>4</sup>.

A similar detection principle, used especially for lower energy showers (GeV up to about 100 TeV), is the detection of Cherenkov light emitted by the particles of the EAS while traveling faster than the speed of light in the atmosphere. As Cherenkov light is only emitted in forward direction, it can not be used to properly resolve the longitudinal development of a shower and only has a small effective area per detector station, but has a much smaller energy threshold compared to fluorescence light detection<sup>5</sup>.

### 2.2.5.2. Particle detection at ground level

The easiest way to observe extensive air showers is to use particle detectors at ground. Due to the large areas that need to be covered (multiple thousand square kilometers for energies above  $10^{19}$  eV) only a sampling with relatively small stations and distances up to a few km can be performed. Depending on the detector type and placement, different detection efficiencies and weights for the different shower components can be reached, which can lead to a separation of the shower components when multiple detector techniques are combined. An example for this is the combination of a scintillator detector at the surface to detect mainly the electromagnetic component with a buried scintillator detector to detect mainly the muonic component.

---

<sup>4</sup>no rain, fog or significant cloud coverage

<sup>5</sup>Cherenkov light is distributed only in a small solid angle range and results in a very short time-compressed light pulse.

### 2.2.5.3. Radio detection

An important additional technique to detect extensive air showers is the observation of radio waves. These waves are produced by the electrons ( $e^\pm$ ) in the electromagnetic component and can be detected as short pulses by antenna stations near the shower axis. Two radio production mechanisms can be observed in air showers. With the so called geomagnetic effect the charge separation in the Earth's magnetic field causes a direction and position dependent signal [47]. A negative charge excess in the (moving) shower front caused by annihilation of positrons and knock-out of electrons from air molecules is the second mechanism [16]. From the signal strength and timing of the radio pulses shower observables like  $N_{\max}$  and  $X_{\max}$  can be reconstructed.

### 2.2.5.4. Hybrid approaches

A combination of multiple detection techniques on a single EAS can yield complementary information, enabling a better shower reconstruction. For example does a combination of fluorescence telescopes with a detector on the surface allow a better reconstruction of the arrival direction and subsequently the longitudinal profile than each of the systems alone. A combination of the longitudinal information about the electromagnetic component from fluorescence telescopes and the lateral information about the muonic component from a ground detector allows much higher precision for particle type determination and energy reconstruction than the single systems.

# 3. The Pierre Auger Observatory

The Pierre Auger Observatory is a detector complex for extensive air showers induced by ultra-high energy cosmic rays. It is the biggest cosmic ray detector ever built and is located near the city of Malargüe in western Argentina. It was originally designed to detect cosmic rays with energies between  $10^{18}$  eV up to the highest energies beyond  $10^{20}$  eV, but had its lower energy threshold extended down to  $10^{17}$  eV with newer upgrades.

An extensive overview over the observatory is provided in [3].

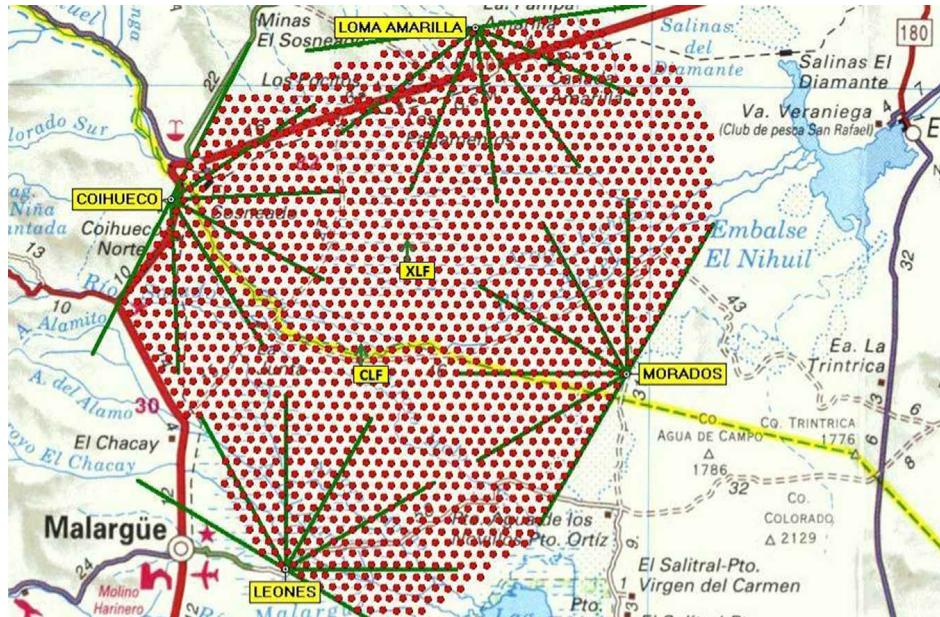

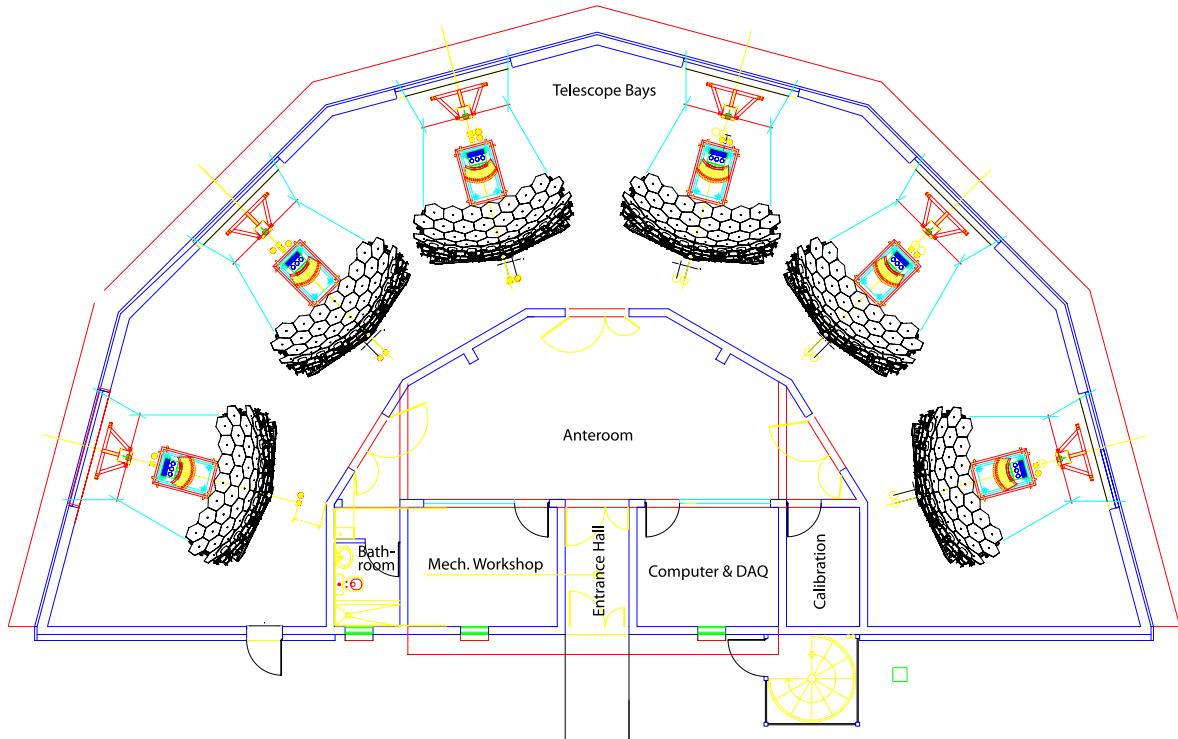

The observatory is based on a hybrid design with two complementary detectors, which simultaneously measure the lateral shower profile on the ground and the longitudinal shower development. The part devoted to the lateral shower profile is the *Surface Detector* (SD), which consists of around 1600 detector stations on an area of roughly  $3000 \text{ km}^2$ . For the measurement of the longitudinal shower profile, the *Fluorescence Detector* (FD) is used. It consists of multiple fluorescence telescopes overlooking the area covered by the Surface Detector. Some additional detector enhancements, either extensions of the existing detectors or new detectors, have been added during the 15 years of operation and are also present in the area. An overview of the regular detectors is provided in figure 3.1.

The hybrid design of the detector allows to combine the advantages of both detection methods, while allowing the reconstruction of the properties of the primary cosmic rays with a precision not possible with a single detector type. While the FD has a much lower duty cycle compared to the SD, its systematic uncertainty of the energy determination is much lower, allowing for a good cross calibration. Even for analyses where mainly the FD is used, usually some information from the SD is added to improve the accuracy of the geometry reconstruction of the shower. Especially to determine the chemical composition of the primary cosmic rays, a combination of observables determined by both SD and FD leads to better separation between types of primary particles.

## 3.1. The Surface Detector

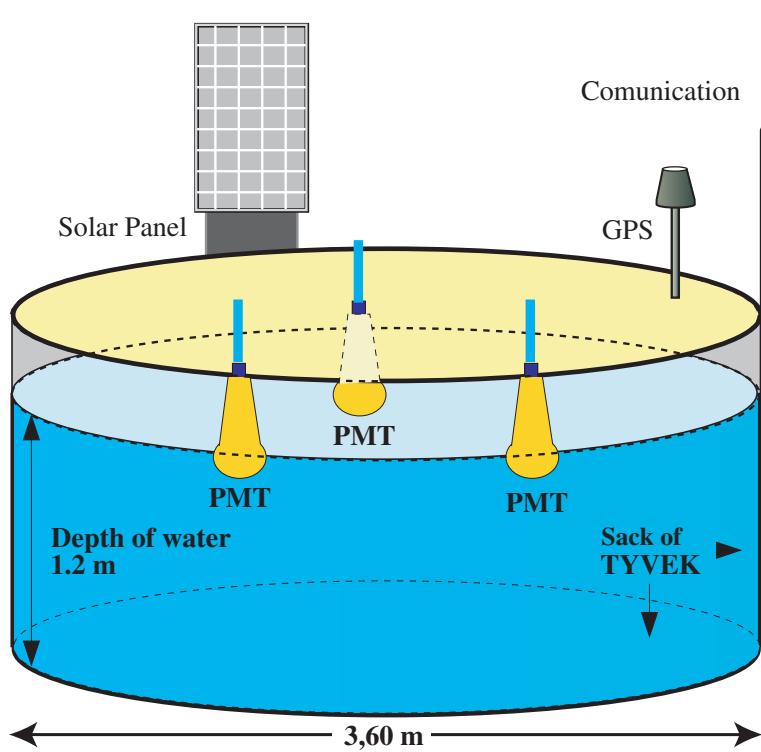

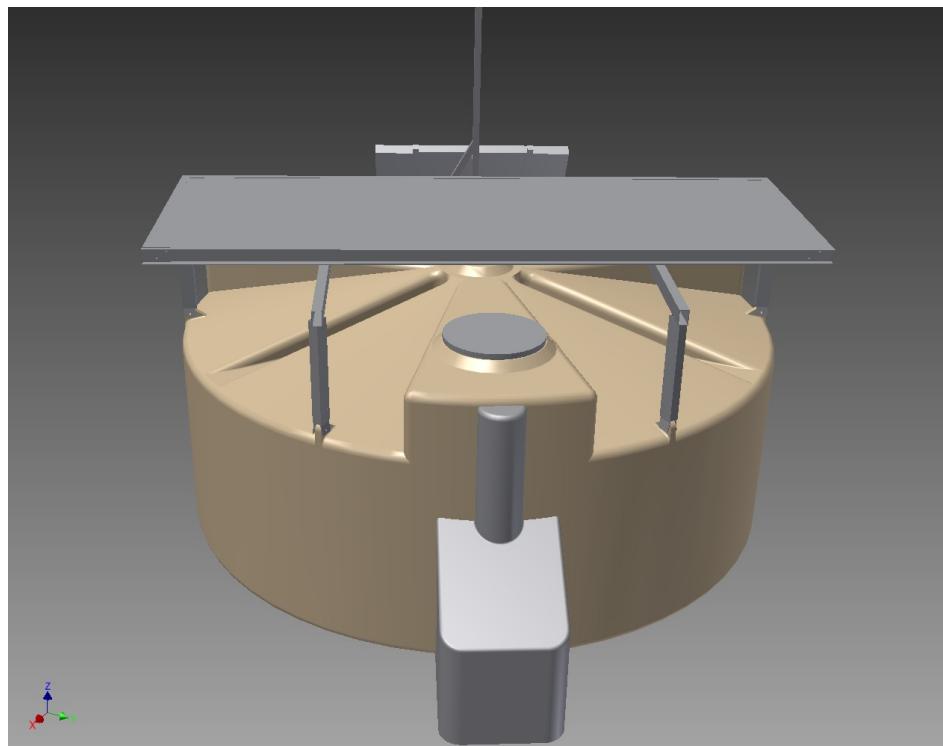

The Surface Detector consists of about 1600 detector stations using the Cherenkov effect in water (see figure 3.2). The stations are arranged on a hexagonal (triangular) grid with 1.5 km spacing in an area of about  $3000 \text{ km}^2$ . Each station is a tank with

Figure 3.1.: The Pierre Auger Observatory. Stations of the Surface Detector are shown as red dots, while the field of view of the Fluorescence Detector is indicated by the green lines. Also two laser facilities (CLF and XLF) used for calibration are shown. Taken from [3].

about 12 tons of ultra-pure water, instrumented by three PMTs<sup>1</sup> to detect the light produced by Cherenkov radiation. The station is designed for autonomous operation with power being generated by a solar panel and stored in a battery for operation at night and during cloudy periods. Wireless communication is used to distribute triggers and facilitate data readout, while a GPS<sup>2</sup> module is employed to synchronize the internal clock of each station with the GPS atomic clocks.

The detector stations sample the lateral distribution of shower particles on the ground. A combination of muons and electromagnetic particles (electrons, positrons and photons) is measured, with the electromagnetic component mostly being stopped in the tank, while the muons as minimum ionizing particles mostly traverse the tank. Using timing information, the arrival direction of the shower and therefore the arrival direction of the primary cosmic ray can be determined. Evaluating the lateral shower profile, the energy of the primary cosmic ray particle can be estimated.

It is difficult to determine the type of the primary particle with the SD alone. Various approaches using the signal timing in single stations<sup>3</sup> or the overall shape of the lateral distribution are applied. These, however, are not able to achieve a clear separation between particle types for single showers, while additionally being strongly influenced by uncertainties on hadronic interaction models for air shower simulation.

---

<sup>1</sup>photomultiplier tubes

<sup>2</sup>Global Positioning System

<sup>3</sup>The arrival time distribution of muons is different from that of the electromagnetic component, with the muons arriving first.

Figure 3.2.: Schematic view of an SD station [32]. The station is a tank with about 12 tons of ultra-pure water as a Cherenkov radiator, instrumented by three PMTs to detect the produced light. Power is generated by a solar panel and stored in a battery for operation at night and during cloudy periods. Wireless communication is used to distribute triggers and facilitate data readout, while a GPS module is employed to synchronize the internal clock to the atomic clocks in the GPS network.

## 3.2. The Fluorescence Detector

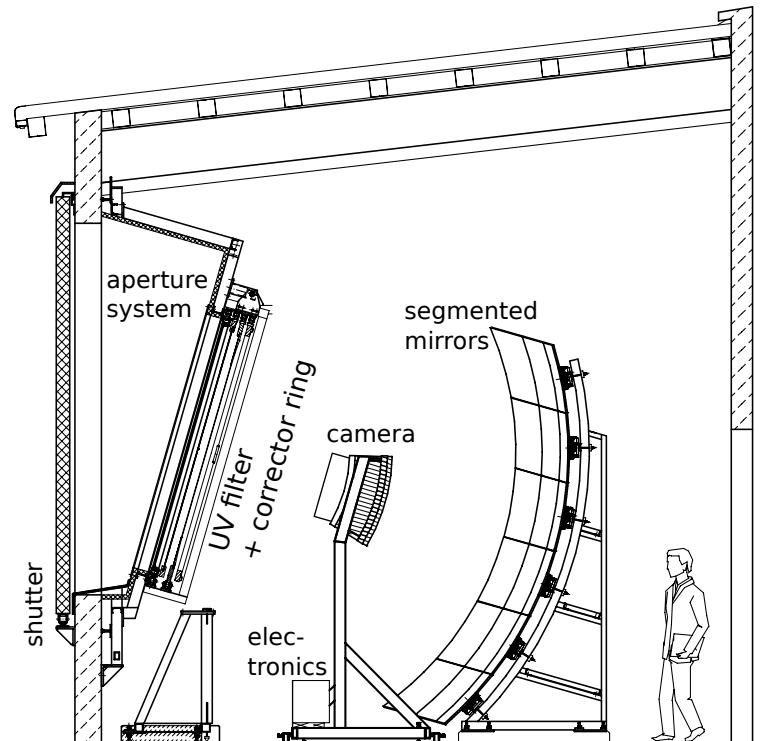

The Fluorescence Detector of the Pierre Auger Observatory [5] consists of 4 telescope sites or buildings<sup>4</sup> (see figure 3.3), housing 24 telescope *bays* (see figure 3.4) with Schmidt cameras. The segmented mirror of each telescope has an area of  $10\text{ m}^2$ , focusing the light onto a camera equipped with 440 PMTs. To reduce the night sky background, a UV pass filter, which is mostly transparent for nitrogen fluorescence light, is installed at the aperture. A corrector ring is used as an approximation of a Schmidt plate. Each telescope has a field of view (FoV) of  $30^\circ \times 30^\circ$ . Each telescope site with six telescopes has a combined FoV of  $180^\circ \times 30^\circ$  (azimuth  $\times$  altitude). All sites together overlook the complete SD array.

The Fluorescence Detector measures the fluorescence light, which is emitted by nitrogen molecules excited by the secondary particles of the air shower. Hereby mainly the electromagnetic part of the shower is visible with about 4 photons produced per electron per meter [71]. The angular resolution of about  $1.5^\circ$  per cam-

<sup>4</sup>Coihueco, Loma Amarilla, Los Morados and Los Leones

Figure 3.3.: Sketch of one Fluorescence Detector building [5]. Six fluorescence telescopes are located around some auxiliary rooms.

era pixel allows for a measurement of the longitudinal development with the atmospheric depth of the shower maximum  $X_{\max}$  being the main composition sensitive observable of the FD. With the produced light being proportional to the energy deposit of the shower in the atmosphere, a direct calorimetric measurement of the shower energy is possible, based on an existing measurement of the *fluorescence yield*<sup>5</sup> as a calibration constant. Because the fluorescence yield as well as the light propagation from the shower to the telescopes depend on atmospheric parameters, these are continuously monitored, mainly using laser-based methods.

The FD can operate only during moonless nights with fine weather, which leads to a duty cycle of about 15 %.

---

<sup>5</sup>number of photons per deposited energy

Figure 3.4.: Schematic view of one fluorescence telescope bay [5]. Fluorescence light enters through the shutter and aperture, passes a UV pass filter and is focused onto the PMT camera by a segmented mirror. Physicist for size comparison.

### 3.3. Existing enhancements and upgrades

In addition to the two main detector types, FD and SD, further detector components have been added since the start of the observatory.

#### 3.3.1. AMIGA

AMIGA (*Auger Muons and Infill for the Ground Array*) [77] itself consists of two parts. One part of it is the infill, which consists of 61 additional SD stations between the original stations to reduce the grid spacing to 750 m in a small part of the array. The infill reduces the lower energy threshold of the surface detector to  $10^{17}$  eV. With a steep increase in flux with lower energy, covering only a small part of the complete array is sufficient. The second part of AMIGA consists of scintillator muon detectors, which are buried near existing SD stations at a depth of 2.5 m. Here the pure muon signal at the SD stations is measured, due to the shielding provided by the earth, which only muons can pass. These muon detectors are a new component for the overall hybrid design of the observatory and allow for an improvement of the understanding of extensive air showers. Since the infill consists of normal SD stations it is nowadays often seen as part of the regular SD with AMIGA just referring to the muon detector part. AMIGA muon counters are currently installed at seven tanks in one hexagon in the infill area (*unitary cell*) with more planned.

#### 3.3.2. HEAT

HEAT (*High-Elevation Auger Telescopes*) [56] is the name for three additional telescopes near the Coihueco FD site. These telescopes, which are optically identical to normal FD telescopes, can be tilted 30° upwards and a combined operation with Coihueco results in a total field of view up to 60° in elevation. This allows to observe showers at lower energies down to  $10^{17}$  eV, which generally have an  $X_{\max}$  above the standard FD field of view, as the visible faint showers are observable only very close to the telescopes while they also develop higher in the atmosphere. The HEAT telescopes overlook the area covered by the infill, so that both low energy extensions can be operated together in hybrid mode.

#### 3.3.3. AERA

AERA (*Auger Engineering Radio Array*) [49] is the third enhancement of the Pierre Auger Observatory, covering an area of 6 km<sup>2</sup> in the infill area. It consists of 153 antennas sensitive between 30 MHz and 80 MHz. AERA is used to study the radio emission of extensive air showers in the VHF<sup>6</sup> band. With the radio emission in

---

<sup>6</sup>Very High Frequency

principle being calculable from basic electrodynamics, it could in the future be possible to improve the energy scale of the observatory using a cross calibration of the shower energy with AERA instead of the FD, thus eliminating the dependence on measurements of the fluorescence yield and atmospheric parameters. Also  $X_{\max}$  can be determined with AERA, which allows a determination of this important shower parameter with 100 % duty cycle instead of the reduced FD duty cycle.

## 3.4. AugerPrime

After more than 15 years of data taking at the Pierre Auger Observatory, there are still open questions which can not be answered with more statistics alone. The solutions to the questions rely heavily on a more precise determination of the number of muons  $N_{\mu}$  in the shower. To achieve this for the highest energies, the AMIGA unitary cell and the further planned AMIGA stations in the infill do not offer sufficient area coverage. Therefore a new detector component has to be added to the SD stations. The new detector part chosen for the upgrade is the *Scintillator Surface Detector (SSD)*, which consists of scintillator bars placed above each SD station. For better overall detector performance and to facilitate readout of the SSD, the main station electronics are upgraded. The complete upgrade is called *AugerPrime*, which is described in more detail in its preliminary design report (PDR) [4].

### 3.4.1. Upgrade of the SD electronics

For various reasons the electronics of the SD stations (SDE) is upgraded (SDEU). For this an Updated Unified Board (UUB) as the core of the SD tank electronics is developed.

The original design, which is more than 15 years old, only offers limited computational power for newer, more advanced triggers and data reduction for transfer. State-of-the-art FPGAs and processors can improve the capabilities.

To improve the possibilities of SD-tank based analyses using the exact shape and timing of the light pulses in the water Cherenkov detectors, the sampling rate of the ADCs used for the SD tank PMTs will be increased from the original 40 MHz to 120 MHz. With typical time differences between the tank PMTs in the order of 6 ns depending on particle direction and time bins of 8.3 ns, it becomes possible to extract some direction information for single stations. With the more precise measurement of the rising edges caused by single muons crossing the tank, for stations far away from the shower core counting of muons becomes possible with the WCD alone.

Very close to the shower core, the SD tank PMTs often saturate, which leads to the data of the station providing only a lower limit on the signal. Through the addition of a smaller PMT to the tank, which has to be read out and provided with bias voltage, the high-signal events can be recorded without clipping. This will be supported by

the new electronics.

For further additions of detector components to the SD stations, digitization and communication has to be provided.

### 3.4.2. Proposals for a new muon detector

In order to determine the muon number with an accuracy higher than what is possible by a better timing resolution alone, an additional muon detector component will be added. Various approaches and concepts were proposed, each with different pros and cons. Two general approaches were possible:

- Add a muon detector either below the tank or buried close to the tank, which uses the tank or the earth as shielding to detect almost exclusively muons. The *Aachen Muon detector (AMD)*, which is described further in this thesis, belongs to this category.

- Add a detector with a different response to muons and electrons in the shower compared to the SD tank and calculate the muon and electron content using the inversion of the response matrix (*matrix method*).

While buried detectors like the ones used for AMIGA provide great accuracy, they are also very difficult to deploy, especially in parts of the array with high water levels<sup>7</sup>. While these will be deployed for part of the array to do a proper calibration of the matrix method (*high precision array*), the complete array will be outfitted with a scintillator detector mounted on top of the SD stations (*SSD*), which needs a much more complex analysis, but is vastly easier and cheaper to build and deploy.

### 3.4.3. SSD

The *Scintillator Surface Detector (SSD)* is the name for the surface detector extension. It consists of a scintillator panel with an area of  $4\text{ m}^2$ , made up of multiple plastic scintillator bars with wavelength shifting fibers guiding the light onto a single PMT. The new SD electronics board is used to digitize the single PMT signal per station. The SSD mainly measures electrons, while the SD tank measures more muons in comparison, enabling the matrix method for muon number determination. The planned SSD is shown in figure 3.5.

---

<sup>7</sup>Some SD stations are placed in a river.

Figure 3.5.: The planned Scintillator Surface Detector (SSD) to be placed on top of the SD stations as part of AugerPrime [4].

## 4. Scintillators for particle detection

Scintillators are materials that emit light when they are crossed by ionizing particles. When read out by sensitive photon detectors (like photomultiplier tubes (PMTs) or silicon photomultipliers (SiPMs; see chapter 5)) this can be used to detect the particles. An almost linear relation exists between the number of photons emitted and the deposited energy. This can be used for the measurement of particle properties like energy or particle type. If the particle is stopped in the scintillator, the particle energy can be determined directly. For thin scintillators a measurement of  $dE/dx$ , the deposited energy per track length, together with its known dependence on the energy  $E$ , can be used to derive the energy. For some scintillator materials the time shape of the resulting light pulse contains information about the type of primary particle [55].

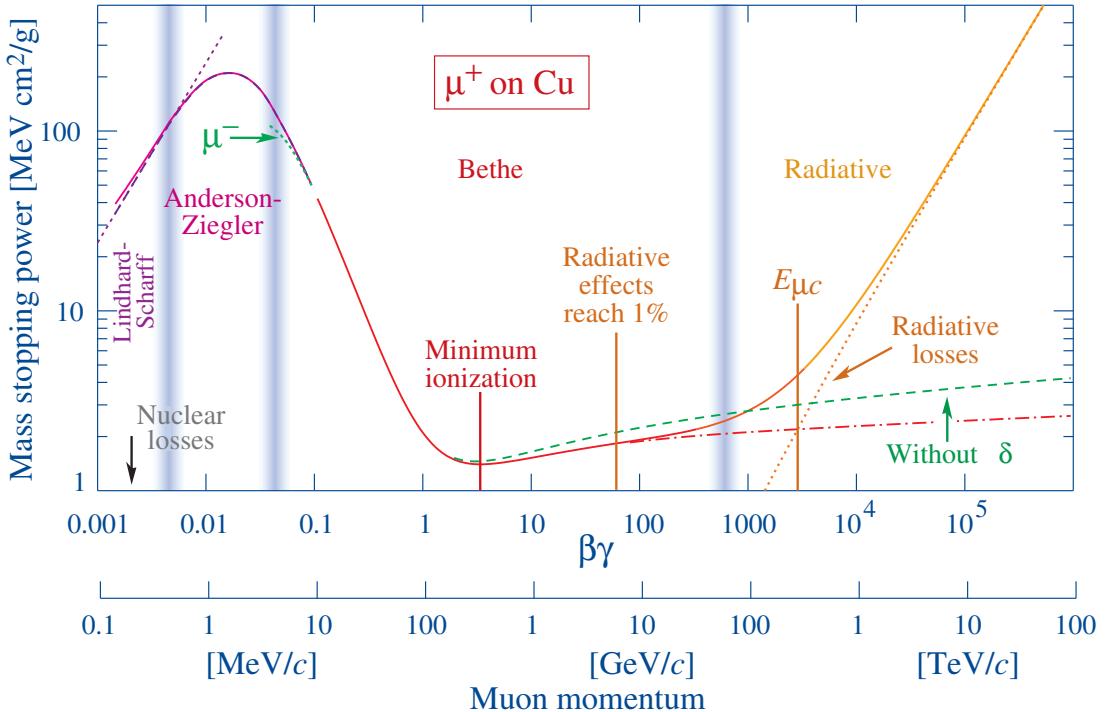

A special case of particles are muons, which over a broad range of momenta deposit a small, almost constant amount of energy per track length (see figure 4.1), and are therefore called *minimum ionizing particles* (MIPs). This on the one hand leads to their high penetration power and on the other hand makes them well suited for the calibration of particle detectors.

Other applications are time-of-flight measurements using thin scintillators and a readout with good timing resolution, as well as position measurements using segmented scintillators.

There are various materials used as scintillators, each having different characteristics. While inorganic scintillators like NaI have a good energy resolution due to high light output and their high density, they are difficult to handle because of their hygroscopy and brittleness and do not have a good timing resolution (e.g. decay constant  $\tau = 230$  ns for NaI(Tl)). Organic scintillators offer a great timing resolution ( $\tau \sim$  ns) at the expense of a rather mediocre energy resolution, caused by a lower light yield. Due to their lower density compared to inorganic scintillators,  $\gamma$ -rays are only detected through the Compton effect, which leads to a continuous Compton spectrum instead of a clear peak resulting from photoelectric conversion. Organic scintillators are often embedded into plastic material and are easy to handle and manipulate while being relatively robust to mechanical stress and moisture. Especially for big detector volumes, also liquid scintillators (organic scintillators in a liquid solvent) are used.

While the mean energy deposit for a MIP muon is a constant, the distribution of the

Figure 4.1.: Mass stopping power ( $= \langle -dE/dx \rangle$ ) for positive muons in copper as a function of  $\beta\gamma = p/Mc$ . The region of minimum ionization for this material reaches from roughly 100 MeV to 100 GeV. Taken from [63, chap 32].

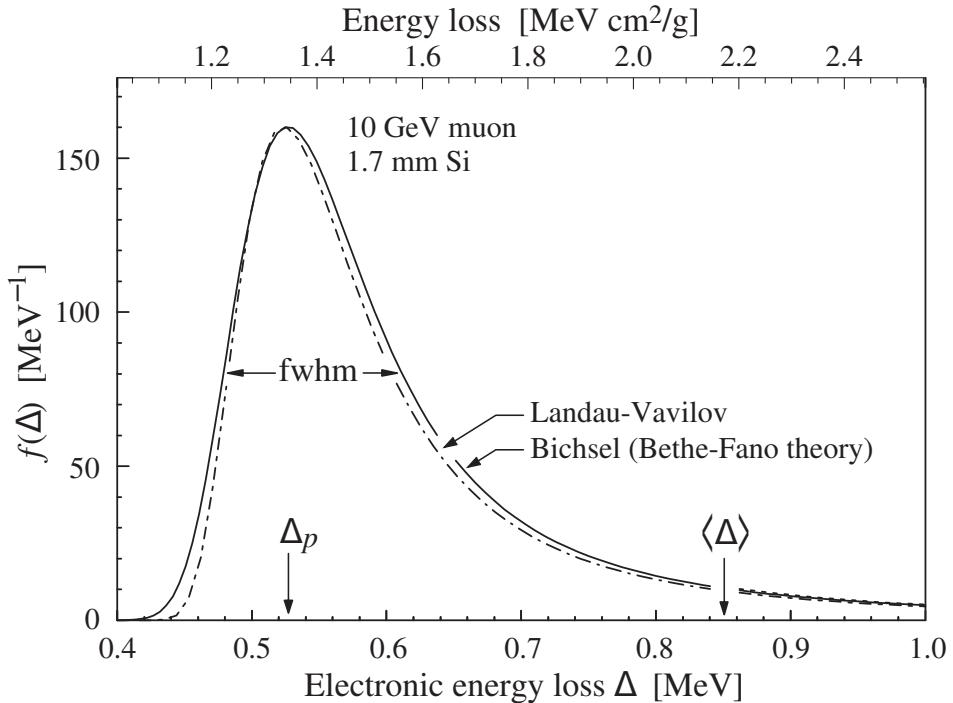

energy deposit when crossing a thin scintillator detector can be described roughly by a skewed Landau (or Landau-Vavilov) distribution [63, chap 32]. In figure 4.2 two different models are shown. The pure mathematical Landau distribution has a long tail, which causes the mean and variance of the distribution to be undefined. For this reason, to characterize the energy deposit and therefore the photon yield in a scintillator, usually the *most probable value* (MPV) is used rather than the mean, and the width at half maximum is utilized instead of the standard deviation. Of course a particle can at maximum deposit its total energy, therefore in physical reality there will be a suppression or cutoff of the tail.

Figure 4.2.: Distribution of energy deposit for a 10 GeV muon traversing 1.7 mm of silicon (equivalent to about 0.3 cm of plastic scintillator) calculated using two different models.  $\Delta_p$  is the most probable energy loss, and  $\langle \Delta \rangle$  is the mean Bethe  $\langle dE/dx \rangle$ . Adapted from [63, chap 32].

## 4.1. Plastic scintillators

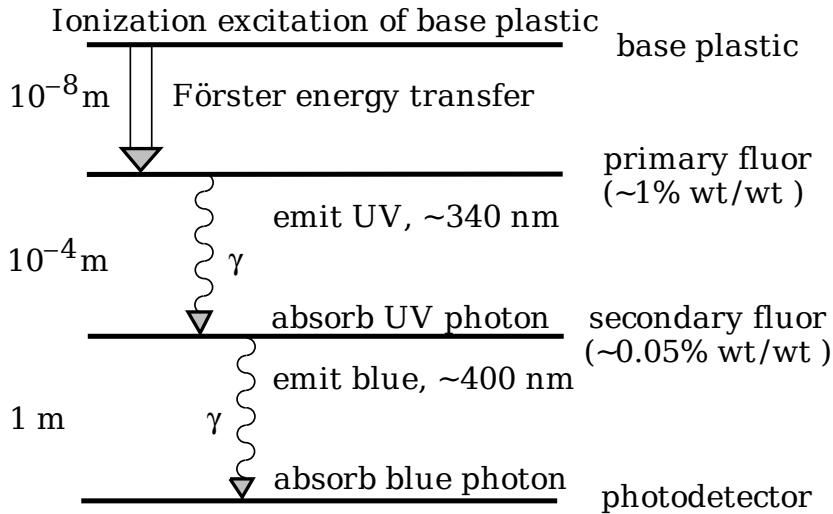

For the Aachen Muon Detector described in this thesis, plastic scintillator tiles are used. Plastic scintillators are the solution of an organic scintillator (fluorescent emitter, also called *fluor*) in a solid plastic solvent with a concentration of about 1 % [55]. The energy absorption from the passing particles mainly occurs in the base material. A part of the energy is then quickly transferred in a so-called *Förster resonance energy transfer* [36] to the actual scintillator emitting the detectable light. Often also a secondary solute in a low concentration is added as a wavelength shifter to reabsorb the primary photons (often in the UV range) and re-emit them in a different wavelength (often blue) which is easier to detect. The operation principle is sketched in figure 4.3.

During photon emission, a higher state often transits into a vibrationally excited lower state which then undergoes a radiationless deexcitation to the ground state. Due to this, good scintillators show a high transparency for their own light as the emitted photons do not have enough energy to directly excite the ground state to a higher energy level.

Figure 4.3.: Sketch of the operation principle of a plastic scintillator based detector with included wavelength shifting. The approximate length scales of the processes are shown on the left and the approximate fluor concentrations are shown on the right. Taken from [63, chap 33].

## 4.2. Photon collection and detection

To detect the light produced in a scintillator, often a PMT or an SiPM (see chapter 5) is used.

When the direct coverage of a sufficiently large surface area of the scintillator with a photon detector is not possible, there are two possibilities to increase the light output. An adiabatic light guide can be used to change the form of a surface without changing the area. This is for example often used to couple a thin but wide scintillator panel to a round PMT. By this the area covered is not changed but only its form, as Liouville's theorem has to be respected. The phase space (position spread and angle spread) covered by the ensemble of photons can not be reduced without losses. A reduction of the position spread at the expense of a larger angle spread is usually not possible as the angle spread already has its maximum possible value.

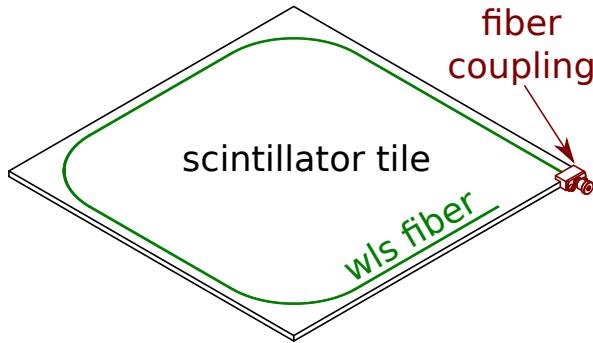

To overcome this limitation, wavelength shifting (WLS) fibers can be used. These are often glued or otherwise placed into plastic scintillators. When scintillation photons enter the fiber, they are absorbed and re-emitted with a shifted wavelength. This re-emission occurs isotropically, with about 5 % probability of the photon being contained in the fiber and being guided to its end [70]. In this application the shifting of the wavelength is just a side effect. The fiber usually has the absorption wavelength matched to the scintillation light, with the emission wavelength shifted such that the WLS fiber has an acceptable absorption length for its own light ( $\gtrsim 2 \text{ m}$ ) and that the new photons can be detected with a high efficiency by the photon sensor. A clear fiber without the isotropic photon re-emission would not cause the same collection efficiency as all photons entering through the side do not fulfill the containment condition (total reflection) of the fiber and exit it again on the other side.

The WLS fibers cause a very big compression, which allows for the readout even of big scintillator tiles by SiPMs with their relatively small area. Also, the light yield of a larger scintillator tile becomes much more homogeneous through the use of WLS fibers compared to a coupling of the photo sensor directly to a small part of a side face [69].

### **4.3. Wrapping of scintillators**

Bare scintillators lose light at the surfaces which are not covered by photo sensors. It is usually desired to (diffusely) reflect the photons back into the scintillator to allow part of them to be still detected. For this, scintillator detectors are often wrapped in a reflecting material like Teflon, Tyvek paper, aluminum foil or Titanium dioxide (as paint or co-extruded with a plastic scintillator). According to reflectivity measurements [46] the reflectance of all materials is similarly high, except for aluminum foil. Due to total reflection, which is better than any external reflection, occurring at polished scintillator surfaces, having an air gap between the scintillator and the reflector, is advantageous. Often the material that is easiest to apply, especially for a high quantity of detectors, is used.

# 5. Silicon Photomultipliers – SiPMs

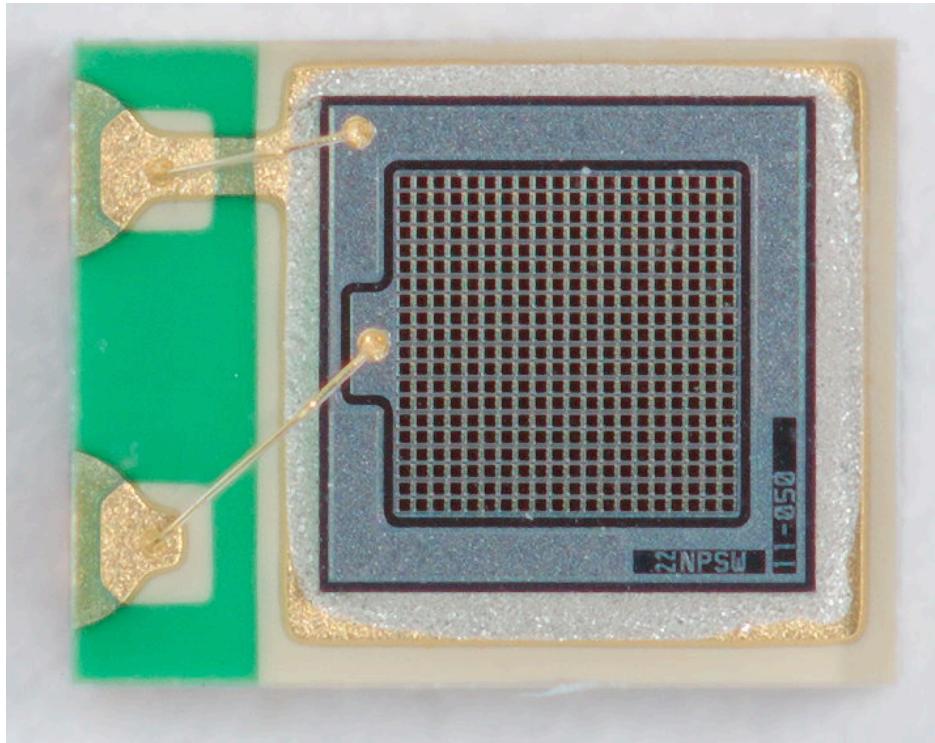

Silicon Photomultipliers (SiPMs) are semiconductor photon detectors for low light levels with a good timing resolution. They are used as light sensors in the Aachen Muon Detector to detect the photons produced in the scintillator tiles and collected by the wavelength shifting fibers. SiPMs are also marketed under different names like MPPC (Multi Pixel Photon Counter) or SPM by some manufacturers. A photograph of an SiPM is shown in figure 5.1. A short but more complete introduction to SiPMs can be found in [73].

## 5.1. Structure

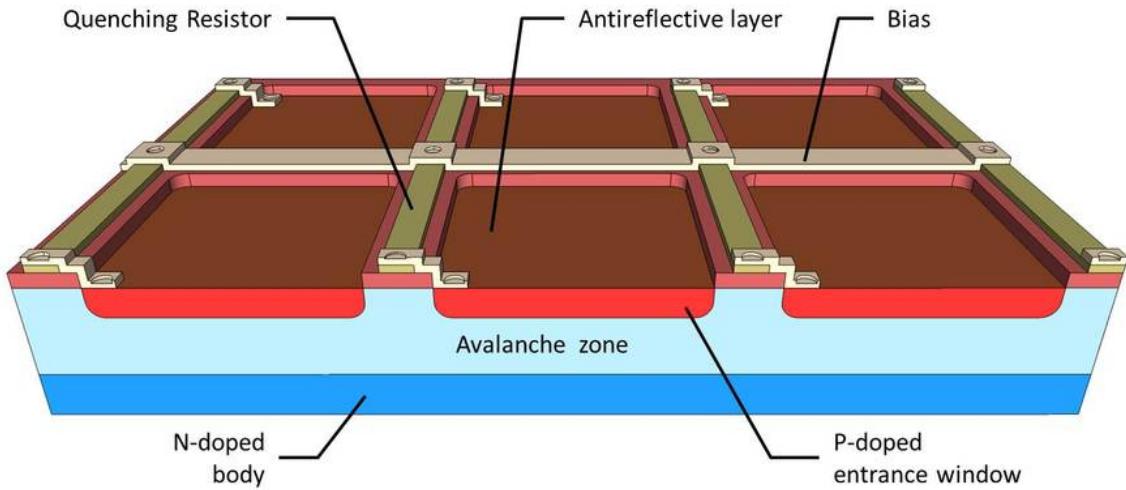

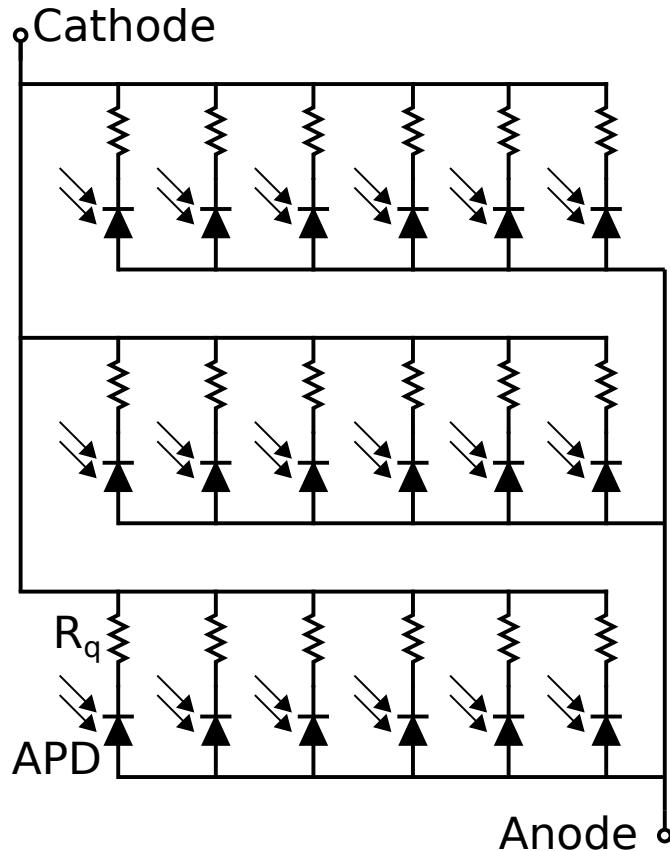

SiPMs mainly consist of an array of avalanche photodiodes (APDs), called cells, on a single silicon die, operated in Geiger mode. The general structure is shown in figure 5.2.

An APD is a diode which is operated with reverse bias, accelerating charge carriers (electrons and holes) in the depletion zone. When absorbing a photon in the silicon, an electron-hole-pair is created. The doping concentration of the silicon is often chosen such that a moderate drift field exists in an absorption zone, optimized in thickness for optimal photon absorption of a selected wavelength. Strong acceleration and amplification occurs in a small highly-doped acceleration layer, which the created electrons drift into.

When the energy gain in the electric field within the mean free path of the charge carrier is above the ionization energy of the silicon atoms, an avalanche of charge carriers is created, with the secondary charge carriers also being accelerated and causing further secondary charge carriers. This energy threshold is first reached for electrons, which leads to an avalanche developing only in the direction of the electron drift with the total number of charge carriers proportional to the number of primary electrons. This operation mode is called *proportional mode* and leads to a charge gain of  $\mathcal{O}(10^2)$ . When the energy threshold is reached for holes, also the holes can create secondary electron-hole pairs and contribute to the forming of the avalanche. This leads to a self-sustaining avalanche with a signal that is no longer proportional to the number of primary charge carriers. This is called *Geiger mode* in analogy to the famous Geiger-Müller tube gaseous detector. The energy threshold is reached at the so called breakdown voltage  $V_b$ , which is usually between 20 V and 100 V.

Figure 5.1.: Photo of a Hamamatsu S12571-50C SMD type SiPM. The active area is  $1 \times 1 \text{ mm}^2$ , the distance between the 400 cell centers is  $50 \mu\text{m}$ .

To end a cell breakdown, quenching is needed. For this, each cell has a quenching resistor, either made from polysilicon or metal, in series. The resistor causes the voltage applied to the cell to be reduced on cell breakdown below the breakdown voltage needed to supply the avalanche and therefore causes the avalanche to stop. After that, the cell, which can be modeled as a capacitor, slowly recharges (time constant  $\tau \sim 50 \text{ ns}$ , strongly depending on SiPM type) and is ready again to break through and detect photons.

The cells being operated in Geiger mode means that each detected photon in one cell causes an identical signal of  $\mathcal{O}(10^6)$  elementary charges, independent of the photon energy and also independent of the number of instantaneous photons hitting a cell. All cells are connected in parallel, which results in an output signal that is proportional to the number of simultaneously firing cells. The signal generated by one cell breakthrough is often named *photon equivalent* (p.e.).

A simplified SiPM circuit diagram is given in figure 5.3.

SiPMs are offered in different sizes (often  $1 \times 1 \text{ mm}^2$ ,  $3 \times 3 \text{ mm}^2$  or  $6 \times 6 \text{ mm}^2$ ), different cell sizes (usually between  $10 \mu\text{m}$  and  $100 \mu\text{m}$  cell pitch) and packages (through hole with conventional wire leads or surface mounted (SMD)).

Figure 5.2.: General structure of an SiPM. Taken from [51]. Light is coming in from the top. The exact layer structure differs between manufacturers and device series. For the depicted doping a positive supply voltage has to be applied at the bottom.

Figure 5.3.: Simplified SiPM circuit diagram. The order of diode and quenching resistor  $R_q$  can be inverted, depending on SiPM type.

Figure 5.4.: Possible approaches for SiPM readout.

### 5.1.1. Readout

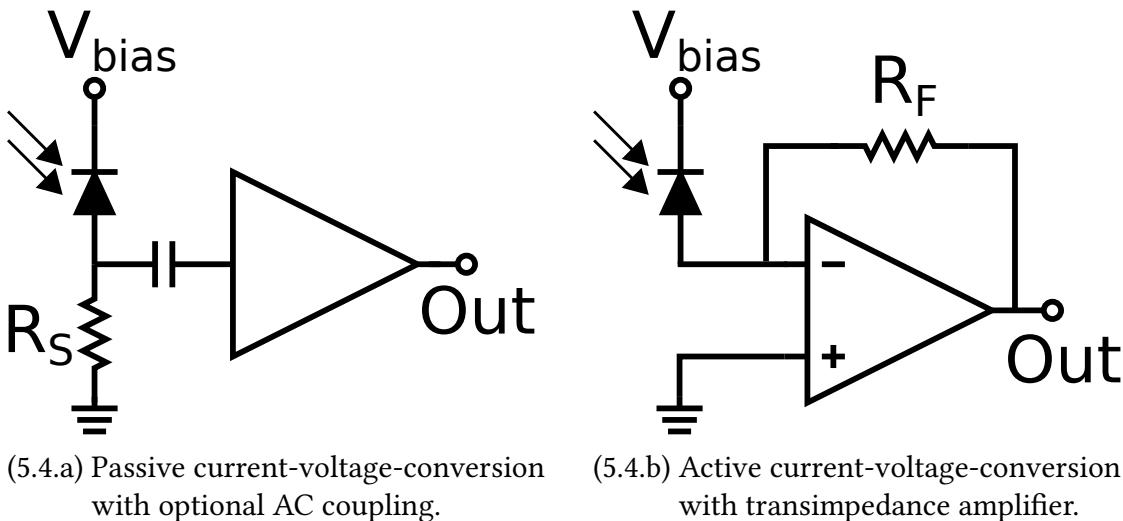

As SiPMs cause a current signal on breakdown<sup>1</sup>, it usually has to be converted to a voltage signal that can be detected. Also further amplification beyond that achieved by the avalanche is often needed. To achieve this, either passive current-voltage-conversion using a shunt resistor  $R_S$  and successive voltage amplification can be done, or active current-voltage-conversion using a transimpedance amplifier can be implemented. Both approaches are shown in figure 5.4.

The passive approach is easy to implement and has few requirements on the amplifier (type, inverting/non-inverting, linear/integrating), which does not influence SiPM operation<sup>2</sup>. If an AC coupling capacitor is installed between the SiPM and the amplifier, the ground level of the SiPM can be different from the ground level of the amplifier if desired. The main downside is that the bias voltage of the SiPM is reduced by the voltage drop over the shunt resistor  $R_S$ , which reduces the bias voltage especially for big light fluxes and increases recharge times after a pulse. The complete transimpedance<sup>3</sup> is given by  $R_S$  times the gain of the amplifier.

With the active approach, the amplifier pulls its inverting input to ground (*virtual ground*), which leads to the SiPM always seeing the complete bias voltage applied without a voltage drop. To achieve this, a high speed current feedback amplifier should be used, which is often expensive, has relatively high power requirements and noise and can lead to an undesired oscillating behavior. This of course is no relevant disadvantage if a high speed amplifier is required anyway. As only an inverting amplifier can be realized, a second inverting amplifier in series is needed if positive polarity pulses are required. No AC coupling can be achieved at the input of the

<sup>1</sup>discharge and subsequent recharging of the diode capacity

<sup>2</sup>If its input impedance is high compared to  $R_S$ .

<sup>3</sup>Used instead of a gain for current-voltage conversion. Transimpedance has the dimension of a resistance.

amplifier, which leads to the ground levels of the SiPM and of the amplifier to be identical. The complete transimpedance is given by the feedback resistance  $R_F$  of the amplifier.

## 5.2. Characteristics

The main operation parameter which influences the SiPM characteristics is the overvoltage  $V_{\text{over}} = V_{\text{bias}} - V_b$ . It is the amount by which the supplied bias voltage  $V_{\text{bias}}$  succeeds the breakdown voltage  $V_b$ .

### 5.2.1. Pulse form and time behavior

Electrically an SiPM cell can be described as a capacitor with capacitance  $C_d$  charged to  $V_{\text{bias}}$ . It is internally discharged down to the breakdown voltage  $V_b$  during the avalanche process. The pulse form is influenced mainly by parasitic capacitances of the quenching resistor and the other cells, as well as parasitic inductances and capacitances of the connections of the SiPM. After discharge, the capacitor is recharged over the quenching resistor  $R_q$  which leads to a nearly exponential tail of the pulse. The length of the tail, which is at the same time the recovery time  $\tau$  of the SiPM, is determined by  $\tau = C_d \cdot R_q$ . To a lesser degree it can also be influenced by an external shunt resistor, especially for large pulses with many simultaneously firing cells.

The recovery time of an SiPM is typically in the range of a few 10 ns to a few 100 ns, depending strongly on the cell sizes, with smaller cells (and therefore smaller capacitances) leading to faster recovery.

If a cell is hit by a second photon while it still recovers, during detection and breakthrough it behaves identical to a cell in an SiPM that is operated with the reduced overvoltage. The tail of the second pulse, which is caused by the recharge of the cell capacitor, is still determined by the full overvoltage.

### 5.2.2. Photon detection efficiency

One important feature of SiPMs is their Photon Detection Efficiency (PDE). It is the probability that a photon hitting the SiPM causes a cell breakthrough and is detected. For a given device it depends on the wavelength  $\lambda$  of the photon, the overvoltage  $V_{\text{over}}$  and the incident angle of the photon. It can be written as

$$PDE(\lambda, V_{\text{over}}, \theta) = \eta(\lambda) \cdot \varepsilon(V_{\text{over}}) \cdot F \cdot (1 - R(\theta)) \quad (5.1)$$

where  $R(\theta)$  is the angle dependent reflectivity of the silicon surface and the applied coating of the SiPM,  $\eta(\lambda)$  is the quantum efficiency of silicon,  $\varepsilon(V)$  is the avalanche probability and  $F$  is the geometrical fill factor of the sensor. The fill factor is the ratio between the active cell surfaces and the complete device surface, which is reduced

by dead space between cells needed for proper cell separation and for connections and quenching resistors. It is one important parameter to be optimized during device design. The avalanche probability gives the probability for the electron-hole pair to actually trigger a cell breakthrough and not recombine “harmlessly” before initiating an avalanche.

The PDE for SiPMs usually has a peak of between 20 % and 50 % for light with a wavelength of around 500 nm. This value varies strongly with cell sizes and device generations. The wavelength of the peak sensitivity can be shifted through changes in the device structure (layer thicknesses and doping).

### 5.2.3. Gain

The gain  $G$  of an SiPM, which is the ratio between the charge in a pulse and the charge of the electron that is created in the absorption of a photon, is given by the charge of the diode capacity divided by the elementary charge  $e$ :

$$G = \frac{C_d \cdot V_{\text{over}}}{e} \quad (5.2)$$

This means it is directly proportional to the overvoltage. For usual operation voltages and cell sizes, the gain is  $\mathcal{O}(10^6)$ .

### 5.2.4. Noise phenomena

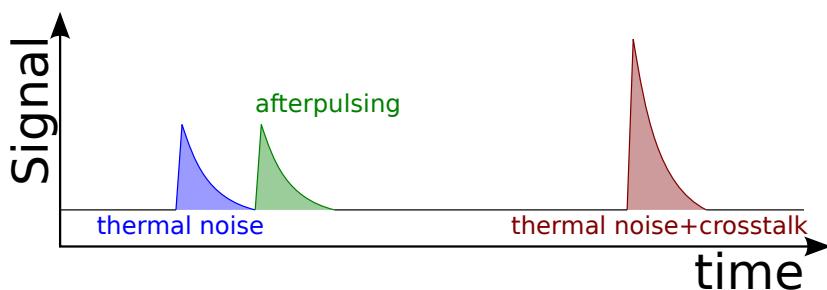

Various SiPM noise phenomena exist, which are illustrated in figure 5.5.

Figure 5.5.: Illustration of different SiPM noise phenomena.

#### 5.2.4.1. Dark noise

The most noticeable noise phenomenon is *dark noise* or *thermal noise*. It arises when electron-hole pairs are created by thermal excitation of silicon atoms without the presence of impinging photons. A cell discharge can happen, which is indistinguishable from the ones of photon detection. Through being dependent of the avalanche probability  $\varepsilon$ , it also increases with the applied overvoltage.

For current SiPM devices and usual overvoltages at room temperature, the dark noise rate is around 100 kHz/mm<sup>2</sup>.

#### 5.2.4.2. Crosstalk

While dark noise is happening randomly, other noise effects can only occur during or after a cell breakthrough and are therefore called *correlated noise*.