# RF COMMISSIONING OF THE SPIRAL2 RFQ IN CW MODE AND BEYOND NOMINAL FIELD

M. Di Giacomo, R. Ferdinand, H. Franberg, J-M. Lagniel, G. Normand, GANIL, Caen, France

M. Desmons, Ph. Galdemard, Y. Lussignol, O. Piquet, S. Sube, CEA-DRF-IRFU, Saclay, France

## Abstract

The SPIRAL2 RFQ was recently successfully commissioned at nominal voltage of 114 kV, corresponding to 1.65 Kilpatrick factor. The paper describes limitations of the RFQ main subsystems, cavity conditioning difficulties, as well as changes implemented in the LLRF and automatic procedures to simplify turn on and operation of the whole system.

## INTRODUCTION

The SPIRAL2 RFQ [1] is driven with four independent RF chains directly combined into the cavity. Cavity loss was estimated around 160-180 kW at highest operating voltage ( $\sim 114$  kV) and four 60 kW RF power chains were chosen to preserve the quadrant symmetry and to lead to realistic specifications for the circulators and amplifiers.

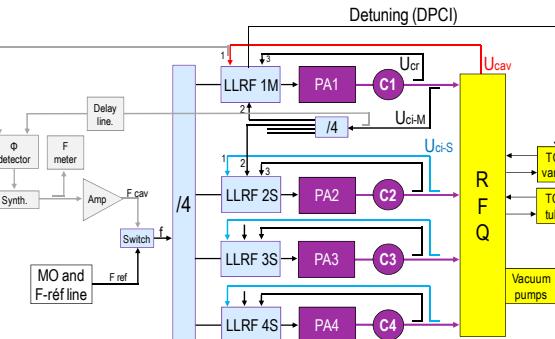

Figure 1: RFQ RF system.

The RFQ RF system is shown in Fig. 1. The LLRF defines the master/slave configuration chosen to synchronise the four chains. Master LLRF controls the amplitude and phase stability, while slave LLRF follow the incident power of the master chain. Master LLRF also measures the cavity detuning and provides tools to condition and power up the cavity as well as to recover voltage after sparks.

The system is completed by the Tuning Control System (TCS) and by external devices for the Phase Locked Loop (PLL) driving mode and by the Local Control System (LCS, not shown).

## RF SYSTEM ISSUES

### Cavity Zs Drop

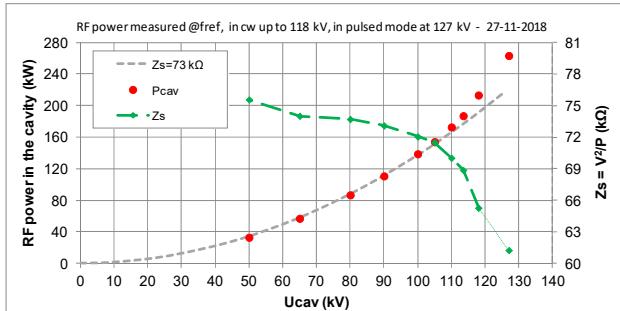

The equivalent shunt impedance  $Z_s$  was estimated around 73 k $\Omega$  after the final bead pull tuning. Unexplained drop is observed at highest voltage, as shown in Fig. 2, where the cavity loss ( $P_{cav}$ ) vs voltage ( $U_{cav}$ ) law is more than squared. Almost 5% more RF power than expected is required at nominal voltage and the deviation increases to

~12% at the highest voltage reached in continuous wave (CW) mode.

Figure 2: expected and measured  $P_{cav}$  vs  $U_{cav}$  laws, and corresponding  $Z_s$  drop.

### Cavity Maximum E Field

The electric field along the vanes depends on the voltage law, the vane modulation, the beam aperture and is enhanced at vane separation (at each 1-m section) where misalignment can still worse the situation.

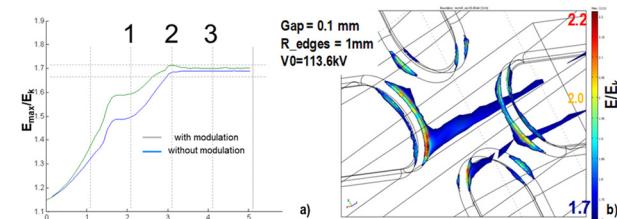

Figure 3 shows that  $E$  field rises well above  $1.7 E_k$  at vane separation # 2, 3 and 4 and stays around  $1.7 E_k$  along the forty cells of the last two meters. Each section interface counts eight spots with  $E >$  to  $2 E_k$ .

Figure 3: a)  $E$  field vs RFQ length, b) hot spots @nominal field with misaligned vanes (electrostatic simulation).

### TCS Loop Delay

The tuning control system is based on two cooling circuits, one for the cavity outer body, driven at constant temperature ( $40^\circ\text{C}$ ), and one for the four vanes, whose temperature is controlled by the tuning loop (from  $\sim 38^\circ\text{C}$  at very low voltages to  $\sim 33^\circ\text{C}$  at 115 kV). Each circuit is equipped with an actuator (3-way valve) and a pump. The actuator is rather far from the cavity and the loop delay is long (half a minute), letting a very slow feedback response: temperature stabilisation takes some 15 min at constant voltage so the system accepts only small power changes.

### Amplifier Power Margin

Each chain provides almost 10% more power than specified in CW and almost 20% more in short ( $<0.5$  ms) pulsed mode.

Power amplifiers are built in three stages: a 2-W almost

linear preamplifier, a 3-kW C-class solid state driver and an AB-class tetrode final stage. The final stage features two limitations: several percent of residual ripple (mainly coming from the filament power supply) reducing available power in feedback mode and small energy pit (8  $\mu$ F capacitance) preventing stability of the anode voltage with frequent pulses high power.

Each amplifier is designed to work with a circulator and withstands  $\sim$ 5% of reflected power. The circulator and the transmission lines introduce almost 7% loss.

### Circulator Tuning Control

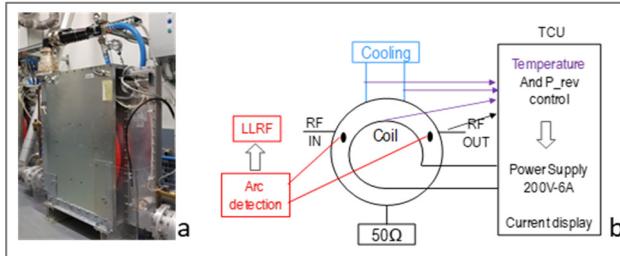

The circulators are designed for almost full reflection at all phases and are equipped with 50-kW loads. They are equipped with arc detectors interlocked to the LLRF and with a tuning control unit (TCU) that keeps them tuned (Fig. 4). The TCU uses both the device temperature and the reflected power at the input port to keep isolation well below 25 dB in bandwidth of several tens of kHz. Nevertheless, the control algorithms don't work correctly in pulsed mode and an external control capability would be required to grant isolation during pulsed RF conditioning.

Figure 4: Circulator and associated devices.

### LLRF

The digital LLRF [2] (VME64X standard) manages all fast protections, provides configurable pulse pattern for RF conditioning and configurable data logger for post event analysis. The circular buffer size is 64 MB; twenty parameters are constantly logged, the sampling rate can be changed and the highest resolution is 12 ns.

The LLRF boards can internally generate a different frequency from the reference one ( $f_{ref}=88.0525$  MHz) but the required range of  $\pm 35$  kHz was putting too much constraints on the power amplifiers. The RFQ LLRF has then been upgraded to work with an external PLL system, as shown in Fig. 1 (grey blocs).

## RF CONDITIONING ISSUES

### Multipactor

Figure 5: MP effect on the vacuum pressure.

### MC7: Accelerator Technology

#### T06 Room Temperature RF

Neither the RFQ prototype nor the RFQ suffered significant multifactor (MP). When the RFQ is ramped slowly (80 kV in 20') as in Fig. 5, three small bumps can be observed on the vacuum pressure between 45 and 75 kV, but they don't affect the voltage rise.

### Pulsed Mode RF Conditioning

RF conditioning is usually performed in pulsed mode, at voltages possibly higher than the nominal one, by increasing the power level first, and the duty cycle later, until breakdowns disappear almost completely and the CW regime is reached.

In our case, instabilities in the thermal control of both cavity and circulators prevent using duty cycles above  $\sim$ 2%. To bypass these instabilities, we pulse in Generator Driven Resonator (GDR) mode, at very low duty cycle (0.1 to 2%), so that the change in the circulator thermal load is negligible whether the cavity accepts or rejects the pulses. The driving frequency is the nominal one the circulators are tuned for, while the cavity is kept tuned by controlling the vane cooling water input temperature.

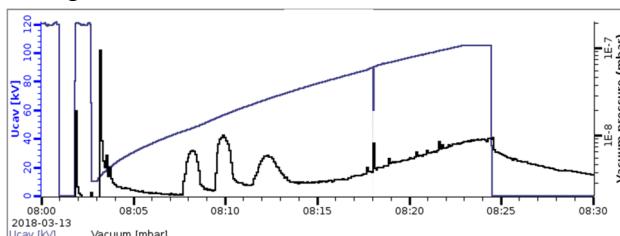

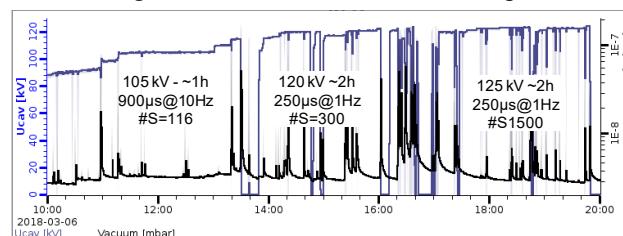

The rise from 80 to 127 kV was achieved with pulse lengths from 0.25 ms to 2 ms and repetition rates ranging from 1 to 10 Hz. Almost every voltage step generated a train of sparks which rate decreased in the next minutes. as shown in Fig. 6, where the first 10 hours are represented.

Figure 6: pulsed mode RF conditioning.

After 60 hours the cavity was able to run at 120 kV with only few sparks over 12 hours, most of them arriving in bunches after (and before) a long quiet period. This bunch trend is observed also at higher voltages and in CW/PLL mode.

### CW/PLL Mode RF Conditioning

The evolution toward higher duty cycle would require an upgrade of the circulator tuning control unit (external control port is missing) and the development of a more complex conditioning control procedure.

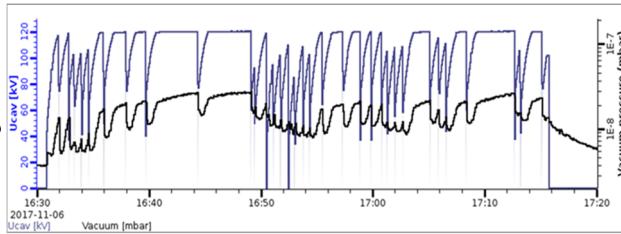

Instead, we have chosen to drive the RFQ with a slow ramp in CW and PLL mode. The PLL frequency follows the cavity resonance, which changes slowly due to the high thermal inertia, while the VME controller increases the power progressively so that the circulator TCU can follow the changes in frequency and amplitude (200 kW in  $\sim$ 1').

Figure 7 shows a typical plot of the first hours after switching from pulsed to CW/PLL mode. The spark rate rises again switching to CW, proving that copper outgassing is part of the spark rate explanation. A great time improvement was achieved rising the cavity to 55°C during the RF conditioning.

Figure 7: CW ramped RF conditioning in PLL mode.

Only few hundred arcs per day were generated in this way and it took several days to reach voltages up to  $\sim 121$  kV, stable for several minutes (15 min best score). The Zs drop and the small power margins prevented going beyond this level in CW mode. At the end of the conditioning phase, the cavity was able to work for more than 2 hours (mean value) at 118 kV, without breaking down but, sometimes, some more “violent” sparks made it impossible to recover the previous level immediately. In these cases it was necessary to go through a new phase of multiple sparks at lower voltages. As no conditioning difficulties were observed on the prototype cavity, we didn’t expect such behaviour.

Conditioning to reach operation at 114 kV took few days in pulsed mode at 125 kV, plus several weeks in PLL at 118-121 kV the first time.

## CW/GDR OPERATION AND LLRF SPARK RECOVERY PROCEDURE

Water temperatures are chosen so that the cavity reaches its nominal frequency after a few minutes at required power. The VME procedure then switches from PLL to GDR mode. Average sparking rate is still of  $\sim 0.25$  sparks/hour at 114 kV, and this rate is expected to improve after longer run time without vacuum breaks.

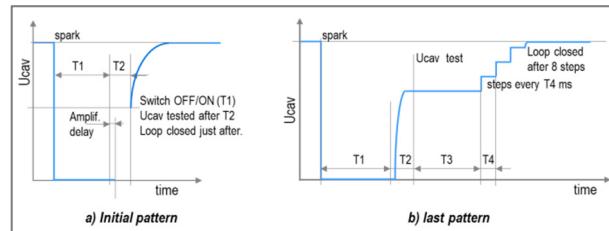

When the cavity voltage drops of more than 50% in less than  $1\mu\text{s}$ , the LLRF recognizes and counts a breakdown event in the cavity and stops the driving power for a short time T1 to let the resulting outgassing be pumped before powering the cavity again. T1 was expected to range from  $100\ \mu\text{s}$  to 1 ms and it was foreseen to power again the cavity just switching off/on an RF relay as shown in Fig. 8a. The cavity voltage presence ( $\text{Ucav} > 30\text{kV}$ ) was checked after some  $70\ \mu\text{s}$  (T2), the RF relay was switched off again in case  $\text{Ucav}$  did not rise, and the attempt was repeated no more than 10 times. This procedure revealed to be insufficient. One reason was that the cavity was not yet able to stand the voltage: either the voltage was not rising enough or a new arc was arriving just after the rising transient. A second reason was that the number of attempts could be very high (the counter is reset every time  $\text{Ucav} > 30\text{kV}$ ), making the tube anode voltage decreasing and triggering the amplifier alarm.

We upgraded several times the FPGA procedure using not only the RF switch but also the control signals of the I/Q modulator. Considering the cavity thermal inertia and the amplifier power margin, we expected to have a few seconds to recover the voltage before the cavity was too much detuned. Today, as shown in Fig. 8b, the cavity

voltage is resumed and kept at intermediate level (below 100 kV) for some hundreds of ms (T3) so that the detuning is slowed down, then it is ramped (8 steps) to the final level. The loop is closed at the end only in order to avoid as much as possible new arcs with the amplitude loop closed. The number of attempts is limited to three, so that the whole cycle doesn’t take more than few seconds.

Figure 8: Spark recovery pattern upgrade.

Conditioning to reach GDR operation at 114 kV took few days in pulsed mode at 125 kV, plus several weeks in PLL at 118-121 kV the first time. It took only few hours in pulsed mode and less of one hour in PLL, after the last vacuum break, due to the possibility to automatically switch from PLL to GDR mode and to the improvements in the spark recovery pattern that allow the LLRF recover most of the sparks.

## CONCLUSION

RF conditioning of the RFQ cavity was performed in an alternative way that releases pulsed mode constraints in the power amplifiers and the circulators. Digital LLRF flexibility and PLL have been of enormous help to solve or bypass all encountered issues.

Despite of the Zs drop, the cavity sensitivity to breakdown and the low power margin, the RFQ RF system works beyond 114 kV CW ( $\sim 200$  kW RF power) with low spark rate. The voltage is immediately recovered after sparks and very well controlled by the automatic procedure.

The spark rate increases to  $\sim 0.5/\text{hour}$  @118 kV, the maximum voltage at which available power allows to switch from PLL to GDR mode, without waiting too much time ( $< 4\ \text{min.}$ ) for thermal stabilization.

## ACKNOWLEDGEMENT

The authors wish to thank L. Valentin, J-F. Leyge and F. Pillon for implementing the PLL system, P. Baret, D. Besnier and A. Dubosq, R. Decouvelaere and R. Alves Condé and for their patient work to improve the reliability of the RFQ RF system and TCS.

## REFERENCE

- [1] R. Ferdinand *et al.*, “SPIRAL 2 RFQ Design”, in *Proc. 9th European Particle Accelerator Conf. (EPAC’04)*, Lucerne, Switzerland, Jul. 2004, paper WEPLT076, pp 2026-2028

- [2] P. De Antoni *et al.*, “The architecture of the low level RF electronics for Spiral2”, in LLRF Workshop, Knoxville, TN, USA, October 22-25, 2007