Università di Pisa

---

FACOLTÀ DI SCIENZE MATEMATICHE, FISICHE E NATURALI

Corso di Laurea Magistrale in Fisica

TESI DI LAUREA MAGISTRALE

## Ricostruzione di tracce in tempo reale su FPGA a LHC

Candidato:

**Daniele Ninci**

Relatori:

**Prof. Giovanni Punzi**

**Dott. Franco Spinella**

**Dott. Riccardo Cenci**

# Indice

|                                                                                    |           |

|------------------------------------------------------------------------------------|-----------|

| <b>Introduzione</b>                                                                | <b>1</b>  |

| <b>1 Trigger di traccia per collisionatori adronici</b>                            | <b>3</b>  |

| 1.1 Motivazioni sperimentali . . . . .                                             | 3         |

| 1.2 Il trigger e la tracciatura di quark pesanti alle macchine adroniche . . . . . | 5         |

| 1.3 Sistemi di trigger basati su tracce a CDF . . . . .                            | 6         |

| 1.3.1 Il Silicon Vertex Tracker . . . . .                                          | 7         |

| 1.3.2 L'eXtremely Fast Trigger . . . . .                                           | 9         |

| 1.4 Il Fast TracK di Atlas a LHC . . . . .                                         | 10        |

| <b>2 L'ambiente sperimentale al Large Hadron Collider</b>                          | <b>13</b> |

| 2.1 Il Large Hadron Collider . . . . .                                             | 13        |

| 2.2 Il rivelatore di LHCb . . . . .                                                | 15        |

| 2.2.1 I rivelatori di traccia . . . . .                                            | 17        |

| 2.2.2 Rivelatori per riconoscimento di particelle . . . . .                        | 24        |

| 2.2.3 Il trigger di LHCb . . . . .                                                 | 29        |

| 2.2.4 Il sistema di readout . . . . .                                              | 33        |

| 2.3 Modifiche al rivelatore di LHCb per l'upgrade del 2020 . . . . .               | 34        |

| 2.3.1 I nuovi rivelatori per LHCb . . . . .                                        | 35        |

| 2.3.2 Il nuovo sistema di acquisizione dati e di trigger per LHCb . . . . .        | 36        |

| 2.4 Ricostruzione di tracce in tempo reale ad LHC . . . . .                        | 37        |

| <b>3 Un Processore di tracce basato sull'algoritmo della Retina Artificiale</b>    | <b>41</b> |

| 3.1 L'apparato visivo nei mammiferi . . . . .                                      | 41        |

| 3.2 L'algoritmo della retina artificiale . . . . .                                 | 42        |

| 3.2.1 Differenze con altri metodi di tracciatura . . . . .                         | 45        |

| 3.3 Architettura della TPU . . . . .                                               | 46        |

| 3.3.1 La rete di switch . . . . .                                                  | 46        |

| 3.3.2 Gli engine . . . . .                                                         | 48        |

---

|          |                                                              |           |

|----------|--------------------------------------------------------------|-----------|

| 3.3.3    | Il calcolo dei parametri delle tracce . . . . .              | 50        |

| 3.4      | Studio di fattibilità di alto livello . . . . .              | 50        |

| <b>4</b> | <b>Implementazione su dispositivi a logica programmabile</b> | <b>55</b> |

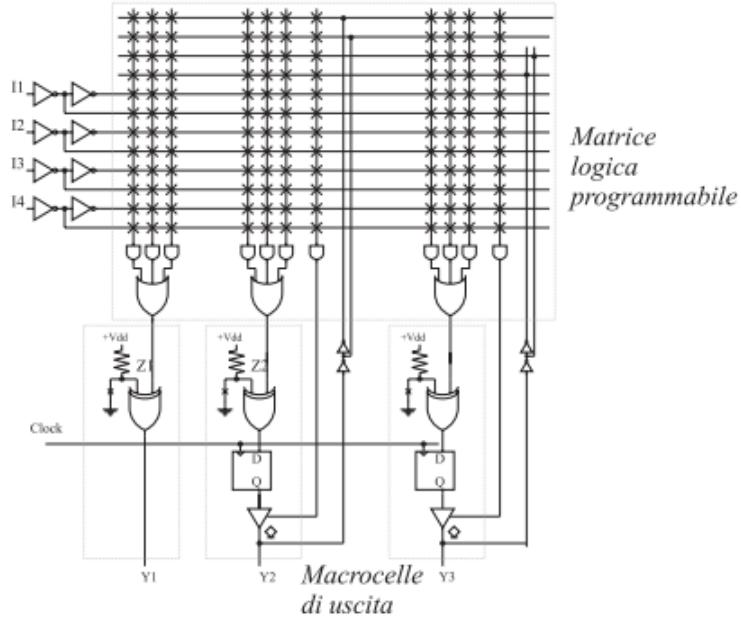

| 4.1      | Scelta della tecnologia per la TPU . . . . .                 | 55        |

| 4.2      | Introduzione ai dispositivi a logica programmabile . . . . . | 56        |

| 4.2.1    | Matrici logiche programmabili . . . . .                      | 57        |

| 4.2.2    | Dispositivi logici programmabili complessi . . . . .         | 57        |

| 4.2.3    | Matrici di porte programmabili . . . . .                     | 58        |

| 4.3      | I dispositivi a logica programmabile di Altera . . . . .     | 62        |

| 4.3.1    | Software per la progettazione del firmware . . . . .         | 64        |

| <b>5</b> | <b>Applicazione all'Inner Tracker di LHCb</b>                | <b>69</b> |

| 5.1      | Parametri della TPU applicata all'Inner Tracker . . . . .    | 69        |

| 5.1.1    | Caratteristiche dell'Inner Tracker . . . . .                 | 69        |

| 5.1.2    | Parametrizzazione del rivelatore . . . . .                   | 69        |

| 5.1.3    | Calcolo dei pesi . . . . .                                   | 70        |

| 5.2      | Scelta del dispositivo . . . . .                             | 72        |

| 5.2.1    | Stratix III . . . . .                                        | 72        |

| 5.2.2    | La scheda di readout TEL62 . . . . .                         | 73        |

| 5.3      | Progettazione logica della TPU . . . . .                     | 73        |

| 5.3.1    | Formato dati in ingresso . . . . .                           | 76        |

| 5.3.2    | Protocollo per la gestione dei dati in ingresso . . . . .    | 76        |

| 5.3.3    | Modulo per il calcolo dei pesi . . . . .                     | 78        |

| 5.3.4    | Modulo per la ricerca massimi locali . . . . .               | 79        |

| 5.3.5    | Protocollo per la gestione dei dati in uscita . . . . .      | 80        |

| 5.3.6    | Parametri di configurazione . . . . .                        | 81        |

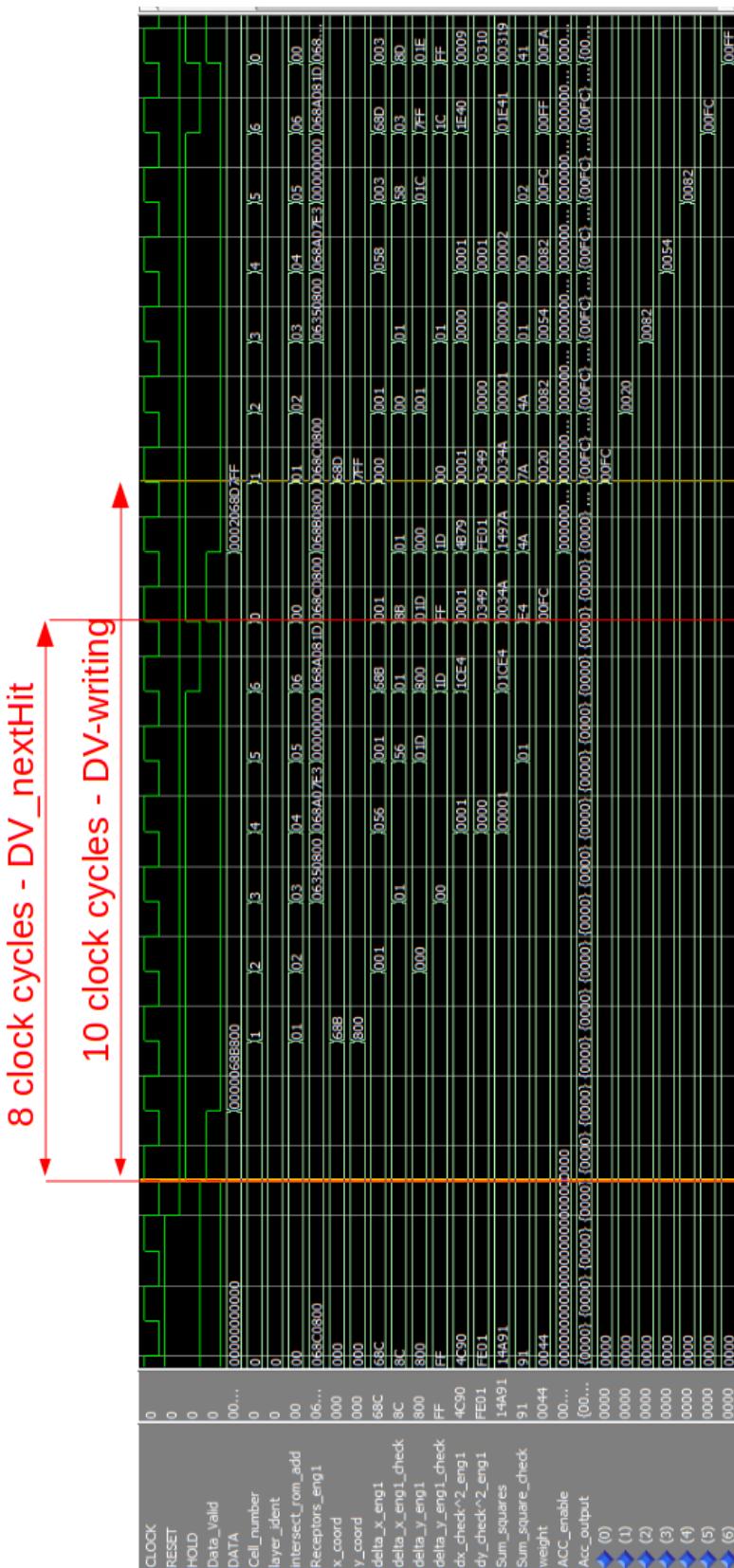

| 5.4      | Simulazione della logica della TPU . . . . .                 | 82        |

| 5.4.1    | Impostazione dei segnali in ingresso . . . . .               | 82        |

| 5.4.2    | Prestazioni temporali del dispositivo . . . . .              | 83        |

| 5.4.3    | Risposta della TPU ai segnali in ingresso . . . . .          | 87        |

| <b>6</b> | <b>Applicazione ai rivelatori VELO e UT di LHCb</b>          | <b>91</b> |

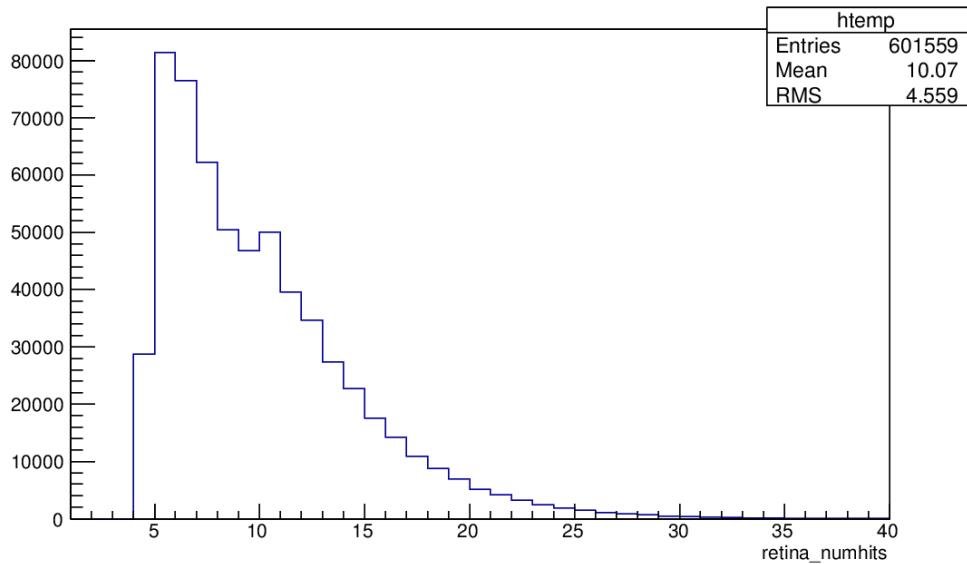

| 6.1      | Parametri della TPU applicata a VELO e UT . . . . .          | 91        |

| 6.2      | Scelta del dispositivo . . . . .                             | 94        |

| 6.2.1    | Lo Stratix V . . . . .                                       | 94        |

| 6.3      | Progettazione logica della TPU . . . . .                     | 95        |

| 6.3.1    | Formato dati in ingresso . . . . .                           | 96        |

| 6.3.2    | Protocollo per la gestione dei dati in ingresso . . . . .    | 97        |

| 6.3.3    | Modulo per il calcolo dei pesi . . . . .                     | 97        |

| 6.3.4    | Modulo per la ricerca dei massimi locali . . . . .           | 101       |

| 6.3.5    | Protocollo per la gestione dei dati in uscita . . . . .      | 103       |

| 6.3.6    | Parametri di configurazione . . . . .                        | 103       |

|                                                       |            |

|-------------------------------------------------------|------------|

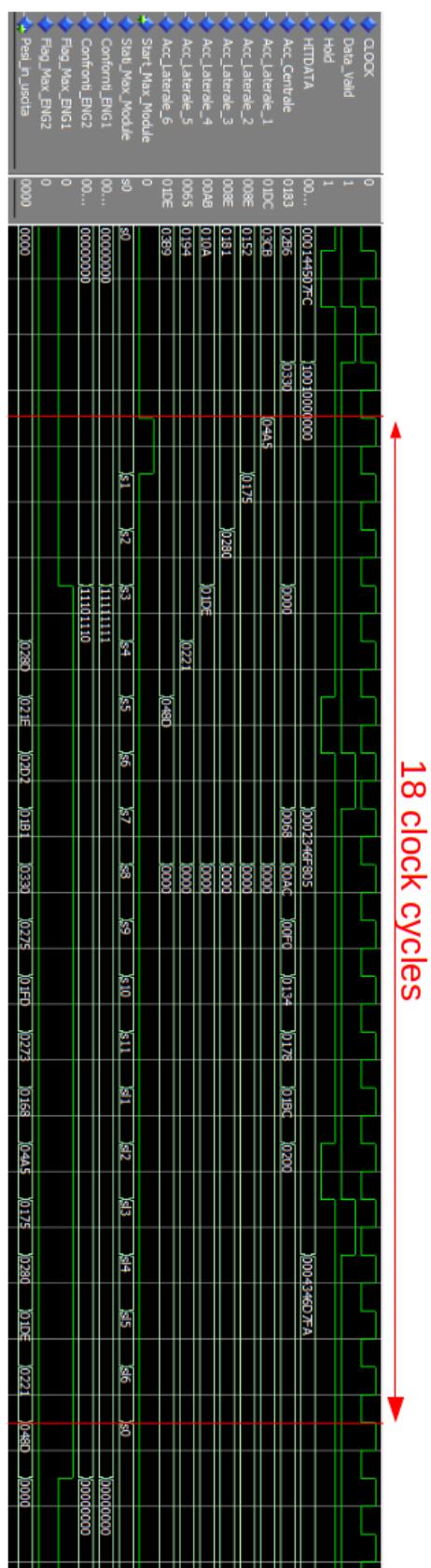

| 6.4 Simulazione della logica della TPU . . . . .      | 103        |

| 6.4.1 Prestazioni temporali del dispositivo . . . . . | 107        |

| <b>Conclusioni</b>                                    | <b>109</b> |

| <b>Bibliografia</b>                                   | <b>111</b> |

## Introduzione

Nei moderni esperimenti situati agli acceleratori adronici i sistemi di tracciatura in tempo reale e di trigger rivestono un'importanza fondamentale per la discriminare gli eventi interessanti dal fondo. Inoltre gli elevati valori di energia e luminosità raggiunti attualmente dagli acceleratori richiedono agli esperimenti lo sviluppo di tecniche avanzate e innovative per effettuare una tracciatura in tempo reale in modo efficiente.

In questa tesi abbiamo studiato l'implementazione su dispositivi a logica programmabile (FPGA) di un nuovo algoritmo di tracciatura che trae ispirazione dal funzionamento dell'apparato visivo dei mammiferi, chiamato Retina Artificiale. Questo algoritmo sfrutta il calcolo parallelo della risposta di una matrice di celle, che contengono una banca dati di tracce memorizzate, coprendo tutto lo spazio dei parametri in cui le tracce sono definite. Interpolando la risposta delle celle adiacenti, è possibile ottenere un'alta efficienza mantenendo limitato il numero di celle usate. Descriviamo in particolare il progetto di una unità di processamento di tracce (Track Processing Unit, TPU), un sistema che implementa l'algoritmo Retina Artificiale realizzato su FPGA. La TPU ha come obiettivo finale quello di ricostruire tracce con alta efficienza alla frequenza di 40 MHz, che è anche la frequenza delle collisioni raggiunta negli odierni acceleratori adronici.

L'utilizzo di questo algoritmo è in particolarmente importante negli esperimenti dedicati a misure di precisione, in cui eseguire una efficiente selezione degli eventi richiede una ricostruzione accurata delle tracce dell'evento stesso, in particolar modo quelle che coinvolgono i quark pesanti charm e bottom. Infatti, gli eventi che contengono i quark b e c, sono privi di una segnatura caratteristica (come ad esempio l'energia totale trasversa, l'energia trasversa mancante o la presenza di leptoni ad alto impulso trasverso) utile per preselezionare gli eventi. Un esempio di questo tipo di esperimenti è LHCb, situato lungo l'acceleratore LHC presso i laboratori del CERN di Ginevra, che ha come scopo lo studio della fisica dei quark pesanti. In questo caso I sistemi di tracciatura in tempo reale sono indispensabili per effettuare le misure previste dall'esperimento stesso.

Le basi di partenza per questo lavoro sono state le simulazioni delle prestazioni della TPU sia nella configurazione di LHCb prevista per il 2015, in cui la frequenza di lettura degli eventi è pari a 1 MHz, sia nella configurazione prevista per il 2020, in cui la frequenza sarà di 40 MHz. Nel primo caso si è assunto di inviare alla TPU i dati provenienti dal rivelatore Inner Tracker (IT), mentre nel secondo dal rivelatore di vertice (VELO) e dal rivelatore Upstream Detector (UT). Il lavoro di tesi consiste nell'implementazione dell'algoritmo con i parametri definiti nello studio precedente utilizzando il linguaggio di descrizione della logica di alto livello VHDL e nella successiva simulazione della logica. Infatti la simulazione della logica, anche ad uno stadio iniziale, risulta fondamentale per dimostrare la fattibilità tecnica in termini di velocità, dimensioni e costi dell'apparato.

Per l'implementazione della TPU, abbiamo utilizzato due diversi dispositivi a logica programmabile prodotti dalla ditta Altera. Nel caso del rivelatore IT abbiamo utilizzato un dispositivo di media grandezza, appartenente alla famiglia Altera Stratix III, mentre nel caso dei rivelatori VELO e UT, che costituiscono un tracciatore in 3D assai più complesso, abbiamo usato un dispositivo altamente performante, appartenente alla famiglia Altera Stratix V. La prima scelta è stata guidata dal fatto che lo Stratix III è usato in una scheda elettronica sviluppata dalla Sezione di Pisa dell'Istituto Nazionale di Fisica Nucleare. Questo permette di eseguire facilmente e in tempi brevi dei test di laboratorio su schede complete già disponibili, senza doverne progettare e costruire di nuove. Inoltre, anche se progettata per altri scopi, la scheda in questione mantiene una completa compatibilità con il sistema di acquisizione dati di LHCb e questo apre la possibilità di effettuare in futuro un test parassitico della TPU direttamente sui rivelatori di LHCb. Dall'altro lato, la famiglia Altera Stratix V è stata scelta perché comprende dispositivi all'avanguardia come quantità di celle logiche contenute e l'applicazione dell'algoritmo ai rivelatori VELO e UT ne richiede una grande quantità.

Nel primo Capitolo si discutono i benefici di un sistema di tracciatura in tempo reale, riferendoci ad alcuni esempi di sistemi di tracciatura implementati in esperimenti passati e attuali installati ai collisionatori adronici. Nel secondo Capitolo si descrive l'attuale esperimento LHCb e la configurazione prevista per l'upgrade del 2020, focalizzandoci sul sistema di trigger e dei rivelatori di traccia. Descriviamo quindi in dettaglio l'algoritmo della retina artificiale e la TPU nel Capitolo 3. Nel Capitolo 4 si introducono i dispositivi a logica programmabile, motivando la scelta dei dispositivi FPGA, e vengono descritti gli FPGA di Altera e i software utilizzati per la progettazione e la simulazione degli stessi. Nel quinto Capitolo si descrivono l'implementazione della TPU applicata all'IT, le sue prestazioni e i risultati della simulazione logica. Infine, nel Capitolo 6 si descrivono ancora l'implementazione, le prestazioni e i risultati della simulazione logica ma questa volta per l'applicazione della TPU ai rivelatori VELO e UT nella configurazione di LHCb del 2020.

## Trigger di traccia per collisionatori adronici

### 1.1 Motivazioni sperimentalì

Nel 1964, durante lo studio dei decadimenti dei mesoni  $K$  neutri a vita media lunga in stati finali di due e tre pioni [1], è stata osservata per la prima volta l'evidenza indiretta della violazione della simmetria CP, cioè la simmetria dei processi fisici sotto inversione delle coordinate spaziali (trasformazione di parità, P) e di tutti i numeri quantici intrinseci delle particelle considerate (trasformazione di coniugazione di carica, C). Nel caso dei mesoni  $K$ , la violazione di CP riguarda i quark di tipo  $s$ . Sin da allora l'asimmetria di CP è stata ampiamente studiata nell'ambito della fisica delle alte energie e molto importanti sono stati gli studi effettuati sulla fisica del *flavour* alle macchine acceleratrici, in particolare nei settori del *charm* e del *beauty*.

Infatti gli adroni formati da quark di tipo  $b$  e  $c$ , rappresentano due importanti sistemi per lo studio della violazione di CP. Gli adroni contenenti il quark  $b$  appartengono alla terza famiglia di quark e possono quindi decadere in quark appartenenti alla prima ed alla seconda famiglia. In questo modo, si possono misurare effetti maggiori della violazione di CP rispetto al sistema contenente i  $K$ . Inoltre sono accessibili cinematicamente molti più canali di decadimento, in quanto il quark  $b$  ha una massa circa 20 volte maggiore rispetto a quella del quark  $s$ . Gli adroni con il quark  $c$  sono gli unici sistemi nei quali è possibile studiare le interazioni con i quark  $u$ , che, almeno in linea di principio, possono avere una dinamica differente rispetto ai quark  $d$ . Tuttavia, la presenza di molti canali di decadimento disponibili risulta in una piccola frazione di decadimento (*branching ratio*, B.R.) dei processi individuali, richiedendo così di acquisire campioni con un elevato numero di eventi per avere alta statistica.

La fisica dei quark pesanti può essere studiata con l'utilizzo di due tipi di versi di macchine acceleratrici: le *B-factories* e gli acceleratori adronici.

Le B-factories sono collisionatori  $e^+e^-$  in cui i due fasci hanno un'energia differente, e collidendo producono la  $\Upsilon(4S)$ , che decade con un B.R. del 96% in coppie  $B\bar{B}$  [2] (dove  $B = B^0$  or  $B^+$ ) con un vertice secondario distante tipicamente  $200 - 300 \mu\text{m}$

dal punto di interazione elettrone-positrone. Utilizzando un'energia nel centro di massa leggermente al di sopra della massa della  $\Upsilon(4S)$ , ovvero della soglia di produzione del quark  $b$ , si evita la presenza di prodotti di frammentazione, imponendo delle restrizioni cinematiche che si riflettono in una riduzione degli eventi di fondo. Interazioni primarie multiple in una singola collisione dei fasci (*pile-up*) sono generalmente assenti e la molteplicità delle tracce è tipicamente di  $\sim 5$  tracce per evento. Tuttavia la sezione d'urto di produzione di una coppia  $B\bar{B}$  è limitata a  $\sigma(b\bar{b}) \sim 1$  nb. Esperimenti installati alle B-factories sono stati BABAR[3] al *Linear Accelerator Center* di Stanford (SLAC) e BELLE [4] ai laboratori KEK in Giappone.

Ai collisionatori adronici invece la sezione d'urto di produzione dei quark  $b$  e  $c$  è molto maggiore rispetto alle B-factories e il processo di produzione dominante è la produzione inclusiva non risonante  $b\bar{b}$ :

$$\begin{aligned} \sigma(p\bar{p} \rightarrow b\bar{b}X, \sqrt{s} = 1.96 \text{ TeV}) &\sim 80 \mu\text{b}, \\ \sigma(p\bar{p} \rightarrow b\bar{b}X, \sqrt{s} = 7 \text{ TeV}) &\sim 250 \mu\text{b}, \end{aligned} \quad (1.1)$$

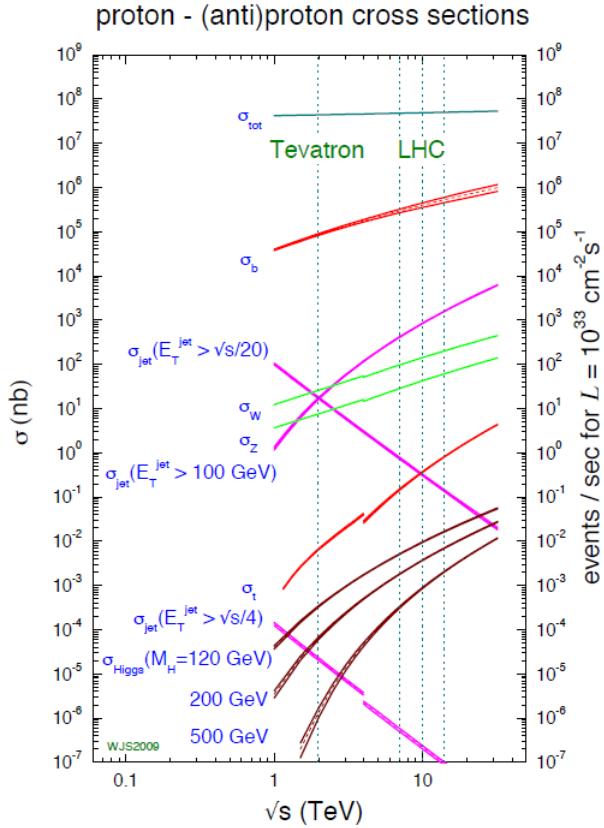

dove  $\sqrt{s}$  è l'energia nel centro di massa della collisione integrata su tutto l'angolo solido. In Figura 1.1 si mostra la sezione d'urto per processi  $p\bar{p}(\bar{p})$  in funzione dell'energia nel centro di massa. L'energia disponibile nel centro di massa  $\sqrt{s}$ , permette la produzione di tutte le specie di adroni contenenti  $b$ : i mesoni  $B^0$  e  $B^+$ , ma anche  $B_s^0$ ,  $B_c^+$  insieme ad altri barioni. Tuttavia, la sezione d'urto di produzione  $b\bar{b}$  ai collisionatori adronici è circa 3 ordini di grandezza più piccola della sezione d'urto totale inelastica protone-protone  $\sigma(p\bar{p} \text{ inelastic}, \sqrt{s} = 7 \text{ TeV}) \sim 70 \text{ mb}$  [5], col risultato di un rapporto segnale rumore tipicamente molto piccola per i canali di maggiore interesse; ad esempio per il processo  $B^0 \rightarrow K\pi$  si ha un rapporto segnale rumore dell'ordine di  $\mathcal{O}(10^{-9})$ . Simili argomentazioni sono valide anche per gli adroni  $c$ , sebbene siano caratterizzati da una sezione d'urto di produzione maggiore  $\sigma(p\bar{p} \rightarrow c\bar{c}X, \sqrt{s} = 7 \text{ TeV}) \sim 6 \text{ mb}$  [6]. Dal 2015, l'energia nel centro di massa disponibile ad LHC aumenterà a  $\sqrt{s} = 14 \text{ TeV}$ , aumentando ulteriormente le sezioni d'urto di produzione [7, 8]:

$$\begin{aligned} \sigma(p\bar{p} \rightarrow b\bar{b}X, \sqrt{s} = 14 \text{ TeV}) &\sim 500 \mu\text{b}, \\ \sigma(p\bar{p} \rightarrow c\bar{c}X, \sqrt{s} = 14 \text{ TeV}) &\sim 10 \text{ mb}, \\ \sigma(p\bar{p} \text{ inelastic}, \sqrt{s} = 14 \text{ TeV}) &\sim 100 \text{ mb}. \end{aligned} \quad (1.2)$$

**Figura 1.1:** La sezione d’urto per  $p\bar{p}$  and  $pp$  come funzione dell’energia nel centro di massa. Le discontinuità rappresentano le transizioni tra le sezioni d’urto misurate per processi  $p\bar{p}$  e  $pp$ .

## 1.2 Il trigger e la tracciatura di quark pesanti alle macchine adroniche

Agli acceleratori adroni la complessità tipica di un evento e l’alta molteplicità di traccia rappresentano le difficoltà principali, specie quando vengono effettuate le misure di precisione richieste dalla fisica del flavour. Essendo la larghezza di banda del sistema di acquisizione finita, non è possibile memorizzare tutti i dati di ogni collisione, ma è necessario selezionare gli eventi ritenuti interessanti, in modo da sfruttare al meglio le risorse di calcolo e di memoria.

I decadimenti di adroni composti da quark pesanti, possono essere selezionati applicando specifiche richieste sulle variabili cinematiche, poiché risultano avere una distribuzione diversa rispetto al segnale di fondo. Il momento trasverso  $p_t$  degli adroni che contengono  $b$  è generalmente dell’ordine di  $\langle p \rangle \approx 5 \text{ GeV}/c$ , che risulta maggiore dei valori tipici del fondo dovuto ai quark leggeri. Tuttavia, la distribuzione di  $p_t$  per gli adroni con  $b$  decresce rapidamente, con il risultato che molti adroni

hanno un basso momento trasverso e i prodotti di decadimento hanno spesso  $p_t < 1 \text{ GeV}/c$ . Quindi la selezione di particelle di basso momento risulta particolarmente importante. È possibile distinguere tra i differenti decadimenti degli adroni  $b$  tramite la loro vita media relativamente lunga  $\tau \approx 1.5 \text{ ps}$ . Questo corrisponde a un vertice di decadimento (vertice secondario) spostato dal vertice primario di circa  $c\tau \approx 500 \mu\text{m}$ .

Argomenti simili risultano validi anche per gli adroni  $c$ . I mesoni neutri contenenti il quark  $c$  hanno vite medie  $\tau \approx 0.41 \text{ ps}$ ,  $c\tau \approx 120 \mu\text{m}$ , mentre i mesoni carichi hanno  $\tau \approx 1 \text{ ps}$ ,  $c\tau \approx 310 \mu\text{m}$ . Tuttavia, avendo questa famiglia di adroni una massa più piccola, i loro prodotti di decadimento hanno un  $p_t$  minore rispetto ai prodotti degli adroni  $b$ .

Il sistema utilizzato per la selezione in tempo reale degli eventi è generalmente chiamato *trigger*. Sistemi di trigger basati sulla ricostruzione di tracce in tempo reale sono necessari per effettuare studi di fisica del flavour ai collisionatori adronici, perché è necessario acquisire eventi molto rari immersi in un fondo prodotto con sezioni d'urto maggiori di alcuni ordini di grandezza.

Il principio fondamentale di funzionamento di un sistema di trigger e di tracciatura in tempo reale riguarda la possibilità di poter suddividere in un numero finito di celle la regione di interesse dello spazio dei parametri. La configurazione degli hit sui rivelatori dovuti ad una tipica traccia può essere precalcolata e memorizzata in una banca dati (*pattern bank*). Quindi gli hit provenienti dai rivelatori sono confrontati in tempo reale con i valori memorizzati nella pattern bank. Vari autori hanno proposto soluzioni diverse riguardo ai metodi usati per la pattern bank dati e per eseguire i confronti.

### 1.3 Sistemi di trigger basati su tracce a CDF

Il Collider Detector al Fermilab (CDF) [9] è stato un rivelatore costruito per lo studio delle interazioni  $p\bar{p}$  ad alta energia, al collisionatore Tevatron nei pressi di Chicago. Nell'ultimo Run di presa dati, cominciato nel 2001, la macchina ha eseguito collisioni con energia nel centro di massa di  $1.96 \text{ TeV}$ , con una luminosità di  $2 \times 10^{32} \text{ cm}^{-2} \text{ s}^{-1}$ . L'acceleratore è stato operativo per circa 30 anni, dal 1983 al 2011, quando ha terminato le operazioni a causa dei tagli del budget e la competizione dovuta ad LHC, che ha raggiunto una maggiore energia ed una più alta luminosità .

Il rivelatore di CDF aveva una struttura concentrica, a strati successivi in cui erano installati i rivelatori di traccia al silicio, una camera a fili, i calorimetri e i rivelatori a muoni, partendo dalla regione piu' vicina al punto di interazione e andando verso l'esterno.

Gran parte dei successi di fisica raggiunti da CDF sono stati possibili grazie alle migliori apportate ai sistemi di tracciatura e di trigger. Infatti, oltre a migliorare le prestazioni dei singoli rivelatori, sono stati implementati algoritmi di ricostruzione di tracce in tempo reale per l'elaborazione delle decisioni di trigger. Inoltre lo stesso sistema di trigger venne riprogettato suddividendolo in 3 livelli: il Livello 1 e 2 erano completamente implementati in hardware, mentre il Livello 3 era gestito da software

eseguiti su una farm di PC. Gli algoritmi di tracciatura realtime sviluppati sono stati XFT (*eXtremely Fast Trigger*) per la camera a fili, ed SVT (*Silicon Vertex Trigger*) per il tracciatore al silicio.

### 1.3.1 Il Silicon Vertex Tracker

Il sistema di ricostruzione di tracce in tempo reale, applicato al tracciatore al silicio, era il *Silicon Vertex Tracker*, SVT [10]. L'idea originale è stata sviluppata all'inizio degli anni '90 [11], per poi essere implementata all'interno di CDF a partire dal 2001. Questo algoritmo ha permesso di ricostruire tracce sul piano trasverso alla linea di fascio, usando la terna di parametri composta da  $(p_t, \phi, d)$ , dove  $p_t$  è l'impulso trasverso,  $\phi$  è l'angolo azimutale della traccia e  $d$  è il parametro d'impatto, la minima distanza di avvicinamento della traccia alla linea di fascio.

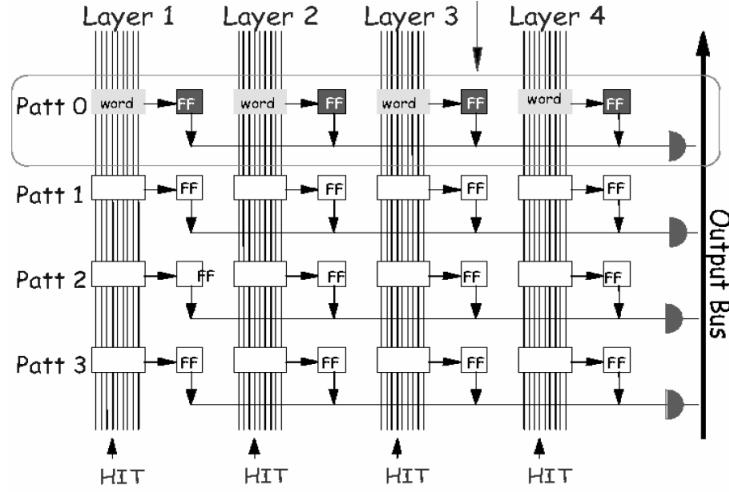

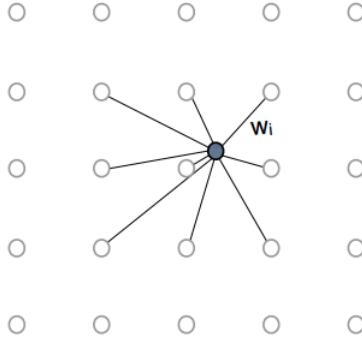

L'algoritmo era implementato in due fasi, una di confronto tra le tracce e i modelli (*pattern*) precalcolati, ed uno di *fitting* delle tracce, per il calcolo dei parametri. La prima fase era implementata utilizzando le Memorie Associative, un sistema di calcolo altamente parallelizzato. Lo schema di funzionamento della memoria associativa è mostrato in Figura 1.2. Al suo interno, sono memorizzate tutte le possibili tracce derivanti da eventi di fisica interessanti (*Patt0-Patt1...*), calcolate in precedenza attraverso una simulazione di alto livello. Ogni pattern è composto da una *word* ogni piano, cioè le coordinate di intersezione della traccia sul piano. La risoluzione di queste tracce è minore rispetto a quella offerta dal rivelatore.

Gli hit provenienti dal rivelatore sono divisi per piano di appartenenza e vengono confrontati in parallelo con tutti i possibili patterns, identificati nella figura su righe orizzontali (*Patt 0-Patt 3*). Se un hit risulta essere uguale alla corrispondente word del pattern, si alza un segnale, settando un flip-flop ad 1. L'AND logico di tali flip-flop indica se la traccia è compatibile con una di quelle precalcolate. Gli hit vengono successivamente passati allo stadio di fitting. Il calcolo dei parametri viene eseguito con un fit linearizzato sugli hit [12], utilizzando il metodo della minimizzazione del  $\chi^2$ .

La selezione del pattern tramite l'AND logico dei flip-flop è stata modificato negli anni, per evitare di perdere eventi a causa dell'inefficienza del rivelatore. Infatti si è passati ad eseguire una logica maggioritaria, in cui si accetta una traccia anche se manca una corrispondenza.

Il sistema SVT lavorava suddividendo il rivelatore in 12 settori  $\phi$ , ed eseguendo calcoli su ogni settore completamente in parallelo.

SVT è stato pensato per poter generare il trigger di secondo livello, sia a causa della velocità di lettura dei silici a CDF, sia perché il processo di estrazione dei parametri risulta non essere compatibile con i tempi richiesti dal trigger di primo livello. Questo sistema, è stato implementato totalmente via hardware, utilizzando per le memorie associative un chip costruito appositamente per questa applicazione, in tecnologia *full-custom ASIC* [13] (si veda la sezione 4.2), dato l'alto grado di parallelismo che non poteva essere supportato da altri dispositivi.

**Figura 1.2:** Schema di funzionamento di una memoria associativa.

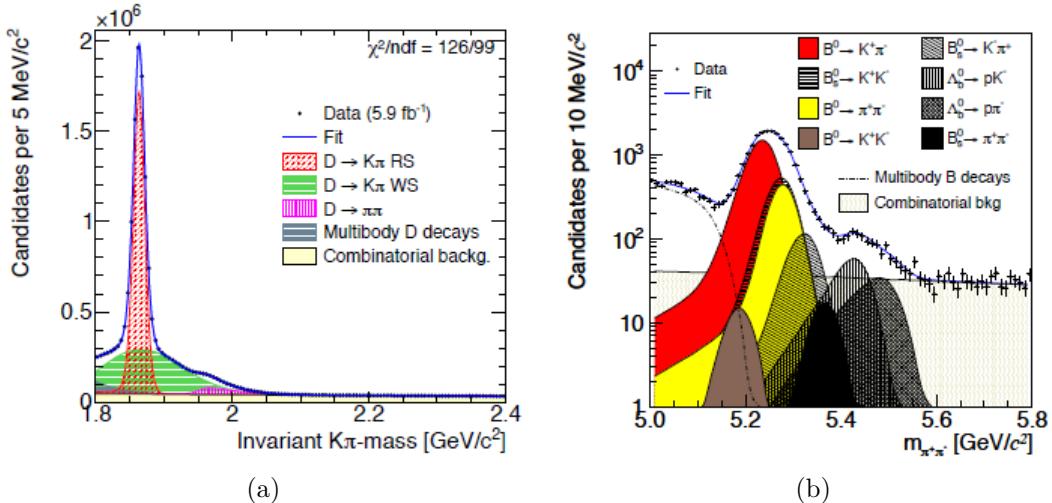

**Risultati ottenuti con SVT** Il sistema SVT è stato capace di fornire misure dei parametri di impatto con una precisione ed un efficienza paragonabile all’analisi offline, permettendo di eseguire misure sulla fisica dei quark  $b$  e  $c$  con una precisione molto elevata, per un ambiente adronico. I campioni di adroni  $B$  e  $D$  raccolti sono stati molto numerosi, ad esempio per i canali  $D^0 \rightarrow K\pi$  and  $B^0 \rightarrow K\pi$  [14, 15] come si vede in Figura 1.3.

**Figura 1.3:** Distribuzione di massa invariante per i candidati  $k\pi$  derivanti dal decadimento del  $D^0$  (a) e del  $B^0$  (b), misurati a CDF.

Gli eventi raccolti hanno permesso di effettuare per la prima volta in un ambiente adronico misure di precisione essenziali per la fisica dei quark pesanti. Ad esempio CDF ha effettuato la prima osservazione della violazione di CP diretta nei decadimenti di mesoni  $B_s$  e di barioni che contengono un quark  $b$  [16]. Inoltre è stata

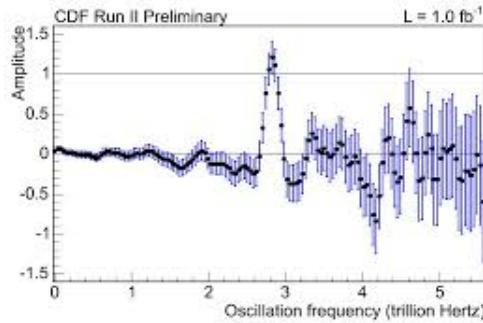

misurata l'asimmetria di CP in importanti decadimenti come  $B_s^0 \rightarrow K^- \pi^+$ , la cui rilevanza è data dalla possibilità di verificare la presenza di fisica oltre il modello standard senza una forte dipendenza dai modelli teorici. Recentemente è stata anche riportata la prima evidenza per il decadimento  $B_s^0 \rightarrow \pi^+ \pi^-$  [17], che rappresenta una classe di decadimenti interessanti per la mancanza di valide predizioni teoriche quantitative. In aggiunta CDF ha effettuato anche la misura dell'angolo gamma del triangolo CKM usando per la prima volta decadimenti  $B^\pm \rightarrow D K^\pm$  [18] raccolti ad un acceleratore adronico. Infine l'esperimento ha misurato per la prima volta l'ampiezza delle oscillazioni del  $B_s$  e la relativa frequenza [19], come mostrato in Figura 1.4, che possono essere usati per estrarre il modulo dell'elemento  $V_{ts}$  della matrice CKM.

**Figura 1.4:** Valori dell'ampiezza di  $B_s^0 - \bar{B}_s^0$ , in funzione della frequenza di oscillazione, misurati a CDF. Il grafico è stato ottenuto combinando le misure derivate dai decadimenti adronici e semileptonici.

### 1.3.2 L'eXtremely Fast Trigger

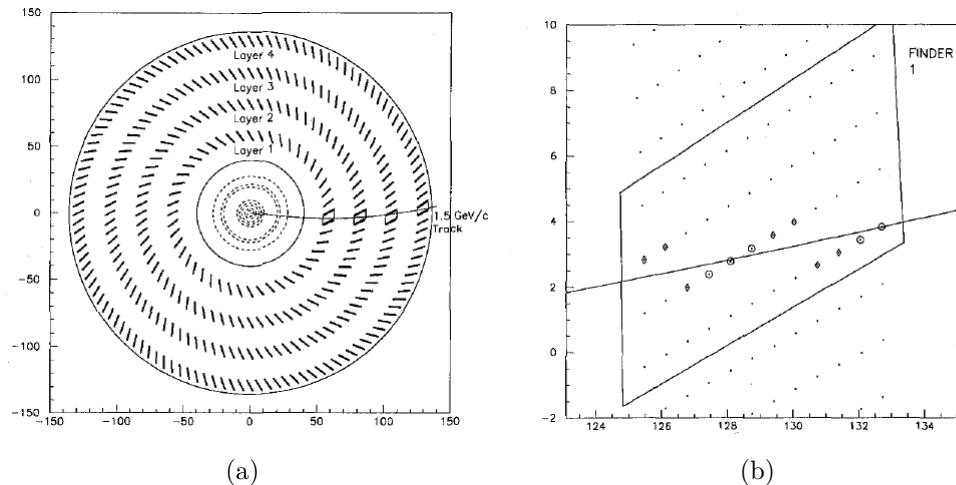

L'eXtremely Fast Tracker (XFT) [20] è stato un sistema utilizzato per ricostruire le tracce cariche nella camera a fili di CDF, il *Central Outer Tracker*, COT (Figura 1.5(a)), utilizzato per la decisione del primo livello di trigger. Il rivelatore a fili era formato da 4 strati, composti da celle di 12 fili, inclinate di  $35^\circ$  rispetto alla direzione radiale. La ricostruzione delle tracce veniva effettuata unendo 4 celle adiacenti. XFT era in grado di misurare, con risoluzione sufficiente per il trigger di livello 1, il momento trasverso e l'angolo azimutale  $\phi$  di particelle con alto impulso trasverso.

L'algoritmo di ricostruzione era diviso in due fasi distinte, la fase di ricerca (*Finder*) e di combinazione (*Linker*). Nella fase di Finder si va a confrontare la traccia trovata in ogni gruppo di 4 celle, per ciascuno strato, con un modello delle tracce interessanti precedentemente calcolato chiamato *mask*. Le mask sono formate da una combinazione di 12 fili, come si vede in Figura 1.5(b). Ogni Finder passa le informazioni trovate ad un sistema chiamato Linker, che cerca le tracce interessanti confrontando le diverse maschere individuate con una delle combinazioni calcolata

**Figura 1.5:** (a) il rivelatore COT, attraversato da una traccia con impulso di  $P_t = 1.5 \text{ GeV}/c$ . (b) un ingrandimento della traccia che attraverso un piano, identificando il gruppo di 4 celle su cui il Finder ricerca i segmenti di traccia. I punti marcati con i rombi, rappresentano quei fili che hanno generato un segnale ritardato rispetto a quelli cerchiati, a causa della diversa distanza dalla traccia. L'unione di questi punti crea una mask.

precedentemente. L'algoritmo ricercava le tracce confrontando le combinazioni di 4 maschere su 4 o di 3 su 3, per coprire eventuali inefficienze del rivelatore.

L'intero processo era eseguito in  $5.5 \mu\text{s}$ . Le informazioni ricavate da XFT erano poi combinate insieme a quelle provenienti dai calorimetri e dalle camere a muoni per elaborare il trigger di livello 1.

## 1.4 Il Fast TracK di Atlas a LHC

I buoni risultati ottenuti utilizzando l'algoritmo di SVT in un ambiente adronico, hanno portato a cercare di ricreare una soluzione simile utilizzabile ad LHC. Attualmente, l'esperimento ATLAS sta sviluppando un nuovo sistema di tracciatura in tempo reale, il processore *Fast Track* (FTK) [21], partendo dallo stesso principio di funzionamento di SVT. Questo dispositivo sarà utilizzato nel Run di LHC previsto per il 2015 per ricostruire le tracce nel tracciatore al silicio interno, per il secondo livello della catena di trigger, in un ambiente più estremo rispetto a quello di SVT. Questo è possibile usando le nuove tecnologie a disposizione che hanno permesso di migliorare il sistema SVT, in modo che possa lavorare con prestazione più elevate, in termini di velocità e quantità di dati da elaborare, a causa dell'ambiente più estremo rispetto a quello in cui lavorava CDF. Inoltre il chip che agisce da memoria associativa è stato ridisegnato, dando la possibilità di memorizzare un numero di pattern maggiore rispetto ai chip usati a CDF.

L'utilizzo di FTK può risultare necessario per la misura dei parametri di impatto a livello del trigger, uno strumento fondamentale per identificare i decadimenti provenienti dal quark  $b$ . Un altro contributo riguarderà i canali di fisica in cui particelle decadono in leptoni  $\tau$  [22]. In questo modo sarà possibile, grazie ad FTK, la misura di importanti canali di decadimento, come  $H \rightarrow b\bar{b}$  e  $H \rightarrow \tau\tau$ , oltre a migliorare la precisione nelle misure delle caratteristiche della particella di Higgs.

## L'ambiente sperimentale al Large Hadron Collider

Il settore della fisica dei quark pesanti rappresenta ancora oggi una delle principali linee di ricerca per lo studio della fisica oltre il modello standard. L'esperimento LHCb al *Large Hadron Collider* (LHC), è stato progettato appositamente per lo studio della fisica dei quark pesanti (*bottom* e *charm*), in particolare per avere l'opportunità di effettuare misure precise dell'asimmetria CP in un ambiente adronico.

In questo Capitolo descriveremo in dettaglio le condizioni sperimentali, le caratteristiche dell'esperimento attuale e le prospettive di potenziamento per il futuro.

### 2.1 Il Large Hadron Collider

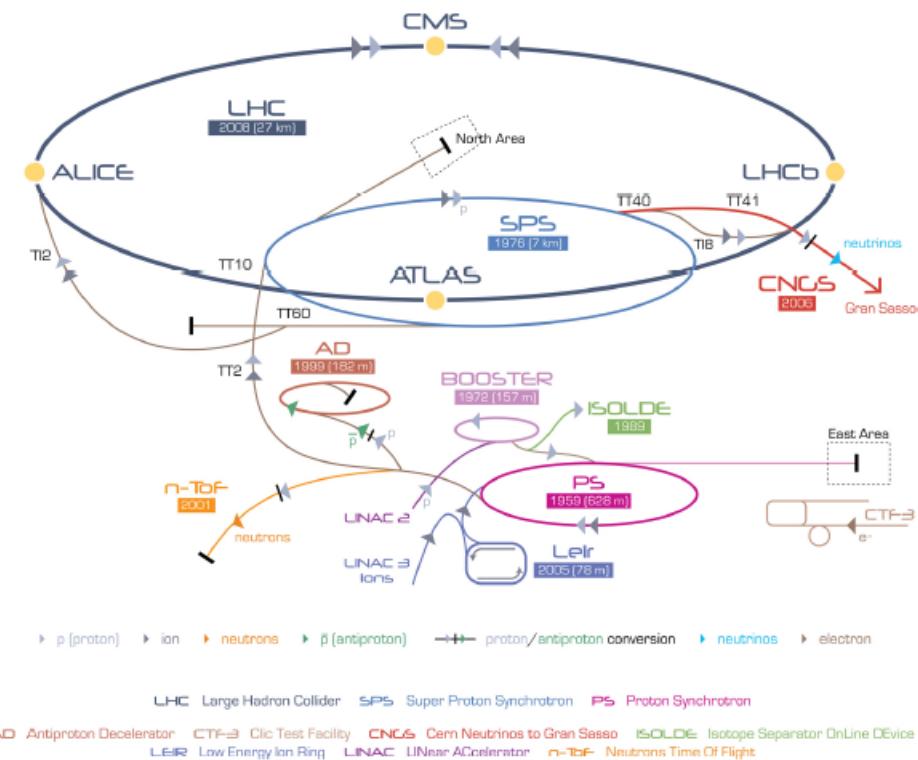

Il Large Hadron Collider (LHC) [23] è un acceleratore destinato allo studio delle collisioni tra protone-protone e tra ioni pesanti, situato ai laboratori del CERN di Ginevra, sul confine tra Svizzera e Francia. LHC è stato installato in un tunnel circolare lungo 27 Km, a circa 100 m di profondità, nella stessa cavità dove prima era alloggiato il *Large Electron Positron* (LEP). I protoni sono estratti da idrogeno gassoso e la loro energia viene gradualmente incrementata da una serie di macchine acceleratrici, di cui mostriamo uno schema in Figura 2.1. I protoni estratti vengono accelerati dal Linac 2 fino ad un'energia di 50 MeV, successivamente dal Booster fino ad un'energia di 1.4 GeV. Quindi i protoni entrano prima nel *Proton Synchrotron*(PS), raggiungendo un'energia 25 GeV, e poi nel *Super Proton Synchrotron* (SPS), raggiungendo i 450 GeV. Infine i protoni vengono immessi in LHC.

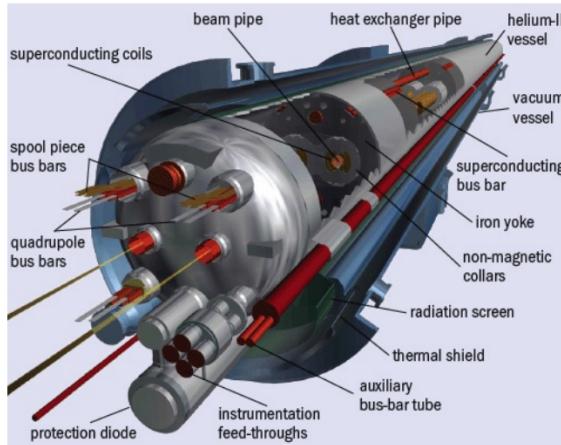

In LHC, i due fasci di protoni o di ioni, circolano in direzioni opposte in due cavità separate. I fasci vengono curvati utilizzando 1200 dipoli magnetici superconduttori lunghi 15 m, raffreddati a temperature di 1.9 K tramite 120 tonnellate di elio superfluido, i quali generano un campo magnetico di 8.3 T. Come mostrato in Figura 2.2, per accelerare i due fasci sono richieste due cavità separate, poste all'interno della stessa struttura di ferro. I dipoli magnetici sono costituiti da spire superconduttrici di Niobio-Titanio (NbTi) di diametro  $d = 6 \div 7 \mu\text{m}$ , distanziate di  $1 \mu\text{m}$ . Per realizzare tutti i dipoli magnetici sono stati impiegati 300000 Km di filo superconduttore.

**Figura 2.1:** Schema del complesso degli acceleratori del CERN.

Usando il NbTi si riescono ad ottenere delle spire con concentrazioni di metallo omogenee, essenziali per non compromettere le qualità superconduttrici. Infatti disomogenità superiori all'1 % provocherebbero una non perfetta supercondutività, che può rovinare il magnete.

I fasci collidono in quattro punti lungo l'anello, dove sono installati i quattro maggiori esperimenti di LHC. Gli esperimenti ATLAS e CMS sono classificati come *general porpose*, ovvero non hanno un obiettivo di fisica specifico, mentre ALICE ed LHCb sono stati costruiti rispettivamente per lo studio delle interazioni tra ioni pesanti e per la fisica dei quark pesanti. Altri due esperimenti minori sono stati installati lungo l'acceleratore: TOTEM, destinato per la misura della sezione d'urto totale  $pp$  e per lo studio della fisica in “avanti” ed LHCf per lo studio di particelle di interesse astrofisico.

I fasci di protoni non sono continui, ma suddivisi in pacchetti di protoni detti *bunch*. LHC prevede la possibilità di avere bunch distanti 25 ns l'uno dall'altro, il che corrisponde ad una frequenza di interazione massima di  $1/(25 \text{ ns}) = 40 \text{ MHz}$ . La configurazione dei bunch all'interno dell'anello può essere modificata a seconda dell'energia e della luminosità delle collisioni richieste [24]. La massima luminosità raggiungibile, secondo progetto, è di  $\mathcal{L} = 10^{34} \text{ cm}^{-2}\text{s}^{-1}$ , ad un'energia nel centro di massa di  $E_{cm} = 14 \text{ TeV}$ . Tuttavia fino ai Run del 2012, le interazioni sono avvenute

**Figura 2.2:** Rappresentazione di una sezione di un dipolo magnetico ad LHC.

ad un'energia di 8 TeV. Si prevede di raggiungere l'energia massima di progetto con l'upgrade di LHC previsto per il 2015. Un riassunto dei principali parametri di LHC utilizzati per le interazioni  $pp$  fino al 2012 viene mostrato in Tabella 2.1.

| Parametri                                             | Progetto             | 2010                | 2011                | 2012                |

|-------------------------------------------------------|----------------------|---------------------|---------------------|---------------------|

| Luminosità di picco ( $\text{cm}^{-2}\text{s}^{-1}$ ) | $1 \cdot 10^{34}$    | $2.1 \cdot 10^{32}$ | $3.7 \cdot 10^{33}$ | $7.7 \cdot 10^{33}$ |

| Energia protoni (TeV)                                 | 7                    | 3.5                 | 3.5                 | 4                   |

| bunch per fascio                                      | 2808                 | 368                 | 1308                | 1380                |

| Intensità dei bunch                                   | $1.15 \cdot 10^{11}$ | $1.2 \cdot 10^{11}$ | $1.5 \cdot 10^{11}$ | $1.6 \cdot 10^{11}$ |

| Distanza tra i bunch (ns)                             | 25                   | 150                 | 50                  | 25-50               |

**Tabella 2.1:** Principali parametri di LHC durante i run svolti nel 2010, 2011 e 2012, confrontati con i valori definiti dal progetto.

## 2.2 Il rivelatore di LHCb

LHCb è un esperimento dedicato allo studio della fisica dei quark pesanti [25]. Lo scopo principale è quello di ricercare evidenze indirette della fisica oltre il modello standard attraverso lo studio delle transizioni con quark pesanti e attraverso lo studio della violazione di CP e dei decadimenti rari degli adroni  $b$  e  $c$ .

LHCb è costruito come uno spettrometro a singolo braccio, con una copertura angolare intorno al fascio da 10 mrad a 300 (250) mrad sul piano di curvatura (non curvatura), corrispondente ad un intervallo di pseudorapidità<sup>1</sup>  $\eta$  compresa tra 1.8

<sup>1</sup>La pseudorapidità è definita come  $\eta = -\ln(\tan(\frac{\theta}{2}))$ , dove  $\theta$  è un angolo che si misura a partire dalla linea di fascio.

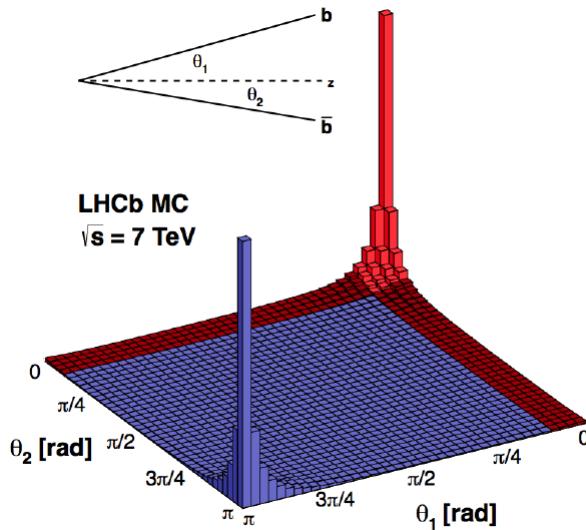

e 4.9. La copertura angolare dell'esperimento è giustificata dal fatto che la sezione d'urto di produzione per coppie di quark  $b\bar{b}$  è una funzione dell'angolo di produzione dei due quark. La sezione d'urto decresce rapidamente all'aumentare dell'angolo di produzione, il che risulta in coppie  $b\bar{b}$  prevalentemente prodotte lungo la linea del fascio, come si può vedere dalla Figura 2.3 [26, 27].

**Figura 2.3:** Correlazione angolare tra i quark  $b$  e  $\bar{b}$ , nel processo di produzione di coppie, simulata utilizzando il generatore di eventi PYTHIA.

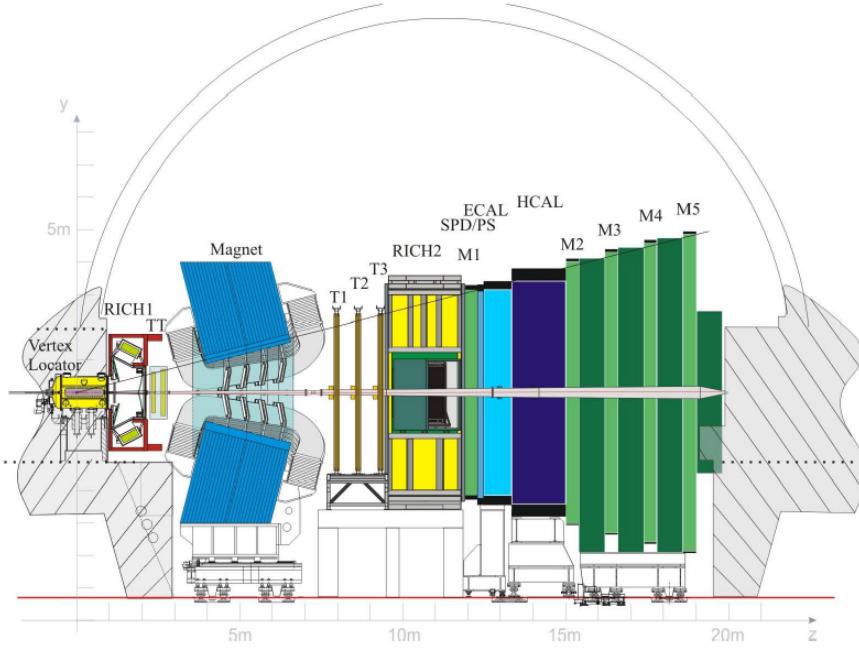

La configurazione dei rivelatori in LHCb è mostrata in Figura 2.4. Il sistema di coordinate adottato è destrorso, in cui l'asse  $x$  è diretto verso il centro dell'acceleratore, l'asse  $y$  verso l'alto e l'asse  $z$  lungo la direzione del fascio.

LHCb è formato da un sistema di tracciatura per particelle cariche e da un sistema di identificazione di particelle. Il sistema di tracciatura include un dipolo magnetico non superconduttore, un rivelatore di vertice, e due serie di tracciatori posti subito prima e subito dopo il campo magnetico (TT e T1-T2-T3). Il sistema di identificazione di particelle è formato da due rivelatori Cherenkov (*Ring Imagine Cherenkov*, RICH), un calorimetro elettromagnetico ed uno adronico, ed un sistema di rivelazione dei muoni.

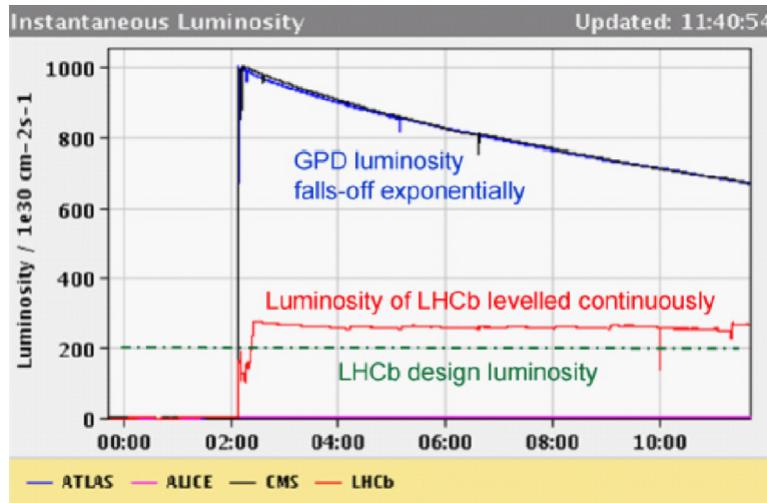

Ad ogni collisione dei fasci, il rivelatore è interessato da un alto numero di particelle provenienti dalle molteplici interazioni primarie che possono avvenire. Queste rendono difficile il compito dei sistemi di processamento degli eventi che lavorano in tempo reale, oltre a causare danni ai rivelatori dovuti alla radiazione. Nella configurazione attuale i dati provenienti dai rivelatori possono essere letti ad una frequenza massima di 1 MHz. Quindi, per diminuire la probabilità di avere un alto numero di interazioni ad ogni collisione, è stato implementato un metodo che riduce la luminosità nominale dei fasci di LHC ad un valore di  $\mathcal{L} = 4 \cdot 10^{32} \text{ cm}^{-2}\text{s}^{-1}$ , nel punto di intersezione di LHCb [28]. Questo valore massimizza la probabilità di avere un

**Figura 2.4:** Vista trasversale dell'esperimento LHCb. La linea di fascio è lungo l'asse  $z$ .

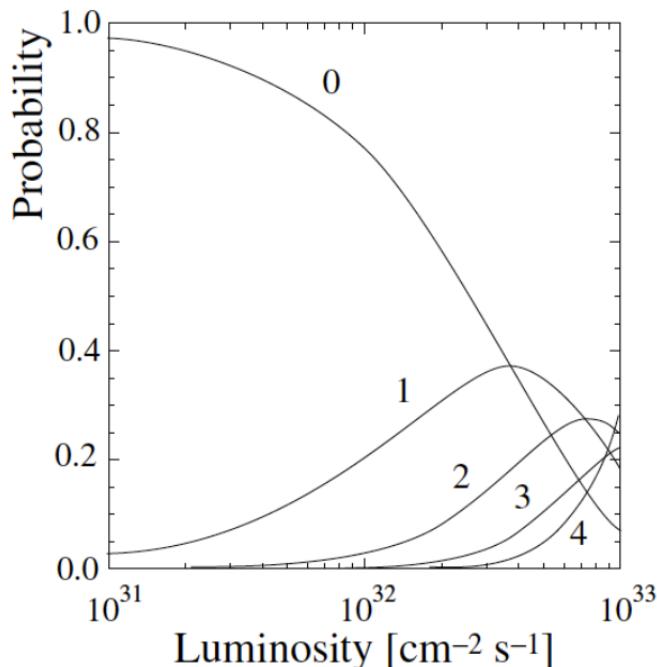

unico vertice primario per ogni collisione dei bunch, come riportato in Figura 2.5. La luminosità viene regolata modificando la distanza dei fasci sul piano orizzontale. La corrente dei fasci diminuisce in modo esponenziale durante le collisioni a causa dei protoni che finiscono fuori dall'orbita nominale ad ogni giro e vengono persi all'interno dell'anello. Quindi, per mantenere una luminosità il più possibile costante, la distanza dei fasci viene progressivamente ridotta. La dimensione trasversa dei fasci al punto di interazione è di circa  $160 \mu\text{m}$  e la distanza tra i centri varia da  $100 \mu\text{m}$  a  $40 \mu\text{m}$ . In Figura 2.6 mostriamo gli effetti del controllo della luminosità durante una tipica acquisizione dati effettuata fino al 2012. In queste condizioni, il numero medio di vertici primari delle interazioni  $pp$  per ogni collisione di fasci si riduce ad 1 [29].

A causa della geometria in avanti dei rivelatori in LHCb, solo le particelle prodotte ad alta pseudorapidità entrano nell'accettanza dell'esperimento. Le particelle prodotte all'indietro attraversano solamente il primo rivelatore di vertice, e sono utilizzate nel sistema di trigger per determinare la posizione longitudinale ed il numero dei vertici primari delle interazioni.

### 2.2.1 I rivelatori di traccia

Il sistema di tracciatura fornisce una ricostruzione della geometria delle tracce cariche, utilizzata ad esempio per il calcolo della carica e del momento delle particelle,

**Figura 2.5:** Probabilità di avere 0, 1, 2, 3 e 4 vertici primari in una collisione tra bunch, in funzione della luminosità istantanea. Questo grafico è stato ottenuto mediante una simulazione, in cui sono stati assunti bunch separati di 25 ns e una sezione d'urto  $pp$  inelastica di 80 mb. Il valore di luminosità istantanea che massimizza la probabilità di avere un unico vertice primario per ogni collisione tra bunch è di  $4 \cdot 10^{32} \text{ cm}^{-2} \text{s}^{-1}$ .

**Figura 2.6:** Confronto tra la luminosità istantanea di LHC e di LHCb durante la presa dati del Run tra il 2010 e il 2012.

misurando la posizione del vertice e la curvatura causata dal campo del dipolo magnetico.

## Il dipolo magnetico

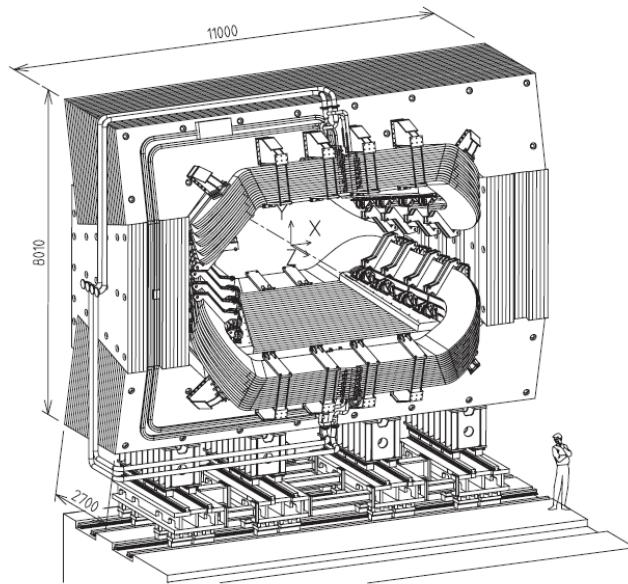

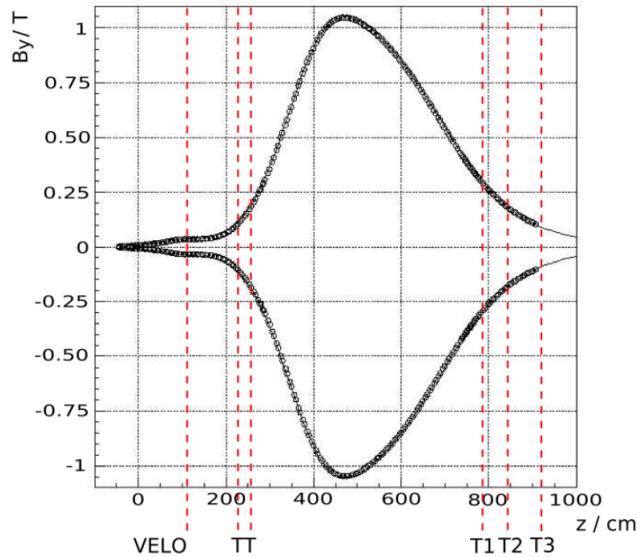

Il campo magnetico di LHCb è generato da un dipolo magnetico non supercondutture, prevalentemente diretto lungo l'asse  $y$ . Il campo magnetico integrato generato è di circa  $4 \text{ T}\cdot\text{m}$ , nella regione compresa tra  $0 < z < 10\text{m}$ , dove sono disposti i rivelatori di traccia. Il campo magnetico permette la misura del momento delle particelle con una risoluzione del  $0.4\div0.6\%$  su un intervallo di momento compreso tra  $5 - 100 \text{ GeV}/c$ . Le disomogenità del campo magnetico sul piano  $xy$  interessano un'area di circa  $1 \text{ m}^2$  e sono misurate con la precisione dell' 1%. Il campo magnetico integrato nella regione centrale tra  $z = 3 \text{ m}$  e  $z = 8 \text{ m}$  vale circa  $\int B dl = 3.615 \cdot \text{Tm}$ , mentre nella regione del VELO  $\int B dl = 0.1159 \text{ Tm}$ . A causa dell'elevata sensibilità al campo magnetico, i rivelatori RICH sono schermati, riducendo il campo magnetico interno ad un valore di  $20 \cdot 10^{-4} \text{ T}$ .

Il dipolo magnetico è formato da due avvolgimenti identici, ognuno formato da 15 piatti di alluminio carbonato spesso 10 cm. Le spire, pesanti in totale 54 tonnellate, sono installate simmetricamente intorno alla linea di fascio. Una vista del dipolo magnetico è mostrata in Figura 2.7(a). Il Dipolo ha dimensioni di  $11 \text{ m} \times 8 \text{ m} \times 5 \text{ m}$ . Il magnete dissipava una potenza elettrica di 4.2 MW, con una corrente nominale di 5.85 kA, supportando correnti fino 6.6 kA. Attualmente il campo magnetico viene periodicamente invertito, per ridurre gli effetti di sistematica nelle misure dell'asimmetria CP.

Per fornire una risoluzione elevata nella ricostruzione del momento delle particelle, l'intensità del campo magnetico deve essere conosciuta con grande precisione. Per questo motivo, la calibrazione è avvenuta con l'utilizzo di 180 sonde Hall, che hanno fornito una precisione relativa di  $4 \cdot 10^{-4}$  nell'intero volume della tracciatura. In Figura 2.7(b) viene mostrata la misura della componente  $B_y$  del campo magnetico.

### **Vertex locator detector**

Il rivelatore di vertice *Vertex Locator* (VELO) [30], misura la traiettoria delle particelle cariche nella regione più vicina al punto di interazione. Il suo scopo è di misurare i vertici primari e lo spostamento dei vertici secondari, che rappresentano una segnatura dei decadimenti di quark pesanti, con una risoluzione spaziale più elevata della tipica lunghezza di decadimento degli adroni  $b$  e  $c$  in LHCb ( $c\tau \sim 0.01 \div 1$  cm). Il VELO ricopre quindi un ruolo fondamentale nella discriminazione del segnale derivante dai quark pesanti dagli eventi di fondo, specialmente ai livelli superiori del trigger.

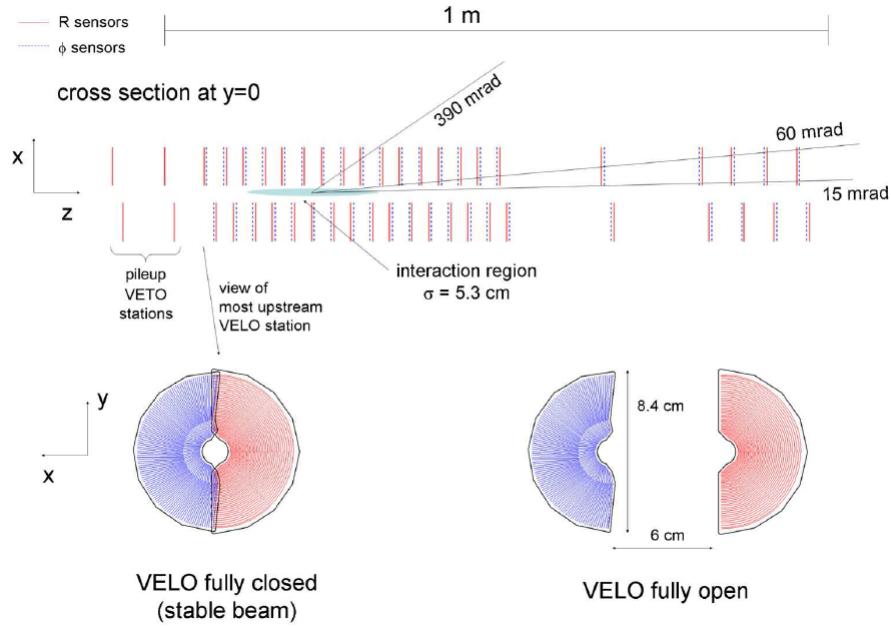

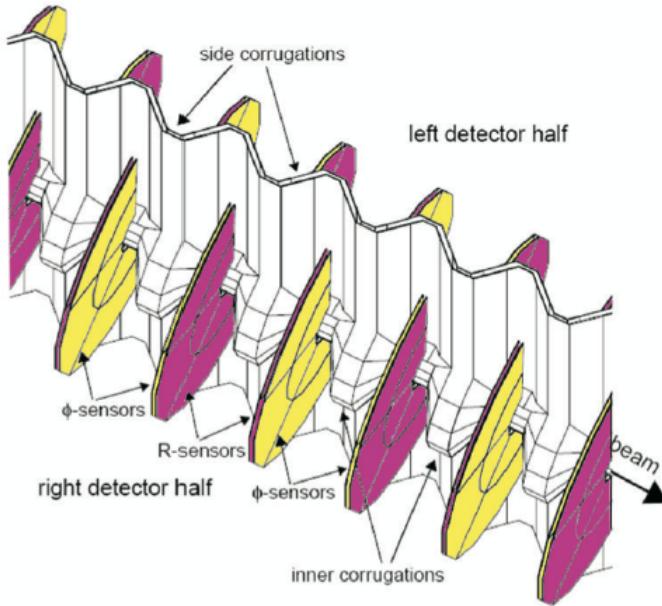

Il VELO è formato da 21 stazioni di forma circolare, installate lungo l'asse del fascio all'interno della *beam pipe*, da entrambi i lati del punto di interazione nominale lungo l'asse  $z$ . Le stazioni poste nella regione  $z > 0$  forniscono la misura ad alta precisione dei vertici, mentre le stazioni a  $z < 0$  sono utilizzate come sistema di voto per gli eventi multipli di *pile-up*, che comporta la misura della posizione dei vertici lungo l'asse  $z$  e la misura delle particelle totali prodotte all'indietro. Ogni piano del VELO è costituito da due tipi di sensori al silicio, ovvero strip radiali  $r$  e azimutali  $\phi$ , per la misura delle coordinate delle particelle. Ogni stazione è divisa in due metà mobili, chiamate moduli, come possiamo vedere in Figura 2.9. Questo permette di regolare la distanza dei sensori di silicio dal fascio, affinché non si danneggino nella fase di iniezione dei fasci. In questa fase, in cui il VELO viene detto aperto, la distanza tra i moduli è di 30 mm dall'asse del fascio, mentre durante la presa dati con i fasci stabili, in configurazione chiusa, la distanza si riduce a 5 mm. Ogni piano nella parte delle  $z$  positive è composto da sensori di tipo  $r$  e di tipo  $\phi$ , mentre le stazioni a  $z$  negativo sono costituite solamente da sensori di tipo  $r$ .

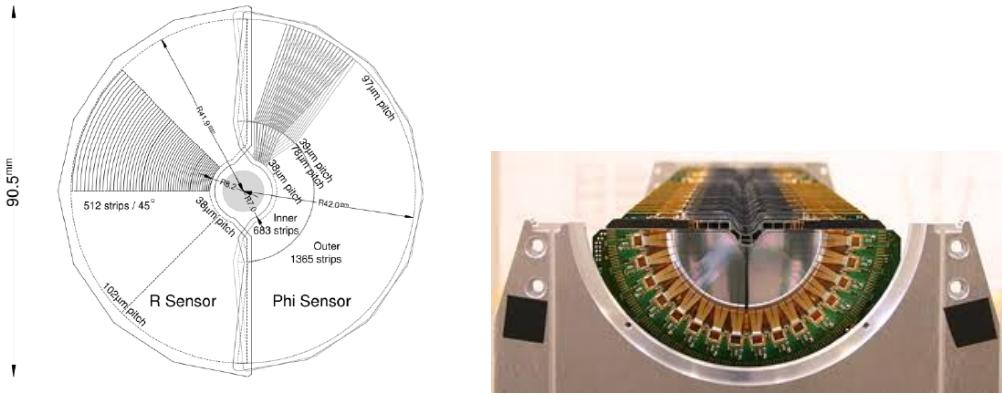

Entrambe le strip  $r$  e  $\phi$  sono centrate intorno alla posizione nominale del fascio, coprendo una regione in  $r$  compresa tra 8 mm  $\div$  14 mm, suddivisi in 4 settori da  $45^\circ$ , per ridurre l'occupazione. La geometria dei sensori è rappresentata in Figura 2.8. I sensori  $r$  consistono in strip concentriche semicircolari, con passo che si incrementa da  $38\mu\text{m}$  fino a  $102\mu\text{m}$ . I sensori  $\phi$  sono suddivisi in due regioni concentriche: quella interna copre una regione  $r = 8 \div 17.25\text{mm}$  e quella esterna  $r = 17.25 \div 42\text{mm}$  con un passo che si incrementa linearmente dal centro. Questo design è stato progettato per migliorare la risoluzione sulle tracce e per distinguere meglio il segnale dal rumore.

Per minimizzare la quantità di materiale incontrata dalle particelle che attraversano il rivelatore di veritce, il sensore deve operare nel vuoto. Questo è separato dalla beam pipe attraverso uno strato di alluminio, in modo da prevenire eventuali contaminazioni della beam-pipe dovute ai moduli. Ogni modulo del VELO è schermato dalle radiofrequenze, utilizzando una copertura chiamata *RF-foil*, come si vede

(a) Dipolo Magnetico

(b) Componente  $B_y$  del campo magnetico di LHCb, in funzione della coordinata  $z$ .

**Figura 2.7:** (a) una vista del dipolo magnetico utilizzato in LHCb. (b) la misura effettuata per la componente  $B_y$  del campo magnetico del dipolo, nei due stati di polarizzazione.

**Figura 2.8:** A sinistra: una vista della geometria del VELO e dei sensori  $r$  e  $\phi$ . Sono riportati i sensori  $\phi$  appartenenti a due moduli adiacenti, così da rappresentare due moduli stereo. A destra: i rivelatori al silicio del VELO.

in Figura 2.10. La struttura è corrugata, così da permettere la sovrapposizione dei moduli del VELO nella configurazione chiusa.

Le prestazioni del VELO sono state studiate tramite test su fascio. La risoluzione su un singolo hit è fortemente correlata con il passo dei sensori e l'angolo della traccia rispetto alla linea di fascio. La risoluzione sugli hit, varia tra  $\approx 10 \mu\text{m}$  e  $\approx 25 \mu\text{m}$  a seconda del passo delle strip.

### Tracciatori al silicio: Tracker Turicensis (TT) e Inner Tracker (IT)

I tracciatori al silicio (ST) [31] consistono in un Tracciatore Turicense (TT) e il rivelatore Inner Tracker (IT). Entrambi utilizzano sensori a microstrip di silicio, distanziate di  $\approx 200 \mu\text{m}$ . Tali rivelatori sono utilizzati per la misura della curvatura della traccia.

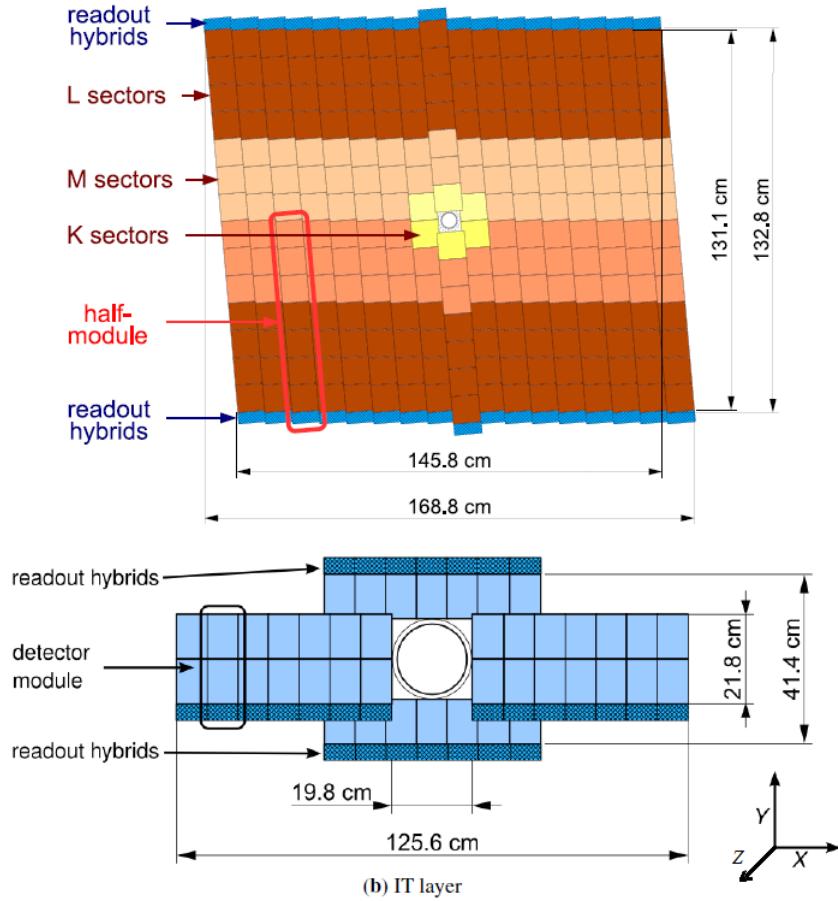

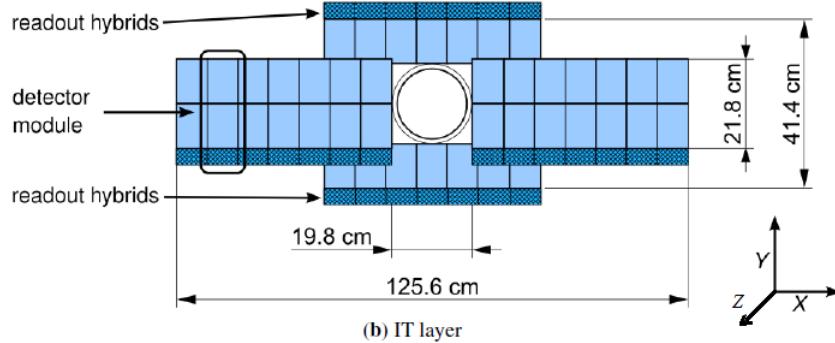

Le stazioni TT, situate nella regione antestante il dipolo magnetico, hanno un'accettanza di  $\sim 150$ - $200$  mrad sul piano di curvatura, e di  $\sim 40$ - $60$  mrad sul piano  $yz$ . Il rivelatore è stato progettato per la ricostruzione delle tracce a basso momento che vengono deviate dal campo magnetico al di fuori dell'accettanza del rivelatore interno, mentre l'IT ricostruisce le tracce che oltrepassano il campo magnetico mantenendosi vicine alla linea di fascio. Il TT è formato da un'unica stazione di rivelatori, mentre l'IT ne ha 3. Ciascuna stazione degli ST è suddivisa in 4 piani, in cui il primo e l'ultimo hanno le strips verticali, e quelli centrali hanno le strips orientate di  $+5^\circ$  e  $-5^\circ$  rispetto alla verticale. Le coordinate misurate sono  $x-u-v-x$ . In Figura 2.11 vediamo due rappresentazioni del TT e dell'IT sul piano  $xy$ . Ogni piano del TT è suddiviso in due moduli verticali, ognuno formato da 7 sensori al silicio, raggruppati in 3 settori di lettura (K, L, M).

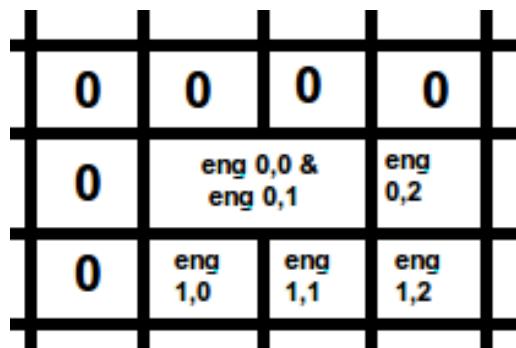

Ogni piano dell'IT è formato da 4 moduli posizionati intorno alla linea del fascio, due laterali e due assiali. I moduli assiali sono formati da una singola unità di sen-

**Figura 2.9:** Struttura del rivelatore VELO e di una stazione di tracciatura, nella configurazione aperta e chiusa.

sori, mentre quelle laterali sono formate da due unità ciascuna. La risoluzione su un singolo hit è di  $\approx 50 \mu\text{m}$ . Il TT ha una copertura in accettanza pari a quella massima dell'esperimento, mentre l'IT ne copre solamente il 2%, che equivale al 20% del totale delle tracce in LHCb.

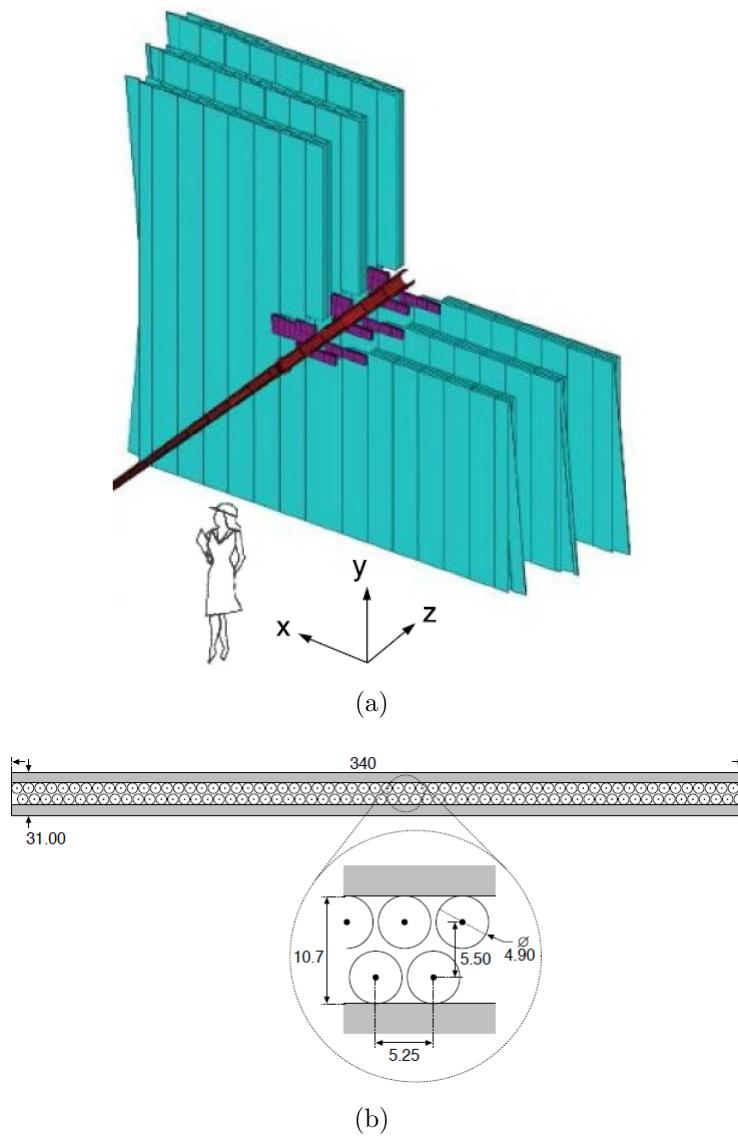

### L'Outer Tracker

L'*Outer Tracker*, OT [32], è l'ultimo rivelatore di traccia di LHCb, e ricopre una regione di accettanza fino a 300 (250) mrad nel piano di curvatura (non curvatura). L'OT è formato da camere a *straw*, grazie al quale le tracce vengono ricostruite con una risoluzione spaziale di  $\approx 200 \mu\text{m}$  in un intervallo di momento molto ampio, in quanto l'OT è usato per la ricostruzione di tracce per la regione di accettanza non coperta dall'IT. L'OT ha la stessa struttura dell'IT, come mostrato in Figura 2.12, ed è posto intorno allo stesso IT. È quindi formato da 3 stazioni di 4 piani, con gli straw tube orientati secondo la configurazione di coordinate  $(x, u, v, x)$ . Ogni piano del rivelatore consiste in una matrice di moduli ognuno contenente due piani da 64 tubi, disposti in modo da garantire la massima sovrapposizione tra due piani adiacenti. Le camere a straw sono riempite con una mistura di ArCO<sub>2</sub> in un rapporto di 70 : 30, che assicura un tempo di deriva al di sotto di 50 ns, corrispondente a due intersezioni dei fasci.

**Figura 2.10:** Struttura dei RF foil nela configurazione col VELO chiuso.

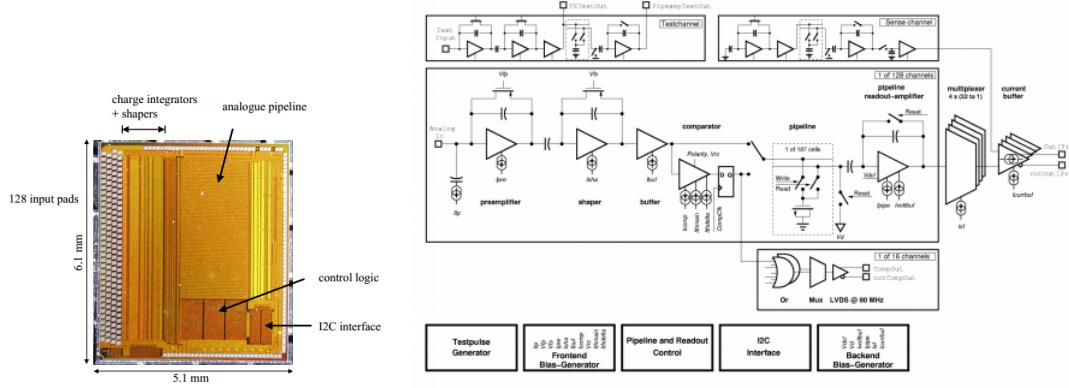

### Beetle Chip

Tutti i rivelatori al silicio utilizzano lo stesso chip di *front-end*. Il chip, chiamato Beetle Chip [33], è un chip custom, resistente alle radiazioni, progettato in tecnologia CMOS a  $0.12 \mu\text{m}$  con un front end analogico. Le specifiche temporali, come la frequenza di campionamento, sono state progettate per essere compatibili con la frequenza delle collisioni di 40 MHz di LHC. Ciascun Beetle chip ha 128 canali, ognuno possiede un preamplificatore, un formatore ed una pipeline analogica di 160 stadi, disegnata per la latenza di  $4 \mu\text{s}$  del Livello 0 di trigger. I dati vengono fatti uscire attraverso 4 uscite comandate da multiplexer a 32 ingressi, con una frequenza di 40 MHz. Con queste specifiche, un evento può essere letto in 900 ns. Il funzionamento del chip in ambiente altamente radioattivo è garantito per almeno 5 anni, sottoposto ad una dose annuale di 2 MRad. La protezione contro il cambiamento dei registri interni dovuti alle radiazioni (*single event upset*) è implementata attraverso una logica di ridondanza. La programmazione dei registri interni e il controllo delle impostazioni avviene tramite il protocollo I2C. Le funzioni interne possono essere testate tramite un impulsatore interno, di cui può essere regolata l'altezza dell'impulso.

### 2.2.2 Rivelatori per riconoscimento di particelle

L'identificazione di particelle ricopre un ruolo importante nello studio dei decadimenti della fisica del flavour. In particolare i rivelatori Cherenkov devono essere

**Figura 2.11:** Vista di un piano di coordinata  $v$  per il TT e di un piano  $x$  dell'IT.

capaci di separare i kaoni dai pioni, in modo da aiutare nell'identificazione dei processi di interesse fisico dal fondo. I calorimetri permettono invece l'identificazione di elettroni, fotoni e adroni, mentre i muoni sono riconosciuti dalle camere a muoni.

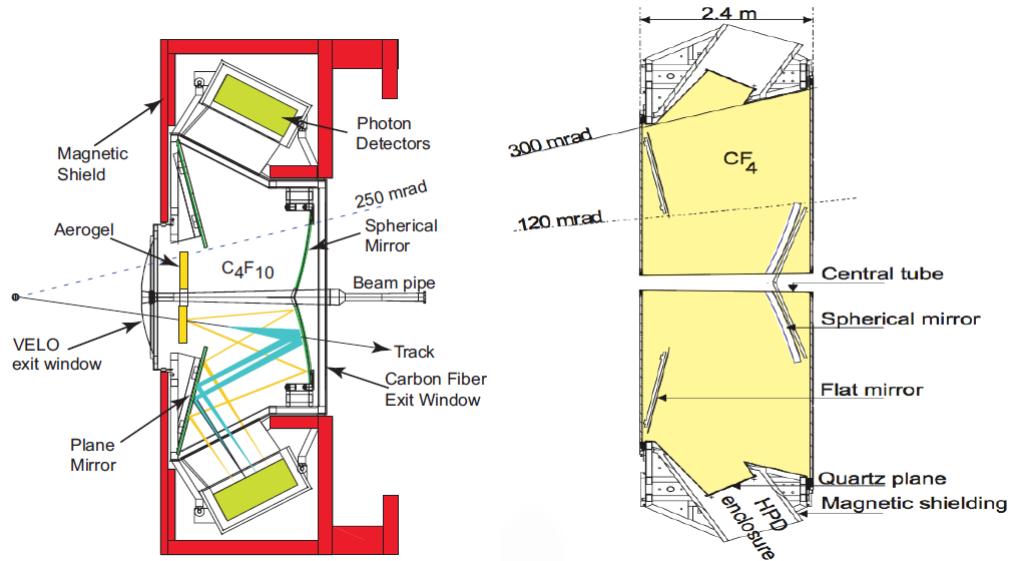

### Rivelatori Cherenkov

Due rivelatori ad anelli Cherenkov, il RICH1 e il RICH2 [34], permettono l'identificazione di particelle cariche con un momento compreso tra 1 e 100  $\text{GeV}/c$ . In particolare, il RICH1 è sensibile ad un intervallo di momento tra 1 e 60  $\text{GeV}/c$ , mentre il RICH2 è ottimizzato per valori di momento tra 15 e 100  $\text{GeV}/c$ . Questa differenza è dovuta ai diversi radiatori utilizzati: aerogel e  $\text{C}_4\text{F}_{10}$  per il RICH1 e  $\text{CF}_4$  per il RICH2. La geometria dei RICH è mostrata in Figura 2.14. Ciascun rivelatore è dotato di due tipi di specchio: uno specchio sferico per identificare l'anello Cherenkov, e una serie di specchi piatti per guidare i fotoni sugli *Hybrid Photon Detector* (HPD), posti fuori dall'accettanza dei rivelatori che sono sensibili a fotoni con lun-

**Figura 2.12:** Vista di una stazione dell'OT lungo l'asse del fascio (a) e di un modulo di straw tube (b).

**Figura 2.13:** Il Beetle Chip: una vista del chip e uno schema a blocchi delle principali operazioni.

ghezze d'onda compresa tra 200 e 600 nm. I due RICH sono entrambi schermati dal campo magnetico per permettere il corretto funzionamento degli HPD. Il RICH1 è posto nella regione che precede il magnete, ricoprendo l'intera accettanza dei LHCb, mentre il RICH2 è situato oltre le stazioni di tracciatura dell'OT, con un'acettanza compresa tra 10 mrad e  $\approx 110$  mrad. L'efficienza di separazione di  $\pi$ - $K$  è del 90%, per particelle di momento superiore a  $30 \text{ GeV}/c$ .

## Calorimetri

Il sistema di calorimetri è utilizzato per fornire informazioni per l'elaborazione del Livello 0 di trigger, distinguendo elettroni, fotoni e adroni e fornendo insieme una rozza misura dell'energia e della posizione.

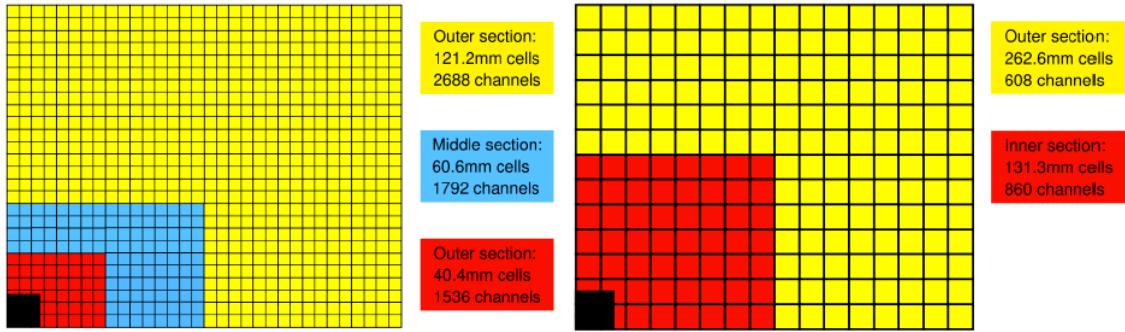

Il sistema di calorimetria è composto da un calorimetro elettromagnetico (ECAL) [35] ed uno adronico (HCAL) [36]. Sono posizionati tra le prime due camere a muoni, coprendo una regione angolare tra 25 e 300 (250) mrad sul piano di curvatura (non curvatura). Di fronte all'ECAL sono posti due ulteriori sottorivelatori: un *preshower* e una matrice di scintillatori, separati da uno spessore di piombo per la conversione di fotoni-elettroni. Questi due sono usati per rigettare pioni carichi e neutri nel trigger di elettroni di Livello 0, in modo da diminuire la contaminazione [37]. I pioni carichi vengono identificati guardando lo sviluppo longitudinale dello sciame nel preshower. Lo strato di piombo è spesso 15 mm, equivalenti a circa 2.5 lunghezze di radiazione per gli elettroni, che generano un segnale molto superiore rispetto a quello dei pioni carichi. Gli scintillatori sono usati per identificare e rigettare i pioni neutri.

I calorimetri sono divisi in 4 quadranti disposti intorno alla linea di fascio. La segmentazione laterale varia a seconda della distanza dal fascio, e risulta più grande nel calorimetro adronico, come mostrato in Figura 2.15. Lo spessore totale dell'ECAL corrisponde a 25 lunghezze di radiazione, garantendo il contenimento quasi totale

**Figura 2.14:** Geometria dei rivelatori Cherenkov, RICH1 a sinistra e RICH2 a destra. Nel primo le ottiche sono disposte verticalmente, nel secondo orizzontalmente.

dello sciame. Lo spessore del HCAL risulta invece essere di circa 5.6 lunghezze di interazione. I due calorimetri vengono letti allo stesso modo: la luce di scintillazione viene trasmessa a fotomoltiplicatori con fibre ottiche di tipo *wavelength-shifter*. L'ECAL è composto da un alternanza di strati di materiale scintillante spessi 4 mm e fogli di piombo da 2 mm, mentre l'HCAL ha il materiale scintillante spesso 4 mm alternato a spessori di ferro di 16 mm.

Le risoluzioni in energia sono di  $\sigma_E/E(\text{GeV}) \approx 10\%/\sqrt{E(\text{GeV})}$  per l'ECAL e di  $\sigma_E/E(\text{GeV}) \approx 70\%/\sqrt{E(\text{GeV})}$  per l'HCAL.

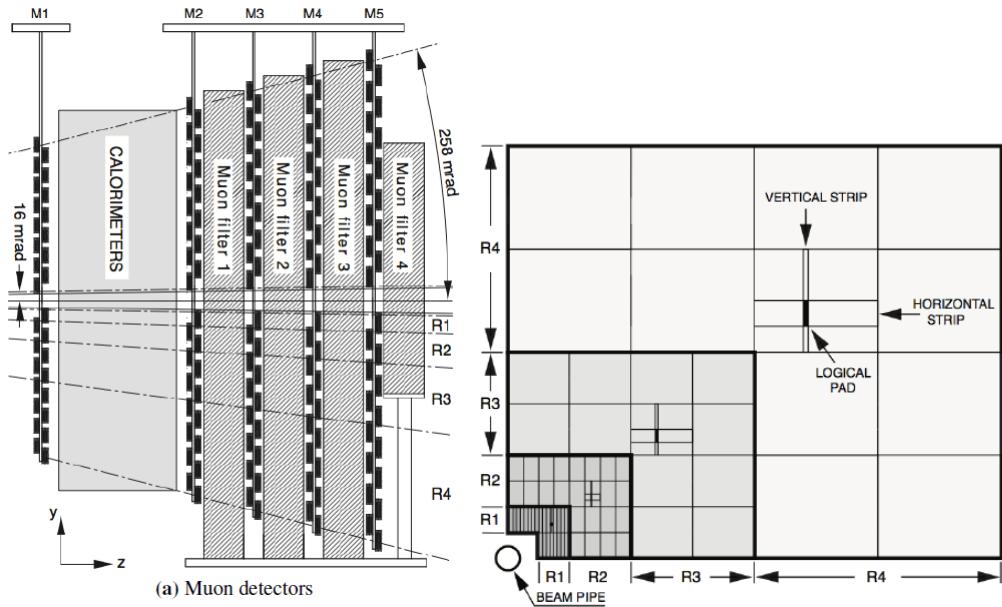

### Rivelatori di muoni

I rivelatori di muoni [38] riescono ad identificare e a misurare il momento trasverso dei muoni penetranti, per le decisioni del trigger di basso ed alto livello, con una risoluzione paragonabile a quella della ricostruzione offline. Sono formati da 5 stazioni rettangolari, identificate con M1÷M5, posizionate lungo la linea di fascio, ricoprendo un accettanza angolare da 20 (16) a 306 (258) mrad nel piano di curvatura (non curvatura). La stazione M1 situata tra il RICH2 e i calorimetri, serve per migliorare la misura del momento trasverso dei muoni rivelati nelle stazioni successive. Le stazioni M2-M5 sono situate dopo i calorimetri. Tra una stazione e l'altra è presente uno spessore di ferro spesso 80 cm, equivalente a circa 20 lunghezze di interazione, per selezionare i muoni più penetranti. Per attraversare tutte le stazioni, un muone deve avere un'energia minima di 6  $\text{GeV}/c$ . Le stazioni sono state costruite con una geometria proiettiva che parte dal nominale punto di interazione. Ogni stazione è

**Figura 2.15:** Segmentazione laterale del preshower, della matrice di scintillatori e dell'ECAL a sinistra, e dell' HCAL a destra. Viene mostrato solamente un quadrante dei calorimetri. L'area in nero rappresenta la distanza del rivelatore dalla linea di fascio.

suddivisa in quattro quadranti, disposti intorno alla linea del fascio. Come mostrato in Figura 2.16, ciascun quadrante è diviso in quattro regioni, chiamate R1-R4, identificate da uno spessore crescente allontanandosi dalla linea di fascio. La rivelazione dei muoni è effettuata usando due diverse tecnologie: rivelatori *triple gas electron multiplier* e camere proporzionali multifilo. La prima è utilizzata nella regione più interna (R1) della prima stazione, dove l'alta densità di particelle richiede un rivelatore con un elevata tolleranza alle radiazioni; le seconde sono usate nel resto delle camere. Il gas usato è una mistura di Ar, CO<sub>2</sub>, e CF<sub>4</sub> in proporzioni diverse. Le prime tre stazioni (M1-M3) contribuiscono alla misura del momento trasverso, mentre le ultime due (M4-M5) mostrano la presenza di particelle che hanno superato gli spessori di materiale assorbente. La risoluzione media sul momento trasverso è del 20%, calcolata con la ricostruzione di un muone isolato.

### 2.2.3 Il trigger di LHCb

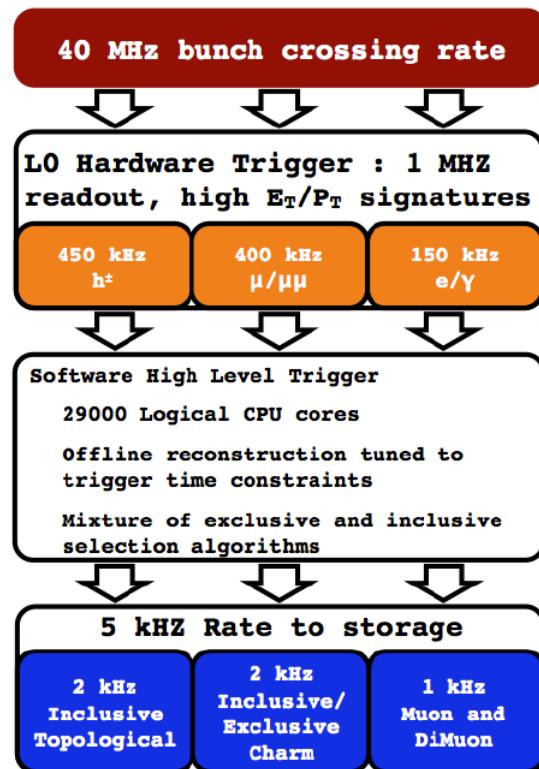

Il trigger di LHCb [39] è stato concepito per effettuare una selezione efficiente dei decadimenti dei quark pesanti, rispetto al grande fondo dovuto ai quark leggeri, passando dai 40 MHz delle collisioni a 5kHz, che è la frequenza massima con cui è possibile memorizzare gli eventi. Solamente una piccola frazione degli eventi, circa 15 kHz, contiene decadimenti derivanti dagli adroni *b* dentro l'accettanza di LHCb. La frequenza di decadimenti di adroni *b* interessanti è più bassa, equivalente a pochi Hz. Il corrispondente valore per adroni *c* è circa 20 volte maggiore. Diventa quindi cruciale per il trigger riuscire ad eliminare il fondo fin dai primi stadi dell'acquisizione.

Il trigger di LHCb è suddiviso in due stadi: il Livello 0 (L0) e il trigger di alto livello (*High Level Trigger*, HLT). La struttura a doppio livello permette una ricostruzione veloce e parziale degli eventi al livello 0, ed una ricostruzione più complessa ad alto livello. Il livello L0 è completamente implementato su elettronica dedicata,

**Figura 2.16:** A sinistra: una vista laterale del rivelatore di muoni. A destra: la geometria di un quadrante delle camere, in cui ogni rettangolo rappresenta una camera. Le dimensioni lineari e la segmentazione di R1, R2, R3 ed R4 stanno nel rapporto 1:2:4:8.

lavorando in modo sincrono con la frequenza delle collisioni. Tramite l'L0, utilizzando le informazioni dei calorimetri e delle camere a muoni, si riesce abbattere il flusso di dati da 40 MHz fino a 1.1 MHz, che risulta essere la massima velocità a cui gli eventi possono essere letti dai rivelatori. HLT invece viene implementato in un sistema software, in cui si esegue una selezione più fine degli eventi, basata sull'utilizzo di tutti i rivelatori e riducendo il flusso di dati a 5 kHz, la massima frequenza a cui gli eventi possono essere memorizzati. In Figura 2.17 mostriamo il flusso del trigger di LHCb.

## Il trigger di Livello-0

Il trigger L0 è effettuato combinando canali indipendenti, *L0 pile-up*, *L0 muon*, *L0 calorimeter* ed *L0 hadron*. La decisione di livello 0 viene effettuata attraverso l'OR logico del risultato dei tre rami, con il risultato di ridurre il flusso dati da 40 MHz ad 1.1 MHz.

L'unità di decisione del L0 fornisce la decisione globale di livello 0, distribuendola a tutte le schede del readout, e successivamente alle schede di front-end. Questo è necessario in quanto le informazioni di alcuni rivelatori vengono fornite solamente dopo la generazione dell'L0. I dati di tutti i rivelatori vengono memorizzati in registri formati da una pipeline analogica, letta con una latenza fissata a  $4\ \mu\text{s}$ , in cui viene presa la decisione del trigger di livello 0. Queste specifiche sono state raggiunte

**Figura 2.17:** Il flusso del trigger di LHCb, con riportate le selezioni e la frequenza degli eventi all'ingresso di ogni stadio.

costruendo schede elettroniche *custom* per l'intero sistema L0, facendo largo uso di strutture parallele ed a pipeline per concludere il processamento entro la latenza fissata. A questo stadio, sono processate le informazioni derivate dai calorimetri e dai rivelatori a muoni.

Il trigger Level 0 pile-up contribuisce alla misura di luminosità e non è utilizzato per la selezione di eventi interessanti. Le informazioni sono quelle derivanti dalle stazioni di voto del VELO, con le quali vengono misurati il pile-up e la molteplicità delle tracce.

Il trigger Level 0-muon utilizza le informazioni delle 5 stazioni del rivelatore di muoni, per identificare i muoni più energetici. Una volta identificati due candidati muoni con alto momento trasverso in un quadrante, la decisione del trigger dipende da due soglie: una sul valore più elevato del momento trasverso (Level 0 muon) ed una sui due valori più alti di momento trasverso (Level 0 dimuon).

Il trigger Level 0-calorimeter viene elaborato grazie alle informazioni derivanti dal sistema di calorimetri, inclusi il preshower e gli scintillatori. Viene calcolata l'energia trasversa depositata in un cluster di  $2 \times 2$  celle della stessa dimensione, sia per l'ECAL che per l'HCAL. L'energia trasversa è combinata con il numero di hit presenti nel preshower e nello scintillatore, in modo da definire un trigger specifico per i fotoni, gli elettroni e gli adroni.

Il trigger Level 0-hadrons ha lo scopo di collezionare campioni numerosi di particelle provenienti dai decadimenti di adroni  $c$  e  $b$ . Tali particelle hanno in media un momento trasverso maggiore rispetto alle particelle provenienti dai decadimenti dei quark leggeri, il che aiuta nella discriminazione rispetto al fondo.

## Il trigger di alto livello

Gli eventi selezionati dal Livello 0 di trigger vengono inviati ad un centro di selezione, composto da una farm di 29000 processori commerciali per PC, per la decisione dello stadio di HLT. L'algoritmo di HLT è implementato tramite un programma scritto in C++, che viene eseguito da ogni processore, ricostruendo e selezionando gli eventi nel modo più simile possibile all'algoritmo usato per le ricostruzioni offline. Una sostanziale differenza tra gli algoritmi online ed offline è il tempo disponibile per ricostruire un singolo evento. La ricostruzione offline richiede 2 s per evento, mentre l'algoritmo online deve completare la ricostruzione di un evento in circa 50 ms, tempo che dipende sia dalla frequenza di arrivo degli L0 e dalla potenza di calcolo dei processori.

Le selezioni usate all'interno di HLT sono molteplici e sono specifiche per gli eventi di interesse. In particolare decadimenti di adroni  $c$  e  $b$ . Ogni selezione è specificata da un certo algoritmo di ricostruzione e da criteri di selezione che riguardano la cinematica delle particelle, la topologia del decadimento e l'identificazione delle particelle. Il tempo di processamento di HLT è diviso tra due livelli, chiamati HLT1 ed HLT2. La principale differenza tra i due riguarda la complessità delle informazioni che possono essere utilizzate ed il tempo che hanno a disposizione. Viene quindi

effettuata una ricostruzione parziale, in HLT1, per diminuire il flusso a 30 kHz, per poi procedere ad una ricostruzione complessa in HLT2.

In HLT1, vengono ricostruite le tracce nel VELO e selezionate quelle candidate ad essere provenienti dal decadimento di quark pesanti andando a valutare il parametro di impatto della traccia rispetto al vertice primario più vicino alla traccia. In HLT2, si procede ad una ricostruzione completa in tutti i tracciatori dei candidati trovati nel VELO. Si ricostruiscono quindi i vertici secondari, imponendo delle condizioni sulle lunghezze di decadimento e sulle masse, così da ridurre il flusso dei dati a 5 kHz.

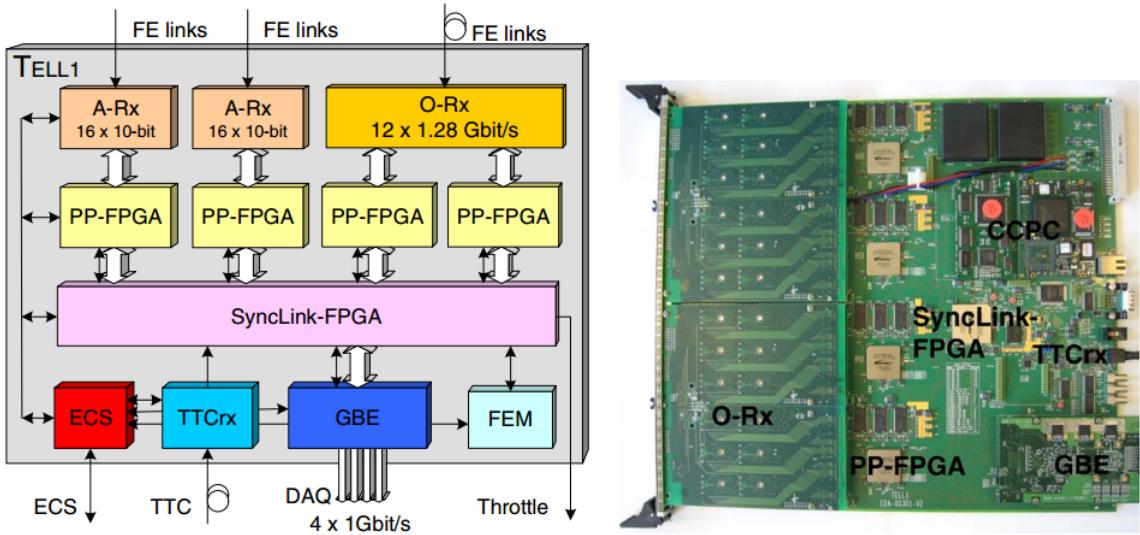

### 2.2.4 Il sistema di readout

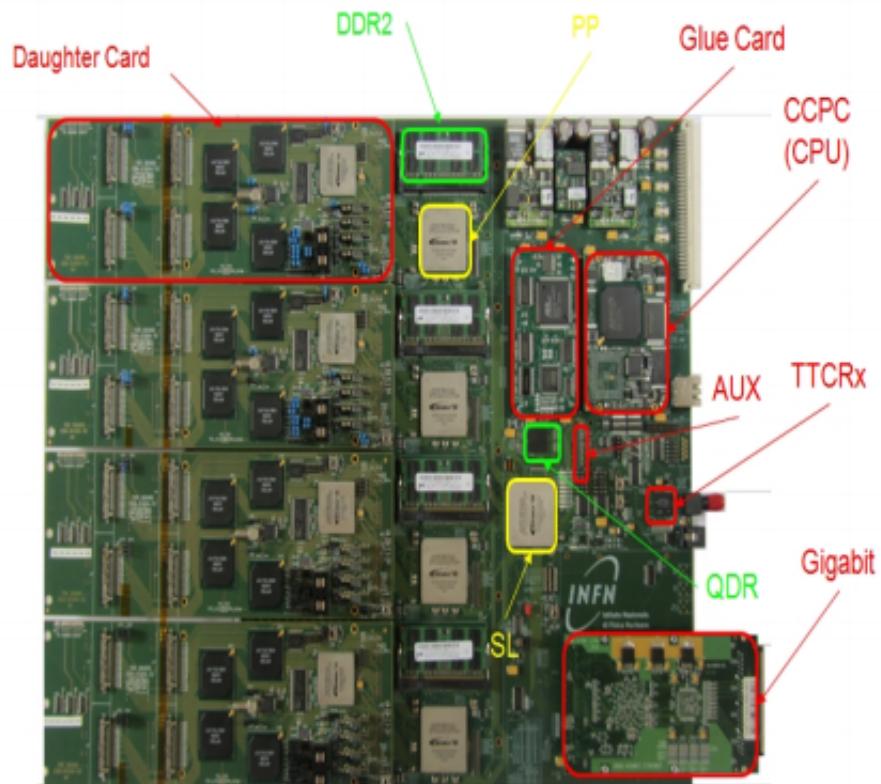

Una volta che il segnale L0 è stato generato, i dati vengono trasferiti dalle schede di frontend alla *counting room*, situata ad un piano sopra i detector, tramite fibre ottiche o linee di rame, dove le schede di readout, chiamate TELL1, interfacciano i rivelatori con il sistema di acquisizione dati.

La TELL1 [40] è una scheda generica su cui possono essere montate piccole schede aggiuntive, chiamate mezzanini, per ricevere in ingresso dati da differenti rivelatori. Esistono due tipi di mezzanini: uno con interfaccia analogica (A-Rx) per i dati del VELO, i quali vengono digitalizzati in loco, ed uno con interfaccia ottica (O-Rx) per gli altri rivelatori. Ciascuna scheda A-Rx monta un ADC con 16 canali a 10 bit, campionati a 40 MHz; ogni scheda O-Rx usa due connettori con ricevitori ottici a 12 vie che sostengono un flusso dati di  $\sim 1.3 \text{ Gb/s}$ , per un totale 24 canali per scheda. La banda totale di ingresso risulta quindi essere  $16 \times 4 \times 10 \times 40 \text{ MHz} = 25.6 \text{ Gb/s}$  per i canali analogici e di  $24 \times 1.28 \text{ Gb/s} = 30.7 \text{ Gb/s}$  per quelli ottici.

I dati ricevuti dai mezzanini sono processati da 5 FPGA Altera, della famiglia Stratix, 4 di pre-processamento (PP) ed uno per la formattazione dei dati (*Synk Link*, SL).

Ciascuna PP riceve dati che hanno superato il livello 0 di trigger, da una delle schede Rx, ad una frequenza di 1.1 MHz. Le operazioni svolte riguardano a riduzione del rumore, la *zero suppression* e il trasferimento dei dati alla SL.

La SL distribuisce alle PP i segnali di sincronizzazione, come il clock, il trigger, e l'identificatore degli eventi. In più ha il compito di formattare i dati provenienti dalle PP, e di trasmettere tali pacchetti al resto della catena di readout via Ethernet.

La TELL1 è equipaggiata anche con:

- una *credit card PC* (CCPC) commerciale, che utilizza Linux come sistema operativo, il quale gestisce gli *slow control* della scheda e l'ECS (vedi sotto);

- una scheda (TTCrx) che riceve i segnali di controllo, come il clock, il reset e il trigger L0;

- una scheda Ethernet con 4 connessioni da 1 Gb/s in uscita;

**Figura 2.18:** A sinistra: un diagramma a blocchi della TELL1, con entrambi i tipi di mezzanini per la ricezione dei dati. A destra: una foto della scheda equipaggiata con i ricevitori ottici.

- una mezzanina che simula alcuni segnali provenienti dai Beetle chip, in particolare il segnale di validazione dei dati (*data valid*), poiché questo non viene inviato alle schede insieme ai dati.

La sincronizzazione con il resto del sistema di DAQ è garantita dalla rete di *Timing and Fast Control* (TFC), che genera il clock globale e gestisce l'invio dei segnali veloci e dell'*Experiment Control System* (ECS).

## 2.3 Modifiche al rivelatore di LHCb per l'upgrade del 2020

A partire dal 2020, l'esperimento LHCb sarà oggetto di sostanziali miglioramenti, riguardanti sia il rivelatore che i sistemi di trigger e di acquisizione dati [41]. Fra i più importanti cambiamenti, ci sarà quello del sistema di acquisizione dati, capace di leggere l'intero rivelatore a 40 MHz invece dell'attuale frequenza di 1.1 MHz, e lo sviluppo di un trigger puramente basato su software. Inoltre molti dei rivelatori dell'esperimento saranno migliorati per rimanere pienamente efficienti anche nelle nuove condizioni sperimentali: energia nel centro di massa  $\sqrt{s} = 14 \text{ TeV}$  e un importante aumento nella luminosità, fino a  $\mathcal{L} = 2 \cdot 10^{33} \text{ cm}^{-2}\text{s}^{-1}$ . Questo porterà ad una più alta molteplicità di traccia rispetto alla configurazione attuale, e ad un numero di interazioni pp primarie per collisione pari a  $\mu = 7.6$ .

### 2.3.1 I nuovi rivelatori per LHCb

I più importanti miglioramenti nel rivelatore riguarderanno i rivelatori di traccia, che saranno totalmente riprogettati per ottenere misure più precise. I rivelatori per l'identificazione di particelle saranno migliorati per permettere una lettura a 40 MHz readout, e per meglio sostenere il nuovo ambiente sperimentale caratterizzato dalla maggiore molteplicità di tracce.

#### Il rivelatore VELOPIX

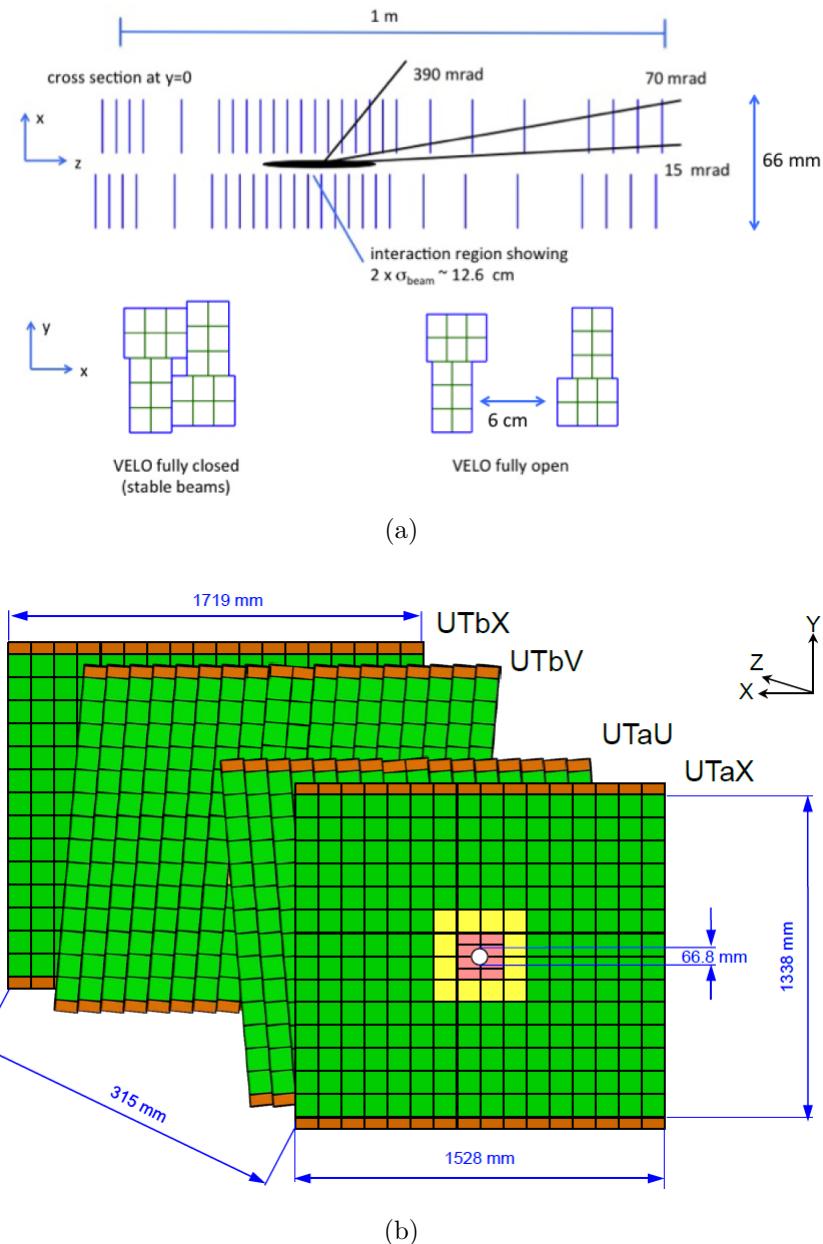

Il rivelatore di vertice sarà radicalmente migliorato [42], con una migrazione alla tecnologia a pixel (VELOPIX) invece dell'attuale tecnologia a microchip, comportando la sostituzione di tutti i sensori al silicio e dell'elettronica. Il nuovo VELO è composto da 26 tracking layers, due dei quali sono pile-up stations usati per misurare la molteplicità di tracce nella regione a  $z$  negativo. Ogni stazione è divisa in due moduli, con la possibilità di distanziarli dall'asse del fascio come nell'attuale VELO. Ogni modulo contiene 4 sensori al silicio con un'area attiva di  $42.46 \times 14.08 \text{ mm}^2$ . L'intero rivelatore VELOPIX detector conta 41 M pixels, con una dimensione di  $55 \times 55 \mu\text{m}^2$  in un piano trasverso all'asse del fascio. Il raggio interno dell'area sensibile sarà ridotto da  $r = 8.2 \text{ mm}$  a meno di  $r = 5.1 \text{ mm}$ , per migliorare la risoluzione dei parametri di impatto. La risoluzione prevista per un singolo impatto è  $\approx 12\text{-}15 \mu\text{m}$  per le coordinate  $x$  ed  $y$ . In Figura 2.19(a) sono riportate le caratteristiche principali del nuovo VELO.

#### Upstream Tracker

L'attuale tracciatore Turicense [43] sarà rimpiazzato dal rivelatore *Upstream Tracker* (UT), un rivelatore formato da 4 piani di sensori a micro-strip di silicio. Rispetto al TT, il nuovo UT avrà dei sensori più sottili, con una segmentazione più fine, e coprirà una regione più grande in accettanza. Le strip nei piani saranno orientate secondo la configurazione  $x-u-v-x$ , con le strip verticali nel primo e nell'ultimo piano, mentre i piani intermedi avranno le strip direzionate con un angolo rispetto alla verticale di  $-5^\circ$  e  $+5^\circ$ . La dimensione ed il passo dei sensori dipendono dalla loro posizione sul piano del rivelatore. Vicino alla linea del fascio i sensori hanno uno spessore di  $95 \mu\text{m}$ , con un passo di 5 cm, mentre nell'area più lontana, le strip sono spesse 190  $\mu\text{m}$  e distanti 10 cm. La copertura angolare dell'UT è di 314 (248) mrad nel piano di curvatura (non curvatura). In Figura 2.19(b) vediamo è riportata la struttura dell'UT.

#### Tracciatore a fibre scintillanti

Il complesso di rivelatori OT ed IT saranno rimpiazzati da un tracciatore a fibre scintillanti (SFT). Ogni piano dell'SFT sarà formato da fibre scintillanti lunghe 2.5 m lette da fotomoltiplicatori posti al di fuori dell'accettanza del rivelatore. Il nuovo tracciatore avrà 3 stazioni, ognuna formata da 4 piani, in cui le fibre sono

disposte secondo la configurazione di coordinate  $x-u-v-x$ , già descritta nei precedenti paragrafi. Le fibre avranno un diametro di 0.25 mm, formata internamente da un polimero ricoperto di materiale organico scintillante. La luce viene prodotta dall'eccitazione del polimero, e viene propagata lungo la fibra tramite riflessione multiple. La luce si propaga all'interno della fibra con un tempo di 6 ns/m, con una lunghezza di attenuazione tipica di  $\sim 4$  m ed un tempo di decadimento di  $\sim 3$  ns.

### Rivelatore Cherenkov

Nell'Upgrade del rivelatore RICH1 sarà mantenuto il radiatore con il  $C_4F_{10}$ , mentre sarà rimosso il modulo con l'aereogel. Il RICH2 manterrà la stessa struttura con il radiatore di  $CF_4$  [44]. L'attuale sistema di lettura sarà sostituito con fotomoltiplicatori multi-anodo con un elettronica di lettura esterna che può operare a 40 MHz. Tutti i componenti ottici saranno riutilizzati il più possibile, ricalibrando la posizione e l'orientamento.

### Calorimetri

Il sistema di calorimetri sarà equipaggiato con un'elettronica completamente nuova, poiché saranno usati dei differenti fotomoltiplicatori per la lettura. L'apparato di reiezione del fondo, il preshower e gli scintillatori, saranno rimossi perché non verranno più utilizzati nella decisione del trigger di livello 0. La struttura del calorimetro elettromagnetico e adronico rimarrà invariata.

### Camere a muoni

Nella nuova configurazione del rivelatore di muoni, la stazione M1 sarà rimossa, a causa della grande occupazione attesa di questa stazione con la luminosità attesa nell'upgrade, che renderebbe difficile l'associazione degli hit in M1 con le tracce dei muoni nelle altre camere. La configurazione delle stazioni M2-M5 rimarrà invariata, ma sarà aggiunto uno spessore ulteriore intorno alla linea di fascio prima dell'HCAL, per migliorare l'assorbimento degli sciami e ridurre il flusso di particelle nella zona più vicina al fascio della stazione M2.

### 2.3.2 Il nuovo sistema di acquisizione dati e di trigger per LHCb

Con l'upgrade di LHC del 2020, la luminosità crescerà fino ad un valore di  $10^{34} \text{ cm}^{-2} \text{s}^{-1}$  ( $2 \cdot 10^{33} \text{ cm}^{-2} \text{s}^{-1}$  per LHCb) gli attuali sistemi di trigger non saranno più in grado di selezionare dati in modo efficiente, a causa dell'elevata luminosità prevista. Quindi, in LHCb, le informazioni provenienti dai calorimetri e dalle camere a muoni non saranno più adatte per elaborare il trigger di livello 0. Quindi, il nuovo sistema di trigger dovrà essere fortemente basato sulle informazioni dei rivelatori di traccia, che diventeranno la base fondamentale per le decisioni del trigger. Requisito di questo nuovo sistema sarà la capacità di elaborare gli eventi dai tracciatori ad una frequenza di 40 MHz, rispetto a quella attuale di 1 MHz.

L’interfaccia tra i rivelatori e il sistema di acquisizione dati, attualmente implementato nella scheda TELL1, sarà implementata in una nuova scheda di lettura, denominata TELL40. La scheda sarà progettata mantenendo la struttura base della TELL1 e utilizzando dispositivi più performanti, come gli FPGA della famiglia Altera Stratix V. Questa è la nuova famiglia di FPGA prodotta da Altera, ed offre molte risorse per il processamento locale dei dati, sia in termini di blocchi logici sia come numero di connessioni disponibili. La scheda riceverà gli hit dai sottorivelatori ad una frequenza di 40 MHz per evento, formattandoli in pacchetti da distribuire alla farm di processamento degli eventi. I pacchetti sono inviati attraverso una rete di connessione veloce basata su protocolli standard di comunicazione, per la quale si pensa di utilizzare reti Ethernet a 10 Gigabit. La scheda sarà compatibile con lo standard hardware ATCA (*Advanced Telecommunication Computing Architecture*), che sarà utilizzato in altri esperimenti del CERN. Inoltre la scheda dispone di un interfaccia per la ricezione dei segnali di temporizzazione e di TFC ed ECS).

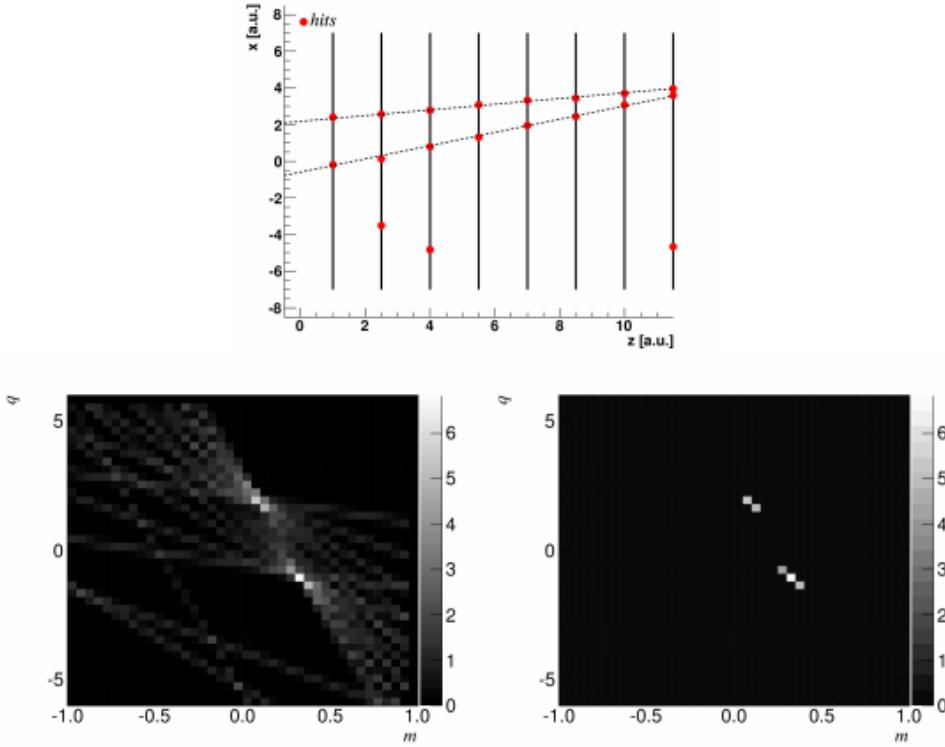

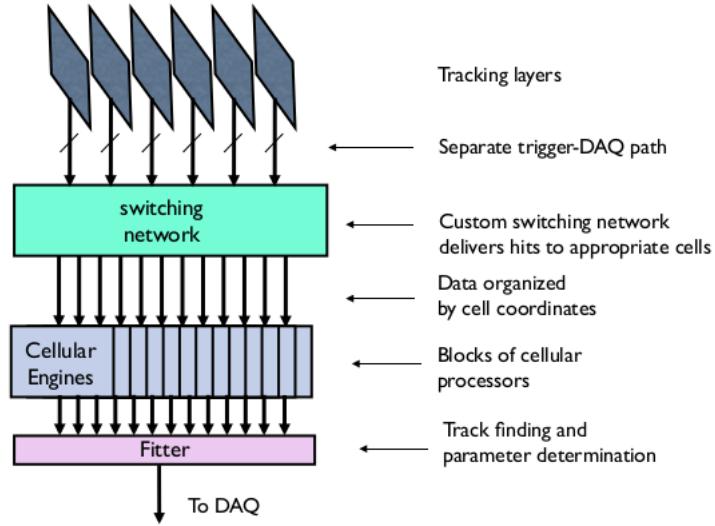

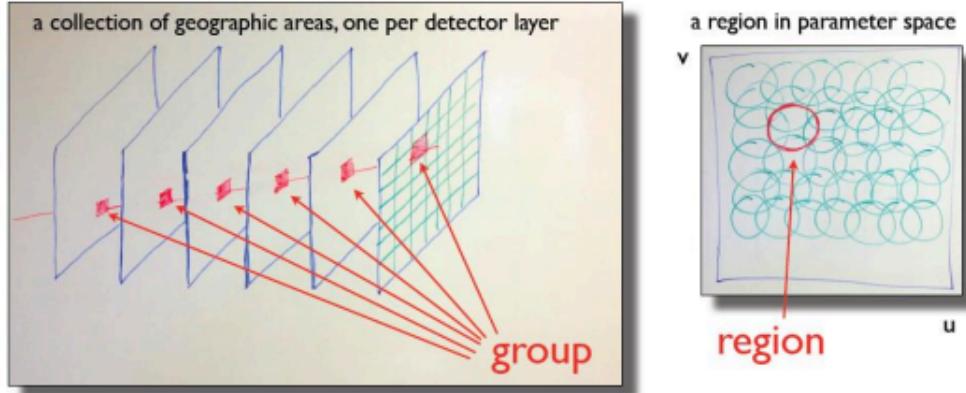

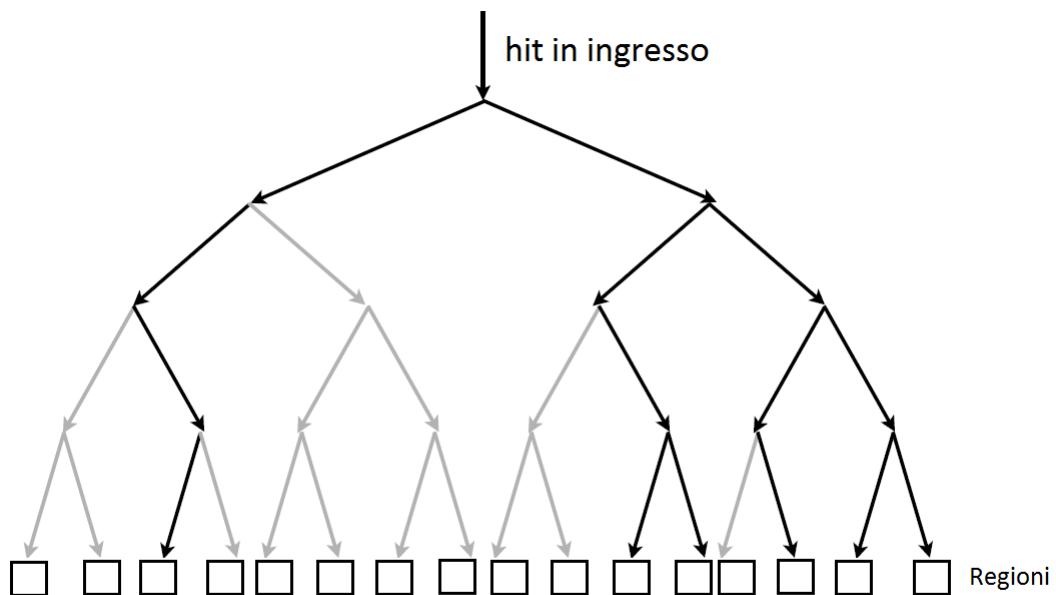

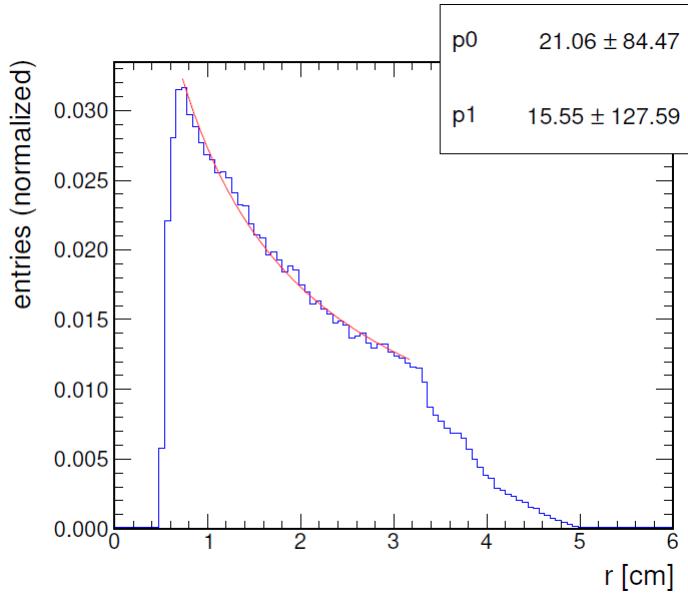

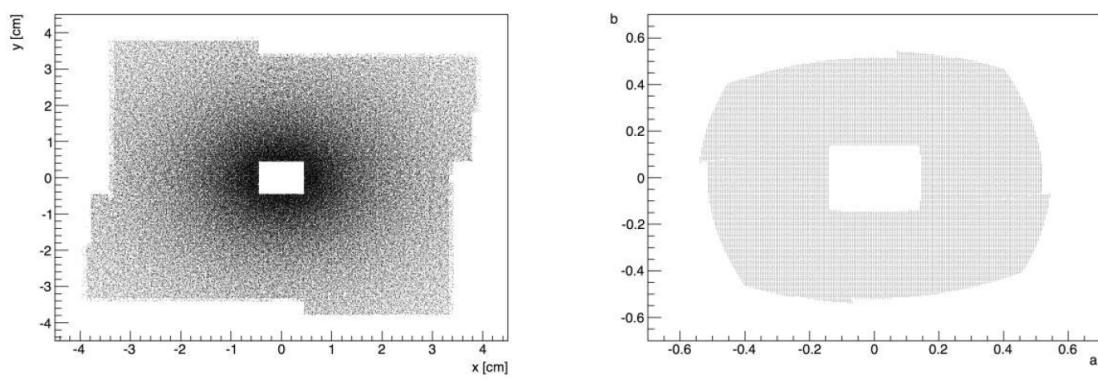

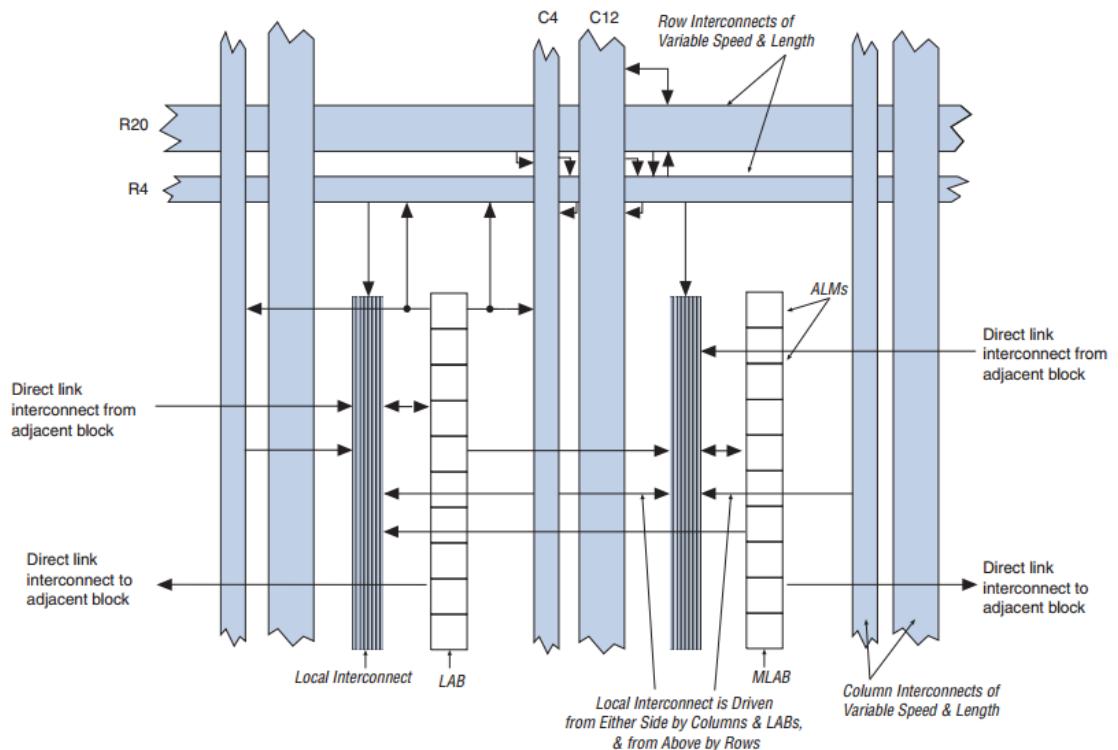

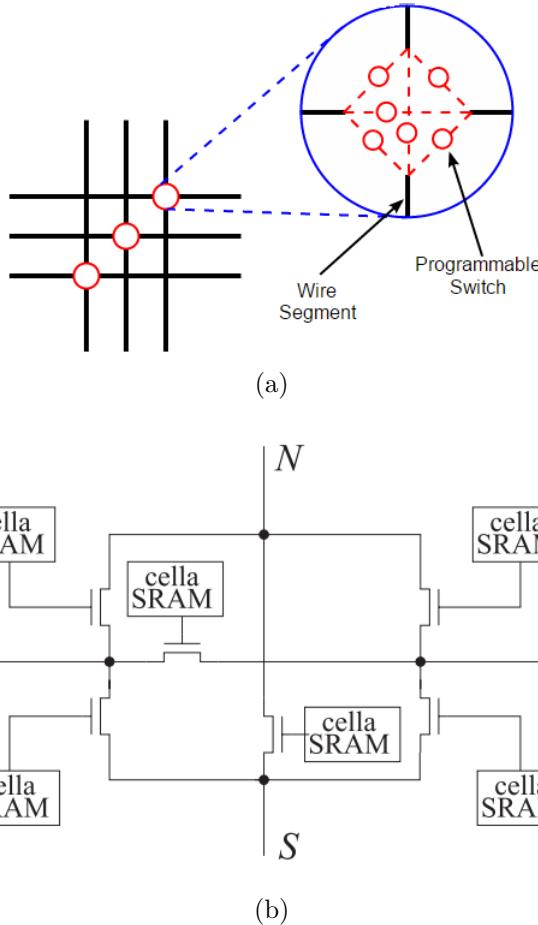

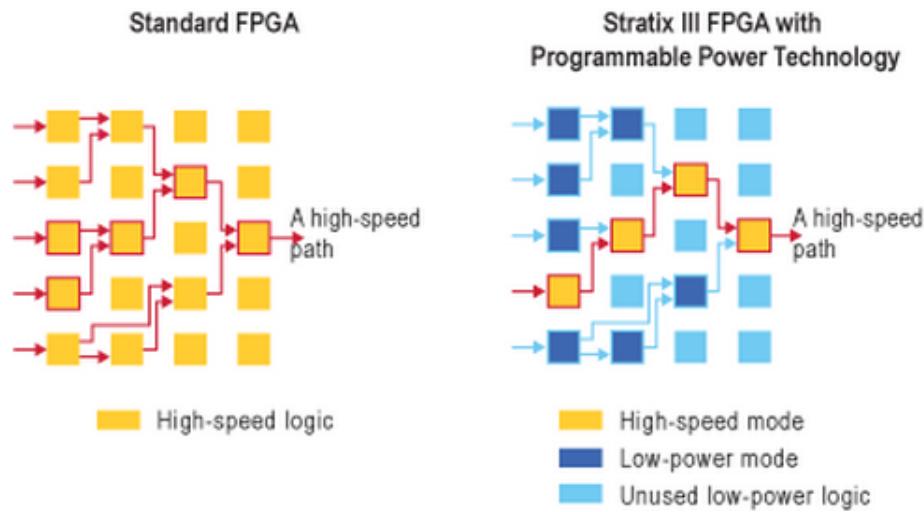

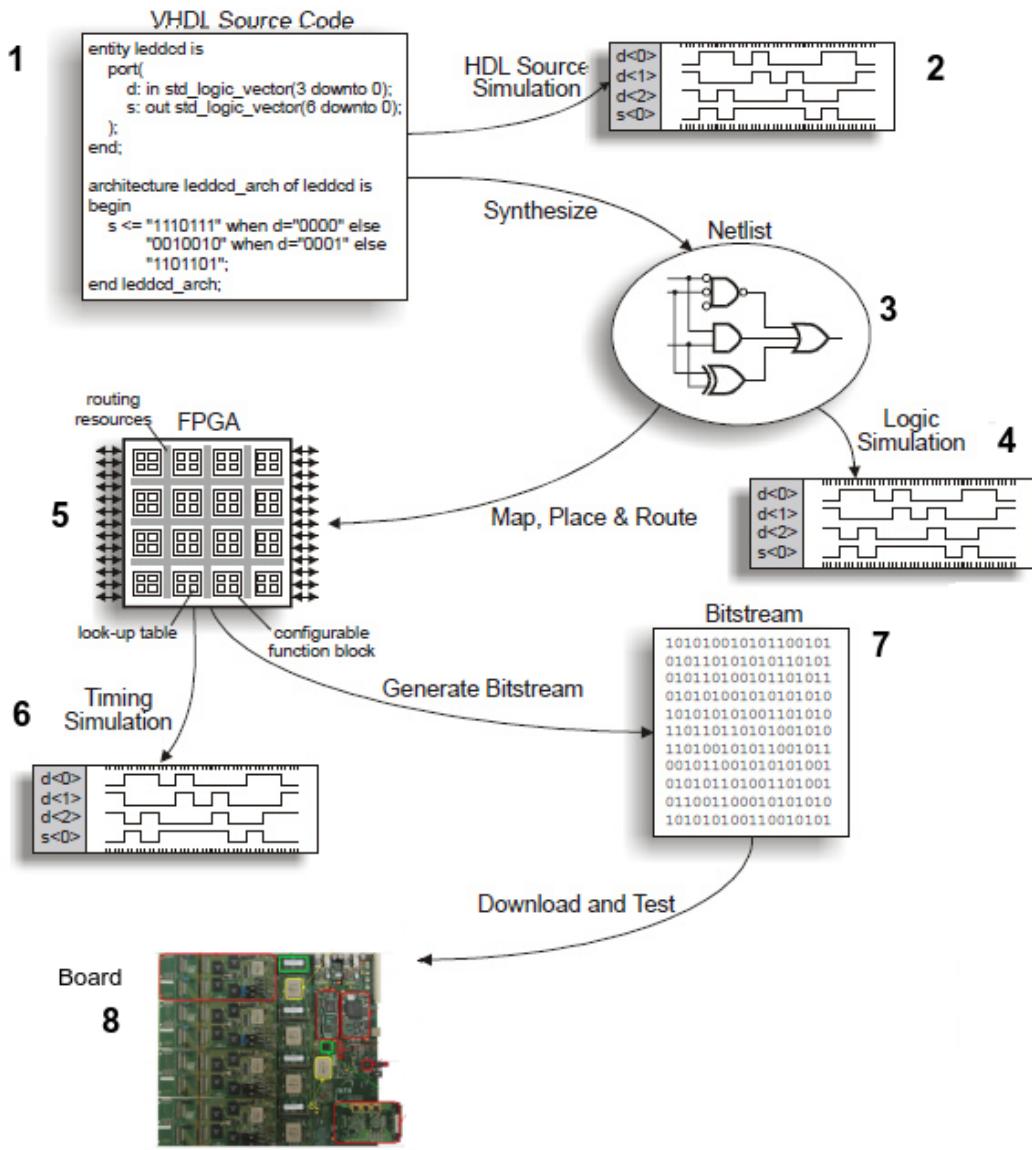

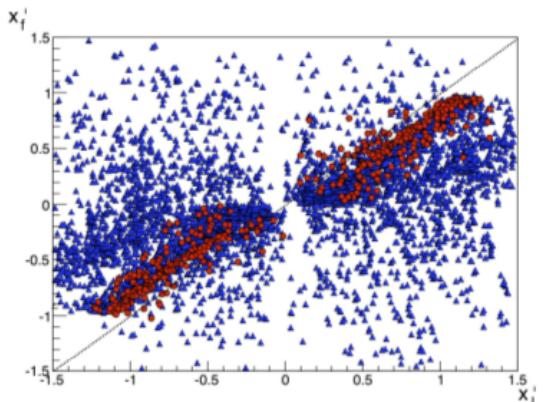

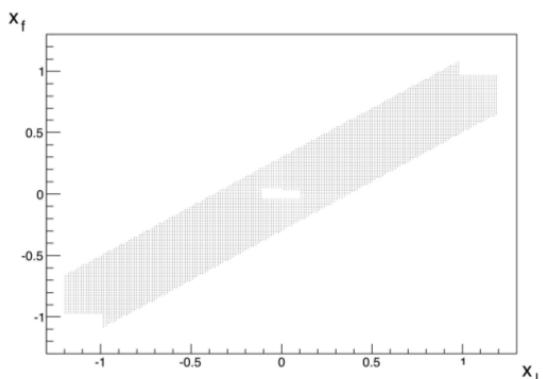

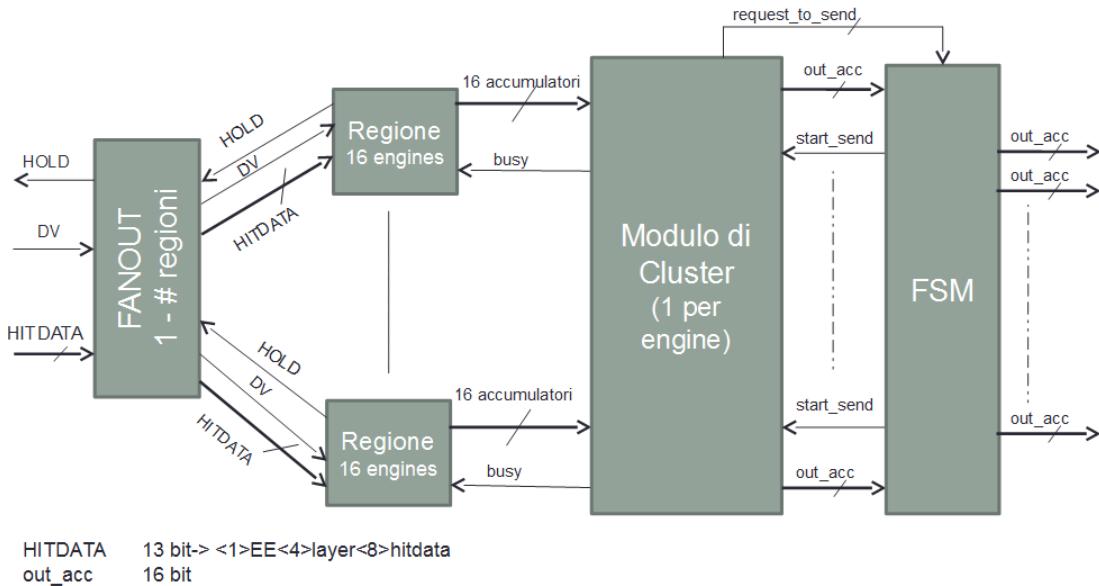

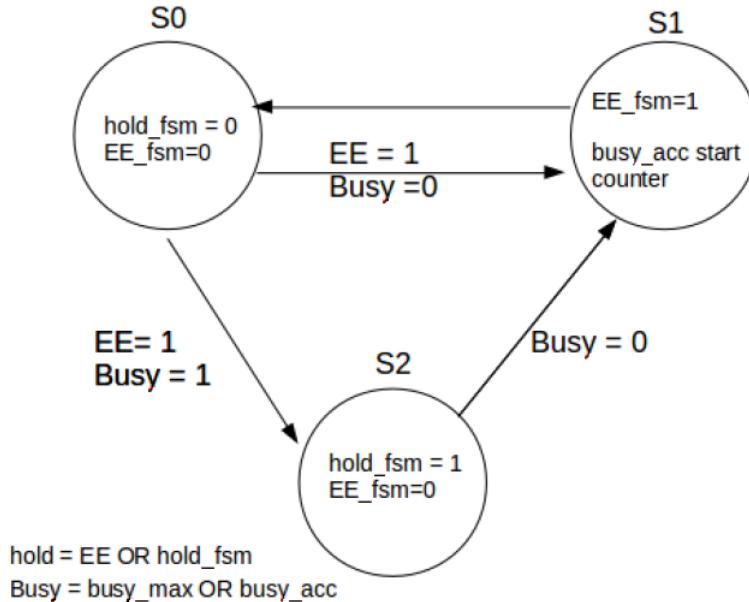

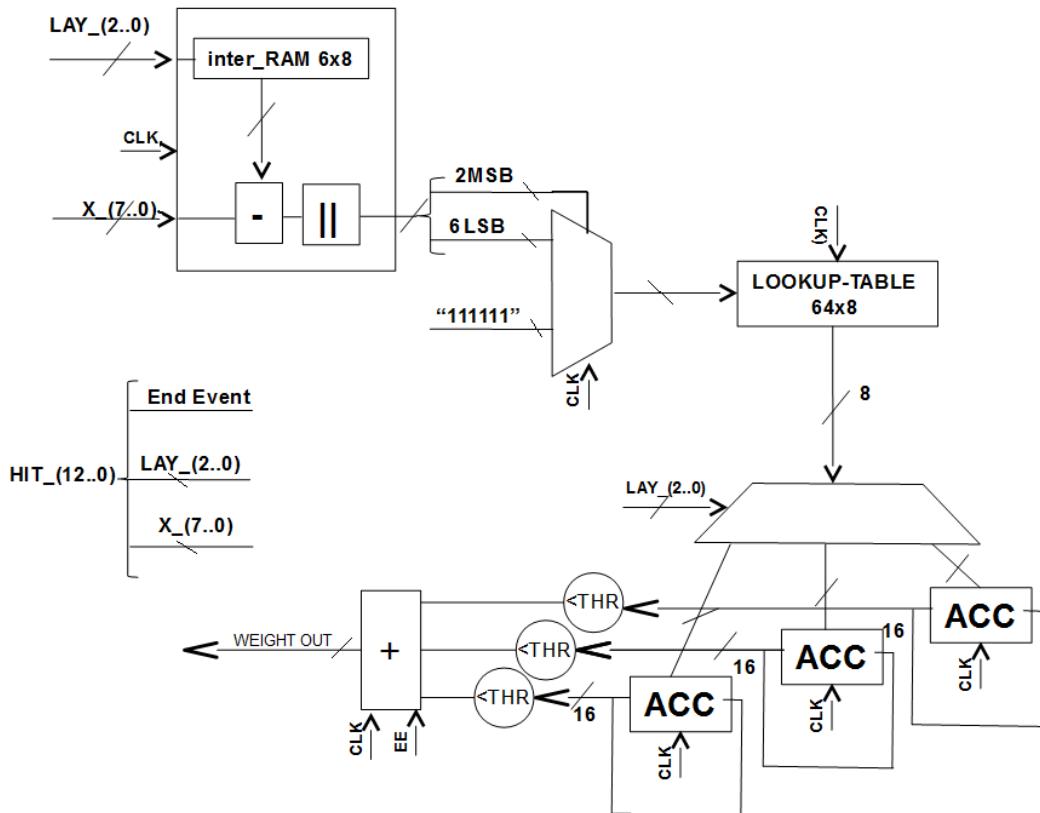

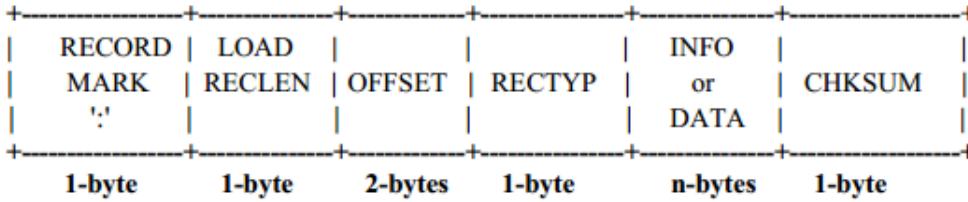

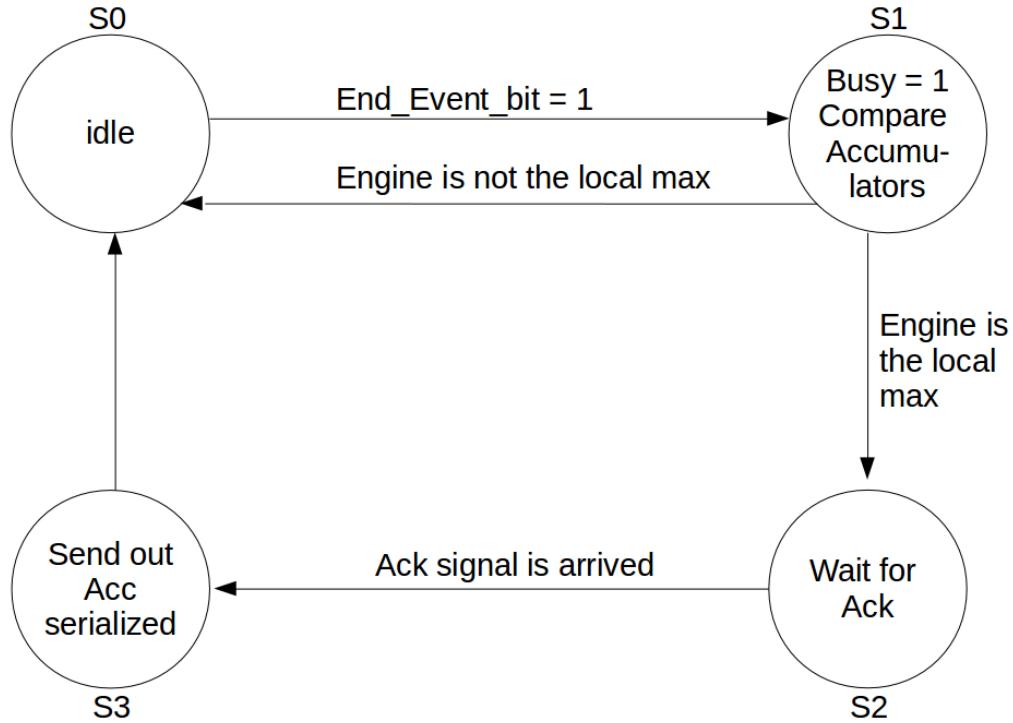

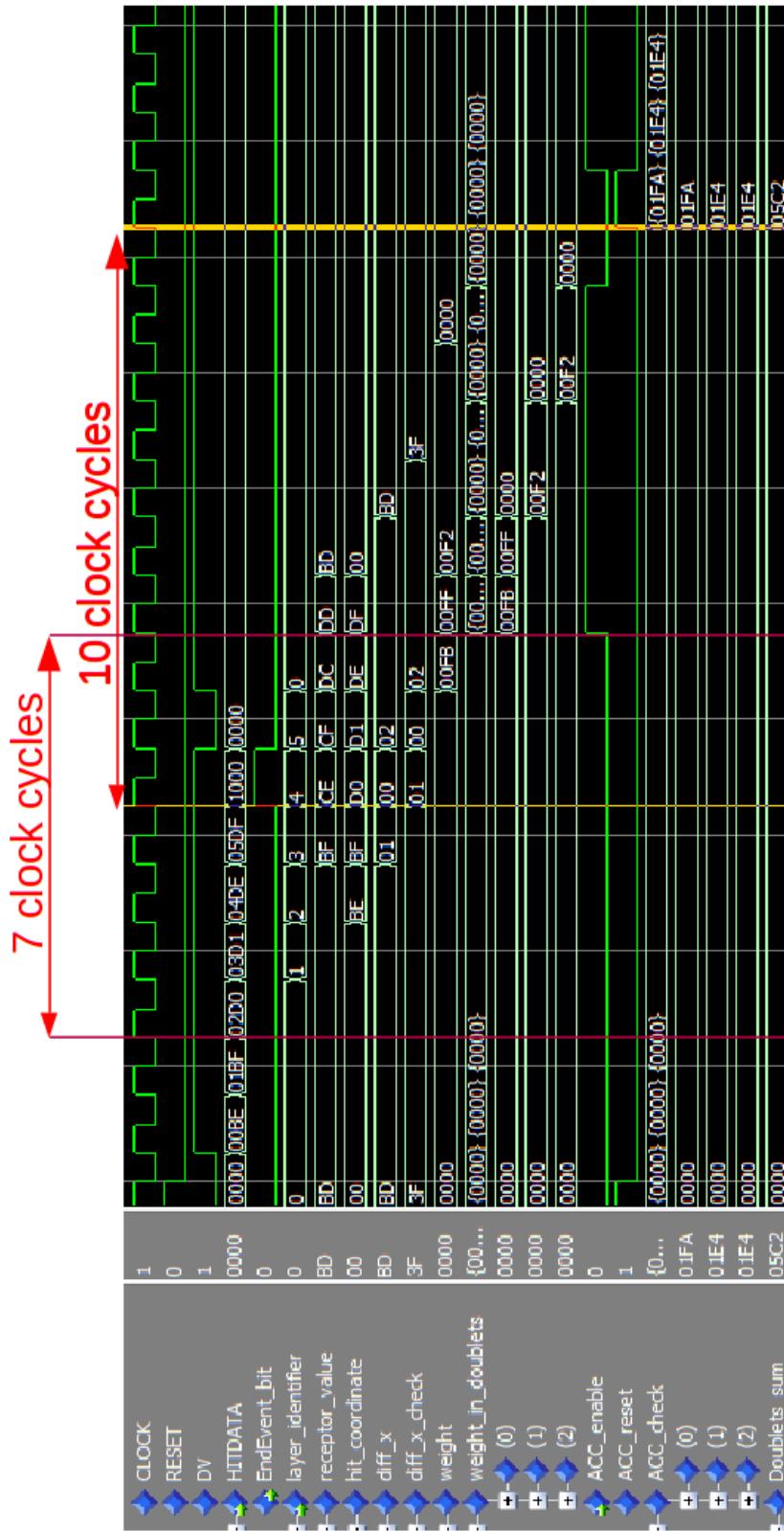

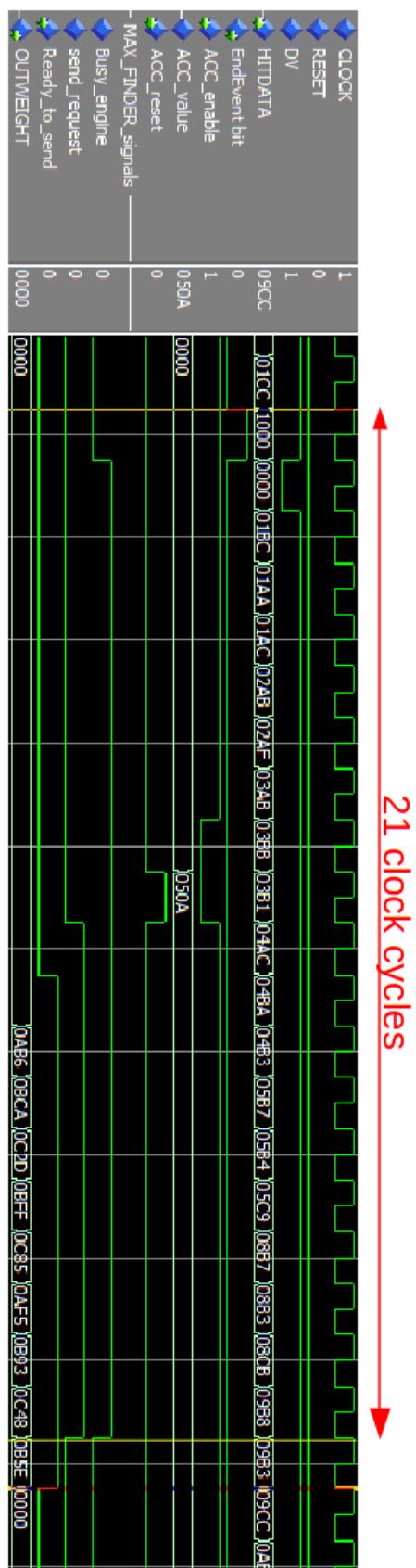

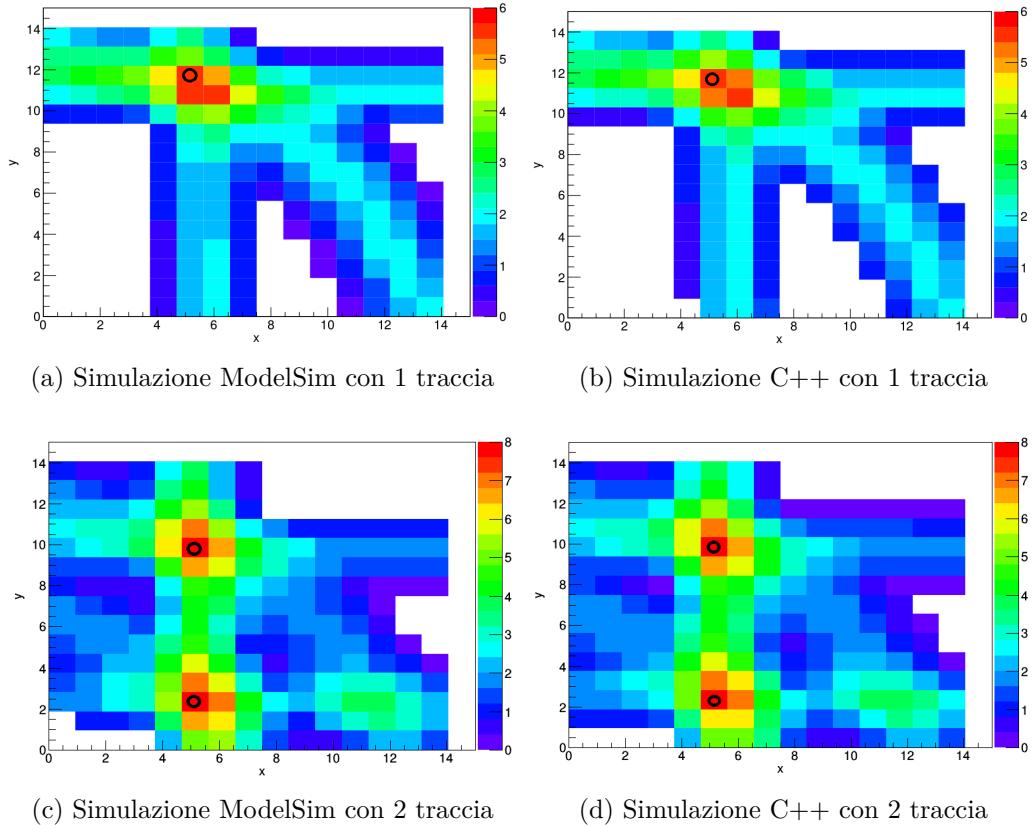

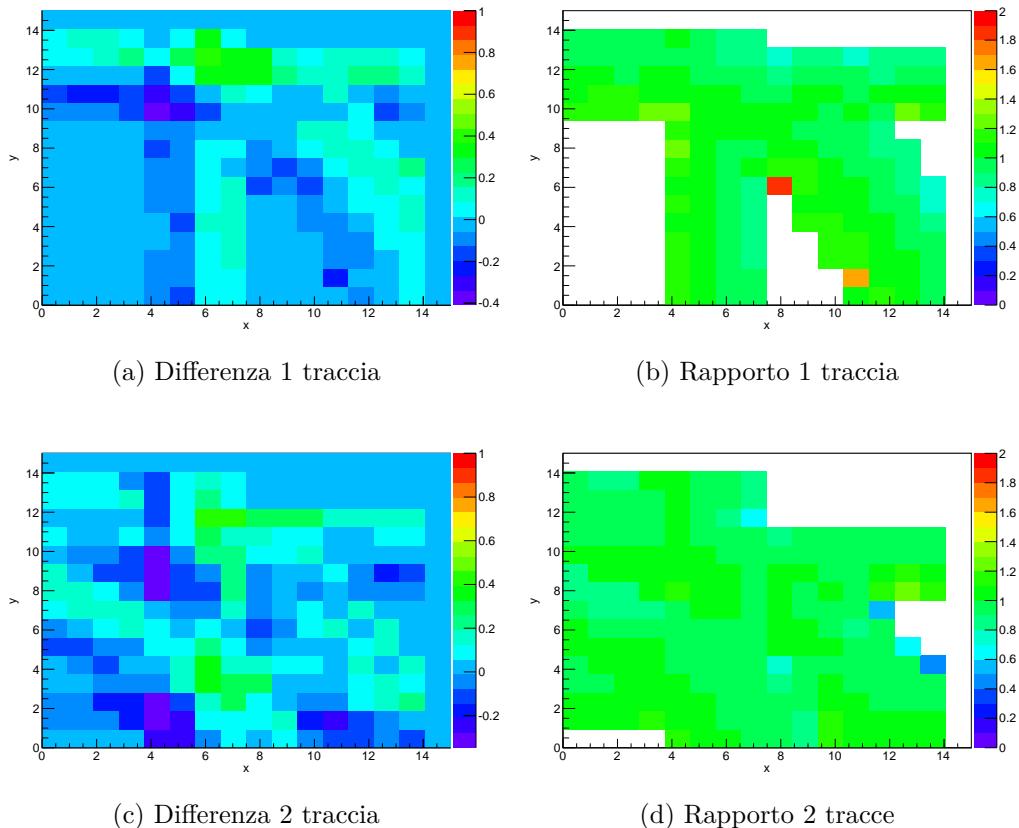

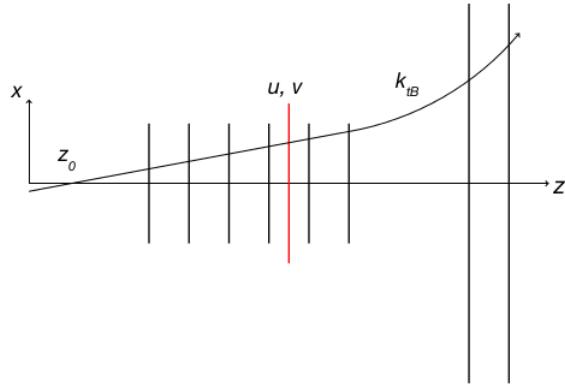

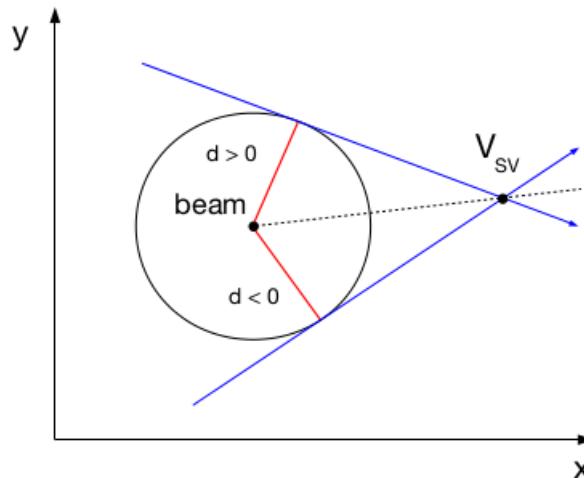

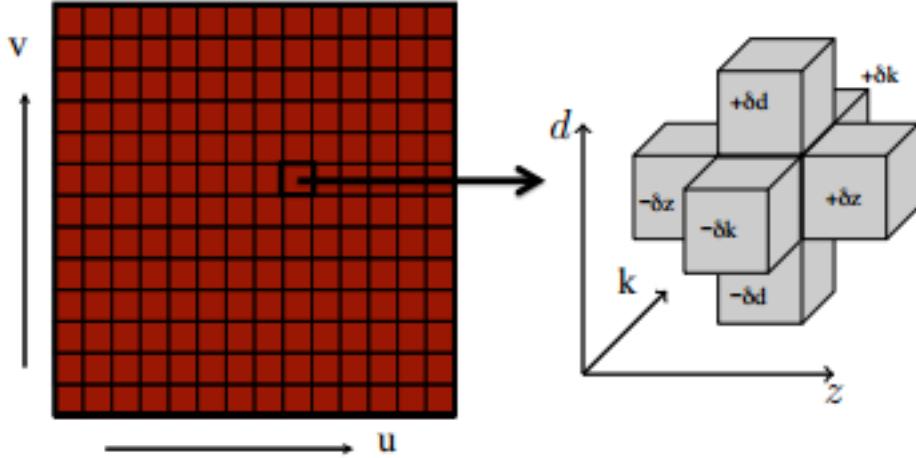

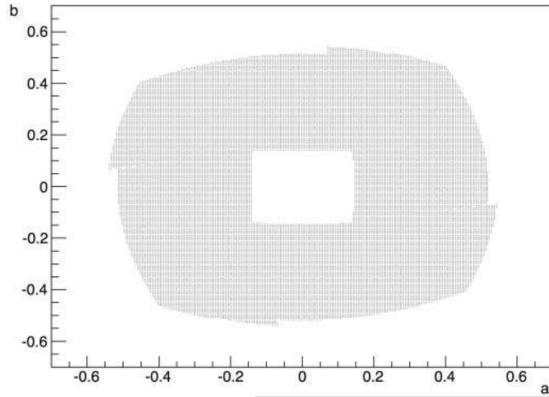

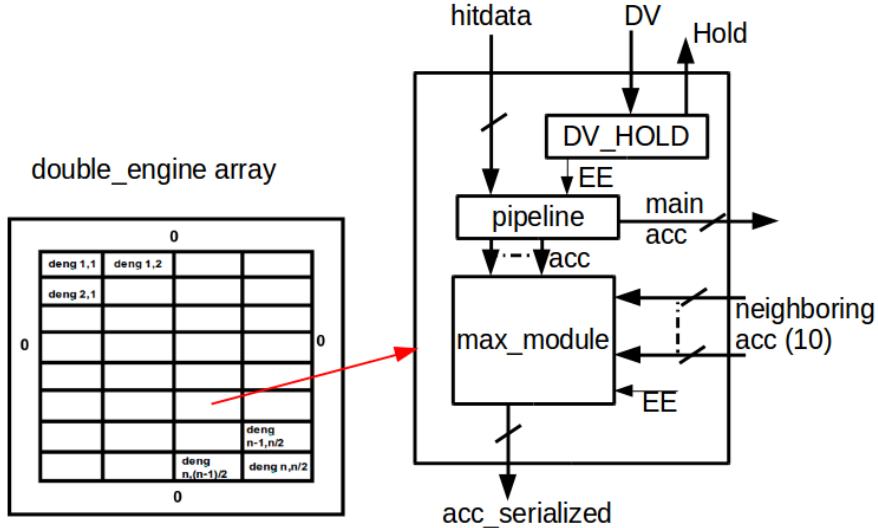

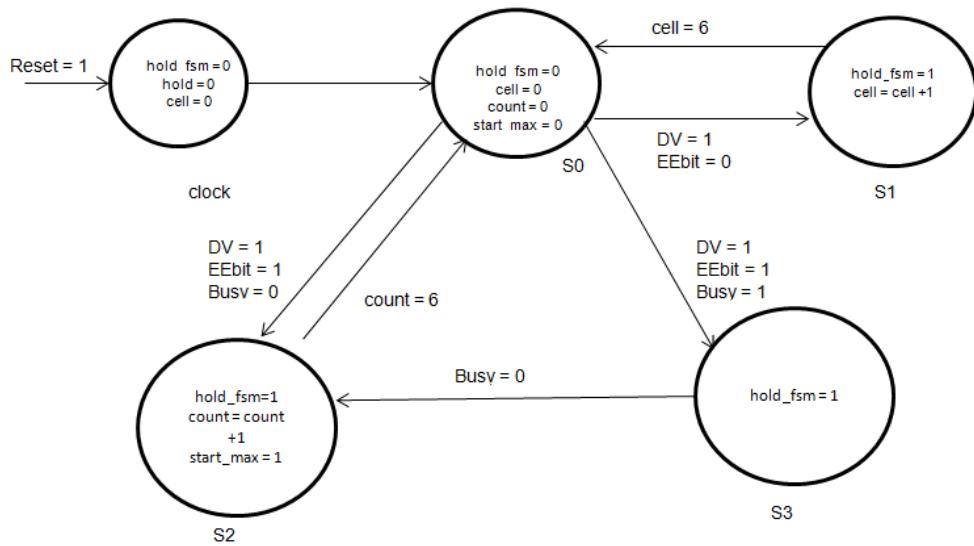

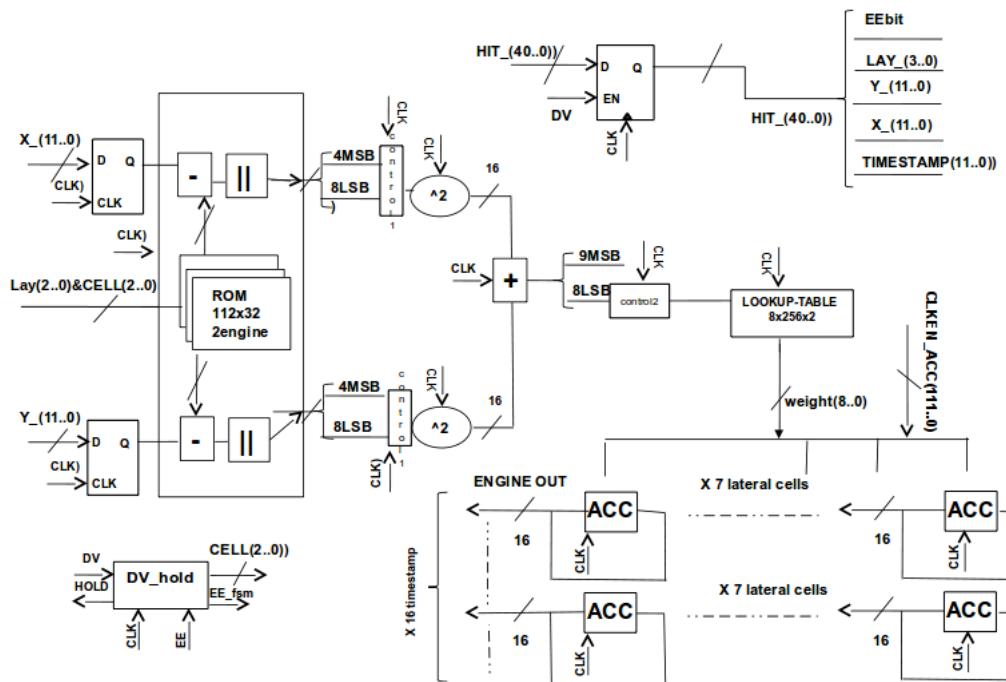

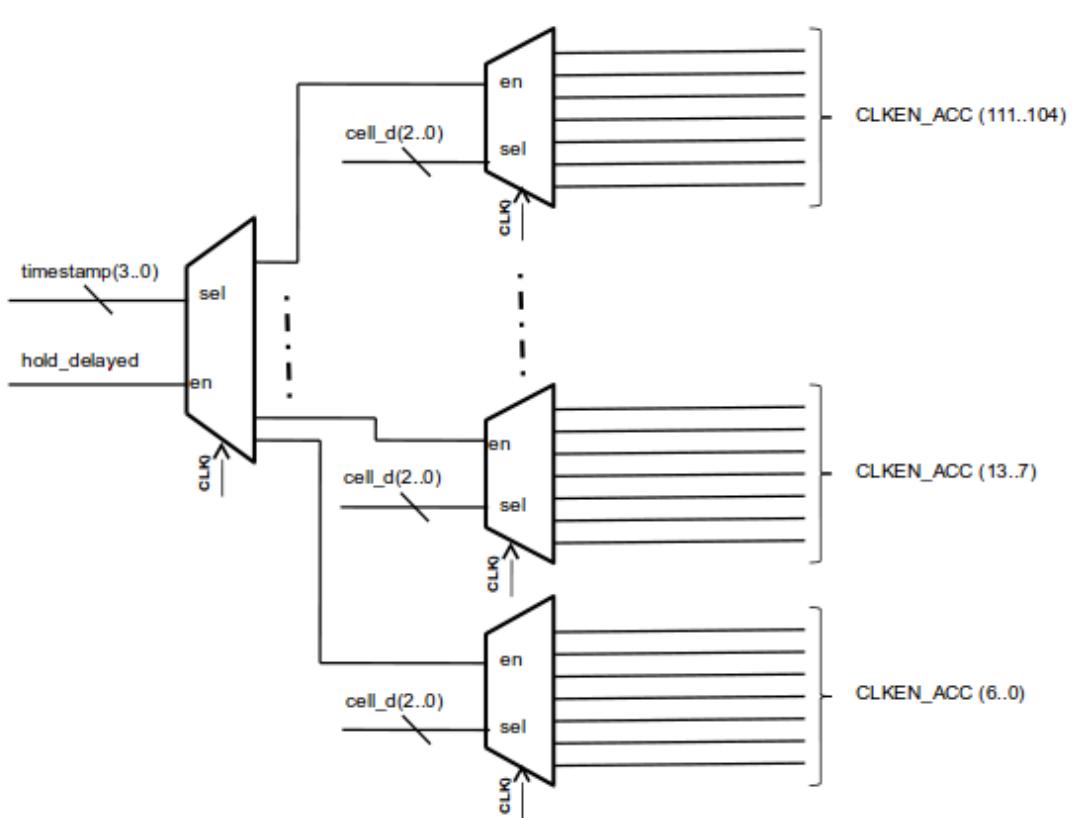

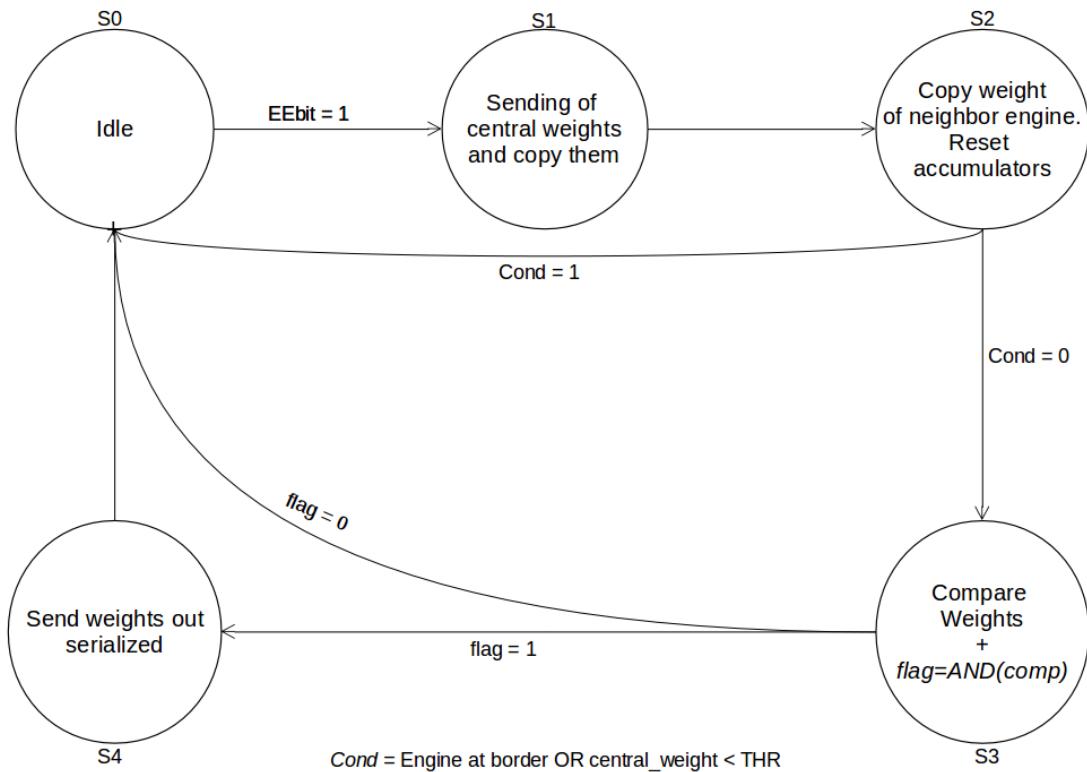

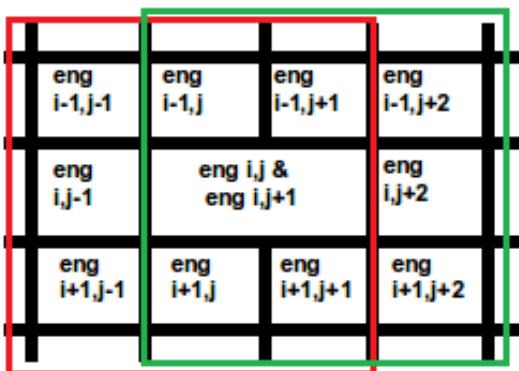

All’interno di questo sistema di FPGA è possibile inserire un dispositivo come quello che sarà discusso in questa tesi