# An Accurate Ultra-low Current Measurement ASIC for Ionization Chamber Readout

**BERGISCHE

UNIVERSITÄT

WUPPERTAL**

## Dissertation

Submitted in partial fulfillment of the requirements for the degree of

*Doktor der Ingenierwissenschaften*

at the

University of Wuppertal, Germany

School of Electrical, Information and Media Engineering

by

**Sarath Kundumattathil Mohanan**

submitted on 26<sup>th</sup> of August, 2021 in Wuppertal, Germany

*This page is intentionally left blank.*

# Declaration

I, Sarath Kundumattathil Mohanan, hereby declare that the thesis is written independently and without making use of aids other than those indicated. Any part of the content that is taken up from other sources are marked and properly acknowledged. The produced or any other version of the thesis is not previously submitted to another university.

The thesis work was conducted from 2018 to 2021 under the supervision of Prof. Dr. rer. nat. Ullrich R. Pfeiffer at the University of Wuppertal and Dr. Hamza Boukabache at CERN. This work was fully funded under the Doctoral Student Program of CERN.

Wuppertal, August 2021

*This page is intentionally left blank.*

# Acknowledgements

This thesis was completed under the doctoral student program at CERN in collaboration with the University of Wuppertal. The successful completion of this research was the result of the support of many people at CERN and my host university. I would like to express my sincere gratitude towards my advisors Prof. Ullrich Pfeiffer, Dr. Hamza Boukabache, and Daniel Perrin. I thank them for believing in me from the very beginning and for the continuous encouragement and motivation imparted to me throughout the journey. Prof. Pfeiffer is a visionary and is always a great source of inspiration nurturing the academic researcher in me. Hamza was there at every critical juncture directing me well to proceed to perfection. I would like to also thank him for being there always more as a friend, approachable for all professional or personal matters. Daniel is the kindest person whom I have ever known and was always enthusiastic in providing all that I needed to carry out the research. Valuable feedback from Prof. Daniel Neumaier helped in improving the thesis and I would like to thank him for the same.

I would like to thank all my colleagues at HSE-RP-IL. Gael Ducos always had the solutions for all my queries from electronics design to mechanical assembly. Michel Pangallo was there for interesting discussions to troubleshoot issues. I would like to thank Katharina Ceesay-Seitz for the great exchange of ideas and proofreading the thesis. The help offered by Vassili Cruchet during the characterisation of the ASIC was incredible. Special thanks to colleagues from BE-CEM for the PCB design and manufacturing. I would also like to thank Salvatore Danzeca, Matteo Brucoli, Alix Joaquim, and Pierre Carbonez for all the help in carrying out the measurements with radiation sources. Markus Widorski and Claudia Ahdida are like the extended members of the team and would like to thank them for the help with tests at PSAIF.

I would like to thank colleagues from EP-ESE-ME - Dr. Francois Vasey, Prof. Michael Campbell, and Dr. Federico Faccio for the advice and resources provided; Dr. Xavi Llopard Cudie for the detailed design review; Dr. Wojciech Bialas for the support with the design tools; Dr. Alessandro Caratelli for the support with the memory compiler and PDKs; and Dr. Giacomo Ripamonti for the invaluable help in getting me accustomed to TSMC 130 nm PDK and for the troubleshooting during the design phase.

My colleagues from IHCT were also extremely helpful especially during the design of the first chip in this research. Special thanks to Dr. Ritesh Jain for the support with the PDK of 22FDX

and Dr. Philipp Hillger for proofreading the thesis. I would also like to thank my friend Utpal Kalita for introducing me to this wonderful team.

Most importantly, I would like to thank my family and friends for their love and support. I am always indebted to my parents who prioritized my education above anything else. I can't thank enough my brother Abijith for being such a wonderful person. Finally, I would like to thank the most important person in my life - my wife, Aswathy. I have a million reasons to thank her. She definitely made this whole journey easier and enjoyable.

# Contents

|                                                                    |               |

|--------------------------------------------------------------------|---------------|

| <b>List of Figures</b>                                             | <b>xi</b>     |

| <b>List of Tables</b>                                              | <b>xv</b>     |

| <b>List of Abbreviations</b>                                       | <b>xix</b>    |

| <b>Publications</b>                                                | <b>xxi</b>    |

| <b>Contributions of Others</b>                                     | <b>xxiii</b>  |

| <b>Abstract</b>                                                    | <b>xxvi</b>   |

| <b>Zusammenfassung</b>                                             | <b>xxviii</b> |

| <br>                                                               |               |

| <b>1 Introduction</b>                                              | <b>1</b>      |

| 1.1 Need for radiation monitoring . . . . .                        | 2             |

| 1.2 Radiation monitoring system . . . . .                          | 4             |

| 1.2.1 Ionization chambers . . . . .                                | 5             |

| 1.2.1.1 Centronic IG32 . . . . .                                   | 5             |

| 1.2.1.2 PTW PMI T32006 . . . . .                                   | 5             |

| 1.2.1.3 Centronic IG5 . . . . .                                    | 6             |

| 1.3 Motivation for the research and thesis organization . . . . .  | 7             |

| <br>                                                               |               |

| <b>2 Radiation Monitors at CERN</b>                                | <b>9</b>      |

| 2.1 ARCON . . . . .                                                | 9             |

| 2.2 RAMSES . . . . .                                               | 10            |

| 2.3 CROME . . . . .                                                | 11            |

| 2.4 UTOPIA . . . . .                                               | 13            |

| 2.4.1 Static characterization of UTOPIA 2 . . . . .                | 13            |

| 2.4.2 Dynamic laboratory characterization of UTOPIA 2 . . . . .    | 14            |

| 2.4.2.1 Laboratory characterization with pulsed currents . . . . . | 15            |

| 2.4.3 UTOPIA 2 characterization with pulsed radiation . . . . .    | 19            |

| 2.5 Conclusion . . . . .                                           | 23            |

| <br>                                                               |               |

| <b>3 State of the Art Low Current Measurement Methods</b>          | <b>25</b>     |

| 3.1 Transimpedance amplifiers . . . . .                            | 28            |

| 3.2 Current conveyors . . . . .                                    | 29            |

| 3.3 Current to frequency conversion . . . . .                      | 29            |

| 3.4 Current input delta sigma ADC . . . . .                        | 30            |

|          |                                                                   |           |

|----------|-------------------------------------------------------------------|-----------|

| 3.5      | Radiation monitoring systems . . . . .                            | 30        |

| 3.6      | Conclusion . . . . .                                              | 31        |

| <b>4</b> | <b>Attaining Femtoampere Sensitivity in 22 nm Technology</b>      | <b>33</b> |

| 4.1      | GF22FDX evaluation . . . . .                                      | 33        |

| 4.2      | Architecture . . . . .                                            | 35        |

| 4.3      | Measured results . . . . .                                        | 37        |

| 4.4      | Conclusion . . . . .                                              | 40        |

| <b>5</b> | <b>Technology Demonstrator ASIC in 130 nm Technology</b>          | <b>41</b> |

| 5.1      | Analysis of different current measurement architectures . . . . . | 41        |

| 5.1.1    | Reset counting method . . . . .                                   | 42        |

| 5.1.1.1  | Duration of the reset pulse . . . . .                             | 43        |

| 5.1.1.2  | Comparator delay . . . . .                                        | 44        |

| 5.1.1.3  | Comparator threshold . . . . .                                    | 44        |

| 5.1.1.4  | OTA offset . . . . .                                              | 45        |

| 5.1.2    | Direct slope measurement method . . . . .                         | 45        |

| 5.1.2.1  | Noise in the OTA output . . . . .                                 | 46        |

| 5.1.2.2  | Comparator delay . . . . .                                        | 46        |

| 5.1.2.3  | Comparator threshold . . . . .                                    | 46        |

| 5.1.2.4  | Resistor values . . . . .                                         | 46        |

| 5.1.3    | Charge balancing method . . . . .                                 | 46        |

| 5.1.3.1  | Capacitor values . . . . .                                        | 47        |

| 5.1.3.2  | Switched capacitor non-idealities . . . . .                       | 48        |

| 5.1.3.3  | OTA offset and input bias voltage . . . . .                       | 48        |

| 5.2      | Leakage current evaluation . . . . .                              | 48        |

| 5.3      | System design . . . . .                                           | 50        |

| 5.4      | Current measurement limits . . . . .                              | 52        |

| 5.4.1    | Lower limit . . . . .                                             | 52        |

| 5.4.2    | Upper limit . . . . .                                             | 53        |

| 5.4.2.1  | Reset counting method . . . . .                                   | 54        |

| 5.4.2.2  | Direct slope method . . . . .                                     | 54        |

| 5.4.2.3  | Charge balancing method . . . . .                                 | 55        |

| 5.5      | Measurement results . . . . .                                     | 55        |

| 5.5.1    | Chip 1 results . . . . .                                          | 56        |

| 5.5.2    | Chip 2 results . . . . .                                          | 57        |

| 5.5.3    | Chip 3 results . . . . .                                          | 60        |

| 5.5.4    | Chip 4 results . . . . .                                          | 61        |

| 5.5.5    | Chip 5 results . . . . .                                          | 61        |

| 5.6      | Leakage current measurements . . . . .                            | 62        |

| 5.7      | Conclusion . . . . .                                              | 64        |

|                                                                          |            |

|--------------------------------------------------------------------------|------------|

| <b>6 A Single Chip Solution for the Front-End of Ionization Chambers</b> | <b>67</b>  |

| 6.1 System architecture . . . . .                                        | 67         |

| 6.1.1 Analog section . . . . .                                           | 68         |

| 6.1.2 Digital section . . . . .                                          | 72         |

| 6.2 Reset generation scheme . . . . .                                    | 78         |

| 6.3 Design flow . . . . .                                                | 78         |

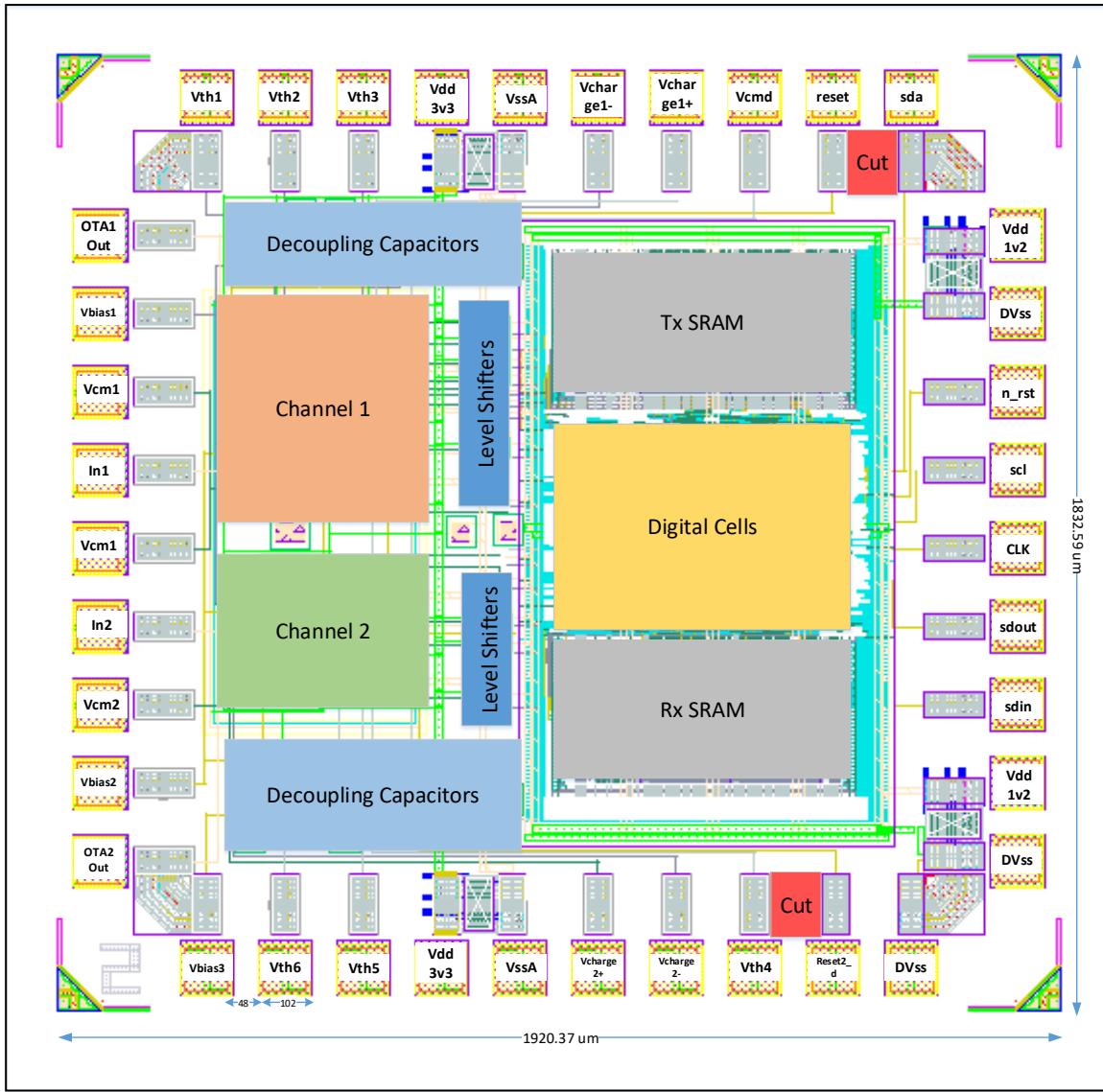

| 6.4 Mixed signal layout . . . . .                                        | 81         |

| 6.5 Measurement set-up and results . . . . .                             | 82         |

| 6.6 Conclusion . . . . .                                                 | 89         |

| <b>7 Characterization of ACCURATE 2</b>                                  | <b>91</b>  |

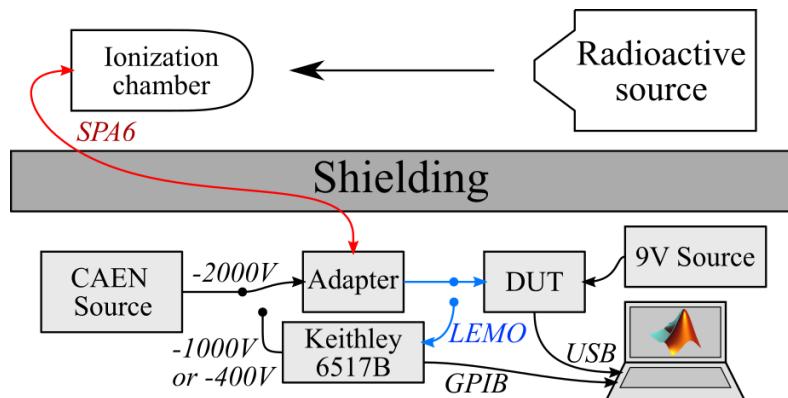

| 7.1 Measurements with radioactive sources . . . . .                      | 91         |

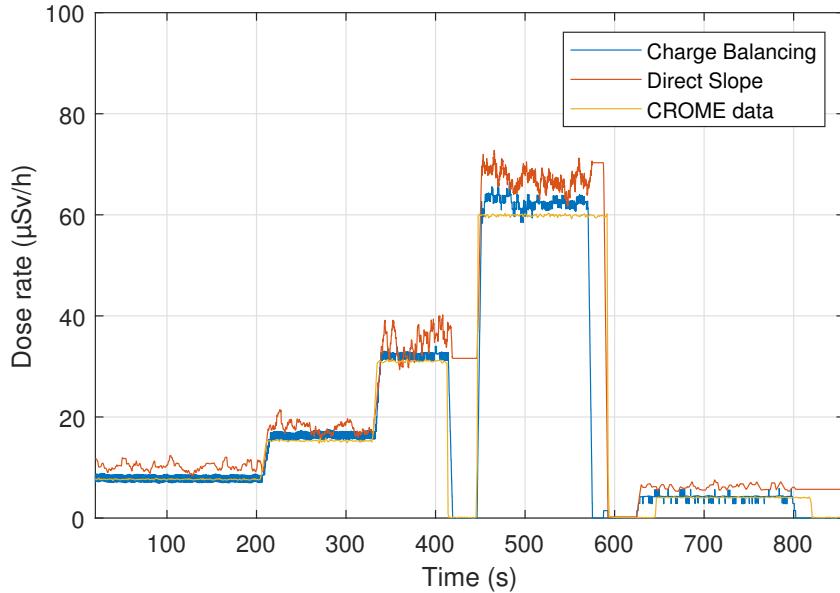

| 7.1.1 Comparison with CROME . . . . .                                    | 92         |

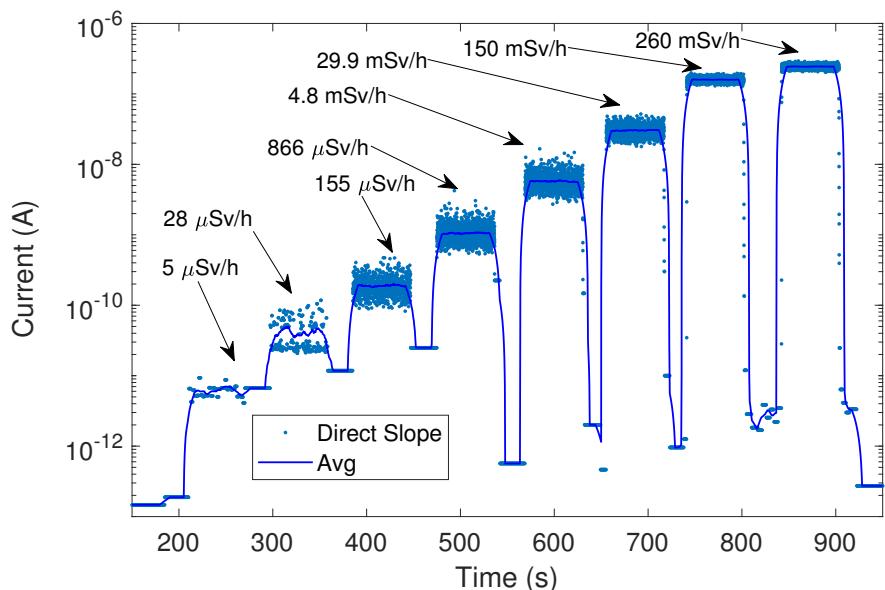

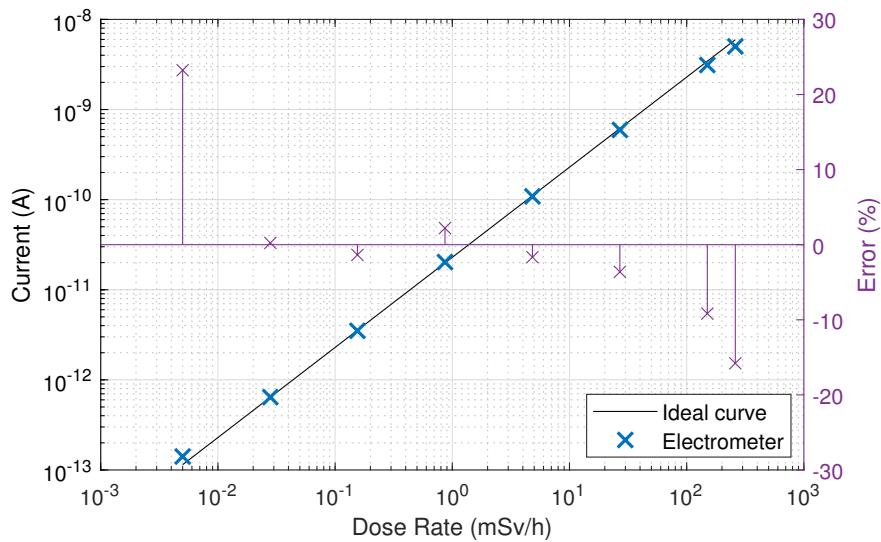

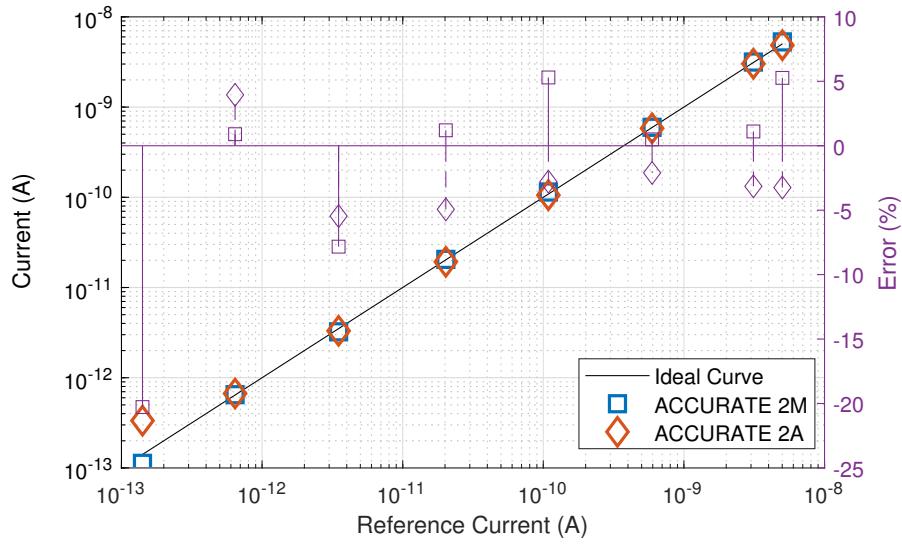

| 7.1.2 Comparison with electrometer . . . . .                             | 93         |

| 7.1.2.1 Interfacing with the PTW PMI T32006 chamber . . . . .            | 94         |

| 7.1.2.2 Interfacing with IG32 chamber . . . . .                          | 95         |

| 7.1.2.3 Interfacing with the IG5 chamber . . . . .                       | 96         |

| 7.2 Characterization of ACCURATE 2 with pulsed radiation . . . . .       | 98         |

| 7.3 Influence of humidity on current measurement . . . . .               | 103        |

| 7.4 Influence of temperature on current measurement . . . . .            | 103        |

| 7.4.1 Leakage current measurement at different temperatures . . . . .    | 104        |

| 7.4.2 Temperature dependency for the DSM method . . . . .                | 108        |

| 7.4.3 Stability analysis of the charge quantum . . . . .                 | 108        |

| 7.5 Conclusion . . . . .                                                 | 109        |

| <b>8 Conclusion and outlook</b>                                          | <b>111</b> |

| <b>Bibliography</b>                                                      | <b>117</b> |

*This page is intentionally left blank.*

# List of Figures

|      |                                                                                                  |    |

|------|--------------------------------------------------------------------------------------------------|----|

| 1.1  | CERN's accelerator complex . . . . .                                                             | 1  |

| 1.2  | Creation of radiation by particle accelerators . . . . .                                         | 2  |

| 1.3  | SPS BIS interface . . . . .                                                                      | 4  |

| 1.4  | Radiation monitoring system . . . . .                                                            | 4  |

| 1.5  | PTW PMI T32006 chamber . . . . .                                                                 | 6  |

| 1.6  | IG5 chamber . . . . .                                                                            | 6  |

| 2.1  | ARCON system . . . . .                                                                           | 10 |

| 2.2  | RAMSES system . . . . .                                                                          | 11 |

| 2.3  | CROME architecture . . . . .                                                                     | 12 |

| 2.4  | UTOPIA 2 FPGA architecture . . . . .                                                             | 14 |

| 2.5  | Integration time for different input currents . . . . .                                          | 15 |

| 2.6  | Laboratory set-up for pulsed current measurement . . . . .                                       | 16 |

| 2.7  | Charge measurement with pulsed input current . . . . .                                           | 17 |

| 2.8  | Response of UTOPIA 2 to exponential input . . . . .                                              | 18 |

| 2.9  | Response of UTOPIA 2 to square wave . . . . .                                                    | 18 |

| 2.10 | Experimental set-up at CLEAR showing positions of the ionization chambers . . . . .              | 19 |

| 2.11 | Results from measurement at CLEAR facility . . . . .                                             | 20 |

| 2.12 | Measurement set-up at IRA . . . . .                                                              | 21 |

| 2.13 | Charge measurement by UTOPIA 2 and reference electrometer for a pulsed beam . . . . .            | 22 |

| 3.1  | Low current measurement methods . . . . .                                                        | 28 |

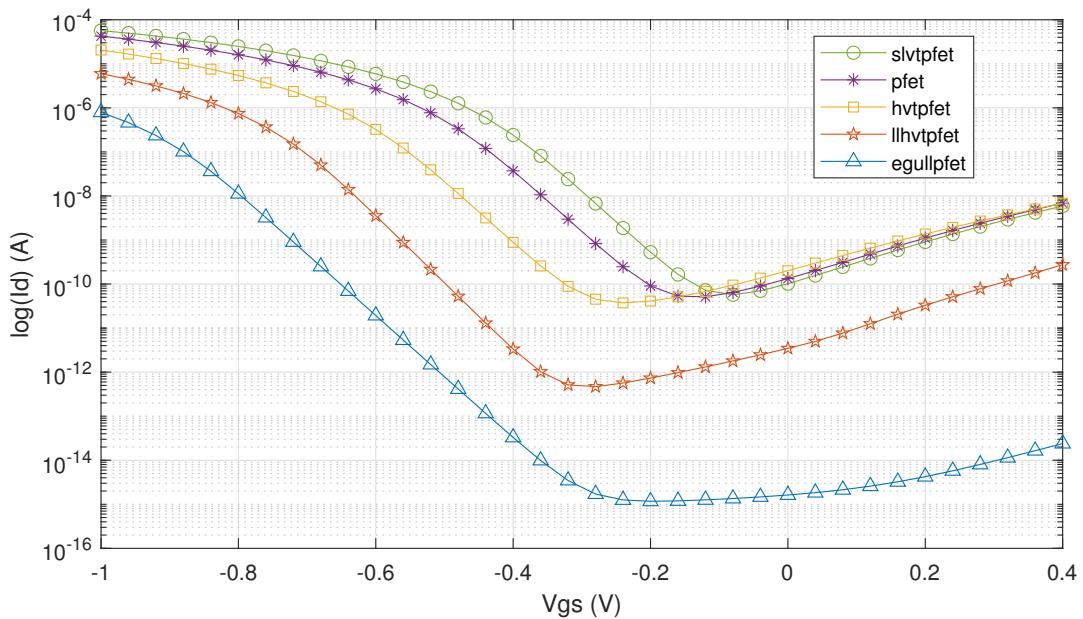

| 4.1  | Drain current characteristic for different transistors of 22FDX process design kit . . . . .     | 34 |

| 4.2  | Gate current characteristic for different transistors of 22FDX process design kit . . . . .      | 35 |

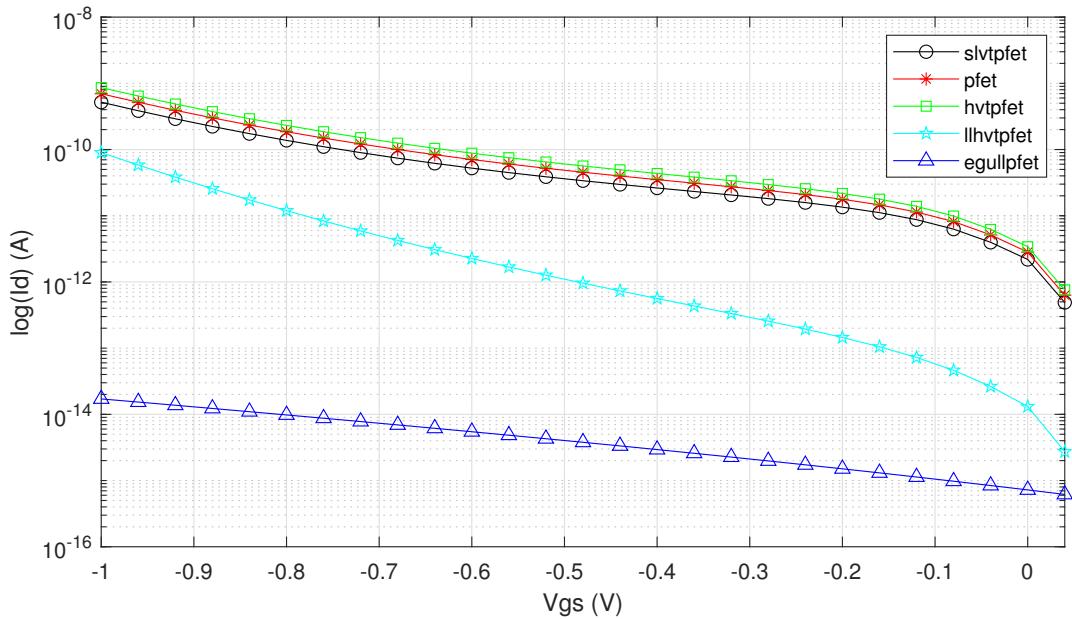

| 4.3  | OTA integrator . . . . .                                                                         | 35 |

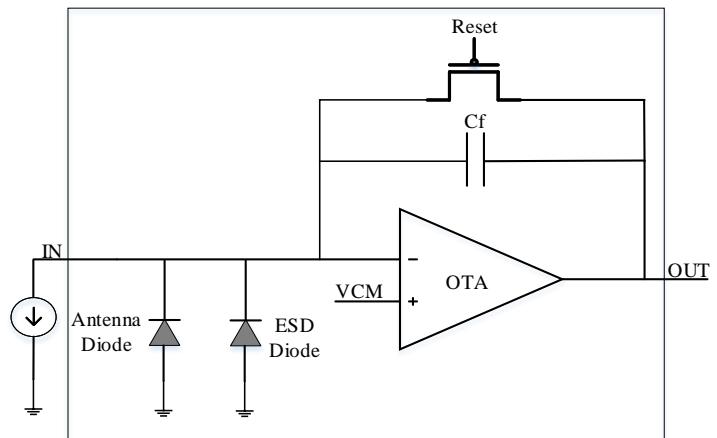

| 4.4  | Folded Cascode OTA . . . . .                                                                     | 36 |

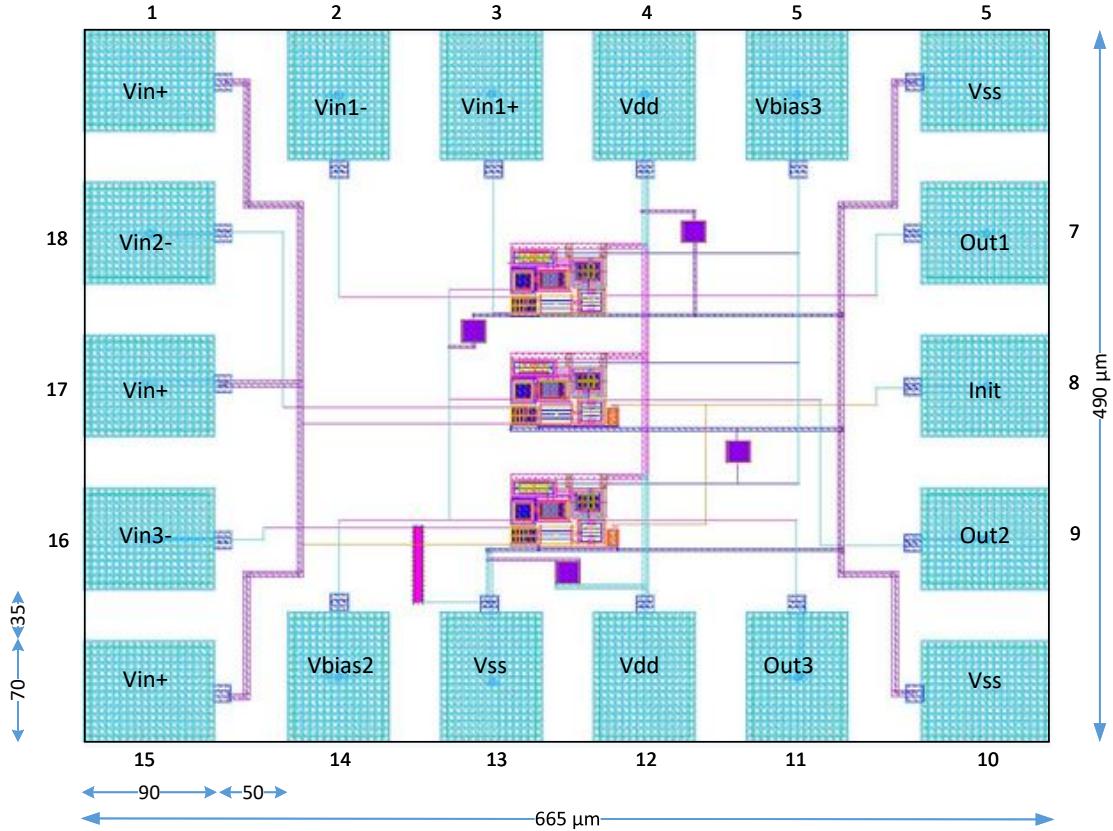

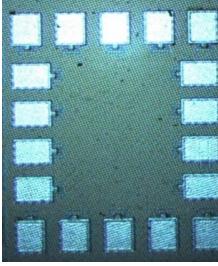

| 4.5  | Layout of ACCURATE 0 . . . . .                                                                   | 37 |

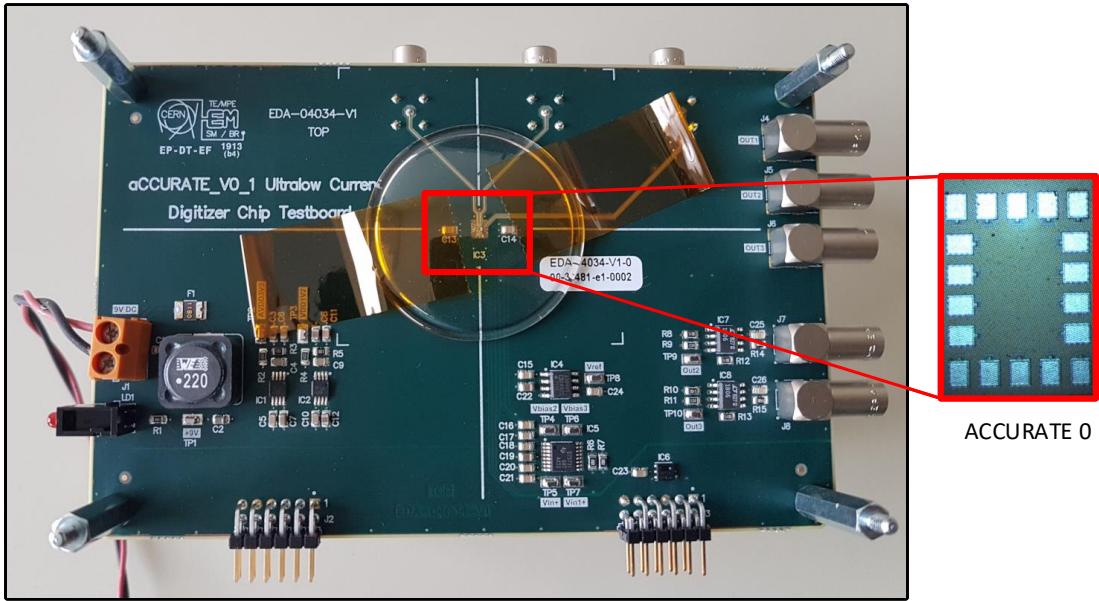

| 4.6  | ACCURATE 0 test board . . . . .                                                                  | 38 |

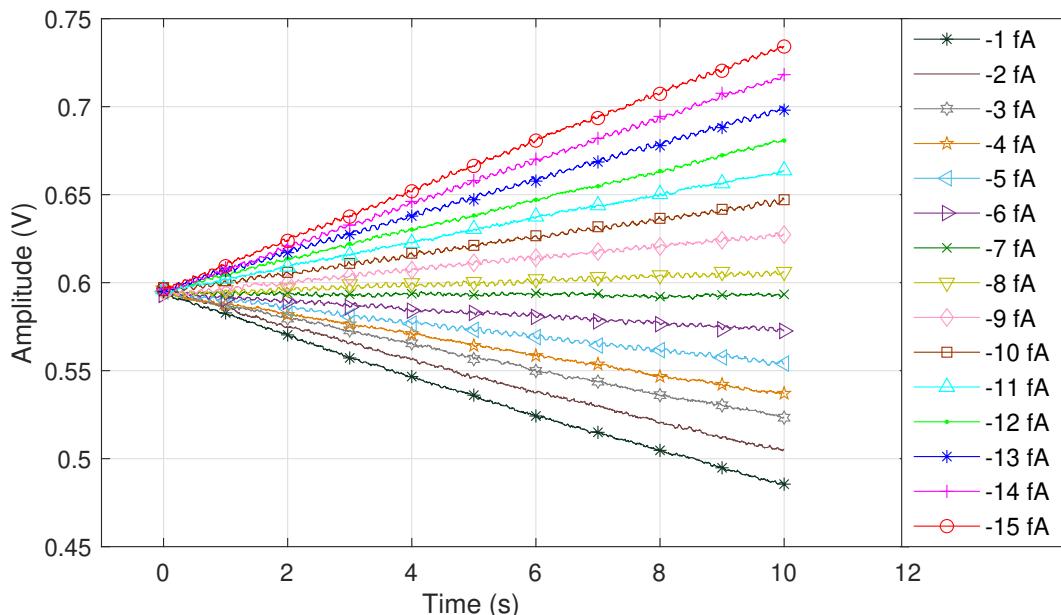

| 4.7  | Channel 2 output with input current swept from $-1\text{ fA}$ to $-15\text{ fA}$ . . . . .       | 38 |

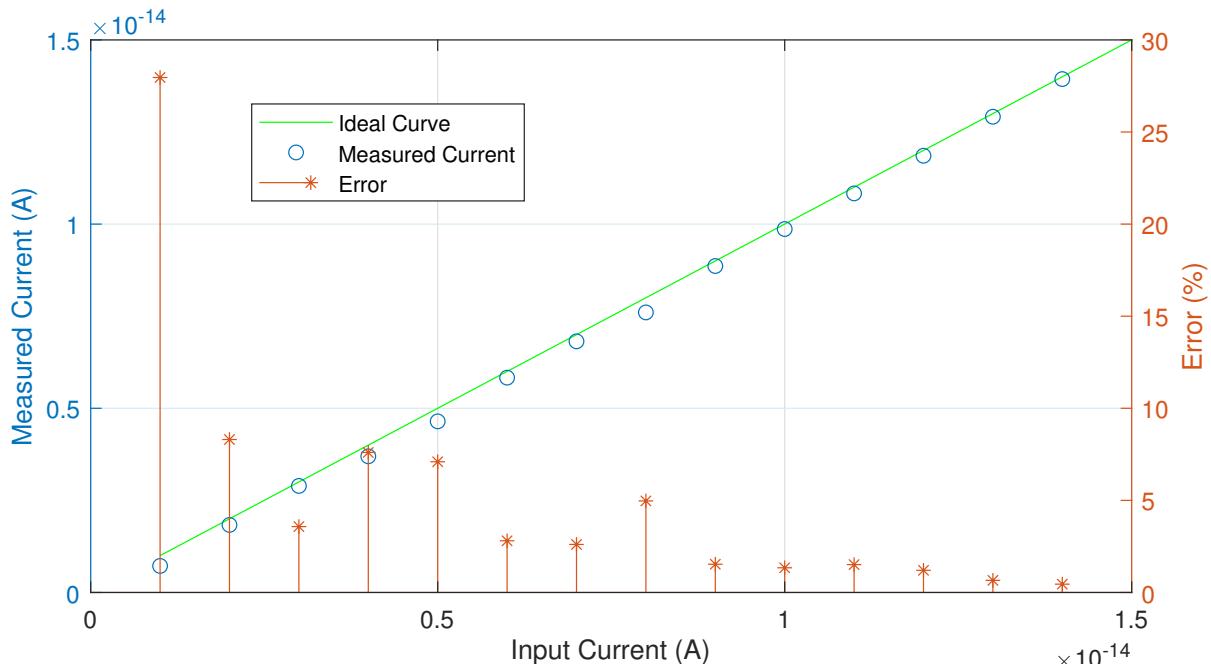

| 4.8  | Linearity and error plot channel 2 for currents from $-1\text{ fA}$ to $-15\text{ fA}$ . . . . . | 39 |

| 4.9  | Channel 2 output for input current sweep of $-1\text{ pA}$ to $-1\text{ nA}$ . . . . .           | 40 |

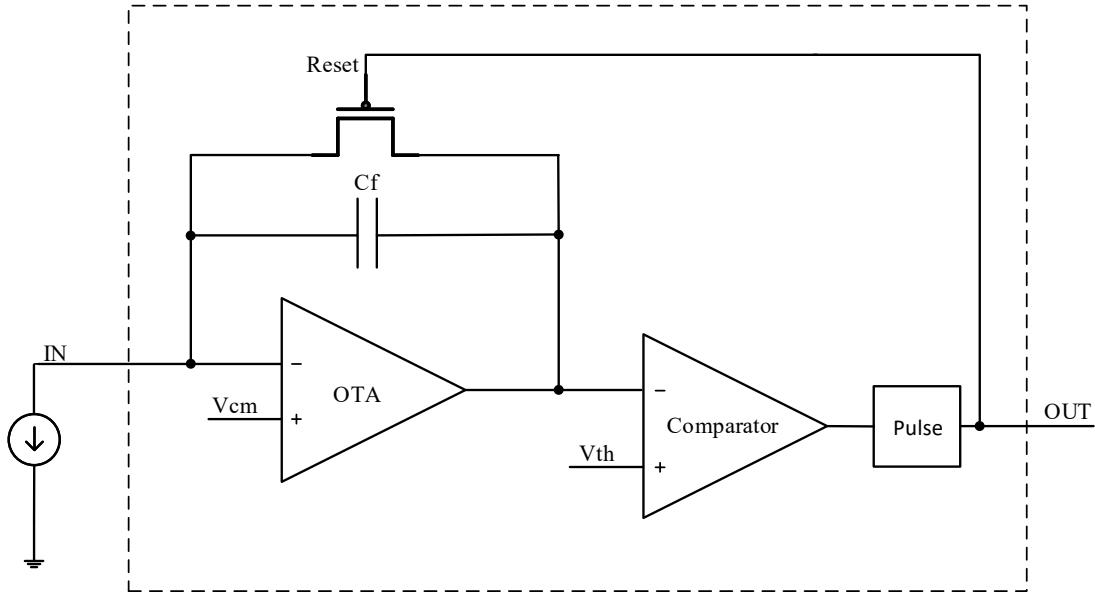

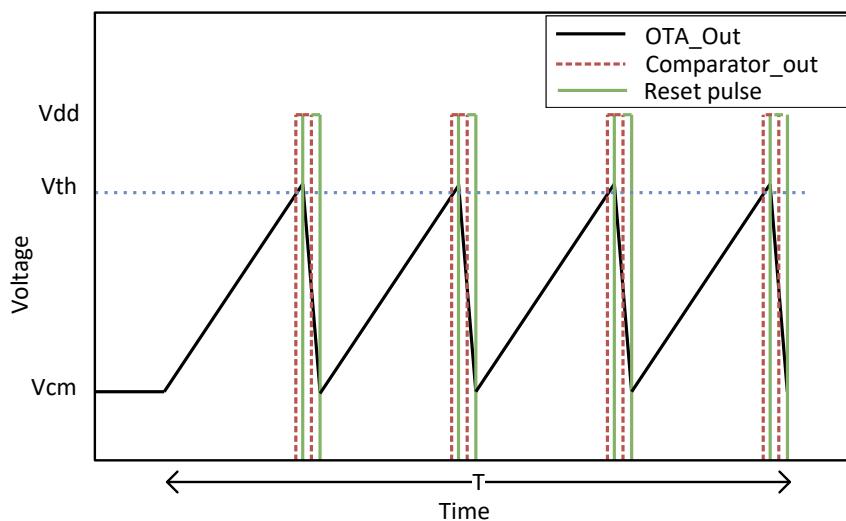

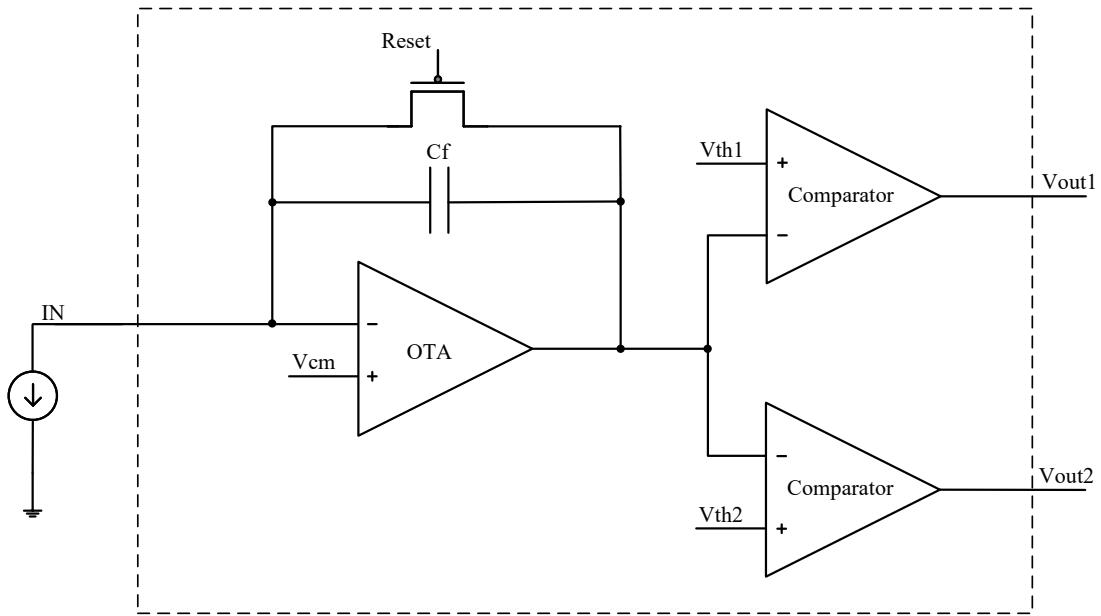

| 5.1  | Reset counting method . . . . .                                                                  | 42 |

|      |                                                                                                                       |    |

|------|-----------------------------------------------------------------------------------------------------------------------|----|

| 5.2  | CFC output in the reset counting method . . . . .                                                                     | 42 |

| 5.3  | Ideal output of the reset counting CFC . . . . .                                                                      | 43 |

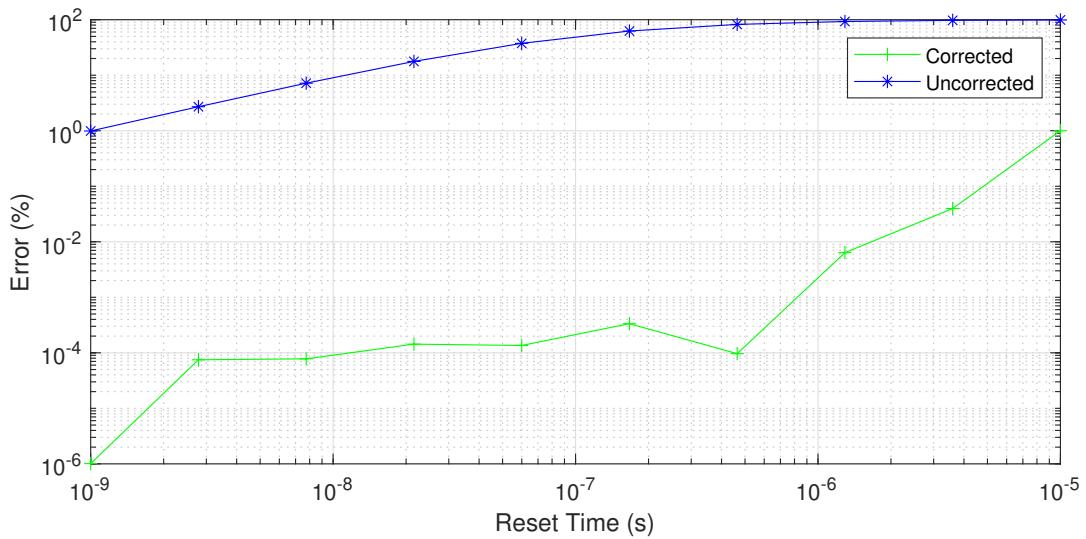

| 5.4  | Effect of reset time on current calculation in the reset counting method . . . . .                                    | 44 |

| 5.5  | Direct slope measurement method . . . . .                                                                             | 45 |

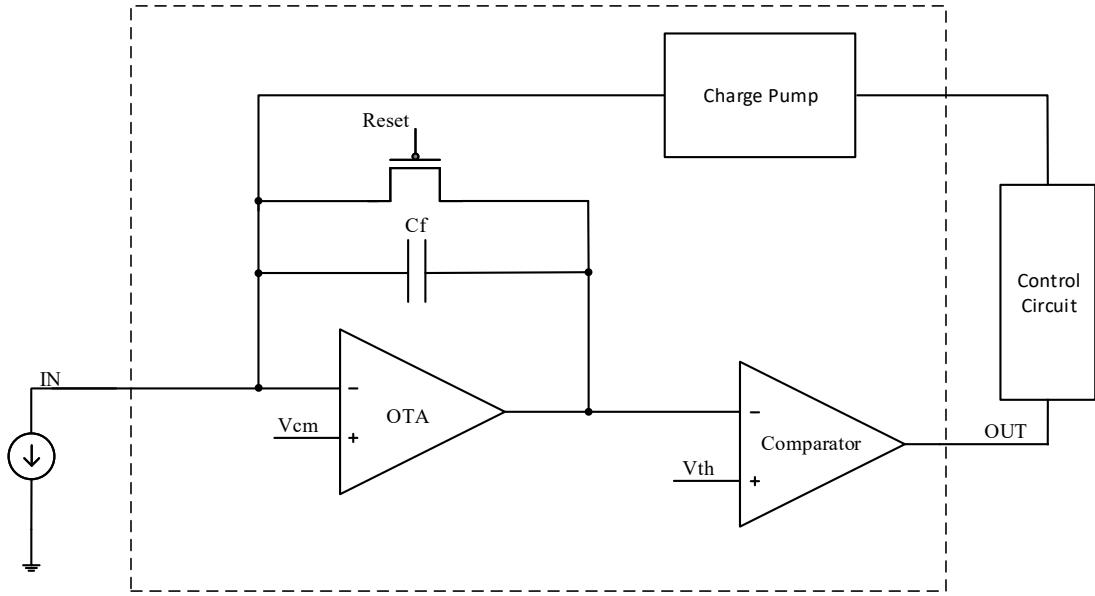

| 5.6  | Charge balancing method . . . . .                                                                                     | 47 |

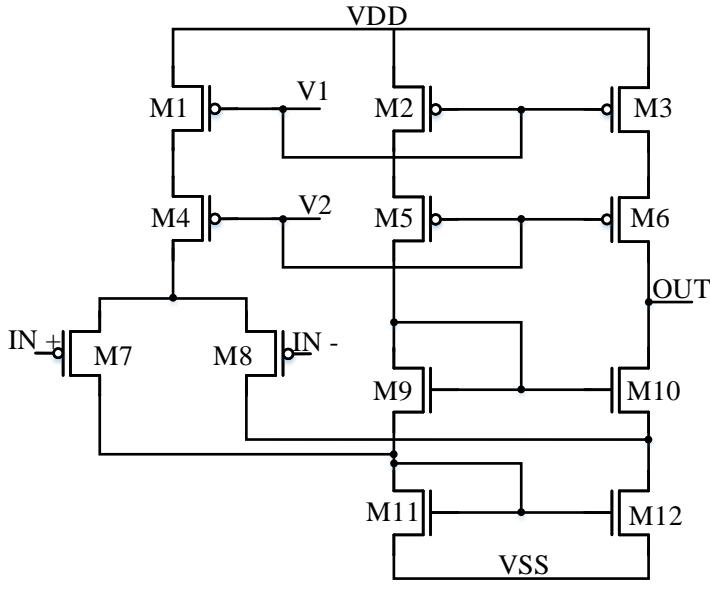

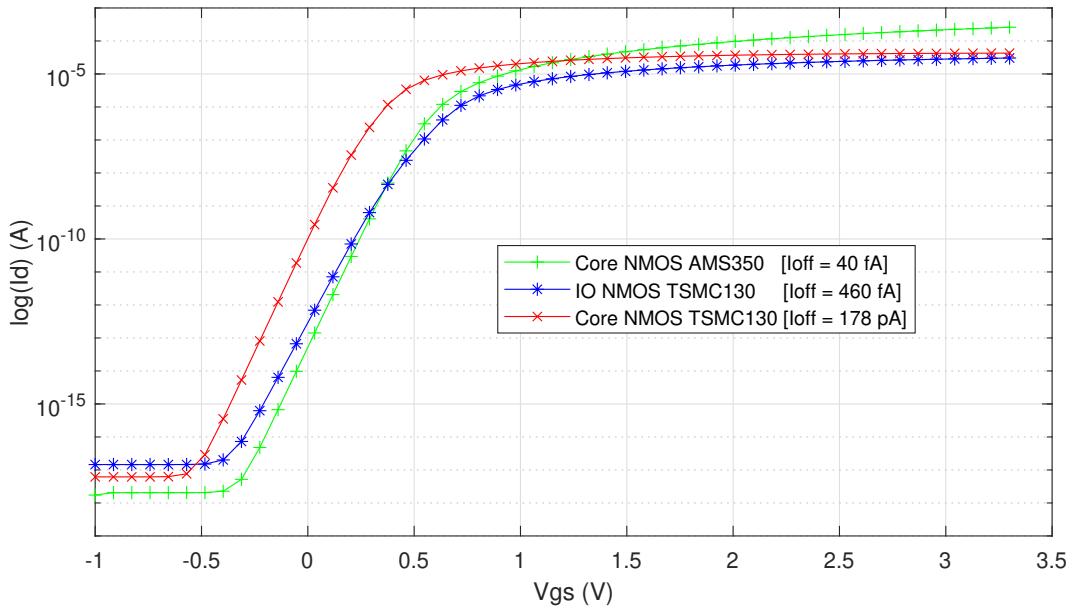

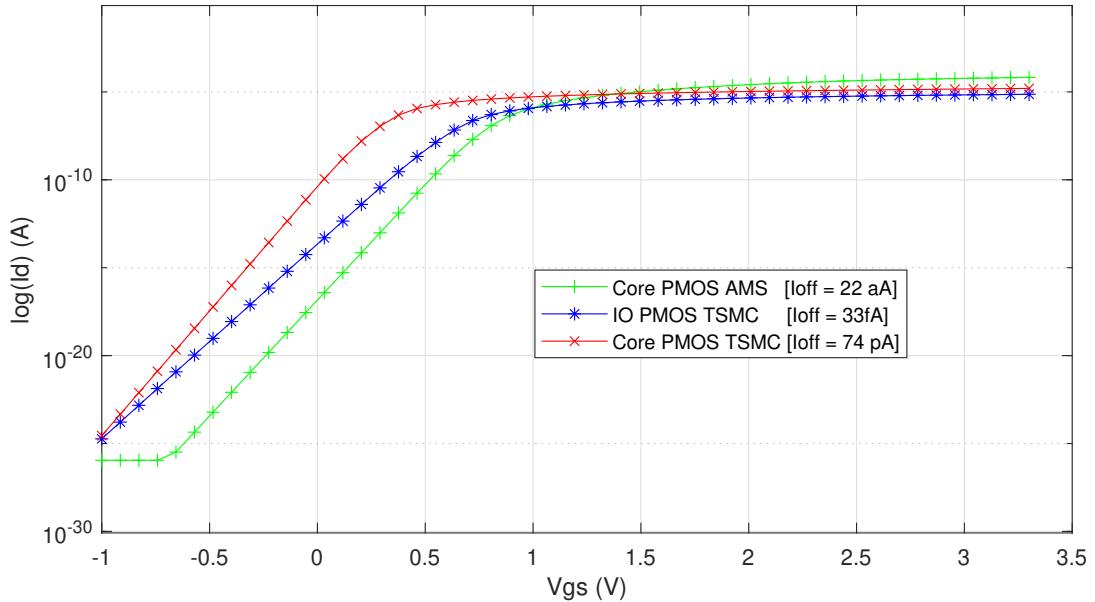

| 5.7  | Drain current characteristics for TSMC 130 nm and AMS 350 nm NMOS transistors . . .                                   | 49 |

| 5.8  | Drain current characteristics for TSMC 130 nm and AMS 350 nm PMOS transistors . . .                                   | 49 |

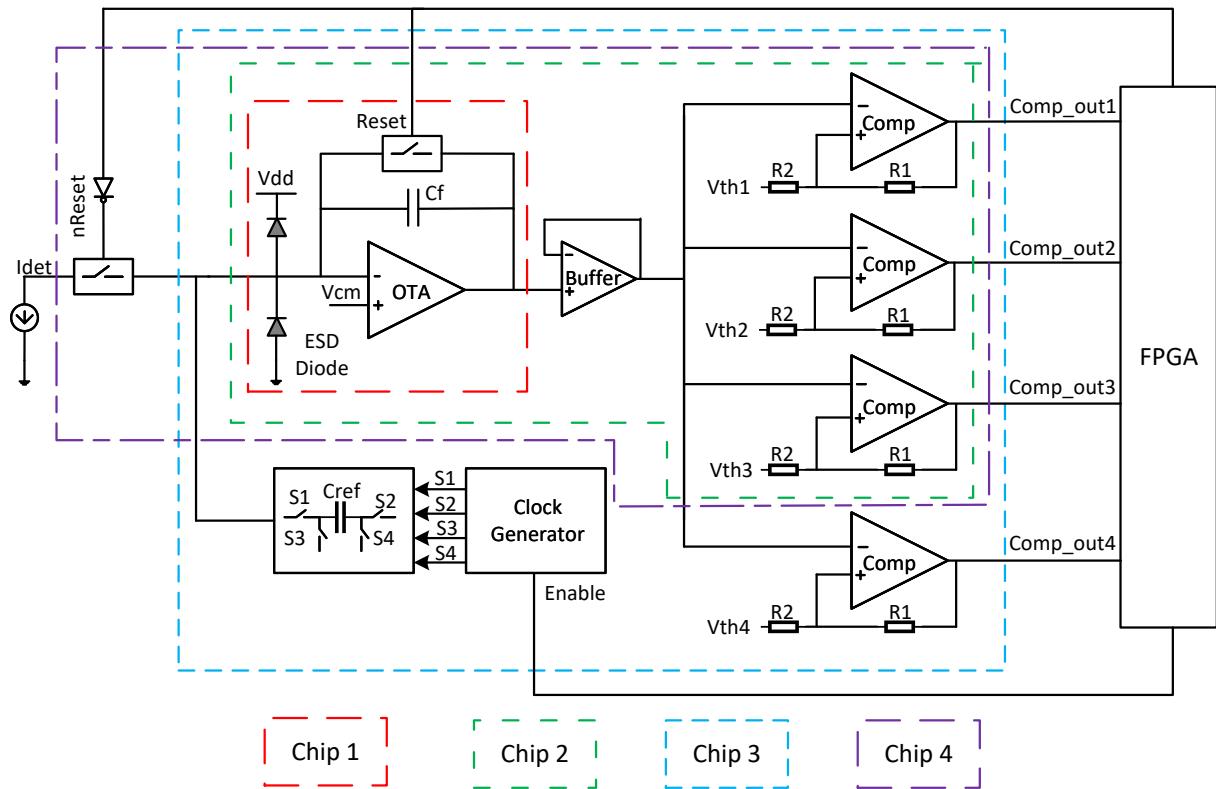

| 5.9  | System architecture of ACCURATE 1 . . . . .                                                                           | 50 |

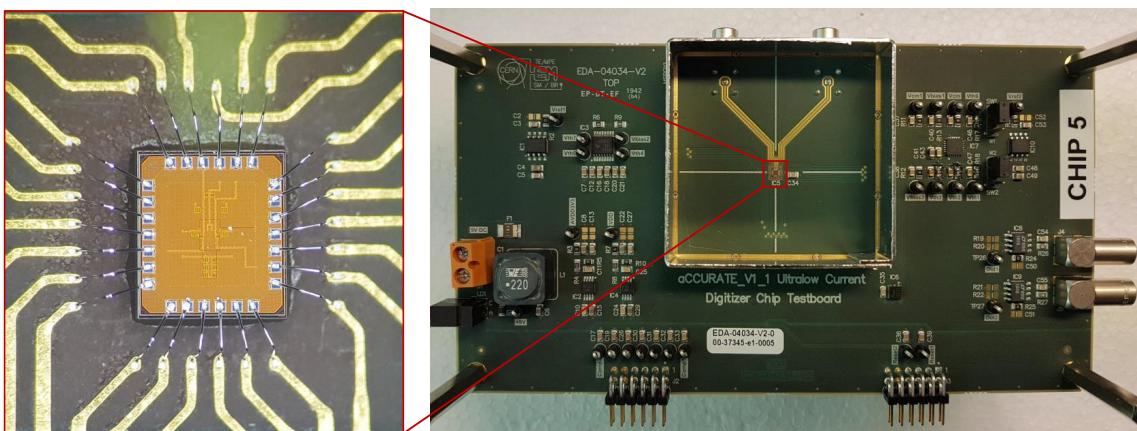

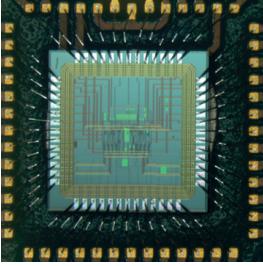

| 5.10 | ACCURATE 1 ASIC and its test board . . . . .                                                                          | 55 |

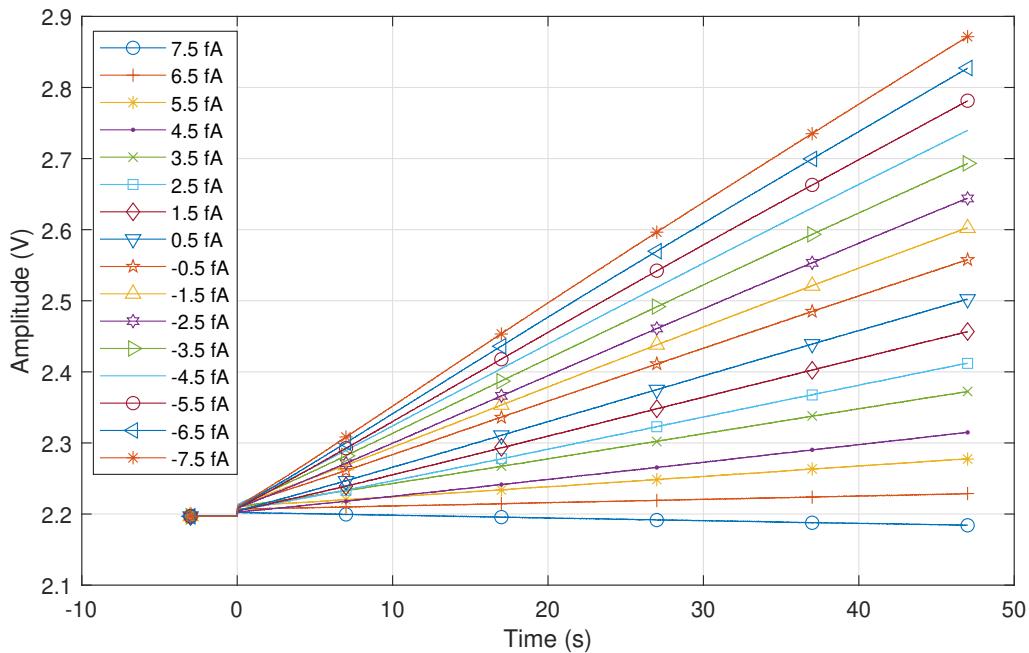

| 5.11 | Femtoampere sensitivity demonstrated by the output of Chip 1 . . . . .                                                | 56 |

| 5.12 | OTA output for an input current of $-1\text{ pA}$ for two different common-mode voltages . .                          | 57 |

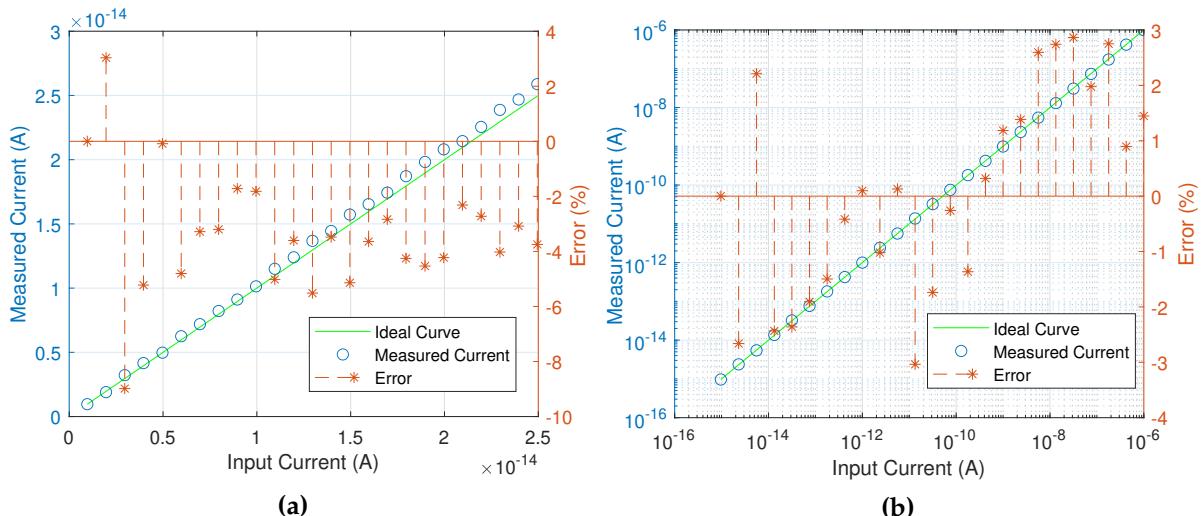

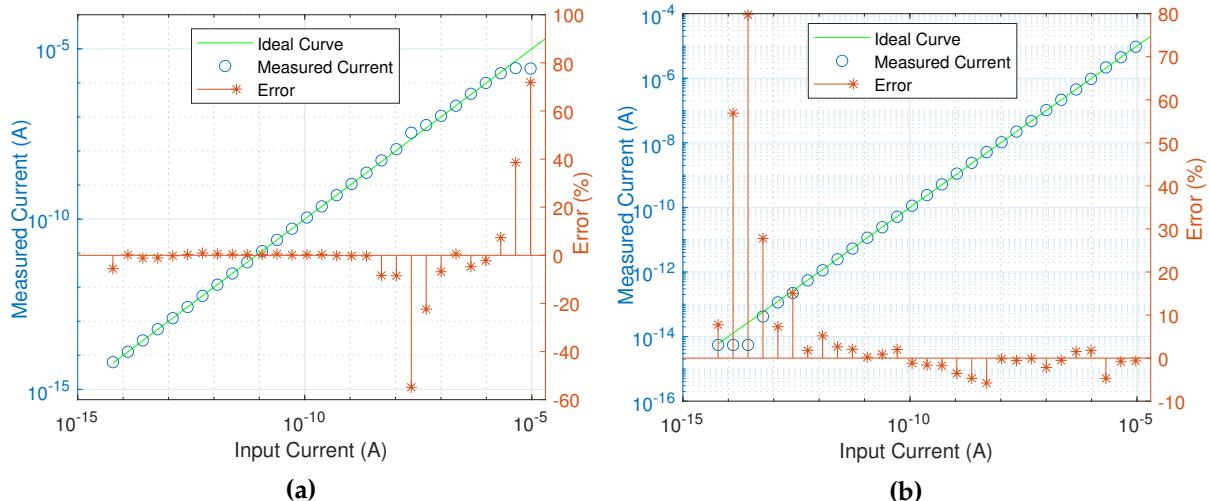

| 5.13 | Femtoamperes characterization of (a) reset counting method, (b) direct slope method . .                               | 57 |

| 5.14 | Output of Chip 2 with input swept from $-1\text{ pA}$ to $-1\text{ nA}$ . . . . .                                     | 58 |

| 5.15 | OTA output from ACCURATE 1 and UTOPIA2 influenced by external noise . . . . .                                         | 59 |

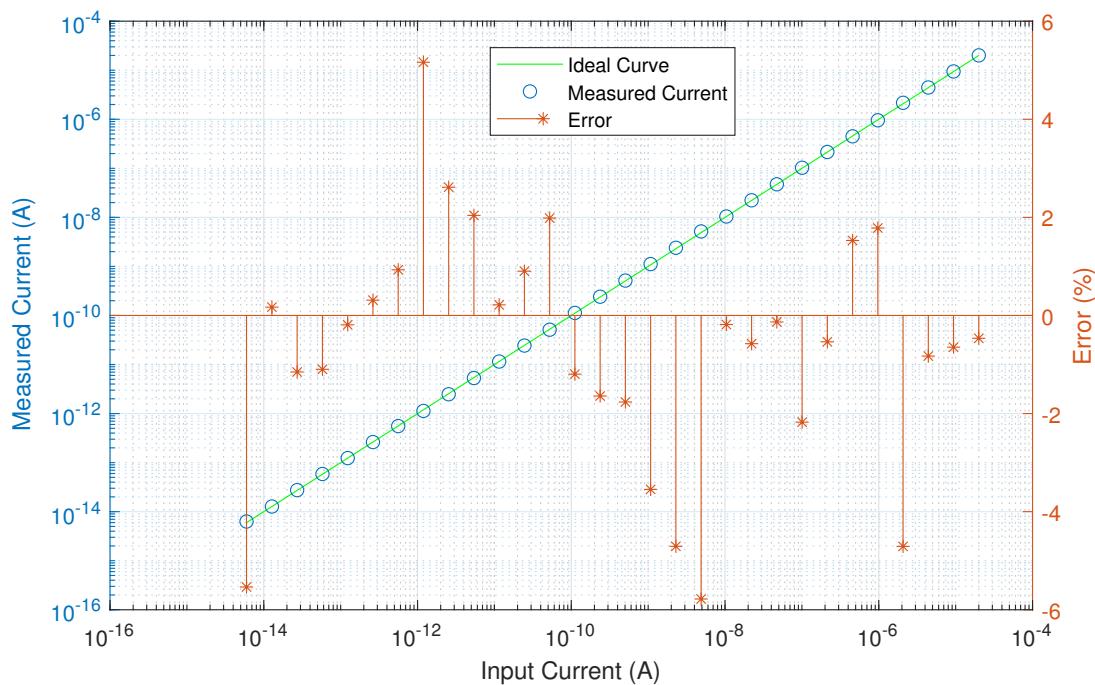

| 5.16 | ACCURATE 1 Chip 3 output for currents from $-1\text{ fA}$ to $-25\text{ fA}$ and $-1\text{ fA}$ to $-1\text{ uA}$ . . | 60 |

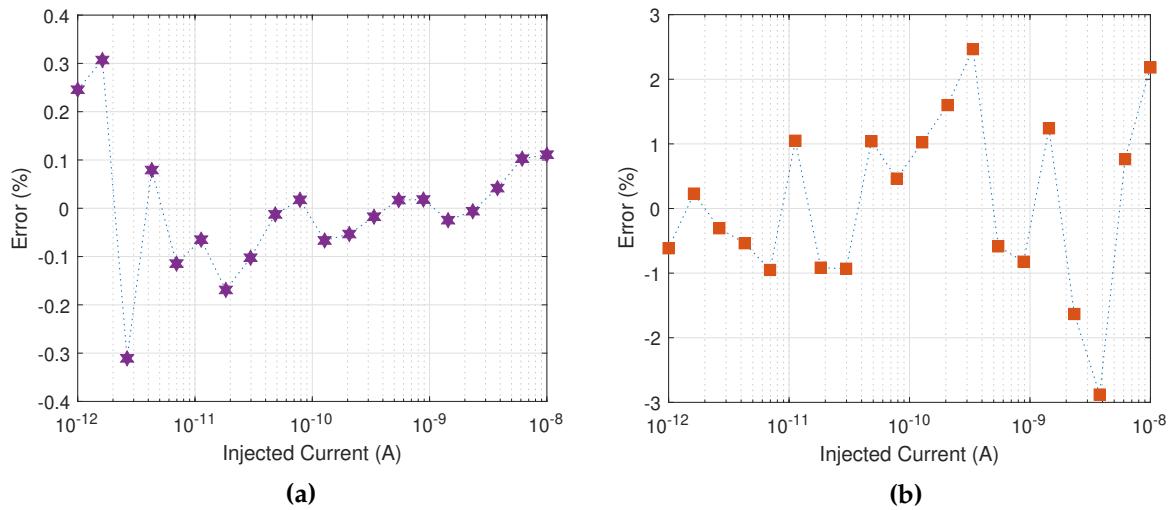

| 5.17 | Output of ACCURATE 1 Chip 3 for CB and DSM method . . . . .                                                           | 61 |

| 5.18 | ACCURATE 1 Chip4 output showing the effect of input switch on current measurement                                     | 62 |

| 5.19 | Leakage current measurements by Chip 4 . . . . .                                                                      | 63 |

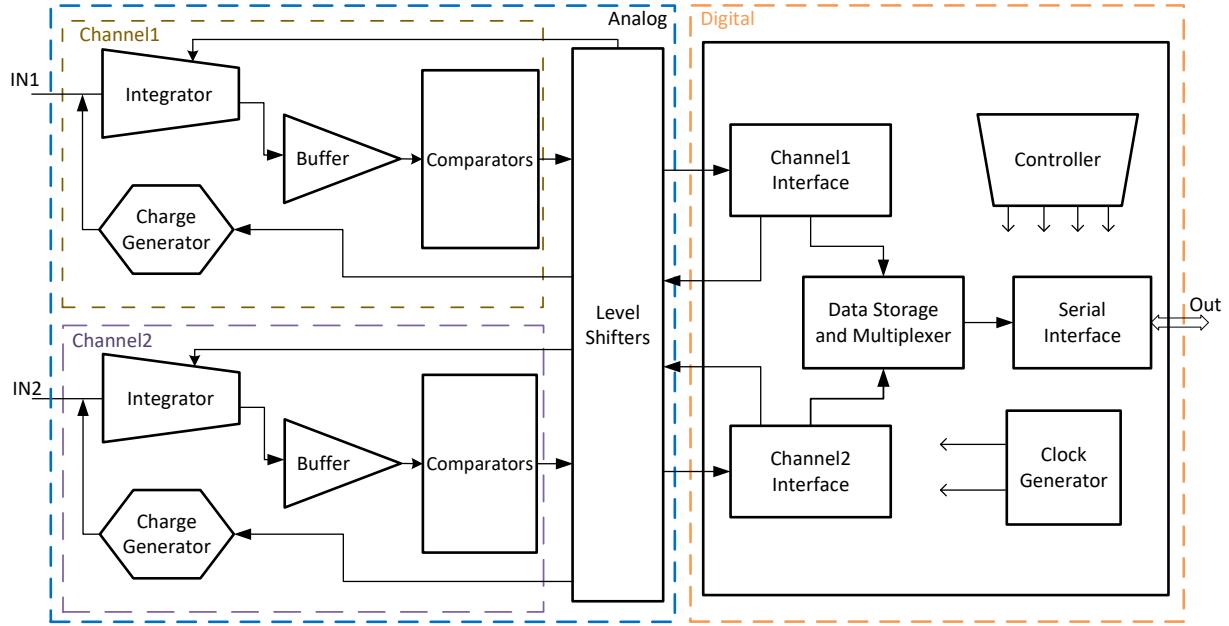

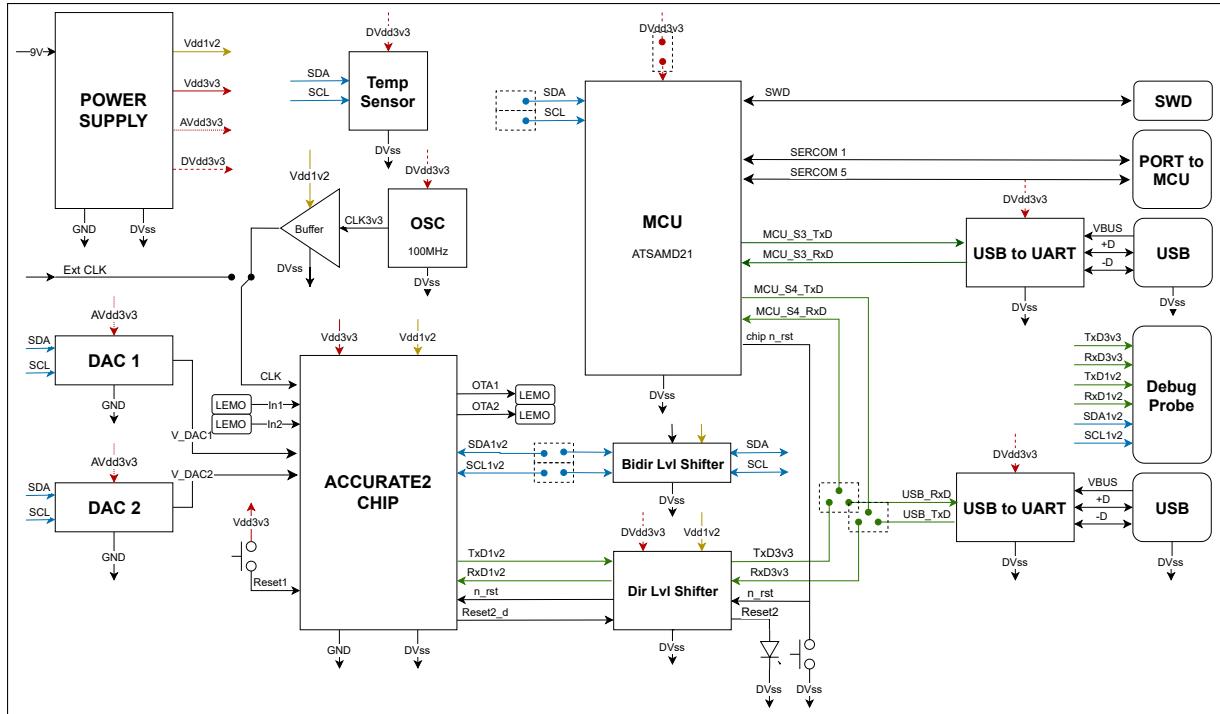

| 6.1  | ACCURATE 2 system architecture . . . . .                                                                              | 68 |

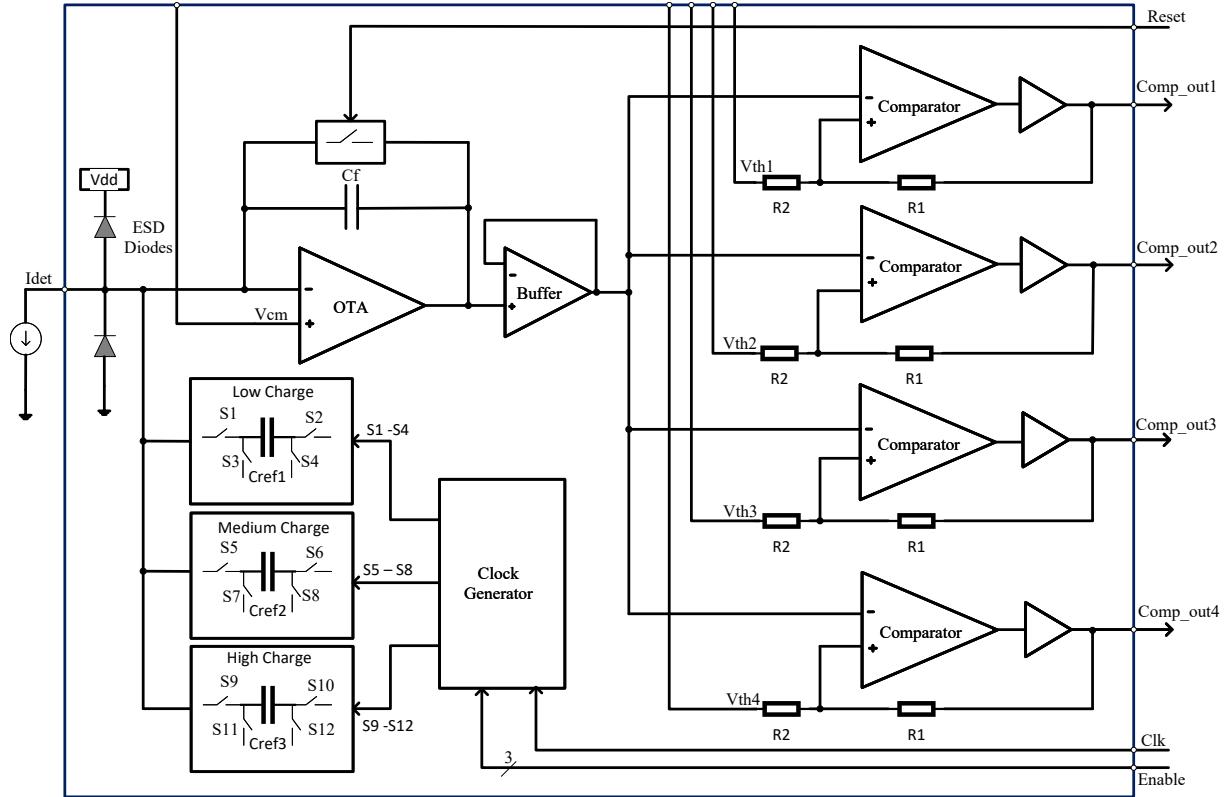

| 6.2  | Analog section of ACCURATE 2 system architecture . . . . .                                                            | 69 |

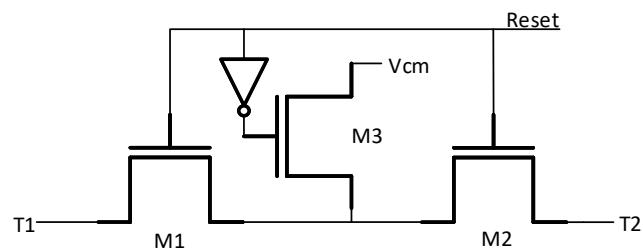

| 6.3  | Reset switch configuration . . . . .                                                                                  | 70 |

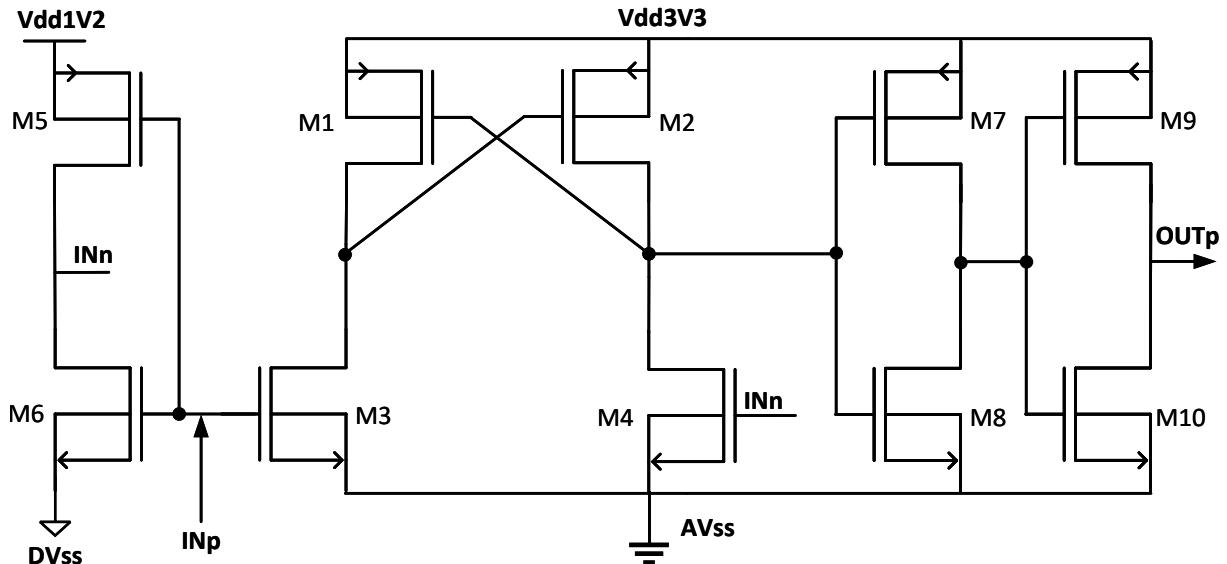

| 6.4  | 1.2 V to 3.3 V level shifter . . . . .                                                                                | 71 |

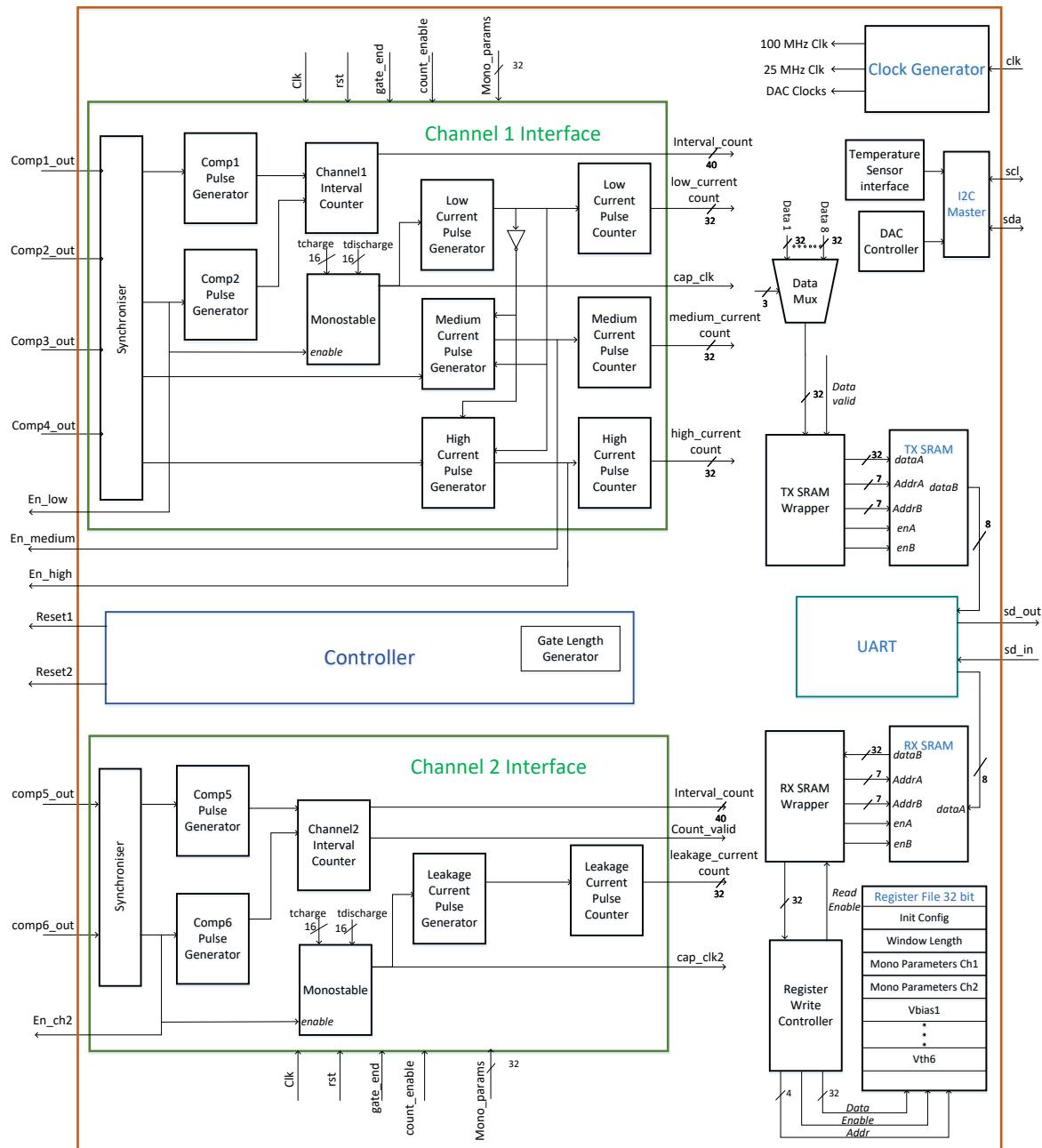

| 6.5  | Digital section of ACCURATE 2M . . . . .                                                                              | 73 |

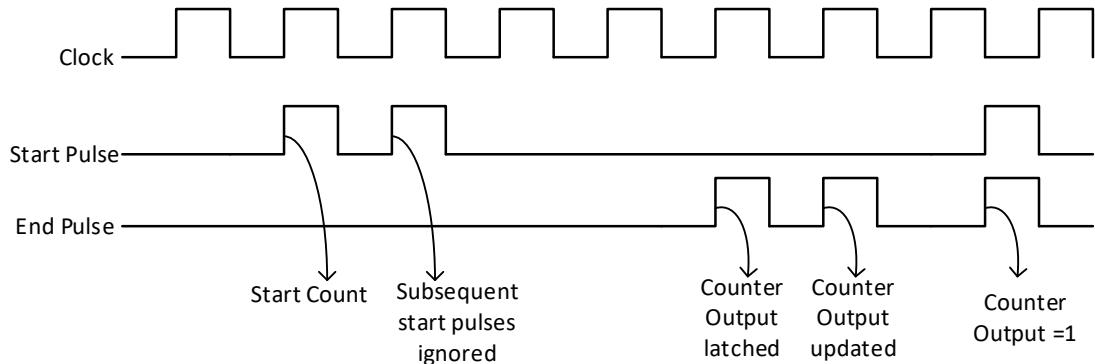

| 6.6  | Behaviour of interval counter module . . . . .                                                                        | 74 |

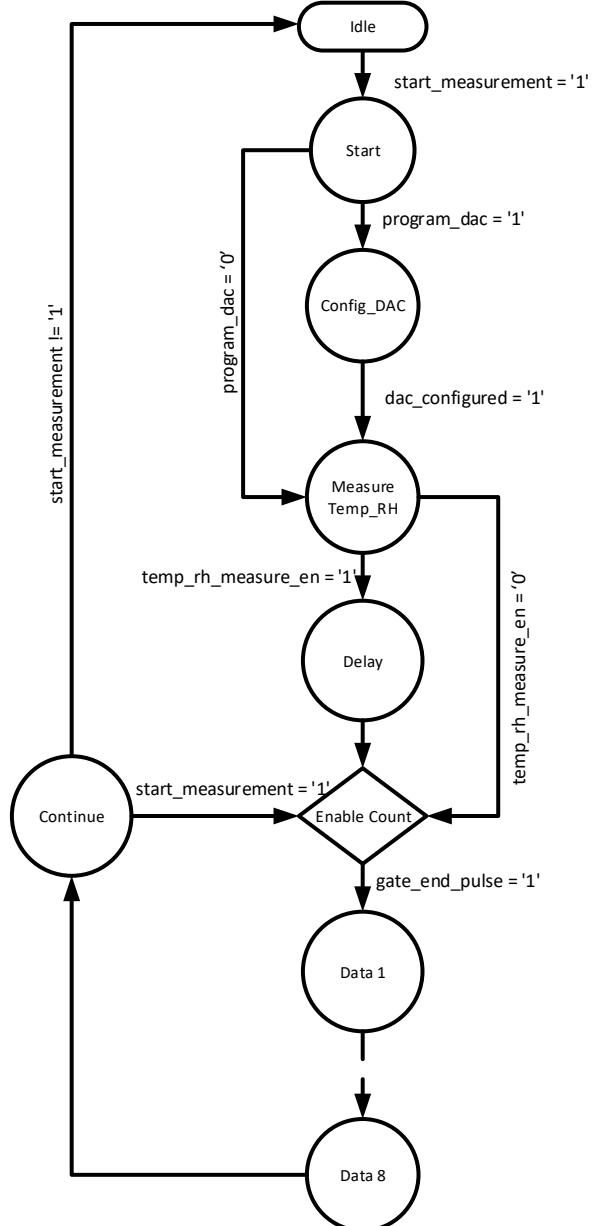

| 6.7  | ACCURATE 2 controller state machine . . . . .                                                                         | 76 |

| 6.8  | Reset generation logic . . . . .                                                                                      | 78 |

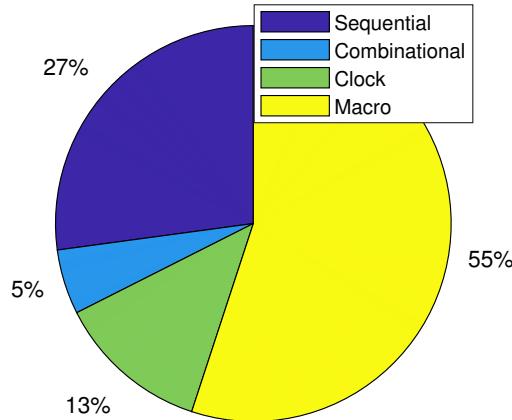

| 6.9  | Power distribution in the digital section of ACCURATE 2M . . . . .                                                    | 80 |

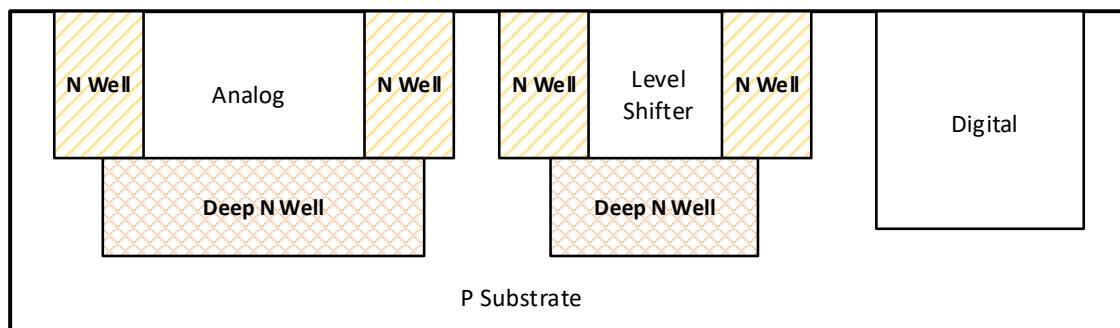

| 6.10 | Design separation using Deep N-Well . . . . .                                                                         | 81 |

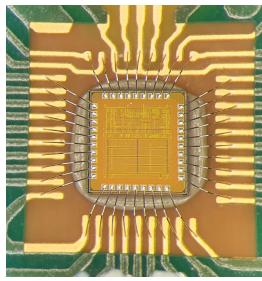

| 6.11 | ACCURATE 2 layout . . . . .                                                                                           | 83 |

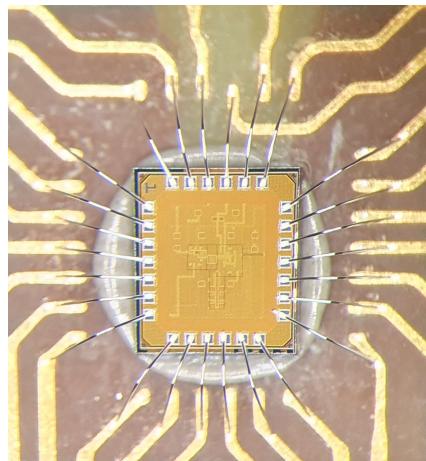

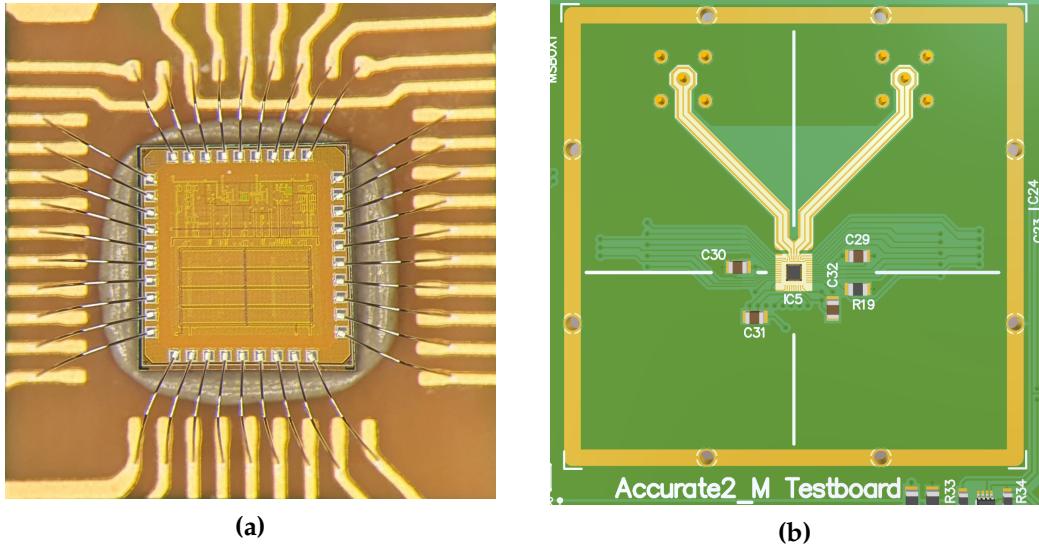

| 6.12 | Micrograph of ACCURATE 2A . . . . .                                                                                   | 84 |

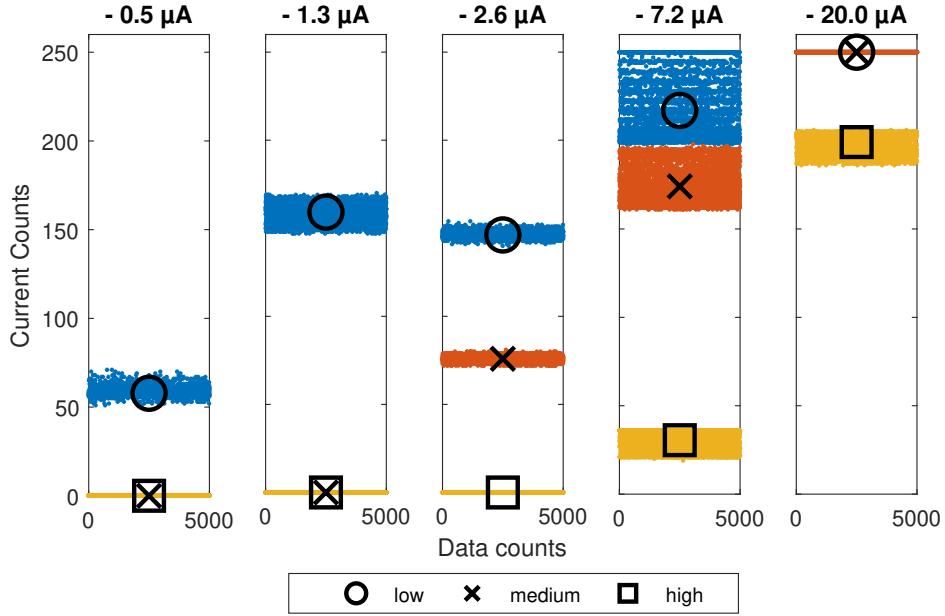

| 6.13 | Spread of charge injection pulse counts for different currents . . . . .                                              | 85 |

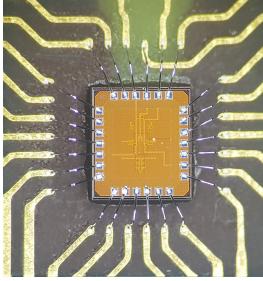

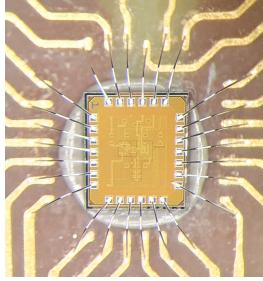

| 6.14 | Test board of ACCURATE 2M . . . . .                                                                                   | 85 |

| 6.15 | ACCURATE 2M of (a) micrograph, (b) bonding section on test board . . . . .                                            | 86 |

| 6.16 | ACCURATE 2A output with DSM and CB methods . . . . .                                                                  | 86 |

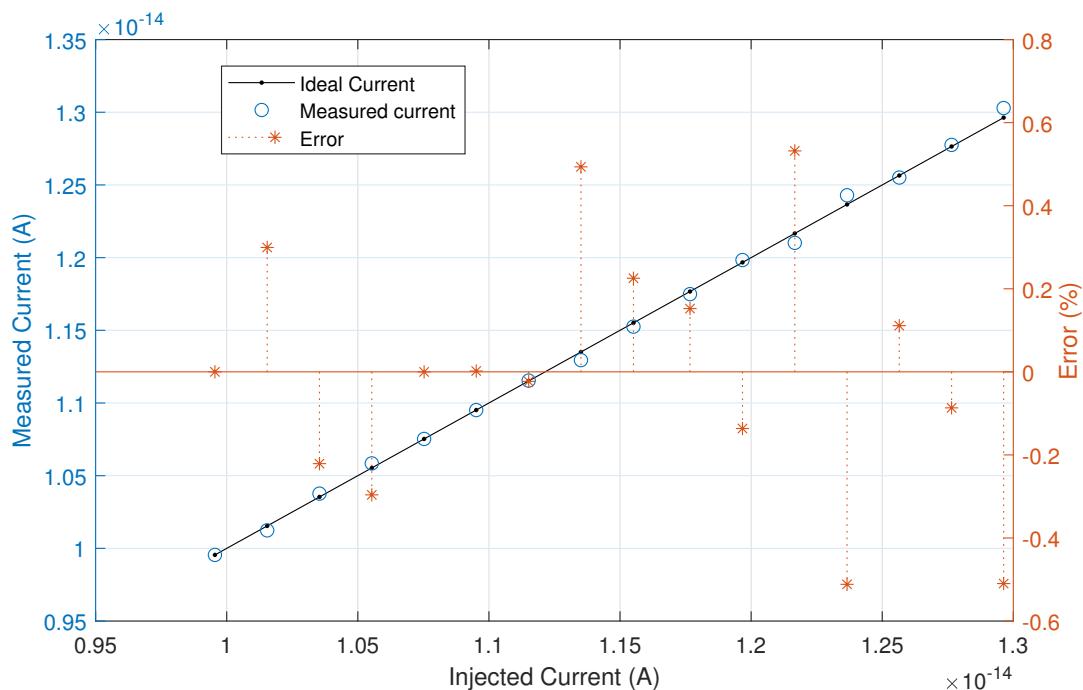

| 6.17 | System linearity of ACCURATE 2A . . . . .                                                                             | 87 |

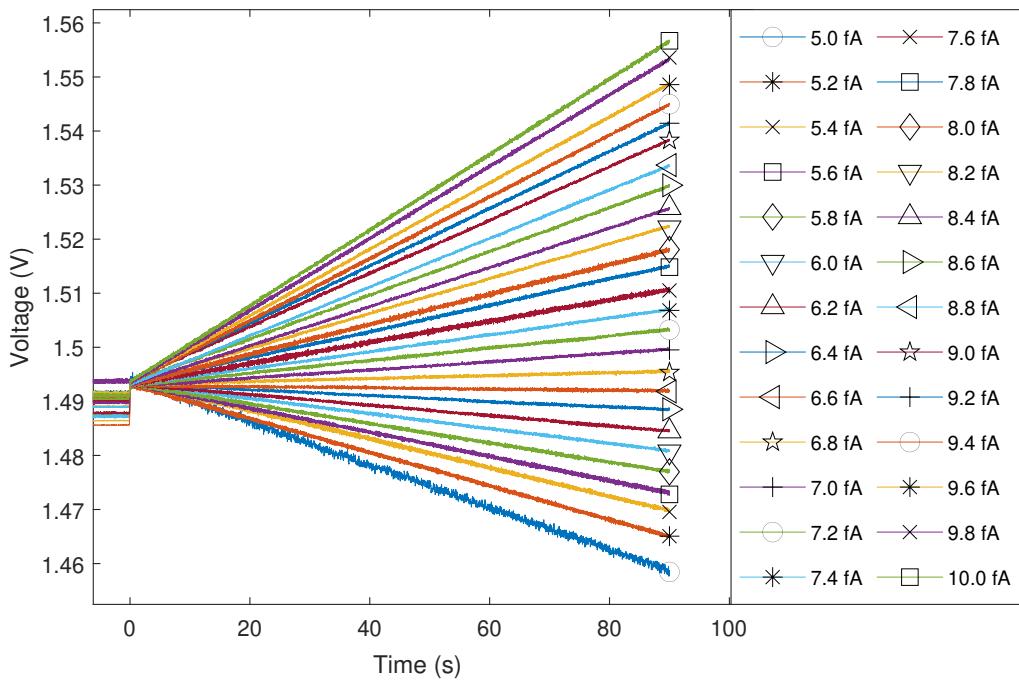

| 6.18 | Integrator output with input current swept from $-5\text{ fA}$ to $-10\text{ fA}$ in steps of $200\text{ aA}$ . .     | 88 |

| 6.19 | ACCURATE 2 output with input current swept from $-10\text{ fA}$ to $-13\text{ fA}$ in steps of $200\text{ aA}$        | 89 |

| 7.1  | Calibration laboratory arrangement . . . . .                                                                          | 91 |

| 7.2  | Measurement set-up at calibration lab . . . . .                                                                       | 92 |

|      |                                                                                                        |     |

|------|--------------------------------------------------------------------------------------------------------|-----|

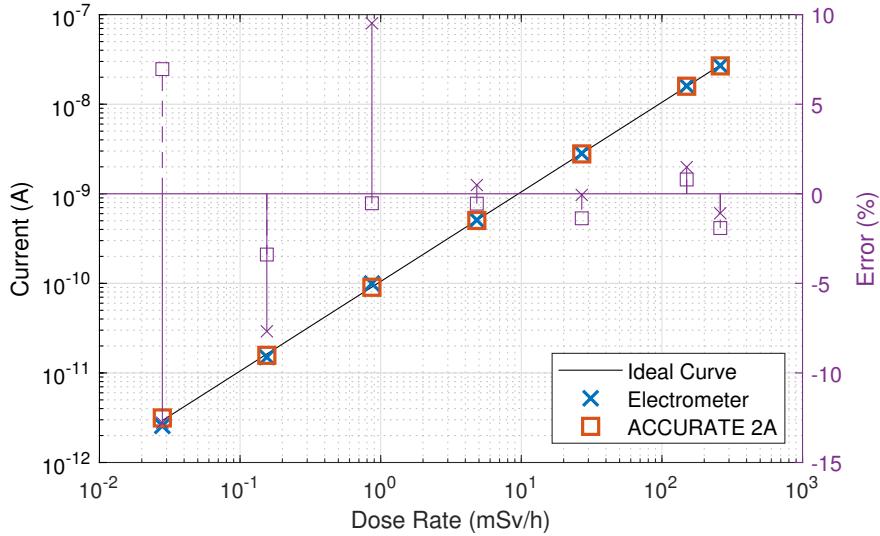

| 7.3  | ACCURATE 2A measurement in comparison with CROME . . . . .                                             | 93  |

| 7.4  | Current measured by ACCURATE 2M using IG5 ionization chamber for different dose rates . . . . .        | 94  |

| 7.5  | Current measured by electrometer for different dose rates . . . . .                                    | 95  |

| 7.6  | Linearity of ACCURATE 2A with PMI chambers . . . . .                                                   | 96  |

| 7.7  | Current measurement with IG32 chamber . . . . .                                                        | 96  |

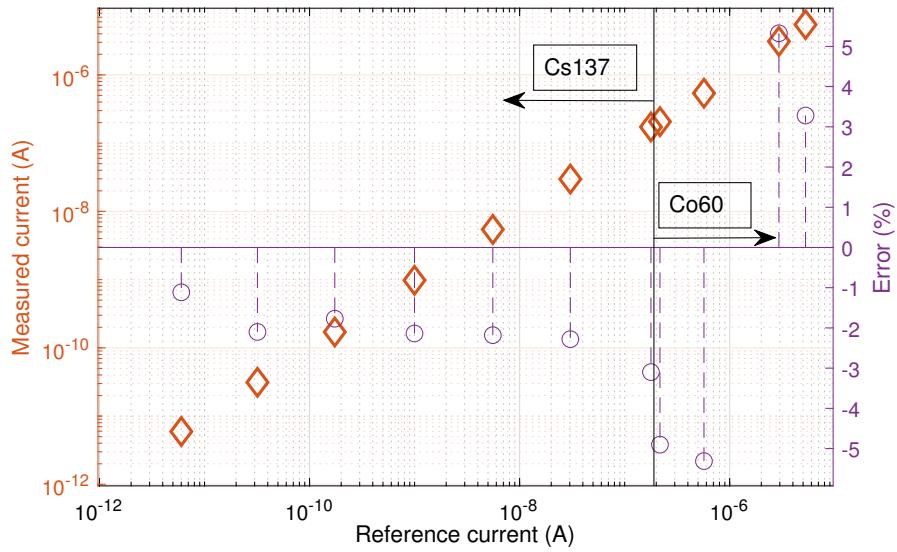

| 7.8  | Current measurement with IG5 chamber . . . . .                                                         | 97  |

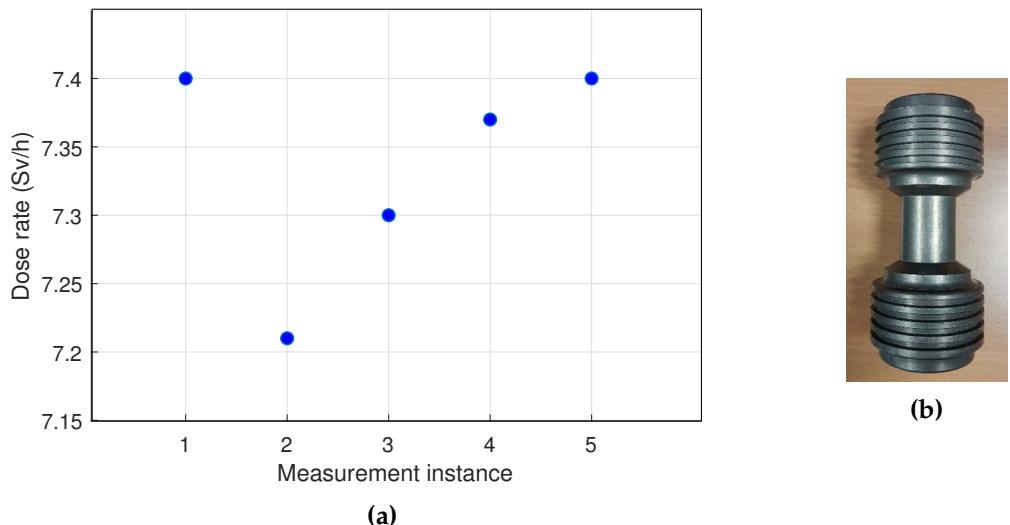

| 7.9  | (a) Dose rates measured at the same exposure settings, (b) container of the radiation source . . . . . | 97  |

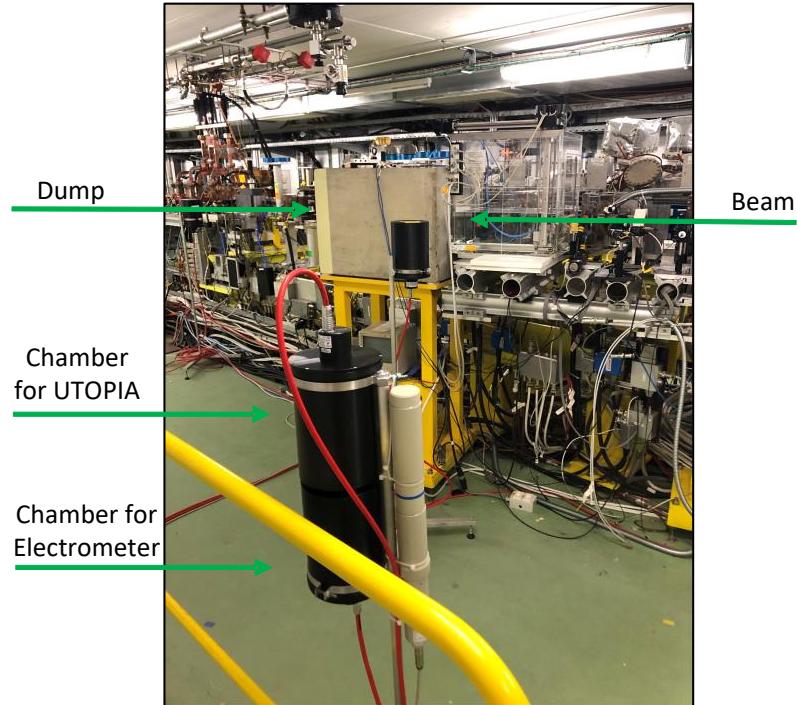

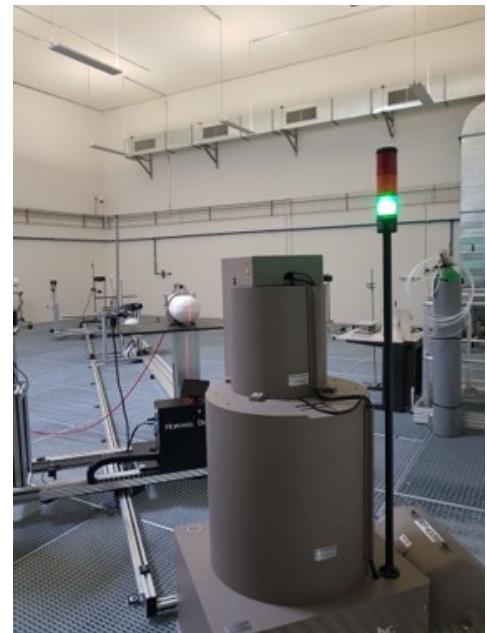

| 7.10 | PSAIF pit . . . . .                                                                                    | 98  |

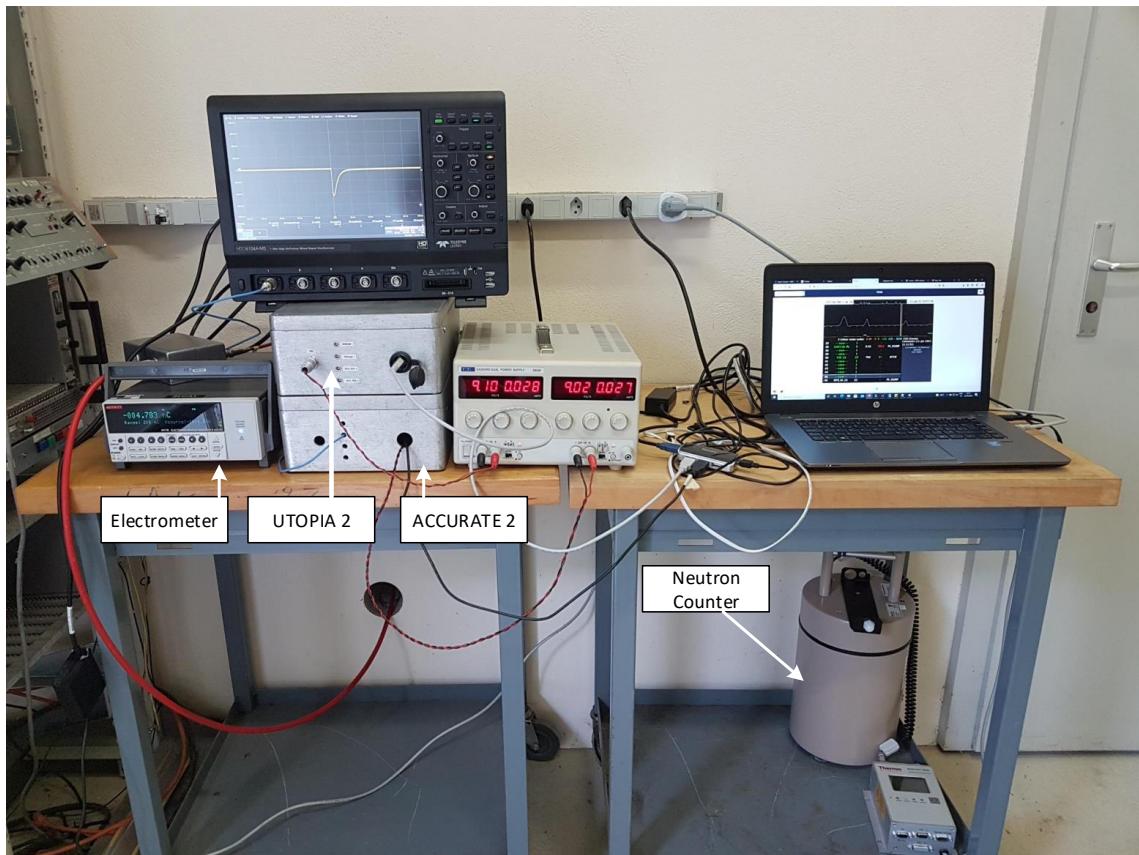

| 7.11 | Measurement set-up at PSAIF . . . . .                                                                  | 99  |

| 7.12 | Ionization chamber output recorded by oscilloscope with $1\text{ M}\Omega$ input resistance . . . . .  | 100 |

| 7.13 | Charges measured by ACCURATE 2 and UTOPIA 2 with pulsed radiation . . . . .                            | 101 |

| 7.14 | OTA output of ACCURATE 2A with an input pulse of 55 nC . . . . .                                       | 101 |

| 7.15 | Charges measured by ACCURATE 2A with 50 $\text{M}\Omega$ input resistor . . . . .                      | 102 |

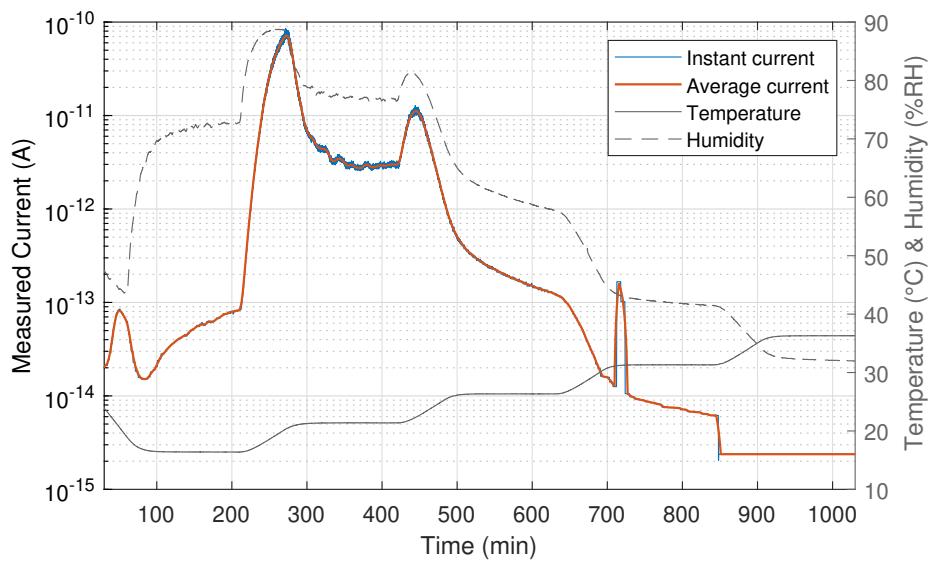

| 7.16 | Leakage current variation with humidity . . . . .                                                      | 104 |

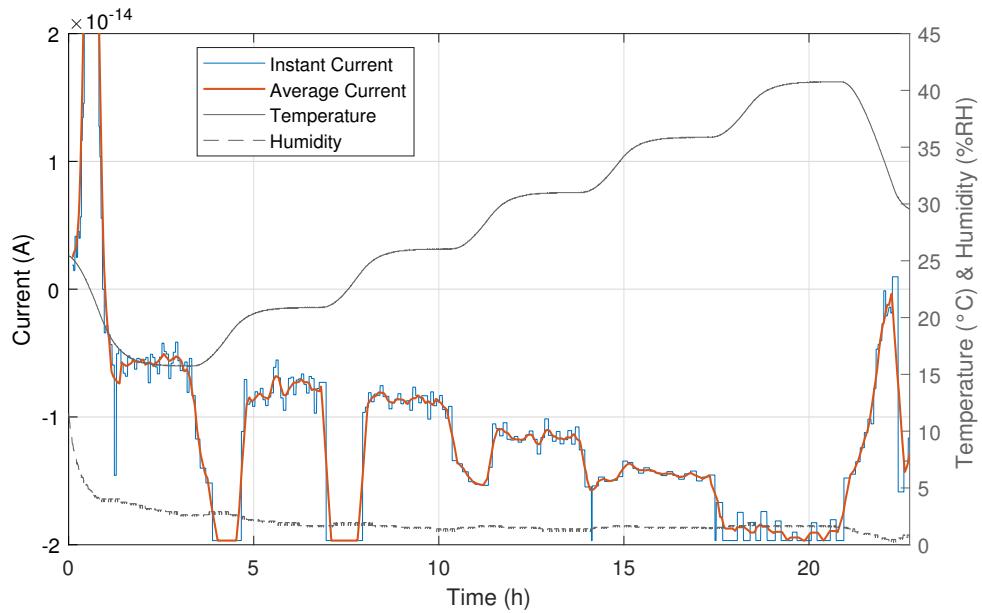

| 7.17 | Leakage current variation of ACCURATE 2A with temperature . . . . .                                    | 105 |

| 7.18 | Output variation of Keithley 6430 current source with temperature . . . . .                            | 105 |

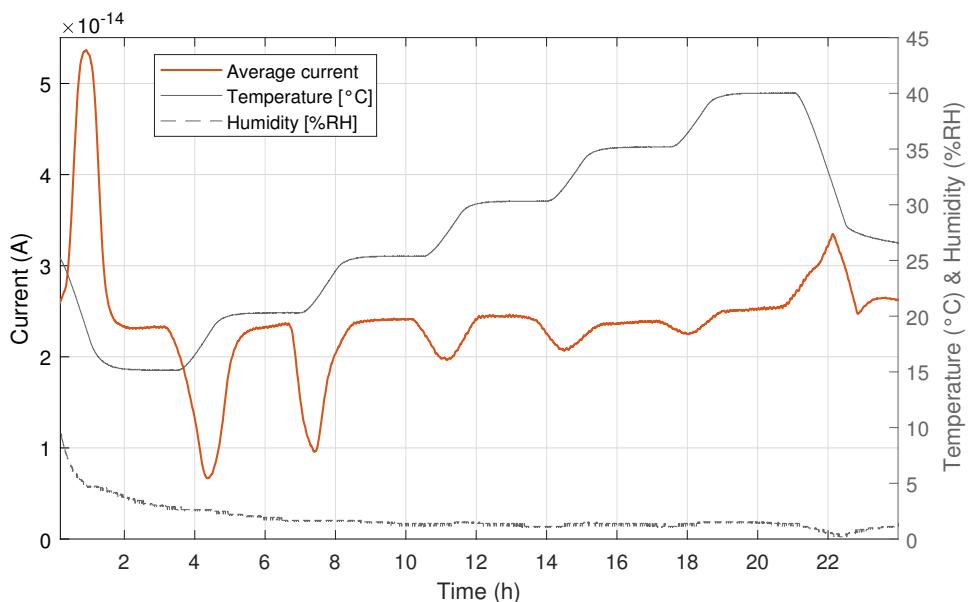

| 7.19 | Temperature cycling output of ACCURATE 2M . . . . .                                                    | 106 |

| 7.20 | Simulated leakage currents of ESD diodes . . . . .                                                     | 107 |

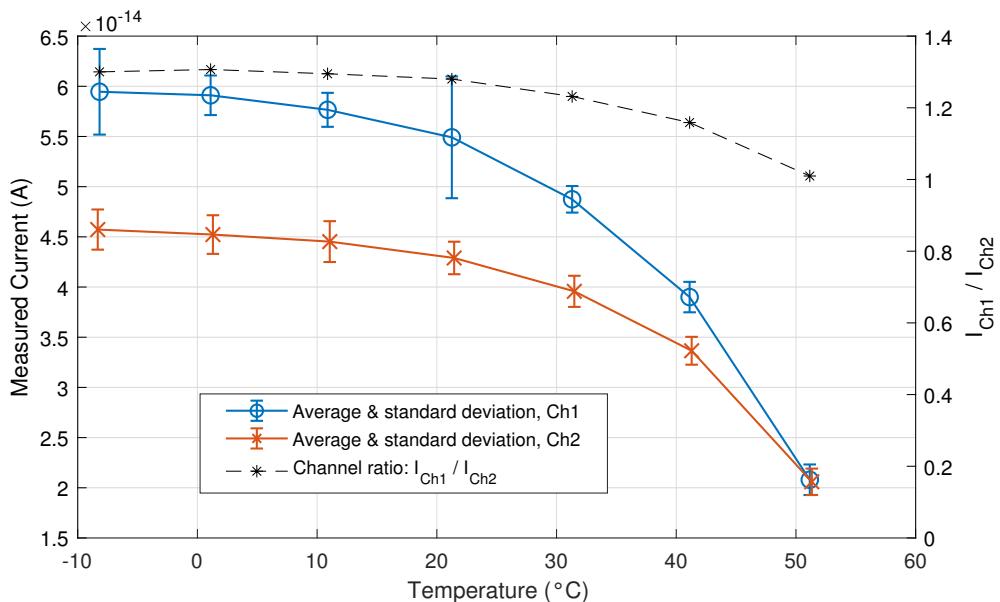

| 7.21 | Variation of net leakage measured by two channels of ACCURATE 2M with temperature . . . . .            | 107 |

| 7.22 | Variation of current measurement accuracy of DS method with temperature . . . . .                      | 108 |

| 7.23 | Variation in charge quantum with temperature . . . . .                                                 | 109 |

*This page is intentionally left blank.*

# List of Tables

|     |                                                                                              |     |

|-----|----------------------------------------------------------------------------------------------|-----|

| 2.1 | Current measurement time of UTOPIA 2 . . . . .                                               | 14  |

| 2.2 | Charges measured by UTOPIA and reference electrometer at CLEAR . . . . .                     | 20  |

| 2.3 | Charges measured by the reference electrometer for different pulse settings at IRA . . . . . | 22  |

| 3.1 | State of the art low current measurement systems . . . . .                                   | 25  |

| 3.2 | CERN Radiation monitoring systems . . . . .                                                  | 31  |

| 4.1 | Transistor dimensions . . . . .                                                              | 36  |

| 5.1 | Leakage current of different ACCURATE 1 ASICs . . . . .                                      | 64  |

| 6.1 | Functional verification results summary . . . . .                                            | 80  |

| 7.1 | Sources used to generate different dose rates . . . . .                                      | 94  |

| 8.1 | Comparison with the state of the art . . . . .                                               | 112 |

| 8.2 | Comparison of different ASICs designed in this research with UTOPIA 2 . . . . .              | 114 |

*This page is intentionally left blank.*

# List of Abbreviations

---

| Abbreviation | Meaning                                       |

|--------------|-----------------------------------------------|

| ACCURATE     | Atto to miCro CoURAnt meTER                   |

| AD           | Antiproton factory                            |

| ADC          | Analog to digital convertor                   |

| ALICE        | A Large Ion Collider Experiment               |

| AMS          | Austriamicrosystems                           |

| ARCON        | ARea CONtroller                               |

| ASIC         | Application specific integrated circuit       |

| ATLAS        | A Toroidal LHC Apparatus                      |

| BIC          | Beam interlock controller                     |

| BIS          | Beam interlock system                         |

| BJT          | Bipolar junction transistor                   |

| BLM          | Beam loss monitor                             |

| CB           | Charge balancing                              |

| CC           | Current conveyor                              |

| CERN         | European Organization for Nuclear Research    |

| CFC          | Current to frequency conversion               |

| CHUV         | Lausanne university hospital                  |

| CLEAR        | CERN Linear Electron Accelerator for Research |

| CMOS         | Complementary metal-oxide-semiconductor       |

| CMS          | Compact Muon Solenoid                         |

| COTS         | Commercial off-the-shelf                      |

| CPU          | Central processing unit                       |

| CROME        | CERN Radiation Monitoring Electronics         |

| DAC          | Digital to analog convertor                   |

| DC           | Direct current                                |

| DRC          | Desing rule check                             |

| DSM          | Direct slope measurement                      |

| ESD          | Electrostatic discharge                       |

| EMC          | Electromagnetic compatibility                 |

| EMI          | Electromagnetic interference                  |

|        |                                                                |

|--------|----------------------------------------------------------------|

| FC     | Folded Cascode                                                 |

| FCC    | Future Circular Collider                                       |

| FDSOI  | Fully depleted silicon-on-insulator                            |

| FET    | Field-effect transistor                                        |

| FIFO   | First-in first-out                                             |

| FPGA   | Field-programmable gate array                                  |

| GPIB   | General Purpose Interface Bus                                  |

| I2C    | Inter integrated circuit                                       |

| IC     | Integrated circuit                                             |

| IHP    | Leibniz Institute for High Performance Microelectronics        |

| IO     | Input-output                                                   |

| IRA    | Institute of radio physics                                     |

| JFET   | Junction field-effect transistor                               |

| LEIR   | Low energy ion ring                                            |

| LHC    | Large hadron collider                                          |

| LHCb   | LHC-beauty                                                     |

| LINAC  | Linear accelerator                                             |

| LSB    | Least significant bit                                          |

| LVS    | Layout vs schematic                                            |

| MATLAB | Matrix laboratory                                              |

| MEMS   | Microelectromechanical systems                                 |

| MIM    | Metal-insulator-metal                                          |

| MPS    | Machine protection system                                      |

| NMOS   | N-type metal-oxide-semiconductor FET                           |

| OPAMP  | Operational amplifier                                          |

| OTA    | Operational transconductance amplifier                         |

| PCB    | Printed circuit board                                          |

| PLC    | Programmable logic controller                                  |

| PMOS   | P-type metal-oxide-semiconductor FET                           |

| PPS    | Personal protection system                                     |

| PS     | Proton synchrotron                                             |

| PSAIF  | Proton Synchrotron - Antiproton collector Irradiation Facility |

| PSB    | Proton synchrotron booster                                     |

| RAMSES | RAdiation Monitoring System for the Environment and Safety     |

| REMUS  | Radiation and Environment Monitoring Unified Supervision       |

| RC     | Reset counting                                                 |

| RF     | Radio frequency                                                |

| RP     | Radiation protection                                           |

| RTL    | Register-transfer level                                        |

| SAR    | Successive-approximation-register                              |

| SCADA  | Supervisory Control and Data Acquisition                       |

---

|        |                                                                   |

|--------|-------------------------------------------------------------------|

| SIL    | Safety integrity level                                            |

| SoC    | System-on-a-chip                                                  |

| SPI    | Serial peripheral interface                                       |

| SPS    | Super proton synchrotron                                          |

| SRAM   | Static random-access memory                                       |

| TIA    | Transimpedance amplifier                                          |

| TSMC   | Taiwan Semiconductor Manufacturing Company                        |

| UART   | Universal Asynchronous Receiver Transmitter                       |

| USB    | Universal serial bus                                              |

| UTOPIA | Ultra-low picoammeter                                             |

| VHDL   | Very High Speed Integrated Circuits Hardware Description Language |

---

*This page is intentionally left blank.*

# Publications

1. **S. K. Mohanan**, H. Boukabache, D. Perrin, and U. R. Pfeiffer, "Comparative Analysis of Ultra-Low Current Measurement Topologies with Implementation in 130 nm Technology", IEEE Access, vol. 9, pp. 63 855–63 864, 2021

2. **S. K. Mohanan**, H. Boukabache, D. Perrin, and U. Pfeiffer, "Femtoampere sensitive current measurement ASIC in 22 nm technology", in 2019 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), IEEE, Oct. 2019, pp. 1–3

3. **S. K. Mohanan**, H. Boukabache, D. Perrin, and U. Pfeiffer, "Towards the next generation of CERN radiation monitoring front end ASICs", in Topical Workshop on Electronics for Particle Physics (TWEPP), 2021

4. **S. K. Mohanan**, H. Boukabache, V. Cruchet, D. Perrin, S. roesler, and U. Pfeiffer, "An Ultra Low Current Measurement Mixed-Signal ASIC for Radiation Monitoring Using Ionisation Chambers", IEEE Sensors Journal, vol. 22, pp. 2142–2150, 2021

5. K. Ceesay-Seitz, **S. K. Mohanan**, H. Boukabache, and D. Perrin, "Formal Property Verification of the Digital Section of an Ultra-Low Current Digitizer ASIC", in The Design and Verification Conference and Exhibition Europe (DVCon Europe), 2021

*This page is intentionally left blank.*

# Contributions of Others

1. The thesis presents the design of a current measurement ASIC to be used as the front-end of ionisation chambers. The ASIC was designed in line with the ASIC development program taken up by the Radiation Protection group at CERN. The first two ASICs in this program - UTOPIA 1 and UTOPIA 2 was designed by a previous colleague Evgenia Voulgari. The ASICs presented in this thesis - ACCURATE, forms the next generation of the UTOPIA ASICs. The various circuit blocks designed for UTOPIA in AMS 350 nm technology were redesigned in GF 22FDX and TSMC 130 nm technology and used in this thesis.

2. The IO pads with ESD cells and custom standard cells used in ACCURATE 1 and ACCURATE 2 were designed by Stephano Michelis and Giacomo Ripamonti of EP-ESE-ME section of CERN.

3. The verification of the digital logic of ACCURATE 2M was done by my colleague - Katharina Ceesay-Seitz.

4. The ASICs were bonded by Florentina Manolescu of the bond lab at CERN.

5. The test board for ACCURATE 2M and its MATLAB test scripts were designed by Vassili Cruchet.

The research not included in the above list has been conducted by myself.

*This page is intentionally left blank.*

# Abstract

CERN houses one of the most sophisticated pieces of machinery ever built by humans to carry out cutting-edge research in the field of particle physics. The experiments carried out at CERN can generate different kinds of ionizing radiation as a side effect. Using dedicated radiation monitors, the radiation protection (RP) group ensures that the generated radiation is contained within the allowable limit and thrusts to minimize the exposure which ensures the safety of the personnel and surrounding habitants. Ionization chambers are the most used sensors for continuous radiation monitoring for RP. This thesis explains the design, development, and characterization of an application specific integrated circuit (ASIC) that aims to replace the existing discrete component-based front end of ionization chambers used at CERN.

The presented research started with the in-depth characterization of the first-generation ASICs designed in the RP group - UTOPIA. Measurements with pulsed radiation fields exposed the limitation of UTOPIA for efficient collection of charge pulses necessitating the need for a redesign with architectural modification. Apart from capacitating the analog front end for improved charge measurement, integrating the digital data processing section into the ASIC to create a mixed-signal, single-chip solution was also envisaged. UTOPIA ASICs were designed in AMS 350 nm technology which exhibited femtoampere leakages which were vital in achieving the ultra-low current measurement capability. The main hurdle faced in designing the second generation of the ASIC – ACCURATE, was identifying a suitable long-term replacement for the proven 350 nm node. A detailed literature review ascertained that no design is reported in technology nodes of 130 nm or finer that achieves femtoampere sensitivity and attains the dynamic range from femtoampere to microampere. Test structures made in 22FDX of GLOBALFOUNDRIES and TSMC 130 nm technology established techniques and architectures to attain the required dynamic range and sensitivity.

Design of ACCURATE 2, which is the main focus of the research, is presented in detail. An architecture combining two current measurement methods, charge balancing current to frequency conversion and direct slope measurement method, was designed. It also incorporates all the digital logic along with the analog section to process the generated data and provide data storage and eventual transfer to an external system through a serial interface. The ASIC is successful in achieving a remarkable sensitivity of 200 aA and demonstrated a wide dynamic range from around -6 fA to -20  $\mu$ A. The use of thick gate transistors in the leakage critical analog path, optimal feedback capacitance and three stepped progressive charge balancing with 500 fC,

1 pC, and 4 pC charge paths helped in achieving this performance. Prudent floorplanning utilizing Deep N-Well structures to minimize noise coupling along with guard rings and path length matching helped in attaining the sensitivity even with the mixed signal version. The ASIC occupies an area of  $3.52\text{ mm}^2$  and reports a total power consumption of 17.4 mW.

Characterization with the continuous current generated by different kinds of ionization chambers when exposed to radiation sources demonstrated the dose rate measurement of the ASIC from  $5\text{ }\mu\text{Sv/h}$  to  $7.4\text{ Sv/h}$ . Dynamic characterization with pulsed radiation established the improvement of around 16% more charge collection by ACCURATE 2 compared with UTOPIA 2 for a charge pulse of 100 nC. The reason for the limitation in charge collection for charges above tens of nanocoulombs was identified to be caused by saturation of OTA with the high influx of charges beyond that could be compensated by the charge balancing block. The improvement achievable by increasing the time constant of the charge collection path was demonstrated.

The designed ASIC thus improves the sensitivity, dynamic range and charge measurement efficiency of the existing systems and offers a first of its kind mixed-signal single chip solution for ionization chamber frontends. The ASIC can also be employed in applications such as biosensor readouts and device characterization which demands similar performance levels.

ACCURATE 2 must be upgraded from a prototype to a certified reliable unit for the next generation of radiation monitors for CERN. The path culminating in ACCURATE 3 with different improvements and modifications is also laid out.

# Zusammenfassung

Das CERN, die Europäische Organisation für Kernforschung, beherbergt eine der ausgeklügeltesten Anlagen, die je von Menschen gebaut wurden und betreibt Spitzforschung auf dem Gebiet der Teilchenphysik. Die am CERN durchgeföhrten Experimente können verschiedene Arten von ionisierender Strahlung als Nebenprodukt erzeugen. Mit Hilfe von speziellen Strahlungsmonitoren stellt die Strahlenschutzgruppe (Radiation Protection Group, RP) sicher, dass die erzeugte Strahlung innerhalb der zulässigen Grenzen bleibt. Sie bemüht sich, die Exposition von Personen zu minimieren, um die Sicherheit des Personals und der Bewohner der umliegenden Gebiete, zu gewährleisten. Ionisationskammern sind die von der RP am häufigsten verwendeten Sensoren zur Messung der Strahlungsniveaus. Diese Arbeit beschreibt den Entwurf, die Entwicklung und die Charakterisierung eines ASICs, das das bestehende, auf diskreten Komponenten basierende Frontend der Ionisationskammern am CERN ersetzen soll.

Die Forschungsarbeiten begannen mit der eingehenden Charakterisierung der ASICs der ersten Generation - UTOPIA -, die in der Strahlenschutzgruppe entwickelt wurden. Messungen mit gepulsten Strahlungsfeldern zeigten die Grenzen von UTOPIA bei der effizienten Erfassung von Ladungspulsen auf, so dass ein Neuentwurf mit architektonischen Änderungen erforderlich wurde. Das analoge Frontend sollte mit einer verbesserten Fähigkeit zur Ladungsmessung ausgestattet werden. Darüberhinaus wurde auch die Integration der digitalen Datenverarbeitung in das ASIC ins Auge gefasst, um eine Mixed-Signal Lösung in einem einzigen integrierten Chip zu ermöglichen. Die UTOPIA-ASICs wurden in der AMS-350 nm-Technologie entwickelt. Diese wies Leckströme im Femtoampere-Bereich auf, was für die Erzielung der Messfähigkeit von extrem geringen Strömen entscheidend war. Die größte Hürde bei der Entwicklung der zweiten Generation des ASICs - ACCURATE - war die Suche nach einem geeigneten langfristigen Ersatz für die bewährte 350 nm-Technologie. Eine ausführliche Literaturrecherche ergab, dass für Technologieknoten von 130 nm oder feiner kein Design bekannt ist, das eine Femtoampere-Sensitivität und einen Dynamikbereich von Femtoampere bis Mikroampere erreicht. Basierend auf Teststrukturen, die in der 22FDX Technologie von GLOBALFOUNDRIES und in der 130 nm Technologie von TSMC entworfen wurden, konnten Techniken und Architekturen entwickelt werden, die den geforderten Dynamikbereich und die geforderte Sensitivität erreichen.

Das Schaltungsdesign von ACCURATE 2, das den Schwerpunkt der Forschung bildet, wird im Detail vorgestellt. Es wurde eine Architektur entwickelt, die zwei Strommessmethoden kombiniert, nämlich die Strom-Frequenz-Wandlung mit Ladungsausgleich und die Methode der direkten Steigungsmessung. Zusätzlich zu der analogen Schaltung umfasst das Design auch die gesamte digitale Logik, welche die erzeugten Daten verarbeitet, und eine Möglichkeit zur Datenspeicherung und eventuellen Übertragung an ein externes System über eine serielle Schnittstelle bietet. Das ASIC erreicht eine bemerkenswerte Sensitivität von 200 aA und demonstriert einen weiten Dynamikbereich von etwa -6 fA bis -20 µA. Der Verbesserungen wurden durch die Nutzung von Transistoren mit dickem Gate-Oxid, die optimale Auslegung der Rückkopplungskapazität, sowie eine Architektur mit dreistufigem Ladungsausgleich mit unterschiedlichen Ladungsmengen (500 fC, 1 pC, und 4 pC) erreicht. Durch ein detailliertes Floorplanning, die Integration von Deep N-Well Strukturen zur Minimierung der Rauschkopplung ins Substrat und den Abgleich von Pfadlängen konnte die Sensitivität selbst in der Mixed-Signal-Version beibehalten werden. Das ASIC nimmt eine Fläche von 3,52 mm<sup>2</sup> ein und hat eine Gesamtleistungsaufnahme von 17,4 mW.

Bei der Charakterisierung mit Gleichstrom, der von verschiedenen Arten von Ionisationskammern durch Bestrahlung mit Strahlungsquellen erzeugt wurde, zeigte die Dosisleistungsmessung des ASICs 5 µSv/h bis 7,4 Sv/h. Bei der dynamischen Charakterisierung mit gepulster Strahlung wurde festgestellt, dass ACCURATE 2 im Vergleich zu UTOPIA bei einem Ladungspuls von 100 nC etwa 16% mehr Ladungen sammelt. Es wurde identifiziert, dass Ladungsmengen über zehn Nanocoulomb zu einer Sättigung des OTAs führen, welche durch den Ladungsausgleich nicht kompensiert werden können. Durch eine Erhöhung der Zeitkonstante in dem Pfad zur Ladungakkumulation konnte diesbezüglich eine Verbesserung nachgewiesen werden. Der entworfene ASIC verbessert somit die Empfindlichkeit, den Dynamikbereich und die Effizienz der Ladungsmessung im Vergleich zu den bestehenden Systemen und ist die erste vollständig integrierte Mixed-Signal-Lösung für die Ionisationskammersensorik. Der ASIC kann auch in Anwendungen mit ähnlichen Leistungsanforderungen eingesetzt werden, wie zum Beispiel in der Biosensorik und in der hochpräzisen Messtechnik. Um den entworfenen ASIC für die nächste Generation von CERN's Strahlungsmessgeräten verwenden zu können, muss es von einem Prototypen in ein zuverlässiges und zertifiziertes Bauteil überführt werden. Abschließend wird der Weg zur Entwicklung von ACCURATE 3 mit verschiedenen Verbesserungen und Modifikationen dargelegt.

# Chapter 1

## Introduction

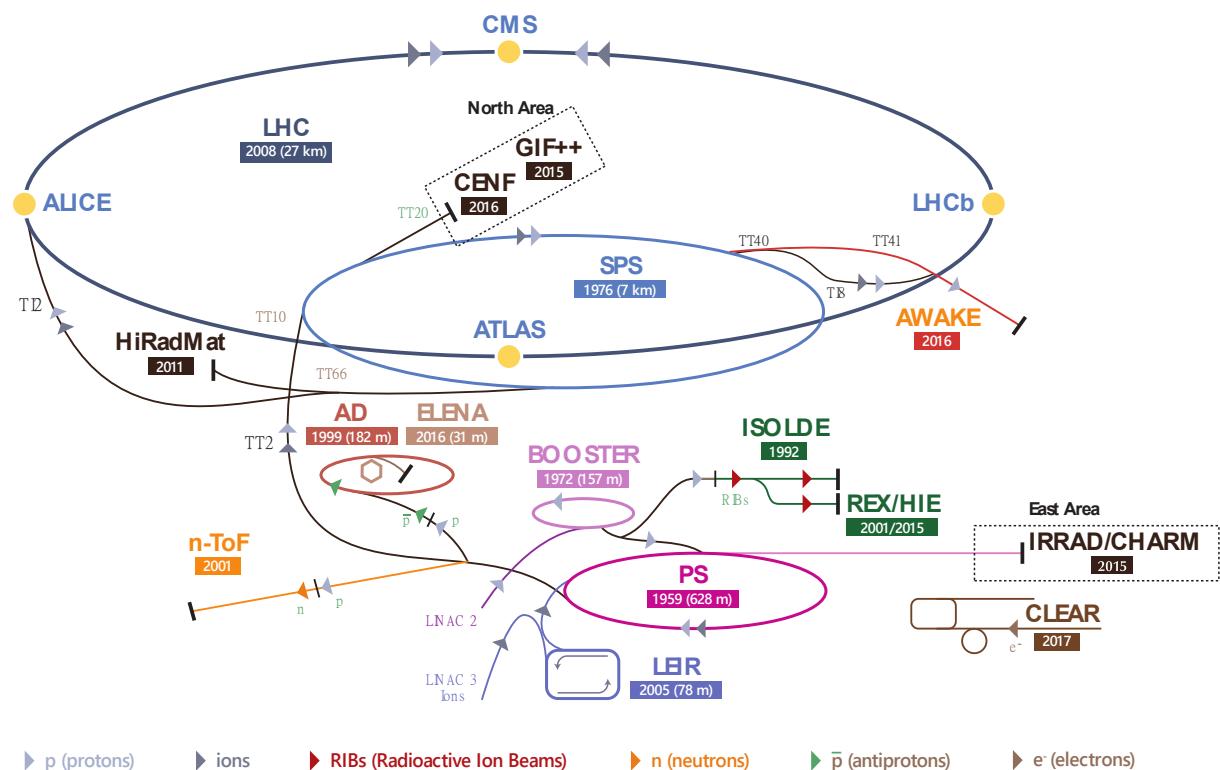

CERN, the European Organization for Nuclear Research, is a unique research facility designed to understand the basic constituents of matter by colliding particles traveling at a high speed. A series of accelerators have been built at CERN to push the particles to almost the speed of light. An overview of the accelerator complex at CERN is shown in Fig. 1.1.

Figure 1.1: CERN's Accelerator Complex [1]

CERN accelerates protons and ions in its accelerators. The path of the protons starts from a bottle of hydrogen from which the protons are extracted and fed to LINAC 2, the first accelerator. Here, the protons are accelerated to an energy of 50 MeV. The beam then traverses the proton synchrotron booster (PSB) where the beam energy level increases to 1.4 GeV, the

proton synchrotron (PS) pushing the energy further to 25 GeV, and the super proton synchrotron (SPS) with a target energy of 450 GeV, before reaching the large hadron collider (LHC). The final energy level achieved in the LHC is 6.5 TeV. The ions make their journey from vaporized lead through LINAC 3 and the low energy ion ring (LEIR) before entering the PS. There are two beam pipes for the LHC, where the beams travel in opposite directions. The beams are made to collide in four detectors – ALICE, ATLAS, CMS, and LHCb. The total energy at these collision points equals 13 TeV.

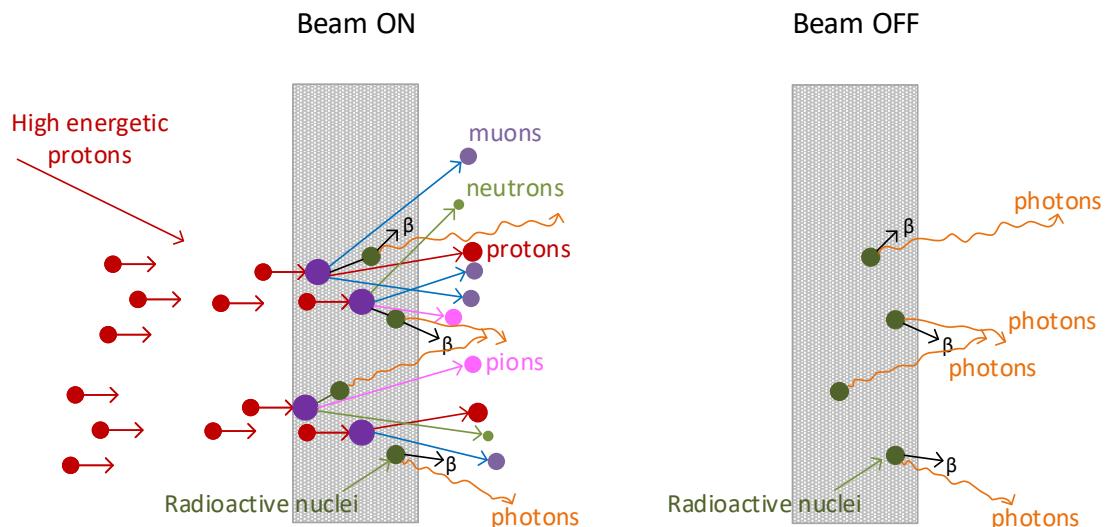

## 1.1 Need for radiation monitoring

When the particle beams collide or when they hit a target, different kinds of ionizing radiation are created, as shown in Fig. 1.2. This created secondary field, called stray radiation, is different from the ionizing radiation observed in the nuclear industry in terms of composition, energies, and temporal dynamics. The energy of the created radiation is reduced to a great extent by the shielding provided around such facilities thus containing the radiation within the beam tunnel. Hence, when the accelerators are on, access to the tunnel or experimental area is forbidden. The ambient dose equivalent in these areas is monitored. Depending on the collision energy, the material around the collision area or the target might be activated, resulting in stray radiation even after the accelerators have been switched off. Using dedicated monitors, the level of radiation in all of the risk areas is continuously monitored and only when the levels are below the safety threshold is access re-enabled.

Figure 1.2: Creation of radiation by particle accelerators [2]

For each facility of the accelerator complex and experiments at CERN, there exists a very complex network of interconnected systems that offer various levels of protection. The three main objectives of these systems are: 1. Protecting people from different threats such as radiation exposure, 2. protecting the environment, and 3. protecting the machine [3]. A highly reliable

personal protection system (PPS) is entrusted with the responsibility of protecting the people operating the experiments and in the vicinity.

For the sophisticated accelerators to which damage should be avoided at all costs due to their inherent complexity and the magnitude of the energy involved, the use of a machine protection system (MPS) is also of paramount importance. Specifically, in the case of LHC, a SIL3 (safety integrity level) classified MPS [4] protects the LHC and the associated systems. The main objectives of the MPS are to protect the machine, protect the beam, and provide evidence [5]. The heart of the MPS is a beam interlock system (BIS). In the event of an incident that necessitates the beam being aborted, the beam interlock system communicates with the beam dump system and the beam will be safely directed to a dump. For the LHC, as many as around 10000 electronic channels could request a beam dump [6]. The architecture of the beam interlock system for the LHC is described in detail in [5]. The beam interlock system comprises 16 beam interlock controllers (BIC) which act as the backbone for protecting the LHC against any beam loss related damage. Each BIC can receive up to 14 signals from various systems [7]. One of the main protection systems that interfaces with the BIS is comprised of the beam loss monitors (BLMs) [8], [9]. Some 3600 detectors of the BLM system are installed along the cryostats of the LHC machine and at other critical locations where protons are lost from the beam and hit surrounding material. Beam losses are prone to occur at collimation, injection, and extraction points, as well as along the beam pipes. Any event that could lead to high radiation is immediately detected by the BLMs and the BIS interlock is triggered immediately.

While the beam loss monitors act as the first line of defense protecting against unintentional radiation, separate radiation monitors from the radiation protection (RP) group are also installed close to the LHC ring as well as at various crucial points. The main objective of the RP radiation monitors is to provide protection to people rather than the machine itself. Thus, it is part of the PPS and not the MPS. The operational philosophy of the LHC keeps the PPS and MPS systems separate. However, all radiation events are recorded by the RP radiation monitors and appropriate alarms are raised when the threshold is exceeded.

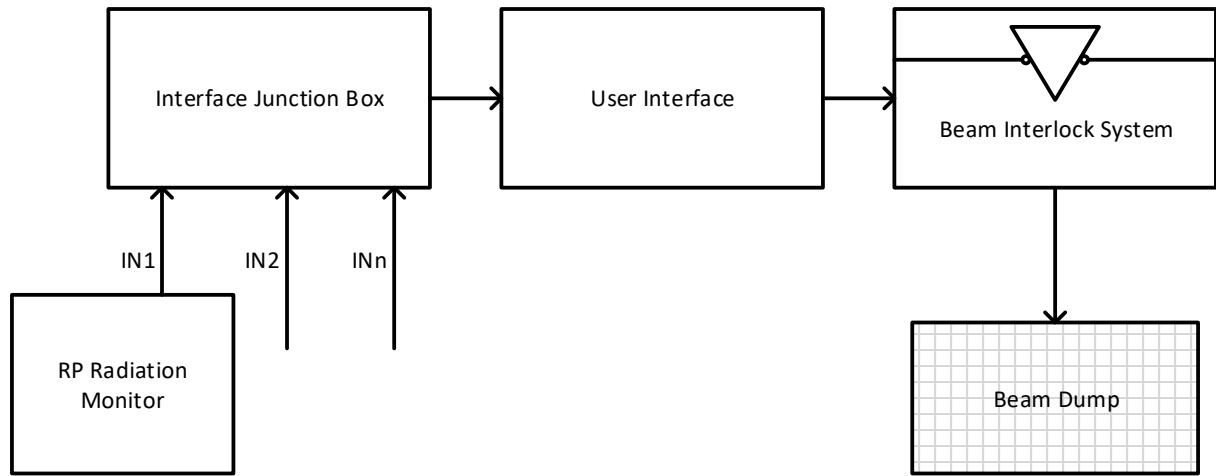

In the case of other complexes, such as the SPS, RP radiation monitors are interfaced also to the beam interlock system. Thus, apart from generating alarms and recording events, they can interrupt the beam through the BIS. A block diagram of the path from the radiation monitor to the SPS BIS [10] is shown in Fig. 1.3.

The interlock signals from different radiation monitors are collected in a junction box which then redirects the interlock to the BIS through a user interface. The junction interface also allows different logic operations on the received interlocks. Apart from the scenario where the measured radiation field is above the set threshold, if any of the systems are not powered or not in the right operational mode, an interlock signal is triggered according to the fail-safe operating principle.

The radiation protection system thus ensures a safe environment for the people working on site and for the general public by protecting against any unjustified exposure to ionizing radiation.

Figure 1.3: SPS BIS interface

The three main functionalities of the system are detection and measurement of radiation levels, generating alarms and interlocks, and finally logging the recorded data for the long term.

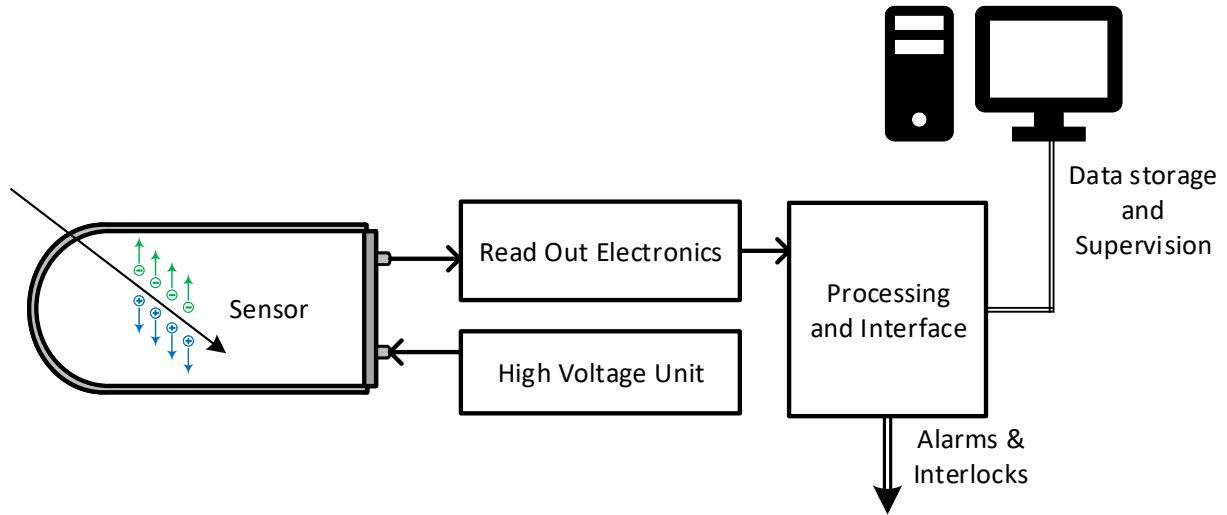

## 1.2 Radiation monitoring system

The typical components of a radiation monitoring system are shown in Fig. 1.4. The ionizing radiation is detected by an ionization chamber which produces a current proportional to the received radiation dose rate.

Figure 1.4: Radiation monitoring system

In order to bias the sensor, a high voltage generation unit generates the required voltage depending on the type of chamber used. The generated current is measured by a front-end electronics system. The readout unit converts the current into a digital format which is further processed by a digital section. The processing unit transfers the measured data to a supervision

system and to storage. Depending on the set thresholds and measured dose rate, alarms or interlocks could be generated by the processing system.

### 1.2.1 Ionization chambers

Ionization chambers are the ubiquitous choice of sensor in radiation monitoring as they are sensitive to different kinds of particles. The chamber is filled with gas and has two electrodes – an anode and a cathode. The gas gets ionized by incident radiation generating electron–ion pairs. The anode which forms the collecting electrode receives the electrons and is connected to the readout electronics. The cathode is applied with the high voltage which determines the region of operation of the chamber.

There are four characteristic regions for a gas filled detector [11] depending on the applied voltage. The first one is a recombination region, where the applied voltage is not high enough and hence the majority of the generated electron–ion pairs are lost by recombination. As the voltage increases beyond a certain threshold, the electric field is high enough to have a significant amount of charge collection by the chamber. This region, called the ionization chamber region, is characterized by a constant charge generation by the chamber for a defined range of applied voltage. As the name suggests, this is the most favorable region of operation for the ionization chamber. The third region of operation is the proportional region, where the generated charges are proportional to the applied voltage. After this region, any increase in the applied voltage places the chamber in the Geiger–Muller region, which is the favored regime for Geiger–Muller counters. For the ionization chambers used at CERN, each chamber is characterized at dedicated facilities and the voltage range to be used in the ionization chamber region for maximum efficiency is determined.

Different kinds of ionization chambers are used at CERN depending on the environment. The three main types are explained further.

#### 1.2.1.1 Centronic IG32

IG32 is argon filled with at a pressure of 3.1 bar. The electrode arrangement follows alternate anode and cathode combs along the center of the chamber, thus allowing for faster collection of charges. The typical dose rates encountered for this chamber are from  $1 \mu\text{Sv}/\text{h}$  to  $1 \text{ Sv}/\text{h}$ . The nominal bias voltage is  $-1500 \text{ V}$ .

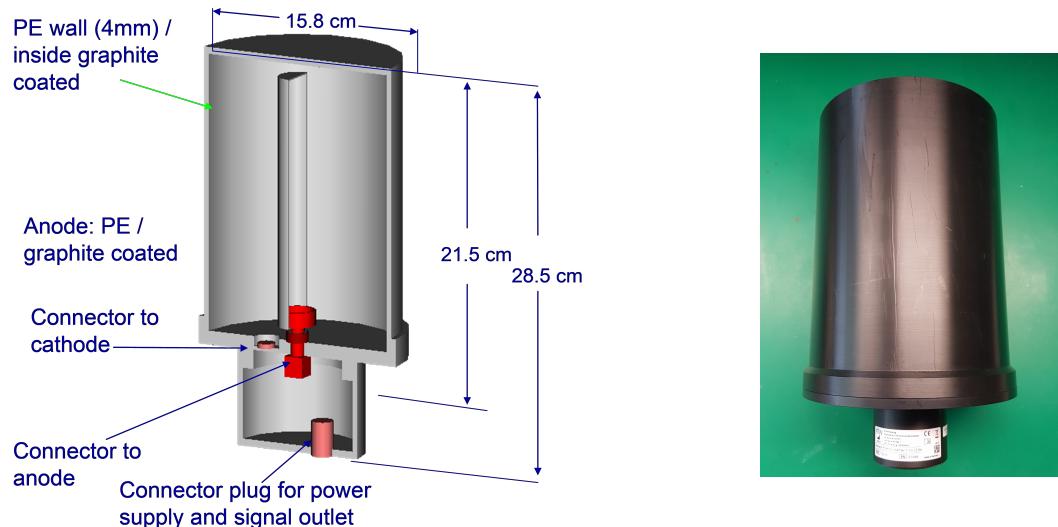

#### 1.2.1.2 PTW PMI T32006

The PMI is a plastic ionization chamber manufactured by PTW-Freiburg specifically for CERN. The construction details of the chamber are shown in Fig. 1.5. It is filled with air at 1 atmospheric pressure. Since these plastic chambers will not be activated by the created radiation, they are installed inside the tunnel for monitoring the radiation dose when the beam is on and to record the residual dose when the accelerators are stopped. The chamber is biased usually with a voltage of  $-400 \text{ V}$ . The PMI chambers are used for measuring doses from  $0.5 \mu\text{Sv}/\text{h}$  to  $10 \text{ Sv}/\text{h}$ .

Figure 1.5: PTW PMI T32006 chamber [12]

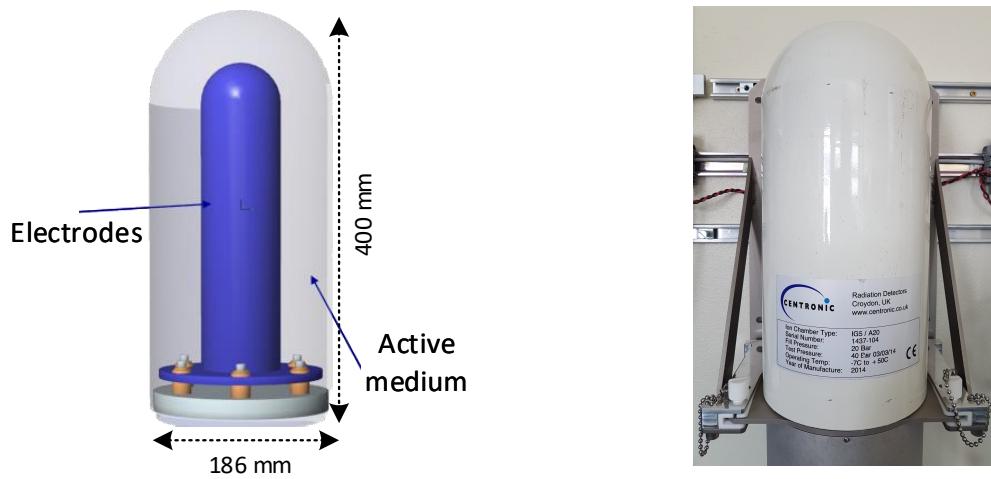

### 1.2.1.3 Centronic IG5

IG chambers are steel shelled detectors manufactured by Centronic limited. The internal structure is shown in Fig. 1.6. Depending on the radiation field, either Hydrogen filled (IG5 H20) or Argon filled (IG5 A20) chamber is used. Both chambers have a volume of 5.2 l pressurized at 20 bars. The electrodes are arranged in the center of the chamber and along the envelope. They are used for dose rate measurements from 50 nSv/h to 0.1 Sv/h and are normally biased with a voltage of  $-1000$  V.

Figure 1.6: IG5 chamber [12]

It is thus clear that the range of current generated by these ionization chambers varies a lot. The current generated by the IG5 H20 chamber, when used for detection of neutrons, can be as low as

a few femtoamperes [13]. The radiation expected by the PMI chambers could be of the order of 10 Sv/h, resulting in a current of around 250 nA. An IG5 A20 chamber, when exposed to a similar radiation dose, can generate currents higher than 10  $\mu$ A. Also, another requirement specifies the capability of measuring charges up to 500 nC within a pulse of milliseconds duration. The pulse width of the output of the ionization chamber depends on the time constant of the interface circuit. The output pulse of a typical chamber, when observed with an oscilloscope with characteristic impedance, exhibited pulse widths of 50 to 100 ms with the majority of the charge concentrated in the initial few milliseconds. Hence, the peak current could also be beyond 10  $\mu$ A. The measurement electronics should be able to cater to this wide dynamic range from femtoamperes to tens of microamperes.

### 1.3 Motivation for the research and thesis organization

The unavailability of commercial products which would demonstrate this dynamic range was the driving force for undertaking in-house development of radiation monitoring systems. The various systems developed in the RP group of CERN are explained in Chapter 2. The legacy systems and the latest generation of installed radiation monitors are all based on discrete components. The management of such a complex system with thousands of components is a herculean task and there is often an unavoidable risk of obsolescence of the components. The solution currently applied is the procurement and storage of components that would be required in the foreseeable future. The solution, although temporarily helping to mitigate the obsolescence problem, nonetheless renders any fault repair or upgrade cumbersome. Hence, an application specific integrated circuit (ASIC) development program was initiated in the group.

This thesis starts with the characterization of an ASIC developed in this program by a previous colleague. From different field tests, the need to upgrade the ASIC was evident. A direct upgrade of the ASIC was unfortunately not feasible due to the unavailability of the technology used for the design of the chip. Hence, a detailed technology evaluation to find a potential new technology node for the future version of the ASIC was necessary. A literature review presented in Chapter 3 reveals that the majority of the research work carried out in the ultra-low current measurement systems discusses the implementation in technology nodes of 350 nm or higher. Also, no reported work demonstrates the required dynamic range and attains a sensitivity of 1 fA. Since the technology nodes available for the design of a future system at CERN were 130 nm or lower, a suitable candidate had to be found in these finer technology nodes and their achievable sensitivity had to be evaluated.

Chapters 4 and 5 explain the research carried out in this direction and establishes the techniques and architectures for designing a low current measurement system in finer technology nodes. GLOBALFOUNDRIES 22FDX and TSMC 130 nm were the chosen technologies for in-depth study. The various leakage currents that affect the ultra-low current measurement system in the analyzed technologies were determined. In this doctoral research, two technology demonstration ASICs were designed and characterized. Chapter 5 delves deeper into the different non-idealities

that affect various low-current measurement topologies. A detailed comparative analysis to find out which method performs better in different current ranges is also carried out.

From the results of the studies of these two prototype versions, a third version of the ASIC was designed. This version has two variants – an analog only one and a mixed-signal one. The analog version attains a wide dynamic range using two different current measurement methods. With the mixed-signal version, the analog and digital sections are combined to make a single chip solution for the front end of the ionization chambers. The different techniques employed to minimize the impact of the noisy digital section on the sensitive analog nodes are explained. The design of this version of the ASIC, which is the central objective of the thesis, is presented in Chapter 6.

The performance of the designed ASICs in different scenarios was extensively studied. The methodologies adopted and the results of the characterization are summarized in Chapter 7. Measurement results with different types of ionization chambers subjected to varying dose rates and fields are presented. The influence of temperature and humidity on the measurements is analyzed and explained in this chapter. The stability of the two current measurement methods with variation in temperature is studied and demonstrated. The performance of the ASIC with a pulsed radiation field was experimentally determined and it was shown to be much superior to its predecessor, which was one of the driving goals for carrying out this research. The conclusion of the thesis and the direction for the future is presented in the final chapter.

The thesis thus addresses the central research question of:

How can a mixed-signal current measurement ASIC with sub-femtoampere sensitivity and 9-decade dynamic range be designed in technology node of 130 nm?

Additionally, the questions addressed are:

- What are the circuit topologies that could be used for ultra-low current measurement and simultaneously achieve a wide dynamic range? What are the effects of different non-linearities on these methodologies?

- How do leakage currents vary across different technology nodes and what is the influence of temperature and humidity on them?

- What should be factored in while designing a mixed-signal system with a hypersensitive analog front end?

- How is radiation detection performed with ionization chambers, and how are the front-end electronics interfaced to these sensors?

- How do ionization chambers respond to pulsed radiation, and what are the factors to be considered while designing the front end for measuring resulting pulsed currents?

## Chapter 2

# Radiation Monitors at CERN

An extensive network of about 800 ionizing radiation monitors covers CERN’s various accelerators and experimental facilities, to protect staff, the general public, and the environment from unwarranted radiation exposure. The responsibility for radiation protection and monitoring is shouldered by different systems. The most widely used radiation monitoring system that has been in operation since 1985 is ARCON (ARea CONtroller) [14]. The next generation, which has been operating since 2004, is RAMSES (RAdiation Monitoring System for the Environment and Safety). Both these systems are now being replaced by the state-of-the-art system – CROME (CERN radiation monitoring electronics). ARCON and CROME were developed in house while RAMSES is a commercial off-the-shelf (COTS) system. All the systems are based on discrete components. The radiation monitors interface to a supervisory control and data acquisition (SCADA) system for data logging. The supervision system is called REMUS (radiation and environment monitoring unified supervision) [15].

This chapter explains the architecture of the readout section of these systems before getting into the details of an ASIC which was developed to have an in-house solution for a radiation monitoring system, avoiding dependency on COTS systems and components. The ASIC, named UTOPIA (ultra low picoammeter) and designed in the AMS 350 nm technology, has a functionality equivalent to the readout section of other systems. There are two versions of this ASIC. The digital section and the details of the static and dynamic characterization of the second version of the ASIC, UTOPIA 2, are presented in detail.

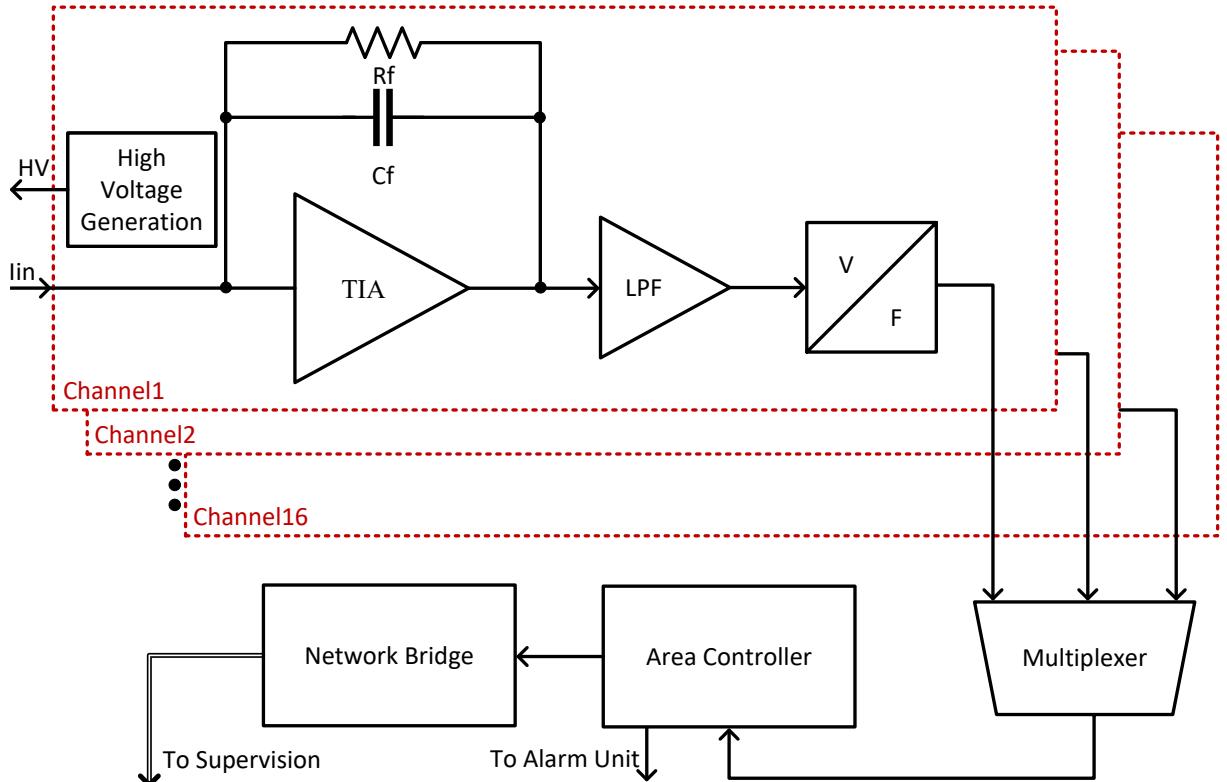

### 2.1 ARCON

ARCON is the first-generation radiation monitoring system deployed at CERN [14]. It is based on a transimpedance amplifier front end converting the current from the ionization chamber into a voltage. The system architecture of ARCON is depicted in Fig. 2.1. The generated voltage is filtered and fed to a voltage-to-frequency converter circuit. The counts, which are generated

proportional to the voltage, are sent out as a digital word. The system also includes a high voltage generation section to provide the appropriate bias voltage to the ionization chamber.

Each ARCON counter card can accommodate up to 16 channels and an ARCON can have up to four of these counter input cards, allowing up to 64 channels to be processed. The programmable logic implementing the multiplexing sends the data to a controller which converts the digital counts into a dose rate. The value thus measured is passed onto a supervision system. The controller can generate alarms depending on the set thresholds. ARCON adopts a centralized architecture where a single controller interfaces to different channels is the point of interface for the supervision and the alarm unit.

Figure 2.1: ARCON system

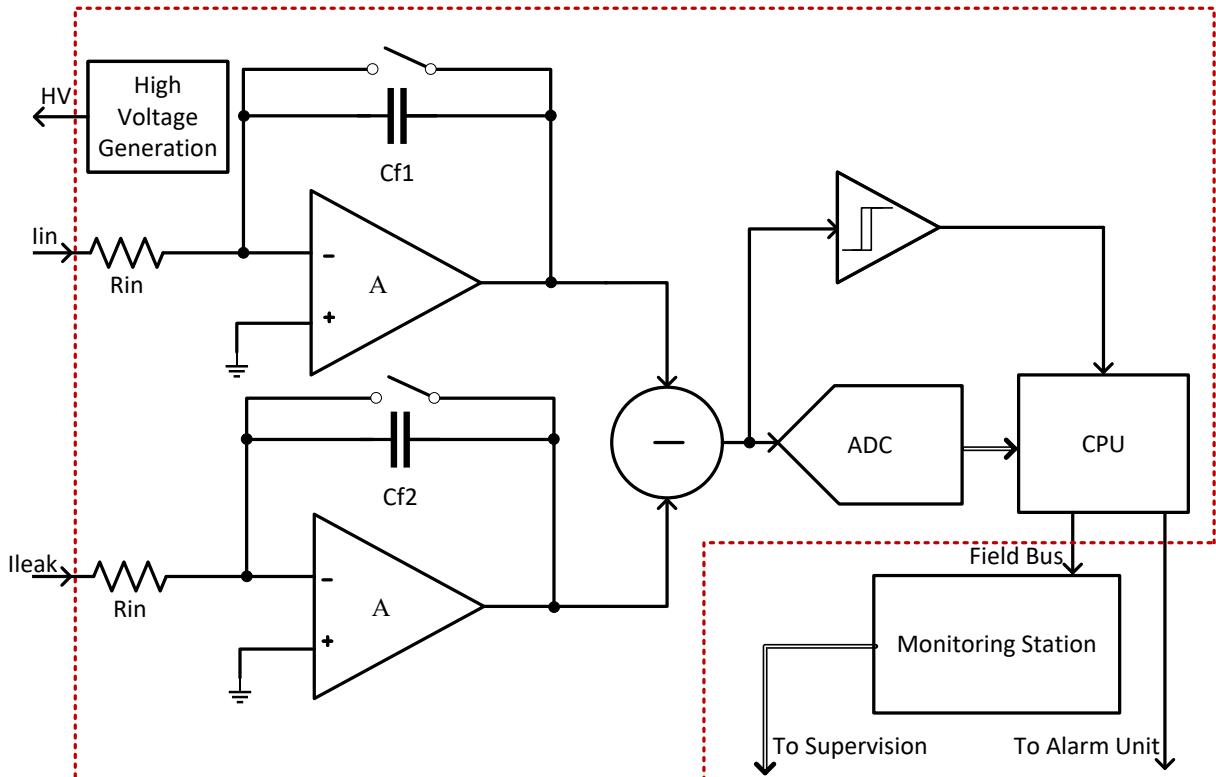

## 2.2 RAMSES

With the expansion of the experimental facilities, ARCON was assisted by RAMSES [15]. The architecture of the system is shown in Fig. 2.2. The system consists of two channels in a single unit, where the second dummy channel is for leakage compensation. In the input path from the ionization chamber, a series resistor is included to increase the time constant of charge collection. Both the channels employ the current to frequency conversion (CFC) principle [16], and the difference between their outputs is digitized by an analog to digital convertor (ADC) and comparators. The digital output is processed by a CPU that interfaces with a monitoring station through a field bus. The interface to supervision is through the programmable logic

controller (PLC) based monitoring station. The CPU interacts directly with the alarm unit. Up to eight such channels can be interfaced to a single monitoring station.

Compared to ARCON, RAMSES is a federated system with each channel having its own CPU and interface to the alarm unit. The channels, however, do not interact directly with the supervision. Each monitoring station thus acts as an independent unit. They are also equipped with temporary data storage provisions before transmitting to the supervision.

Figure 2.2: RAMSES system

### 2.3 CROME

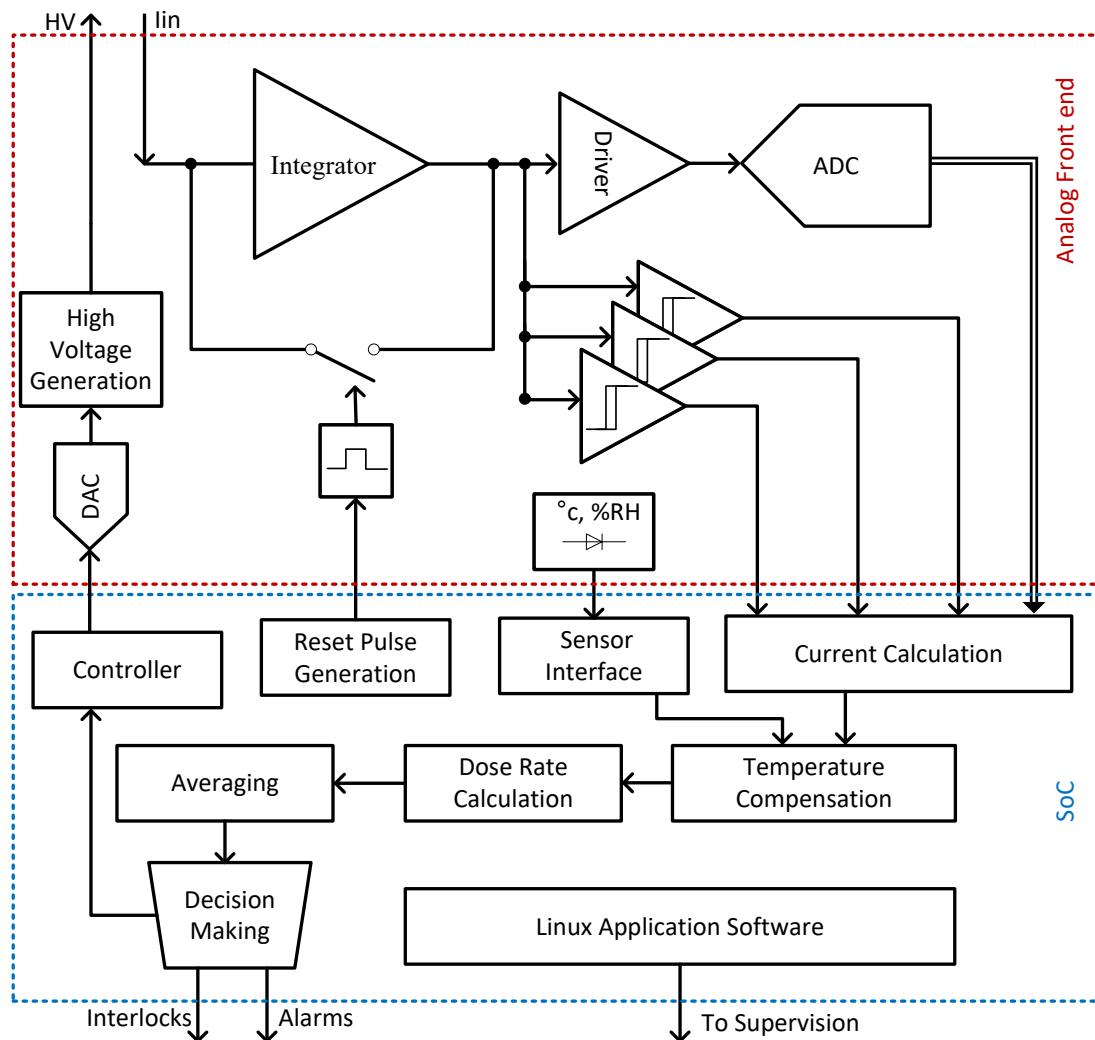

The latest generation of the radiation monitoring system is CROME, which started its era of operation in 2021 by replacing ARCON. The system architecture of CROME is shown in Fig. 2.3.

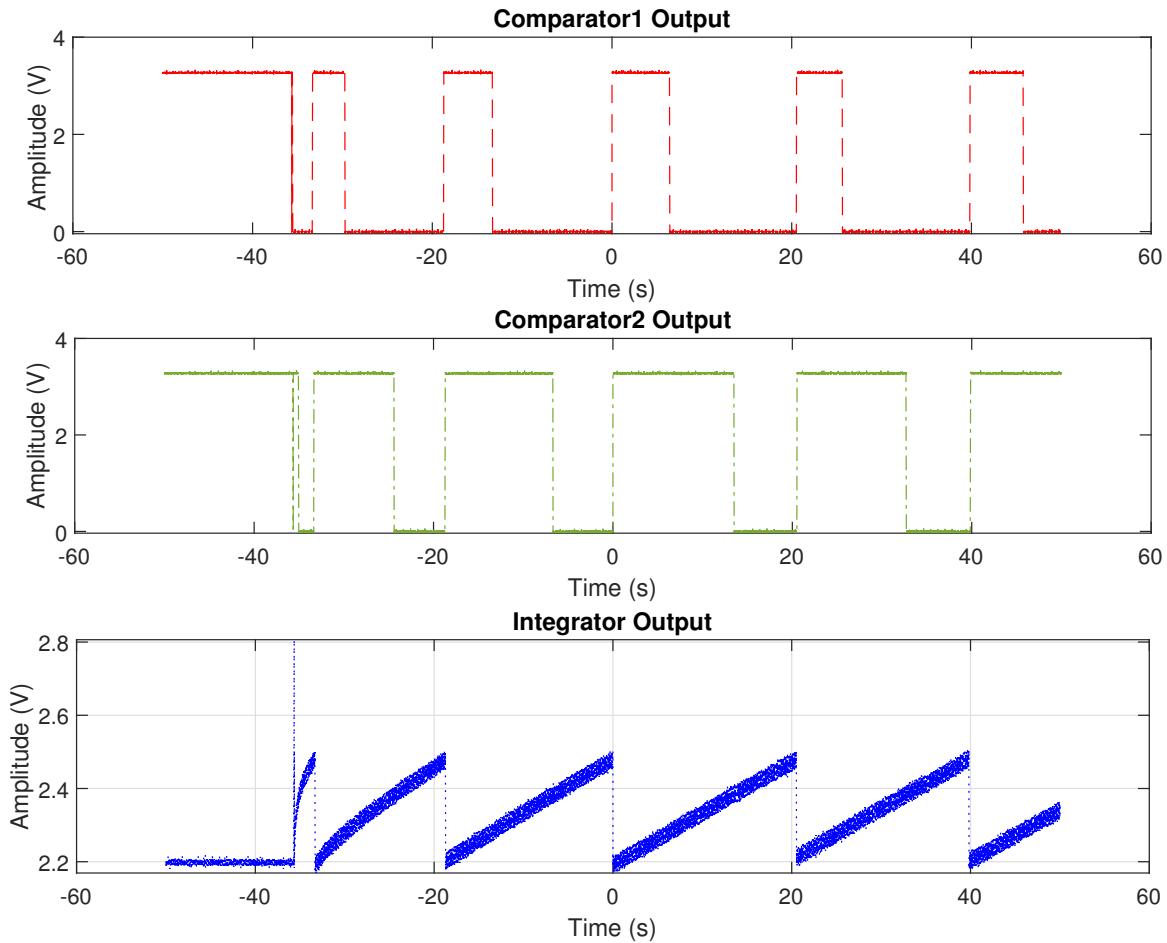

CFC with reset counting is the current measurement principle of CROME. The input current is integrated and fed through a driver to an ADC. The initial voltage at the start of the integration cycle and the final voltage at which the reset is applied are measured by the ADC. The problem of overshoot associated with the reset counting method is tackled by the ADC measurement. Three comparators with progressively higher thresholds generate outputs which are handled by the digital section. A reset pulse of predefined duration is generated depending on the comparator outputs. The current calculations are carried out by a Zynq system-on-a-chip (SoC) module. Temperature compensation based on the temperature data read by an on-board sensor [17], dose rate calculation, and averaging over a defined interval are all handled by the SoC.

The interface to the supervision is also provided through an application software in the SoC. CROME demonstrates a totally modular architecture, with each unit acting as an independent entity with its own processor, a direct interface to the alarm unit, and a network interface to the supervision.

There are around 3000 discrete components in each of the CROME systems. The sheer number of components makes the system extremely complex. The difficulties faced in the maintenance and upgrade of such a system are sourcing all the components, mitigating their obsolescence, and difficult identification in the event of unexpected failures.

Figure 2.3: CROME architecture

An ASIC development program was undertaken by the radiation protection group at CERN to design the future front end of radiation monitors. The goals were to consolidate the functionalities currently demonstrated by the legacy systems into a single chip along with achieving the best possible performance. The development, which started in 2013, resulted in a series of ASIC developments with different goals.

## 2.4 UTOPIA

The first ASIC that was developed in the radiation protection (RP) group is UTOPIA 1. This development aimed to evaluate the various leakage currents associated with a typical ultra-low current measurement front end and to establish ways to minimize them. The second generation of the ASIC, named UTOPIA 2, implemented the findings of its predecessor. The ASIC was able to achieve a remarkable dynamic range of nine decades from  $-1 \text{ fA}$  to  $-5 \mu\text{A}$ . The design of both the UTOPIA ASICs was successfully carried out by a previous colleague, Dr. Evgenia Voulgari, and the results are published in [18]–[21].

UTOPIA 2 is based on an asynchronous CFC architecture based on charge balancing. There is a primary channel for current measurement and a secondary channel for leakage current compensation. The first channel consists of a feedback capacitor of  $1 \text{ pF}$  and two charge injection branches generating charges of  $100 \text{ fC}$  and  $400 \text{ fC}$ . The feedback capacitance of the second channel is  $100 \text{ fF}$  and the charge generation block generates  $100 \text{ fC}$ . The pulses corresponding to charge injection are sent out to an external FPGA.

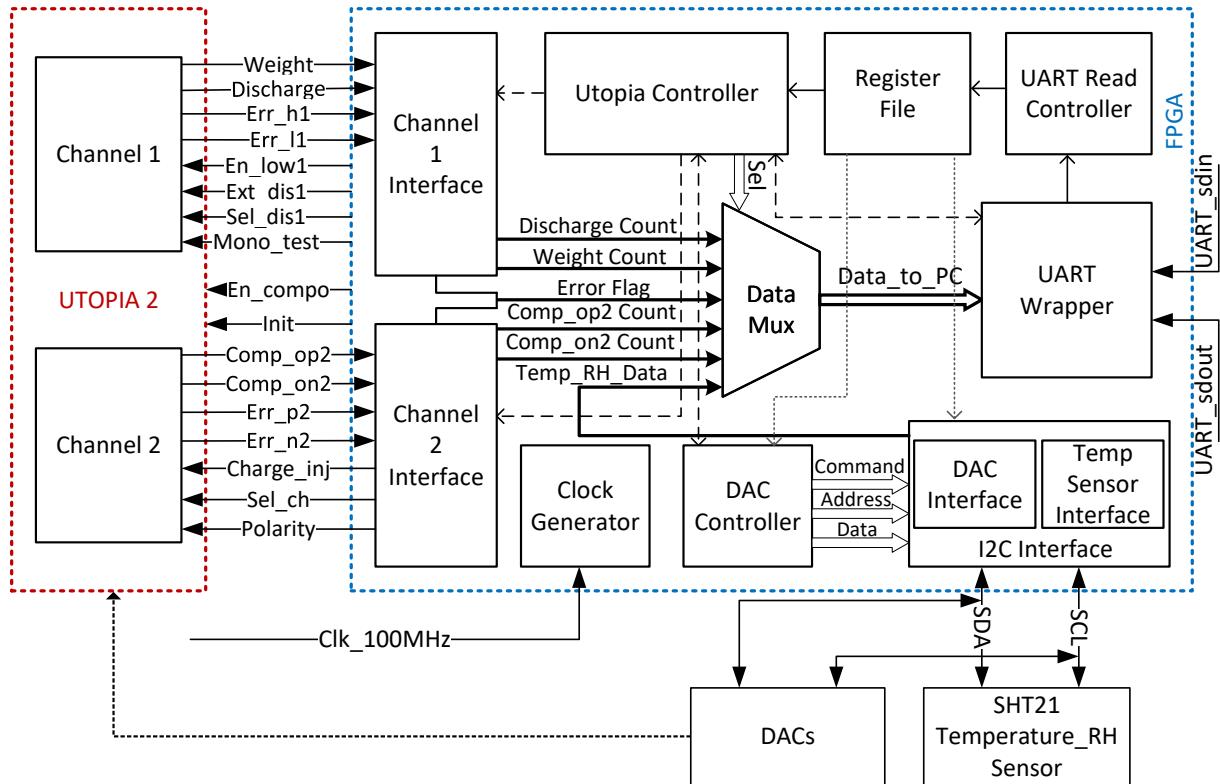

### 2.4.1 Static characterization of UTOPIA 2

This research started with studying UTOPIA system and developing the firmware and software for extensively characterising the ASIC. The firmware was developed in VHDL targeting the Zybo board based on the Z-7010 FPGA from Xilinx. The block diagram of the developed FPGA firmware is shown in Fig. 2.4.

The charge pulse corresponding to  $100 \text{ fC}$ , called Discharge, and that for  $400 \text{ fC}$ , called Weight, are the two main outputs from channel 1 that are processed in the FPGA. The latter also receives a few other error signals and generates some control signals primarily aimed at calibration. For channel 2, depending on the polarity of the leakage current determined by the `comp_op2` and `comp_on2` signals, control signals are generated to select the polarity of the charge to be injected for leakage compensation. The number of charge injection pulses is counted by both of the channel interface modules, resulting in different counts that are multiplexed and sent out through a UART interface. An I2C interface module programs two digital to analog convertors (DACs) on an external board to generate various voltages for the chip. The temperature on board is also read through the same I2C interface. The temperature and humidity read by this module are multiplexed along with the various counts to be sent out serially. The generated data is received by a MATLAB-based software through a serial port.

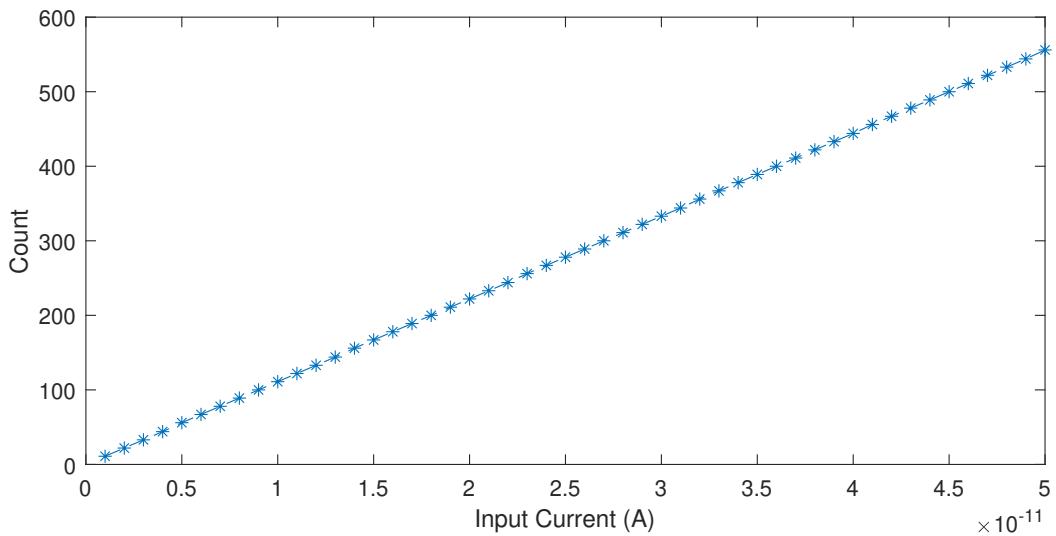

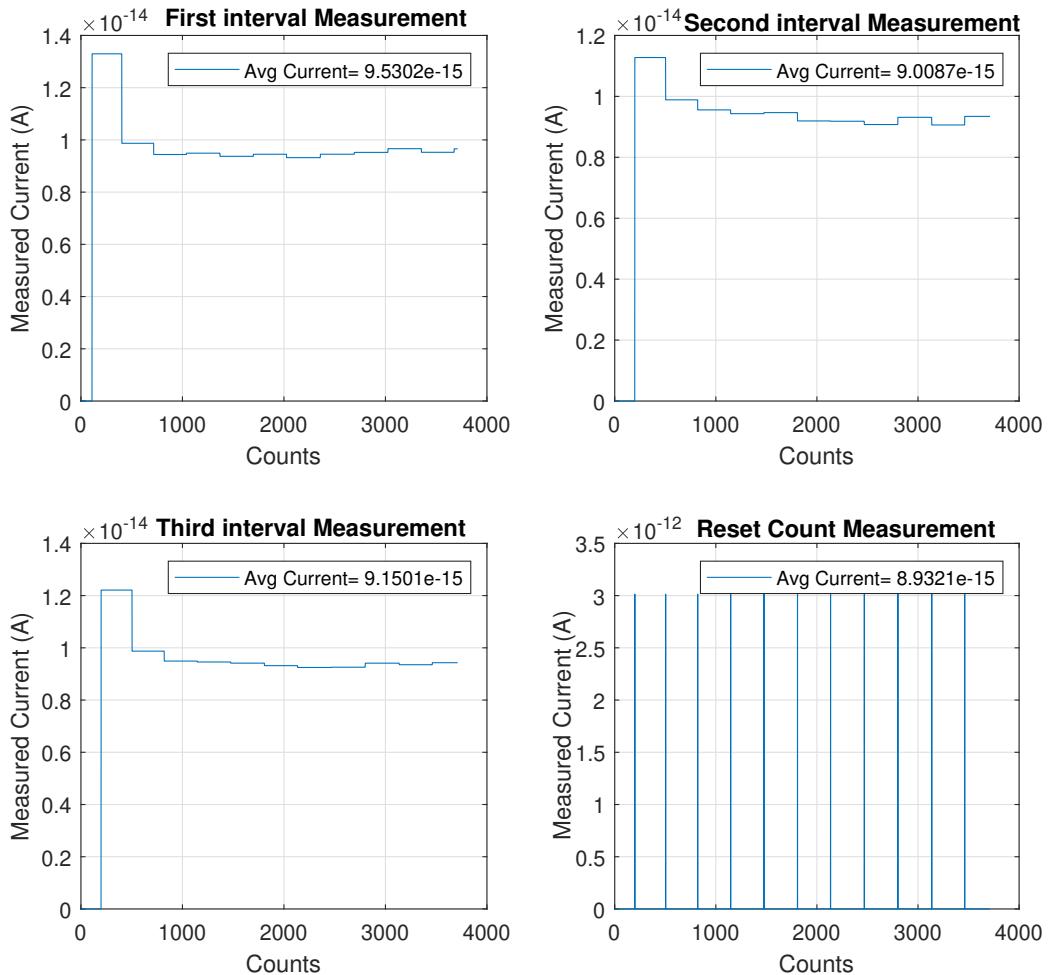

The ASIC was extensively characterized with static currents generated by the current sources Keithley 263 and 6430. Using a MATLAB based characterization software, the various performance metrics of the ASIC were determined. The ASIC showed excellent linearity in the current range from  $-1 \text{ fA}$  to  $-5 \mu\text{A}$ . The input leakage current of the whole measurement system was found to be around  $-50 \text{ fA}$ . This was mainly due to the input electrostatic discharge (ESD) diodes.

Figure 2.4: UTOPIA 2 FPGA architecture

The time window for accurate measurement in different current ranges were determined as follows:

Table 2.1: Current measurement time of UTOPIA 2

| Current range       | Measurement time | Error %    |

|---------------------|------------------|------------|

| -1 fA to -10 fA     | 200 s            | $\pm 20\%$ |

| -10 fA to -50 fA    | 50 s             | $\pm 2\%$  |

| -50 fA to -500 fA   | 10 s             | $\pm 2\%$  |

| -500 fA to -5 pA    | 1 s              | $\pm 2\%$  |

| -5 pA to -5 $\mu$ A | 0.1 s            | $\pm 2\%$  |

As the input current increases, less time is required to collect a sufficient number of counts to obtain the required accuracy.

#### 2.4.2 Dynamic laboratory characterization of UTOPIA 2

The bandwidth requirements of radiation monitors are often very relaxed as the ionization chambers themselves are meant to measure the total ionization dose. The charges generated by an ionization event are accumulated and transferred to the front-end electronics. Especially in the case of environmental monitoring, the generated current is practically a DC for the majority of the measurement time under normal conditions. Hence, the results obtained in the static characterization hold good. However, in applications such as hadron therapy environments or

near particle accelerators, the encountered radiation field is pulsed and the width of the pulse varies with application. The output current pulse from the ionization chamber is a stretched version of the input radiation pulse, with the width depending on the time constant of the discharge path. Most of the charges are delivered in the first few milliseconds followed by an exponentially decreasing discharge. Hence, dynamic characterization of the front-end ASIC was imperative to assess its response to pulsed currents and different input current profiles.

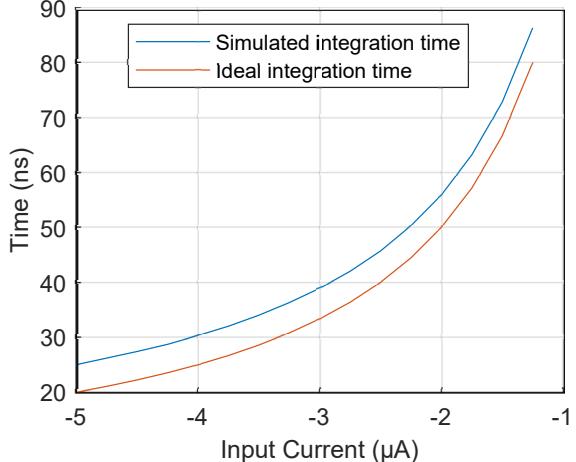

Spectre simulations helped in determining the performance of UTOPIA 2 with pulsed inputs. The chip was simulated to correctly measure pulsed currents. The minimum pulse width of the input current for accurate current measurement was interesting to determine.

The time required by the comparator to generate a pulse is

$$t = \frac{\Delta V \cdot C_f}{I_{\text{det}}}. \quad (2.1)$$

For  $-5 \mu\text{A}$  input current, the time to integrate a voltage of  $0.1 \text{ V}$  on a  $1 \text{ pF}$  capacitor is  $20 \text{ ns}$ . However, this value is arrived at by assuming that the voltage at the input terminal of the OTA ( $V_{\text{in}}$ ) will not move significantly compared to the common-mode voltage  $V_{\text{cm}}$ . There is a dynamic offset due to the limited gain of the OTA. Hence,  $V_{\text{in}}$  does not remain constant and adds to the integration time.

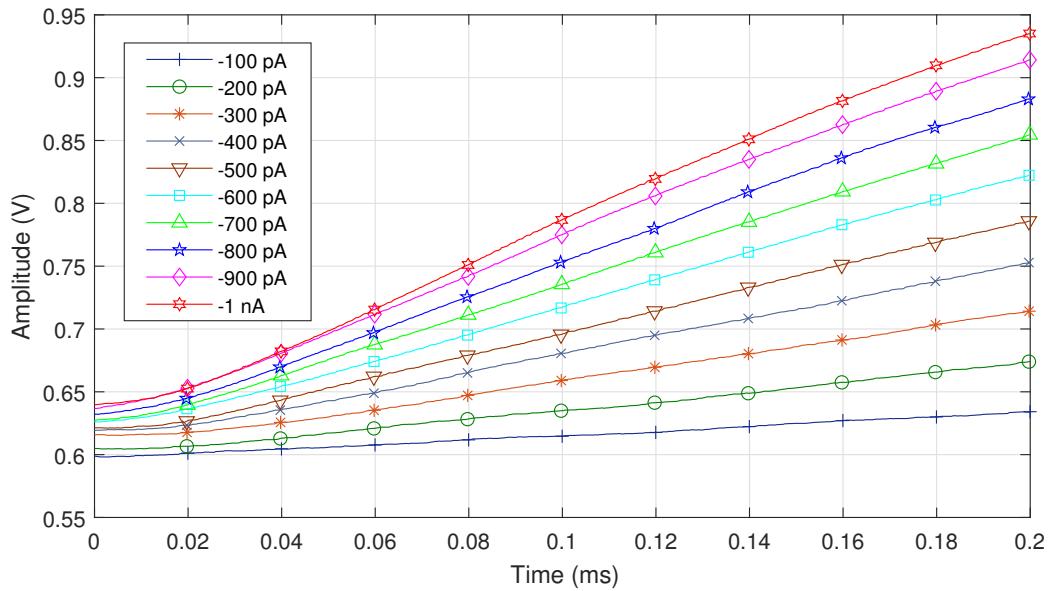

The difference is more pronounced at the higher end of the dynamic range. The results of cadence simulation are shown in Fig. 2.5. The integration time is calculated as the time difference between the falling edge of the input current pulse and the rising edge of the comparator. Thus, for an input current of  $-5 \mu\text{A}$ , the integration time is  $25 \text{ ns}$  instead of  $20 \text{ ns}$ . The difference between the ideal and simulated integration times decreases with the magnitude of the input current. The above simulation time is obtained by feeding the pulse directly to the ASIC.

Adding an input resistance of  $200 \Omega$  and capacitance of  $10 \text{ pF}$ , to emulate an application environment with the chamber and the cable, already delays the response and for the case of  $-5 \mu\text{A}$ , the integration time rises to  $33 \text{ ns}$ .

**Figure 2.5:** Simulation output - Integration time for different input currents

#### 2.4.2.1 Laboratory characterization with pulsed currents

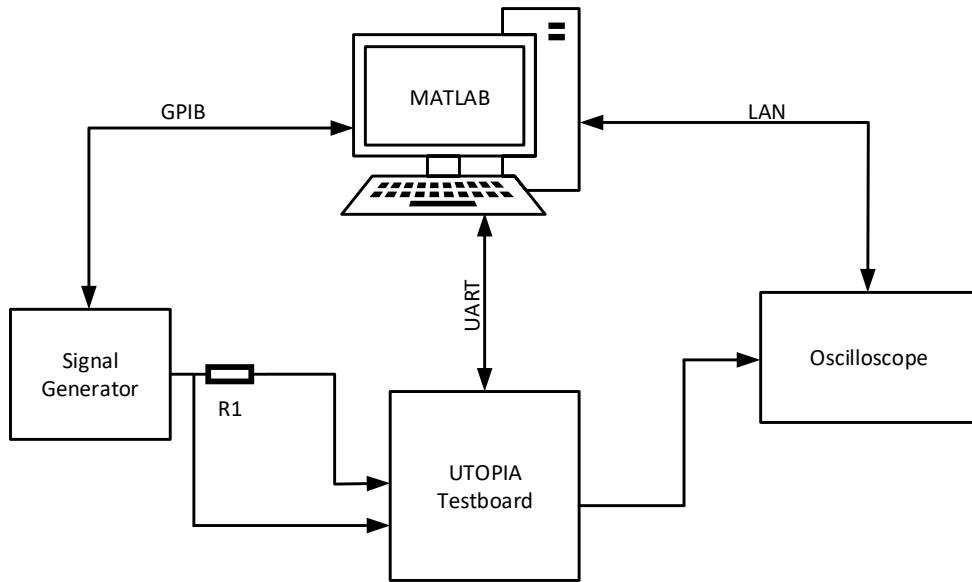

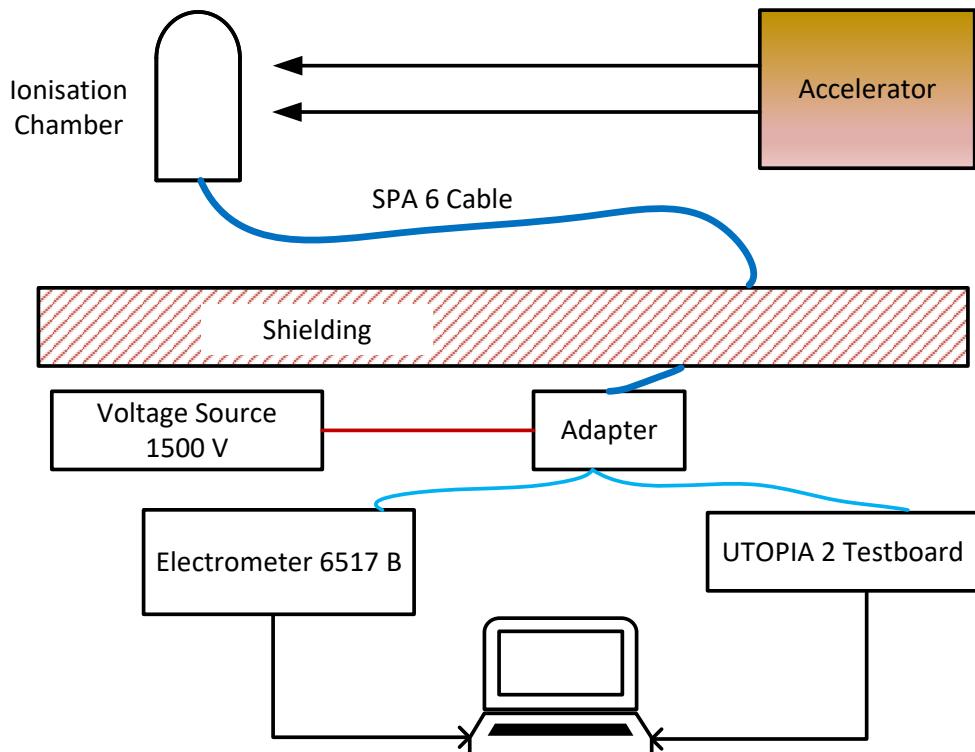

To determine the performance of UTOPIA 2 in a pulsed radiation field, the first measurements were done by injecting pulsed currents. The measurement set-up used is shown in Fig. 2.6.

Figure 2.6: Laboratory set-up for pulsed current measurement with UTOPIA 2

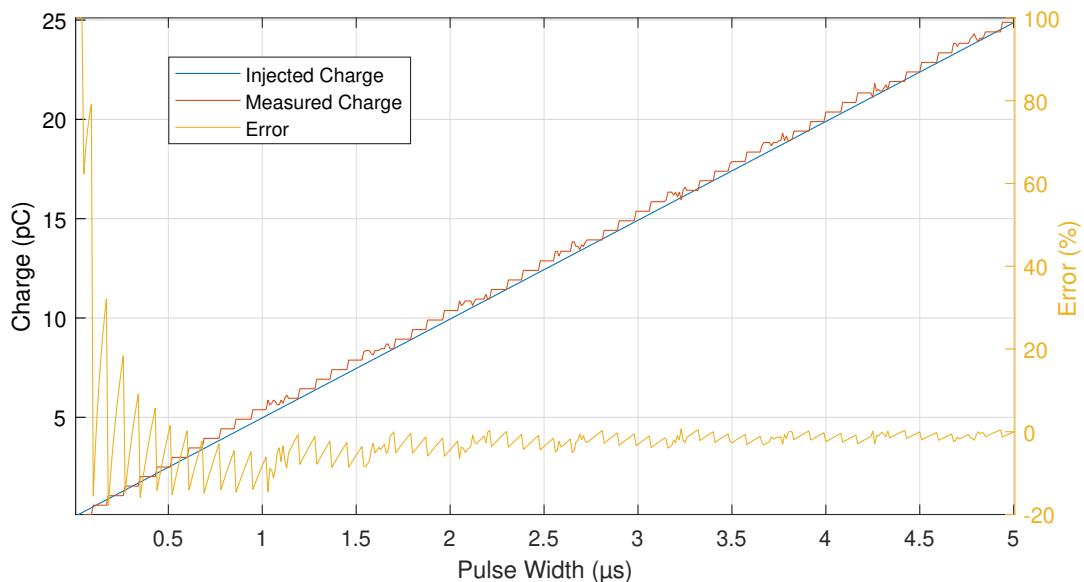

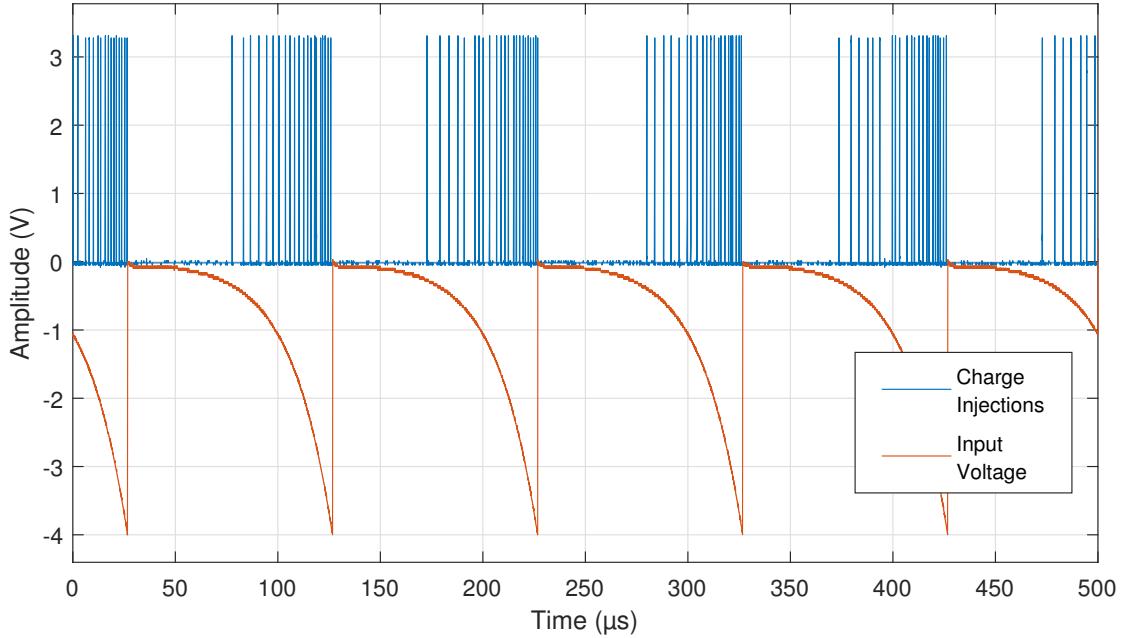

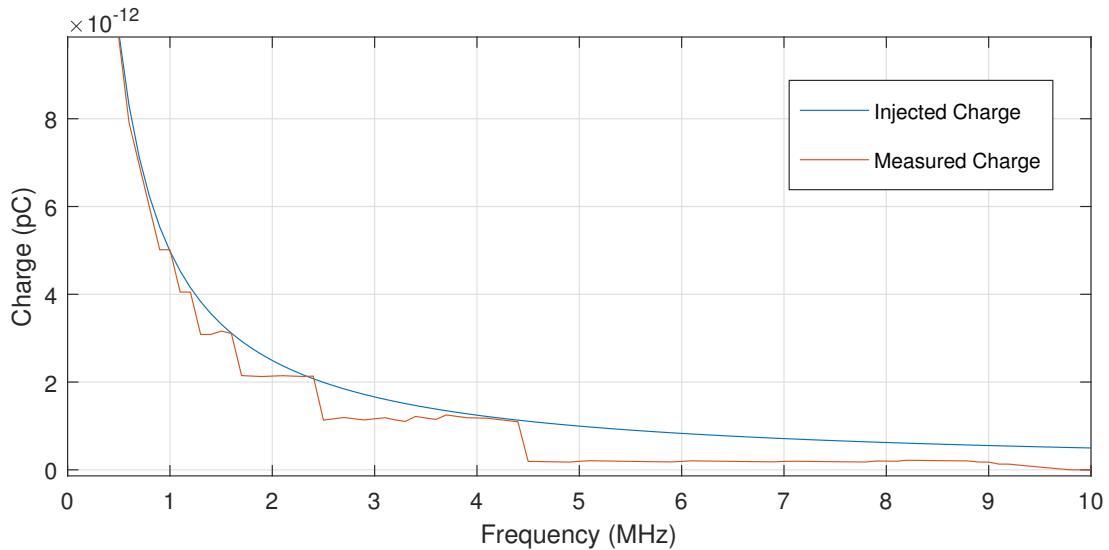

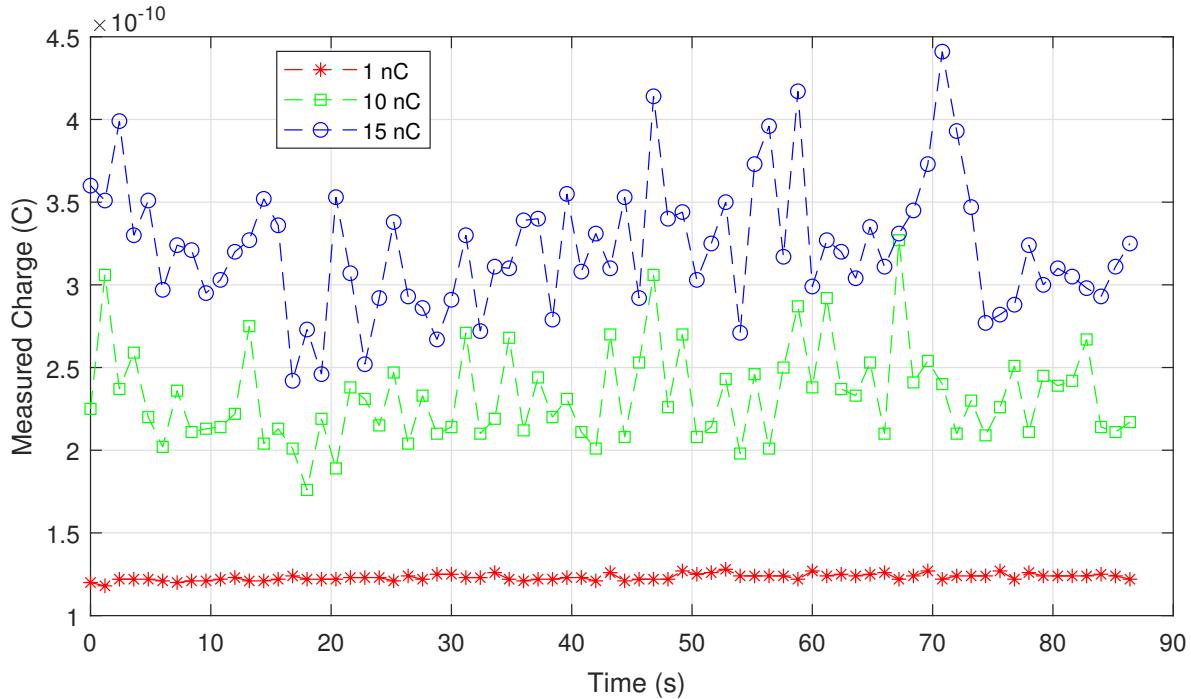

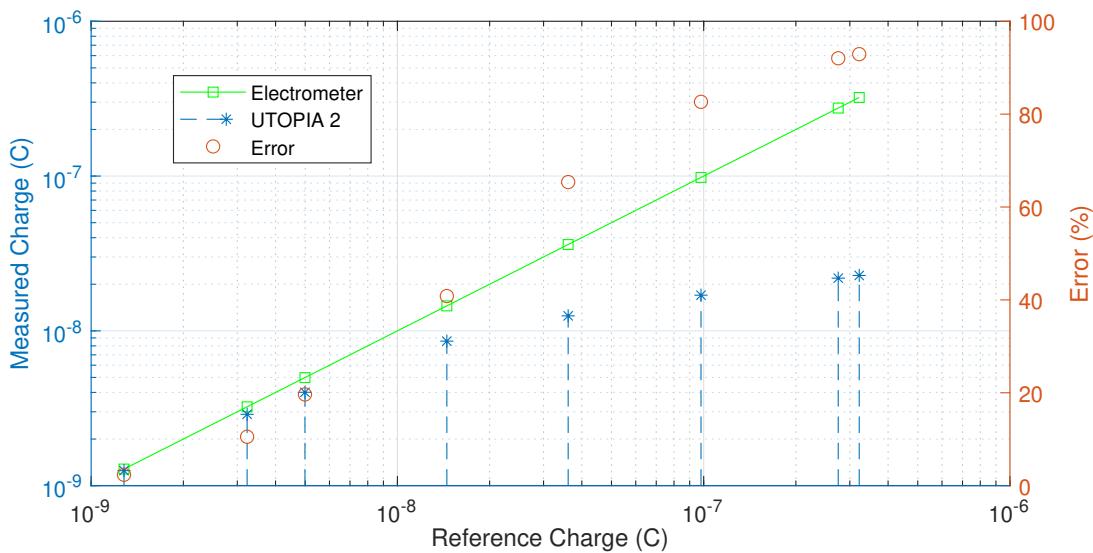

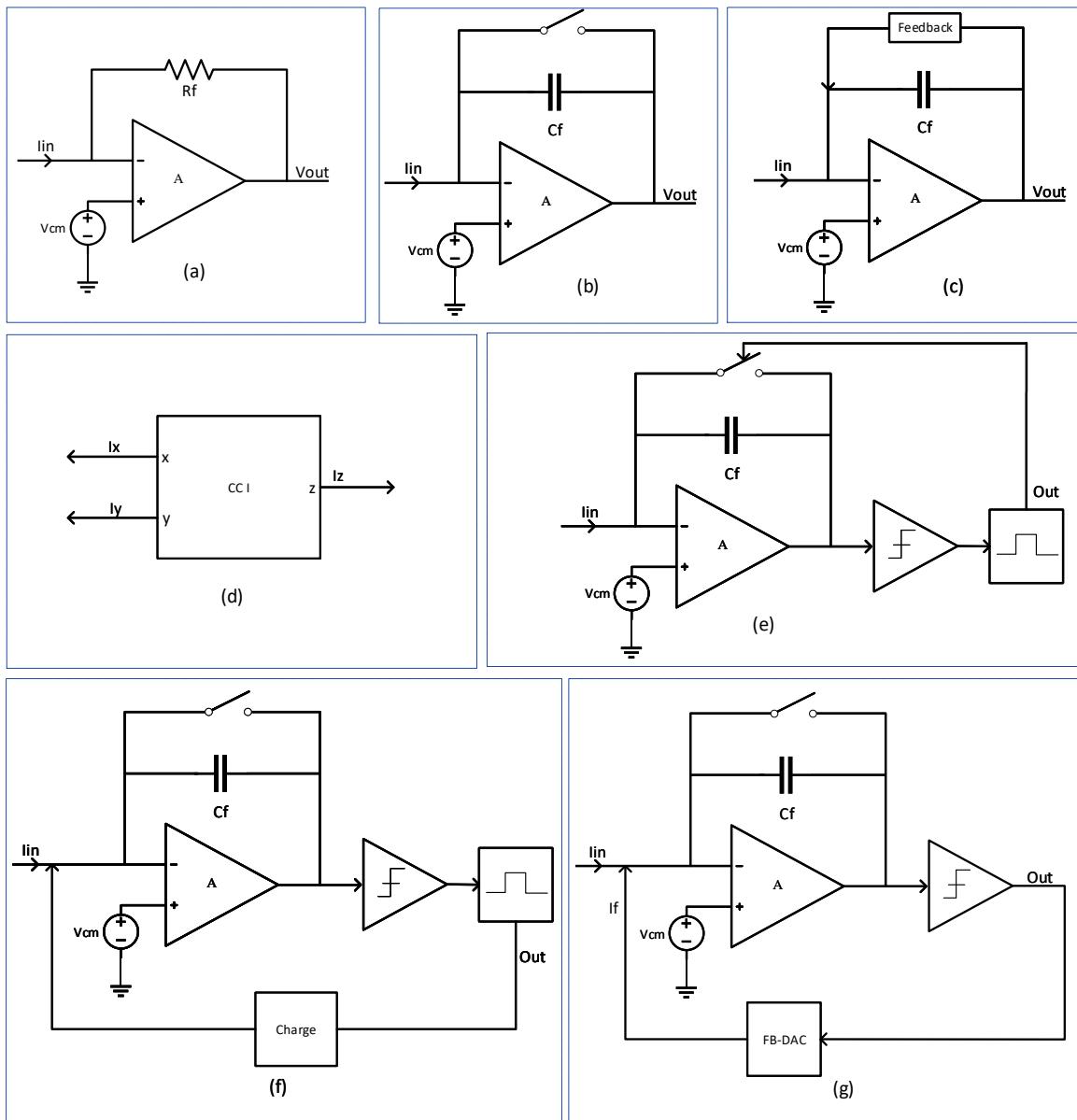

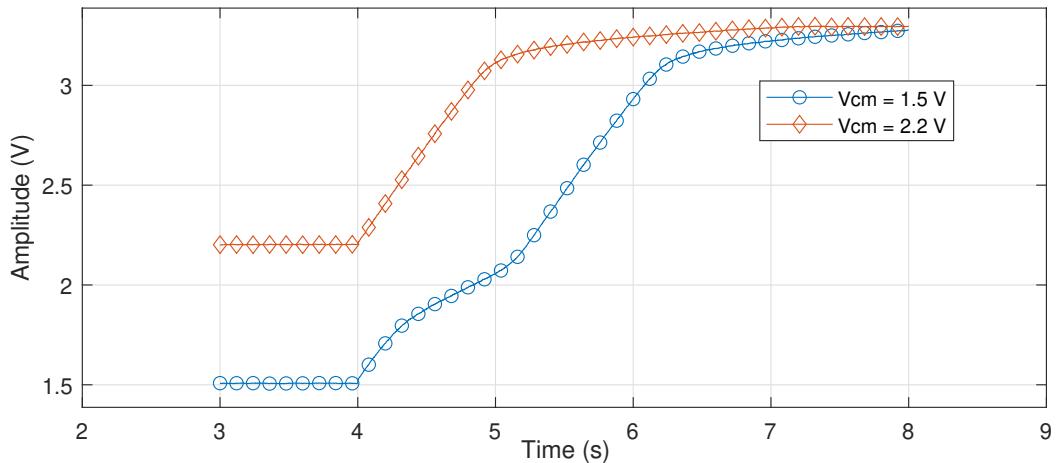

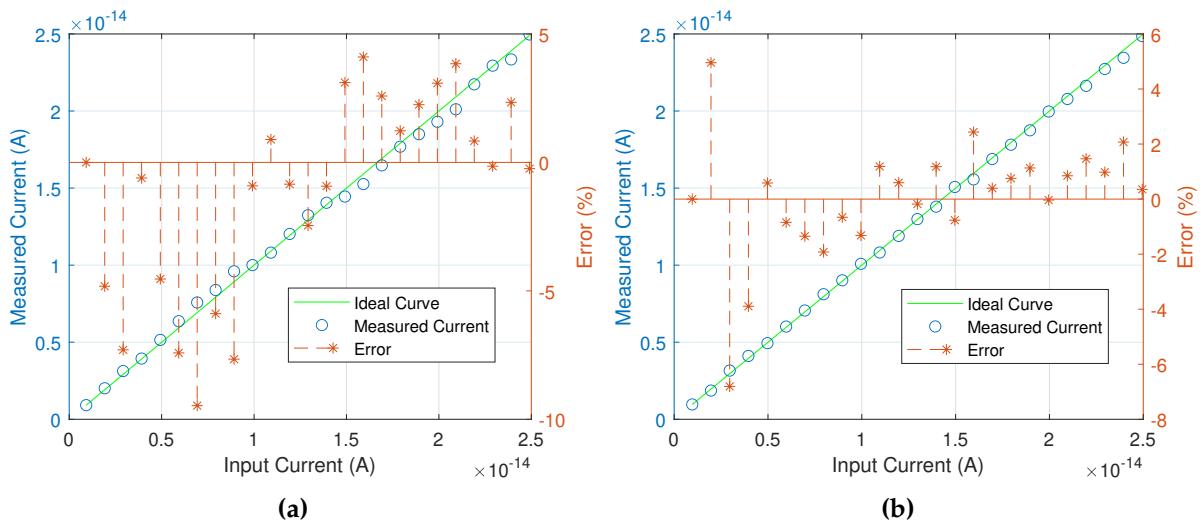

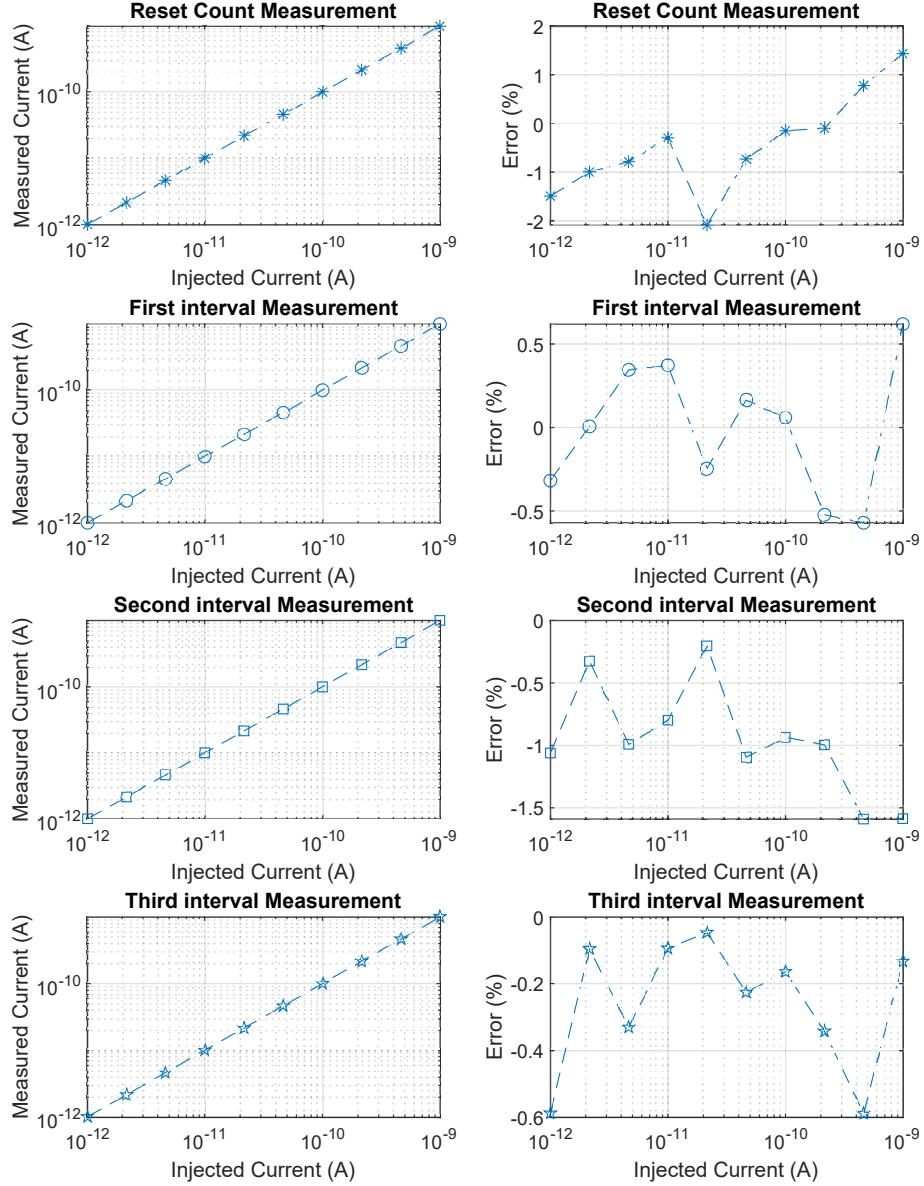

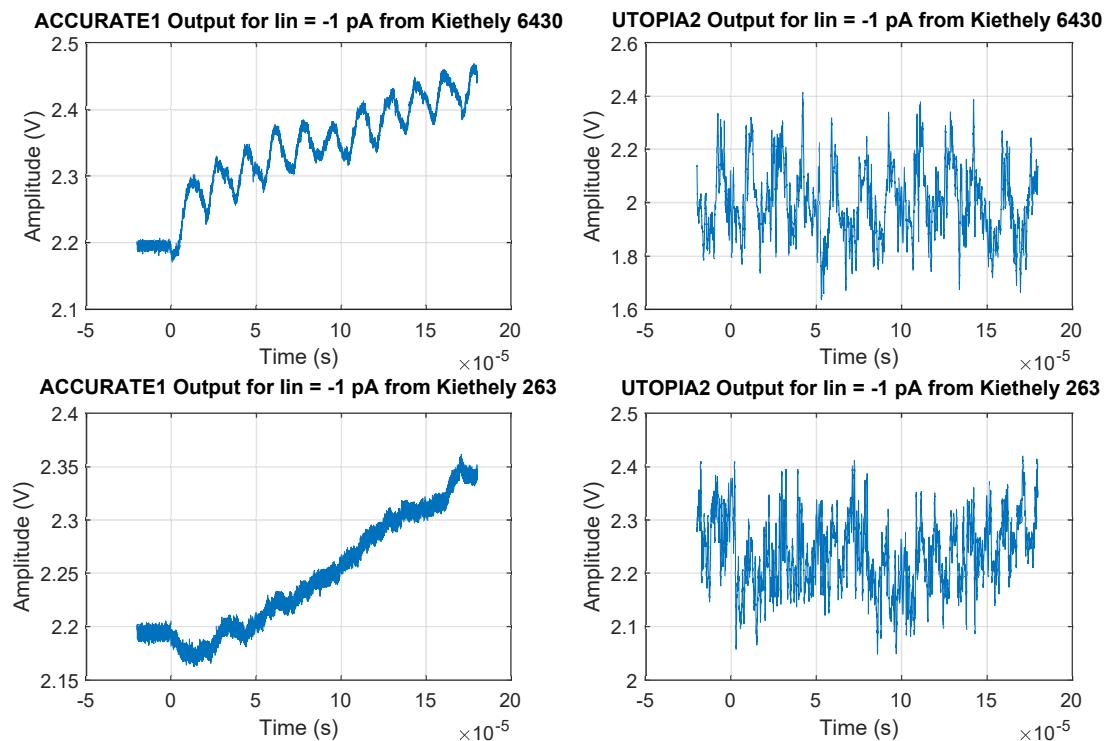

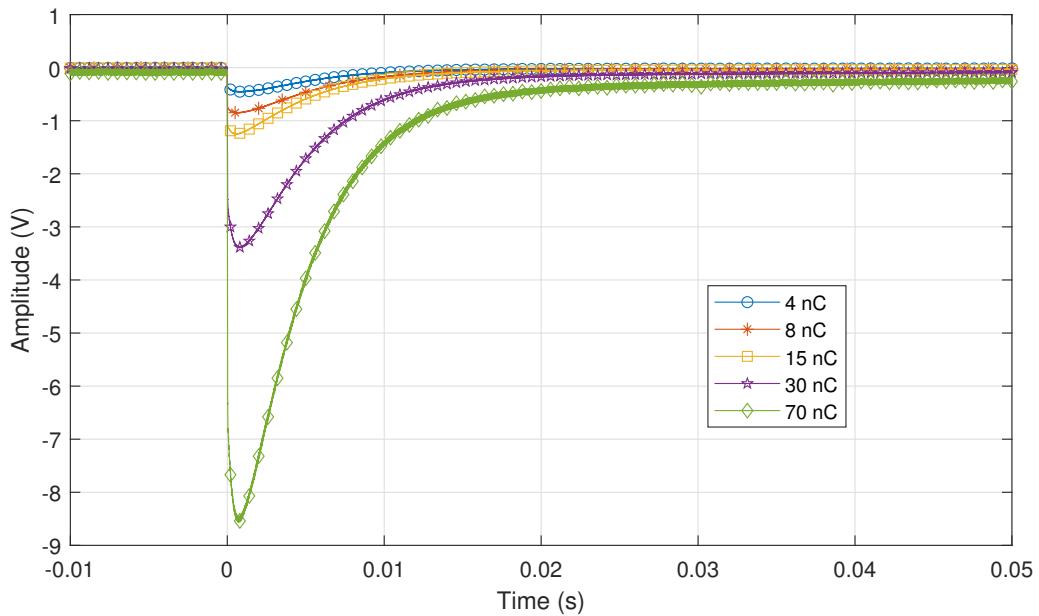

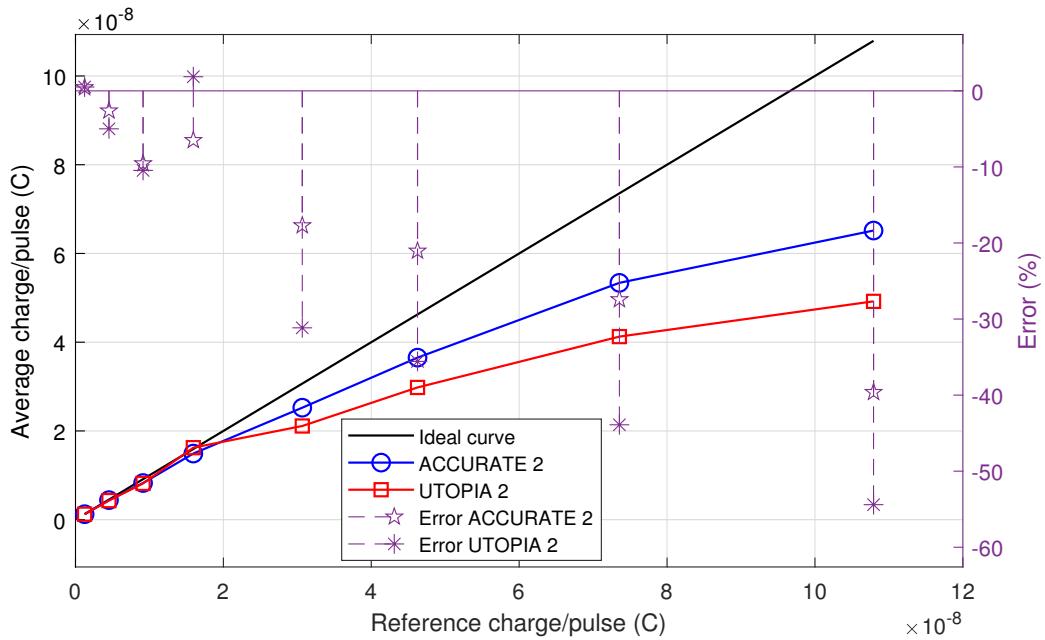

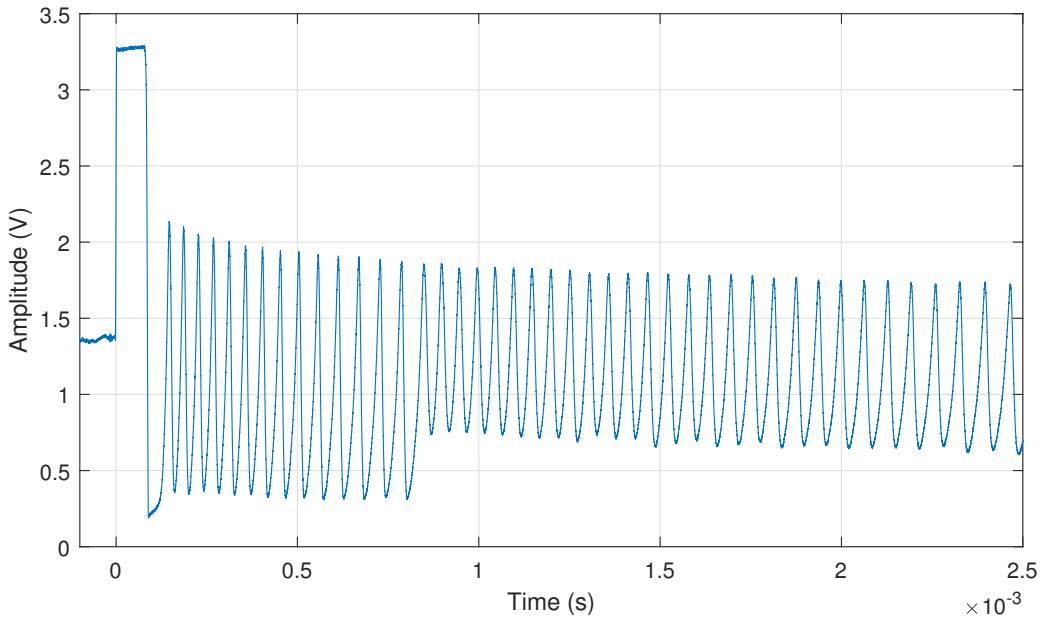

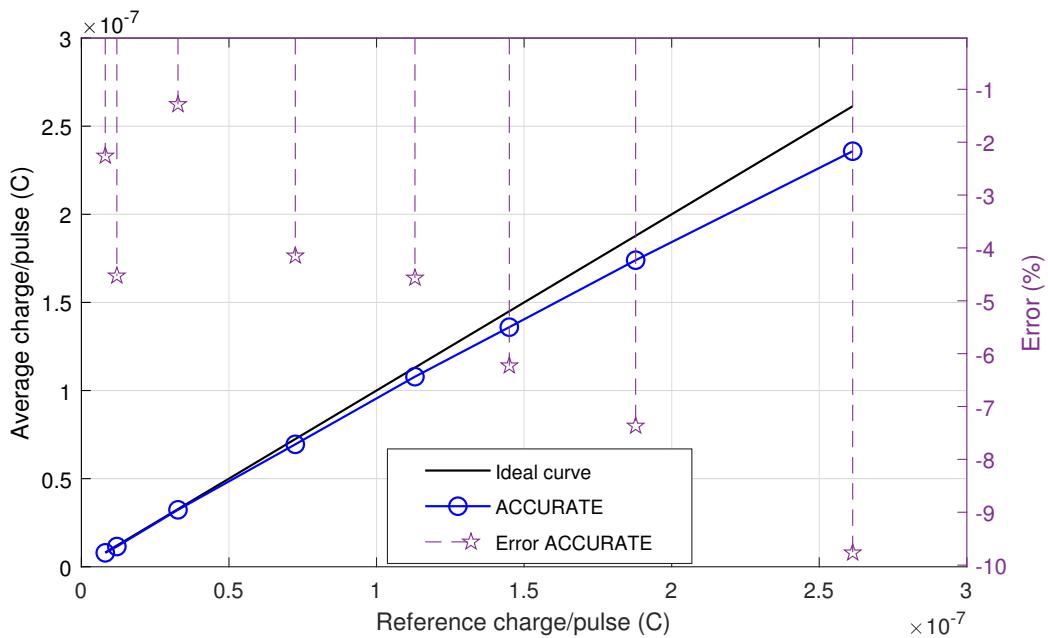

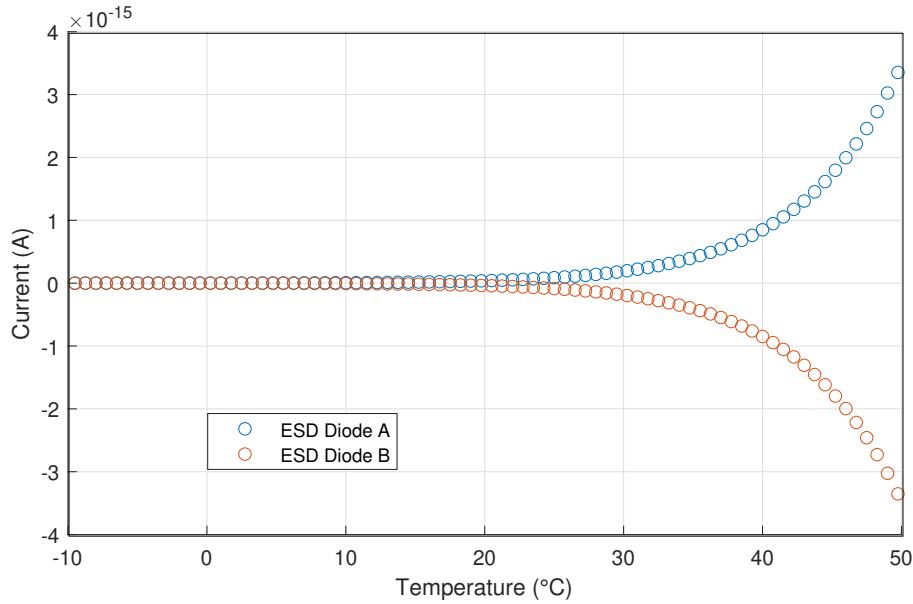

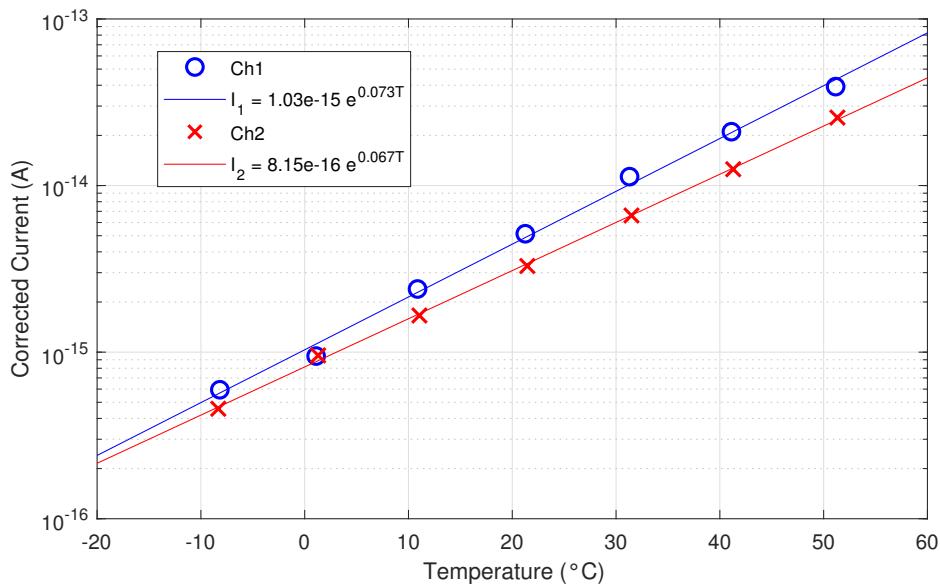

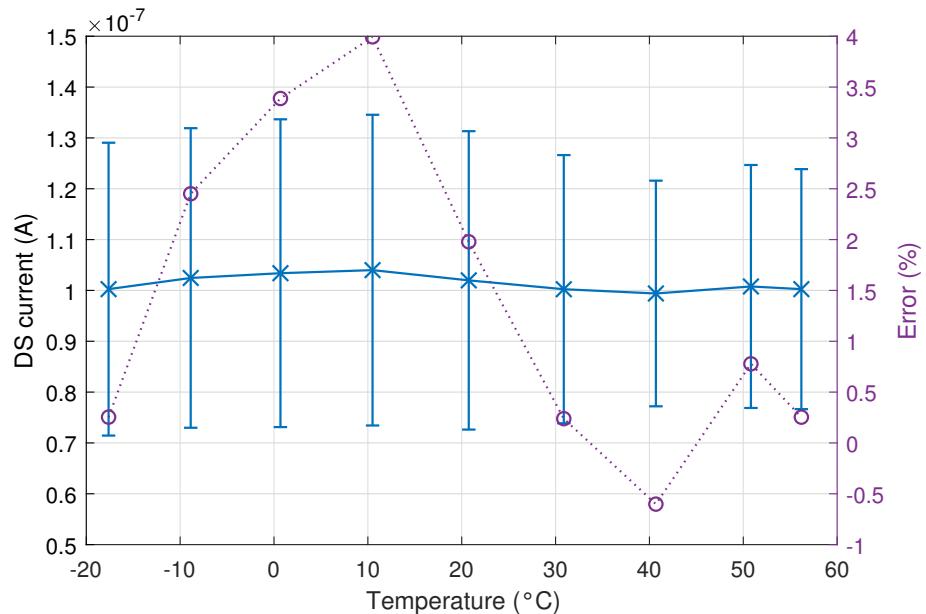

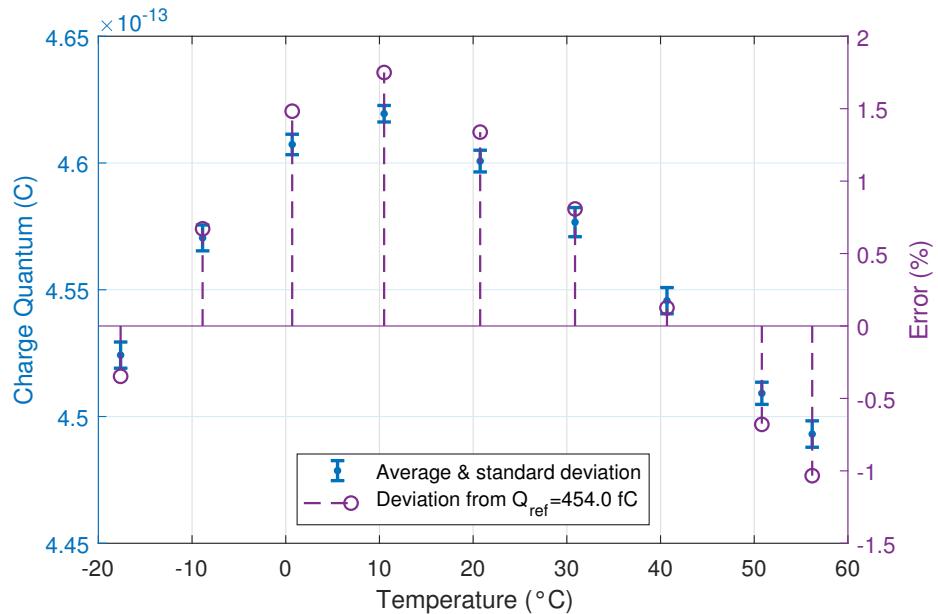

A data acquisition environment was created in MATLAB. Voltage pulses were generated using a signal generator from TTi (TG5021A). The instrument was controlled from MATLAB using the GPIB interface. The generated pulses were fed through a precision resistor R1. The value of the resistor used was  $1\text{ M}\Omega$  or  $100\text{ M}\Omega$ , depending on the desired range of current. The voltage waveform thus gets converted into current and was injected into the ASIC.