# Design and Performance of the SLD Vertex Detector, a 307 Mpixel Tracking System

K Abei, A Arodzerof, C Baltayl, J E Brauf, M Breidenbachh, P N Burrowsd, A S Chouh, G Crawfordh, C J S Damerells\*, P J Dervana, D N Dongd, W Emmetl, R L Englishs, E Etziona, M Fossh, R Freyf, G Hallerh, K Hasukoi, S S Hertzbachc, J Hoeflichh, M E Hufferh, D J Jacksons, J A Jarosh, J Kelseyd, I Leed, V Liad, A L Linterns, M X Liul, S L Manlyl, H Masudah, A K McKemeya, T B Moorel, A Nicholss, T Nagaminei, N Oishie, L S Osborned, J J Russellh, D Rossd, V V Serbok, N B Sinevf, J Sinnottl, K Skarpaas VIIIh, M B Smyb, J A Snyderl, M G Straussc, Su Dongh, F Suekanei, F E Taylord, A I Trandafirc, T Usherh, R Verdierd, S J Wattsa, E R Weissi, J Yashimai, H Yutai, G Zapalack

\*Brunel University, Uxbridge, Middx, UB8 3PM, UK

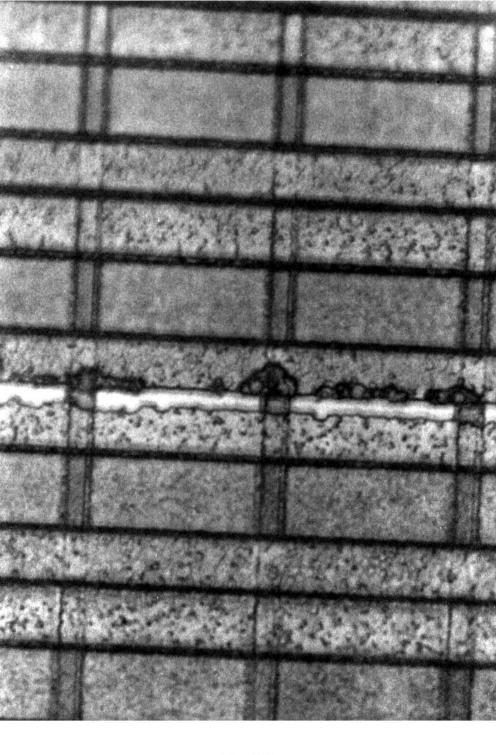

b\*Colorado State University, Fort Collins, CO 80523, USA

c\*University of Massachusetts, Amherst, MA 01003-4525, USA

d\*Massachusetts Institute of Technology, Cambridge MA 02139-4307, USA

e\*Nagoya University, Nagoya 464, Japan

f\*University of Oregon, Eugene, OR 97403-5203, USA

&\*Rutherford Appleton Laboratory, Chilton, Didcot, OX11 0QX, UK

b\*Stanford Linear Accelerator Center, Stanford, CA 94309, USA

i\*Tohoku University, Sendai 980-77, Japan

j\*University of Washington, Seattle, WA 9819501560, USA

k\*University of Wisconsin, Madison, WI 53706, USA

1Yale University, New Haven, CT 06511, USA

Nuclear Instruments and Methods

\* Corresponding author. Tel +44 1235 446298, Fax +44 1235 446733, e-mail c.damerell@rl.ac.uk

This work was supported by US Department of Energy contracts: DE-FG03-93ER40788 (CSU), DE-FG02-92ER40715 (Massachusetts), DE-AC02-76ER03069 (MIT), DE-FG06-85ER40224 (Oregon), DE-AC03-76SF00515 (SLAC), DE-AC02-76ER00881 (Wisconsin), DE-FG02-92ER40704 (Yale); National Science Foundation grant PHY-92-03212 (Washington); the UK Particle Physics and Astronomy Research Council (Brunel and RAL); and the Japan-US Cooperative Research Project on High Energy Physics (Nagoya, Tohoku).

## **Abstract**

This paper describes the design, construction, and initial operation of SLD's upgraded vertex detector which comprises 96 two-dimensional charge-coupled devices (CCDs) with a total of 307 Mpixels. Each pixel functions as an independent particle detecting element, providing space point measurements of charged particle tracks with a typical precision of 4  $\mu$ m in each coordinate. The CCDs are arranged in three concentric cylinders just outside the beam-pipe which surrounds the  $e^+e^-$  collision point of the SLAC Linear Collider (SLC). The detector is a powerful tool for distinguishing displaced vertex tracks, produced by decay in flight of heavy flavour hadrons or tau leptons, from tracks produced at the primary event vertex. The requirements for this detector include a very low mass structure (to minimize multiple scattering) both for mechanical support and to provide signal paths for the CCDs; operation at low temperature with a high degree of mechanical stability; and high speed CCD readout, signal processing, and data sparsification. The lessons learned in achieving these goals should be useful for the construction of large arrays of CCDs or active pixel devices in the future in a number of areas of science and technology.

PACS: 29.40.Gx; 29.40.Wk; 85.60.Gz; 42.79.Pw; 13.20.-w; 12.25.-k; 13.35.Dx

Keywords: Vertex detector; Particle tracking; Pixels; Charge-coupled device (CCD); Heavy flavour; Charm

quark; Bottom quark; Tau lepton

## **Table of Contents**

## 1 Introduction

- 1.1 Summary of VXD2 Design Features

- 1.2 Experience with VXD2

- 1.3 Advances in CCD Technology

- 1.4 VXD3 Design Overview

- 1.4.1 The 3-Barrel Layout

- 1.4.2 Impact Parameter Resolution

- 1.5 Physics Motivation for Upgrade

# 2 Mechanical and Thermal Design

- 2.1 Overview

- 2.2 Ladder Design

- 2.2.1 Mechanical/Thermal Details

- 2.2.2 Electrical Details

- 2.3 Detector Support Structure

- 2.4 Detector-related Mechanical Equipment

- 2.5 Cryostat and Cooling System

# 3 CCD Design and Production

- 3.1 Design Specifications

- 3.1.1 Imaging Area

- 3.1.2 Readout Register

- 3.1.3 Output Amplifier

- 3.2 Prototype Evaluation

- 3.3 Results from Production Phase

- 3.4 Radiation Damage Tests

# 4 Optical Survey and Detector Position Monitoring

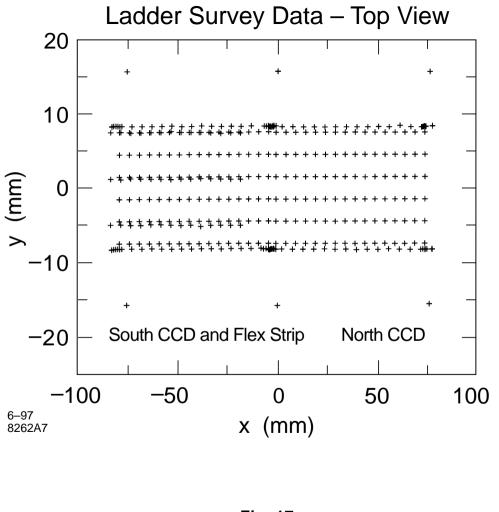

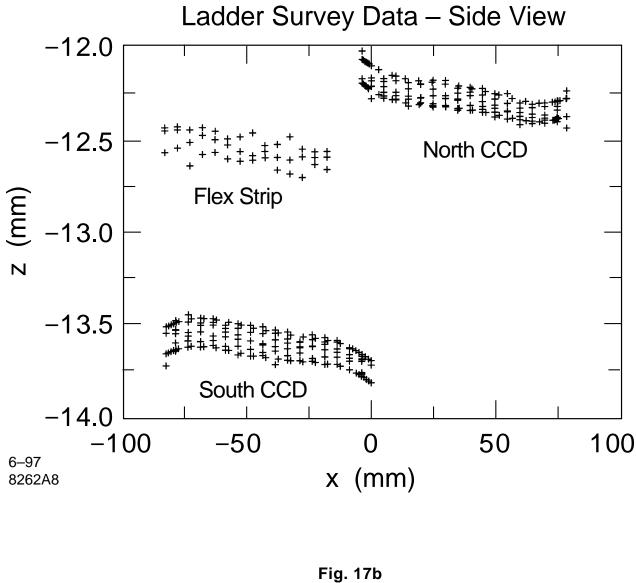

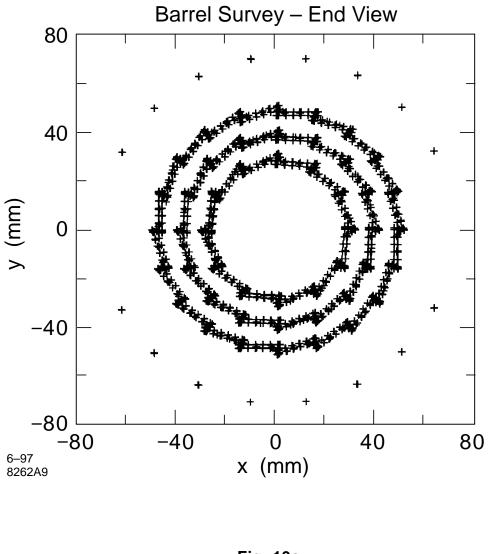

- 4.1 Ladder Survey

- 4.2 Barrel Survey

- 4.3 Survey Data Analysis

- 4.4 Summary of Detector Survey

- 4.5 Detector Position Monitoring

# 5 Detector Electronics and Readout

- 5.1 Charge Transfer on CCDs

- 5.2 Digitization of CCD Output Signals

- 5.3 Data Transfer to FASTBUS

- 5.4 Data Acquisition and Processing

- 5.4.1 Data Acquisition Modules (LFM)

- 5.4.2 Data Processing Overview

- 5.4.3 Cluster Processing

- 5.4.4 Performance of Data Acquisition System

# 6 Detector Performance in SLD

- 6.1 Operational Experience

- 6.1.1 Hardware Performance

- 6.1.2 Beam Background and Data Volume

- 6.1.3 Observation of Radiation Damage Effects

- 6.2 Tracking Efficiency

- 6.3 Alignment and Resolution in Tracking and Impact Parameter

# 7 Lessons Learned and Future Prospects

- 7.1 Lessons Learned from VXD3

- 7.1.1 CCD Design

- 7.1.2 Ladder Design and Support Structure

- 7.1.3 Flex-circuits and Front-end Electronics

- 7.2 Future Prospects

# Acknowledgements

# Abbreviations, Acronyms and Symbols

**Tables**

References

Figure Captions

## 1 Introduction

After the invention of the charge-coupled device or CCD in 1970 [1], the first paper to explore the possibility of using such devices as high precision detectors of minimum-ionizing particles (hereafter referred to as min-I particles) appeared in 1981 [2], followed shortly thereafter by the experimental verification of their performance in a CERN test beam [3]. A pair of these devices, covering the full spectrometer aperture with a total area of less than 1 cm<sup>2</sup>, was subsequently used for the identification of charmed particles in a fixed target experiment [4, 5].

It was realized as early as 1981 [6] that these devices offered the possibility of extraordinary physics performance in the  $e^+e^-$  linear collider environment, significantly superior to what would be achievable with silicon microstrip detectors. The essential reasons for the harmonious match between the linear collider and CCD technologies were:

- (a) very small beam spots, hence a well defined primary vertex for every event.

- (b) small diameter beam-pipe, necessary for precision vertexing and compatible with the limited practicable area coverage with CCD detectors.

- (c) small-scale hence less massive detector; degradation of the track extrapolation due to multiple scattering could be greatly reduced.

- (d) long interval between bunch crossings. While this was not sufficient for complete readout, the background integrated during readout would be only  $\sim 10$  bunch crossings as opposed to  $\sim 10^5$  bunch crossings at a circular machine.

- (e) highly segmented pixel structure, which would comfortably absorb high background per bunch crossing, likely to be found in a linear collider. Using coarsely segmented devices such as silicon microstrips, the inner barrel would need to be pushed out to much larger radius, with consequent degradation in the performance.

The SLD experiment at the SLAC Linear Collider (SLC), provided the first home for these detectors in a colliding beam environment. After tests with a prototype detector VXD1, consisting of a few ladders, the 120 Mpixel detector VXD2 was installed for physics runs starting in January 1992. These early detectors were assembled from a standard commercial imaging CCD of area approximately 1 cm<sup>2</sup> and pixel size  $22 \times 22 \, \mu \text{m}^2$ . While such devices were quite appropriate to the fixed target environment, they were barely adequate for a collider detector with nearly  $4\pi$  solid angle coverage.

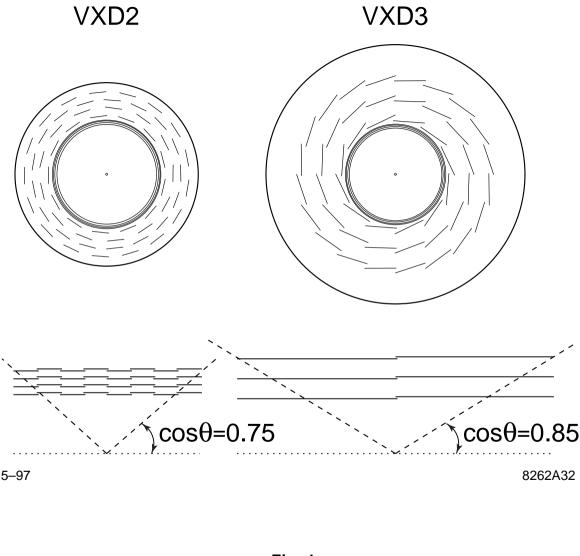

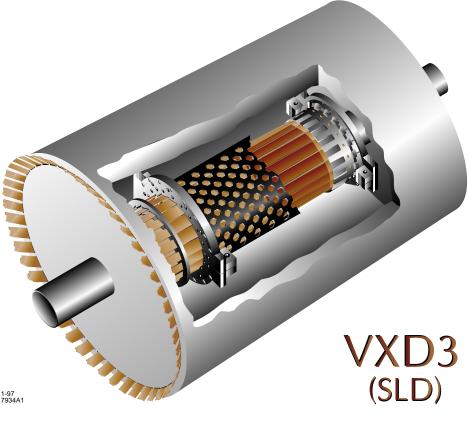

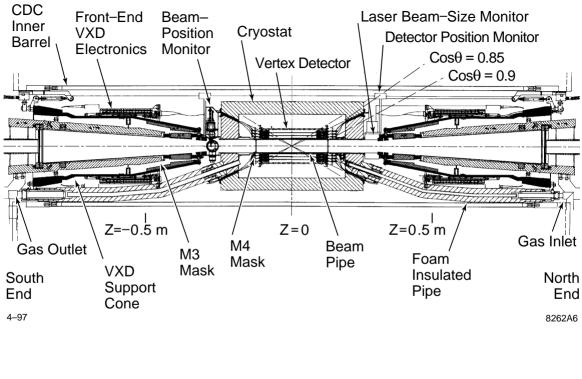

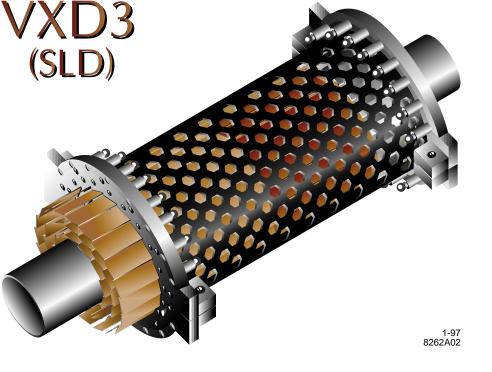

As a result of rapid advances in CCD technology over the past 10 years, the opportunity arose for replacing VXD2 with a much more powerful vertex detector. The proposal to build this upgraded detector VXD3 was approved in March 1994, and the detector was installed in January 1996. Fig. 1 shows the contrasting layout of CCDs around the SLD beam-pipe between VXD2 and VXD3. The geometrical advantages afforded by the much larger VXD3 CCDs are immediately apparent. This paper, which provides a detailed description of this state-of-the-art CCD-based vertex detector, is the first complete technical report on any of these detectors used in high energy physics. For this reason, we include a brief introduction on the characteristics of, and operating experience with VXD2.

## 1.1 Summary of VXD2 Design Features

The overriding technical purpose of any vertex detector is to measure the tracks in an event with sufficient precision that, extrapolating them to the interaction region (IR), it is possible to distinguish between those from the primary vertex (PV) located at the interaction point (IP), and those from secondary or tertiary vertices (SV or TV) due to the decay of particles containing heavy quarks (bottom or charm), or tau leptons. Once this is achieved, a whole range of physics topics related to flavour tagging is opened up. In practice, the majority of tracks are generally rather low in momentum, so that the measurement precision at the IR is limited by multiple scattering in the material of the vertex detector, rather than by its intrinsic measurement precision. In these circumstances, the usefulness of the detector for physics is dependent on achieving a small inner layer radius, a spacing between layers similar to that radius (allowing a good lever-arm for extrapolation to the IR) and the smallest possible layer thickness.

In VXD2, compromises were forced on the detector design due to background conditions at SLC. Design details of this 4-barrel detector are described in [7]. The basic detector elements (8-CCD ladders) had to be drastically redistributed as the design radius of the beam-pipe was increased from 10 mm to 25 mm. The resultant problems are clearly seen in Fig. 1. Barrel 1 (13 ladders) covered only a little more than 50% of the azimuth, leaving Barrel 2 to fill the gaps. Similarly Barrel 3, despite being only 4 mm beyond Barrel 2 in radius, covered not much more than 50% of the azimuth with 17 ladders, with Barrel 4 filling the gaps. This assembly thus guaranteed only two hits on a track, with sometimes a radial separation of only 4 mm between them. As well as the problems with azimuthal coverage, and despite using eight CCDs on a ladder, the polar angle coverage was also barely adequate.

Constructing each ladder out of eight small CCDs implied a rather complex mother board design. On each side of the mother board was a two-layer trace pattern plus a ground plane. Ceramic (alumina) substrates were used, and patterned using thick film technology. CCDs

were attached using a thermoplastic adhesive; rework capability was essential given the finite probability of one of the eight devices failing the acceptance tests. The overall thickness of each ladder was 1.15% radiation length  $(X_0)$ . Electrical contact to the CCDs was made by wire bonding, and to the ends of the ladders by custom designed micro-connectors. To minimise electrical interference, the drive pulses were fed to one end of each ladder, and the analogue biases and signal outputs were routed through the other end.

Front-end electronics, mounted within the inner cylinder of the Central Drift Chamber (CDC) at either end of the VXD cryostat, consisted of fast drive circuits for the linear or readout register (R drive) at the north and preamplifiers at the south end. The slow drive pulses for the parallel or imaging register (I drive), as well as timing signals and analogue biases, were fed in on fine coax cables from the electronics counting house on top of SLD. In order to minimize the effects of radiation damage, explained in Section 1.2, the detector was operated at a temperature of 190 K. It was housed in a very low mass foam cryostat, and cooled by boiloff gas from liquid nitrogen. This coolant gas was piped to and from the detector by means of vacuum jacketed pipes.

The pixel readout rate achievable with this detector was restricted to 2 MHz. The analogue shaping time of approximately 300 ns gave noise performance for each pixel of  $<100 \text{ e}^-$  (rms), adequate for efficient detection and precise centroid finding of the clusters from min-I particles, which typically deposit  $\sim1200 \text{ e}^-$ .

# 1.2 Experience with VXD2

During a rushed installation phase for the detector, two micro-connector fingers (out of 1400 total) failed to make good contact, and these correctable faults were only discovered after the cryostat was sealed and access to the detector was lost. Thus two of the 60 ladders were lost from the beginning of the experiment. This represented the most significant failure throughout the three years operation of the detector. A third bad contact led to the loss of a single CCD. A small number of CCDs developed intermittently high readout noise, an effect due to imperfect contact of micro-connector fingers as a result of thermal cycling. However, these tended to recover in time. No failures of CCDs or front-end electronics were encountered throughout the life of the detector. Occasional failures of accessible FASTBUS modules were of course repaired without problems.

The SLC background environment is predominantly electromagnetic radiation: low energy electrons spiralling around the beam direction, a broad X-ray spectrum resulting from multiple bounces of synchrotron radiation photons, and associated fluorescence. This can lead to two types of radiation damage; see [8] for a general review. Firstly, electromagnetic radiation can

generate electron-hole pairs in the gate oxide, leading to flat-band voltage shifts which may necessitate a change in the device operating bias conditions. Such effects were observed at a rather low level. Secondly, higher energy electromagnetic radiation can cause displacement damage within the bulk of the silicon crystal, leading to electron trapping centres. Due to the large distances over which the signal charge needs to be transported in a CCD (up to several centimetres), it is not surprising that these devices are very sensitive to bulk damage effects. The main effect is an increase in the average charge transfer inefficiency (CTI), as signal electrons are trapped during charge transport. Operating at reduced temperature is effective at increasing the emission time of bulk traps to such an extent that their effect on CTI can be greatly reduced. The intrinsic rate of generation of bulk traps is proportional to the nonionizing energy loss (NIEL) of the radiation [9]. Electromagnetic radiation is much less damaging than hadronic radiation due to its lower NIEL factor. Despite this, and the choice of operating temperature of 190 K, close to the optimal value for CTI suppression, VXD2 did suffer a measurable amount of radiation damage by the end of its life. This was seen as a signal reduction of up to 10% on the inward facing CCDs of Barrel 1, interpretable as an effective CTI of approximately  $1.7 \times 10^{-4}$ , compared with the pre-irradiation value of  $< 10^{-5}$ . The radiation levels when running normally were negligible, but could be very much higher under beam tuning conditions, when the beam would be intercepted by scanned wires, flooding the vertex detector with scattered particles.

The closely spaced 4-barrel system achieved 2-hit coverage for all tracks (on average, a track would physically traverse 2.3 CCDs). The space-point precision on each hit was approximately 5.4  $\mu$ m. However, due to the poor lever-arm between measurements, the impact parameter precision at the IR for a track of momentum p and polar angle  $\theta$  w.r.t. the z-axis (beam direction) was limited to

$$\sigma_{r\phi} = 11 \oplus \frac{70}{p\sin^{3/2}\theta} \ \mu \text{m}$$

and

$$\sigma_{rz} = 38 \oplus \frac{70}{p \sin^{3/2} \theta} \ \mu \text{m},$$

similar to that of a state-of-the-art silicon microstrip vertex detector at LEP.

Nevertheless, the flavour tagging at SLD has benefited from two major advantages with respect to LEP. Firstly, the sub-micron beam spot size and stability in the  $r\phi$  view implies that one can determine the interaction point (IP) extremely accurately at any given time by averaging the fitted IP over the last ~20 interactions. As a result, precise determination of a decay particle flight path direction and distance can be determined if the decay vertex is observed, even if

there are no good tracks from the primary vertex for that event. Furthermore, the very fine segmentation of the CCD detector (2500 pixels per mm<sup>2</sup>) means that, despite the high hit density on Barrel 1 due to background and particles within a jet, the level of cluster merging is truly negligible. Thus, the Monte Carlo generated distribution of impact parameters agrees quite accurately with the experimental one over four orders of magnitude, without the need for large empirical correction factors commonly required with less highly segmented detectors. This agreement forms the foundation for a more elaborate interplay between data and Monte Carlo. Simulated hadronic decays of  $Z^0$ s can be used to develop and evaluate procedures for such requirements as flavour identification within a jet. Confirmation of these procedures is achieved by applying them to real data, and comparing appropriate kinematic and other distributions between the data and the Monte Carlo. While this approach is quite standard, the freedom from large correction factors makes the systematic precision exceptionally high, in this analysis. It has therefore become possible to develop a topological vertex finding method using VXD2 [10], a procedure that goes well beyond the impact parameter method of flavour tagging widely used in the past. The impact parameter method for tagging b-jets (for example) has limited purity due to an irreducible presence of charm jets in the event sample. The topological approach takes advantage of the precisely known primary vertex in SLD for every event. The cleanly measured space points in the vertex detector then permit a search for secondary and/or tertiary vertices. The effective mass of the SV + TV tracks is called the vertex mass, and this can be partly corrected for missing neutrals (e.g. neutrinos) by looking at the transverse momentum imbalance with respect to the vertex flight path direction (PV to SV). This kinematic information provides an effective discriminator between charm and bottom flavoured jets.

Applying this technique to the VXD2 data has led to flavour identification with very small systematic errors, e.g. in the measurement of the b fraction in hadronic  $Z^0$  decays,  $R_b = \Gamma_{b\bar{b}}/\Gamma_{had}$ , [11]. The topological approach also optimises the measurement of decay length, and this has recently led to enhanced systematic precision in the determination of (for example) B lifetimes [12]. As discussed in Section 1.5, there are physics processes for which even higher precision is essential. Apart from some fine tuning (which is ongoing in the analysis of the VXD2 data) it became apparent that any major performance upgrade would be dependent on replacing this detector. This in turn would be made possible only by major advances in the CCD technology underpinning the detector design. Fortunately, by 1993 the required progress in this area had been made.

## 1.3 Advances in CCD Technology

A major advantage of using CCDs is that one benefits from their multi-disciplinary user base. Progress is made by manufacturers with the support of one user community, which may then feed through to help others. High energy physics provides a rather small and intermittent market for scientific CCDs, insufficient to sustain a major R&D programme. The design of the upgrade detector VXD3 was based largely on major progress having been made over 10 years by the CCD manufacturers for other customers. Subsequently, in understanding the VXD3 CCDs it was possible to make modest contributions to advancing the frontiers of CCD development for the common good.

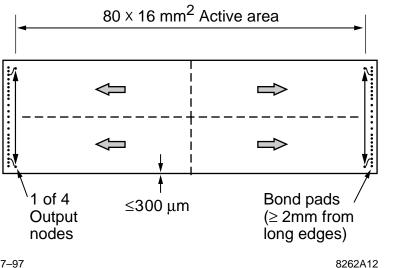

VXD2 was based on the same standard imaging CCDs as had been used for the original beam tests in the early 1980s. By 1993, the most important advance was the availability of affordable fully customized devices, allowing the user to tailor the design to the specific detector requirements rather than being obliged to design a detector around some off-the-shelf CCD product. The next most important advance was the availability of much larger scientific grade devices. Using 5 inch diameter wafers, the SLD requirement for an active area of  $80 \times 16 \text{ mm}^2$  was easily met. This reflects an enormous advance in quality control on the part of the manufacturers: achieving the necessary device uniformity to transport signals of a few hundred electrons reliably across more than 2000 pixels for each of 1600 separate columns represents a major achievement.

Having full flexibility regarding the layout of circuitry around the imaging area, it was possible to almost eliminate the inactive regions along the long edges of the device, and locate all significant additional circuitry (readout registers, output amplifiers, bond pads for external connections, gate protection circuitry, etc) along the short edges of the device. By slightly tapering the imaging area at the ends of the device, all the subsidiary circuits could be accommodated within the width already available.

Increasing the device active area by an order of magnitude was essential in designing a detector with improved polar angle and azimuthal coverage, but a comparable increase in readout time would have been entirely unacceptable. Modern CCD architectures allow a number of output circuits to tap off the signals along a readout register, with corresponding reduction in readout time. This however increases the number of channels of external analogue and A/D circuitry, so a balance must be reached. In the case of VXD3, it was decided to design the CCD with four outputs (one at each corner of the device). Each output could be made more sensitive than that on the VXD2 devices by reducing the load capacitance and using a second stage source follower to buffer the tiny first stage FET from the external load capacitance. With a correspondingly improved noise performance (equivalent noise charge or ENC) the output circuit was designed to run with a pixel clocking rate of 10 MHz as opposed to 2 MHz for VXD2. The combination of an increased number of outputs, operated at higher speed but with no degradation in noise performance, was the key to servicing a three times larger overall active

area for the VXD3 detector, while still keeping the local electronics within the space available for it.

Finally, high performance vertex detectors with 10<sup>8</sup> to 10<sup>9</sup> pixels can only be contemplated if the power dissipation per pixel is extremely low. If one were obliged to install liquid cooling within the active volume (as would be necessary with such a density of active pixels, for example), this would seriously increase the detector thickness, with a consequent degradation in performance. In a CCD system, the power dissipation is due to the drive pulses that transport the signal charges within the devices, and the on-CCD output amplifiers. Numerous advances (low resistance bus lines and gate electrodes, reduced gate overlap, etc) have been made by the manufacturers, greatly reducing the power dissipation per unit area for given clocking conditions. For the output amplifier, the most important factor in reducing power for given performance has been the improved first stage responsivity (by a factor 3 relative to the CCDs of VXD2.

The design specification for the VXD3 CCDs was prepared by the SLD group, with the detailed CCD design being carried out by EEV [13], the manufacturer which won the production contract.

# 1.4 VXD3 Design Overview

These advances in CCD technology permitted an upgrade detector design (Fig. 1) with the following main advantages with respect to VXD2:

- (a) extended polar angle coverage, to benefit from the large polarized asymmetry in physics processes in the most valuable regions of high  $|\cos\theta|$ .

- (b) full azimuthal coverage in each of three barrels, to achieve a self-tracking capability independent of the drift chamber, and consequently improved overall tracking efficiency.

- (c) optimized geometry with stretched radial lever-arm and reduced material in each layer, for significantly improved impact parameter resolution.

Some consideration was given to achieving these aims in a mixed barrel/endcap or barrel/lampshade geometry, but this was easily shown to be non-optimal. Mechanical and electrical connections implied that the endcap detectors would suffer from additional material in the critical region in front of them. In contrast, there was only a minor penalty in precision in extending the barrel coverage, because CCDs (with an active silicon thickness of only  $20 \mu m$ )

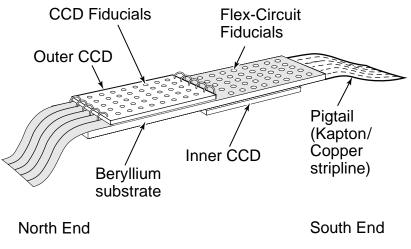

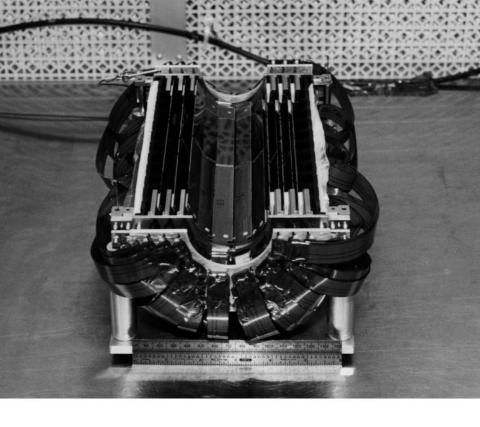

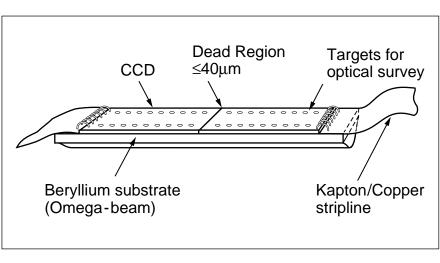

suffer very little spatial resolution degradation due to fluctuations in ionization for tracks at shallow entrance angles, by comparison with the much thicker microstrip detectors. Thus it was certainly preferable simply to extend the barrel length to match the CDC tracking coverage, without the need to consider a mechanically very complex endcap design. The ladder length was set by the wafer sizes used by manufacturers of scientific CCDs (4-5 inches diameter); the  $80 \times 16 \text{ mm}^2$  CCD dimensions permitted a reasonable number of devices per wafer. One CCD is mounted on each side of a supporting substrate (see Fig. 2) forming a 2-CCD ladder as the basic detector component having an active length of 16 cm, 1.7 times longer than the VXD2 8-CCD ladder.

Many of the SLD physics analyses (particularly the b mixing and heavy quark asymmetry measurements) can benefit from an extended polar angle coverage, due to the large analysing power at high  $|\cos\theta|$ . The limit of the angular coverage is defined by the CDC tracking volume, which covers the region from 20 to 100 cm in radius and has an active half-length of ~90 cm. Efficient tracking pattern recognition and reasonable momentum measurement require a minimum of four of the ten CDC superlayers, which defines the polar angle limit of  $|\cos\theta|=0.85$ . These considerations motivated the placement of the outermost layer of VXD3 at a radius of around 48 mm, with the innermost layer at a radius of 28 mm, limited by the SLC beam-pipe. This design provided a very adequate lever-arm for precise track extrapolation to the IP.

#### 1.4.1 The 3-Barrel Layout

Many advanced applications of SLD are dependent on topological vertex reconstruction not only to tag B hadron decays, but also to determine the charge of the B hadron or resolve the  $b \rightarrow c$  cascade vertex charge structure. This requires a high efficiency in correctly assigning all relevant tracks to their corresponding production vertices. These algorithms can only succeed when tracking quality is well under control, since a small deficiency at the single track level can quickly multiply to disable such an attempt. This demands precise impact parameter resolution for a wide momentum range and highly efficient tracking with minimal hit misassignment.

The tracking strategy adopted for VXD2 was to reconstruct the CDC track first, extrapolate it to the VXD and then search for the best VXD hit combination to form the complete track. However, Monte Carlo studies indicate that around 5% of the prompt tracks in a hadronic  $Z^0$  decay within the CDC active volume are either not tracked by the CDC or fail linking to the VXD, mainly due to contamination of wrong CDC hits distorting the extrapolation. This is a consequence of track merging in a dense hadronic jet environment, compounded by the relatively small CDC outer radius and a rather moderate solenoid field of 0.6 Tesla. This

problem becomes progressively worse once the track  $|\cos\theta|$  increases beyond 0.7, when the available tracking length is shortened. Being an effectively two-layer device, VXD2 could not offer independent assistance to alleviate these pattern recognition deficiencies. Considering prompt tracks in hadronic  $Z^0$  decays, for those tracks which linked to VXD2 hits, the links with two VXD hits are 99.4% correct for  $p_T > 0.4~{\rm GeV/c}$ , but only 95.4% correct for  $p_T < 0.4~{\rm GeV/c}$ . However, in the case of occasional hit inefficiency or the presence of a dead ladder, some tracks only have one VXD hit. In this case, the linking purity is significantly worse, at 96% correct for  $p_T > 0.4~{\rm GeV/c}$  tracks, and 91% correct for  $p_T < 0.4~{\rm GeV/c}$ . The low- $p_T$  tracks suffer in addition from the drastic deterioration of the impact parameter resolution. The allowance of one-hit links also introduces another source of confusion, as strange particle decay products or tracks from particle interactions with detector material can also pick up a background hit to produce a false link. The links with  $\geq 3~{\rm VXD}$  hits on the other hand show a much cleaner linking purity of 99.9% for tracks with  $p_T > 0.4~{\rm GeV/c}$ , and 99.5% for  $p_T < 0.4~{\rm GeV/c}$ .

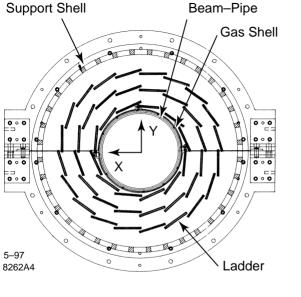

These observations led to the choice of a full three-barrel coverage for VXD3, as sketched in Fig. 1 and shown in more detail in Figs. 3-5. This permits linking with a minimum of two VXD hits even given the allowance for small hit inefficiencies or some dead channels, providing a strong insurance for linking purity, impact parameter resolution uniformity, and reduction of fake links. An even more attractive prospect is that for the majority of VXD3 tracks with ≥ 3 hits, a VXD hit vector is relatively easy to reconstruct stand-alone, while fake combinations only amount to less than 30% of all vectors before any matching with CDC tracks. The very fine granularity of the CCD pixels is ideal for resolving the otherwise difficult merging track cases. These high precision VXD hit vectors in 3-D are powerful additions to the global tracking pattern recognition capability. The detailed implementation of this new strategy to recover the deficiencies in pattern recognition with the CDC alone is already developed, and working well on recent SLD data.

The custom design of the VXD3 CCDs allows the active region to extend across the full ladder width of 16 mm without bond wires protruding out of the ladder surface along the long edge. This feature permits adjacent ladders in the same barrel to be placed in a 'shingled' layout with a small cant angle of  $9-10^{\circ}$ , thus providing azimuthal coverage overlap in the range of  $300~\mu m$  to 1 mm, depending on layer and CCD location on the inner or outer surface of the ladder (see Fig. 3). This layout not only establishes complete azimuthal coverage for each barrel, but also provides important assistance in tracking-based alignment, by using the tracks passing through the overlap regions, establishing direct constraints between adjacent ladders.

## 1.4.2 Impact Parameter Resolution

One of the most unsatisfactory features in the VXD2 design was that the ladders were forced to be very closely packed around a larger beam-pipe than originally anticipated. The consequence was considerably compromised impact parameter resolution, due to the very short radial leverarm between hits (best case 12 mm, worse case 4 mm to extrapolate over 30 mm to the IP). The much larger ladders in the VXD3 design allow significantly improved radial leverarm while still having an increased solid angle coverage.

The combined CDC+VXD track impact parameter resolution has rather varied contributions from the CDC information, depending on the track momentum and viewing projection. The CDC provides its best help in the  $r\phi$  view, high momentum regime. The CDC  $\phi$  resolution at its inner radius is 0.3 mrad at high momentum. This, combined with the innermost VXD hit, supplies the dominant contribution to the impact parameter resolution for VXD2 and is similar to the stand-alone vertex detector contribution for VXD3. The CDC polar angle resolution of approximately 2.0 mrad, on the other hand, is only comparable to the stand-alone polar angle resolution of VXD2. The CDC therefore still helps in the rz view at high momentum in the VXD2 case, but for VXD3 the stand-alone vertex detector capability with extended lever-arm dominates the impact parameter resolution in the rz view. In the momentum regime of a few GeV/c and below, the contribution from the CDC angular information becomes much less significant in both views for both VXD2 and VXD3, due to the multiple scattering in the material between the VXD and the CDC. In the rz view at all momenta, and the  $r\phi$  view at low momenta where one relies on the VXD stand-alone capability, the improvements from the extended radial distribution of layers in VXD3 are most significant. From these basic considerations, it is also clear that one should avoid any need for fallback on links based on single VXD hits, as their impact parameter resolution at low momentum would degrade severely, beside the concern of pattern recognition impurity. This requirement is well met by the VXD3 three-barrel layout.

The mean radii of the three layers were chosen to be 28.0, 38.2 and 48.3 mm, with 12, 16 and 20 ladders respectively. The radius of Layer 1 was constrained by the beam-pipe radius at 23.2 mm which was set by the risk of increased background at a smaller radius. The Layer 3 radius is chosen based on the angular coverage consideration mentioned at the beginning of Section 1.4. There would potentially be further impact parameter resolution gain in the rz view at high momentum by increasing the Layer 3 radius. However, this would be at the cost of losing full three-barrel coverage at high  $|\cos\theta|$ . This would result in not only a loss of resolution when the coverage falls back to the two inner layers, but also loss of the self-tracking capability which is especially needed for global pattern recognition at high  $|\cos\theta|$ . A further radially expanded detector would also increase the cost due to the need for more ladders

and electronics, as well as a more expensive detector mechanical support structure. The position of Layer 2 close to midway between Layers 1 and 3 is optimal for adequate lever-arm in case of hit inefficiency in either Layer 1 or Layer 3.

Beside the geometry optimization, the impact parameter resolution with VXD3 is further improved due to the reduction of detector material. In the case of VXD2, this amounted to  $1.15\%~X_0$  of material per ladder. The advances in technology associated with the various components required for a ladder, have permitted a much improved design (see Section 2) which dramatically reduces the material to  $0.40\%~X_0$  per ladder. The VXD3 beam-pipe titanium liner and the beam-pipe itself are also thinner than for the VXD2 design. Various materials used in the cryostat surrounding the vertex detector are replaced with lighter alternatives whenever possible. The overall material thickness comparison between VXD2 and VXD3 is shown in Table 1.

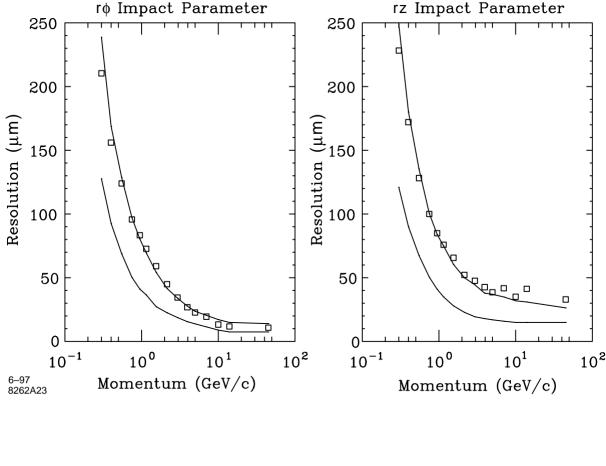

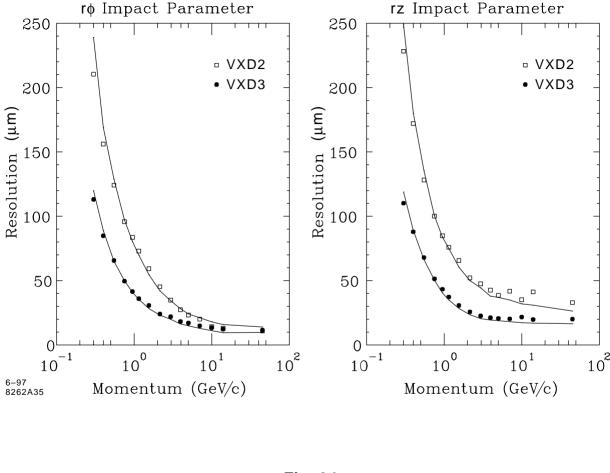

The detailed geometry and material distributions of both VXD2 and VXD3 are simulated in detail with GEANT [14]. The impact parameter resolution of tracks in hadronic  $Z^0$  decays as well as in  $Z^0 \to \mu^+\mu^-$  and  $Z^0 \to e^+e^-$  events are studied for individual momentum and  $\cos\theta$  regions. The expected impact parameter resolutions based on Monte Carlo for tracks at  $\cos\theta=0$  with VXD3 are shown in Fig. 6 in comparison to VXD2 Monte Carlo and data. The impact parameter resolutions for VXD2 data are extracted from raw impact parameter distributions after correcting for heavy flavour decays and IP resolution effects. It should be noted that the VXD2 Monte Carlo simulation generally describes the data remarkably well. The same Monte Carlo framework applied to VXD3 indicates a factor of two improvement from VXD2 in the entire rz view impact parameter resolution. Improvement in the  $r\phi$  view is also a factor of two at low momentum, while somewhat less at very high momentum. A rough approximation of the expected VXD3 impact parameter resolution is

$$\sigma_{r\phi} = 9 \oplus \frac{33}{p \sin^{3/2} \theta} \, \mu \text{m}$$

and

$$\sigma_{rz} = 17 \oplus \frac{33}{p \sin^{\frac{3}{2}} \theta} \ \mu \text{m.}$$

These dramatic resolution improvements combined with a significantly increased solid angle coverage and full three-layer tracking, were expected to bring a powerful enhancement to the SLD heavy flavour physics programme.

# 1.5 Physics Motivation for Upgrade

The physics accessible with precision vertex detection includes some of the most topical and fundamental measurements being made at the  $Z^0$ . The accuracy of these measurements directly reflects the impact parameter resolution of the detector, and to a lesser extent its track reconstruction efficiency. Charge tagging efficiency is also important. With its improved impact parameter resolution, extended solid angle coverage, and enhanced pattern recognition capability, VXD3 improves the accuracy of several key heavy quark measurements to the point where theory leads one to expect new effects to emerge. The enhancement in purity and efficiency of jet flavour identification, in evolving from VXD2 to VXD3, has recently been quantified [15].

The measurements of the couplings of the b-quark to the  $Z^0$  have become an especially interesting chapter of precision electroweak testing because they are experimentally tractable (lifetime tagging efficiently isolates clean b samples) and theoretically interesting (vertex corrections induced by new physics should perturb Standard Model predictions at the 1% level). Measuring  $R_b$  with enough precision to see evidence for new physics, pushes experimental technique to its limits. The measurement requires an extremely *clean* b tag, to minimize the systematic errors arising from charm contamination, yet *efficient enough* to permit self-calibration of the tagging efficiency with a double tag, without paying too high a price in statistics. VXD3's factor of two improvement in impact parameter resolution at low momentum, translates into a significantly improved efficiency for identifying secondary vertex activity. The resulting improvements in topological vertexing allow improved discrimination of charm and bottom. VXD3 can tag a b jet with 45% efficiency and 99% purity, which doubles the statistical power of the current detector. This will lead to an overall error in  $R_b$  of less than 0.7% with a data sample of 0.5 million  $Z^0$ s.

The measurement of the parameter  $A_b$  which describes parity violation in the  $Z^0$  coupling to b-quarks, will also benefit from the improved vertexing capability of VXD3.  $A_b$  is measured with the polarization-enhanced forward-backward asymmetry, which requires both b-tagging and b-quark charge determination in hadronic  $Z^0$  decays. The increased solid angle coverage provided by VXD3 permits vertex-tagging b jets in the range of  $0.75 < |\cos\theta| < 0.85$ , beyond the present VXD2 acceptance, where the asymmetry is nearly maximal and the cross-section is enhanced. The result is a 15% reduction in the statistical error in  $A_b$ . The improved resolution of the new detector can increase the efficiency of a high purity b tag by roughly 30%, leading to an additional 15% reduction in the statistical error. The b-quark charge can be determined topologically when the charge of the b hadron or the subsequent charm meson is non-zero. The enhanced topological vertexing possible with VXD3 will incrementally improve

the determination of the net charge of the tracks associated with the b decay and will improve the ability to distinguish which tracks are associated with the charm decay.

The most exciting physics possibility afforded by VXD3 is the direct observation of  $B_s$  mixing through the measurement of the oscillation frequency. Such a measurement would 'complete' the determination of the CKM parameters by allowing the first precise measurement of  $V_{td}$  and it could provide the first sharp test of the CKM explanation of CP violation. LEP measurements have shown that the oscillation frequency  $x_s$  is high (>13). This puts a premium on the excellent decay length resolution possible with VXD3, which is needed to observe oscillations in the range expected by the Standard Model,  $10 < x_s < 25$ . The improved resolution also improves event selection efficiencies, and most significantly will allow the final state quark charge to be assigned topologically. In this technique, one first selects neutral B decays then asks for a decay pattern consistent with opposite charges at the B decay and D decay vertices. This selection procedure enhances the fraction of  $B_s$  mesons in the sample, and the sign of the B vertex-D vertex charge dipole gives the charge of the decaying b-quark. In conjunction with other techniques, this method will allow the exploration of the oscillation parameter space up to  $x_s \sim 15-20$  with a 0.5 million  $Z^0$  sample. This is well beyond what has been possible at LEP, or would be possible with VXD2. With an even larger data set, VXD3 would have sufficient resolution to see mixing up to  $x_s \sim 30$ .

With VXD3, the art of topological vertexing is being advanced. Already with VXD2, the physics applications [11, 12] have included secondary and tertiary vertex identification, vertex charge determination to isolate charged and neutral *B* meson decays, and charge dipole separation to extract quark charge. With both improved resolution and enhanced pattern recognition capability, it will be possible to clarify the full pattern of vertex topologies. From this improved technical base, one can hope to identify gluon splitting, search for charmless and double-charm *B* decays, isolate charm from bottom decays, and search for topological anomalies. As regards efficiency and purity of flavour tagging, charm is more difficult than bottom, and consequently will show the greater improvement with VXD3. The high resolution together with the sub-micron SLC beam spot will likely enable the development of new methods and new measurements.

# 2 Mechanical and Thermal Design

#### 2.1 Overview

The mechanical design phase of the VXD3 detector was intimately coupled to the plans for optical survey and position monitoring (Section 4) and to the plans for tracking-based global and internal alignment (Section 6.3). The purpose of this overview section is to explain the general principles of the mechanical design and their connection to these other aspects.

The detector operating conditions required the placement of 96 flexible thinned CCDs in a cryogenic environment (operating temperature ~190 K). Obtaining a high level of mechanical stability in a low mass structure was the main design goal. The general approach to satisfying these conflicting requirements was as follows.

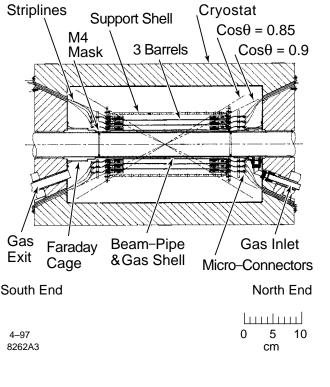

The CCDs were attached to thin beryllium substrates, forming ladders (Fig. 2). These fragile ladders were attached to a series of three concentric beryllium annuli, which were clamped to the overall beryllium support structure, which consists of a closed cylinder external to the detector barrels (Figs. 3-5). This structure was made from an instrument grade of hot isostatically pressed beryllium (I-250 from Brush Wellman) which was found to have exceptional isotropy and a high specific modulus (elastic modulus/density). The support structure could be split to allow the two complete half-detectors to be assembled around the SLC beam-pipe. To obtain a high level of geometrical repeatability of the support structure at assembly, all mating surfaces were lapped flat and all adjacent components were match drilled, reamed, and pinned. This extremely rigid support structure transformed the 48 flexible ladders into a highly stable 3-barrel assembly, with each ladder clamped to its rigid annuli at either end. This demountable structure permitted a succession of assemblies with one barrel at a time, allowing a full optical survey of the CCD geometry to be built up layer by layer. The mesh construction of the support shell, Fig. 5, permitted survey of each installed barrel from the outside. The VXD support structure when fully assembled thus consisted of an essentially rigid cylinder which was mounted to the beam-pipe by means of a low-stress, three-point kinematic mount. This assured that the detector shape during the survey (when the detector was mounted on a short dummy beam-pipe) would be essentially identical to that in the final assembly on the real SLD beam-pipe.

In SLD, the detector is buried within a low mass foam cryostat (Figs. 4, 5). The inner section of beam-pipe on which it is mounted is mechanically isolated from the SLC final focus system by means of an atmospherically balanced bellows system. This reduces (but does not eliminate) occasional disturbances due (for example) to alignment adjustments to the final focus. Despite the fact that the vertex detector is hidden within the cryostat, any positional

variations can be accurately inferred by monitoring the inner section of beam-pipe to which it is rigidly attached; this is discussed in detail in Section 4. Within stable epochs, the position (global alignment) of VXD3 relative to the CDC is deduced by tracking. Tracking data are also used to determine residual corrections to the internal detector geometry, in order to account for effects beyond the precision of the optical survey, as discussed in Section 6.3.

In summary, the mechanical construction of VXD3, combined with a series of optical surveys, followed by tracking-based alignment after installation, formed the basis of a coherent strategy for determining the true geometry of this delicate instrument running at cryogenic temperatures, to very high accuracy. The principal mechanical parameters of the detector assembly are summarized in Table 2.

# 2.2 Ladder Design

The material within the active tracking volume of the vertex detector (out to a polar angle cutoff given by  $|\cos\theta| = 0.9$ ) consists of the CCDs plus the ladder motherboards on which they are mounted. Further out in radius one encounters the vertex detector support shell, the vertex detector cryostat barrel, the inner barrel of the CDC and so on. None of these structures at larger radius is critical in terms of the impact parameter precision which characterizes the capability of the vertex detector for physics. In contrast, the ladder motherboards are extremely relevant for this, and their thickness as well as that of the CCDs needs to be reduced to the lowest possible level. However, the thinned CCDs are extremely flexible, and rely on these substrates for mechanical stability. In addition, the electrical connections to each end of the CCD must be made by traces on these motherboards. Finally, the ladder temperatures even under steady operating conditions are not precisely controlled. There are thermal gradients associated with the power dissipation on the CCDs and the flow of cooling gas, and in the event of electrical failure a CCD might need to be shut down, reducing the operating temperature of its particular ladder. Thus, tolerance to temperature excursions is essential. Designing a motherboard to satisfy these conflicting requirements is a complex compromise. After trying a number of ideas (some of which are mentioned in Section 7) a solution was found which works extremely well, as well as being 35% thinner than the original design.

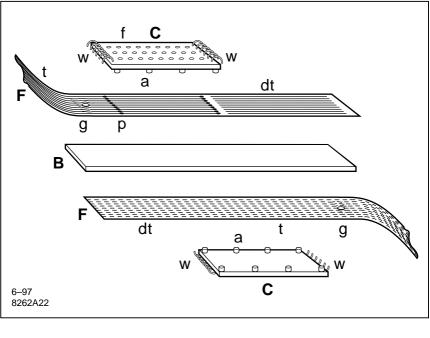

The basic support structure was a thin beryllium beam,  $21 \,\mathrm{cm} \times 1.6 \,\mathrm{cm} \times 0.381 \,\mathrm{mm}$  (0.015 inches thick) having an initial flatness after machining (as measured by the sagitta when held at one end on edge) of less than  $100 \,\mu\mathrm{m}$ . Onto this was bonded, in one operation for both sides, a pair of kapton/copper flex-circuits:  $13 \,\mu\mathrm{m}$  kapton, carrying  $\frac{1}{2}$  ounce (17.8  $\mu\mathrm{m}$ ) rolled, annealed copper traces, passivated by a kapton cover layer. These circuits ran the full width and length of the ladder, with 'pigtail' extensions to carry the electrical traces to microconnectors, approximately 5 cm beyond each end of the ladder. An acrylic thermoplastic

adhesive was used to attach the flex-circuits to the motherboards under pressure, at a temperature of approximately 180 C. The CCDs were attached to the ladders by adhesive pads, and wire bonded from each end of the CCD to gold-plated pads (electroless gold with an electroless nickel barrier) on the traces of the flex-circuits. Fig. 7 shows an exploded view of the ladder assembly and Table 3 lists the contributions to the ladder thickness of  $0.40\%~\rm X_0$  in the active volume of the detector.

#### 2.2.1 Mechanical/Thermal Details

The arrangement of the beryllium substrate sandwiched between two essentially identical flex-circuits provided a balanced structure with respect to thermally induced stresses. Note the presence of the dummy traces (Fig. 7) which optimally balanced the real traces carrying connections to the inner end of the CCD on the opposite face of the ladder. On cooldown, the thin kapton/copper skins were obliged to follow the contraction of the beryllium substrate. Internal forces within this assembly were considerable, but the tendency to bowing was minimized by the balanced structure.

However, this balance was in principle disturbed by the attachment of the CCDs on either side of the ladder, one at each end. Furthermore, the CCD elastic modulus was too great to allow a rigid connection to the beryllium, given the considerable difference in thermal expansion coefficient between these materials. This situation was dealt with by attaching the CCDs with eight relatively thick (200  $\mu$ m) pads of NuSil, a phenyl silicone adhesive [16]. This adhesive, having a low elastic modulus and a very low glass transition temperature (well below 170 K), provided a compliant bond which ensured excellent mechanical stability with low shear stress for repeated thermal cycling of the detector. Thus on cooldown, the ladder motherboard felt very little stress arising from the CCDs attached to it.

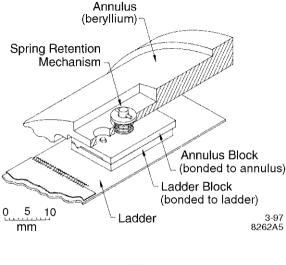

There were two sources of potentially damaging thermal stress which needed to be considered. Firstly, the sandwich described above would never be perfectly balanced. Measurement of unsupported samples cooled to 200 K revealed shape changes which could be described by a quite uniform change of curvature (bow) along the length of the ladder of magnitude in the range 50 to 100  $\mu$ m. This of course would be quite unacceptable for any assembly required to achieve tracking precision of a few microns. However, the ladders in the assembled detector were not free, but attached at each end to the essentially rigid support structure, via the ladder block/annulus block assemblies sketched in Fig. 8. These blocks were themselves attached to their substrates with thin layers of adhesive, and their rigidity in this assembly was such that a ladder which would bow by 100  $\mu$ m when unsupported, would have its sagitta reduced to 0.8  $\mu$ m when attached to these block assemblies. Thus the tendencies of the unsupported ladder substrates to flex on cooldown were suppressed extremely effectively in the overall support

structure. However, these attachment blocks, while solving one potential thermal problem, tended to create a different one. The support structure can be considered to be a homogeneous beryllium assembly. However, the operating temperature of the overall detector is by no means uniform. Due to the thermal dissipation on the CCDs, the ladders are slightly warmer than the parent structure, and the outermost ladders are warmer than the inner ones due to the flow direction of the coolant gas. A minute excess expansion of a rigidly clamped ladder relative to its supports would induce massive bowing. This problem was avoided by allowing one degree of freedom (longitudinal sliding) between one pair of ladder/annulus blocks (at the south end) for each ladder (see Fig. 8). Including this low-friction sliding joint in the overall assembly guaranteed extremely good shape stability of the ladder substrates under thermal cycling. Stress relief between the dissimilar materials used in this assembly (ceramic blocks on beryllium substrates) was again achieved by controlled-thickness layers of the phenyl silicone adhesive mentioned above. In this situation an adhesive layer of  $100~\mu$ m thickness was sufficient to provide the necessary stress relief.

For the CCDs themselves, they could be expected to track precisely the movement of their ladder substrate, as long as their eight adhesive pads were of uniform diameter (~1 mm) and thickness. This was achieved by a collaboration between the SLD group and the CCD manufacturer. One of the most important decisions for the success of this project was how to handle the interface between these two groups. The original contract called for the delivery to SLAC of unpackaged devices. It was however apparent that the issues of static damage, wire bond quality control, and mechanical damage could all cause problems in this scenario. It was therefore decided to switch to an arrangement where EEV were supplied with prepared ladder motherboards, and their work continued through the die attach, wire bonding and final room temperature electrical testing of mounted CCDs, as discussed in Section 3. These are areas in which their experience was essential in achieving a reliable product.

In order to accommodate the die attachment within the standard EEV operation procedures, it was necessary to develop a very well defined and straightforward assembly procedure. This was done by the SLD group, and the outcome was a set of jigs which could be used to carry out the following operations:

dispense eight controlled quantities

of adhesive in precise locations (automated adhesive dispenser, plus templates)

set CCD1 in position (spacers, template, weight for flat hold-down)

(vacuum hold-down)

precisely hold ladder substrate

after curing, wire bond CCD1 (standard deep access K&S bonder used for routine CCD wire bonding)

## repeat with ladder inverted for CCD2

These operations were backed up by QC procedures to verify the adhesive quality and quantity, to tune up and check the wire bonder settings, etc.

In order to meet the schedule, as many as eight assembly jigs were in use at one time, giving a throughput capacity of eight ladders per week. The wafer fab and die preparation facilities at EEV were able to produce tested devices at a rate matched to this. In practice, due to one or two initially low yielding batches, limitations in the supply of ladder motherboards, and a low but finite level of re-work due to CCDs rejected during the SLAC cold tests, the entire production of approximately 50 ladders at EEV occupied a period of 15 weeks.

#### 2.2.2 Electrical Details

Within the active regions of the ladders, the flex-circuits were reduced to the absolute minimal thickness, consisting of one kapton layer plus the copper traces connected at each end of the CCD, plus a kapton cover-layer. Over the outer 1 cm of ladder length, this flex-circuit was overlayed with a copper mesh ground plane, which extended (via the micro-connectors) to the outer stripline and from there to the front-end electronics board. This ground plane was essential in helping with the analogue/drive crosstalk reduction on the striplines, and it was found (not surprisingly) essential that this be continued along the length of the ladder. This was achieved by making a good connection (using conductive epoxy [17]) from the flex-circuit ground to the beryllium ladder substrate, in a region at each end of the ladder (see Fig. 7). Thus the south-end CCD on every ladder had its flex-circuit grounded to the inner surface of the motherboard, and the north-end CCD had its flex-circuit grounded to the outer surface of the motherboard. In order to make these connections, the completed ladders were removed from their transport boxes in a clean room, held carefully while the exposed beryllium surface was etched to improve electrical contact, and bonded with epoxy. After a short curing time under a heat lamp, the ladders were returned to their transport boxes and allowed to cure fully before testing. This epoxy procedure was not performed in the original motherboard fabrication because at that time it had not yet been shown to be necessary. There was some concern that having a common ground for the north and south front-end electronics could cause problems, but this has worked perfectly well.

Throughout the R&D and production phases, the crosstalk between the drive and analogue electronics caused some difficulties. The VXD3 design was in this respect more demanding than that for VXD2; the coupling between these two sets of signal paths all the way from the front-end electronics boards through the stripline/pigtails to the CCDs not surprisingly caused

problems. Achieving R drive pulses which were well balanced and which settled within 50 ns proved quite possible. The difficulty was that these 10 V pulses tended to induce long term ringing on the extremely sensitive analogue signal circuit. This is discussed further in Sections 5 and 7.

# 2.3 Detector Support Structure

The purpose of the support structure was primarily to hold the 48 ladders in the three-barrel assembly (Figs. 3-5). Beryllium was chosen for this structure (as also for the inner section of beam-pipe, the gas shell and the ladder substrates) because of its high elastic modulus  $(44.0 \times 10^6 \text{ psi})$  and its long radiation length (35.3 cm). Other options considered were carbon fibre (ruled out due to the anisotropy of a fibre matrix and due to the detector operating temperature) and aluminium (ruled out due to its serious micro-creep characteristics). As already mentioned the ladders (inherently quite flexible) were mechanically stabilized by the system of spring-loaded ceramic vee blocks (Fig. 8), with one end pinned and the other end free to slide in response to slight thermal variations within the detector. When these blocks were bonded with NuSil to the ladders (the 'ladder blocks') and to the beryllium rings or annuli (the 'annulus blocks'), jigs were used to ensure a minimal thickness glue line of 100  $\mu$ m. For the annulus blocks, a master ladder was used to locate them within the support structure while they were being bonded to the annuli. This assembly procedure allowed the adhesive to compensate for the buildup of manufacturing tolerances. All 18 parts of the support structure were linked by dowels located in match-reamed holes, clearance 5  $\mu$ m, and the mating surfaces were lapped flat to 1.3  $\mu$ m, to ensure stress-free repeatable assembly. This procedure relied on all mating surfaces being extremely clean. Naturally, with exposed CCDs in the detector, all assembly procedures were carried out in clean room conditions. However for the assembly of the support structure, particular additional cleaning procedures were necessary. Using mirrorcleaning techniques developed by laser scientists, the mating surfaces were always wiped clean and inspected before any mechanical assembly. Microscopic contaminants missed by the inspection procedure could be relied on to flatten or bed in to the mating surfaces when the relevant screws were tightened to the specified torque levels.

## 2.4 Detector-related Mechanical Equipment

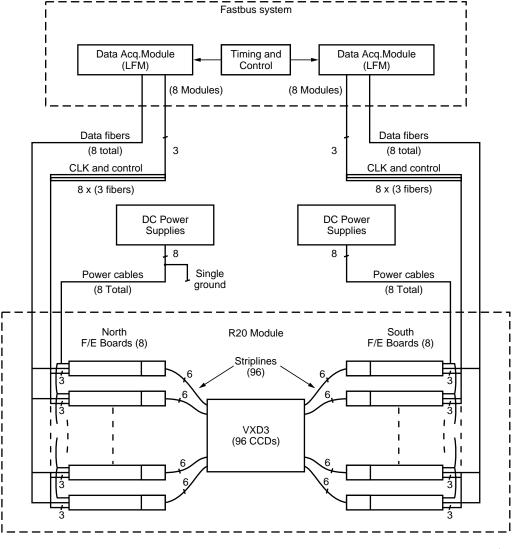

The equipment inside the inner bore of the CDC (of radius 20 cm, hence the 'R20 module') shown in Fig. 9, has the vertex detector at the centre of a two metre long vacuum chamber (the innermost section of SLC beam-pipe). This vacuum chamber is divided into five segments. The central, double-walled beryllium segment (beam-pipe and gas shell, see Fig. 4) of length 34 cm provides the support to which the detector is attached via a low-stress, three-point kinematic mounting system. This uses three small ceramic spheres in a cone/vee/flat

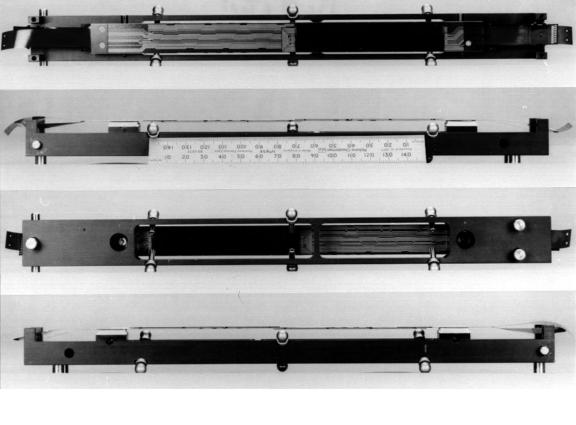

arrangement to provide a stable support while also absorbing thermal expansion differences between the beam-pipe and support structure. Engagement of the mounting system is preserved by light springs acting between these two structures. The vertex detector was divided into two halves to permit installation onto the R20 module in a clean room adjacent to the SLD detector, without disturbing the various flanges and bellows of the baked-out beam-pipe assembly in close proximity to the detector. Figure 10 shows the VXD3 upper module before mating to the lower module around the SLC beam-pipe.

The central section of beam-pipe is clamped to each end of the CDC inner barrel, as indicated in Fig. 9, by means of a pair of aluminium support cones. This system achieves excellent positional stability of the VXD relative to the CDC through long epochs of standard running conditions of SLC/D. Only between runs (when the end-doors of the detector are opened, disturbing the final focus system) or during runs when movements of the final focus quadrupoles or detector are deliberately made for beam tuning purposes, is there a significant disturbance to this alignment. As discussed in Section 4, the VXD/CDC relative alignment is continuously monitored by means of the detector position monitor system (shown also in Fig. 9).

Even door opening and final focus quadrupole motion has relatively little effect on the VXD alignment, since the sections of the SLC beam-pipe within the R20 region are coupled by compliant bellows systems. In particular the sections of vacuum chamber adjacent to the central beam-pipe are conical and float between two atmospherically balanced ten-convolution bellows. This linkage provides positioning freedom and seismic isolation. However, the heavy conical M3 masks which surround the beam-pipe (Fig. 9) are rigidly cantilevered from the final focus quadrupole cryostats north and south, and are therefore obliged to follow any movements of these systems.

The VXD/CDC link itself is not merely a passive clamp. It was necessary to allow for background tuning, including positioning of the critical M4 masks of radius 20 mm (see Fig. 4) which provide the final defence of the innermost beam-pipe from background. To allow this central section to be moved in x and y, it was linked to the CDC at each end by means of a three-point clamp, two of which were adjustable by remotely operated jacks.

#### 2.5 Cryostat and Cooling System

The main requirements of the cooling system are to establish the desired operating temperature for the detector, and to maintain the CCDs reasonably close to this temperature when all ladders are electrically powered and being read out at full speed.

As discussed in Section 1.2, the operating temperature of a CCD detector for HEP applications is determined by the need to minimize radiation-induced degradation in charge transfer efficiency. Choosing a sufficiently low operating temperature results (under the conditions of background charge present in the detector) in effective suppression of the electron traps induced by displacement damage in the buried channel of the device.

The most critical requirement for the coolant gas is that it be of extremely low humidity. Ice formation on the detector could cause numerous problems. The same system is used as for VXD2, and uses liquid nitrogen from the SLD main supply at 40 psi. On demand, this is used to fill a small primary dewar at atmospheric pressure, in which the newly supplied liquid boils vigorously for a short time, as its temperature falls to its boiling point at atmospheric pressure. The quiescent liquid in the primary dewar is used (on demand of a level sensing system) to top up a tall (approximately 2 metre) secondary dewar mounted at a lower level, which is also open to atmospheric pressure above the liquid level. By maintaining the level in the tall dewar constant to  $\pm$  5%, it is possible to obtain a steady flow of liquid from the base of this dewar via a needle valve set to deliver the appropriate rate of approximately 1 g/s to a two-stage boiler system. This consists of two copper cans mounted in a vacuum enclosure, each filled with mesh for good thermal conduction, and wrapped externally with heating tapes. The average power dissipation of the lower can is continually adjusted so as to boil the liquid and raise the temperature of the gas to 85 K in a hardware-controlled feedback loop. The power dissipation of the second can is similarly controlled by a feedback loop to raise the temperature of the exit gas to a set value of around 135 K.

This cooling system is located outside the SLD detector, and the gas is fed in to the vertex detector using a series of linked stainless steel vacuum-jacketed cryo pipes. To achieve a sufficiently low heat leak, these pipes need to be pumped continuously. Minor vacuum leaks which would create negligible thermal leakage in pipes used for liquid transfer, could create a seriously excessive temperature rise in the slow moving coolant gas, and had to be eliminated. For VXD2, the vacuum jacketed pipes continued all the way to the cryostat. In the case of VXD3, the final section of pipe within the CDC barrel, which encroached slightly within the polar angle aperture of the endcap tracking system, was changed to a very low mass foam-jacketed aluminium pipe. The foam material used (as for the cryostat itself) is a polyisocyanurate material using HCDC 141B as filler gas [18]. This pipe had much worse thermal insulation properties than the vacuum jacketed pipes, but over this short length (approximately 1 m out of 15 m total) this resulted in an acceptable heat load on the inlet coolant gas, simply necessitating a somewhat lower temperature setting for the upper heater can of the supply system than was used for VXD2.

The one metre long inlet pipe to the cryostat (see Fig. 9) is sealed with flexible rubber at each end, thus allowing the vertex detector and cryostat (both of which are firmly attached to the inner section of beam-pipe carrying the M4 masks) to be freely translated by the R20 jack system for beam tuning. The inner (aluminium) section of the inlet pipe enters the cryostat, where it is flexibly coupled to the gas shell with a bellows linkage. The inlet gas thus pressurizes the thin cylindrical volume between the beam-pipe and the gas shell, which is sealed, apart from an array of 72 small holes through which jets of coolant gas emerge radially into the detector volume. This gas streams out over the ladders from Barrel 1 to Barrel 3, between the neighbouring ladders within each barrel, and then out through the holes in the support shell. Only a small percentage emerges through the end-plates of the support structure. Finally, after absorbing additional heat flowing in through the walls of the cryostat, the gas exits through the south cryo pipe system (similar to the inlet pipe system on the north, but with larger diameter and/or triple pipes to minimize the overpressure in the delicate cryostat).

The exit gas is led through an electrical heater on the outer periphery of the detector, returning the temperature to 20 C, after which the flow rate and humidity are monitored before the gas is released locally to the atmosphere.

The six sections of the cryostat (two half end-plates each end, and two half cylinders above and below) are sealed with NuSil adhesive. These sealed joints are penetrated by 48 striplines each end and by the beam-pipe. The joints incorporate heater wires near their outer edges, used to maintain them at a sufficient temperature to guarantee freedom from condensation on the outer surface of the cryostat. This is easily achieved, since the R20 volume is moderately well sealed at each end with plastic and adhesive tape, and is blown with dry nitrogen at room temperature. Hence the dew point in this enclosure is normally extremely low (around -20 C). The largest heat leak into the cryostat is due to the beam-pipe (which changes from beryllium to thin stainless steel at a brazed joint at  $|z| \approx 15$  cm). By using extra turns of heater wire round the beam-pipe, its temperature at the outer wall of the cryostat can be maintained at approximately 15 C, entirely adequate to avoid condensation or damage to adjacent delicate equipment, a wire beam-position monitor on the south end, and a laser beam-size monitor on the north (Fig. 9).

The cryostat assembly also provides a re-entrant Faraday cage system (see Fig. 4) that screens the detector from RF associated with the beam current, any other signals coupled to the beampipe, or pickup from other electronics within the SLD enclosure. It should be noted that, as regards external sources of electrical interference, the heart of SLD is much quieter than a typical unshielded laboratory; the magnet and the 4000 ton iron flux return provides a highly effective electromagnetic shield. The elements on the Faraday cage begin with the beryllium gas shell which is isolated electrically from the beam-pipe. The gas shell is connected at each end by a series of aluminium fingers (complete in azimuth) to the end-plates of the cryostat,

which are faced with 0.5 mm thick aluminium. The upper and lower sections of these plates are electrically connected by thin copper jumpers. Similarly, the upper and lower cryostat barrel sections are faced with thin aluminium sheet and electrically linked together with compressible conductive tubing along the length of the barrel. Wires from these three sections of the Faraday cage penetrate the cryostat axially at each end, resulting in a ring of wires from the end-plates inside the radius of the emerging strip-lines, and another ring of wires from the barrel section outside this area. The striplines themselves are sheathed in grounded mesh screens, to which these wires are connected. In this way the Faraday cage is extended to the front-end electronics (see Fig. 9), where a more or less complete set of plates continues the shielding around the electronics. These connections continue on sheaths around the power supply cables (one per front-end board) leading to the power supplies on the periphery of SLD. Those on the south are left floating at the power supply end, whereas those on the north are grounded to the steel frame of the counting house, which is a solid external detector ground. Care was taken to ensure that the Faraday cage system is electrically floating other than for this single point ground connection.

# 3 CCD Design and Production

The development of the CCDs for the detector was initiated by informal discussions with a number of manufacturers to establish reasonable goals for all the key parameters, based on their experience with manufacturing scientific grade devices. This was followed by a detailed design specification, care being taken not to write in requirements that were only available from one or two manufacturers. In parallel with this, interested manufacturers were requested to supply 'engineering grade' devices for evaluation. This involved a considerable amount of testing by the SLD Collaboration, and also demanded a sufficiently flexible drive and readout system to be able to handle device types quite different from those eventually required. As it turned out, this testing period was extremely important since it revealed several unfamiliar types of defects, as a result of which the detailed specification was considerably tightened.

The Request for Production (RFP) divided the project into two phases. The first phase (prototype design and manufacture) resulted in a small number of devices for detailed testing. This was followed by the production phase of approximately 100 devices. In order to avoid the high charges made by all CCD manufacturers for performing detailed low temperature tests on their devices, the RFP specified that the devices should only have been screened for reasonable room temperature images before delivery. This streamlined test procedure minimized the cost of manufacture, but the RFP included the condition that devices found not to satisfy the stringent cold test requirements should be replaced without cost. In practice, the failure rate was low, so this procedure worked out extremely well. Of the 12 manufacturers originally approached, four produced estimates for an early Budgetary Inquiry, and three remained to bid against the RFP. The award of the contract was driven less by the cost of design and prototyping than by the quoted production costs, which varied by a factor of two among the different manufacturers.

# 3.1 Design Specifications

The RFP specified the design requirements for the imaging area, readout area, output amplifier, wire bonding and radiation hardness. It also requested the bidders to respond with their own estimates of the critical parameters for their particular fabrication processes. This response (in the case of the successful bidder, EEV) evolved into the detailed CCD design specification during the prototype design process. It was pleasing to discover that in almost all cases the parameters that emerged from detailed design studies were superior to those specified in the original RFP.

The buried channel CCD was manufactured on a  $p^+$  substrate of resistivity less than 20 m $\Omega$  cm (for short carrier lifetime). This was covered by a 20  $\mu$ m thick, p-type epitaxial

layer of resistivity  $20~\Omega$  cm, with charge collection into an n-channel by a combination of drift and diffusion. With  $20\times20~\mu\text{m}^2$  pixels, the effective detector element is a cube of volume  $(20~\mu\text{m})^3$ , the  $p/p^+$  interface providing a 100% reflective surface for signal electrons diffusing within the epitaxial layer [8]. The 650  $\mu$ m thick inactive  $p^+$  substrate was mechanically lapped down to  $180\pm20~\mu$ m overall device thickness by the manufacturer after dicing, in order to achieve an adequately low degradation in tracking precision due to multiple scattering.

Other than the bond pads and fiducial marks (described later) the top CCD surface was protected in the final stage of processing by a polyimide layer of thickness approximately  $2 \mu m$ .

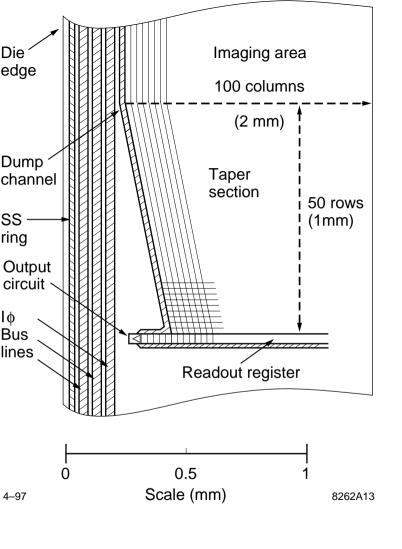

The CCD type number was CCD32, the general layout of which is shown in Fig. 11. This design is of conventional stitched format with six 'middle' sections, and the readout circuitry in two 'end' sections. The image section bus lines (see Fig. 12) are continuous along the full length of the array with the opposite directions of change transfer being achieved by changing the polysilicon electrodes sequence. The image sections have a 3-phase clock configuration, whereas the readout registers at each end are of 2-phase configuration for high speed clocking with minimal feedthrough to the analogue outputs. Standard anti-static gate protection devices were incorporated.

In each corner of the array the pitch of the outermost 100 columns (2 mm wide) tapers down from 20  $\mu$ m to 18  $\mu$ m over a length of 1 mm (50 rows) to give room for the charge detection amplifiers and six blank register run-off elements, as shown schematically in Fig. 12. With a single 'dump' column provided to drain off any peripheral-generated charge, in the main part of the array the distance between the edge of the outermost pixel and the substrate ring is 215  $\mu$ m. By positioning the saw cut off-centre in the 200  $\mu$ m wide 'scribe channel', the specified edge spacing of less than 300  $\mu$ m from the edge of the sensitive area to the edge of the die was achieved in all cases.

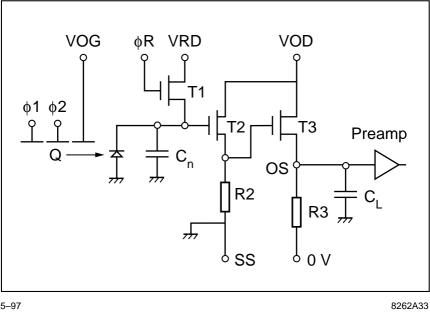

The design of the output amplifier is shown schematically in Fig. 13. A two-stage direct-coupled circuit is employed. The node capacitance is minimized to achieve highest responsivity. The various circuit capacitances are adjusted to give both sufficient bandwidth and adequate damping with the system load capacitance  $C_L$  of 40 pF. The second-stage load resistor R3 is off-chip, on the front-end electronics board, to minimize power dissipation inside the detector cryostat. For the production CCDs, the first and second stage transistors were both surface channel devices.

Fiducial marks, in the form of a 56  $\mu$ m squares of metallization, were provided at intervals of 3 mm horizontally and 2.5 mm vertically within the sensitive area of the device. Windows were left in the polyimide surface passivation in order to allow a clear view of the metal edges, free of any distortions that could be induced by a transparent cover layer of uncertain topography.

The performance parameters estimated by the manufacturer on the basis of simulations, or measurements of similar devices, are summarized in Table 4. Some key features of the three most important sections are as follows.

## 3.1.1 Imaging Area

The total well capacity of the pixel is  $3.5 \times 10^5 \, \mathrm{e^-}$ , more than adequate for min-I and all probable background hits. With drive pulse connections in all four corners of the chip, imaging area transfer rates well in excess of 200 kHz (pixel to pixel) could be achieved, more than adequate for any fast clear requirements in this detector. The associated power dissipation on chip (for 10 V clock drive pulses) is 1.3 W for continuous 200 kHz operation, approximately half of the originally specified maximum.

# 3.1.2 Readout Register

The charge storage capacity for the 2-phase readout register is  $4 \times 10^5$  e<sup>-</sup>. With 10 MHz drive pulses, 20 ns rise and fall times, there is negligible waveform degradation along the length of the register bus. With 10 V clock amplitude, the on-chip power dissipation is 25 mW per register (with two registers per CCD), 10 times lower than in the original specification.

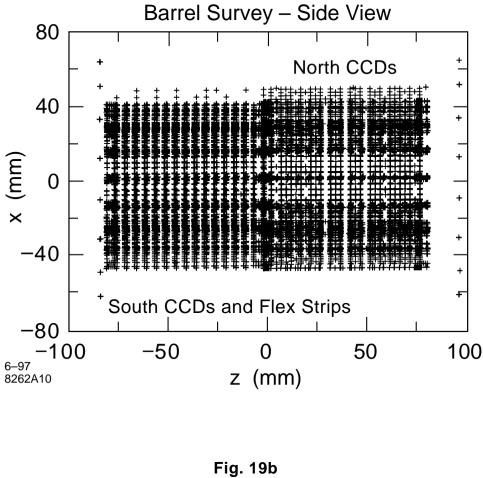

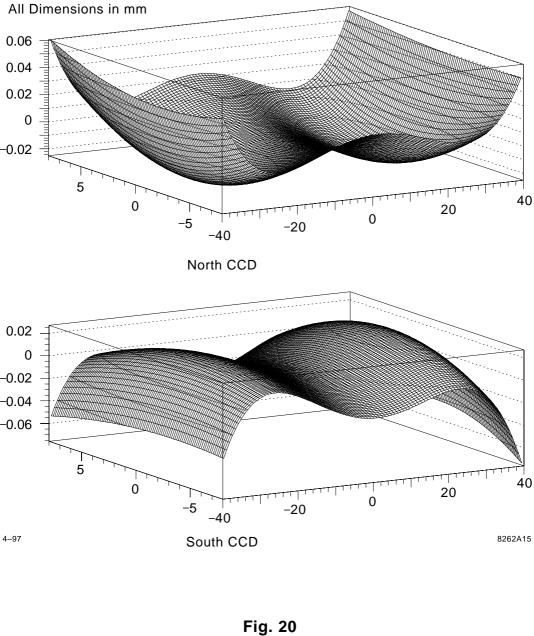

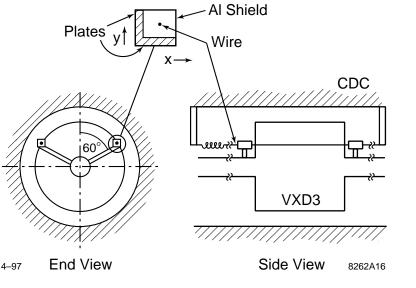

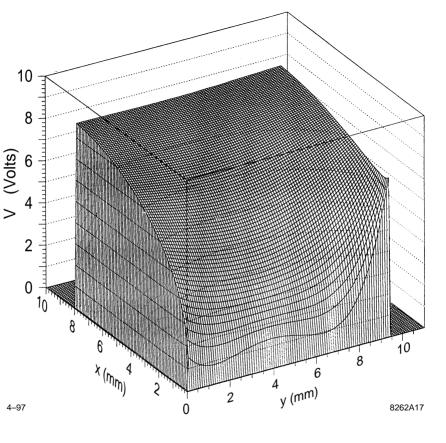

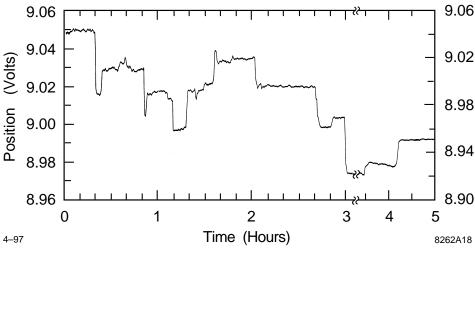

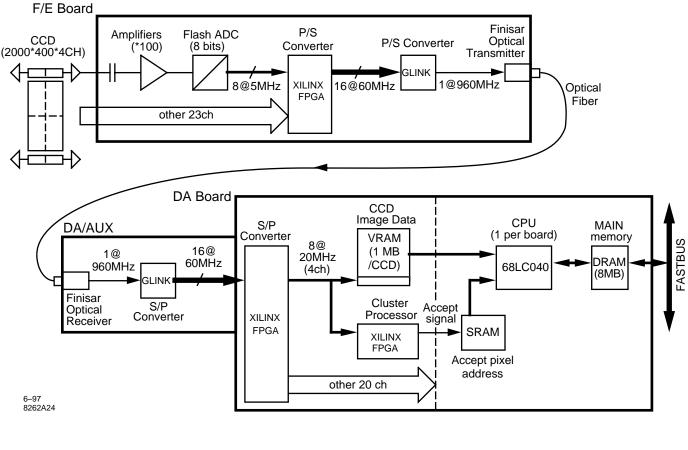

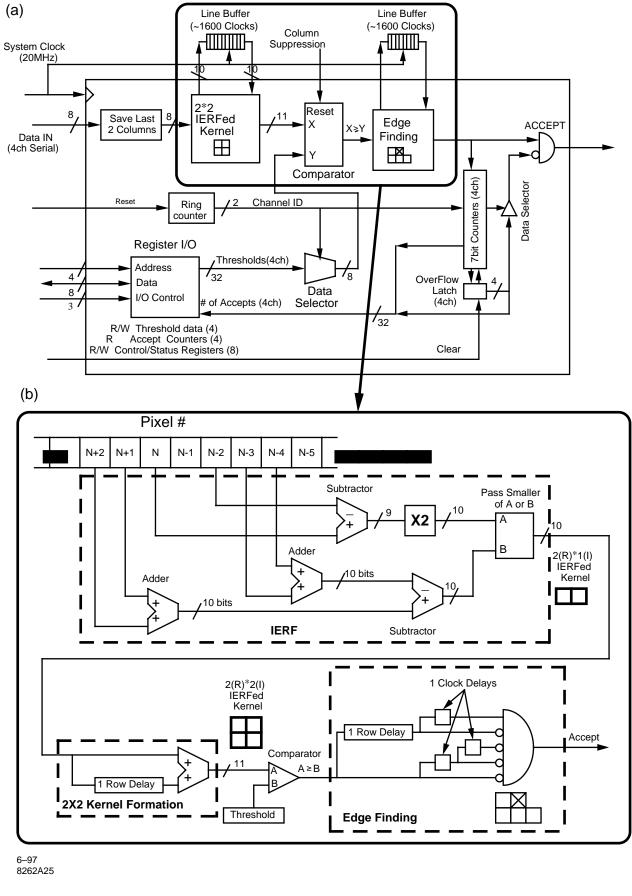

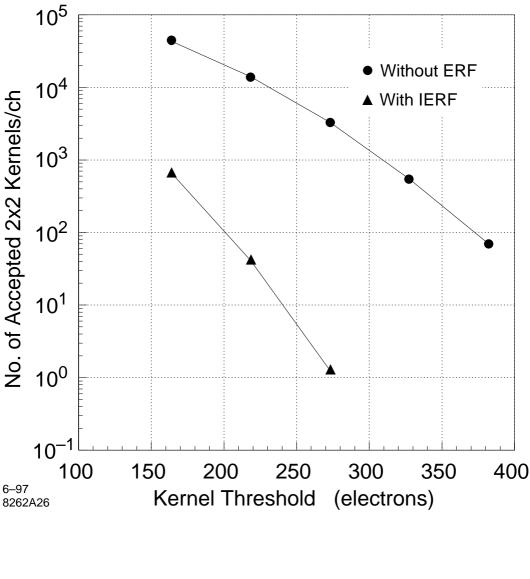

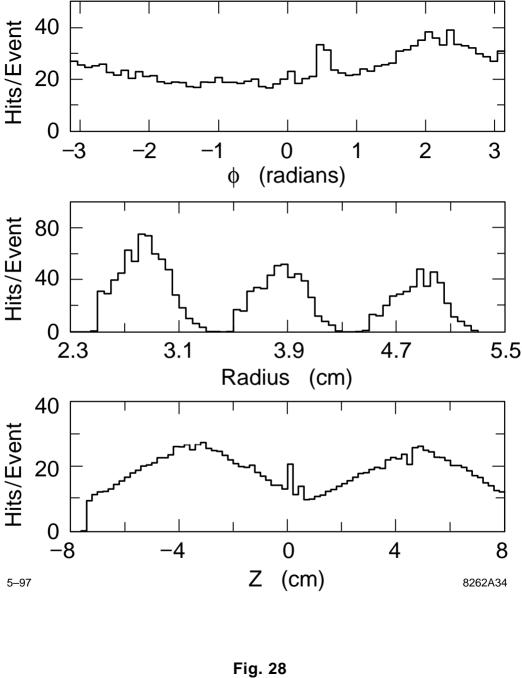

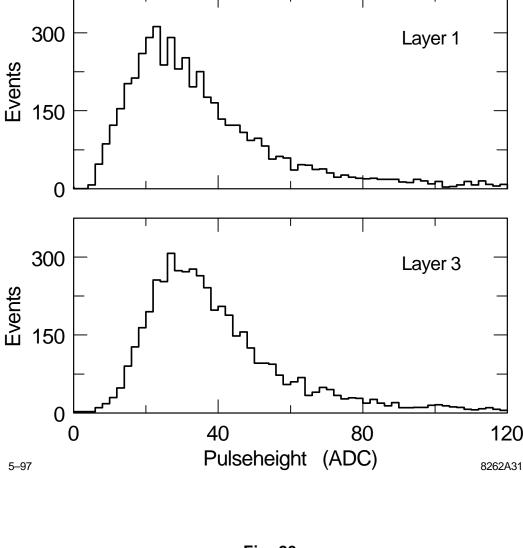

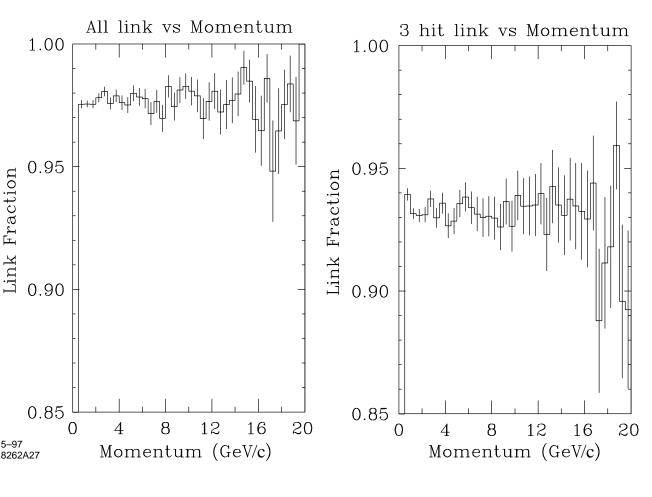

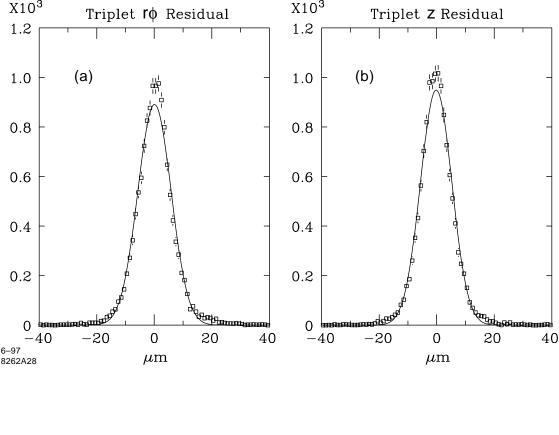

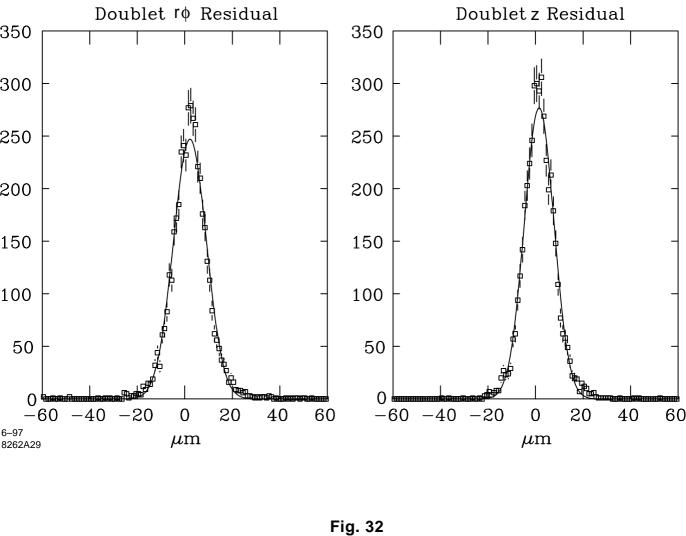

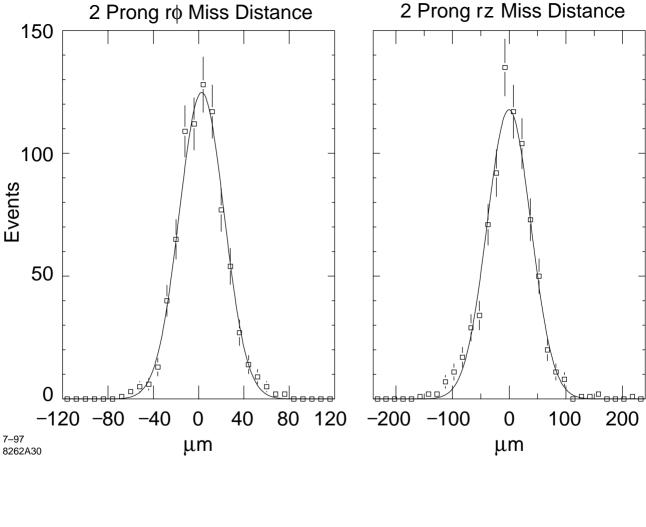

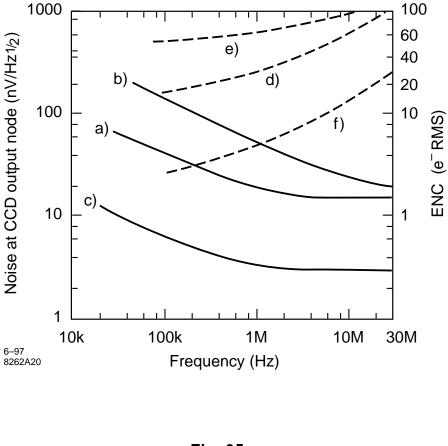

#### 3.1.3 Output Amplifier