RECEIVED: May 29, 2024

REVISED: November 6, 2024

ACCEPTED: February 7, 2025

PUBLISHED: March 19, 2025

# RD53 pixel readout integrated circuits for ATLAS and CMS HL-LHC upgrades

## The RD53 collaboration

G. Alimonti,<sup>11</sup> A. Andreazza,<sup>11</sup> F. Arteche,<sup>22</sup> M.B. Barbero,<sup>1</sup> P. Barrillon,<sup>1</sup> R. Beccherle,<sup>16</sup> G. Bonomelli,<sup>20</sup> G.M. Bilei,<sup>15</sup> W. Bialas,<sup>3</sup> D. Bortoletto,<sup>5</sup> G. Calderini,<sup>26</sup> A. Caratelli,<sup>3</sup> A. Cassese,<sup>9</sup> J. Christiansen,<sup>3,\*</sup> E. Conti,<sup>3,15</sup> F. Crescioli,<sup>26</sup> M. Daas,<sup>35</sup> L. Damenti,<sup>9,10</sup> S.D'Auria,<sup>11</sup> F. De Canio,<sup>13</sup> G. De Robertis,<sup>8</sup> N. Demaria,<sup>17</sup> J. DeWitt,<sup>31</sup> Y. Dieter,<sup>35</sup> A. Dimitrievska,<sup>25</sup> W. Erdmann,<sup>29</sup> S. Esposito,<sup>3</sup> D. Exarchou,<sup>3</sup> D. Fougeron,<sup>1</sup> L. Gaioni,<sup>13</sup> M. Garcia-Sciveres,<sup>25</sup> D. Gnani,<sup>25</sup> C. Gozalez Renteria,<sup>36</sup> M. Grippo,<sup>17,18</sup> A. Guardino,<sup>36</sup> M. Hamer,<sup>35</sup> T. Heim,<sup>25</sup> T. Hemperek,<sup>35</sup> F. Hinterkeuser,<sup>35</sup> S. Huiberts,<sup>34</sup> L.M. Jara Casas,<sup>3</sup> J.J. John,<sup>5</sup> J. Kampkötter,<sup>33</sup> M. Karagounis,<sup>33</sup> I. Kazas,<sup>27</sup> Y. Khwaira,<sup>23</sup> R. Kluit,<sup>28</sup> D. Koukola,<sup>3</sup> A. Krieger,<sup>25</sup> H. Krüger,<sup>35</sup> J. Lalic,<sup>3</sup> M. Lauritzen,<sup>34</sup> F. Licciulli,<sup>8</sup> Peilian Liu,<sup>21</sup> F. Loddo,<sup>8</sup> E. Lopez Morillo,<sup>6</sup> A. Lounis,<sup>23</sup> F. Luongo,<sup>17,18</sup> M. Manghisoni,<sup>13</sup> S. Marconi,<sup>3,15</sup> F. Marquez Lasso,<sup>6</sup> C. Marzocca,<sup>30</sup> K. Mauer,<sup>35</sup> A. Mekkaoui,<sup>4</sup> Lingxin Meng,<sup>24</sup> M. Menichelli,<sup>15</sup> M. Menouni,<sup>1</sup> M. Minuti,<sup>16</sup> M. Mironova,<sup>25</sup> S. Miryala,<sup>2</sup> M. Missiroli,<sup>29,32</sup> E. Monteil,<sup>17,18</sup> K. Moustakas,<sup>35</sup> F. Muñoz Chavero,<sup>6</sup> G. Neue,<sup>7</sup> S. Orfanelli,<sup>3</sup> A. Paccagnella,<sup>12</sup> L. Pacher,<sup>17,18</sup> F. Palla,<sup>16</sup> F.R. Palomo Pinto,<sup>6</sup> A. Papadopoulou,<sup>25</sup> A. Paterno,<sup>17,18</sup> A.R. Petri,<sup>11</sup> P. Placidi,<sup>15</sup> R. Plackett,<sup>5</sup> A. Pradas,<sup>22</sup> A. Pulli,<sup>3</sup> B. Raciti,<sup>19</sup> L. Ratti,<sup>14</sup> V. Re,<sup>13</sup> A. Rehman,<sup>34</sup> P. Rymaszewski,<sup>35</sup> P. Sander,<sup>20</sup> M.C. Solal,<sup>23</sup> M. Standke,<sup>35</sup> B. Stugu,<sup>34</sup> E. Thompson,<sup>25</sup> G. Traversi,<sup>13</sup> D. Vogrig,<sup>12</sup> M. Vogt,<sup>35</sup> Tianyang Wang,<sup>35</sup> Hongtao Yang<sup>37</sup> and J. Zdenko<sup>7</sup>

<sup>1</sup>Aix Marseille Université, CNRS/IN2P3, CPPM, Marseille, France

<sup>2</sup>Brookhaven National Laboratory, Upton, NY, U.S.A.

<sup>3</sup>CERN, European Organization for Nuclear Research, Geneva, Switzerland

<sup>4</sup>Clevert Systems LLC, West Henrietta, NY, U.S.A.

<sup>5</sup>Dept. of Physics, Oxford University, Oxford, United Kingdom

<sup>6</sup>ETSI, Universidad de Sevilla, Sevilla, Spain

<sup>7</sup>Faculty of Nuclear Sciences and Physical Engineering, Czech Technical University in Prague, Prague, Czech Republic

<sup>8</sup>INFN Sezione di Bari, Bari, Italy

<sup>9</sup>INFN Sezione di Firenze, Florence, Italy

<sup>10</sup>Università di Firenze, Florence, Italy

\*Corresponding author.

<sup>11</sup>*INFN Sezione di Milano and Università degli Studi di Milano, Milano, Italy*

<sup>12</sup>*INFN Sezione di Padova and Università di Padova, Padova, Italy*

<sup>13</sup>*INFN Sezione di Pavia and Università di Bergamo, Bergamo, Italy*

<sup>14</sup>*INFN Sezione di Pavia and Università di Pavia, Pavia, Italy*

<sup>15</sup>*INFN Sezione di Perugia and Università di Perugia, Perugia, Italy*

<sup>16</sup>*INFN Sezione di Pisa, Pisa, Italy*

<sup>17</sup>*INFN Sezione di Torino, Torino, Italy*

<sup>18</sup>*Università di Torino, Torino, Italy*

<sup>19</sup>*Institut für Experimentalphysik, Universität Hamburg, Hamburg, Germany*

<sup>20</sup>*Institute for Particle Physics, ETH, Zurich, Switzerland*

<sup>21</sup>*Institute of High Energy Physics, Beijing, People's Republic of China*

<sup>22</sup>*Instituto Tecnológico de Aragón, Zaragoza, Spain*

<sup>23</sup>*Laboratoire de Physique des 2 Infinis Irène Joliot Curie, Orsay, CNRS / Université Paris-Saclay, Paris, France*

<sup>24</sup>*Lancaster University, Lancaster, United Kingdom*

<sup>25</sup>*Lawrence Berkeley National Laboratory, Berkeley, CA, U.S.A.*

<sup>26</sup>*LPNHE, Sorbonne Université, Université Paris Cité, CNRS, Paris, France*

<sup>27</sup>*National Center for Scientific Research, DEMOKRITOS, Agia Paraskevi, Greece*

<sup>28</sup>*National Institute for Subatomic Physics (NIKHEF), Amsterdam, Netherlands*

<sup>29</sup>*Paul Scherrer Institut, Villigen, Switzerland*

<sup>30</sup>*Politecnico di Bari, Bari, Italy*

<sup>31</sup>*SCIPP, University of California, Santa Cruz, CA, U.S.A.*

<sup>32</sup>*Universität Zürich, Zürich, Switzerland*

<sup>33</sup>*University of Applied Sciences and Arts Dortmund, Dortmund, Germany*

<sup>34</sup>*University of Bergen, Bergen, Norway*

<sup>35</sup>*University of Bonn, Bonn, Germany*

<sup>36</sup>*University of California, Berkeley, CA, U.S.A.*

<sup>37</sup>*University of Science and Technology of China, Hefei, China*

*E-mail:* [jorgen.christiansen@cern.ch](mailto:jorgen.christiansen@cern.ch)

**ABSTRACT.** The RD53 collaboration has since 2013 developed new hybrid pixel detector chips with  $50 \times 50 \mu\text{m}^2$  pixels for the HL-LHC upgrades of the ATLAS and CMS experiments at CERN. A common architecture, design and verification framework has been developed to enable final pixel chips of different sizes to be designed, verified and tested to handle extreme hit rates of  $3 \text{ GHz/cm}^2$  (up to  $12 \text{ GHz}$  per chip) together with an increased trigger rate of  $1 \text{ MHz}$  and efficient readout of up to  $5.12 \text{ Gbits/s}$  per pixel chip. Tolerance to an extremely hostile radiation environment with 1 Grad over 10 years and induced SEU (Single Event Upset) rates of up to 100 upsets per second per chip have been major challenges to make reliable pixel chips. Three generations of pixel chips, and many specific mixed signal building blocks and radiation test chips, have been submitted and extensively tested to get to final production chips. The large, complex and high rate pixel chips have been developed with a strong emphasis on low power consumption together with a concurrent development and qualification of novel serial powering at chip, module and system level, to minimize detector material budget.

**KEYWORDS:** Front-end electronics for detector readout; Particle tracking detectors (Solid-state detectors); Radiation-hard electronics; VLSI circuits

---

## Contents

|           |                                               |           |

|-----------|-----------------------------------------------|-----------|

| <b>1</b>  | <b>Introduction and requirements</b>          | <b>1</b>  |

| <b>2</b>  | <b>Pixel detector system</b>                  | <b>6</b>  |

| <b>3</b>  | <b>Chip architecture</b>                      | <b>8</b>  |

| <b>4</b>  | <b>Analog front-ends and hit digitization</b> | <b>10</b> |

| 4.1       | CMS Linear front-end                          | 19        |

| 4.2       | ATLAS differential front-end                  | 24        |

| <b>5</b>  | <b>Data buffering and triggering</b>          | <b>29</b> |

| <b>6</b>  | <b>Control and readout</b>                    | <b>33</b> |

| <b>7</b>  | <b>Power and references</b>                   | <b>37</b> |

| <b>8</b>  | <b>Monitoring</b>                             | <b>45</b> |

| <b>9</b>  | <b>Radiation tolerance</b>                    | <b>46</b> |

| <b>10</b> | <b>Implementation</b>                         | <b>52</b> |

| <b>11</b> | <b>Verification</b>                           | <b>56</b> |

| <b>12</b> | <b>Test and characterization</b>              | <b>59</b> |

| <b>13</b> | <b>Conclusions</b>                            | <b>63</b> |

---

## 1 Introduction and requirements

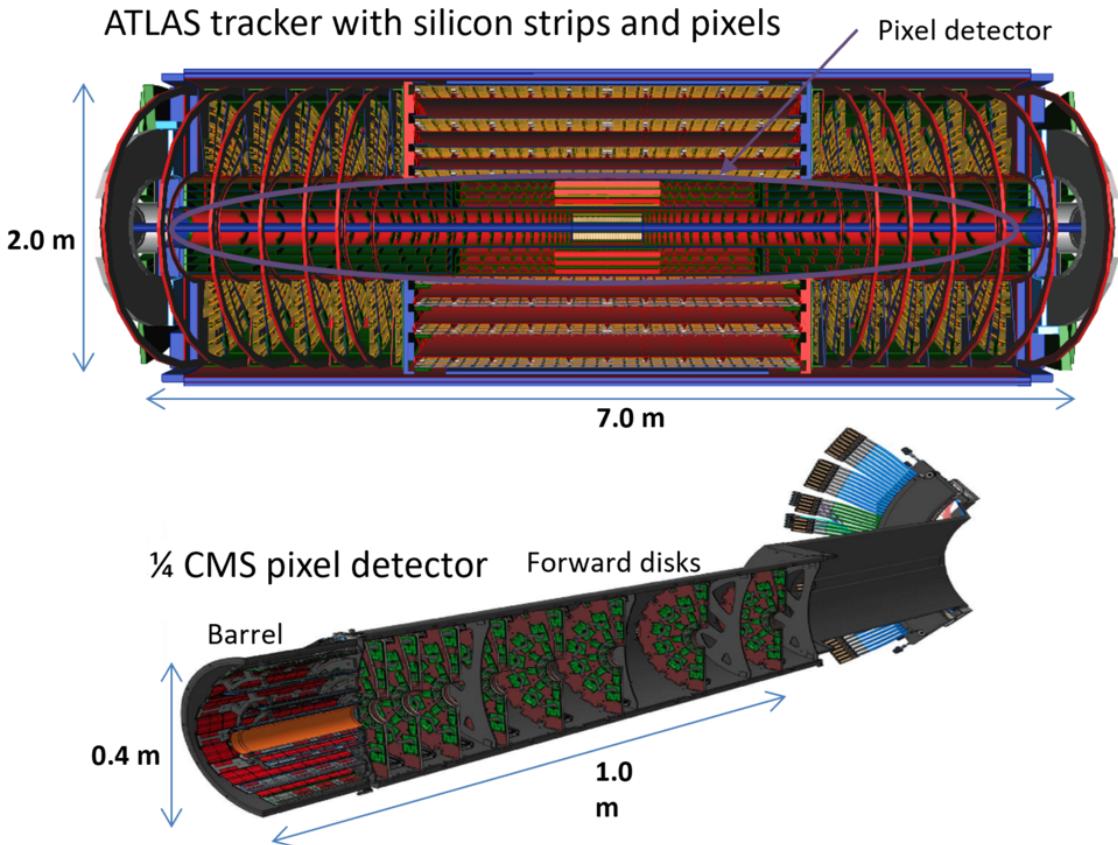

This paper gives an overview of the general requirements, design, architecture and measured performance of the RD53 pixel chips, developed for the ATLAS and CMS High Luminosity Large Hadron Collider (HL-LHC) upgrades. This development has been a major effort by a large number of people ( $\sim 100$ ) over 10 years. The RD53 collaboration [1], with 24 institutes, was established in 2013 to develop the required hybrid pixel detector readout integrated circuits for the ATLAS [2] and CMS [3] pixel detector upgrades for the HL-LHC. The two experiments have very similar requirements to their pixel detector upgrades and both are using lpGBT (low power GigaBit Transceiver) links [4] for control and readout. It was therefore agreed to do such a challenging chip development in common among ATLAS and CMS pixel detector groups with ASIC design and test experience. A common architecture, design and verification framework has been developed to make final production pixel chips, with slightly different chip sizes to enable optimal integration into the two pixel detector systems. The general layout of the ATLAS and CMS pixel detectors are indicated in figure 1.

**Figure 1.** Upper: ATLAS tracker layout with pixel detector at its centre. Lower: one quarter of CMS pixel detector layout. The pixel detectors are highly compact at the center of the experiments with critical material budget and difficult access. Both detectors are constructed from overlapping ladders/staves of multi (2,3 or 4) chip pixel modules for the central barrel part and concentric rings for the forward regions. Inner layers are specifically constructed to enable partial replacement during long shutdowns, in case of significant performance degradation from radiation damage in pixel sensors or pixel chips.

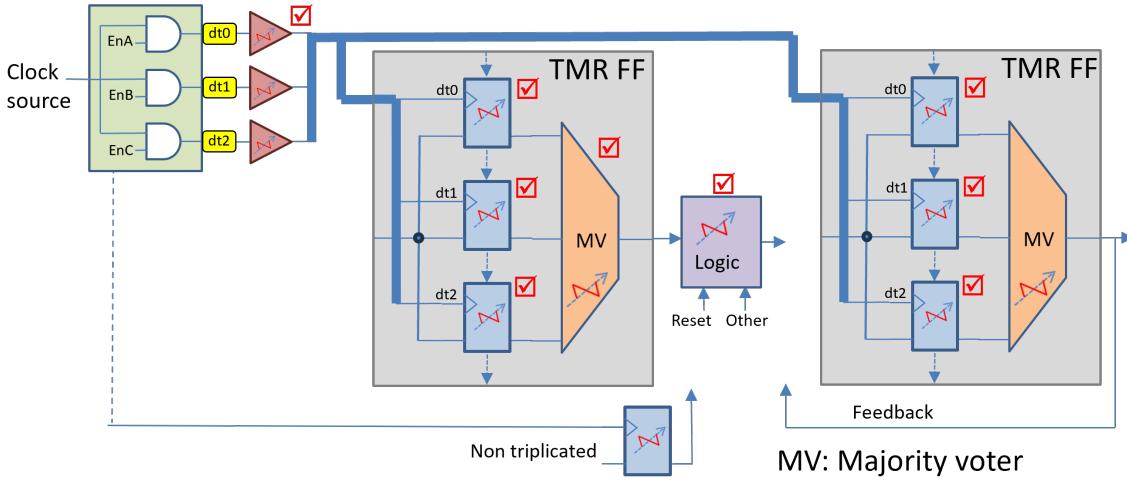

RD53 chips have been developed to meet the stringent rate and radiation requirements for operation at the HL-LHC, projected to begin operation in 2030. The HL-LHC will operate at an instantaneous luminosity of up to  $7.5 \times 10^{34} \text{ cm}^{-2}\text{s}^{-1}$  corresponding to an average pileup of 200 inelastic proton-proton collisions per bunch crossing. This translates into an average pixel hit rate of up to  $3 \text{ GHz/cm}^2$  in the innermost pixel layer at the 40 MHz bunch crossing rate. Inner pixel layers will have to work reliably in an extremely hostile radiation environment with up to 1 Grad Total Ionizing Dose (TID) and a Non Ionizing Energy Loss (NIEL) dose of  $10^{16} \text{ 1 MeV n}_{\text{eq}} \text{ cm}^{-2}$  over 10 years operation. It is assumed that innermost pixel layer(s) will possibly need replacement after 5-10 years, depending on the actual integrated luminosity and pixel sensor and chip performance degradation. The integration of the pixel detectors in the experiments has been made to enable partial replacement of inner pixel layer(s). The extreme radiation levels require the pixel chip design to be made with a strong emphasis on rad-hard design and effective SEE (Single Event Effects) protection. An inner layer pixel chip can be estimated to have up to 100 Hz of SEUs (Single Event Upsets) and SETs (Single Event Transients) and must function reliably despite these upsets in its internal data buffers,

state-machines and configuration registers. This unprecedented radiation tolerance requirement is a factor  $\sim 10$  higher than what has previously been made for High Energy Physics (HEP) applications and a factor  $\sim 10,000$  higher than normally required for rad-hard space applications.

The general chip requirements are outlined in table 1. The RD53 chip will be bump-bonded to sensors with a pixel size of  $50 \times 50 \mu\text{m}^2$  in the forward layers and  $25 \times 100 \mu\text{m}^2$  in the central barrel layers. These sizes are  $\sim 4$  times smaller than in previous generation ATLAS and CMS pixel sensors. This combined with the increased hit rate (factor  $\sim 4$ ) and extended trigger latency (factor  $\sim 2$ ) implies that effective trigger latency hit buffering has been increased by a factor of more than 10 compared to current ATLAS [7] and CMS [8] pixel detectors. The increased trigger rate, from 100 kHz to 1 MHz, combined with higher hit rate and smaller pixels implies that effective readout bandwidth is increased by a factor  $\sim 100$ , maintaining a 4 bit charge measurement per pixel hit. Requirements for pixel sensor capacitance and radiation induced leakage together with appropriate charge detection threshold have been determined from scaling from previous pixel detectors and measurements on pixel sensor prototypes in the two experiments.

| Parameter                    | Value (CMS/ATLAS )                                    |

|------------------------------|-------------------------------------------------------|

| Technology                   | 65 nm CMOS                                            |

| Max. hit rate                | 3.0 GHz/cm <sup>2</sup>                               |

| Trigger rate                 | 750 kHz / 1 MHz                                       |

| Trigger latency              | 12.5 $\mu\text{s}$                                    |

| Pixel size (chip)            | 50 x 50 $\mu\text{m}^2$                               |

| Pixel size (sensor)          | 50 x 50 $\mu\text{m}^2$ or 25 x 100 $\mu\text{m}^2$   |

| Pixel array                  | 432 x 336 pixels / 400 x 384 pixels                   |

| Chip dimensions              | 21.6 x 18.6 mm <sup>2</sup> / 20 x 21 mm <sup>2</sup> |

| Detector capacitance         | < 100 fF (200fF for edge pixels)                      |

| Detector leakage             | < 10 nA (20nA for edge pixels)                        |

| Min. threshold               | 1000 e-                                               |

| Threshold spread             | < 100 e- RMS                                          |

| Calibration pulse resolution | 10 e-                                                 |

| Noise                        | < 150 e- RMS, with sensor                             |

| Charge measurement           | 4 bit TOT, max 1% deadtime at 3.0 GHz/cm <sup>2</sup> |

| Radiation tolerance          | 1 Grad over 10 years at -15°C                         |

| SEE tolerance                | SEU rate, innermost: ~100Hz/chip                      |

| Power                        | < 1W/cm <sup>2</sup> , Serial powering                |

| Readout data rate            | 1-4 links @ 1.28Gbits/s = max 5.12 Gbits/s            |

| Temperature range            | -40°C ÷ 40°C (Nominal operation=-20°C ÷ -10°C)        |

**Table 1.** General requirements to RD53 pixel chips for use in ATLAS and CMS pixel detectors at HL-LHC.

At the pixel detector level it is critical to keep the material budget of pixel detector modules and related services as small as possible, so as not to deteriorate significantly tracking performance

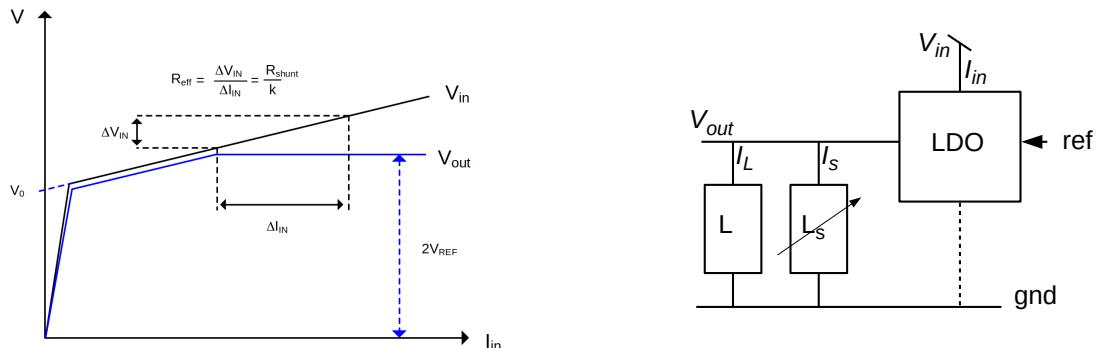

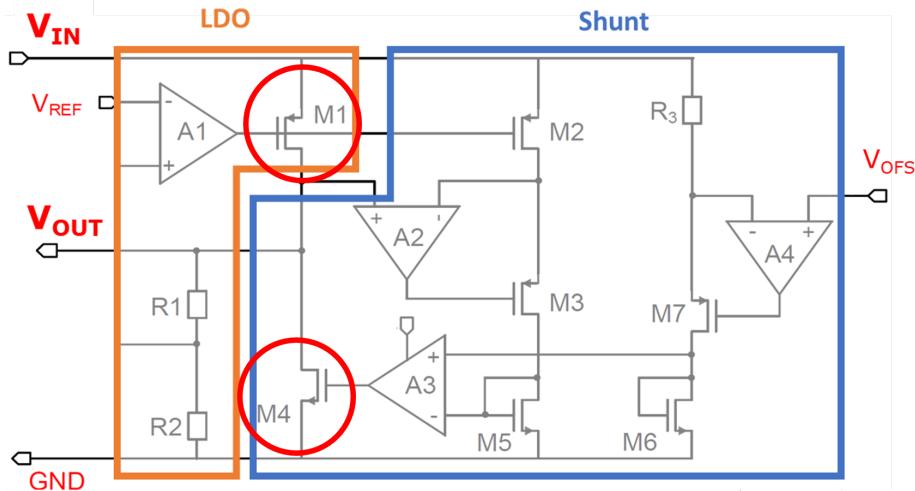

from particle scattering and conversions in the pixel detector and its related cooling, powering and readout services. The chip power consumption must be kept as small as possible, at similar level as the previous generation pixel chips, despite significantly higher pixel density and complexity with higher hit and readout rates. The use of a scaled CMOS technology is critical to keep an acceptable power consumption, from reduced capacitive loading of on-chip gates and the reduction of power supply voltage (Power scales with power supply voltage as  $V_{DD}^2$ ). An unfortunate side effect of power supply voltage scaling is that for the same power consumption, the required power supply current increases, posing problems making an appropriate low mass power distribution system. The use of switched mode DC-DC power conversion on the pixel chip, or on the pixel module, was investigated, but excluded because of the required radiation tolerance and associated space and material budget of local inductive or capacitive power converters. A novel serial powering scheme has therefore been adopted, with on-chip SLDO (Serial Low DropOut) power regulators, based on initial feasibility demonstrations with the FEI4 chip [5, 26, 31]. This particular serial power distribution system has been developed, tested and qualified at the chip, module and system level, while the RD53 pixel chips were actively being developed.

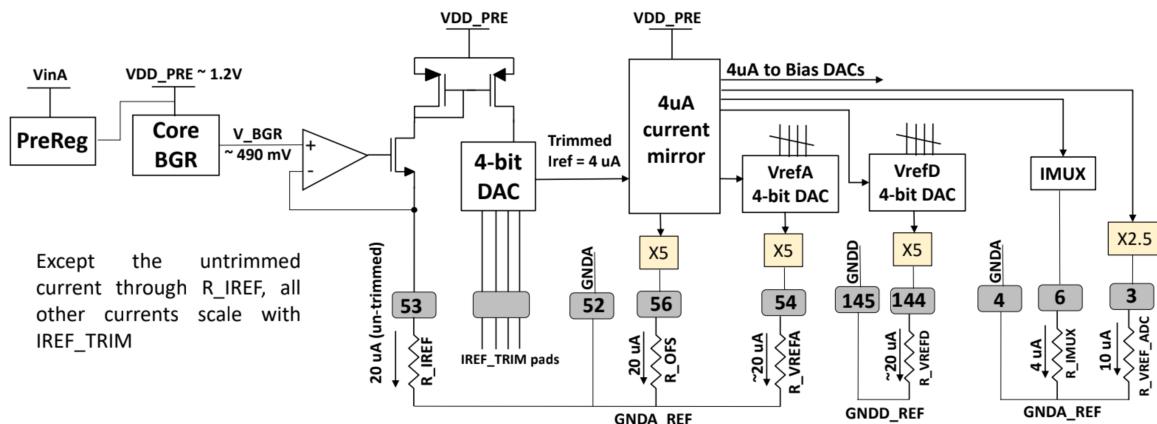

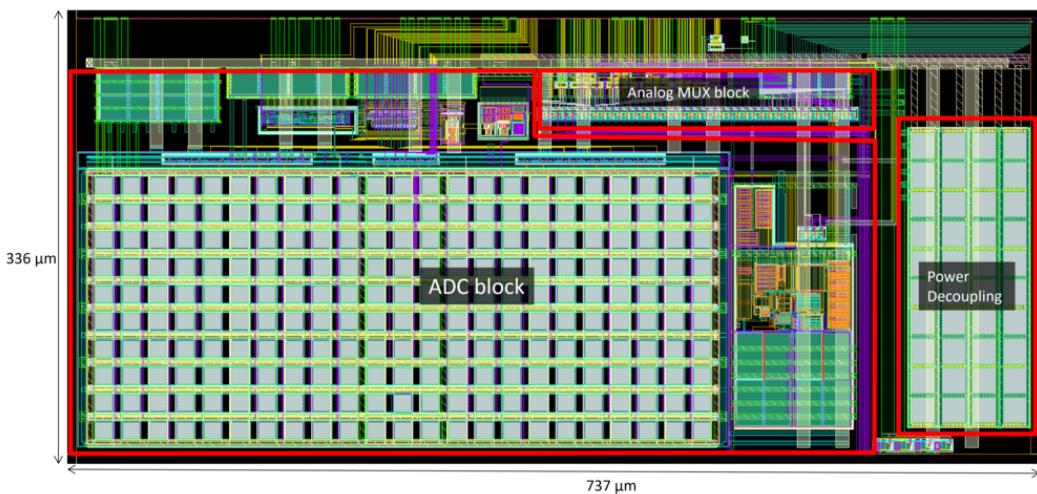

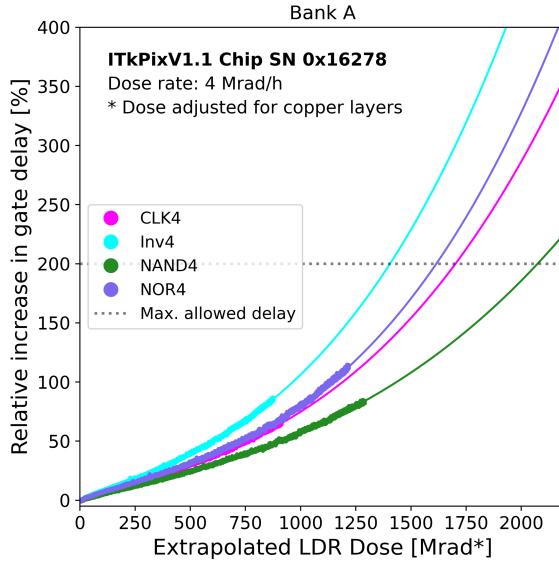

The first years of development in RD53 were focused on radiation tolerance studies of the chosen 65 nm CMOS technology and implementing and testing the required radiation hard building blocks: Digital to Analog Converters (DAC), Analog to Digital Converter (ADC), Analog pixel Front-Ends (AFE), biasing structures, band-gap reference, Phase Locked Loop (PLL), Input-Outputs (IO), SLDO power regulator and temperature and radiation sensors. An appropriate hit buffering, processing and readout architecture for the high hit and trigger rates was developed and extensively simulated and verified in a flexible simulation and verification framework with detector Monte Carlo hit data.

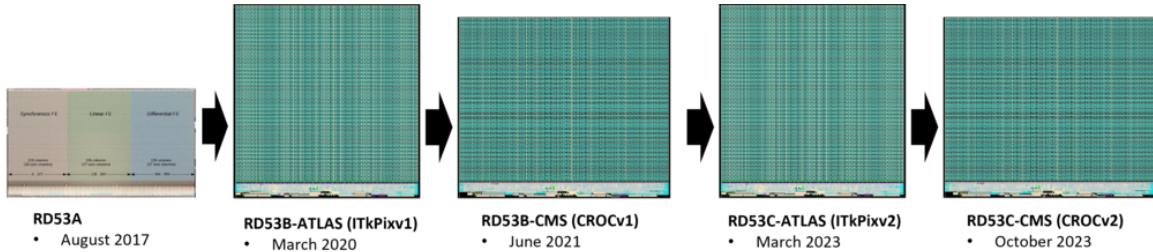

A first 1/2 sized pixel chip called RD53A, submitted in 2017 on a shared submission, has been used for verification of developed building blocks and general architecture. RD53A has also been instrumental as a test vehicle to test and qualify different pixel sensors [6] and for system studies, covering serial powering, design and testing of pixel modules and testing with lpGBT based readout system with optical links to the off-detector DAQ. A large set of irradiation test campaigns have been made with this chip to get a good understanding of reliable functionality of such a complex chip covering TID (Total Ionizing Dose) effects as a function of temperature, dose rate effects, and initial SEE tests. Three different analog front-ends were present in this chip together with two different trigger latency buffering schemes to determine the most appropriate implementation for final chips.

A second generation of RD53 chips, named RD53B-ATLAS & RD53B-CMS [9, 10], are complete full sized pixel chips made with the chosen latency buffer architecture and improved building blocks. RD53 developed a flexible parameterized design and verification environment where full custom macros and Register Transfer Level (RTL) code are instantiated according to the specific ATLAS or CMS implementations. The RD53B generation chips were made specifically for each experiment (RD53B-ATLAS, known as ITkPixv1 in ATLAS, and RD53B-CMS, known as CROCv1 in CMS) with their specific AFEs and chip size adapted to specific integration constraints of each experiment. These two chips, submitted in 2020 and 2021, are functionally equivalent with the same control and readout interfaces, with minor specific features related to the analog front-ends and specific features and bugs. The RD53B-ATLAS chip unfortunately had non-functional TOT (Time Over Threshold) charge measurement and could only be used with binary readout. The RD53B generation chips have been instrumental for extended chip testing in RD53 and pixel module and

**Figure 2.** RD53A to RD53C chip generations with chip submission dates.

system developments, testing and qualification in the ATLAS and CMS pixel detector groups. The evolution of the RD53 chips is shown in figure 2.

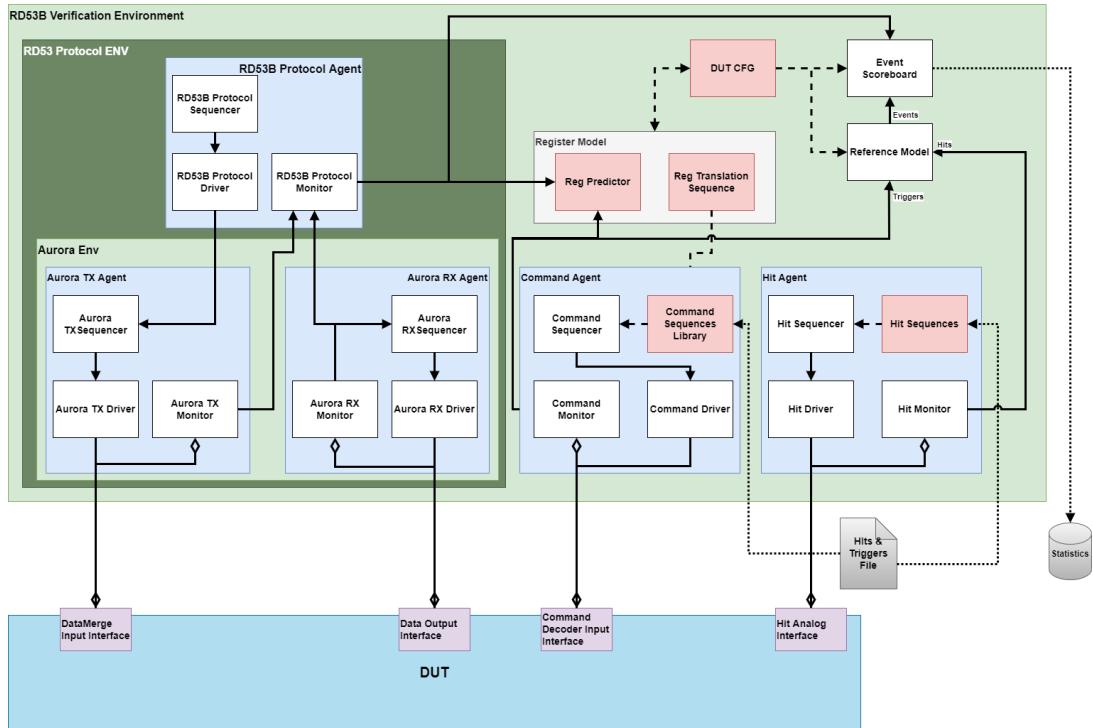

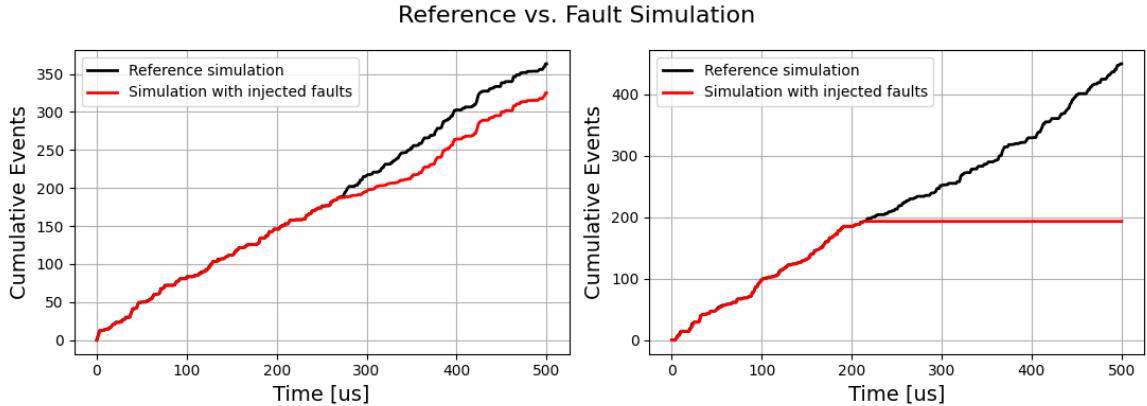

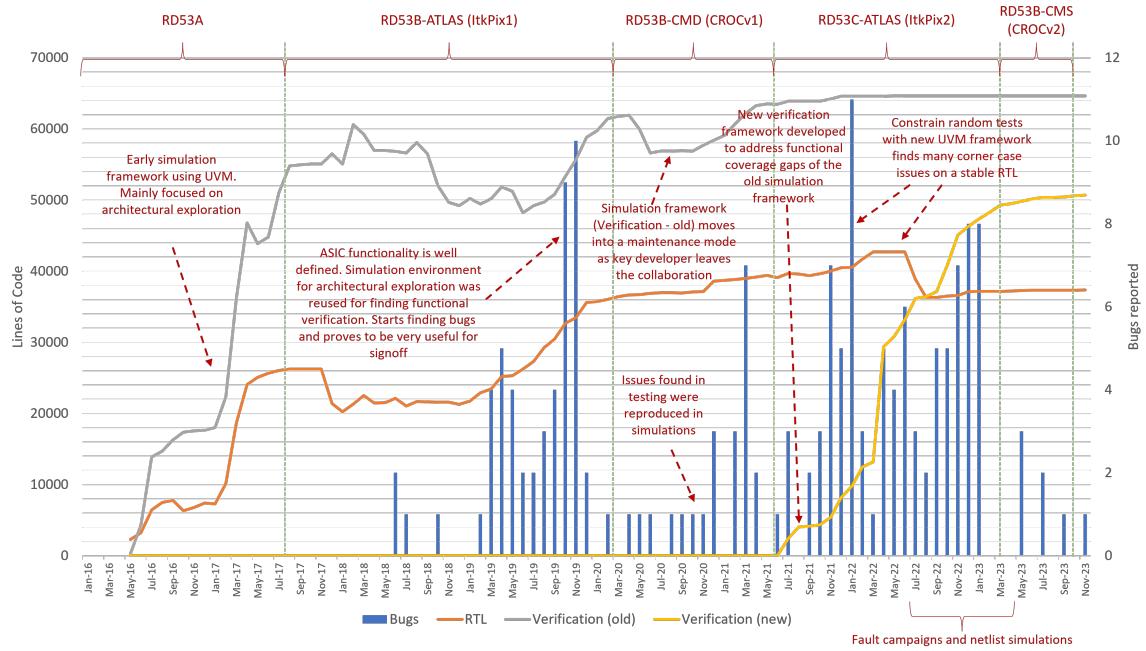

Bug fixes and improvements have been made in the final generation production chips: RD53C-ATLAS and RD53C-CMS [11]. Monitoring functions have been improved and extended. SEU and SET tolerance have been significantly improved based on extensive RD53B ion, proton and laser beam testing and SEU/SET simulations at transistor, gate and RTL level. Testing of serially powered quad chip pixel detector modules, in the ATLAS and CMS pixel detector groups, have enabled system issues to be identified and corrected. An extended verification framework was specifically developed for exhaustive functional and SEU/SET verification.

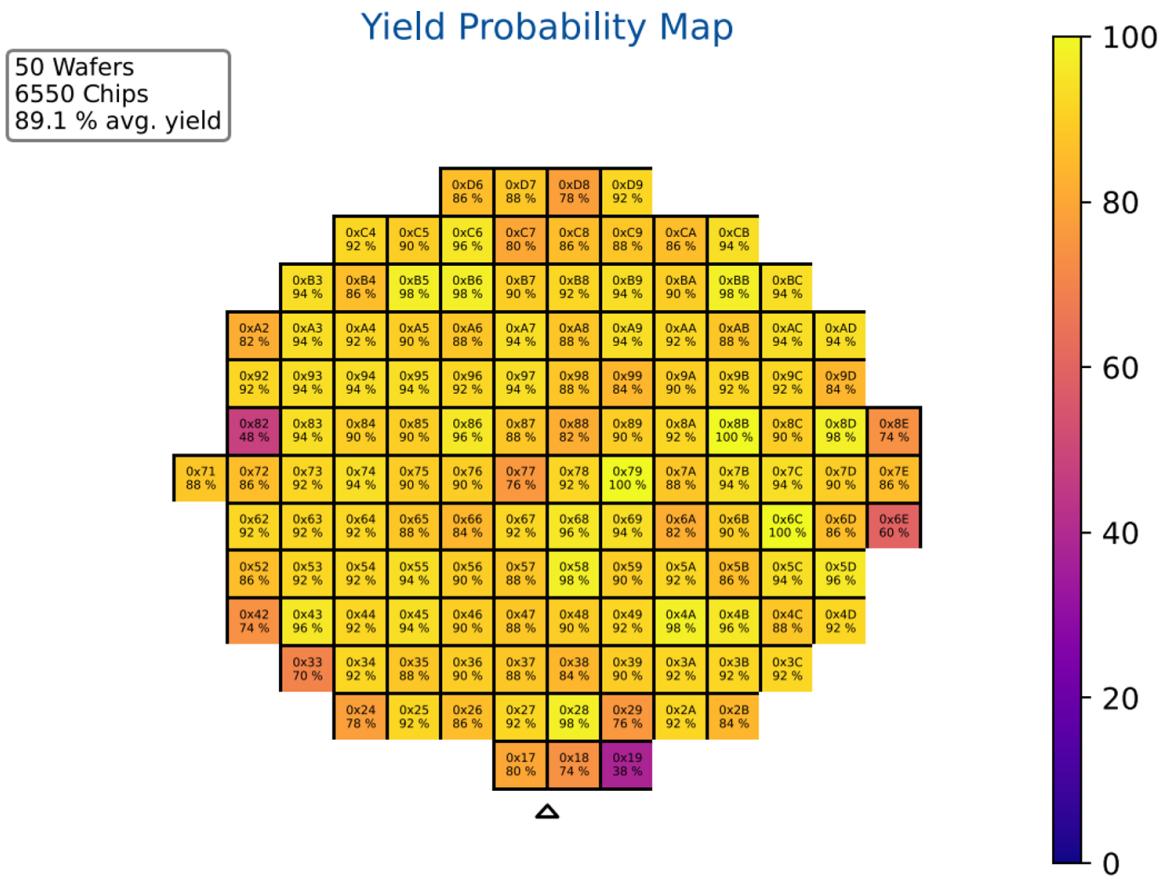

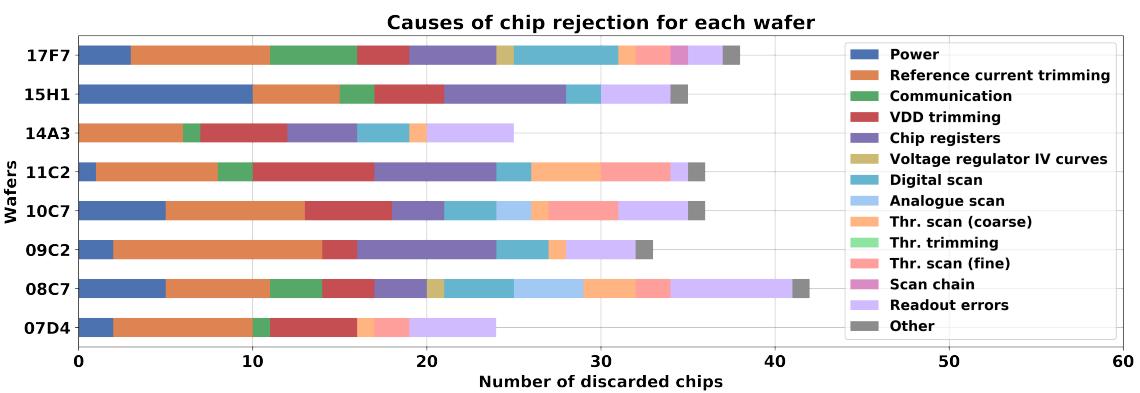

The large scale prototype chips RD53A, RD53B-ATLAS and RD53B-CMS have been produced and extensively tested as reported in this paper. Final production version chips, RD53C-ATLAS and RD53C-CMS, have recently been submitted and are in production for use in the experiment upgrades. The RD53C chips have recently been through extensive chip testing and characterization, with test results as reported in this paper. They are used for pixel module pre-production for large scale system tests. Wafer level production test setups have been developed and qualified for the two experiments.

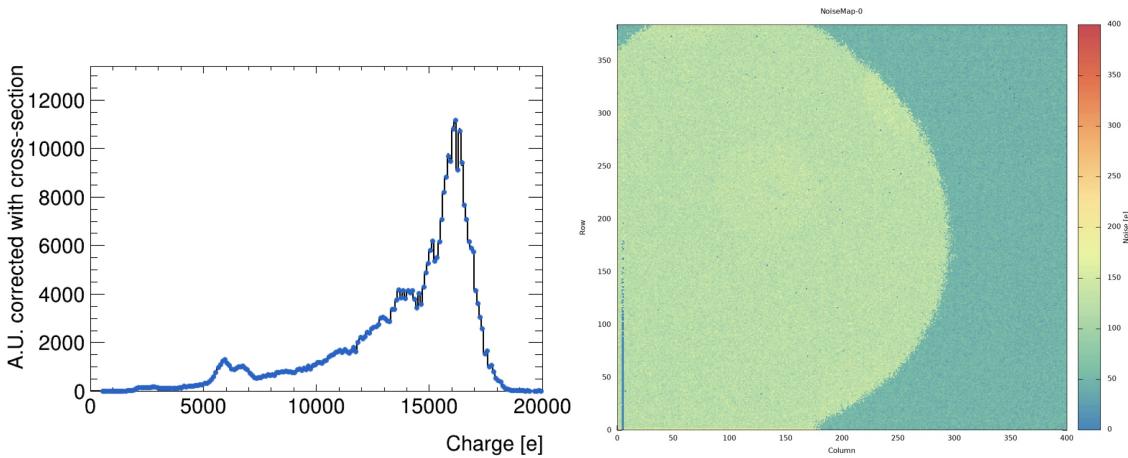

Test results shown in this paper are in general for the bare pixel chip without a pixel sensor, unless specifically mentioned in the figure caption. Bump bonded pixel chip and pixel sensor assemblies have only recently become available in sufficient quantity and quality to make detailed chip characterization of these with measurements shown in section 12. Extensive pixel module test, characterization and qualification is currently ongoing in the ATLAS and CMS pixel groups with their specifically chosen pixel sensors.

The chip architecture and implementations are outlined together with circuit details of critical blocks to achieve required performance in the hostile radiation environment. Most of the discussions make no distinction between the ATLAS and CMS chips, as these are based on a common architecture with only minor implementation differences. The paper is organized as follows. Section 2 provides a short overview of the planned use of the pixel chips in the ATLAS and CMS pixel detectors. Section 3 gives an overview of the pixel chip architecture. Section 4 describes the analog front-ends, performing pixel hit detection with a 4 bit charge measurement. Section 5 outlines hit data buffering during the trigger latency and following data processing. Section 6 defines the control and readout interfaces. Section 7 covers the on-chip serial power regulator and the generation of biasing and references. Section 8 describes the implemented on-chip monitoring features. Section 9 summarizes radiation tolerance aspects. Section 10 outlines the integration and implementation. Section 11 describes final functional and SEU/SET verification. Section 12 summarizes general test results and wafer probing. Finally section 13 concludes the paper.

## 2 Pixel detector system

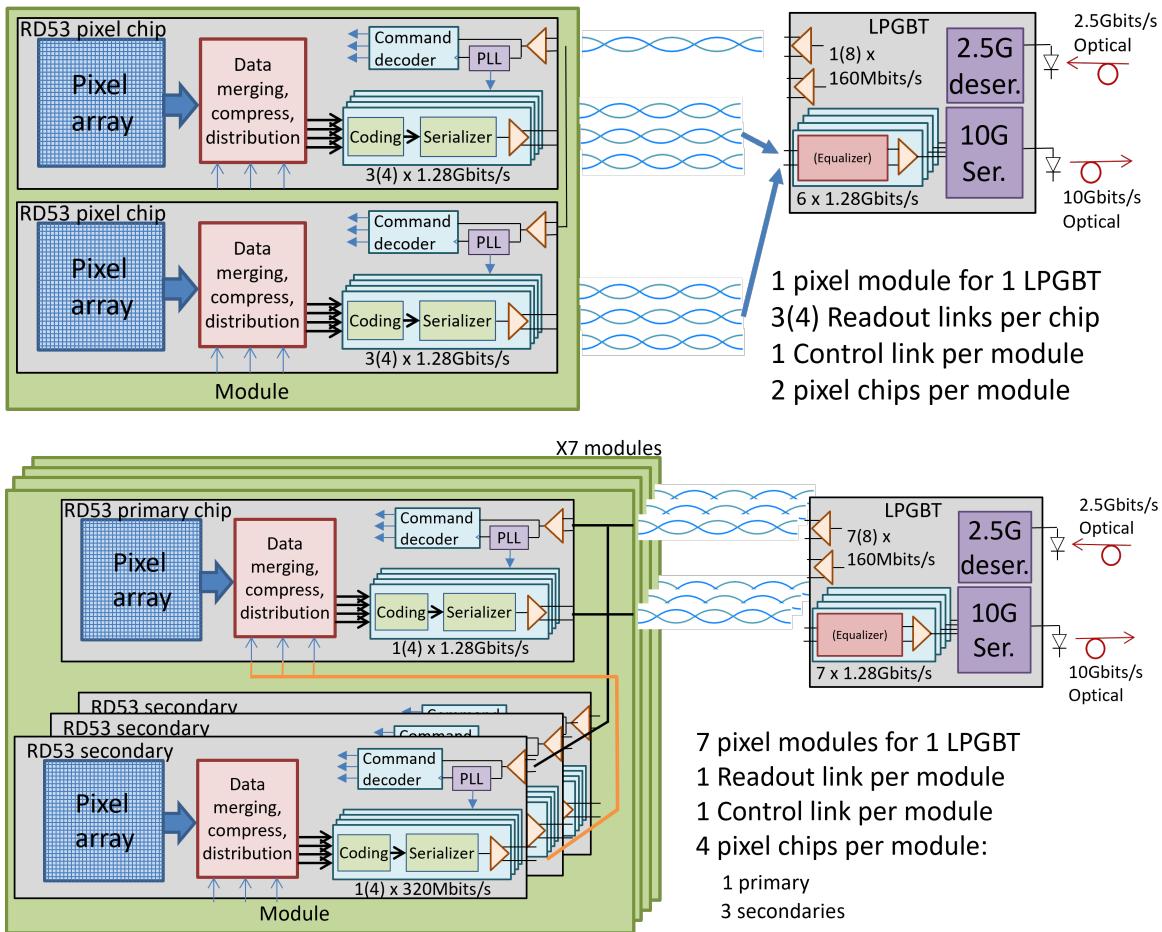

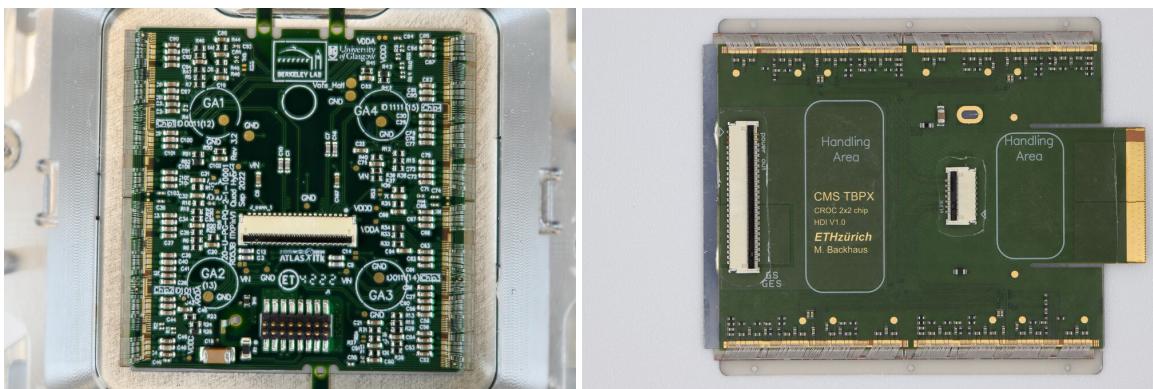

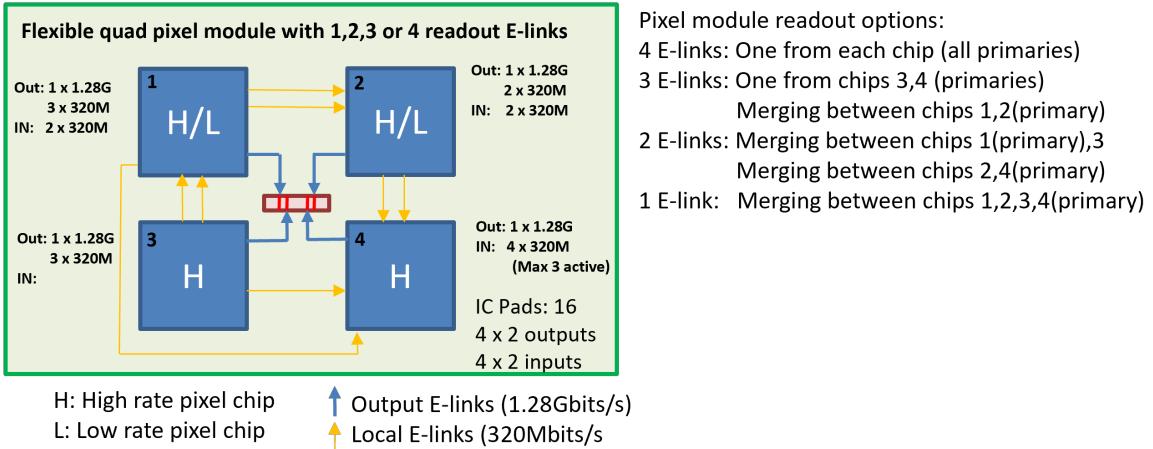

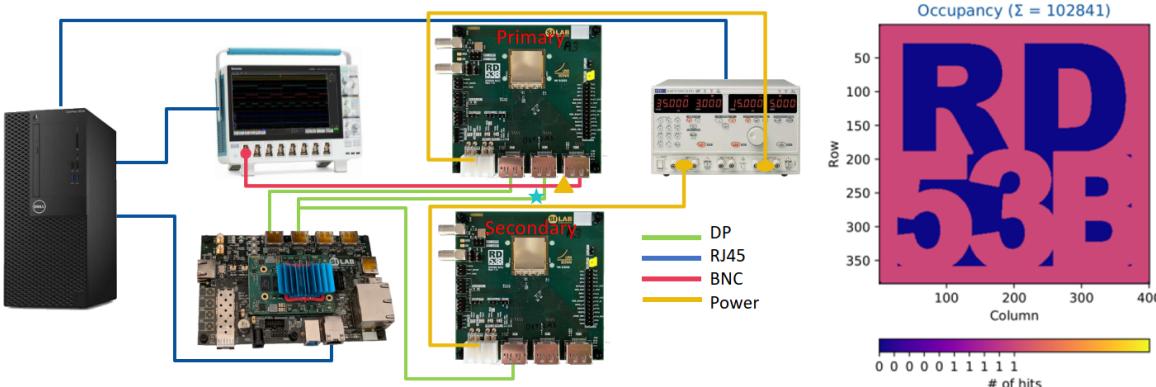

The upgraded pixel detector systems of ATLAS [2] and CMS [3] are made to have the same front-end control, readout and powering interfaces defined for the RD53 pixel chips. Pixel chips are integrated on dual, triple or quad pixel chip modules with a single bump-bonded pixel sensor. Effective hit rates and required readout rates have a strong dependency on the radial distance to the interaction point ( $r^{-2}$ ). Inner layer chips require up to 5.12 Gbits/s readout bandwidth, while pixel chips in outer layers only need a factor 20–50 lower readout bandwidth (depending on detector layout, number of layers and barrel versus forward). The readout via the lpGBT has therefore been defined to allow a high level of readout link modularity to minimize the number, and material, of required readout links. Each pixel chip can use from 1 up to 4 serial Electrical links (E-links) at 1.28 Gbits/s (lpGBT max E-link speed). RD53 pixel chips can also be used in a primary-secondary configuration, where readout data from 2 or 4 pixel chips are merged into a single 1.28 Gbits/s link as illustrated in figure 3 with pixel module prototypes shown in figure 4. Multiple chips on the same pixel module are controlled with a single 160 Mbits/s control link carrying clock, configuration and real-time control information. In ATLAS, control and readout links between pixel chips and the lpGBT are up to 8 m long [24], using a dedicated cable driver and equalizer GBCR ASIC [23]. In CMS, with an E-link distance limited to 1.5 m, the pixel chips are connected directly to the lpGBT.

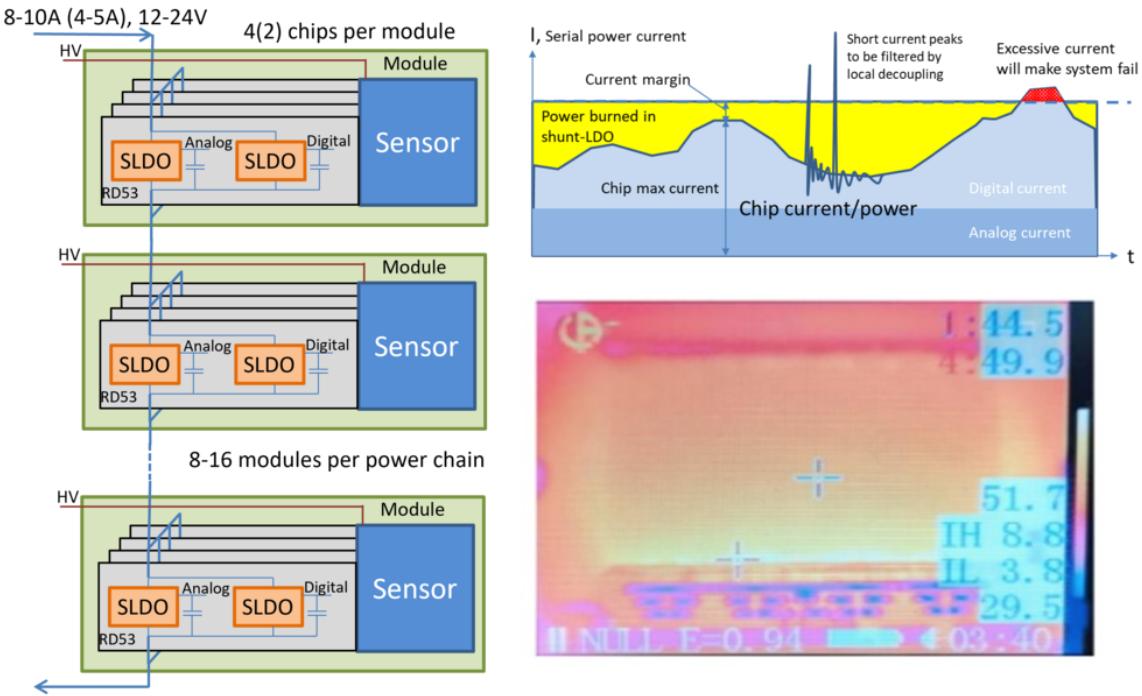

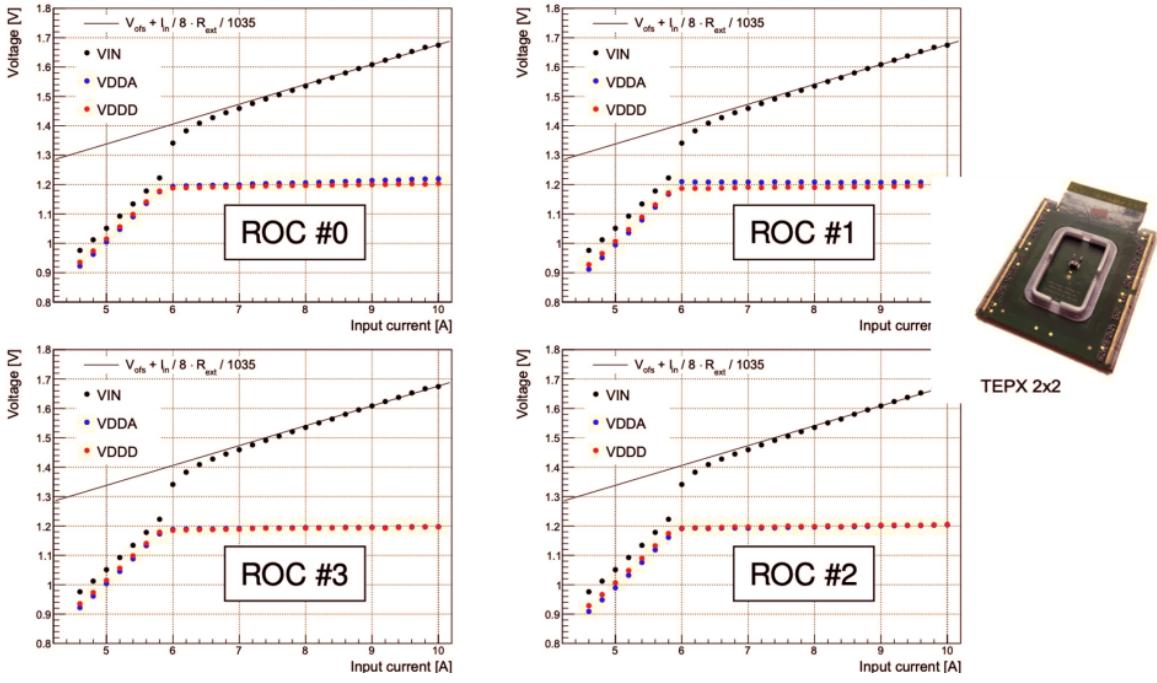

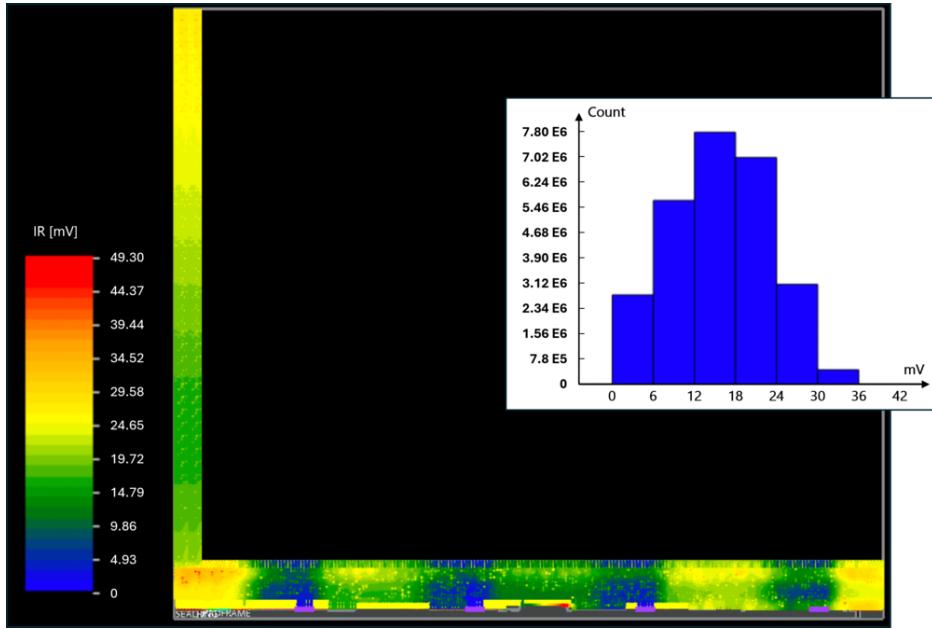

Serial powering is used in both pixel detector systems to minimize the material budget for the power distribution. The power supply current on a single power cable pair is used to power up to 16 pixel modules in series as shown in figure 5. Multiple pixel modules are powered in series with a constant current and on-chip SLDO regulators dynamically adjust their chip power impedance, to have constant and well regulated local voltages for the analog and digital parts of the chip. In such a powering scheme it is critical to minimize fluctuations in circuit power consumption and have sufficient current headroom and local decoupling capacitors to enable the local power regulators to absorb such fluctuations, as shown in figure 5 in upper right plot. Each chip has separate analog and digital SLDO regulators, connected in parallel to the common input power, to assure the best possible isolation of the sensitive analog front-ends from switching noise induced in the power rails by the digital circuits. The effective load impedance is dynamically regulated with a controlled shunt current, maintaining constant input voltages and currents, independently of the actual current consumed by the analog and digital circuits in the chip.

Such a constant current (and constant voltage) powering system is highly advantageous in systems where low noise is primordial and where long power cables will have significant voltage drops. Assuring constant power supply currents also prevents power cables in strong magnetic fields to have induced dynamic forces with possible resonances. System drawbacks of serial powering are the power dissipated in the on-chip regulators, with necessary current (10–20 %) and voltage (0.2–0.3 V) headrooms, adding up to a total power overhead of 20–40 %. In particular, if the pixel chip goes into a low power state, the on-chip regulators will have to dissipate the full nominal chip power as shown in figure 5 lower right thermal image. Both pixel detectors will be cooled with highly efficient high pressure CO<sub>2</sub> cooling systems that will be designed to cope with this. Another system issue with serial powering is the requirement that all control and readout links to/from the pixel chips must have AC coupling, with appropriate DC balanced link encoding. Special care must be taken for system grounding as pixel module grounds can not be connected to system ground, which implies the need for good galvanic isolation between pixel chips and local CO<sub>2</sub> cooling. The High

**Figure 3.** Pixel module control and readout. Upper: dual chip inner module with multiple (CMS:3 or ATLAS: 4) readout E-links per pixel chip. Lower: quad chip outer module with data merging to single readout link.

**Figure 4.** Quad chip pixel modules with RD53B chips and bump-bonded sensor. Pixel chips and sensor located behind Kapton pixel hybrid, with wire-bonds to pixel chips visible on the sides. Left: ATLAS quad module. Right: CMS quad module.

**Figure 5.** Serial powering of pixel modules with multiple chips in parallel per module (left). System issues with varying load current (constant analog current plus varying digital current) that must be suppressed by the SLDO (upper right) to get a constant serial chip current. SLDO power dissipation hot spot issue (lower right thermal image), that must be appropriately cooled in the pixel detector.

Voltage (HV) biasing of the pixel sensors (Planar: 100–1000 V, 3D: 20–100 V) will have voltage differences between modules along the serial powering chain of up to 12–24 V, depending on the number of modules in the serial power chain.

The novel serial powering scheme developed for the RD53 chips also enables multiple chips on a pixel module (up to 4) to be powered in parallel. This enables pixel chips on the same module, and bump-bonded to a common pixel sensor, to be at the same potential. It also improves the overall reliability of serial powering significantly, as individual chips can be allowed to fail with a power-open, without affecting other chips and modules on the serial power chain (e.g. 16 quad pixel modules with a total of 64 pixel chips in single serial power chain). To assure appropriate power by-passing, in case of a failing chip on a module, the shunt capability of the on-chip regulators can handle up to 200 % of nominal chip current. As an additional protection capability, chips have a built-in 2 V over-voltage clamp to assure that local voltage fluctuations do not cause damage during power cycling or during local power anomalies. Extensive chip, module and system tests of serial powering have been made to qualify such a novel powering scheme as shown in figure 6 with appropriate cooling infrastructure.

### 3 Chip architecture

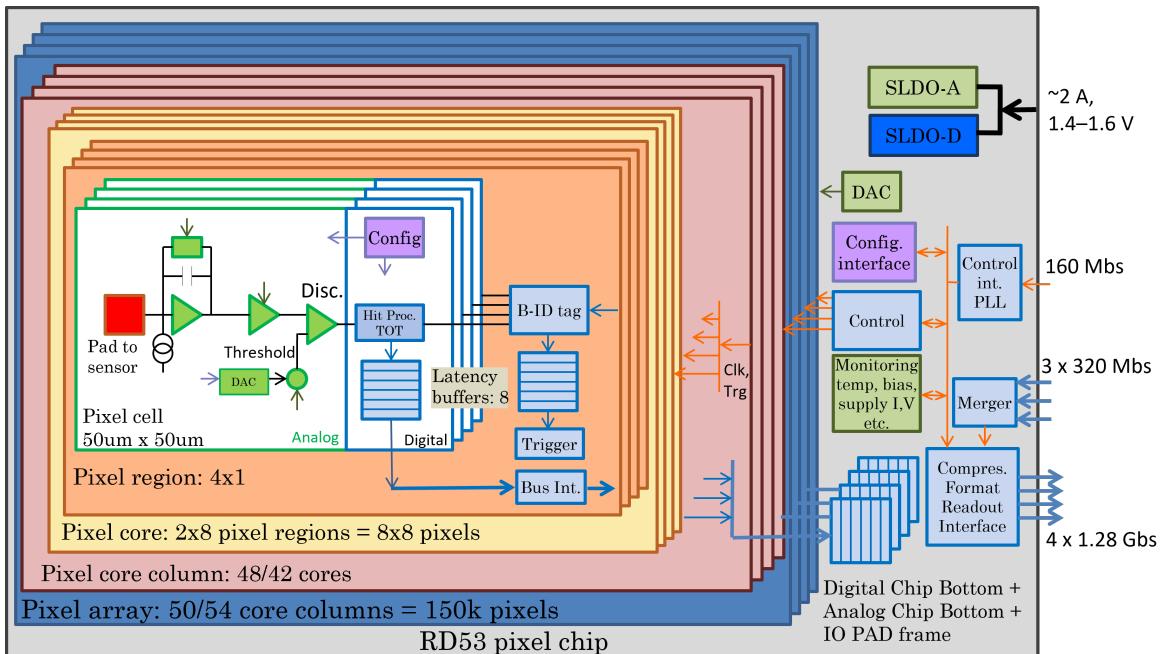

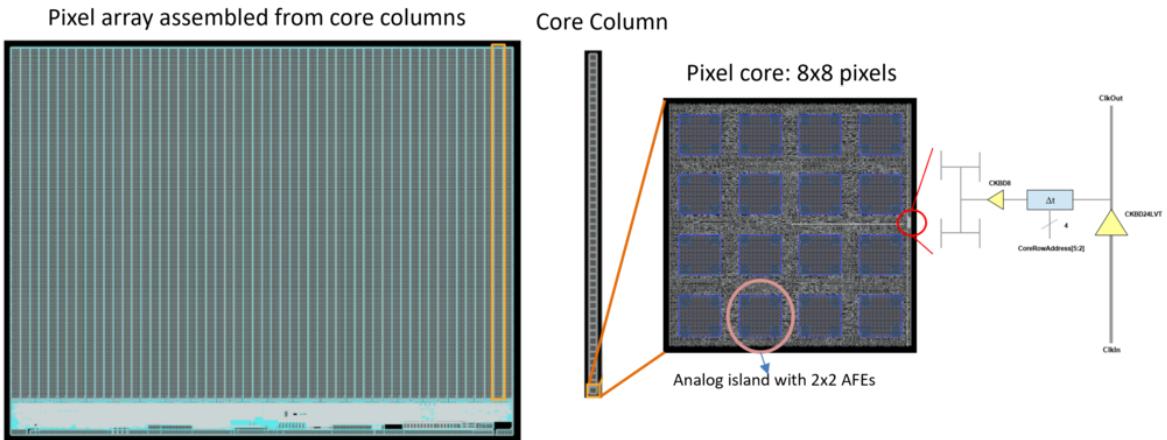

RD53 pixel chips capture pixel hits across the  $2 \times 2 \text{ cm}^2$  pixel array with appropriate timing to enable triggering of hits in individual bunch crossings for readout. Charge deposited in the pixel sensor, bump bonded to the pixel chip, is amplified and shaped so it can be sampled precisely in the correct

**Figure 6.** Initial cooling tests with multiple quad RD53B chip pixel modules with serial powering. Left: ATLAS quad chip pixel module testing with water cooling pipes and serial power being connected to pixel modules with Kapton flexes to a power distribution flex [32, 33]. Right: CMS quad chip pixel module testing on a water cooled cooling plate, with serial power and power return passing from one module to the next for the barrel part of the CMS pixel detector. Reproduced with permission from [33].

**Figure 7.** RD53 Data flow architecture.

bunch crossing, with associated 4 bit charge information, via TOT measurement. Sampled and zero-suppressed hit information is stored during the trigger latency in latency buffers distributed across the pixel array in local pixel regions consisting of 4 pixel cells. The transfer of triggered and extracted pixel hit data from the pixel regions is organized into  $8 \times 8$  pixel cores (consisting of  $2 \times 8$  pixel regions) via columns of pixel core buses to the Digital Chip Bottom (DCB). Triggered hit data are then assembled and processed before being queued in derandomizer FIFOs for event readout over serial links in their original trigger order.

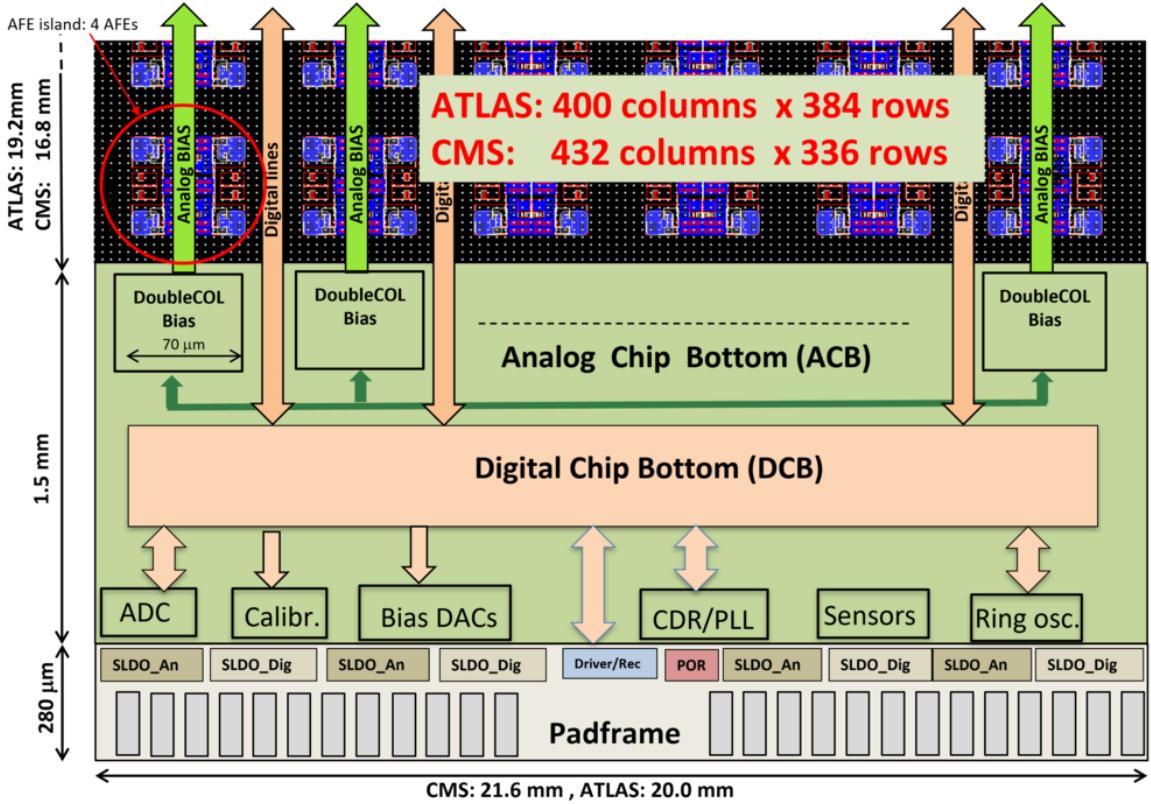

The RD53 architecture is organized in a hierarchical fashion of which some parts are related to the logical data flow, as shown in figure 7, while others are related to the implementation floorplan of the chip as shown in figure 8:

- *Pixel*: experiment specific AFE with threshold adjust, charge injection and configuration.

- *Pixel region*:  $4 \times 1$  pixel digitization with TOT and 8 latency buffer locations.

- *Pixel core*:  $2 \times 8$  pixel regions,  $8 \times 8$  pixels.

- *Pixel core column*: 48 cores in ATLAS chip, 42 cores in CMS chip.

- *Pixel core row*: 50 cores in ATLAS chip, 54 cores in CMS chip.

- *Pixel array*: ATLAS:  $8 \times 8 \times 50 \times 48 = 153,600$  pixels, CMS:  $8 \times 8 \times 54 \times 42 = 145,152$  pixels.

- *Analog pixel island*:  $2 \times 2 = 4$  pixel AFEs.

- *Analog biasing column*: 2 pixels wide columns for AFE biasing with drivers.

- *Digital Chip Bottom (DCB)*: digital logic outside the pixel array.

- *Analog Chip Bottom (ACB)*: peripheral analog circuitry: bandgaps, biasing DACs, monitoring ADC, PLL.

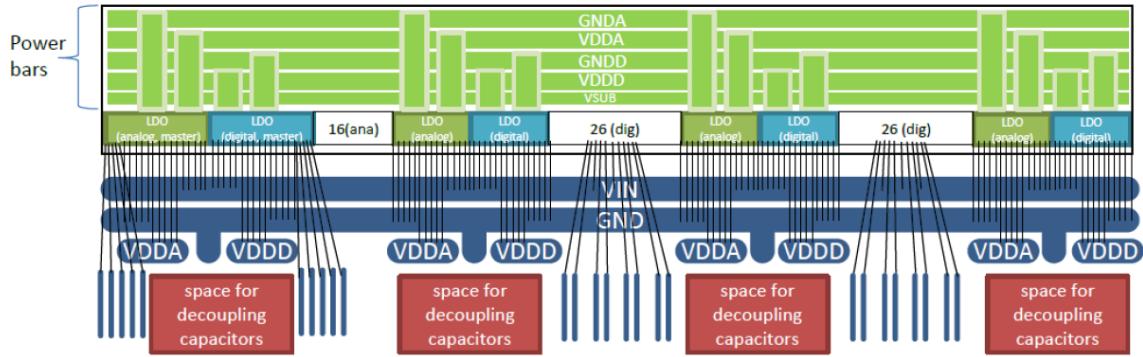

- *Pad frame*: IO with wire-bond pads, ESD protection, distributed SLDO power regulators and power-on reset.

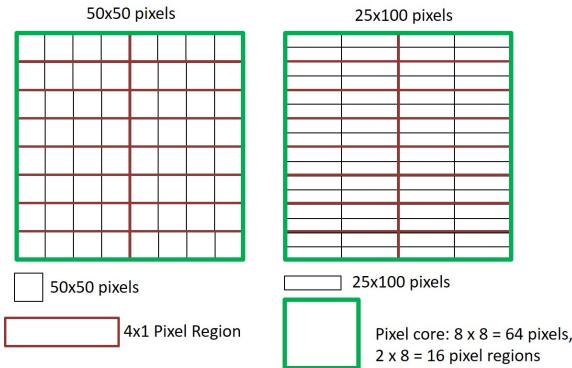

It is important to notice that the effective organization of pixels into pixel regions, with shared latency buffer, depends on the organization and routing on the pixel sensor. For square  $50 \times 50 \mu\text{m}^2$  pixels the sensor array and the chip have the same array structure and the pixel regions are seen as  $4 \times 1$  pixels covering  $200 \times 50 \mu\text{m}^2$ . Such an elongated pixel region shape is advantageous for latency buffer sharing at the end of the detector barrel, where hit clusters are elongated because of particle angle and active sensor thickness. When having elongated pixels of  $25 \times 100 \mu\text{m}^2$  on the sensor, the pixel region is effectively seen as a  $2 \times 2$  pixel region covering the same  $200 \times 50 \mu\text{m}^2$  area as indicated in figure 9.

## 4 Analog front-ends and hit digitization

The Analog Front-Ends (AFE) are grouped in 4 pixels and implemented as small analog islands in a sea of digital pixel array logic, as illustrated in figure 8. The grouping of 4 AFEs into analog islands, where the AFE layout has been mirrored and flipped to fit together, can cause minor systematic mismatch differences, that after appropriate threshold tuning become negligible. The analog islands are isolated from the surrounding noisy pixel logic using a deep N-Well (triple well) available in the chosen 65 nm technology. AFEs also use a separate analog power supply (together with Analog Chip Bottom) from a dedicated analog SLDO regulator.

Charge induced by traversing particles in the pixel sensor is transferred to the pixel chip via fine pitch bumps as shown in figure 10. The AFE in each pixel integrates the collected charge in a pre-amplifier stage, with charge integrating feedback, followed by appropriate signal shaping and buffering. The discharge of collected integrated charge is done with a configurable discharge

**Figure 8.** Physical implementation floorplan with analog pixel islands surrounded by digital pixel logic and digital/analog chip bottom.

**Figure 9.** Pixel region organization with  $50 \times 50 \mu\text{m}^2$  and  $25 \times 100 \mu\text{m}^2$  sensor pixels.

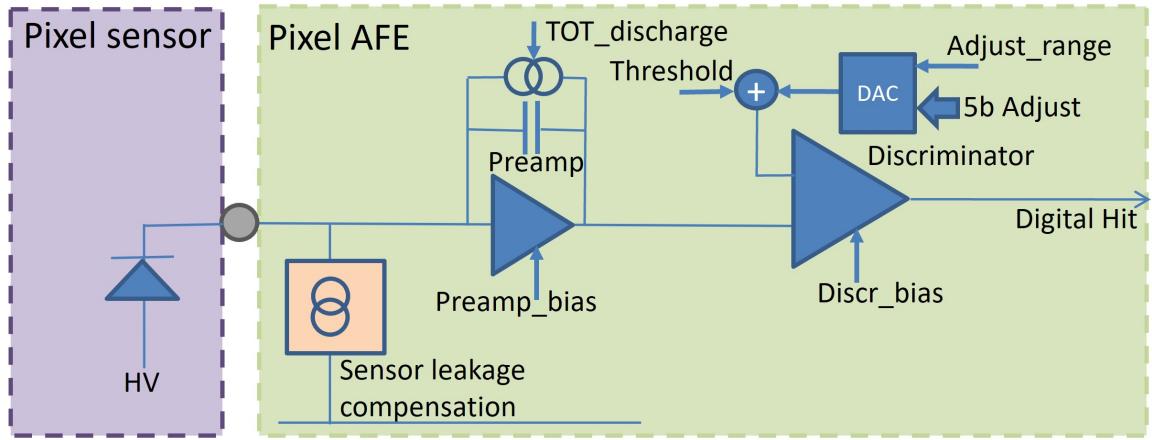

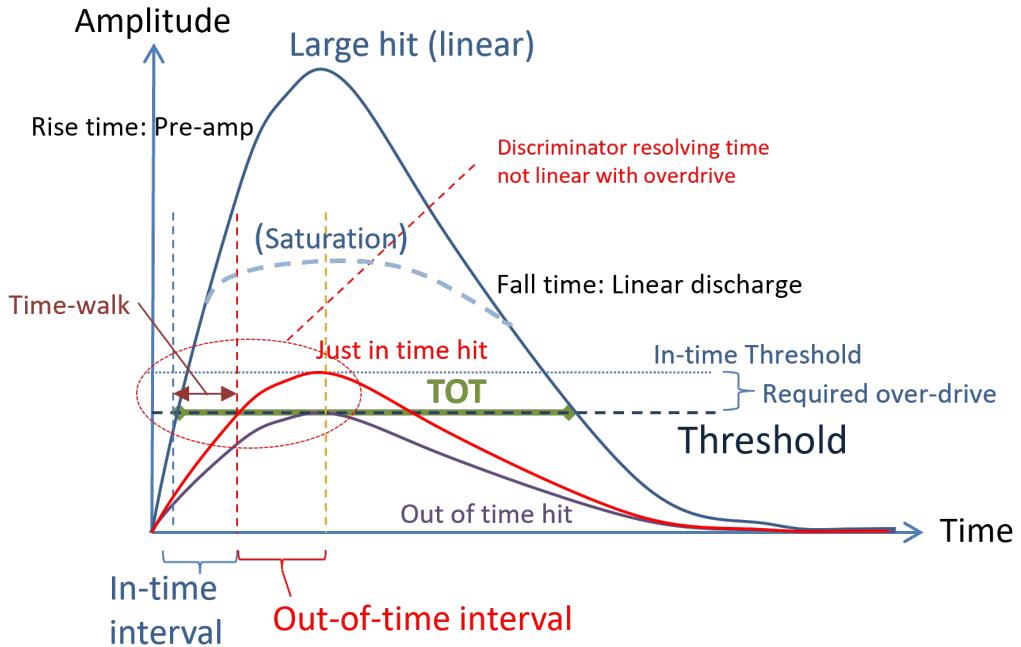

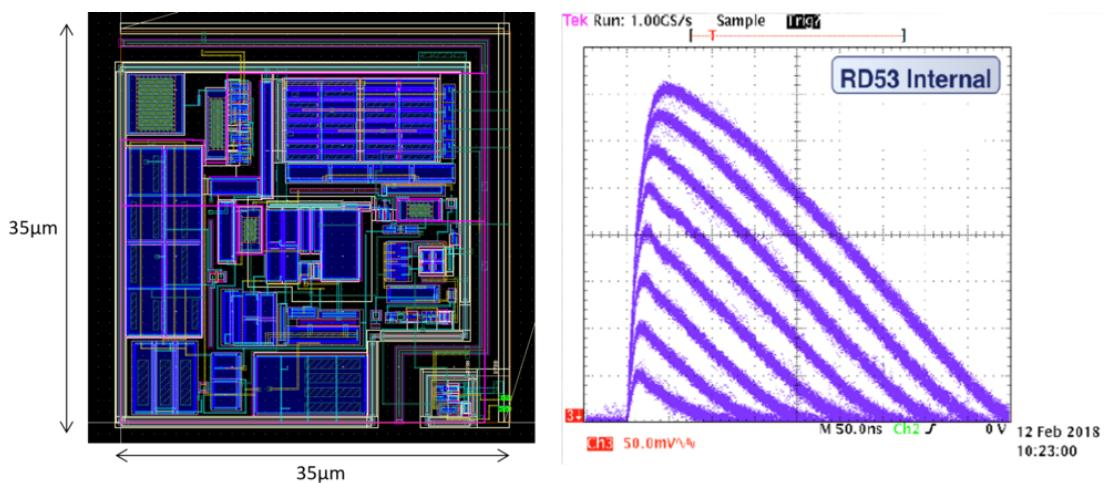

current (in some implementations referred to as Krummenacher current [14]), resulting in an analog pulse width proportional to charge. The shaped signal, with fast rising edge and slowly decreasing falling edge, as illustrated in figure 11, is transformed into a 1 bit digital hit signal by a discriminator with programmable threshold.

The AFEs work asynchronous to the 40 MHz bunch crossing clock and hits are synchronized to the 40 MHz chip clock at the entry to the digital pixel hit processing in the pixel regions. The effective threshold per pixel is determined by a global threshold bias together with a 5 bit threshold

**Figure 10.** Block diagram of generic pixel Analog Front-End (AFE).

**Figure 11.** Charge measurement with TOT and indication of related time-walk, dead-time and amplitude saturation effects.

adjust per pixel, to compensate for threshold dispersion among pixels. The range of the threshold adjustment is defined by a global programmable bias to allow its dynamic range and resolution to be optimized for the observed pixel array threshold dispersion.

The simple small area and low power hit detection with TOT charge measurement has some side effects as indicated in figure 11. The prolongation of the analog hit signal, to get an appropriate TOT charge resolution, gives an analog dead-time hit loss of the order of: (Average TOT time)  $\times$  (Hit rate per pixel) = (from 50 ns to 200 ns)  $\times$  75 kHz/pixel = 0.4–1.5 % for the highest hit rate in inner layers. The maximum TOT dead-time loss in inner layers have been specified to be 1 %,

enforcing a short average TOT time below 133 ns. In outer low rate layers a longer TOT time can be used to get better charge resolution.

It can be mentioned that if the charge integrated analog signal has amplitude saturation effects, the TOT charge measurement can be corrected off-line, when used at low thresholds as indicated in figure 11. If the detection threshold is set at a charge level below where the saturation effect sets in, the leading edge is detected at the correct level. Saturation effects occurring above the threshold detection level will affect the TOT pulse width. This can be corrected for offline if this non-linearity has been appropriately characterized. This TOT non-linearity can though have relatively large variations between individual pixels and be sensitive to temperature and radiation effects.

Small hit signals, just above threshold (e.g. at edge of pixel clusters), will get time walk from the combined effect of analog signal shape and the discriminator reacting slower when having small signal over-drive. For a time-walk below 20 ns (25 ns clock period minus 5 ns sampling margin for system jitter and time alignment to collisions) the hit will be detected in the appropriate bunch crossing for triggered readout. For time walk larger than this, the hit can be seen as a low TOT/charge “noise” hit in the following bunch crossing and will therefore not be read out for the corresponding trigger (unless forcing double triggering).

Each experiment has chosen their specific low power AFE implementation based on their specific emphasis on particular performance characteristics. The differential AFE used in the ATLAS chip has particular emphasis on low noise and small time-walk. The linear AFE used in the CMS chip has particular emphasis on linearity ( $\sim 5\%$ ) and capability to work with short analog/TOT dead-time in inner high rate pixel layers [16]. The two AFEs have similar effective area and interfaces and are integrated into the RD53 design framework with a few design configuration parameters.

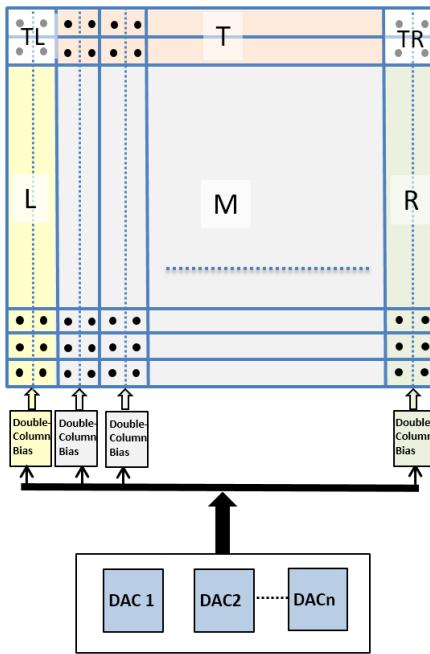

Multiple biasing levels for the AFEs are defined by global configuration registers connected to biasing DACs driving the analog pixel array via column drivers as shown in figure 12:

- *Pre-amplifier bias*: determines the effective speed of AFE charge integration, but also affects effective gain, noise and dispersion. Major contributor to AFE power consumption.

- *TOT discharge current*: determines the discharge rate of integrated charge, thereby defining TOT resolution and related analog dead-time.

- *Discriminator bias*: determines the effective speed (and time-walk) of discriminator.

- *Global threshold*: global chip threshold onto which local pixel threshold adjustment is applied.

- *Threshold adjust range*: determines the range of local threshold adjust DACs.

Biasing of the AFEs has significant effects on their behavior and is a delicate optimization to be done according to the allowed power consumption, hit rate, noise, time walk and pixel sensor characteristics. It will also be needed to take into account accumulated radiation effects in both pixel sensor and the pixel chip itself. Edge and corner pixels have separate pre-amplifier biasing as they are typically 2-4 times larger to cover the gap between pixel chips on multi-chip pixel modules (e.g. quad pixel modules) and minimize insensitive areas at pixel module edges. This is organized in 6 groups: Main, Left side, Right side, Top, Top Left corner, Top Right corner, as indicated in figure 12, to enable flexible adaptation to different pixel sensor and module configurations with enlarge pixels in boundary regions between pixel chips.

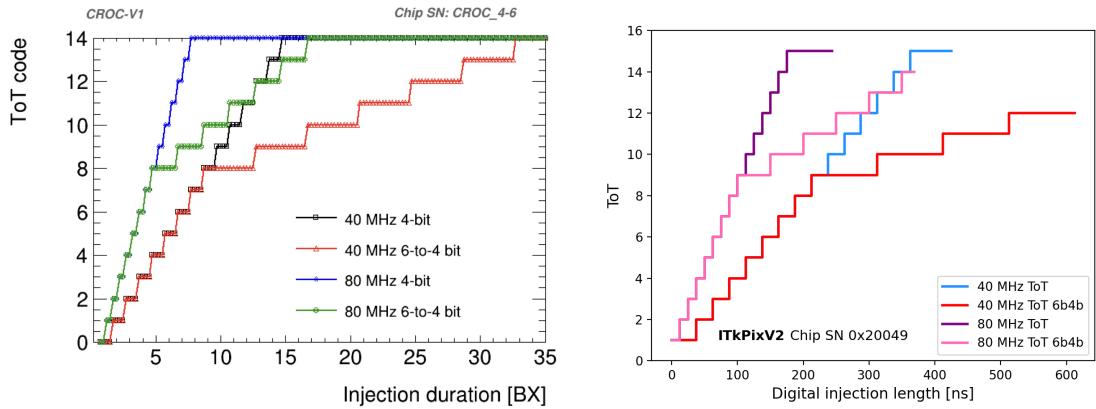

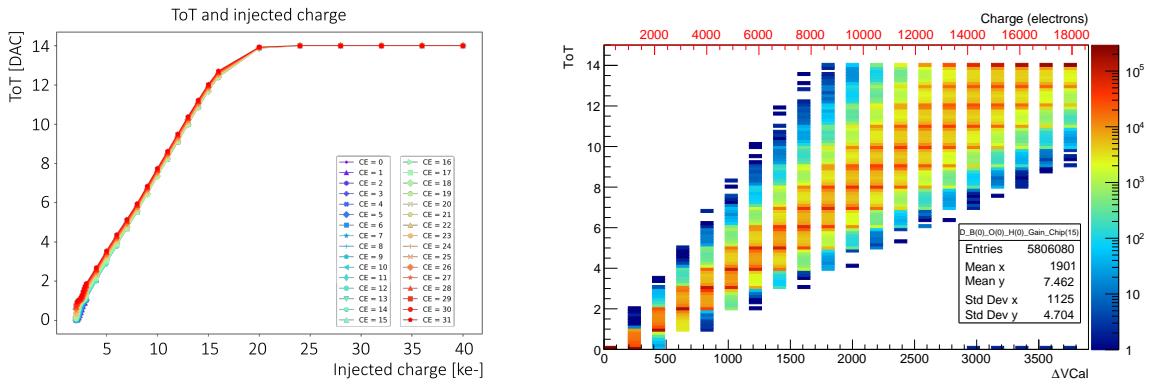

**Figure 12.** AFE bias distribution with different pre-amp biasing of different pixel regions: Main (M), Left side (L), Top Left side (TL), Top (T), Right side (R), Top Right (TR).

The leading edge of the discriminator hit signal is a measure of the particle Time Of Arrival (TOA), with associated time walk, and the Time Over Threshold (TOT) is proportional to the collected charge. The leading edge is synchronized to the 40 MHz sampling clock and the pulse width is measured with the rising or both edges of the 25 ns sampling clock (40 and 80 MHz TOT sampling) for a 6 bit TOT count. The 6 bit TOT count can be mapped directly into 4 bit TOT, ignoring the 2 MSB (Most Significant Bits) bits with saturation, or can be mapped into 4 bits with a dual slope mapping. With dual slope mapping the full TOT resolution is maintained in the first half of the 4 bit dynamic range, whereas extended dynamic range is obtained in the second half as illustrated in figure 13. Dual slope mapping assures good position interpolation at the edge of pixel clusters, where the collected charge is normally small, and high dynamic range for  $dE/dx$  measurements of pixel clusters that can be used to identify highly ionizing particles and contribute to general particle identification [15].

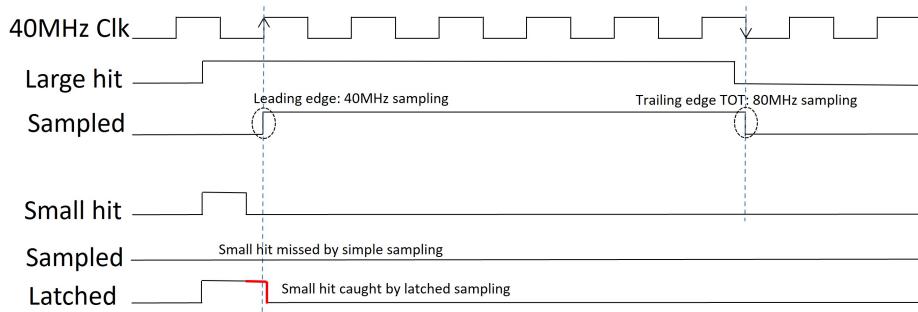

Capture of the discriminated hit signal can be performed synchronously or asynchronously. For synchronous/simple sampling, short hits not present at the rising edge of the sampling clock will be ignored. For asynchronous/latched sampling, a discriminator hit pulse is kept high until it has been captured by the first coming 40 MHz sampling clock edge. Async sampling is guaranteed to capture short hit pulses, but will have slightly higher sensitivity to noise hits as indicated in figure 14. One should also be aware that short/small hits will typically also be affected by time-walk. In RD53B chips the hit sampling mode was configurable. For the final RD53C chips, ATLAS has chosen the async sampling mode, given the low noise and low time-walk AFE and issues fitting both modes in available area. For the RD53C-CMS chip it has been possible to maintain both sampling modes.

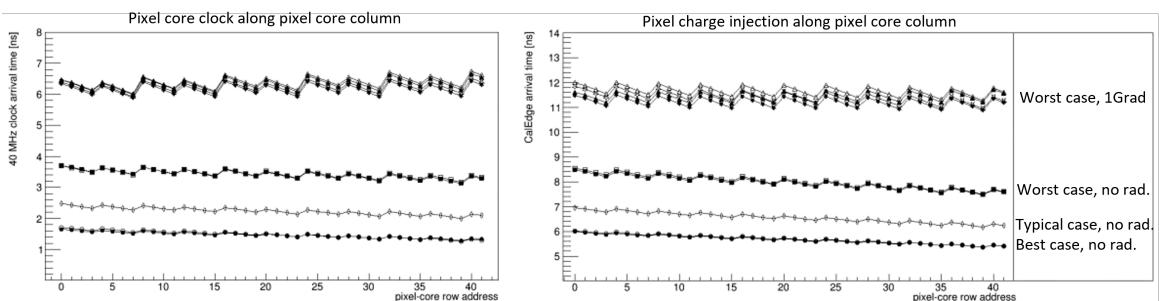

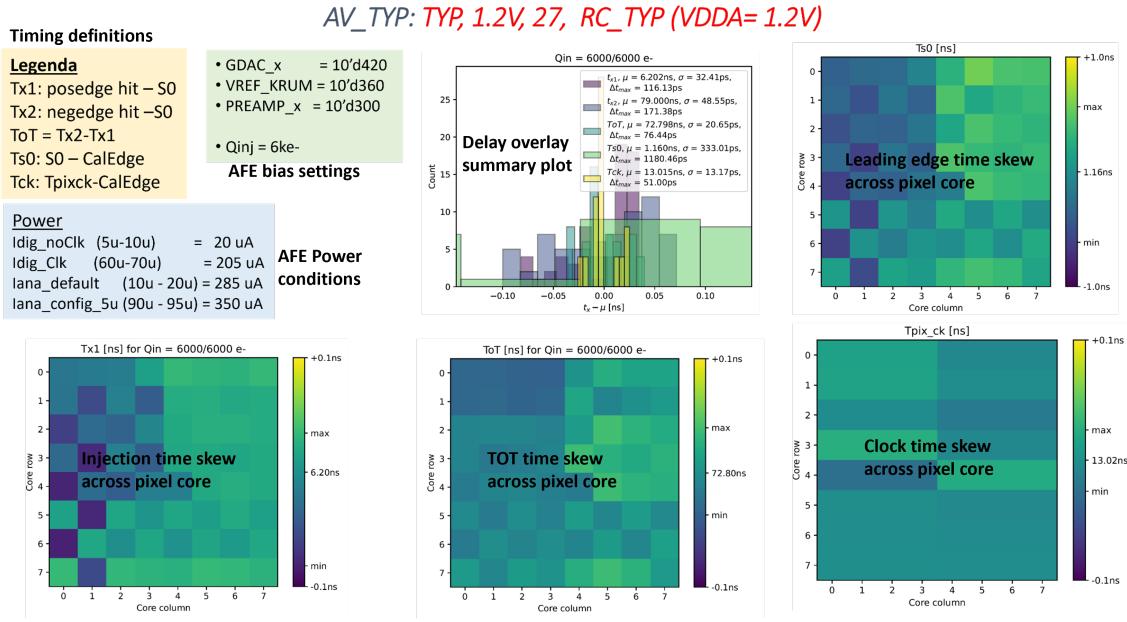

The 40 MHz sampling clock for the hit detection in the individual pixels is carefully distributed across the pixel array with typical (maximum) time skew across the whole array below 1 ns (2 ns)

**Figure 13.** Measured Linear and Dual slope TOT with 40 MHz and 80 MHz sampling using digital pulse width injection. Left: CMS chip with pulse width in BX units (25 ns) and TOT=15 representing no hit (so not shown). Right: ATLAS chip with pulse width injection in ns and TOT=0 representing no hit. Does not include analog non-linearity of the AFE (described later).

**Figure 14.** Hit sampling with synch/asynch sampling. Indication of optional 80 MHz TOT sampling.

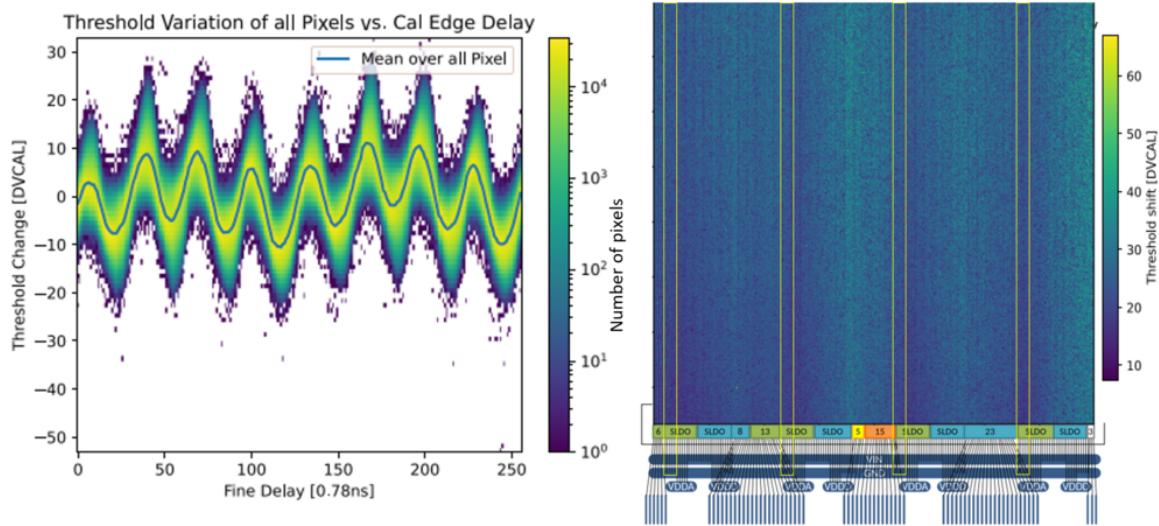

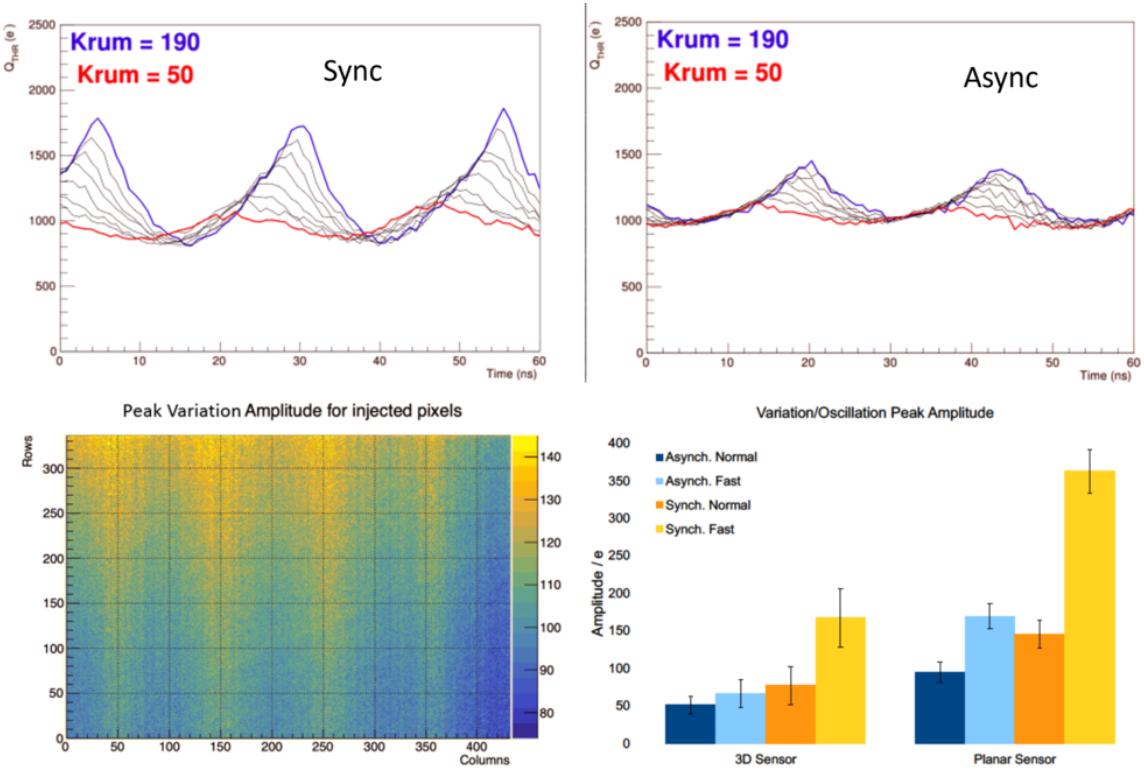

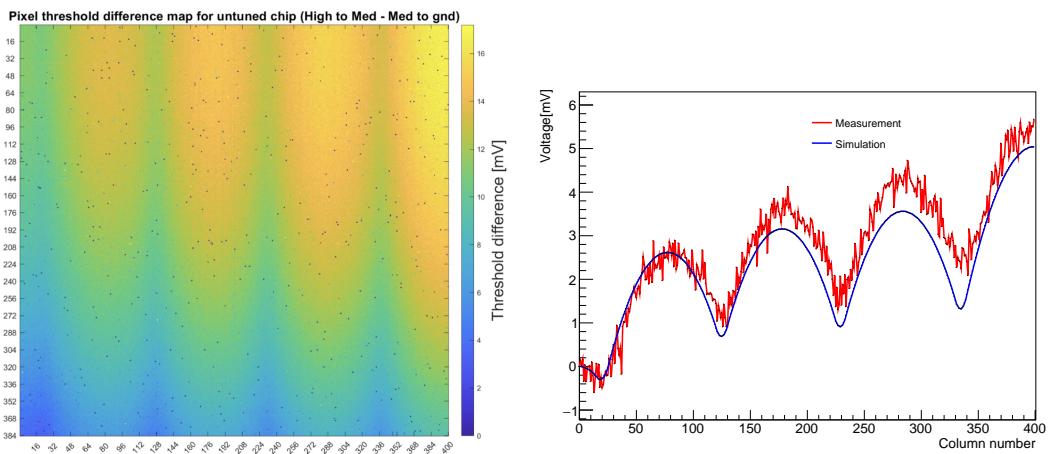

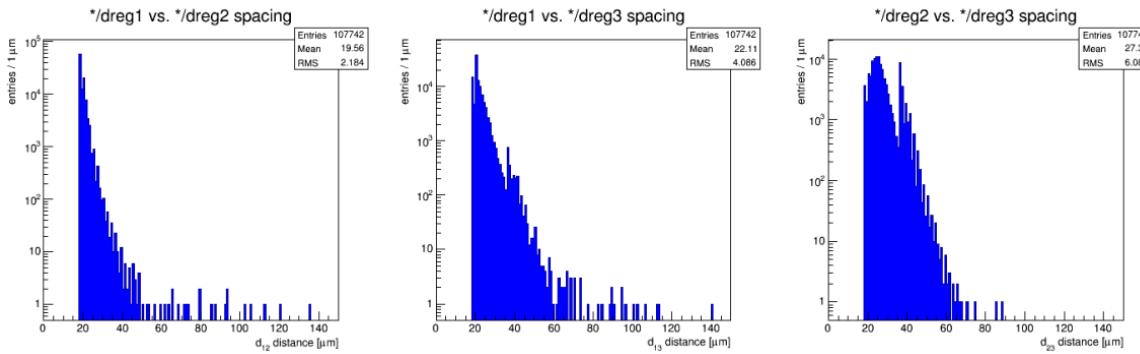

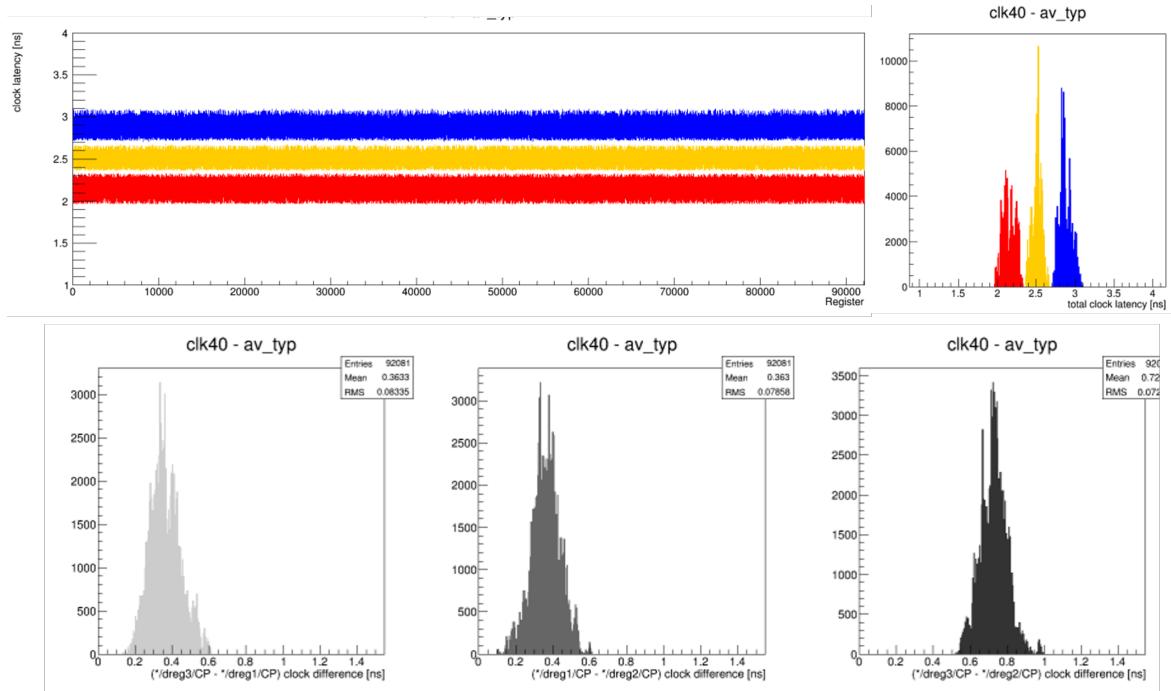

to assure that hits are captured in the correct bunch crossing for triggering and readout. This gives short digital power surges over the pixel array at the rising edge of the clock that can affect the analog front-ends and hit digitization. Local decoupling capacitors are distributed across the array to minimize this effect and the AFEs have been decoupled as much as possible from the digital with separate power domains and the use of separate triple wells for analog and digital. A threshold variation over the 40 MHz clock period has been observed in the full RD53 chips as indicated in figure 15 and figure 16. This can be seen to be related to on-chip power distribution with four distributed sub-instances for each SLDO. The magnitude of this effect is dependent on the sampling mode used (sync or async) and on the configured TOT discharge rate (fast/slow). The Async sampling mode, assured to capture incoming hits in the full clock cycle is intrinsically less sensitive to the arrival time of hits. At a 1000 e threshold the async sampling will have a 50 e (fast shaping assumed use in final application) - 450 e (slow shaping) threshold variation effect. This has been measured to be proportional to the number of pixel core columns actively being clocked and will therefore also in practice depend on power decoupling and wire-bonding (resistance and inductance) on a pixel module. The measured threshold variation across the pixel array is caused by static and dynamic voltage drops in the on-chip power distribution network within the pixel array and four distributed instances of the SLDOs. In

**Figure 15.** Left: RD53B-ATLAS threshold variation (async sampling) across clock cycle from power supply perturbations [56]. Right: threshold variation amplitude across pixel array overlayed on RD53B layout with indication of distributed SLDOs in four groups. DVCAL is digital threshold configuration DAC in steps of 5 e.

sync sampling mode, the effective hit capture threshold has a relatively large dependency on the relative phase to the sampling clock and used TOT discharge rate as shown in figure 16, because short hits can be missed depending on its relative timing/phase to the sampling clock. It has not been possible to improve this further for a one-side powered chip, needed for quad chip pixel modules with no dead detection zones between chips. It should be noted that direct particles from the bunch collisions of the LHC arrive within a relatively narrow time window ( $\sim 1$  ns) and will therefore not be significantly affected by this. It is for each experiment to determine how they want to time align their pixel detector to the bunch collisions, using programmable delays in their timing distribution system and in the RD53 chip, and how to obtain appropriate absolute threshold and charge measurement calibration, using calibration pulse injections in the RD53 chip.

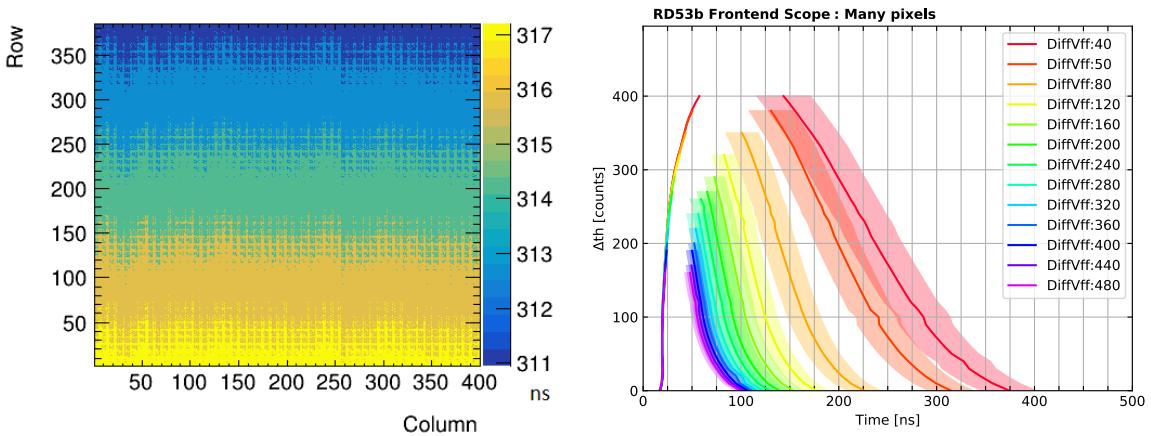

Discriminated hit signals from individual pixels, with local enables, are also connected to a configurable hit-OR column network to measure Time Of Arrival (TOA) and TOT with 640 MHz precision TDCs (Time to Digital Converter) in the Digital Chip Bottom (DCB). The hit-OR signals are also used for a flexible self-trigger function that can be used for detailed chip and sensor characterization in test beams and with radioactive sources. An example of using the precision TOA is shown in figure 17 to measure calibration injection and hit-OR skew along pixel columns in the RD53B-ATLAS chip (improved in RD53C chips to have reduced skew), and measure analog pulse shape with a threshold scan using the precision TOA and TOT.

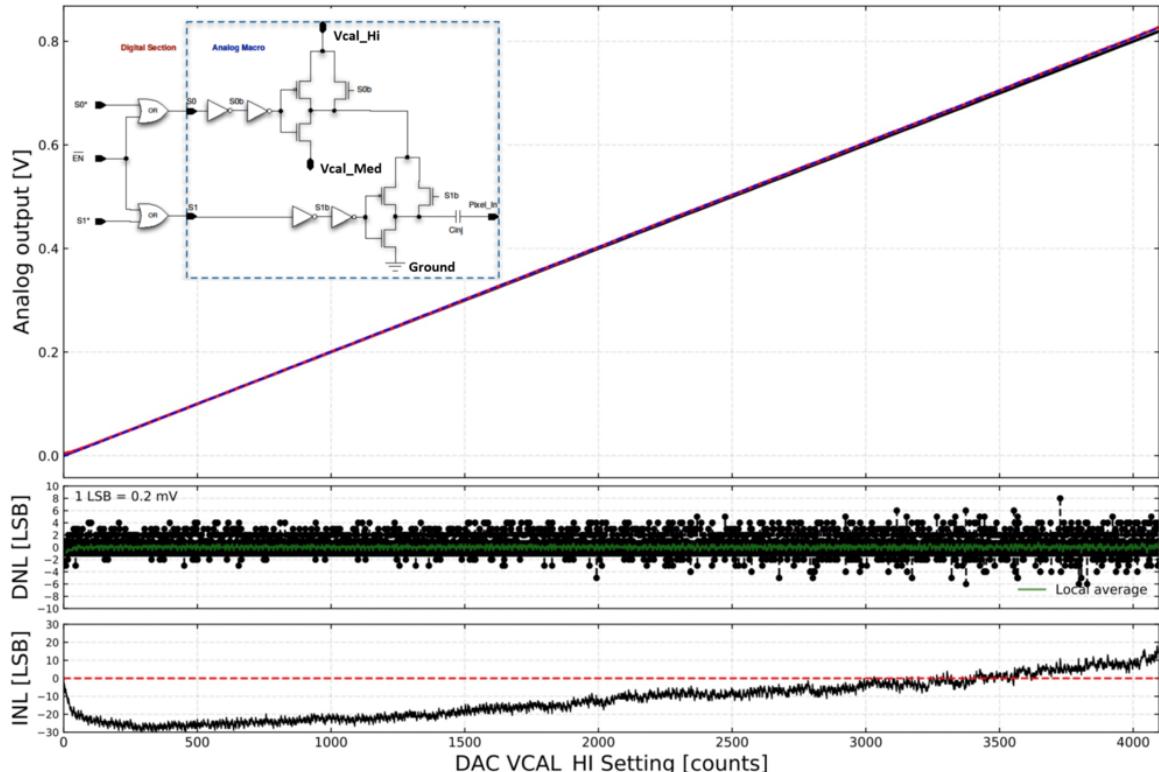

An analog injection circuit is implemented in each pixel, with an equivalent circuit as shown in figure 18, to perform precise threshold tuning and calibration. The calibration injection circuit uses two distributed DC voltages (Vcal\_Med and Vcal\_Hi), from two on-chip 12 bits DACs, followed by in-pixel switches to generate charge injections via a pixel injection capacitor (C<sub>inj</sub>). Having two charge injection voltages enables precise differential charge injections (Vcal\_Hi - Vcal\_Med), independent of ground voltage drops across the pixel array, as well as making two consecutive injections (Vcal\_Hi - Vcal\_Med followed by Vcal\_Med - ground) into the same pixel. The timing of the injection is

**Figure 16.** RD53B-CMS Threshold variation across clock cycle. Upper left: sync sampling mode for different TOT discharge rates from Fast (Krum=190) to Slow (Krum=50). Upper right: async sampling mode. Lower left: 2D map of async threshold variation across pixel array in fast mode with 10 e color step. Lower right: estimated max threshold variation effect for fast (inner) and normal (outer layers) discharge rate for 3D and planar pixel sensors. Reproduced with permission from [17].

**Figure 17.** RD53B-ATLAS precision TOA and TOT. Left: digital pixel injection across pixel array with measured TOA using the high resolution TDC via the hit-OR network. Right: analog pulse shape reconstructed from measured TOA and TOT with high resolution TDC, over different charge injections. DiffVff sets the charge integration discharge current of the Differential AFE and the shaded area indicates the spread among pixels in the pixel array.

controlled by a digital pulse generator with programmable injection time (0.78 ns resolution) and time between two consecutive injections, using the two calibration voltages plus local ground. The same pulse generator can be used for direct digital hit injections.

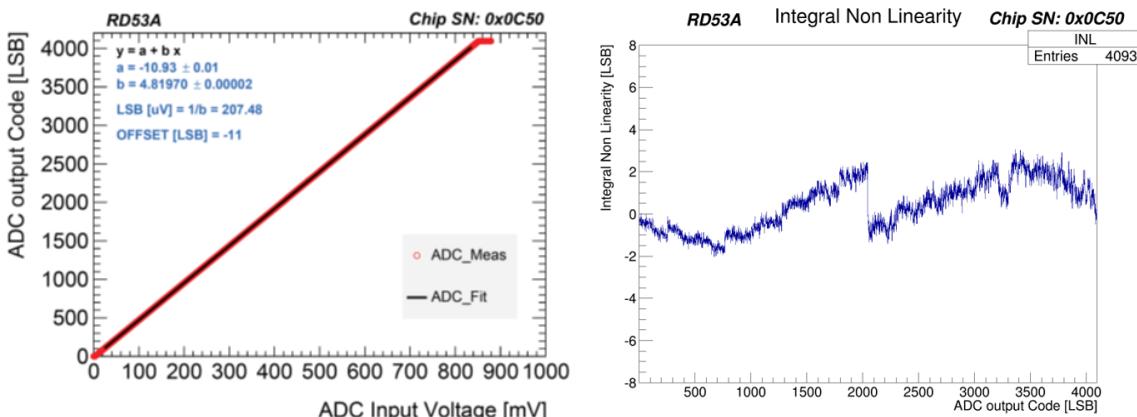

Two 12 bit voltage DACs located in the ACB generate the charge injection voltages, driven with dedicated voltage drivers to the in-pixel charge injection circuits in each pixel. The DAC characteristics are shown in figure 18. Calibration injection has an effective resolution of  $\sim 5$  e when being used concurrently on a limited number ( $\sim 100$ ) of pixels. Used for massive concurrent injections in a large number of pixels, the effective precision is deteriorated by dynamic capacitive loading from the voltage switches in the pixels. Injection capacitance spread among chips on the same wafer has been seen to be 1 - 1.5 % with a 5-10 % difference between wafers.

**Figure 18.** Calibration injection voltage as function of DAC setting with a linear fit and extracted DNL (Differential Non-Linearity) and INL (Integral Non-Linearity). Pixel charge injection circuit shown as an insert with its two injection voltages ( $V_{cal\_Med}$ ,  $V_{cal\_Hi}$ ) and local ground, enabling two consecutive charge injections to be made.

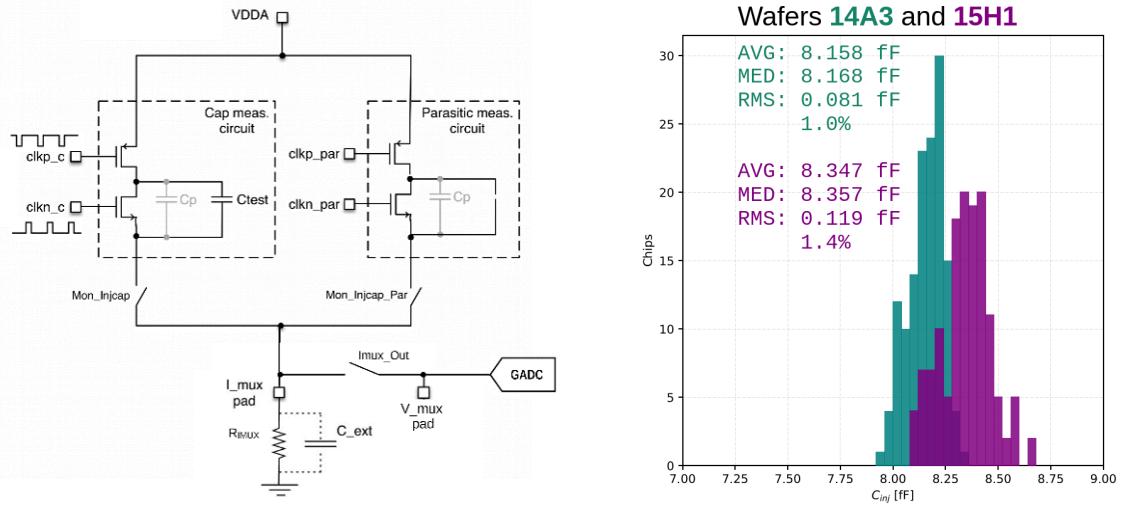

A dedicated charge injection capacitor calibration circuit, shown in figure 19, is available in the ACB to make a precise injection capacitor measurement per chip, during wafer probing to enable calibrated charge injections in the final systems.

Shown AFE test results are in general for bare chips without bump-bonded pixel sensors. Bump bonded assemblies with sensors have only recently become available in sufficient quantity and quality to make detailed AFE characterization with these. No significant changes in pixel chip performance have been seen when tested with a bump bonded pixel sensor, except an AFE noise increase of 10–30 e, as can be expected when having increased input capacitance [19].

**Figure 19.** Left: Pixel Injection capacitor ( $C_{test}$ ) measurement circuit measuring the average current, with on-chip ADC (GADC) or external pin ( $V_{\_Mux\_pad}$ ), when charging and discharging the injection capacitor at a constant injection rate. An equivalent branch, without injection capacitor, enables to measure parasitic capacitance ( $C_p$ ) of the circuit. Right: measured injection capacitor dispersion over two wafers from the same production lot.

#### 4.1 CMS Linear front-end

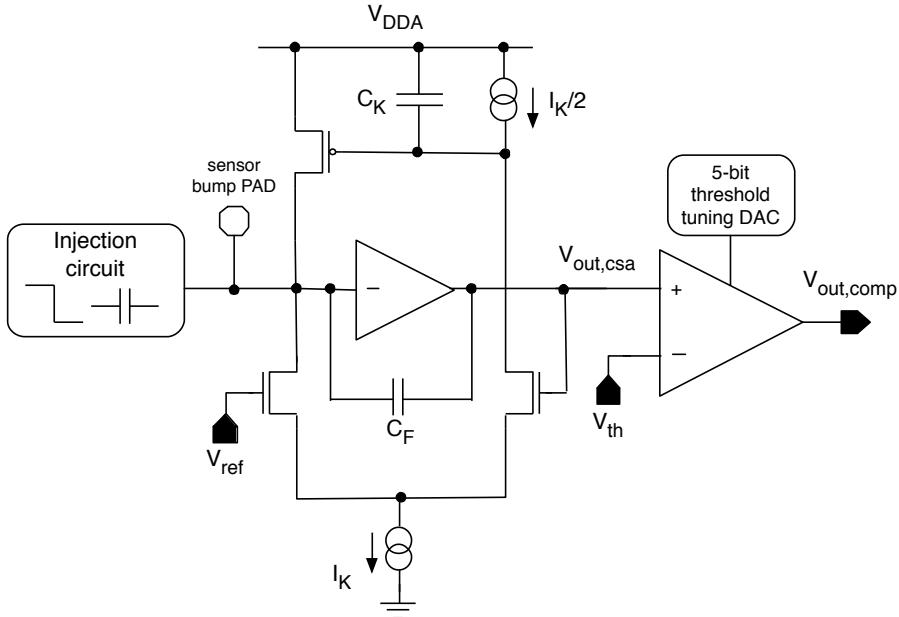

The schematic of the linear analog front-end [18, 19] adopted in the RD53B/C-CMS chip is shown in figure 20 with a Charge Sensitive Amplifier (CSA) with Krummenacher feedback [14] complying with the expected radiation induced detector leakage and providing a linear discharge of the feedback

**Figure 20.** Schematic of CMS linear analog front-end.

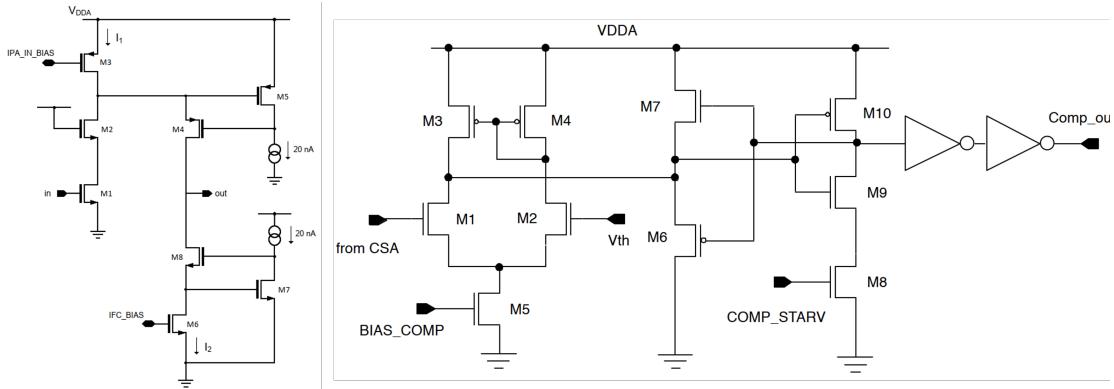

**Figure 21.** Transistor level implementation of linear AFE pre-amplifier (left) and comparator (right).

capacitor  $C_F$ . The choice of a single amplification stage is dictated by power consumption and area constraints with a charge sensitivity, set by  $C_F$ , of around  $26 \text{ mV/ke}^-$ . The signal from the CSA is fed to a low power comparator with a 5 bit, current-mode binary weighted DAC for local threshold tuning. The front-end has been optimized for a linear response for an input charge up to 30 ke and features an overall current consumption of 5  $\mu\text{A}$ .

The charge sensitive amplifier, shown in figure 21 left, is based on a folded cascode input stage with two local feedback networks, composed of the M4-M5 and M7-M8 pairs, boosting the signal resistance at the output node. A 3  $\mu\text{A}$  biasing current in the input branch and 200 nA in the cascode branch are responsible for most of the power consumption with a simulated open-loop DC gain of 76 dB with  $-3 \text{ dB}$  cutoff frequency at 140 kHz with an effective closed loop peaking time of 22 ns. Noise is dominated by the input device and the PMOS transistor in the feedback. The comparator shown in figure 21 right, has a transconductance stage (M1-M5) followed by a Trans-Impedance Amplifier (TIA) (M6-M10) for fast switching, with an optimized feedback network (M6 and M7) for acceptable time-walk. Two inverters are used at the output to assure fast signal transitions to the digital pixel sampling logic. The layout and measured analog pulse shape are shown in figure 22.

**Figure 22.** Left: linear AFE layout. Right: typical analog waveform before comparator, with 1–10 ke charge injections, measured on analog output of the RD53A chip.

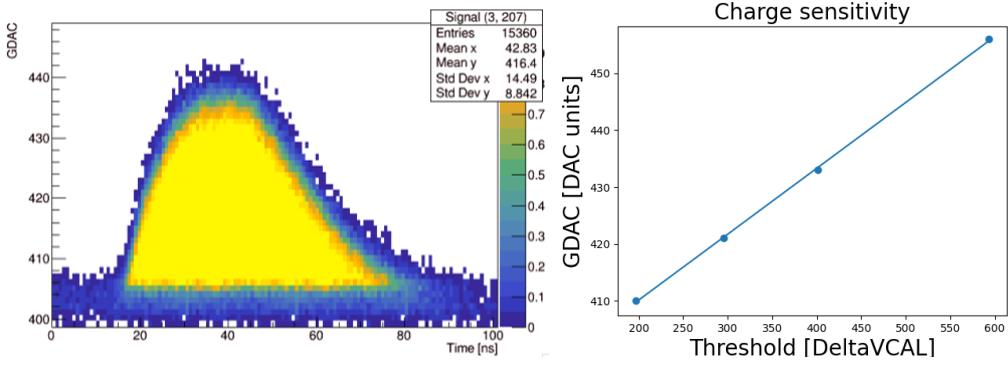

**Figure 23.** RD53B-CMS Linear AFE pulse shape and threshold linearity. Left: reconstructed pulse shape from threshold and time scan combined with high precision TDC information, in fast mode with short TOT charge encoding. Right: threshold as function of global threshold setting. GDAC: global threshold setting, DeltaVCAL: injection voltage DAC setting (5 e per LSB).

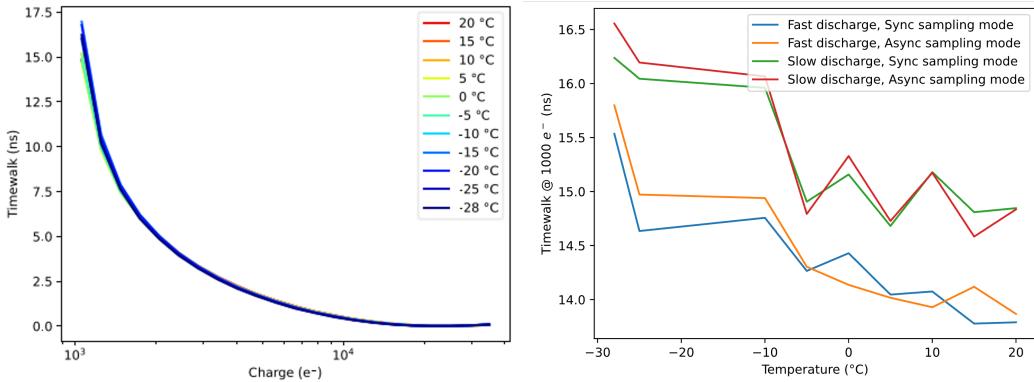

**Figure 24.** RD53B-CMS Linear AFE time-walk as function of injected charge (Left), at slow discharge and sync mode, and at different temperatures (right), at 1000 e threshold for different combinations of sync/async mode and fast/slow discharge rate.

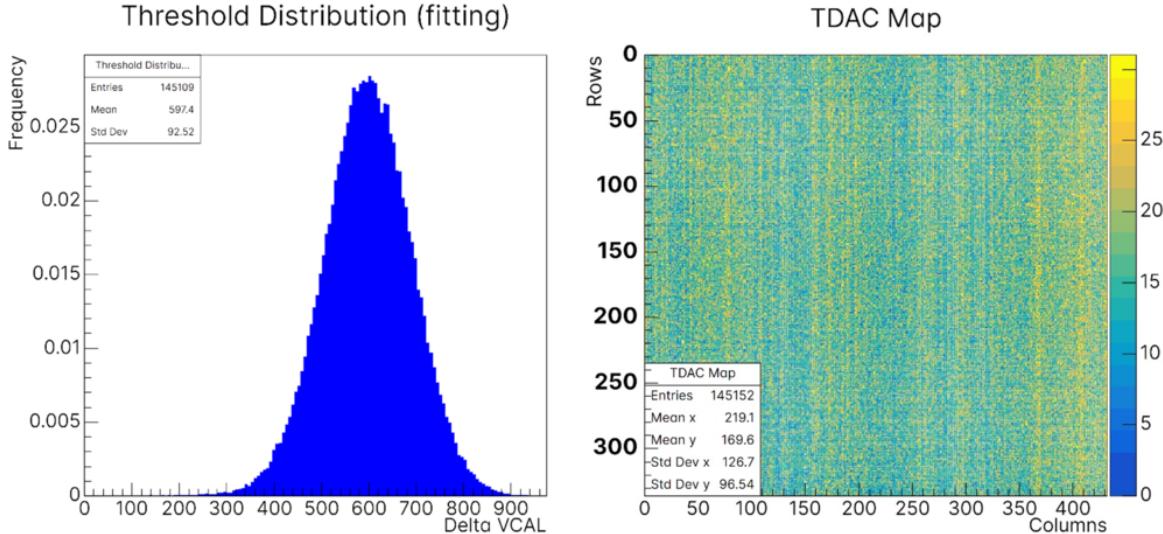

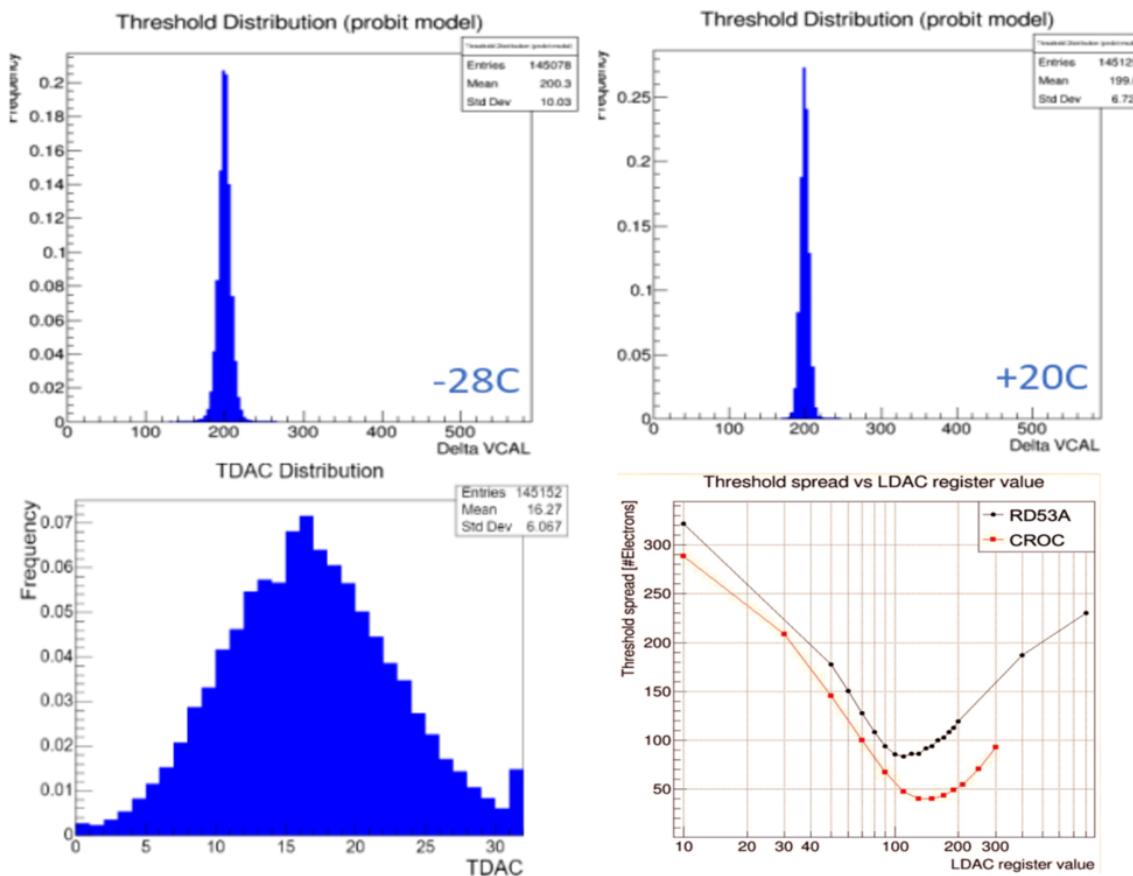

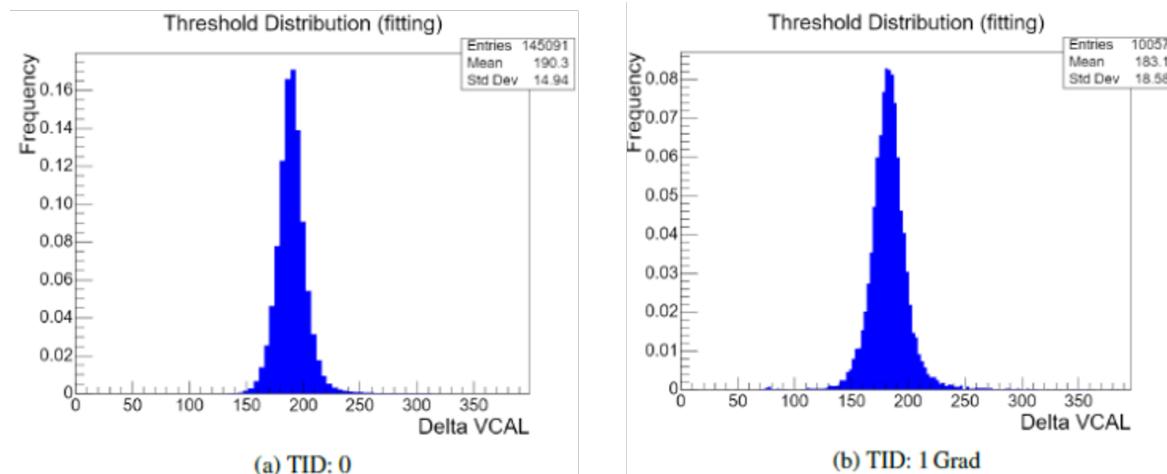

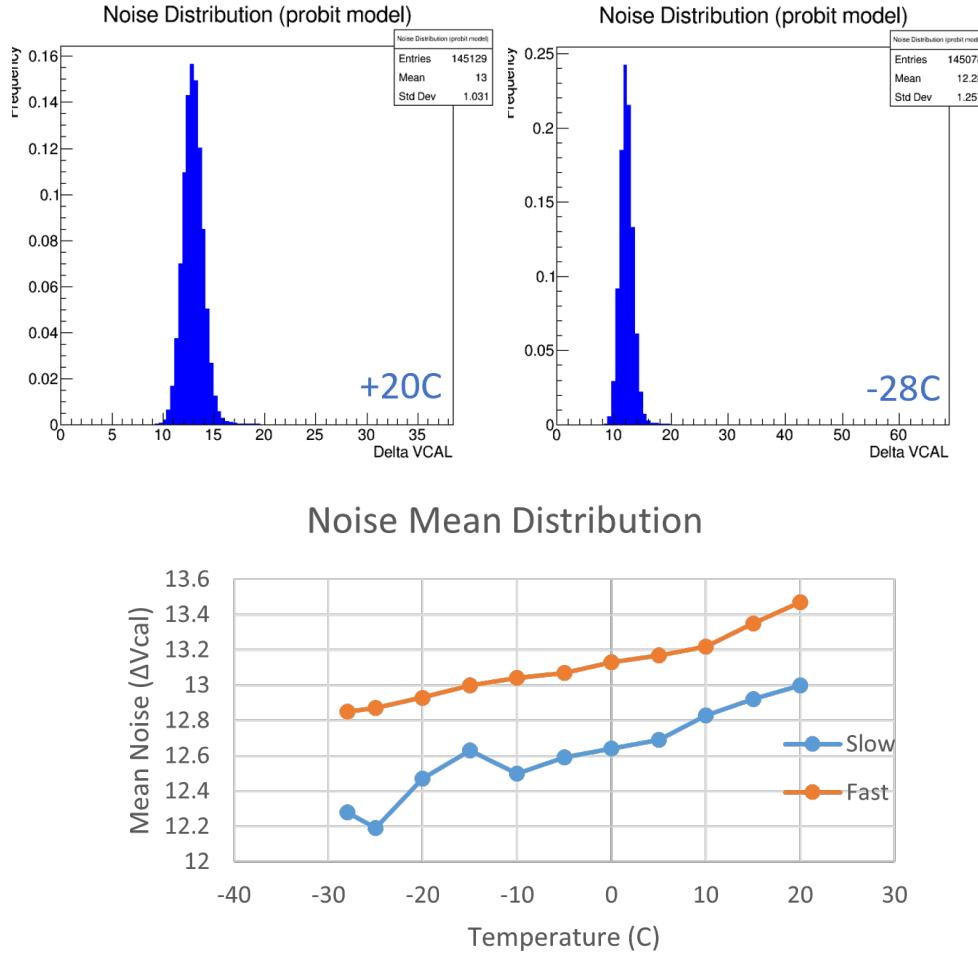

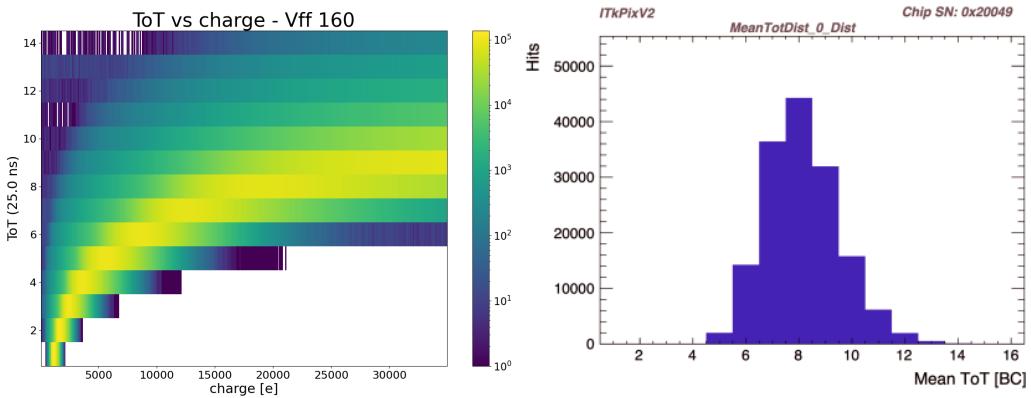

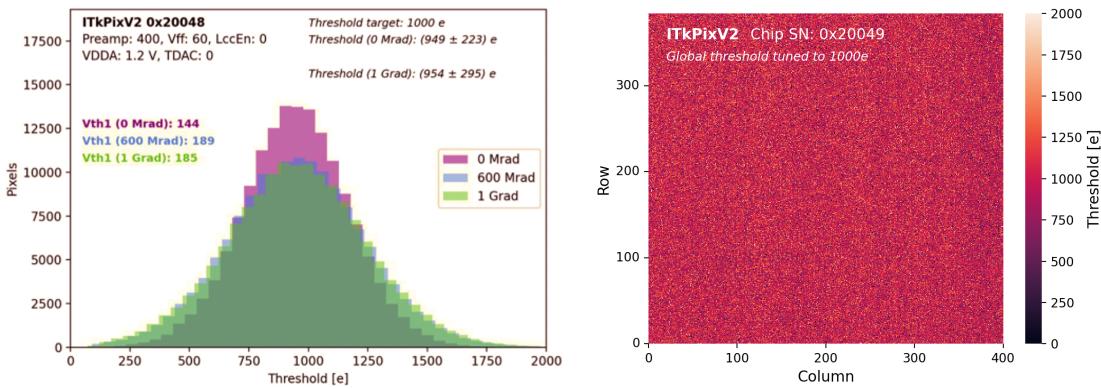

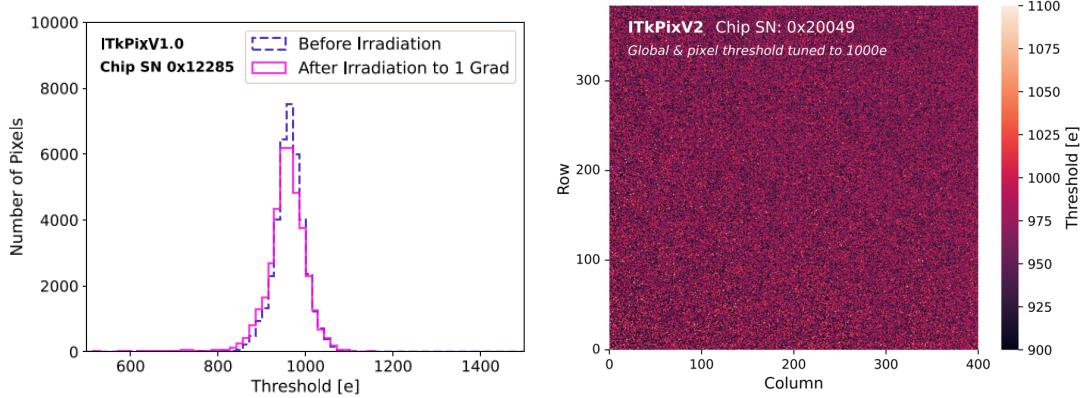

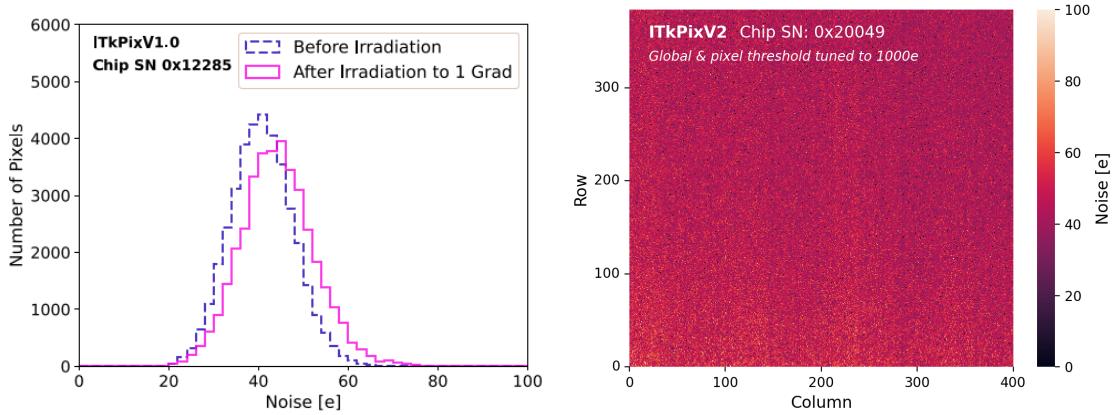

A reconstructed AFE pulse shape from a combined scan of injection time and threshold with TOT is shown in figure 23 together with threshold linearity as function of global threshold setting. Figure 24 shows the time-walk measured as function of injected charge together with time-walk dependency on chip temperature with sync and async sampling and for fast (inner layers) and slow (outer layers) TOT discharge times. TOT linearity, with saturation, is shown in figure 25 together with its dependency on sampling clock phase for different charge injections and TOT spread across the pixel array. Figure 26 shows untuned (before local threshold trimming) threshold dispersion over the full pixel array together with a 2D map of appropriate pixel trimming to obtain tuned pixel threshold dispersion as shown in figure 27, when using the optimal trimming DAC range to cover the full dispersion range with the best possible resolution. Tuned pixel threshold dispersion at 1000 e before and after 1 Grad irradiation is shown in figure 28 with only a small degradation of threshold dispersion (after re-tuning at 1 Grad). Finally pixel noise distribution is shown in figure 29 at room temperature and cold with mean noise as function of temperature for fast and slow TOT discharge. No noticeable change of noise has been observed with irradiation up to 1 Grad.

**Figure 25.** RD53C-CMS Linear AFE TOT linearity and spread. Left: average TOT value as function of injected charge with linear encoding up to 15 ke, of interest for hit position interpolation between pixel hits in pixel cluster, for different relative clock phases (CE unit = 25 ns/32 = 0.78 ns). Right: measured TOT linearity and spread across pixel array.

**Figure 26.** RD53B-CMS Linear AFE untuned threshold dispersion together with 2D trim DAC values to get uniform threshold (effectively shows untuned threshold map). Delta VCAL = 5 e. A column structure is clearly visible, coming from columns of pixel islands with their biasing drivers.

No differences have been seen for the linear AFE in the RD53B-CMS and RD53C-CMS chips. In short it can be summarized that the linear AFE with a planar (or 3D) bump-bonded pixel sensor complies with the defined requirements in table 1 and works fully satisfactory for the CMS pixel detector upgrade at a 1000 e threshold with  $\sim 50$  e dispersion, mean noise below  $\sim 70$  e (80-100 e with pixel sensor), time walk below 17 ns with a linear TOT charge measurement and radiation tolerance up to 1 Grad. At the time of writing, extended testing of the RD53C-CMS chip is ongoing in the CMS pixel detector project with different sensor types on pre-production modules in test beams and after irradiation.

**Figure 27.** RD53B-CMS Linear AFE tuned threshold dispersion at 1000 e threshold at cold and room temperature together with trim-DAC tuning (TDAC) distribution and effective threshold spread as a function of used trim-DAC range (LDAC). Delta VCAL = 5 e. CROC = RD53B-CMS.

**Figure 28.** RD53B-CMS Linear AFE tuned threshold dispersion at 1000 e before and after irradiation to 1 Grad. Delta VCAL = 5 e.

**Figure 29.** RD53B-CMS Linear AFE noise (without sensor) as function of temperature and for fast and slow TOT discharge. Delta VCAL = 5 e.

## 4.2 ATLAS differential front-end

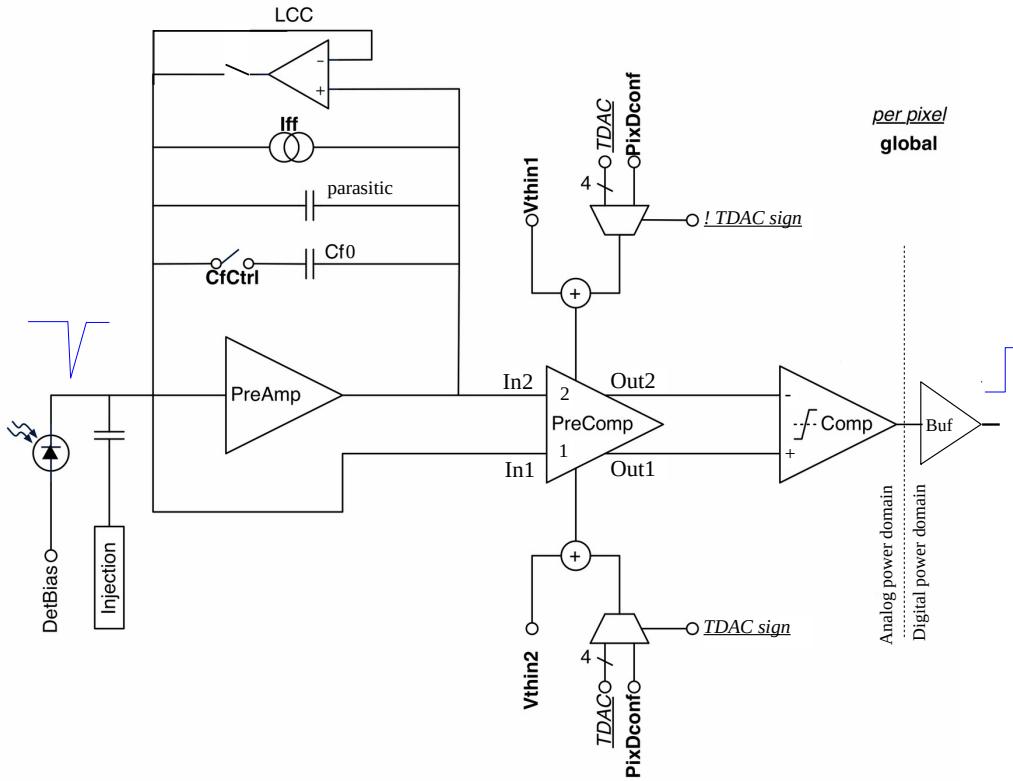

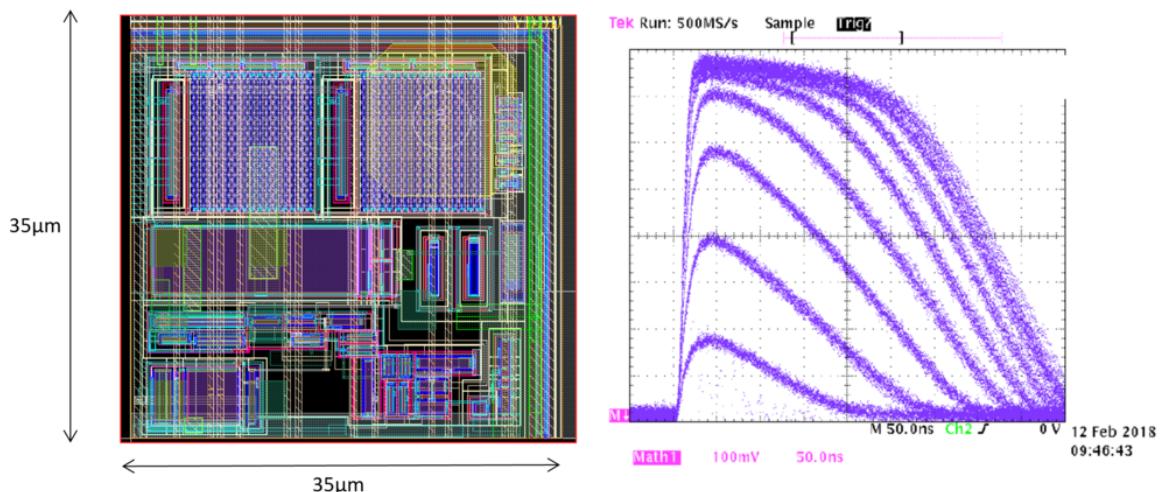

The differential AFE, as shown in figure 30, consists of 4 main stages: Pre-amplifier, Leakage Current Compensation (LCC), Pre-comparator, and Comparator. It is made from a single ended pre-amplifier followed by a pseudo differential comparator circuit.

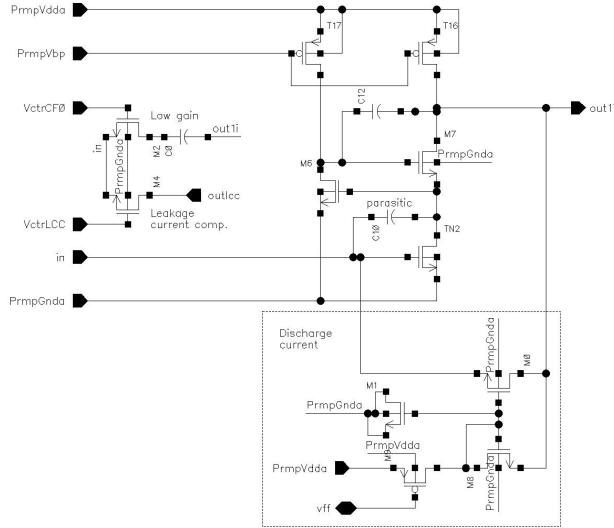

The topology of the pre-amplifier Charge Sensitive Amplifier (CSA) is based on a regulated cascode, with programmable constant current feedback (Iff) for the TOT charge measurement as shown in figure 31. The gate length and inversion region of the input device, as well as the implemented feedback circuit, give the lowest possible noise at low power supply current. Due to its simplicity (small area), the pre-amp exhibits gain compression and non-linear discharge for large signals. This non-linear behavior can be considered advantageous for a pixel detector, giving good resolution at low input charge and compressed dynamic range for large signals, in a similar fashion as the optional digital 6 to 4 bit dual slope TOT encoding. The pre-amp gain is maximized using only the intrinsic input device and parasitic routing capacitance for charge integration (parasitic). A reduced gain programmable option is available, adding a feedback capacitor in parallel (Cf0).

**Figure 30.** General schematic of ATLAS differential analog front-end. It can be noticed that the differential comparator has two 4 bit trim DACs, driven by the same 4 bit TADC values. The TDAC\_sign bit determines which of the two differential branches is used for threshold trimming (effectively the 5th threshold adjust bit).

**Figure 31.** Transistor level schematic of single-ended analog pre-amp using parasitic capacitance for charge integration and its discharge circuit. Optional Leakage Current Compensation (LCC) and low gain feedback capacitance shown on left side.

Leakage Current Compensation (LCC) can be enabled with an optional auxiliary feedback path with a tunable low-pass pole to drain detector leakage. LCC is required for a pixel sensor leakage current above 2 nA. It eliminates DC operation point shifts of the pre-amp, that will otherwise reduce effective dynamic range of the pre-comparator and pixel threshold in the presence of detector leakage. It also reduces leakage current induced noise by having a reduced feedback bandwidth.

The pre-comparator implements two essential features of the AFE. First, it utilizes the DC working point of the pre-amplifier input in concert with the pre-amplifier output (nominally at the same DC level) to form a differential thresholding circuit. Second, it includes a differential trim DAC to compensate for pixel-to-pixel threshold variation. Both the global and trimmed thresholds are set by source-followers, in each branch of the differential pre-comparator. This improves power supply noise rejection for internal and external power supply noise. A differential to single-ended comparator with a two stage open-loop class-A amplifier generates the discriminated hit signal, followed by an inverter for output buffering. Layout and measured analog pulse shape are shown in figure 32.

**Figure 32.** Left: differential AFE layout. Right: typical analog waveform before comparator, with 1-10 ke charge injections, measured on analog output of the RD53A chip without pixel sensor. Saturation of the analog signal giving TOT compression at large charge injections can be noticed.

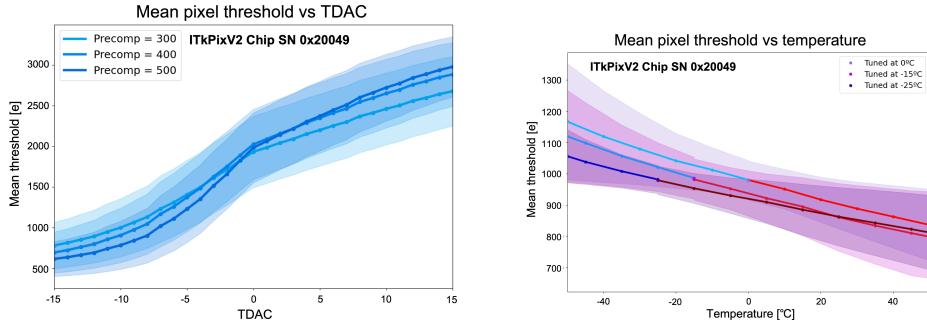

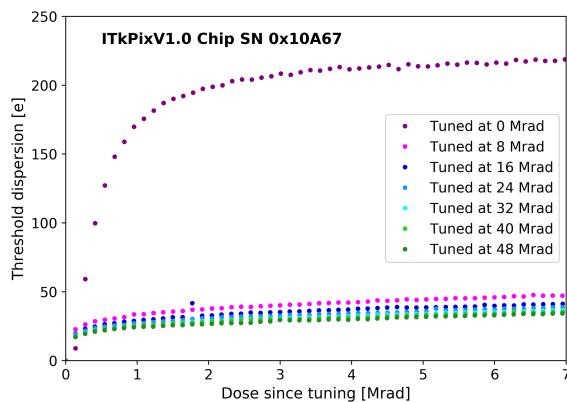

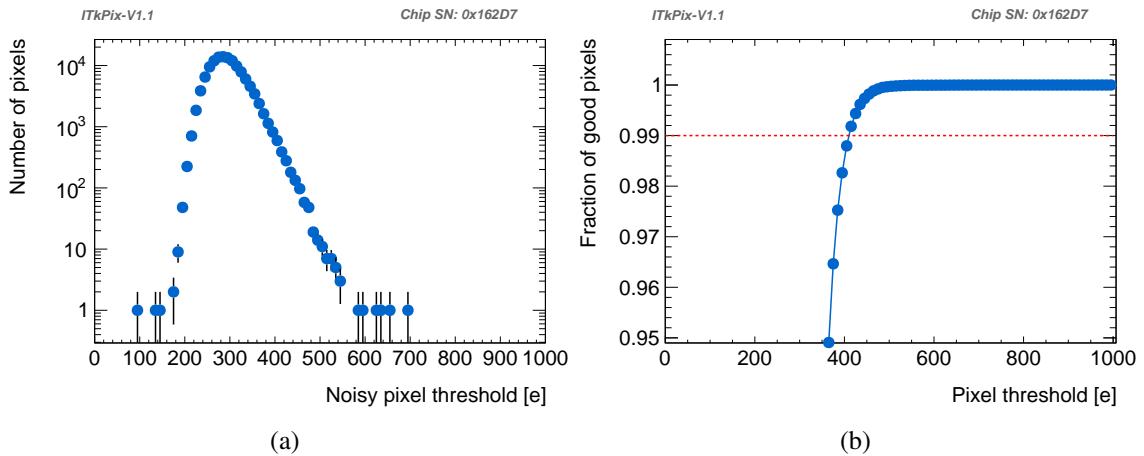

Measured threshold dependency on threshold settings is shown in figure 33 together with its temperature dependency. Figure 34 shows the time-walk of the differential AFE and figure 35 shows TOT linearity and dispersion together with TOT spread for a constant charge injection. There is no in-pixel tuning for pixel to pixel TOT dispersion, as this can be corrected offline if required. Un-tuned threshold dispersion is shown in figure 36, before and after irradiation. Tuned threshold dispersion is shown in figure 37 pre-irradiation and after 1 Grad. An indication of threshold de-tuning with radiation is shown in figure 38 showing only noticeable de-tuning during the first few Mrad of irradiation (typical of several CMOS technologies). Noise variation is shown in figure 39 with no significant noise increase after 1 Grad. Finally figure 40 shows the number and fraction of noisy pixels as function of tuned threshold, and can be seen to be very low for thresholds above 500 e.

In short it can be summarized that the differential AFE with a bump-bonded planar (or 3D) pixel sensor complies with the defined requirements in table 1 and works fully satisfactory for the ATLAS

**Figure 33.** Left: RD53C-ATLAS Differential AFE threshold as function of threshold trimming (TDAC) for different Precomp biasing settings for the discriminator (affects power consumption, offsets, dispersion and time-walk. Default setting = 400). Right: threshold temperature dependency for threshold tuned to 1000 e at different temperatures (0, -15, -25°C) with nominal Precomp = 400.

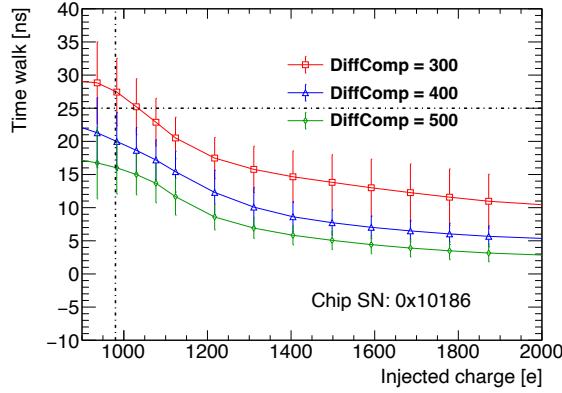

**Figure 34.** RD53C-ATLAS Differential AFE time-walk for different pre-comp biasing settings (DiffComp). To be noticed that for large charges the curves end up with different time offsets so effective time-walk change is difference between time for 1000 e injection and time for 2000 e injection ( $\sim 15$  ns for DiffComp = 500 and  $\sim 20$  ns for DiffComp = 300).

**Figure 35.** RD53C-ATLAS Differential AFE TOT linearity and spread across pixel array at 1000 e threshold. Left: measured TOT as function as injected charge. Right: TOT spread across pixels for a constant 8 ke charge injection. TOT discharge does not have in-pixel tuning. Pixel TOT charge measurement non-linearity and variation between pixels can be compensated for off-line as needed.

**Figure 36.** RD53C-ATLAS Differential AFE untuned threshold dispersion. Left: before and after irradiation. Right: un-irradiated dispersion across pixel array at 1000 e threshold.

**Figure 37.** Differential AFE tuned threshold dispersion. Left: RD53B-ATLAS Dispersion before and after 1 Grad irradiation. Right: RD53C-ATLAS Un-irradiated dispersion across pixel array at 1000 e threshold.

**Figure 38.** RD53B-ATLAS Differential AFE threshold de-tuning at different irradiation levels. The large transistors used in the AFE mainly have (minor) parameter changes during the first 0–2 Mrad irradiation (this has also been seen for other CMOS technologies). Thereafter radiation effects saturate and remain constant. Relatively frequent threshold tuning will therefore be required during initial running of the pixel detectors at high luminosity.

**Figure 39.** RD53C-ATLAS Differential AFE noise variation at 1000 e threshold. Left: before and after 1 Grad Irradiation. Right: variation across pixel array after 1 Grad.

**Figure 40.** RD53B-ATLAS Differential AFE noisy pixels as function of threshold. Left: number of noisy pixels (relative noise occupancy greater than  $10^{-6}$ ). Right: fraction of not-noisy pixels. The differential AFE can be seen to have excellent noise performance with thresholds as low as 500 e.

pixel detector upgrade at a 1000 e threshold with  $\sim 50$  e dispersion, noise of  $\sim 55$  e (65-85 e with pixel sensor), time walk as low as  $\sim 15$  ns, a compressed TOT charge measurement, and radiation hardness up to 1 Grad. At the time of writing, extended testing and qualification of the RD53C-ATLAS chip is ongoing in the ATLAS pixel detector project with final pixel sensors on pre-production modules in test beams and after irradiation.

## 5 Data buffering and triggering

Alternative hit buffering and triggering architectures have been evaluated to choose a final implementation fulfilling trigger latency buffering requirements, with the lowest possible hit loss and acceptable power consumption. Fitting the logic in the available area in the pixel array is a critical design constraint. Sharing of hit buffering between 4 neighbor pixels was quickly identi-

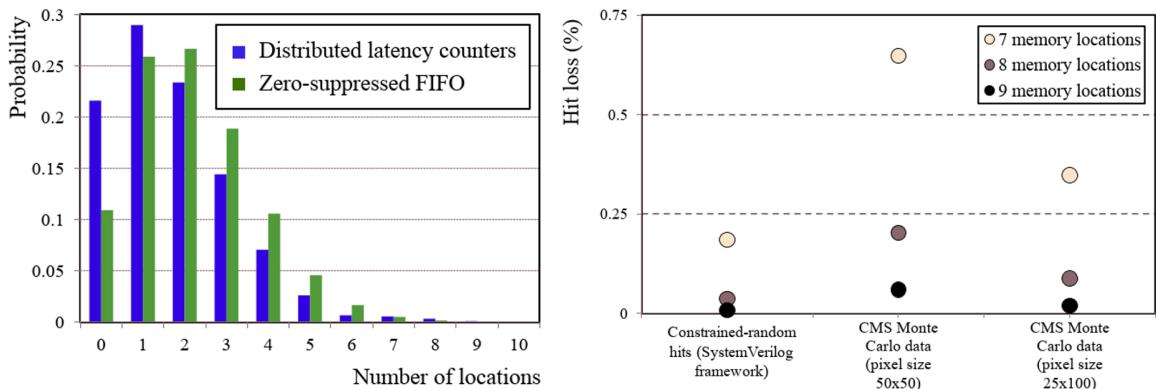

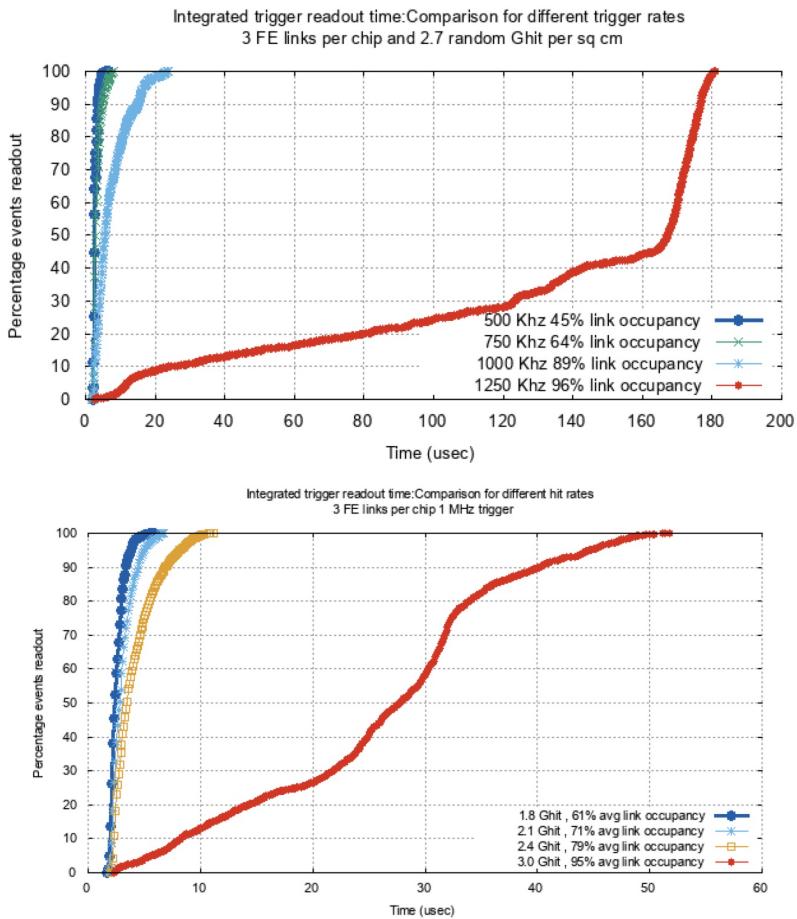

fied to be critical to profit from locally clustered hits from a single particle (typically from 1–4 pixel hits per cluster). Initial studies found a pixel region of  $2 \times 2$  pixels to be ideal for the high hit rate in the middle of the inner barrel layer. Further studies, with detailed Monte Carlo hit data from different parts of the detectors, with both  $50 \times 50 \mu\text{m}^2$  and  $25 \times 100 \mu\text{m}^2$  sized pixels, determined that a pixel region of  $4 \times 1$  pixels is a better overall optimization for the two pixel detector layouts. Pixel hits are clustered from traversing particles depending on multiple factors: location of traversing particle, particle angle, sensor thickness, magnetic field, and also radiation damage in the pixel sensor. Two alternative buffering architectures were implemented in the RD53A prototype [12]. The “zero-suppressed FIFO” architecture uses two levels of shared FIFOs to minimize the required number of storage bits, at the cost of increased logic complexity. The “distributed latency counter” architecture minimizes logic complexity, at the cost of an increased use of memory cells. Both schemes were found fully functional in simulations and in the RD53A chip. The final choice of using the distributed latency counter architecture was based on effective hit losses, and minimizing logic and layout complexity to assure best possible SEU/SET tolerance.

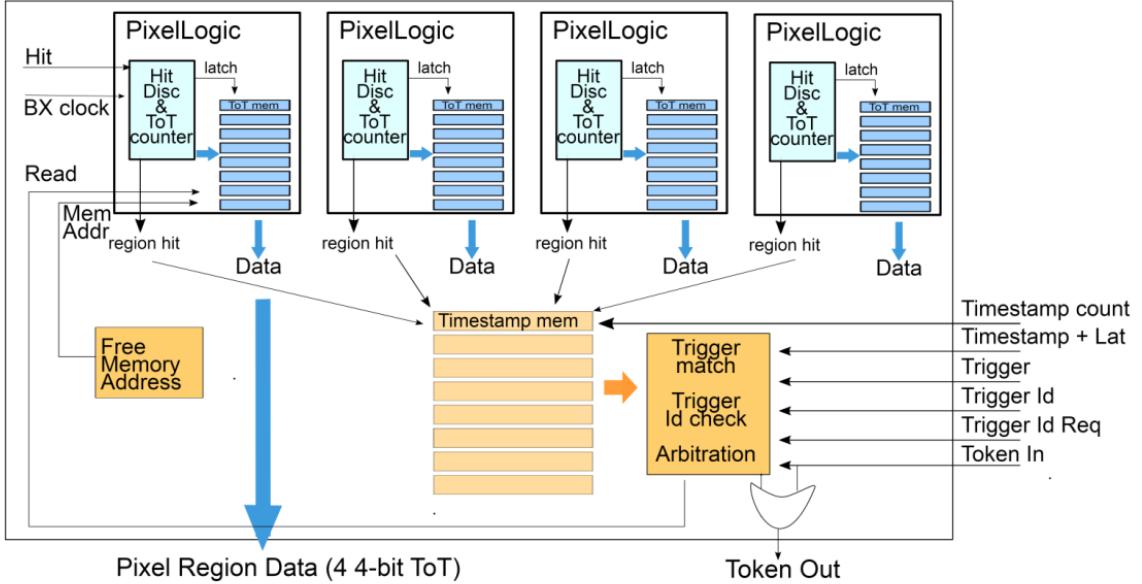

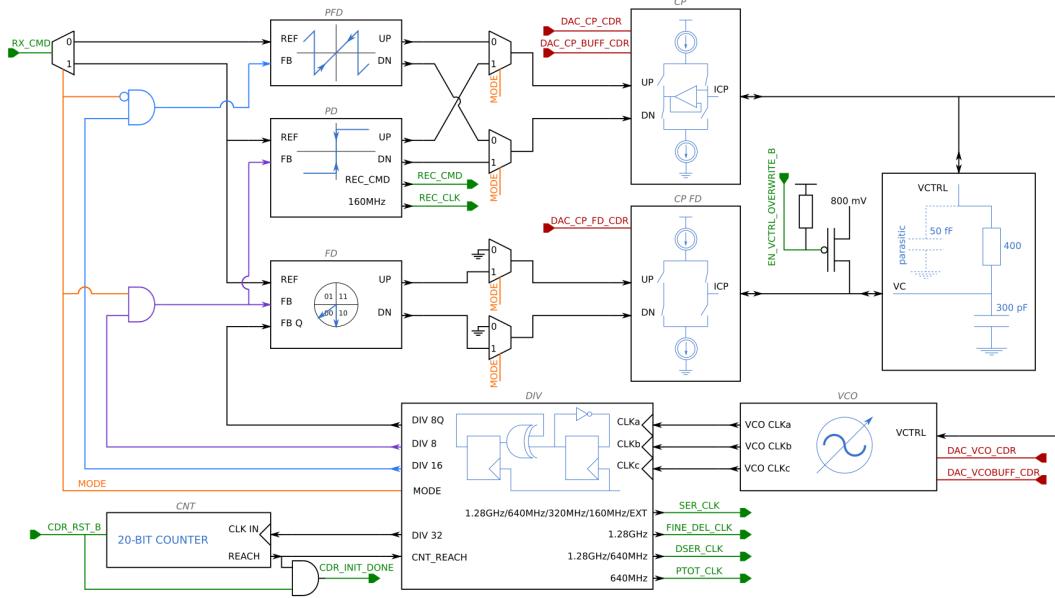

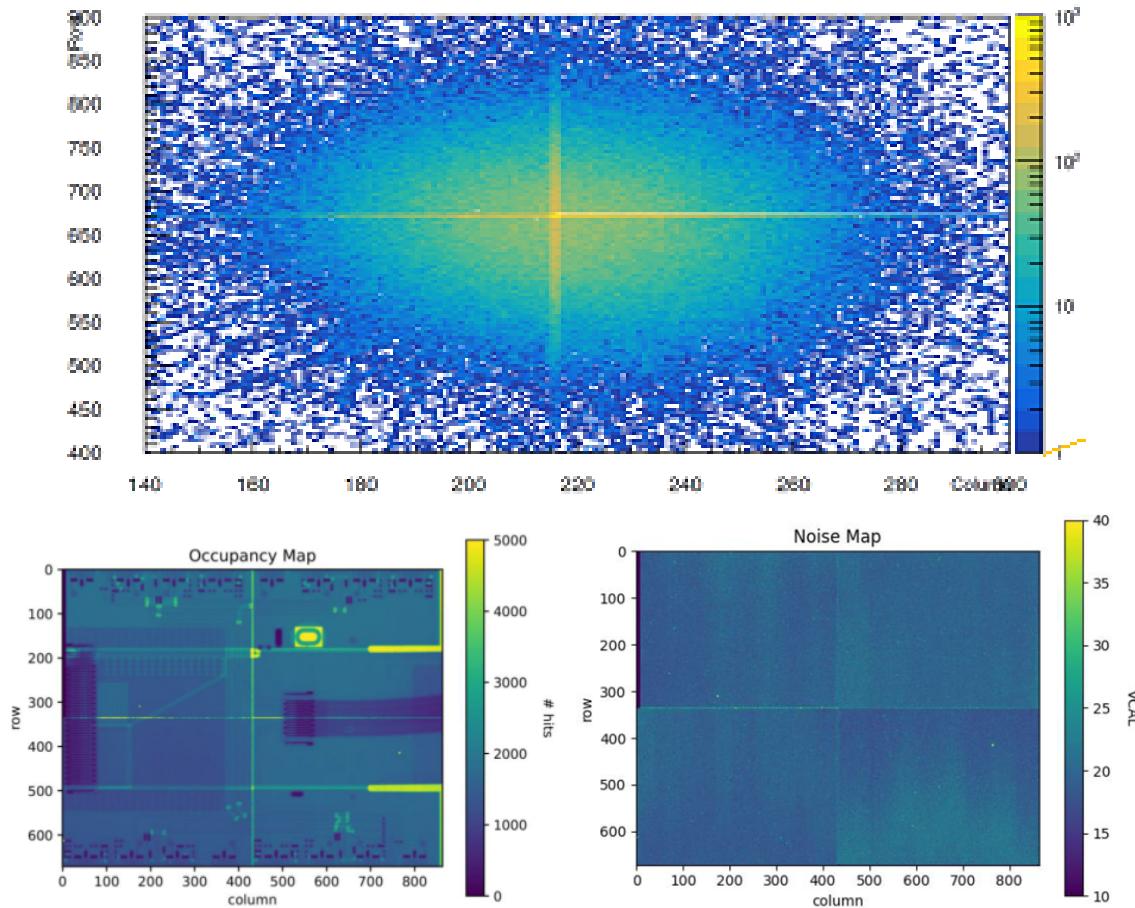

Sampled pixel hit signals are processed and buffered in small local pixel regions consisting of 4 pixels. When one, or multiple, pixels in a pixel region have a hit, a 4 bit TOT register per pixel stores the measured TOT. The four TOT values in the pixel region are stored in a local latency buffer location together with a 9 bit Bunch ID time-stamp from a central 40 MHz Bunch-ID counter, as indicated in figure 41. A TOT register value of 1111 bin indicates that no pixel hit has been detected. Writing to a 4 pixel buffer location is completed when all 4 TOT counting measurements are finalized. The pixel region hit capture and buffering is non-blocking so a new hit arriving in following clock cycles, on a pixel not part of the first cluster, is captured in the next free buffer location. Each pixel region has 8 local latency buffer locations. Hit losses from the limited hit buffering, at the highest hit rates of  $3 \text{ GHz/cm}^2$ , have been modeled and simulated with Monte Carlo hit data and shown to be well below 1% [12], as shown in figure 42. Significant design efforts have been invested to fit the required latency buffering in the highly constrained pixel area, using a custom made compact multi-bit latch and highly optimized logic. Effective hit losses have been measured with X-ray irradiations of a pixel module, as shown in figure 43 and scaled to anticipated HL-LHC hit rates (compensated for different cluster size between X-rays and particles in the HL-LHC environment).

When a latency buffer location is in active use, the stored Bunch ID is continuously compared to a global latency counter with a relative offset, defining the effective trigger latency. When they match and an active trigger is generated, the buffer location is flagged as triggered, or the buffer location is released. Bunch ID information is then replaced with a trigger event ID to handle the readout of multiple pending triggered events with hit data.

Digital logic in the pixel array uses optimized clock gating to obtain significant power savings. The hit capture logic in the pixel region has active local clocking only during the capture window of a hit (effective time window depends on TOT length), making the instantaneous power consumption dependent on hit rates. This requires careful optimization of local power decoupling capacitors, both on-chip and on pixel modules, to work reliably with serial powering.

Readout of triggered hit data from the local pixel region latency buffers is controlled by a core column readout controller at the end of each core column bus. Pixel cores, consisting of  $2 \times 8$  pixel regions ( $8 \times 8$  pixels), share a core column readout bus, with its associated controller in the DCB.

## PixelRegionLogic

**Figure 41.** Pixel region logic for distributed latency counter buffering with TOT and Bunch-crossing ID time tags (Timestamp count). Hit detection is made per pixel, with storage of associated hit TOTs (blue). Hit time stamps are stored in common with associated buffer management logic, handling triggering and token based readout from the pixel array (yellow). Reproduced with permission from [12].

**Figure 42.** Left: pixel region latency buffer occupancy probability for the two alternative architectures evaluated. The selected architecture is the distributed latency counter buffers for  $4 \times 1$  pixel regions. It has lowest hit loss for high hit rates and has the simplest and most compact implementation. Right: hit loss probability for distributed latency counter buffers with detector Monte Carlo hits at  $3 \text{ GHz/cm}^2$  for 7, 8 and 9 buffer locations. Eight Buffer locations are used in final chip implementations as it fits in the available area and have acceptable hit loss in the highest rate regions (below 0.25 %). Reproduced with permission from [12].

**Figure 43.** RD53B-CMS X-ray hit loss probability from latency buffering as function of hit rate, measured in a non irradiated chip with a planar sensor. Left: corrected for analog TOT dead-time. Right: for estimated equivalent HL-LHC hit rate, with particle cluster size of 1.53 hits/cluster.

Readout from the pixel array is initiated by the core column controller signaling the event ID and asserting a readout token. Pixel regions having triggered hit data await the arrival of the readout token and then assert their hit data on the readout bus together with its pixel region address and passes the token. When the token finally returns to the pixel core column controller, all event data in the core column for this event ID has been collected. Pixel core columns have independent readout controllers that can be in the process of reading out different events. This improves the effective readout rate from the array when having multiple pending triggered events. A central trigger table keeps track of events awaiting readout from the pixel array.

A pixel core column bus is covering a large number of pixel regions. This limits the effective readout speed on this long bus and makes it significantly affected by radiation degradation of its bus drivers and handshake logic. The effective readout time is two clock cycles per pixel region with hit data, that with radiation degradation can get as long as 3(4) clock cycles (configurable). It has been confirmed in simulations that such a reduced pixel array readout speed is compatible with required hit and trigger rates. In practice it has not yet been seen necessary to use this extended readout period for highly irradiated chips.

It is possible by configuration to constrain the maximum number of pixel regions to read out from each core column per event, to prevent possible readout congestion from events with excessive number of hits. It is also possible to constrain the maximum time available to readout all pixel core columns, thereby effectively constraining the maximum number of hits per event.

An extended two level trigger mode for potential future trigger upgrades has been implemented. In this mode, L0 triggered hits remain in the pixel region latency buffers for a configurable time-out period (max 25.6 μs). During this time-out period (L1 trigger latency), events can be flagged for readout (L1 accept), or by default be rejected (L1 reject).

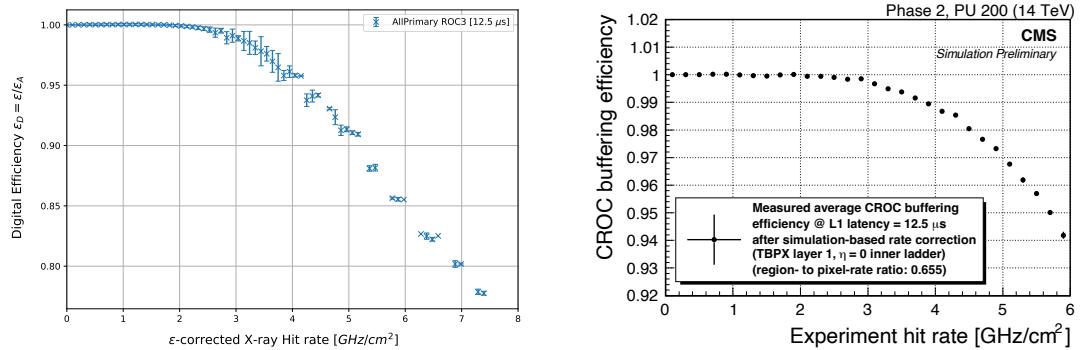

Event data accepted for readout will go through multiple levels of processing, event building, buffering and formatting, as shown in figure 44, before being ready for final readout via the serial readout links. Total event data buffering before final readout is of the order of 25 kBytes in the DCB. Significant hit data buffering also takes place in the pixel array, from when a trigger is received until having been read out from the pixel array. This buffering assures efficient hit data de-randomization that enables good readout bandwidth utilization.

**Figure 44.** Outline of processing and buffering of event data in multiple stages from pixel core columns, processed by End Of Column (EOC) logic, to final readout link Aurora formatting via Clock Domain Crossing (CDC) buffer. Intermediate FIFO's are used for data buffering to enable the different stages to work concurrently to sustain the required bandwidth. Barrel-shifters are used for effective data merging and re-packaging of zero-suppressed event data between processing stages. Colors shown in data buffers represent event data, belonging to same triggered event, in different stages of processing. Data flow: triggered hits are read out of the pixel array with circulating read tokens in the core columns to hit map encoders with column addresses to EOC buffers. Hit data from EOC buffers are merged in two buffering stages (DC and CDC buffers) to form 64 bit data words for chip readout.

## 6 Control and readout

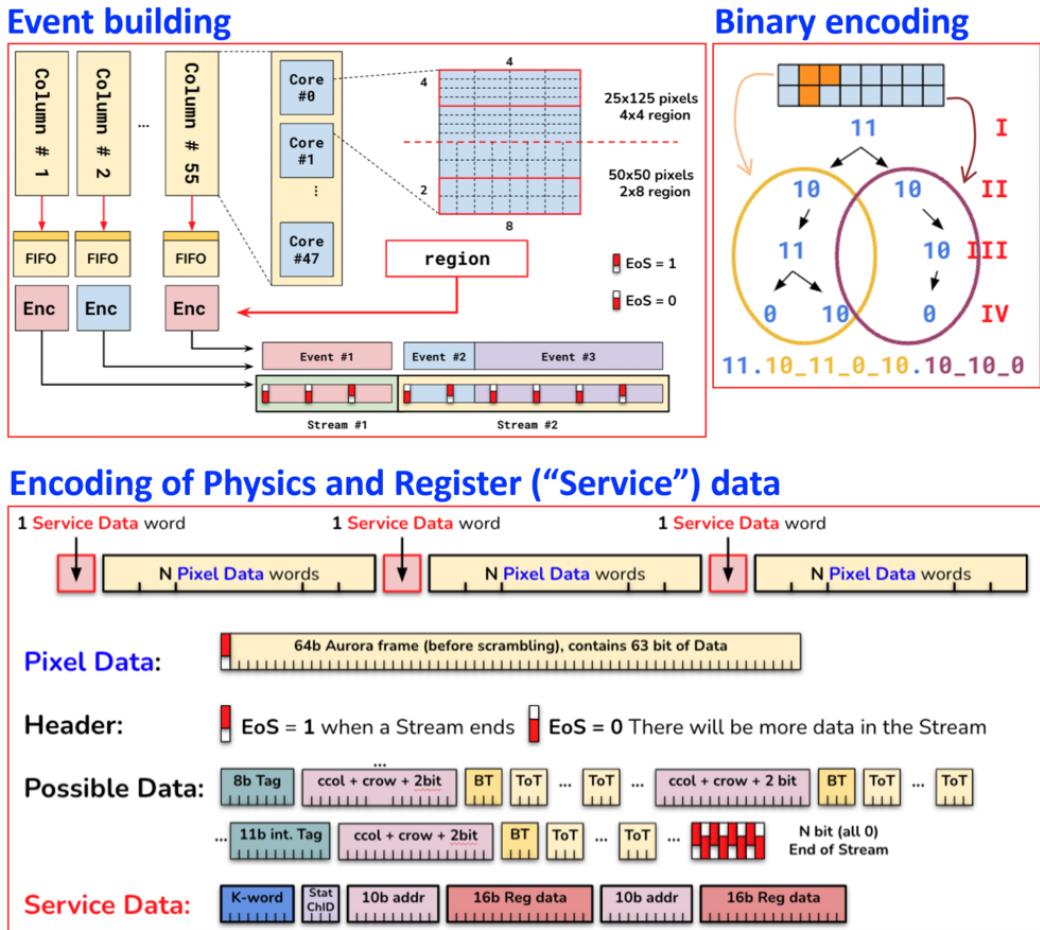

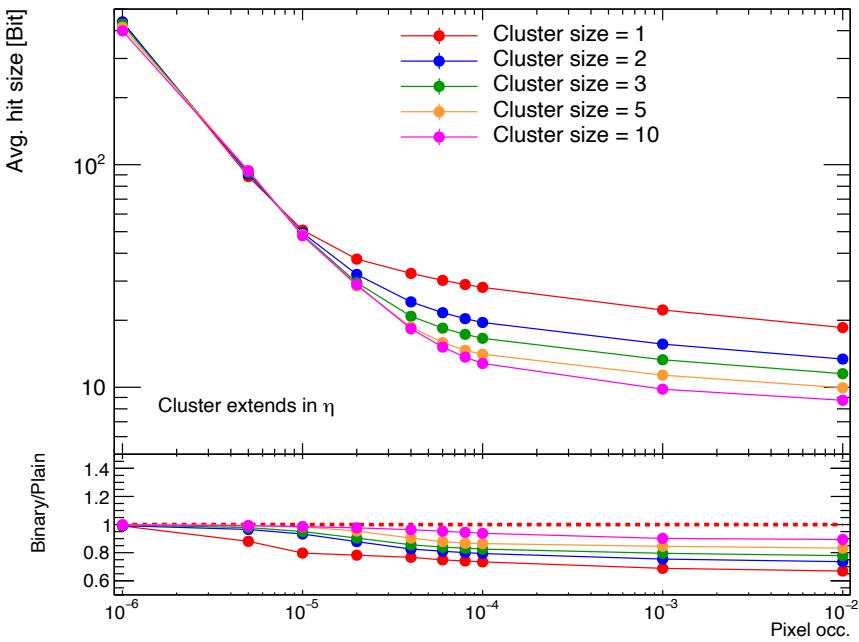

The control and readout interfaces of the RD53 chips are highly constrained from their specific use in an inner high rate and low mass detector with *lpGBT* based optical links to DAQ and control systems. An efficient variable length hit data encoding format, called binary tree encoding, has been developed to minimize readout bandwidth. The use of 1, 2, 3 or 4 readout links per pixel chip, and the option of merging data from 2 or 4 chips into one link, enables the number of required readout cables to be optimized and minimized for different system configurations. Control and readout links use DC balanced encoding, for the AC coupled links required in a serially powered detector system.

A 160 Mbits/s DC balanced differential control link, with transmission error detection, has been specifically developed to address up to 15 chips (e.g. chip specific configuration) and with broadcast capability (e.g. common configuration). It has an embedded 40 MHz reference clock with sub-ns timing control, to appropriately align pixel hit sampling with bunch collisions. Real time commands at 25 ns level have priority over control, configuration and monitoring commands. The control link has sufficient bandwidth to perform continuous scrubbing of pixel configuration, in case needed in the hostile radiation environment (see section 9).

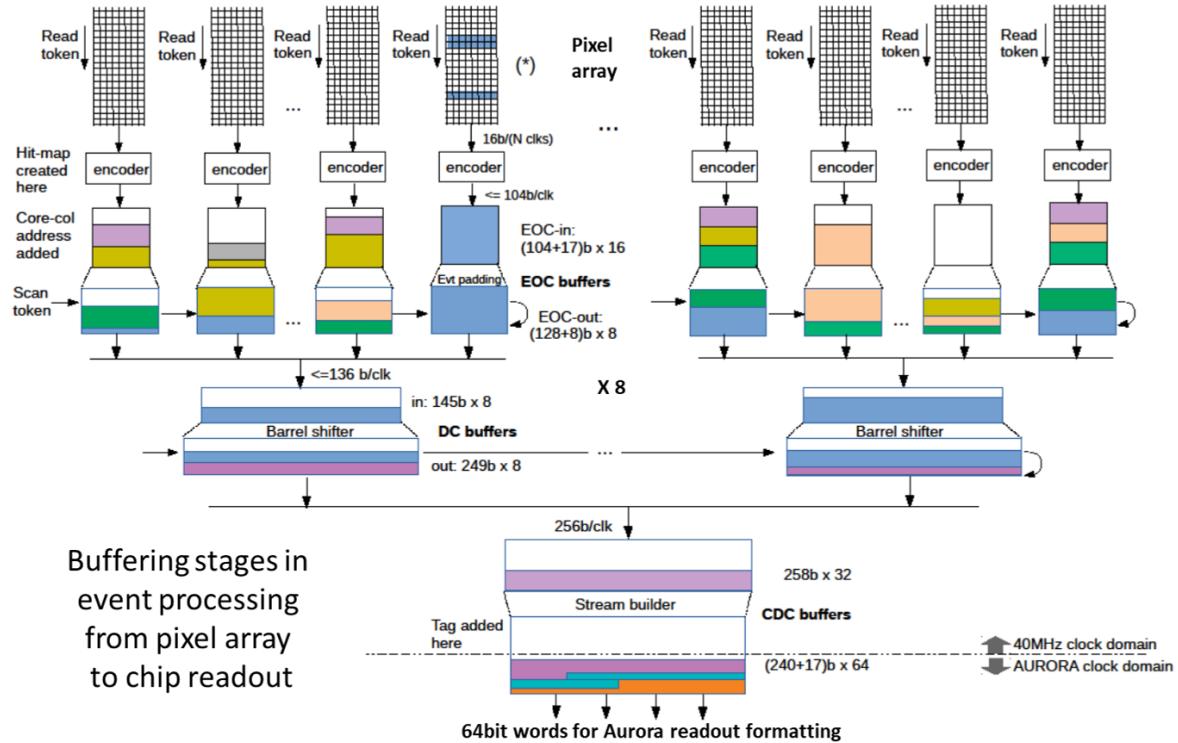

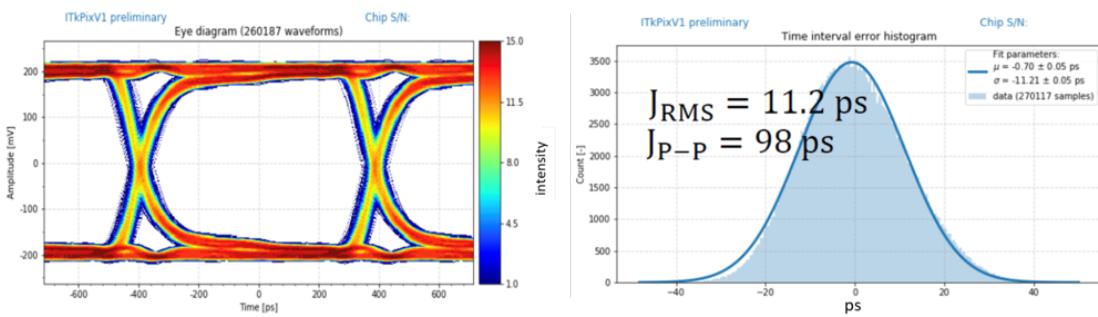

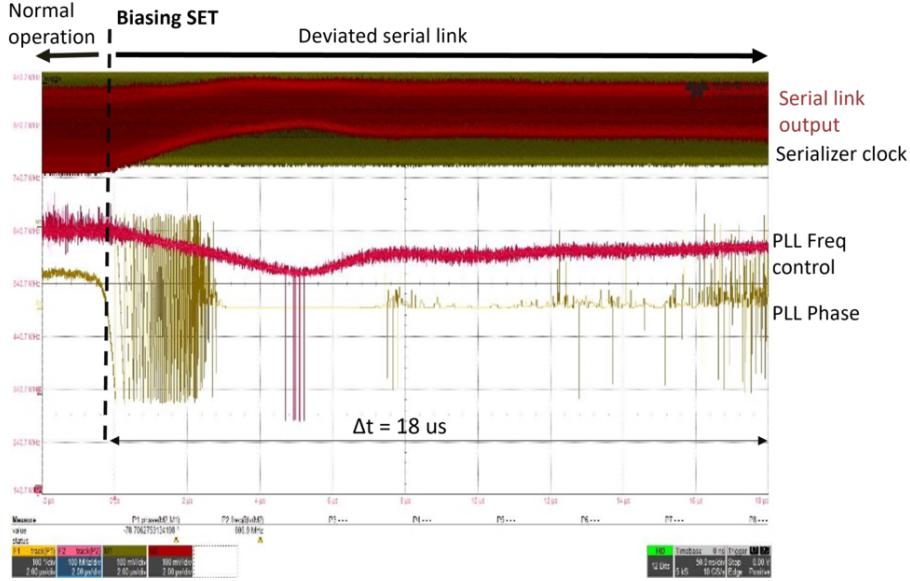

A radiation hard 1.28 GHz Phase Locked Loop (PLL) has been developed for appropriate Clock and Data Recovery (CDR) from the control link and generate the clock for the serial readout links. Initial prototypes have been extensively tested and gradually improved to get lower jitter with sufficient TID and SEU/SET tolerance [21, 22]. The PLL locks to the 160 Mbits/s control stream and generates the required on-chip clocks. The 40 MHz hit sampling clock is generated with a frame alignment circuit, based on regular sync symbols. It can be phase shifted in steps of 0.78 ns to perform precise time alignment to particles from the HL-LHC collisions. The PLL is separately powered to allow additional external filtering of the analog chip power in case needed. The classical PLL architecture, with frequency and phase detectors, is shown in figure 45 with measured jitter and eye diagram of a readout link shown in figure 46.

**Figure 45.** PLL generating high frequency clocks used in the chip. PLL control loop with combined Phase Detector (PD) and Phase - Frequency Detector (PFD) controlling a Voltage Controlled Oscillator (VCO) via analog Charge Pumps (CP) and loop filter. Frequency multiplication from the 160 Mbits/s control link to the 1.28 GHz serializer clock is obtained with SEU protected counters (CNT and DIV).

**Figure 46.** Measured eye diagram and PLL jitter on 1.28 Gbits/s serial readout.

Particular emphasis has been put on efficient and reliable startup, resetting and configuration of the chips for use in a serially powered detector system in a hostile radiation environment. At

power-on startup (see also SLDO startup in section 7) the chip will initially use a default hardwired configuration. Only when all critical re-configuration data have been downloaded, will these settings be activated with a dedicated enable code. Full chip data path and buffers can be cleared quickly or specific parts of the chip can be reset with specific commands. In a worst case scenario where control link synchronization is lost, and it does not self recover as it should normally be the case, a dedicated link reset can be applied that initializes all chip configuration and starts a full chip re-synchronization (as done at power up). This is done by running the control link at a low frequency (invalid link bit rate, but still compatible with AC coupling), that is detected by the chip to be out of normal working range. This removes the need of using power cycling to recover chip operation, which is highly undesirable in a large serial powered system with high voltage sensor biasing.

Up to 4 readout links of 1.28 Gbits/s (or 640 Mbits/s or 320 Mbits/s) are available per chip for readout and monitoring. A subset of the Aurora encoding [20] is used as it supports all the required features: DC balanced 64B/66B encoding, framing with minimum overhead, multi lane support, data and service type frames. Aurora formatting is well documented and well supported for FPGAs in test and DAQ systems, with general event and service data formatting as indicated in figure 47. When used in final ATLAS/CMS pixel detectors with lpGBT optical links, two levels of link encoding (Aurora 64B/66B plus lpGBT FEC) will be present, to be decoded by the DAQ system FPGAs. It should be noted that Aurora formatting does not use Forward Error Correction (FEC). Single bit transmission errors (or SEUs in pixel chip serializer) can therefore occasionally cause the corruption of event fragments. The use of FEC was considered but it was found to have too large bandwidth overhead, especially in combination with the extensive error correction used in the lpGBT. The RD53C-CMS chip has the option to add a CRC (Cyclic Redundancy Check) at the end of each event.

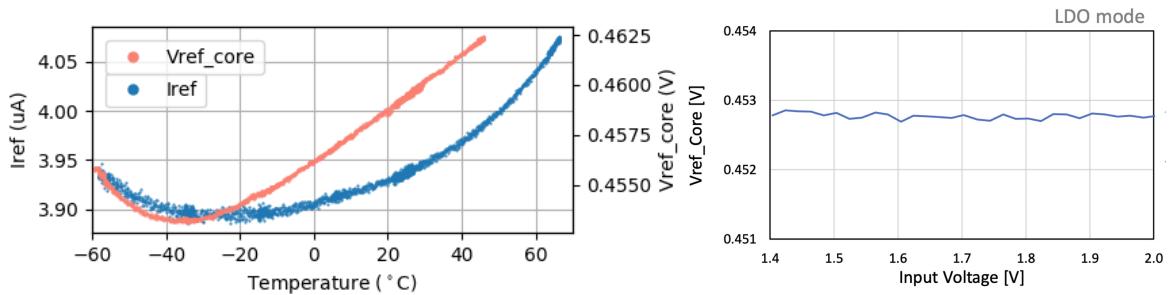

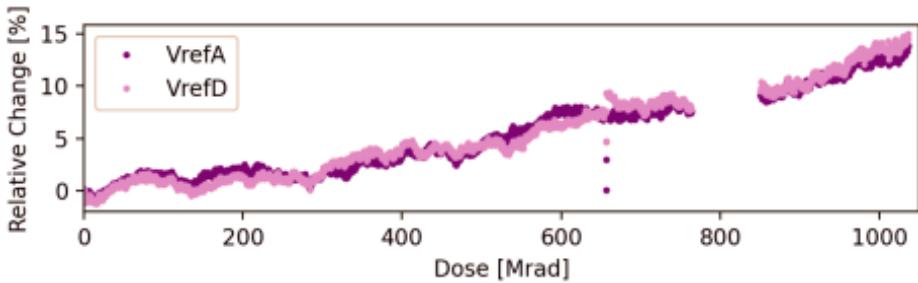

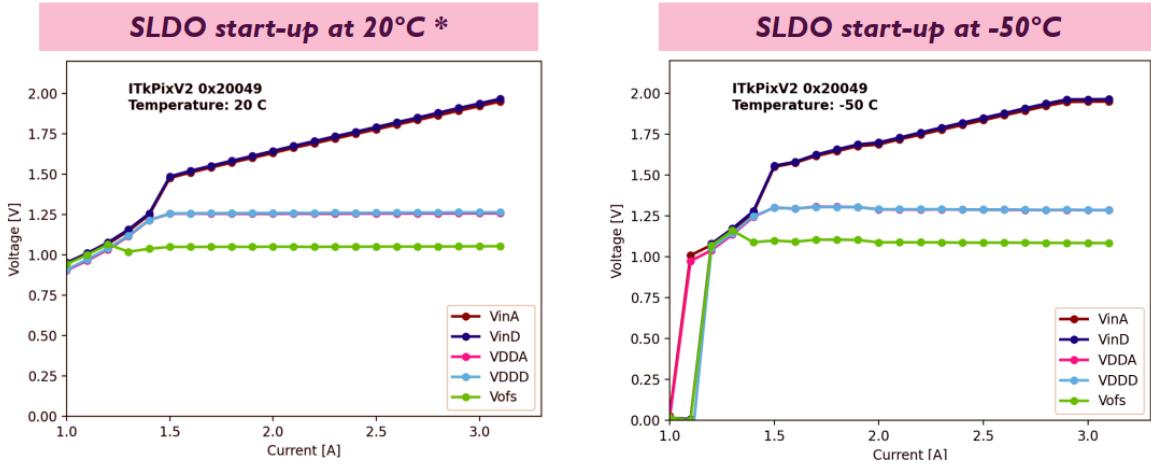

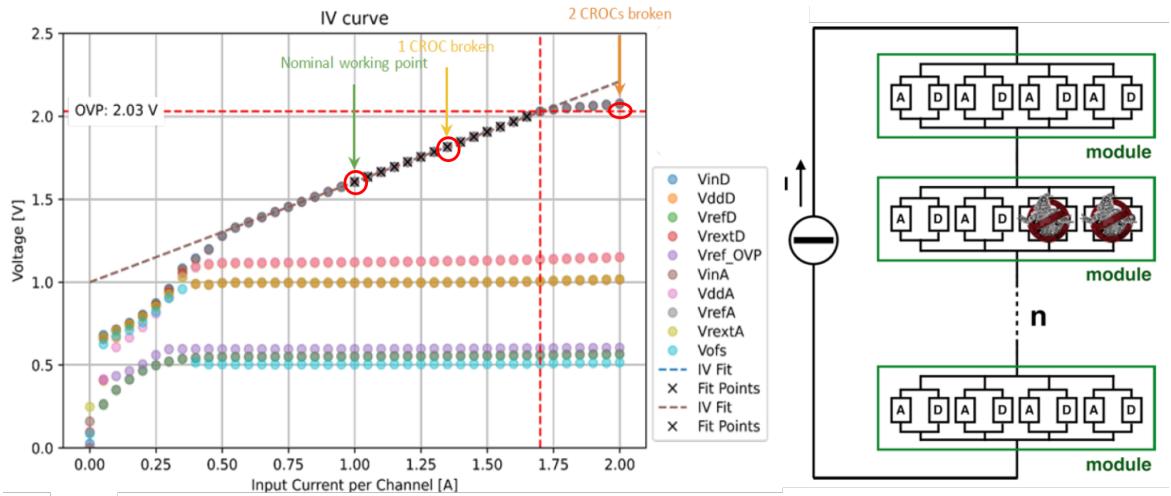

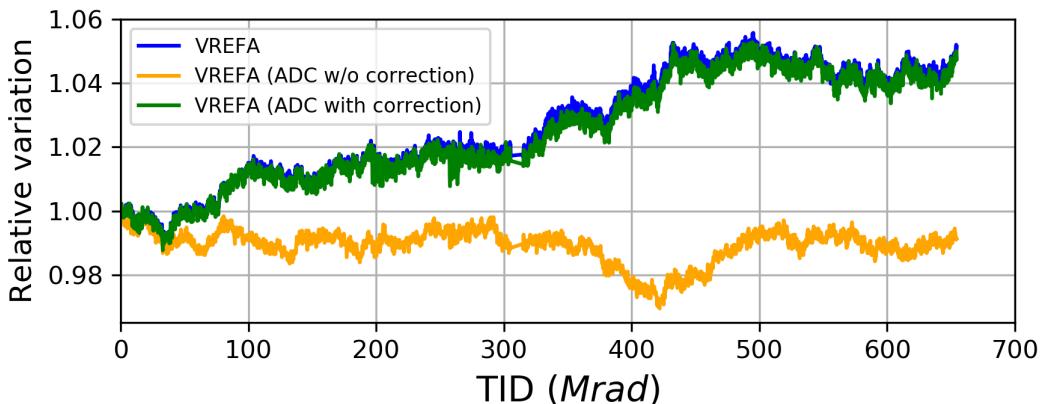

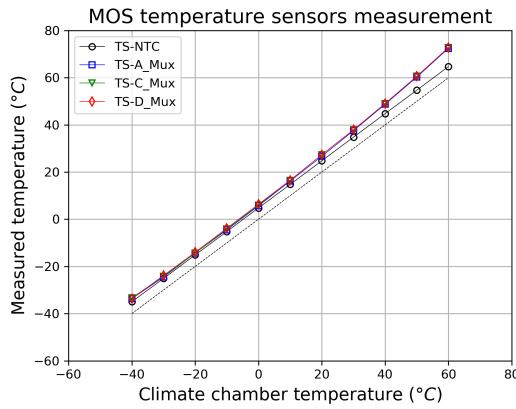

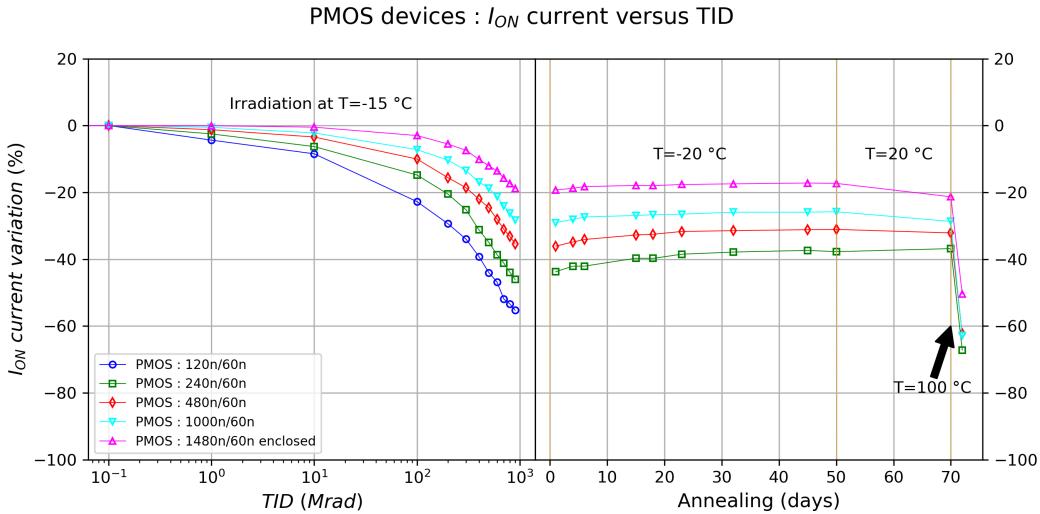

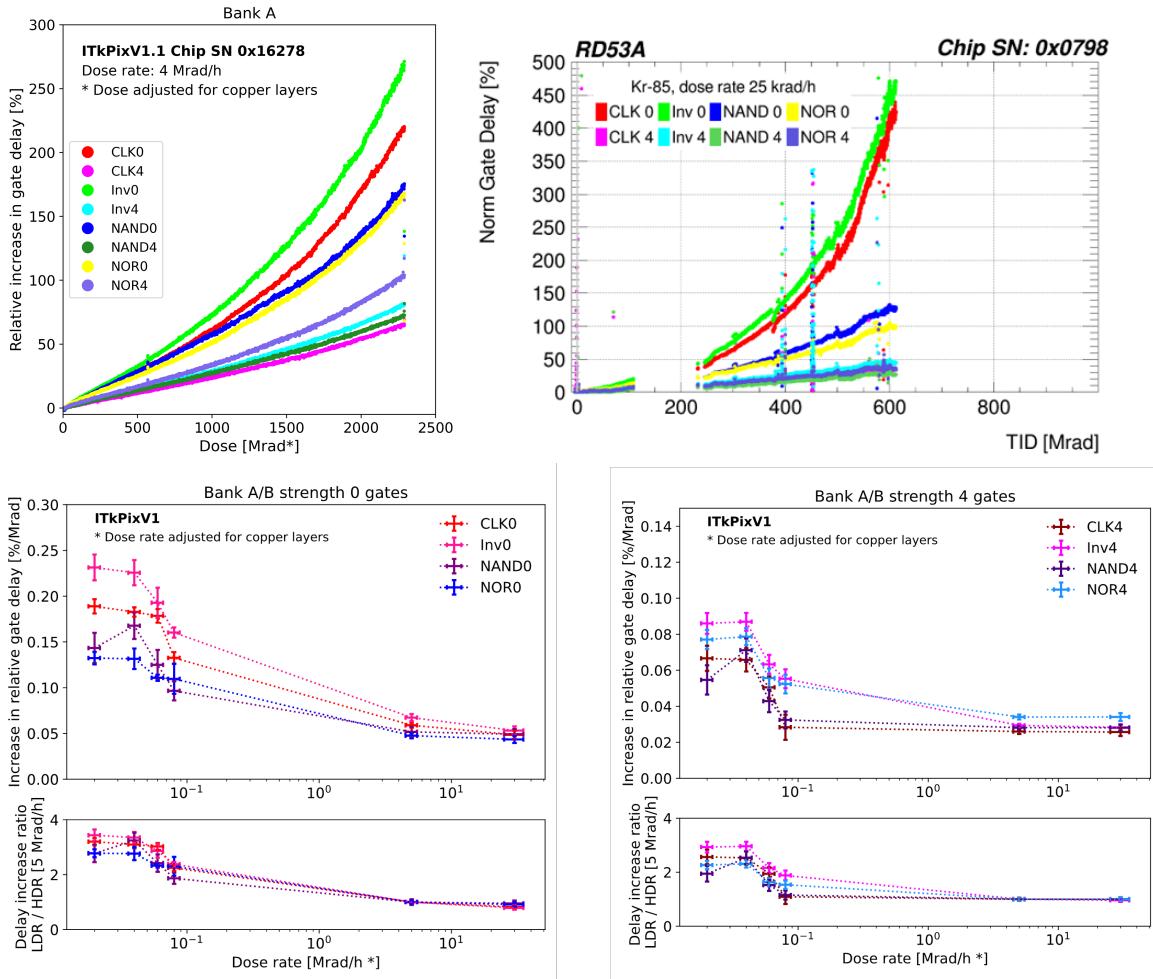

Raw zero-suppressed hit data from the pixel regions consist of a pixel region address followed by 4 bit TOT information from the 4 pixels in the region, with TOT=1111 bin indicating no hit. This is already a relatively efficient data format for clustered hits, compared to individual pixel hit addresses with TOT (18 bit pixel address + 4 bit TOT = 22 bit per hit). An optimized binary tree hit encoding scheme can further reduce readout bandwidth by 10–20 %. It is also possible to suppress TOT charge readout information, having only binary hit information, giving a data reduction of ~ 30 %.