# Universität Bonn

## Physikalisches Institut

### Development of an FPGA-based FE-I3 pixel readout system and characterization of novel 3D and planar pixel detectors

Jens Janssen

USBpix is an FPGA-based test and readout system which was developed for the ATLAS FE-I3 pixel readout chip. The main part of this diploma thesis covers the code maintenance and further development of the USBpix test system. Particular attention will be given to the FPGA code which was redesigned during this work. In another step to become a fully integrated test system, USBpix was adapted to the requirements of the EUDET JRA1 beam telescope. In a second part, the USBpix test system was used for laboratory characterizations of pixel sensors bump bonded to FE-I3 pixel readout chips. All investigated sensor types, planar n-on-n and n-on-p, and 3D n-in-p, are candidates for future upgrades of the ATLAS pixel detector (IBL and HL-LHC). Detailed charge collection efficiency and noise studies were made on unirradiated as well as irradiated detectors.

Physikalisches Institut der

Universität Bonn

Nußallee 12

D-53115 Bonn

BONN-IB-2010-08

December 2010

# Universität Bonn

## Physikalisches Institut

### **Development of an FPGA-based FE-I3 pixel readout system and characterization of novel 3D and planar pixel detectors**

Jens Janssen

Dieser Forschungsbericht wurde als Diplomarbeit von der Mathematisch-Naturwissenschaftlichen Fakultät der Universität Bonn angenommen.

Angenommen am: 31.12.2010

Referent: Prof. Dr. Norbert Wermes

Koreferentin: Prof. Dr. Marek Kowalski

# Contents

|          |                                                             |           |

|----------|-------------------------------------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>                                         | <b>3</b>  |

| <b>2</b> | <b>The LHC Experiment</b>                                   | <b>5</b>  |

| 2.1      | The LHC Accelerator . . . . .                               | 5         |

| 2.2      | The ATLAS Detector . . . . .                                | 6         |

| 2.2.1    | The Inner Detector . . . . .                                | 7         |

| 2.2.2    | The Calorimeter System . . . . .                            | 8         |

| 2.2.3    | The Muon Spectrometer . . . . .                             | 10        |

| <b>3</b> | <b>Silicon Pixel Detectors</b>                              | <b>11</b> |

| 3.1      | Introduction . . . . .                                      | 11        |

| 3.2      | The ATLAS Pixel Detector . . . . .                          | 12        |

| 3.3      | FE-I3 Pixel Readout Chip . . . . .                          | 14        |

| 3.3.1    | Chip Configuration . . . . .                                | 16        |

| 3.3.2    | Analog Pixel Block . . . . .                                | 17        |

| 3.3.3    | Digital Pixel Block . . . . .                               | 19        |

| 3.3.4    | Chip Periphery . . . . .                                    | 19        |

| 3.3.5    | Future Detector Upgrade Plans . . . . .                     | 21        |

| 3.4      | Semiconductor Pixel Sensors in HEP Experiments . . . . .    | 23        |

| 3.4.1    | Energy Loss of Charged Particles and Signal Formation .     | 24        |

| 3.4.2    | Radiation Damage in Silicon . . . . .                       | 28        |

| 3.4.3    | Sensor Types and Technologies . . . . .                     | 29        |

| <b>4</b> | <b>The USBpix Test System</b>                               | <b>33</b> |

| 4.1      | Introduction . . . . .                                      | 33        |

| 4.2      | Requirements . . . . .                                      | 33        |

| 4.3      | Hardware Parts of USBpix . . . . .                          | 34        |

| 4.3.1    | S3Multi-IO-Board . . . . .                                  | 35        |

| 4.3.2    | Single Module Adapter Card . . . . .                        | 36        |

| 4.3.3    | Single Chip Card . . . . .                                  | 36        |

| 4.4      | Software Framework of USBpix . . . . .                      | 36        |

| 4.4.1    | USB Driver . . . . .                                        | 37        |

| 4.4.2    | SiUSBLib Library . . . . .                                  | 37        |

| 4.4.3    | USBpixdll Library . . . . .                                 | 37        |

| 4.4.4    | USBpixController Class . . . . .                            | 38        |

| 4.5      | Microcontroller Firmware . . . . .                          | 38        |

| 4.6      | FPGA Firmware . . . . .                                     | 39        |

| 4.7      | Integration of USBpix into the Framework of EUDET Telescope | 44        |

|          |                                                              |           |

|----------|--------------------------------------------------------------|-----------|

| <b>5</b> | <b>USBpix Test Setup</b>                                     | <b>49</b> |

| 5.1      | Introduction . . . . .                                       | 49        |

| 5.2      | Aim of Measurements . . . . .                                | 49        |

| 5.3      | The Test Setup . . . . .                                     | 49        |

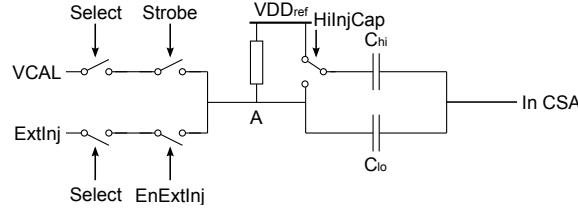

| 5.4      | The Charge Injection Circuit . . . . .                       | 51        |

| 5.4.1    | Measurement of $V_{\text{cal}}$ . . . . .                    | 52        |

| 5.4.2    | Measurement of $C_{\text{hi}}$ and $C_{\text{lo}}$ . . . . . | 52        |

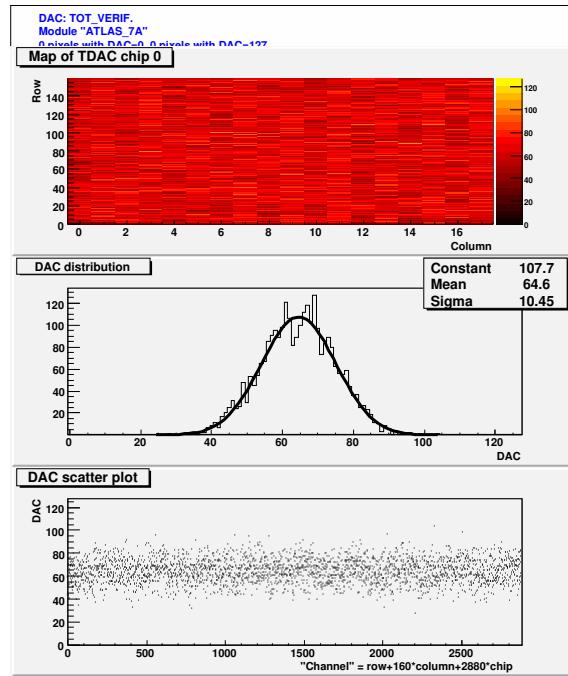

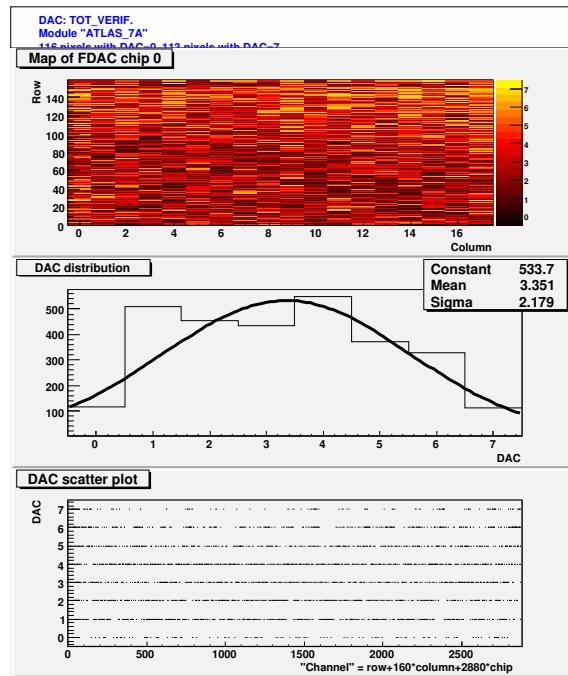

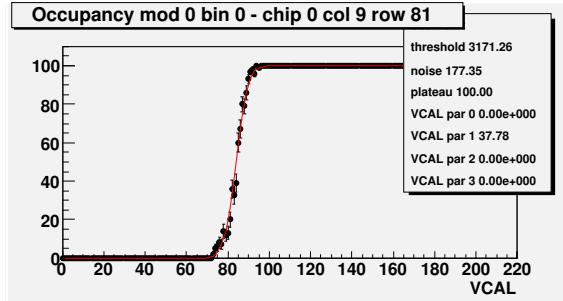

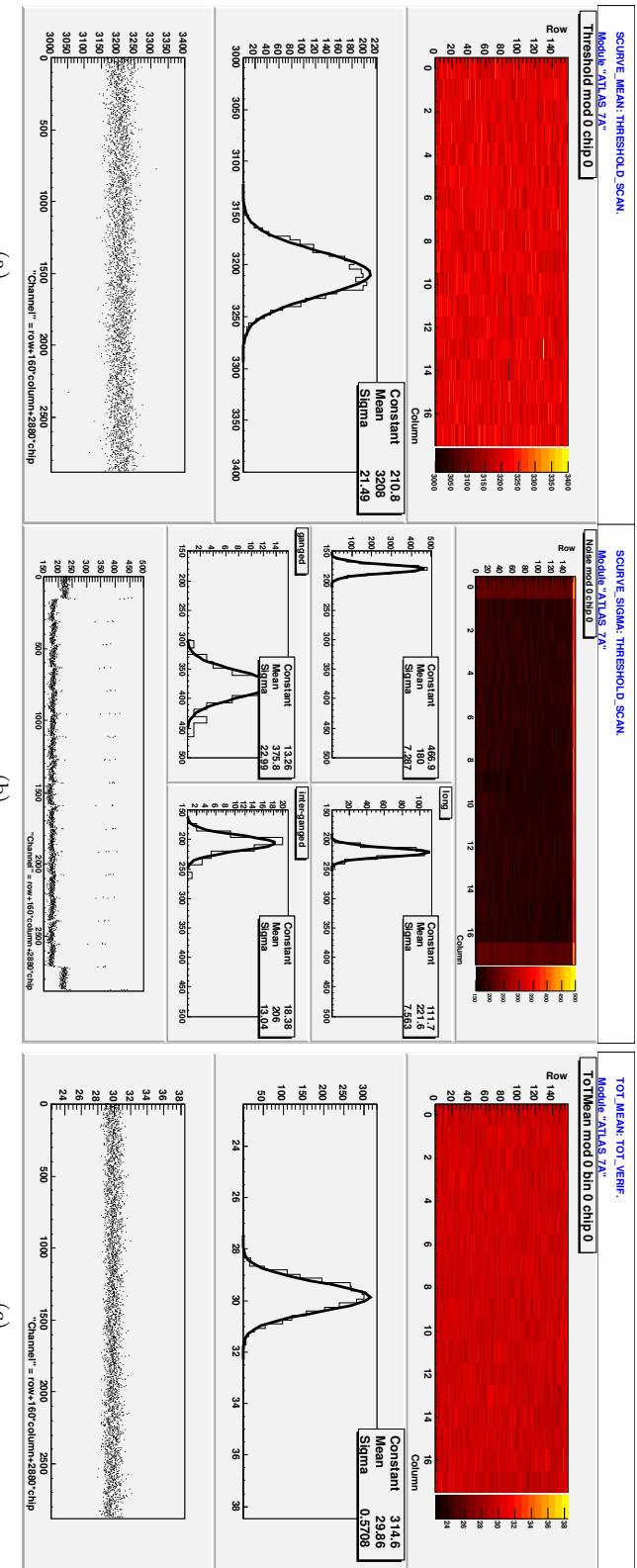

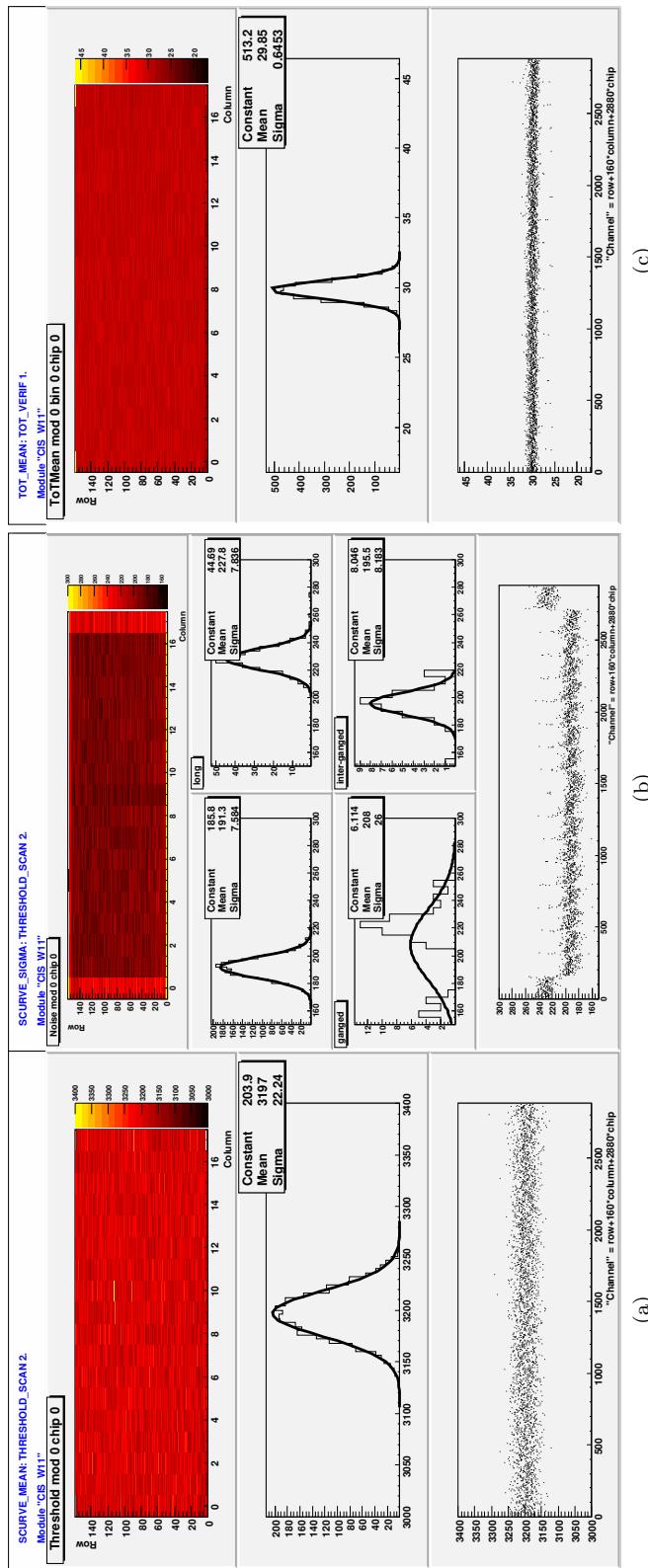

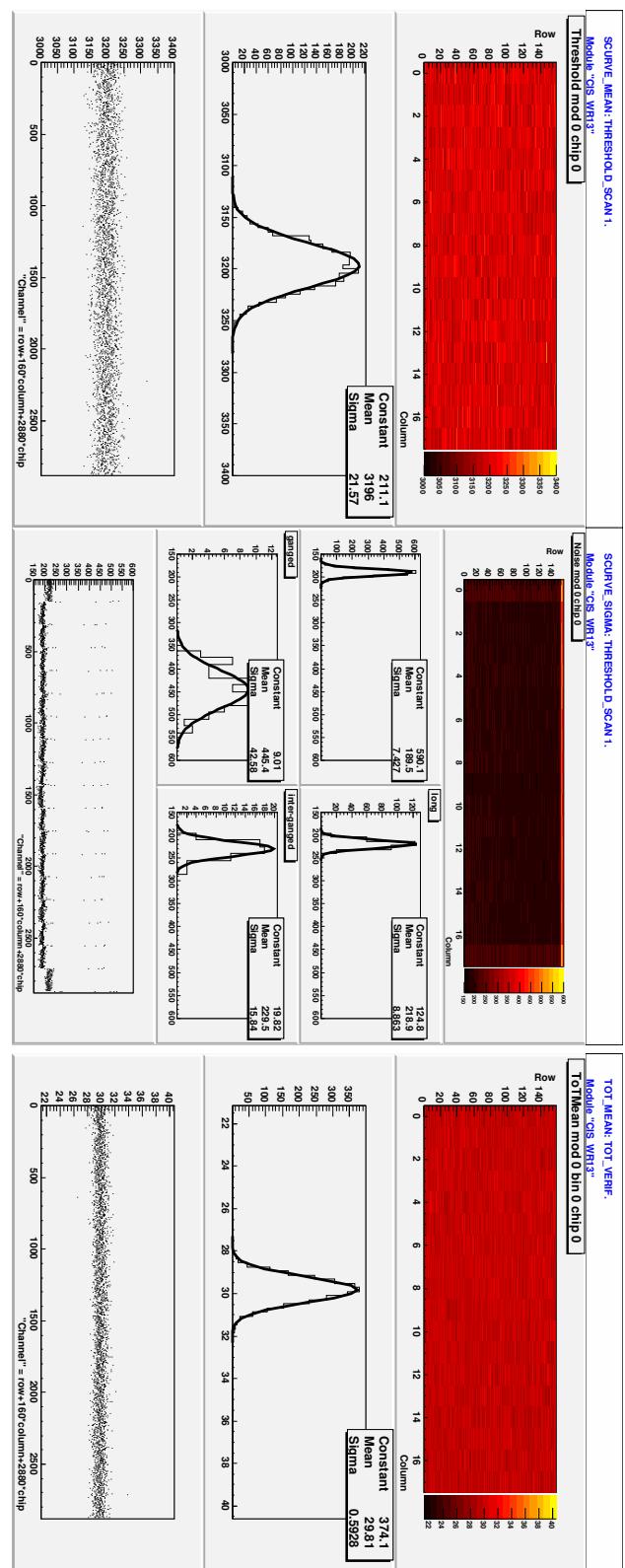

| 5.5      | Tuning of the FE-I3 . . . . .                                | 53        |

| 5.6      | Threshold Scan and Noise Measurements . . . . .              | 56        |

| 5.7      | Bias Scan Setup . . . . .                                    | 58        |

| 5.8      | Source Scan Setup . . . . .                                  | 59        |

| 5.9      | Analysis of the Raw Data . . . . .                           | 60        |

| 5.9.1    | ToT Calibration . . . . .                                    | 62        |

| 5.9.2    | Charge Sharing and Clustering . . . . .                      | 62        |

| 5.9.3    | Analysis and Histogramming . . . . .                         | 63        |

| <b>6</b> | <b>Sensor Characterization</b>                               | <b>65</b> |

| 6.1      | Introduction . . . . .                                       | 65        |

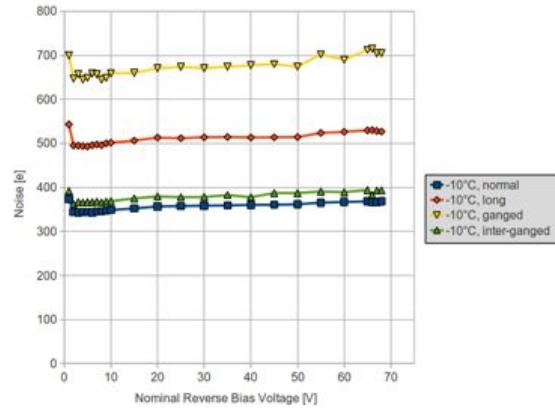

| 6.2      | Unirradiated Planar Sensors . . . . .                        | 66        |

| 6.2.1    | Results of the Bias Scan . . . . .                           | 67        |

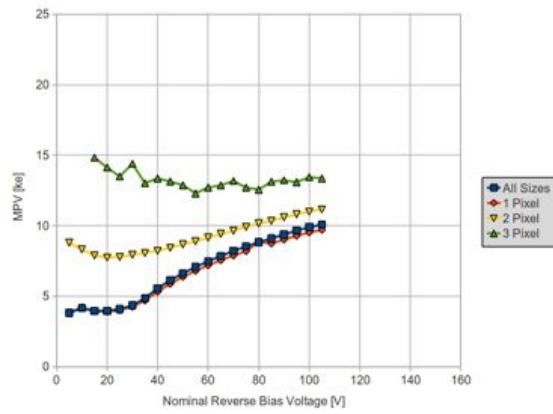

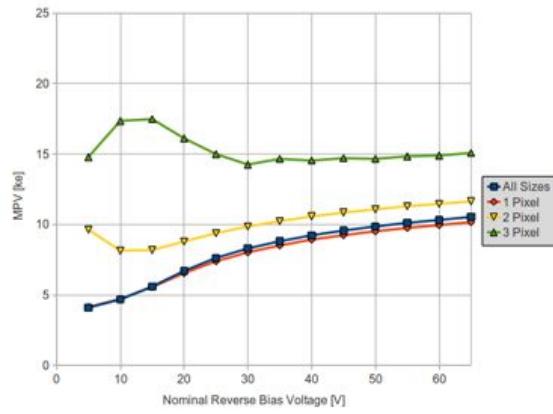

| 6.2.2    | Results of the Source Scan . . . . .                         | 67        |

| 6.3      | Irradiated 3D Sensors . . . . .                              | 71        |

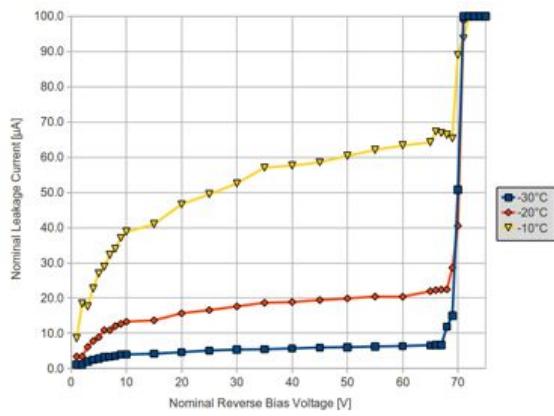

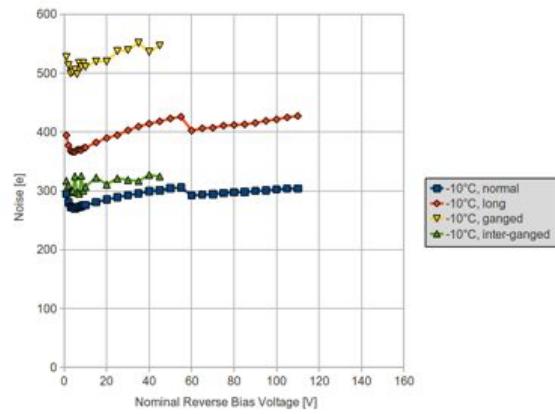

| 6.3.1    | Results of the Bias Scan . . . . .                           | 72        |

| 6.3.2    | Results of the Source Scan . . . . .                         | 73        |

| <b>7</b> | <b>Summary and Outlook</b>                                   | <b>77</b> |

| <b>A</b> | <b>FE-I3 Standard Configuration</b>                          | <b>78</b> |

| <b>B</b> | <b>FPGA Configuration Registers for Source Scan/EUDET</b>    | <b>80</b> |

| <b>C</b> | <b>Tuning Results</b>                                        | <b>82</b> |

# Chapter 1

## Introduction

The ATLAS experiment is one out of four experiments at the Large Hadron Collider. The ATLAS detector is a multipurpose detector that covers a wide range of physics at high energy scale. That includes the search for the Higgs boson, extra dimensions and particles that does not belong to the Standard Model, such as supersymmetric particles and particles that make up dark matter.

The search for new physics relies on advanced technology and innovations in almost every aspect. More than a decade of research & development and construction involving thousands of people was needed to complete the work — for now? A new round of research & development has already begun. The aim is to improve the current detector. Two major upgrades are forthcoming in the next decade.

A major part of the ATLAS upgrade plan concerns the innermost detector, the pixel detector. The upgrade of the pixel detector is of great importance as it is closest to the interaction point. On the one hand, it delivers measurements with highest possible precision. On the other hand it has to be able to withstand the harsh environmental conditions close to the interaction point.

This work is produced within the IBL collaboration. The topic of this thesis is the development of a new test and readout system for the FE-I3 pixel readout chip. In a second step, the test system was used to study two novel sensor concepts, which are considered for future detector upgrades.

Chapter 2 gives a short introduction to the LHC and the ATLAS experiment. A closer view will be taken on the structure of the ATLAS detector.

Chapter 3 gives an introduction to the ATLAS the pixel detector. The ATLAS FE-I3 pixel readout chip is described in greater details and important functionality, which is used this thesis, is highlighted. A second part covers the principles of semiconductor detectors and gives a short introduction on sensor concepts.

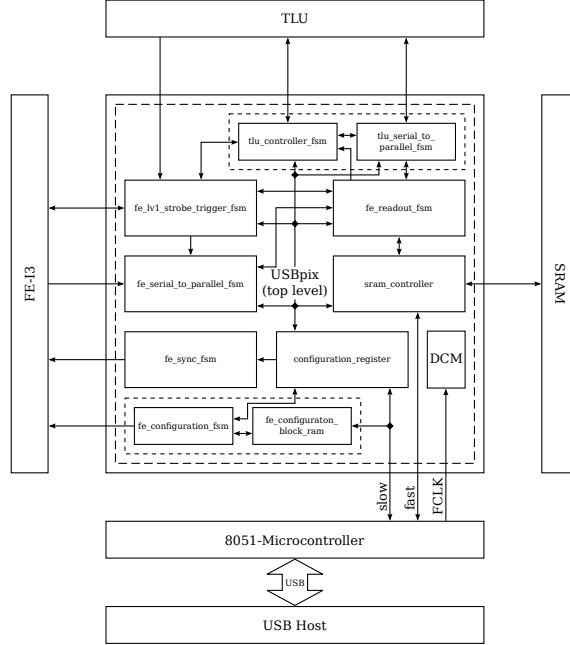

Chapter 4 covers the development of the USBpix test system, a FPGA<sup>1</sup>-based readout system for the FE-I3 pixel readout chip. Software and hardware architecture of USBpix is described in greater details. The emphasis is on the development of Verilog<sup>2</sup> source code specifying the functionality implemented into the FPGA. The work on the FPGA source code is crucially responsible for the success of this work.

---

<sup>1</sup>FPGA stands for field-programmable gate array.

<sup>2</sup>Verilog is a hardware description language (HDL).

In Chapter 5, a detailed description of USBpix test setup and the equipment, which was used for the measurement, is given. This chapter can be read as a “manual labour” how to set up the USBpix test system.

In Chapter 6, the results of the laboratory measurements are presented and discussed.

## Chapter 2

# The LHC Experiment

### 2.1 The LHC Accelerator

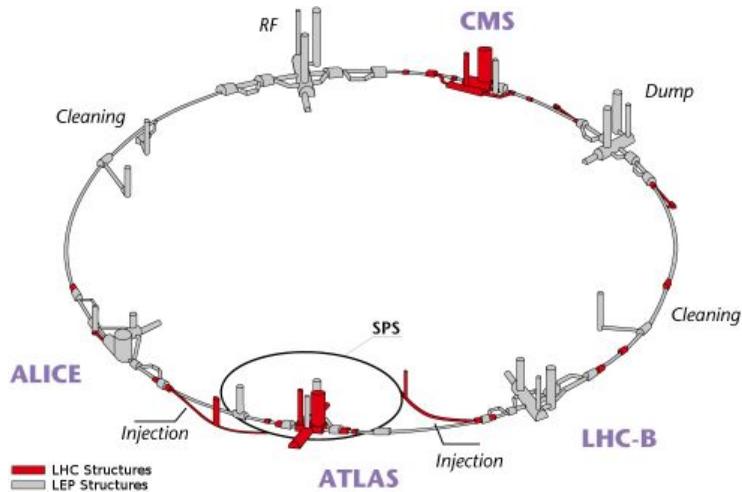

The Large Hadron Collider (LHC, see figure 2.1) is the world's largest circular collider located at the international research facility CERN<sup>1</sup>, the European Organization for Nuclear Research. The LHC was built into the tunnel of the former Large Electron-Positron Collider (LEP). The tunnel has a circumference of 27 km and is sited approximately 100 m beneath the surface and was extended to house new experiments at the LHC. The accelerator ring consists of large superconducting magnets and accelerator structures designed to boost proton pairs up to a center-of-mass energy of  $\sqrt{s} = 14$  TeV. Counter-rotating bunches of particles just mentioned are brought to collision at four distinct interaction points distributed along the accelerator ring. The particle bunches are colliding up to 40,000,000 times per second, which corresponds to the bunch crossing frequency of 40 MHz. Four large detectors (ALICE, ATLAS, CMS and LHCb) are built around these collision points.

Figure 2.1: The Large Hadron Collider and its underground structures [1].

<sup>1</sup>European Organization for Nuclear Research CERN, CH-1211, Genève 23, Switzerland.

## 2.2 The ATLAS Detector

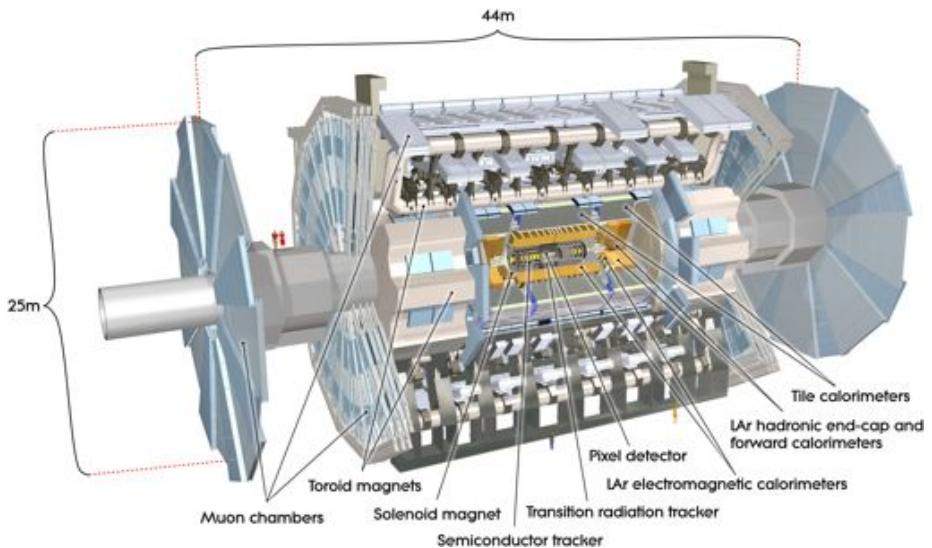

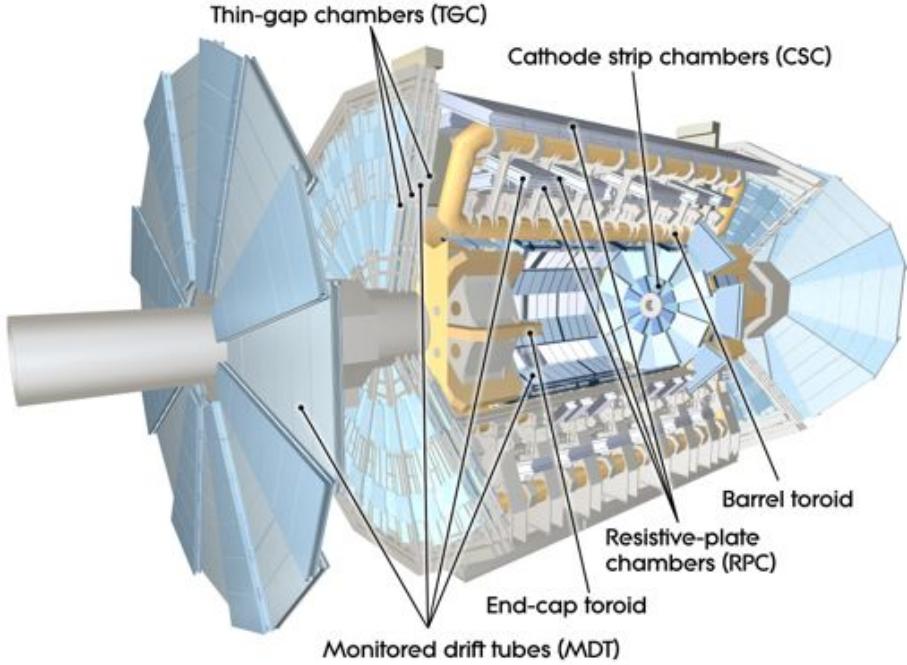

The ATLAS detector [2] (see figure 2.2) is one out of four detectors along the LHC accelerator ring, and is one out of two multipurpose collider detectors that covers a wide range of physics. It was designed to investigate proton-proton and ion-ion interactions at TeV energy scale. The detector is situated inside a cavern 80 m underground and has a diameter of 25 m and a length of 44 m. The particle collisions take place at the center of the detector. Due to the forward-backward symmetry of two colliding beams, the detector has a cylindrical shape along the beam axis.

Figure 2.2: Cut-away view of the ATLAS detector. The LHC accelerator ring is extended in either horizontal direction.

The following points are crucial to meet the experimental challenges: a precise energy measurement, a precise momentum measurement, a possibility for particle identification and a hermetic design that covers a wide pseudorapidity<sup>2</sup> range to allow high particle detection efficiency. This is achieved by six different detector subsystems that identify particles and measure either their momentum or energy. To make the determination of the momentum possible, a solenoid, a barrel toroid and two end-cap toroids produce a magnetic field to bend the trajectory of charged particles. The measurement of the momentum is accompanied by precise track reconstruction.

A multi-stage trigger system reduces the event data recording rate to a level that does not exceed the limits of the data storage infrastructure. A proton-proton interaction rate of 1 GHz is expected at the design luminosity of  $1 \times 10^{34} \text{ cm}^{-2}\text{s}^{-1}$ . First, a fast trigger system that uses a small subset of available detector information (from calorimeter and muon detector) decides on whether or not to continue processing an event. The so-called Level-1 trigger system

<sup>2</sup>Pseudorapidity  $\eta$  is a coordinate to describe the angle  $\theta$  of a particle trajectory with respect to the beam axis:  $\eta = -\ln(\tan \frac{\theta}{2})$ . The pseudorapidity is independent of Lorentz boost along the beam axis.

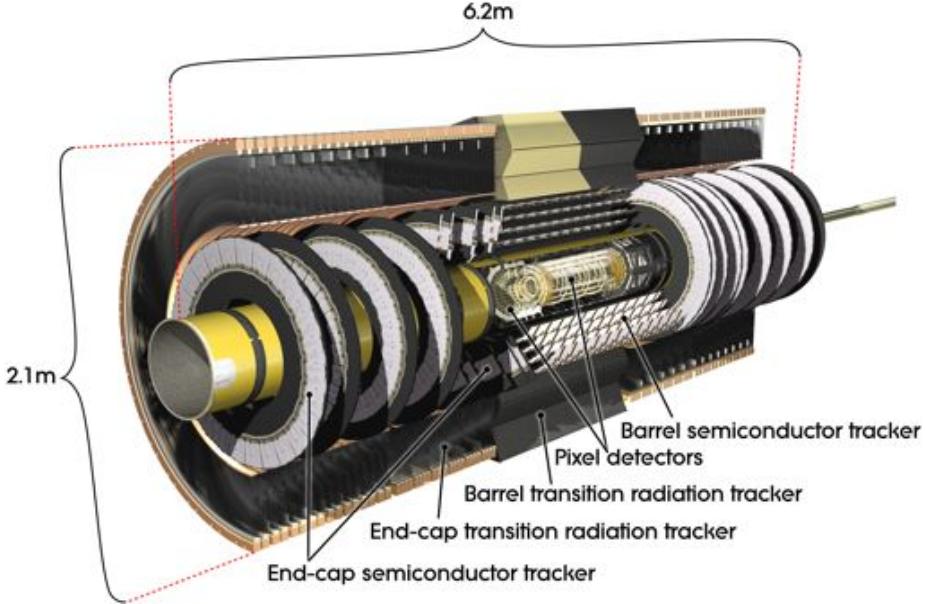

Figure 2.3: Cut-away view of the inner detector. The inner detector is composed of the following sub-detectors in successive order: the pixel detector close to the beam pipe, the silicon microstrip detector (SCT) and transition radiation detector (TRT). The inner detector is enclosed by a solenoid (not shown in the figure).

reduces the event data rate to approximately 100 kHz. Finally, two higher level triggers, the Level-2 trigger and the event filter, further reduce the data taking rate to approximately 200 Hz.

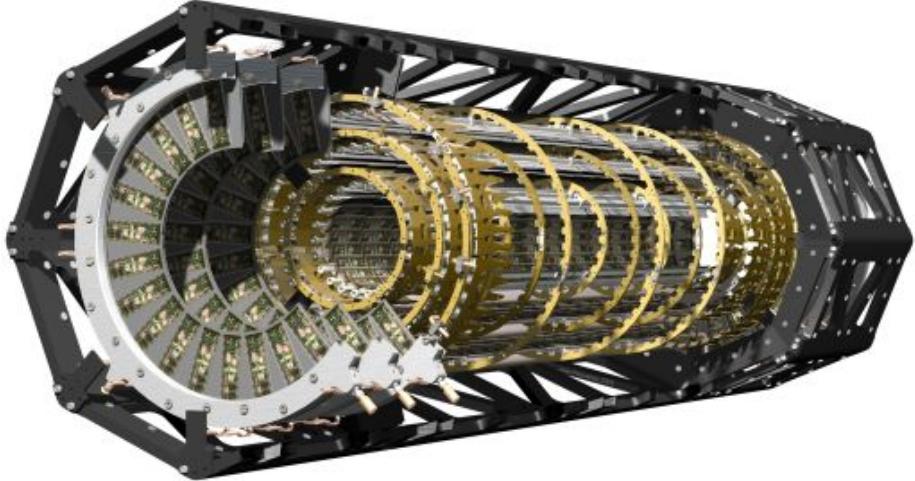

### 2.2.1 The Inner Detector

Figure 2.3 gives an overview about the structure of the inner detector. The multi-layered structure comprises, from the inside to the outside, the following three successive sub-detectors: the pixel detector close to the beryllium beam pipe, the silicon microstrip detector and the transition radiation detector. The inner detector is enclosed by a solenoid, which generates an axial magnetic field of approximately 2 T, to bend the trajectories of charged collision products and thus enable the measurement of their momentum.

The main purpose of the inner detector is the precise determination of the momentum of charged particles. It was also built to provide a hermetic pattern recognition and precise primary and secondary vertex measurements within a pseudorapidity range of  $|\eta| = 2.5$  ( $\theta = 9.4^\circ$ ) and particle identification within  $|\eta| = 2.0$  ( $\theta = 15.4^\circ$ ).

A particle has to interact with the detector material to determine its trajectory. This happens at discrete points within the detector at different distances from the place of origin e.g. the primary vertex of a collision inside the beam pipe. The pixels detector is placed closest to beam pipe. There, it can deliver the highest single point resolution (and thus very good pattern recognition) within

all sub-detectors. Such a high single point resolution is necessary to compete with the high particle occupancy due to the enormous particle flux close to the interaction point. To maintain the pixel detector operable at high radiation dose it must be kept at low temperature (approximately  $-5^{\circ}\text{C}$  to  $-10^{\circ}\text{C}$ ). The innermost layer (or b-layer<sup>3</sup>) has an expected lifetime of 3 years at LHC design luminosity. Beside the b-layer two other pixel layers and three end-cap disks on either side of the cylinder encloses the collision point. They are expected to withstand the particle flux over the operational lifetime of the experiment. More details on the pixel detector will be given in chapter 3.

A second sub-detector is built around pixel detector: the silicon microstrip detector (SCT). Its purpose is the same as that of the pixel detector: measurement of the momentum and pattern recognition. The SCT consists of four barrel layers and nine end-cap disks on either side. Each layer and disc is equipped with back-to-back sensors that have a stereo angle of 40 mrad to obtain two-dimensional spatial resolution. The strip pitch is 80  $\mu\text{m}$  for the barrel sensors and for the disks between 57  $\mu\text{m}$  and 90  $\mu\text{m}$  due to the geometry. This results in an intrinsic resolution of 17  $\mu\text{m}$  in  $R\text{-}\phi$ -direction and 580  $\mu\text{m}$  in  $z$ -direction (barrel) or  $R$ -direction (disks). To withstand the harsh environment the SCT is also kept at the same temperature as the pixel detector.

At larger radii, the transition radiation tracker (TRT) provides tracking information of particles that traverse many layers of close-packed drift straw tube elements of 4 mm in diameter. The straws (cathode) are filled with non-flammable gas mixture of 70% Xe, 27% CO<sub>2</sub> and 3% O<sub>2</sub>. Each straw is equipped with an anode wire (the sense wire) that is placed in the center. Each tube provides a drift time measurement, giving a spatial resolution of 170  $\mu\text{m}$ . Two independent thresholds are applied to every readout channel to discriminate between tracking hits, which pass the lower threshold, and transition radiation hits, which pass the higher one. The barrel is built up from axially oriented straws (approximately 50,000) whereas both end-cap wheels contain radially oriented straws (approximately 320,000). The entire sub-detector is designed to operate at room temperature and is surrounded by CO<sub>2</sub> to avoid pollution of the straws. With an average of 36 hits per crossing particle, it enhances the pattern recognition, improves the momentum resolution and provides electron/positron identification.

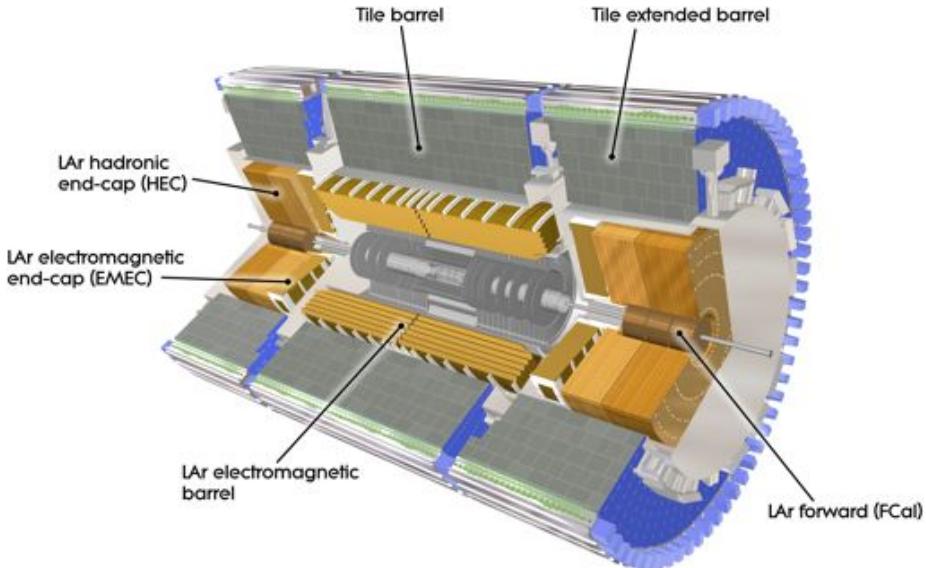

### 2.2.2 The Calorimeter System

An overview of the calorimeter system is given in figure 2.4. The calorimeter system can be classified into two sub-detectors: the inner electromagnetic calorimeter and the outer hadronic calorimeter. The electromagnetic calorimeter measures the energy of particles that primarily loses energy by electromagnetic interaction (e.g. electrons, photons) whereas the hadronic calorimeter measures the energy of the remaining particles, mainly those that are underlying strong interaction (i.e. hadrons). But in both cases the principle is the same: an incident particle of sufficient energy interacts with the absorber (or passive) material producing a particle shower. The constituents of the shower interact with the sensing (or active) material that is used for detecting the particles.

---

<sup>3</sup>The name can be derived from the fact that the innermost layer is designed to reconstruct the vertices of hadrons containing b-quarks and c-quarks (b-tagging).

The electromagnetic calorimeter uses lead as absorber material and liquid argon (LAr) as sensing material. Particles of the shower liberate electrons from the argon atoms. Liquid argon act as a conductor and therefore the electrons can be collected by electrodes and are read out.

The electromagnetic calorimeter has a particular geometry: the accordion-shaped (or folded) absorbers and electrodes allow having several active layers in depth. This is beneficial for the energy resolution which is in the order of  $\sigma(E)/E = 10\%/\sqrt{E}$  [3]. A spatial resolution is obtained by segmenting the first layer.

The hadronic calorimeter is divided into three parts: the tile and tile extended barrel calorimeter, the LAr hadronic end-cap calorimeter (HEC) and the LAr forward calorimeter (FCAL). The both latter are using liquid argon as sensing material. The end-cap calorimeter uses copper (Cu) as passive material whereas the FCAL uses both, copper and tungsten (W). The tile barrel is made of steel with scintillating tiles in between. The light signals are read out by photomultiplier tubes.

Pion measurements show that the energy resolution  $\sigma(E)/E$  is of approximately  $50\%/\sqrt{E}$  for the tile barrel calorimeter,  $90\%/\sqrt{E}$  for the HEC and  $70\%/\sqrt{E}$  for the FCAL [3].

Figure 2.4: Cut-away view of the calorimeter system. The inner detector is indicated at the center and is enclosed by the electromagnetic calorimeter (liquid argon electromagnetic barrel and end-cap). The hadronic calorimeter (tile barrel, tile extended barrel, liquid argon hadronic end-cap and liquid-argon forward calorimeter) is built around the electromagnetic calorimeter. The part of liquid-argon forward calorimeter, which uses copper absorbers, is an electromagnetic calorimeter, while the part, which uses tungsten, is a hadronic calorimeter. A cryostat is required to keep the argon liquid.

Figure 2.5: Cut-away view of the muon spectrometer. The nested structure of the tracking chambers minimizes the gaps in detector coverage.

### 2.2.3 The Muon Spectrometer

The muon spectrometer, as shown in figure 2.5, forms the outer part of the ATLAS detector and is the largest sub-detector in size. The tracking chambers of the muon sub-detector detect charged particles that exit the calorimeter. This are in most cases muons which live long enough to reach the outer regions of the detector. A barrel toroid and the two end-cap toroids generate a large-scale toroidal magnetic field of approximately 0.5 T and 1 T respectively. Thus makes it is possible to measure the momentum of charged particles in the pseudorapidity range of  $|\eta| < 2.7$ . The transverse momentum ( $p_T$ ) resolution is of approximately 10% for 1 TeV particles.

In the barrel region, precision-tracking chambers are located on and between the eight coils of the barrel toroid. The nested chambers are arranged in three cylindrical layers at radii of approximately 5, 7.5 and 10 m. In the end-cap region, several muon chambers form large disks. The end-cap disks are located in front and behind each end-cap toroid at a distance of 7.4, 10.8, 14 and 21.5 m from the collision point.

The muon spectrometer is essential for the search of new physics. It is designed to deliver a fast trigger on particles in the pseudorapidity range of  $|\eta| < 2.4$ . The trigger occurs if a certain transverse momentum threshold is exceeded.

## Chapter 3

# Silicon Pixel Detectors

### 3.1 Introduction

This chapter will give an introduction on the ATLAS pixel vertex detector and the FE-I3 pixel readout chip (sections 3.2 and 3.3, respectively). The purpose of a vertex detector is to reconstruct the primary and secondary vertices of hadrons containing b- and c-quarks. The vertices are reconstructed by extrapolating the hit information measured by several detector layers around the interaction point. The high single point resolution and tracking efficiency of a pixel detector are required to obtain better tagging efficiency of the jet flavor. Also, in order to cope with the harsh environment close to the collision point, a pixel detector has an advantage of low per-pixel hit occupancy and per-pixel leakage current and thus noise.

In sum, the following criteria must be met by a modern pixel vertex detector:

- The innermost vertex layer should be as close to the collision point as possible to increase the accuracy of the vertex and impact parameter reconstruction.

- The detector and its components should be based on a radiation-hardened design.

- The material budget (in radiation length) of the detector and its supporting structures should be as low as possible to reduce the effect of multiple scattering. This is particularly important for the innermost detector layer.

- The pixel detector should have a high spatial resolution in order to provide a good hit resolution. Low noise and low hit occupancy are also important qualities for pattern recognition and for finding primary/secondary vertices [4] in a high multiplicity environment (e.g. nearby tracks in a jet).

- Hermetic coverage over a wide pseudorapidity range.

In a second part (section 3.4) and in a more general approach, the effect of radiation on silicon will be discussed. In section 3.4.1, the interaction of ionizing particles with the sensor material will be explained and thus the generation of charge that is detected as electrical signal. Section 3.4.2 will highlight another

Figure 3.1: Cut-away view of the ATLAS pixel vertex detector. The mechanical support structure is built out of carbon composites which have a high stiffness, low mass and near-zero coefficient of thermal expansion. The global support frame (truss-like structure) holds three barrel layers and three end-cap disks on each side. The pixel modules (see figure 3.3) are mounted on local support structures (staves and sectors) with embedded cooling. The barrel layers and the end-cap disks are composed of several staves and sectors respectively.

effect of radiation on silicon: the damage to the silicon crystal lattice and its consequences will be discussed. In the last section (3.4.3), different sensor concepts will be presented and their advantages and disadvantages will be explored.

## 3.2 The ATLAS Pixel Detector

The ATLAS pixel detector [5] (see figure 3.1) is the smallest sub-detector in size (length of 1.4 m, with a radius of 0.2 m) but has the vast majority of readout channels. More than 80 million readout channels are distributed over a sensitive area of about  $1.7 \text{ m}^2$ . The pixel detector consists of three cylindrical barrel layers at a radius of 5, 9 and 12 cm and three end-cap disks on each side at a distance of 50, 58 and 65 cm from the interaction point. Such a hermetic design allows to have at least three pixel hits in the pseudorapidity range of  $|\eta| < 2.5$ . The entire sub-detector is immersed in a solenoidal magnetic field of approximately 2 T to enable momentum measurement of charged particles.

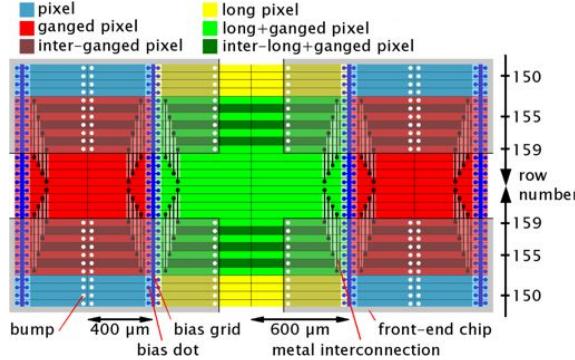

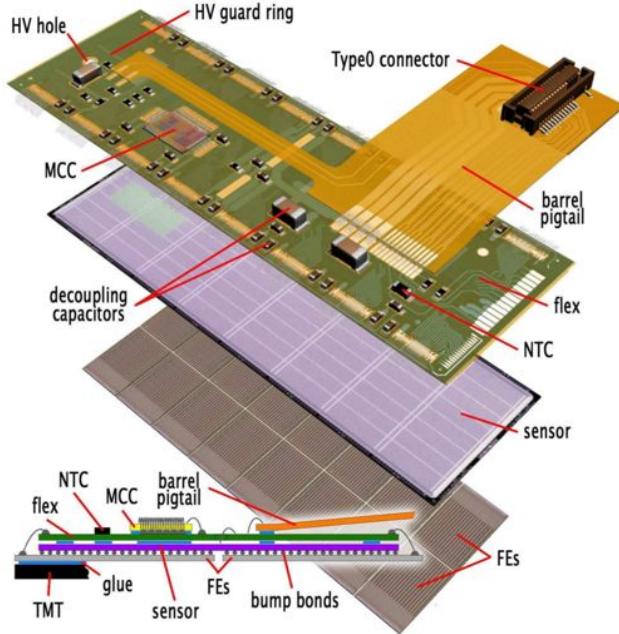

The smallest unit of the pixel detector is the hybrid<sup>1</sup> pixel module (see figure 3.3). It consists of a flex-hybrid holding the module readout electronics and a bare module. The bare module is made of a single sensor bump bonded to 16 FE-I3 chips (2 columns of 8 chips). The entire pixel module has an active area of approximately  $6 \text{ cm} \times 2 \text{ cm}$  containing 46080 readout channels. To allow a contiguous sensitive area between the FE-I3 readout chip boundaries, some of the readout channels are connected to two sensor pixel cells and/or to sensor

---

<sup>1</sup>Sensor and readout chip are separate entities are attached to each other.

Figure 3.2: Layout and interconnection of FE-I3 pixel types in the interchip region. The FE-I3 pixel readout chip is indicated by light grey shading, whereas all four sensors meet in the middle. Normal pixels (red and blue):  $50 \times 400 \mu\text{m}^2$ . Long pixels (green and yellow):  $50 \times 600 \mu\text{m}^2$ . [7]

pixel cells of slightly larger dimension (see figure 3.2). In total, this leads to 47232 pixel cells on the sensor. The sensor is connected to the FE-I3 chips using the flip chip technology to minimize the signal path length between sensor pixel and readout electronics. Two different bump bond techniques are used to attach the sensor: electroplated-PbSn and evaporative-indium bumping [6].

The nominal pixel size is  $50 \mu\text{m}$  in  $\phi$ -direction and  $400 \mu\text{m}$  in  $z$ -direction (barrel) or  $R$ -direction (disk). Under the assumption that only one pixel per particle track fires and binary readout, the spatial resolution is given by

$$\sigma_{\text{position}} = \frac{p}{\sqrt{12}}, \quad (3.1)$$

where  $p$  is the pixel pitch [8]. The alignment of the pixel cells leads to a resolution of  $14 \mu\text{m}$  in  $R\text{-}\phi$ -direction and  $115 \mu\text{m}$  in  $z$ -direction or  $R$ -direction. However it is possible that the signal charge is shared between pixel cells. A group of pixels triggered by a single incident particle further improves the resolution. Having a readout that delivers the collected charge, the spatial resolution can be further improved by using a charge weighted clustering algorithm. The charge sharing and thus also the cluster size is affected by several parameters [8, 6]: the average cluster size is determined by the position and the incident angle of a particle track with respect to the sensor surface (the latter can be adjusted by tilting the modules), by intrinsic sensor properties (e.g. inter-pixel capacitance and pixel capacitance to the backplane), by operational parameters (e.g. reverse bias voltage and radiation damage) and by parameters related to electronic readout (e.g. threshold, crosstalk, charge resolution). Also the presence of the solenoidal magnetic field has an impact on charge sharing and thus cluster size. This is due to the fact that the signal charge inside the sensor is deflected by the Lorentz angle. The results of resolution studies are summarized in [6].

The hybrid pixel modules are mounted on so-called local support structures (glued on the surface with the FE-I3 side). The local support structures, which also carry Al-tubes to provide cooling (evaporative  $\text{C}_3\text{F}_8$ -cooling), are made of thermally conductive carbon composites. The cooling is needed to reduce the leakage current and therefore noise and to control beneficial/reverse annealing

Figure 3.3: The ATLAS hybrid pixel module. The module readout electronics is mounted on a polyimide printed circuit board (flex-hybrid). The flex-hybrid is attached with an adhesive to the bare module (sensor bump bonded to 16 FE-I3 chips). The flex-hybrid also provides high-voltage and low-voltage to the attached components. The sensor is wire bonded through a hole in the flex-hybrid exposing the sensor backplane (p-side). Wire bonds are also used to electrically interconnect the FE-I3 readout chip to the flex-hybrid.

of irradiated sensor material (see section 3.4.2). The use of lightweight materials is crucial to reduce multiple scattering. The contribution of the pixel detector to the total inner detector material budget is of the order of  $10\% X_0$  (radiation length) and  $0.05\% \lambda$  (interaction length) at  $\eta = 0$  [6].

There are two types of local support structures: staves and sectors. A stave holds 13 pixel modules while a sector holds eight pixel modules. Each barrel layer consists of different numbers of staves (22 staves for the b-layer, 38 for the second and 52 for the third layer) and each end-cap disc is made of eight sectors. This leads to a total number of 1744 pixel modules for the entire pixel detector.

### 3.3 FE-I3 Pixel Readout Chip

The ATLAS FE-I3 pixel readout chip is implemented in a  $0.25\text{ }\mu\text{m}$  CMOS fabrication process. The die has a size of  $5.4\text{ mm} \times 11\text{ mm}$ . 3.5 million transistors are fabricated on silicon using radiation tolerant design rules<sup>2</sup> to withstand the

<sup>2</sup>On transistor level: the NMOS transistors are separated by  $p^+$  guard rings. Also a deep sub-micron technology is beneficial for radiation hardening. Due to the small MOS gate oxide thickness the upcharge is reduced significantly. On design level: single event upset (SEU) tolerant redundant structures/registers and parity checking. For more information see

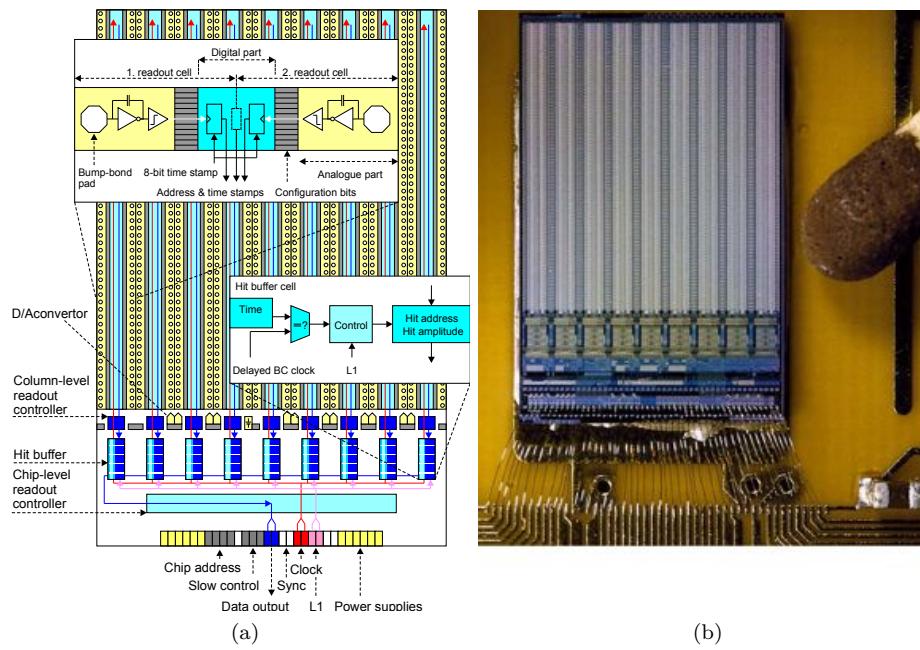

Figure 3.4: On top view of the FE-I3 readout chip. (a) Overview of the most important logic blocks of the FE-I3. (b) Size of the readout chip compared to a match. Clearly visible are the double column structure and the chip periphery at the bottom containing the readout logic and buffers.

required radiation tolerance up to a total dose of 50 Mrad. The chip contains 2880 readout channels arranged in matrix of 160 rows  $\times$  18 columns. The size of each readout cell is  $50\text{ }\mu\text{m} \times 400\text{ }\mu\text{m}$  (row-to-row pitch  $\times$  column-to-column pitch). The power consumption should be less than  $40\text{ }\mu\text{W}$  per readout channel to fulfill the design requirements [11]. However, the chip typically draws  $40\text{ mA}$  of current from a  $2\text{ V}$  (digital supply voltage) supply and  $80\text{ mA}$  of current from a  $1.6\text{ V}$  (analog supply voltage) supply (see also [12]), which is  $30\text{ }\mu\text{W}$  above design requirements per readout channel.

Figure 3.4 shows the most important logic blocks of the FE-I3. Each pixel consists of an analog and a digital block. The task of the analog pixel block is to amplify and shape the input signal charge which is generated by particles hitting the sensor. The digital block comprises all digital elements beginning from the digital pixel block and ending at the readout controller in the chip periphery. The digital pixel block communicates with the logic located in the chip periphery and transmits the hit data. The 18 pixel columns are aligned to 9 double columns. The double column comprises 320 readout channels, each sharing the same column bus, column arbitration unit (CAU, also referred to as column readout controller) and end-of-column (EoC) buffer. Beside the double column readout logic (CAU and EoC buffer), also the chip level readout controller (ROC) is located in the chip periphery. The ROC collects the hit data and sends them out serially. The following sections will give a more detailed description about the analog and digital design.

### 3.3.1 Chip Configuration

The FE-I3 readout chip has a 14-bit local configuration register which is located in each of the 2880 pixel readout blocks. Also 231-bit long global configuration register exists. Parts of the global configuration register are located underneath the pixel matrix and in the chip periphery in vicinity of the corresponding logic blocks. All configuration bits are stored in single event upset (SEU) tolerant latches/RAM cells.

The latches can be accessed by using two long shift register. One 231-bit long shift register for the global register and one 2880-bit long shift register for accessing the pixel register bits.

An additional 29-bit long command register controls the shifting of the bit pattern and the latching of the bits into the corresponding RAM cells. The command register determines into which shift register the received bit pattern is shifted. It also determines into which local register the pixel shift register is latched.

Three input signals are needed: command clock (CCK), data input (DI) and a load signal (LD). The clock is sent in parallel with data: DI must be synchronous to the CCK and the CCK is enabled only during shifting the data.

The procedure is as follows: first, the 29-bit command has to be written to the command register to get access the intended configuration register (clock command). When LD is low the command data can be shifted into the command register (CCK enabled for 29 clock cycles). To latch the command data, LD must be asserted. Immediately, the command becomes active. Second, the configuration data is shifted to the shift register. The LD stays asserted and

---

[8, 9, 10, 11].

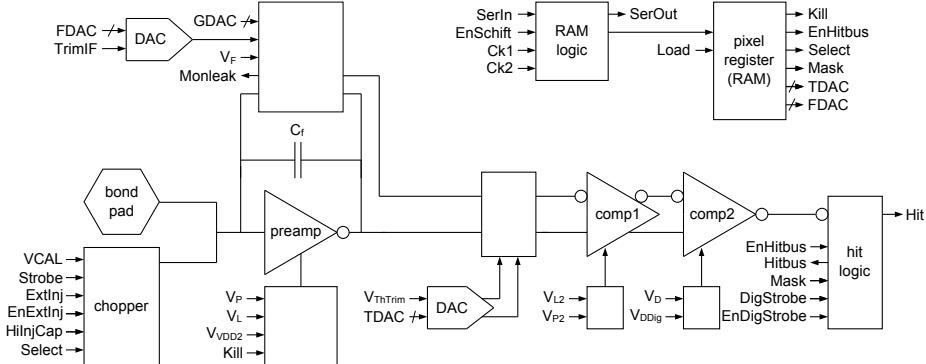

Figure 3.5: The analog pixel block and the associated pixel register of a single readout channel [11]. For a detailed view of the chopper see figure 5.2 and for the hit logic see figure 3.7.

the CCK is enabled for 231 or 2880 clock cycles corresponding to length of the shift register. Now, LD must be de-asserted. Third, to latch the data from the shift register into the RAM cells another command is needed (write command).

A detailed description is given in [12, 11].

### 3.3.2 Analog Pixel Block

The analog pixel block (figure 3.5) consists of various stages, beginning with the bond pad, which is connected to the sensor, and ending with the hit signal output of the hit logic. The analog readout electronic collects the charge that is generated by radiation hitting the sensor. The so-called signal charge is induced by electrons and holes drifting towards the sensor electrodes. The signal charge flows through the bond pad into the charge sensitive amplifier<sup>3</sup> (CSA, also referred to as preamplifier). The current pulse, which arises at the CSA input is integrated on the feedback capacitor  $C_f$  and forms a positive voltage step at the CSA output. To decrease the output voltage and to return again to base level, the CSA is realized with a feedback circuit (continuous reset), which consists of an adjustable resistor (implemented by using only PMOS transistors) in parallel to the capacitor  $C_f$ . In addition, a leakage current compensation circuit prevents the leakage current of the sensor to be integrated over time.

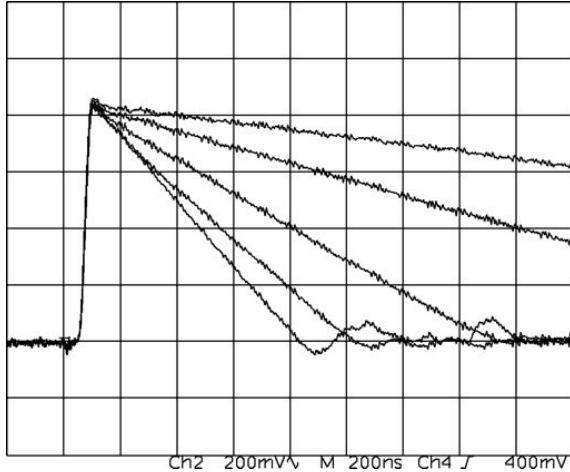

To sum up, the output of the CSA is a unipolar triangular signal whose time over a certain threshold is proportional to the collected charge (see figure 3.6). The rise time is limited by the stringent constraints on the power consumption of the FE-I3 readout electronics and is of approximately 15 ns [6]. In contrary, the fall time of the preamplifier signal is primarily determined by the feedback current and can be adjusted. The feedback current can be tuned locally by the FDAC pixel register (fine tuning) whose step size can be adjusted by the TrimIF global register. The feedback current of every readout channel is pre-biased and is adjusted by the IFDAC global register (coarse tuning).

The output signal of the CSA is DC-coupled to a comparator. The comparator consists of two amplifiers arranged in series: the first stage is a fully

<sup>3</sup>The amplifier uses a single-ended folded-cascode topology with PMOS input transistor, which is a common choice for low-voltage and high-gain amplifiers [13].

Figure 3.6: Output of the charge sensitive amplifier (CSA). The unipolar triangular signal, whose time over a certain threshold is proportional to the collected charge, is DC-coupled to the comparator.

differential low-gain amplifier and the second stage is a classical two-stage differential amplifier [13]. The comparator compares the output signal of the CSA to a well-defined threshold potential. The reason for this is as follows: the base line potential of the CSA output depends on  $VDD_{ref}$ <sup>4</sup>.  $VDD_{ref}$  is also used to generate the threshold potential (often referred to as  $V_{replica}$ ). Then, the threshold is defined as the difference between the threshold potential and base line potential. The threshold potential is generated locally to avoid variations in threshold across the chip. Again, the threshold potential can be adjusted locally by setting the TDAC pixel register (fine tuning) and globally by setting the GDAC global register (coarse tuning). The step size of the TDAC is adjusted by the TrimTh global register.

In the moment when the output signal of the CSA exceeds the threshold potential, the comparator asserts the binary hit signal. The hit signal is de-asserted when output signal falls below the threshold. Consequently, the length of the hit signal depends on the feedback current and threshold and is proportional to the collected charge. The time the signal is asserted is called Time-over-Threshold (ToT).

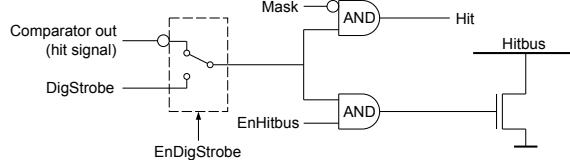

The hit signal is received to the hit logic (see figure 3.7). The hit signal is sent to the hitbus if the WriteHitbus pixel register is set. The hitbus can be asserted by any of the 2880 readout channels (OR'ed). The hitbus signal can be used internally for self-triggering or can be read out from a pad on the FE-I3 readout chip. A second output (indicated as “Hit”) is connected to the digital pixel block. The transmission of the hit signal to the digital block can be disabled by setting the WriteMask pixel register bit to 1.

In addition, each readout channel has a separate charge injection mechanism (indicated as “chopper” in figure 3.5), which is used to adjust the feedback current of the CSA and the threshold of the comparator. The charge injection circuit is topic of section 5.4.

---

<sup>4</sup>As well as on the bias current of the amplifier.

Figure 3.7: The hit logic is part of the analog pixel block [11]. The hit signal can be sent through the global hitbus (OR'ed with all other readout channels) and is available on an output pad of the FE-I3. The hitbus signal can be used for internal self-triggering (see section 4.6). A specific circuit is implemented to test the digital functionality of the FE-I3 (DigStrobe).

### 3.3.3 Digital Pixel Block

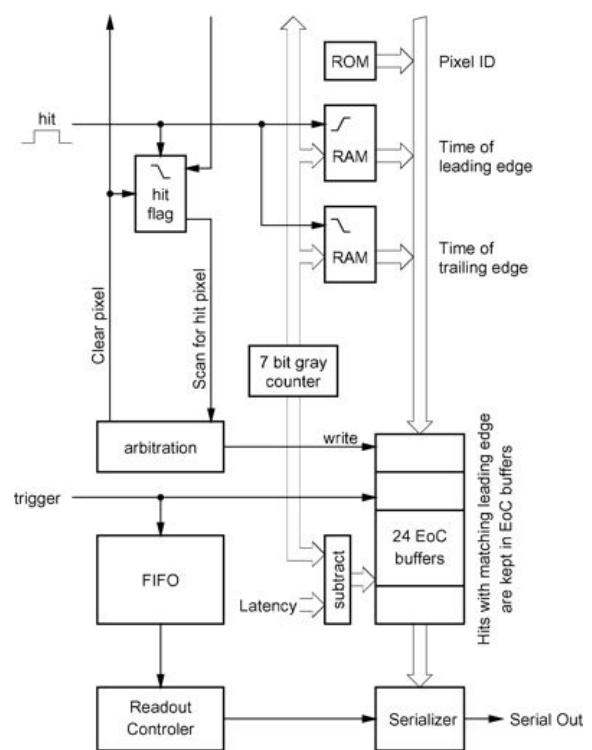

The digital pixel block generates the hit information and preserves the data until transmitted to the CAU in the chip periphery.

A block diagram of the digital pixel block is shown in figure 3.8. The binary hit signal is received by a circuit denoted as differentiator. The differentiator generates two short signals at the leading edge (LE) and trailing edge (TE) of the hit signal. Each signal causes that the current 8-bit Gray-coded time stamp is saved to either the LE RAM or TE RAM, respectively. The time stamp (TSI) is received via the timing bus and is increased by one every 25 ns according to the bunch crossing frequency of 40 MHz. The signal in coincidence with the TE also asserts a read request that is sent to the CAU. Then the CAU starts the readout of the hit information. The hit information (or data) comprises the LE and TE time stamps and the row address<sup>5</sup>. If more than one pixel saw a hit, the CAU starts a readout sequence determined by priority logic. As long as the hit information has not been read out, the digital pixel block is not able to process any other hit signal. A freeze signal prevents sending out of hit data of a pixel cell with higher priority that just received a hit while a pixel cell with lower priority communicates with the CAU. After finishing the readout of a pixel cell (read signal is de-asserted), the readout of a pixel cell with highest priority, which contains hit data, begins.

### 3.3.4 Chip Periphery

The chip periphery contains the CAU, the ROC and a EOC buffer for each column pair. The following paragraphs will only give a brief description of the functionality implemented in the periphery. An introduction into the functionality is needed to understand how the data, which is sent out to the readout system, is generated. More detailed information can be found in [11, 13].

The task of the CAU is to receive the Gray-coded hit information. In second step, the Gray-coded hit information is converted to the binary format and the ToT information is calculated by subtracting the TE time stamp from the LE time stamp. The ToT information is associated to the LE time stamp.

Hits that are affected by a timewalk effect can be discarded or doubled by the CAU. More details can be found in section 5.9.2.

<sup>5</sup>The column address is determined by the CAU.

Figure 3.8: The digital block of the FE-I3.

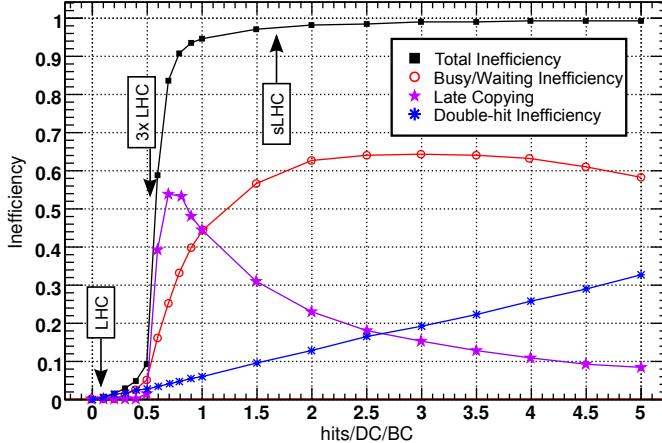

Figure 3.9: Inefficiencies in the current b-layer as function of hit rate per double column (DC) and bunch crossing (BC, equivalent to 25 ns) [14]. Note that the hit rate is even greater at smaller radius as foreseen for the ATLAS detector upgrades, which translates in even more challenging requirements for the IBL.

The LE time stamp and the associated ToT information generated by the CAU are stored in the EOC buffer. The EOC comprises 64 memory block and is associated to a single double column. The LE time stamp stored in each memory block is then compared with a bunch crossing clock. The bunch crossing clock (TSC) is a time stamp, which is offset from the original time stamp (TSI) by an adjustable delay (global register [1:8]). A read out of a buffer cell is initiated by the ROC if the bunch crossing clock coincides with the LE time stamp and if the external initiated LV1 trigger arrives in-time. Otherwise, if no LV1 trigger is asserted, the buffer cell is marked empty and the containing data is lost. The ROC is able to handle 16 consecutive LV1 trigger.

The ROC receives the data stored in a buffer cell, converts it and sends it out serially (hit word). If there is no (more) hit data that correspond to a LV1 trigger, the ROC generates the end of event data and send it out serially (EoE word).

The hit word contains column, row and ToT information and the corresponding bunch crossing time of the LV1 trigger (BCID). The EoE word also contains the BCID, error bits and the LV1 identification number. The LV1 number is increased by one every LV1 trigger. Table 4.1 gives a brief summary of the hit and EoE word data format. More detailed information about the data output format is given in [12].

### 3.3.5 Future Detector Upgrade Plans

The innermost pixel layer, which is built around the beam pipe, has a minimum distance from the interaction point of  $\sim 5$  cm. It has an expected lifetime of three years at design luminosity of  $1 \times 10^{34} \text{ cm}^{-2}\text{s}^{-1}$  and thus has to be functionally replaced before failure due to radiation damage. In addition, not only the pixel b-layer, but the entire pixel detector faces another problem that will be discussed in the next paragraphs: the pixel cells generate more data than

the digital readout of the chip can cope with.

The LHC is planned to be upgraded to higher luminosity. This happens in two steps: with a first upgrade estimated in 2016, it is planned to reach peak luminosity 2 to 3 times higher than the current design luminosity. In a second step, the luminosity will be increased to approximately 10 times the initial luminosity in a more ambitious upgrade. This upgrade is commonly referred to as HL-LHC<sup>6</sup> (or sLHC) and is currently scheduled for completion at the beginning of the next decade.

This higher luminosity leads to new problems that arise from the fact that the double column inefficiency of the ATLAS FE-I3 pixel readout chips increases drastically with the hit occupancy [14]. Figure 3.9 shows the progression of the inefficiency and points out why FE-I3 pixel readout chip cannot cope with higher luminosity as it is foreseen. The following points contribute to the inefficiency:

**Double-hit inefficiency** Two temporally close hits to a given pixel cannot be resolved. After a hit, the pixel is busy for a certain amount of time until the data transfer is finished. A second hit can also result in a pile-up of the first hit.

**Busy/Waiting inefficiency** At high luminosity the double column bus becomes saturated. This increases the time it takes for a pixel to start copying data to the double column buffer. While waiting for double column bus to become free, the pixel gets a second hit that cannot be stored.

**Late copying inefficiency** At high luminosity the double column bus becomes saturated. The increase in time it takes for a pixel to copy data to the double column buffer results in the loss of hit information. The hit information has not arrived at the double column buffer in time to be read out synchronous to the Level-1 trigger.

One possible solution is the reduction of the pixel size. A smaller pixel cell size can cope with a higher luminosity due to lower per-pixel occupancy and will also have a benefit on tracking resolution. The inefficiency related to the data transfer in the double-columns can be overcome by a new digital design of the readout chip. The effort of a new ATLAS readout chip (FE-I4A) has started in 2008 [15] and a full-sized prototype is currently under investigation.

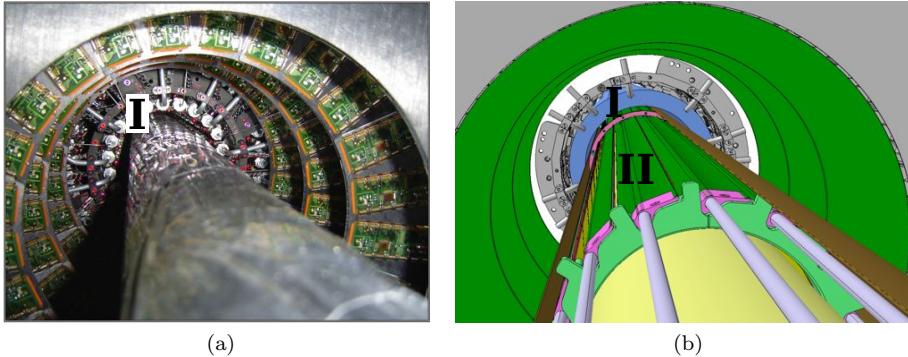

During the first LHC upgrade phase it is planned to insert a new b-layer inside the current pixel detector together with a smaller radius beam pipe (without replacing the former b-layer). This project is referred to as insertable b-layer (IBL). The new b-layer is within a radius of 3 cm away from the interaction point (see figure 3.10). Great efforts must still be made, especially in order to deal with the high radiation dose and to keep the material budget as low as possible, e.g. new powering scheme, thin chips and new types of sensors. The latter is topic of this thesis. In contrast, the HL-LHC upgrade makes it necessary to replace the entire pixel detector.

---

<sup>6</sup>HL stands for high luminosity.

Figure 3.10: a) The ATLAS pixel detector before the IBL upgrade. (I) denotes the current b-layer. b) The ATLAS pixel detector after insertion of the new b-layer which is based on the FE-I4 readout chip (II). The former b-layer stays inside the detector.

### 3.4 Semiconductor Pixel Sensors in HEP Experiments

Semiconductor detectors are widely used in high energy physics (HEP) experiments to detect ionizing radiation. Semiconductor detectors use a semiconductor sensor material to detect ionizing radiation (i.e. charged particles and photons). They are using a broad spectrum of different sensor materials, e.g. silicon (Si), gallium arsenide (GaAs) and Diamond<sup>7</sup>, which have one thing in common: a band gap. Charged particles, which interact with the sensor material, generate free charge carriers. The energy needed to create electron-hole pairs varies with the sensitive material being used but is still low compared to the energy required for production electron-ion pairs in a gaseous detector (even for Diamond<sup>8</sup>). Hence, in semiconductor detectors the statistical fluctuations of the deposited energy are smaller and thus the spread of the signal pulse height. This leads to a better energy resolution compared to a gaseous detector. Also the time resolution is better for the following reasons: free charge carriers, especially electrons, have a high mobility and thus a high drift velocity for a given electric field strength:  $v_d = \mu E$ , where  $v_d$  denotes drift velocity,  $\mu$  mobility, and  $E$  the magnitude of the electric field. Fast charge carriers travelling towards their readout electrode, decrease the rise time of the induced signal (Ramo theorem, see following section).

The simplest semiconductor detector imaginable is a single PIN diode. However, todays detectors consist of thousands of individual readout channels which are densely packed on a chip of a few  $\text{cm}^2$  in size. Such detectors have a high tracking resolution compared to other technologies such as wire chambers. The disadvantages of semiconductor detectors are the high costs for large-volume tracker detectors and the requirement of sophisticated cooling technology to reduce leakage currents and thus noise. In addition, in semiconductor detectors,

<sup>7</sup>Normally considered as an insulator.

<sup>8</sup>Mean ionization energy [16]: 3.62 eV for silicon, 13.1 eV for diamond and 20...30 eV for a gaseous detector.

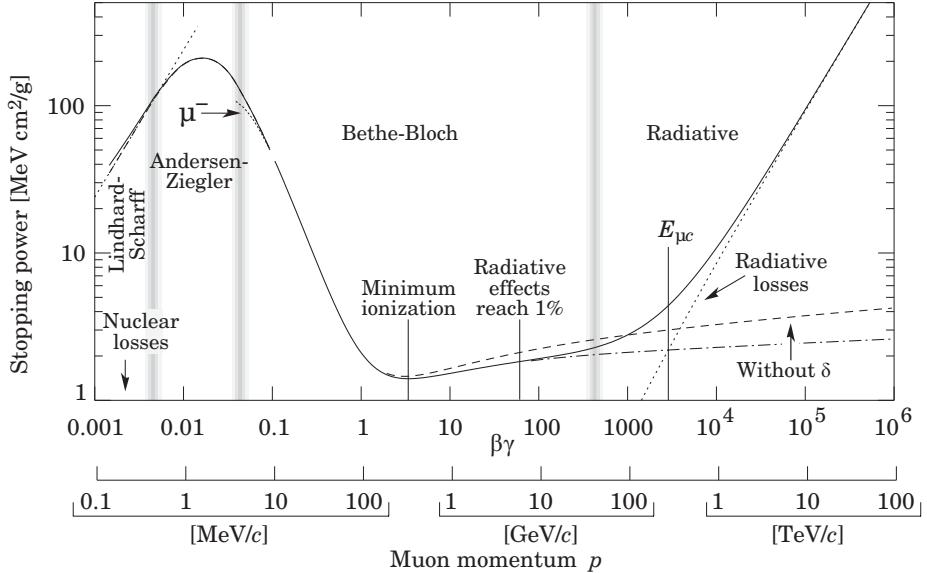

Figure 3.11: Stopping power  $-\langle dE/dx \rangle$  for positive muons in copper as a function of momentum  $p = M\beta\gamma c$  [19].

the sensor material suffers from radiation damage, which leads to a degradation of the signal-to-noise ratio (S/N).

The following sections will focus on silicon hybrid pixel detectors but most topics are also true for semiconductor detectors in general.

### 3.4.1 Energy Loss of Charged Particles and Signal Formation

Charged particles traversing matter lose energy along their path. In case of heavy charged particles, the energy is transferred to the absorbing material through many inelastic scattering processes (e.g. ionization, excitation etc.). The energy loss per length (often referred to as stopping power) at intermediate energy is described by the Bethe formula [17, 8]:

$$-\left\langle \frac{dE}{dx} \right\rangle = K z^2 \frac{Z}{A} \frac{1}{\beta} \left[ \frac{1}{2} \ln \frac{2m_e c^2 \beta^2 \gamma^2 T_{\max}}{I^2} - \beta^2 - \frac{\delta(\beta\gamma)}{2} \right], \quad (3.2)$$

where  $-\langle dE/dx \rangle$  is the stopping power (see figure 3.11). Particles at the minimum of formula 3.2 (corresponds to a value of 3 on the  $\beta\gamma$  scale) are denoted as minimum ionizing particles (MIPs). But due to the flatness of the curve the notion applies to all particles with  $\beta > 0.96$  ( $\beta\gamma > 3$ ) [8].

It is important to mention that the result given by formula 3.2 is only a mean value which is independent of the thickness of the absorber. Formula 3.2 is not adequate for describing the energy loss for a single particle for the following reasons [17, 18]: for absorbers of moderate thickness statistical fluctuations have to take into account. There the number of collisions and the amount of energy transferred at each collision fluctuates.

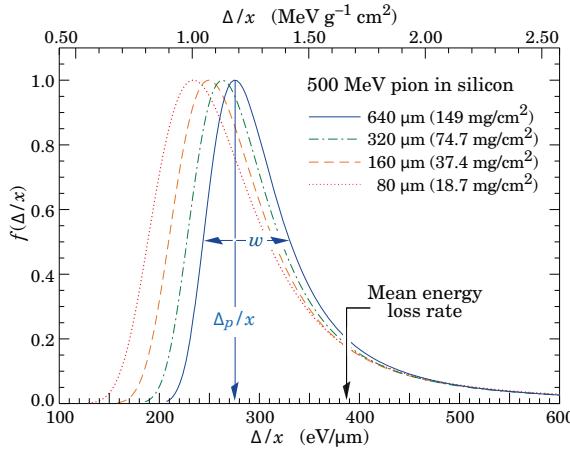

Figure 3.12: Landau distribution in silicon for 500 MeV pions, normalized to unity at the most probable value  $\delta p/x$ . The width  $w$  is the full width at half maximum (FWHM) [17].

The first energy loss probability distribution for a thin detector was carried out by Landau [20]. The skewed Landau distribution shows a high-energy tail (Landau tail, see figure 3.12). The reason for this tail is a rare occurrence of knock-on electrons (also  $\delta$  rays or  $\delta$  electrons) which are generated by large single-collision energy transfers. The knock-on electrons are emitted most likely at approximately  $90^\circ$  angle with respect to the incident particle path. The emitted electrons travel only short distances and deposit their energy into the absorber material. Due to this high energy tail, the most probable energy loss  $\Delta_p$  is always lower than the average energy loss [8]. For thick absorbers the Landau becomes more Gaussian-shaped distribution but a tail still persists.

The energy loss of electrons (and positrons) is different to that of heavy charged particles. This is because of the kinematics of the electron and its collision partners are, in case of shell electrons, of the same identity. At low energies the electrons lose energy by ionization. At high energy, losses by bremsstrahlung are dominant. For that reason formula 3.2 cannot be applied to electrons. But for absorbers of moderate thickness, the Landau shape of the energy loss probability distribution remains valid. For an electron, the most probable energy loss  $\Delta_p$  can be calculated by the following equation [21]:

$$\Delta_p [\text{keV}] = d(0.1791 + 0.01782 \ln d), \quad (3.3)$$

where  $d$  denotes the thickness of the absorber in  $\mu\text{m}$ .

The energy deposited in the absorber material generates electron-hole pairs. For silicon, the minimum energy required is 1.1 eV<sup>9</sup> (at 300 K) which corresponds to the band gap. The mean excitation energy to generate electron-hole pairs is larger than the band gap and is 3.62 eV<sup>10</sup> (at 300 K) for silicon, whereas the excess energy excites phonons. The most probable numbers of electron-hole pairs is given by dividing formula 3.3 by the mean excitation energy.

<sup>9</sup>By neglecting momentum conservation. A phonon is needed for excitation due to the fact that silicon has an indirect band gap.

<sup>10</sup>This is true if the energy of the incident particle is large with respect to the band gap.

The free charge carriers need to be detected by the readout electronics. The movement of the newly generated charge carriers induces a signal which can be detected by the readout electronics. Because of an electric field, which is applied to the detector by an external voltage supply, the electrons and holes start drifting in opposite directions. Without field, the electrons and holes would recombine after a short time without being recognized. The electronic properties and conductivity of a semiconductor are decidedly determined by the concentration of dopant atoms.

The equilibrium concentration of free charge carriers in a semiconductor can be calculated by using the Fermi-Dirac statistics. The result of the calculation is independent of the doping concentration and is known as mass-action law[8]:

$$np = n_i^2 \quad (3.4a)$$

$$= N_C N_V e^{-E_g/kT} \quad (3.4b)$$

In an intrinsic (undoped or pure) semiconductor in equilibrium the free charge carriers are thermally generated. The number of free electrons is equal to the number of free holes and therefore the concentration  $n_i$  of free charge carriers can be calculated. The thermal excitation and recombination is supported by imperfections within the crystal lattice and by impurities. It is extremely difficult to reach purity so that the lifetime of the free charge carriers is long enough so that an intrinsic semiconductor can be used for detecting ionizing radiation.

By adding a small fraction of dopant atoms new energy states are added within the band gap. Donor states are close to the conduction band (e.g. 0.054 eV for arsenic atoms in silicon) and acceptor states are close to the valence band (e.g. 0.045 eV for boron atoms in silicon). At room temperature ( $k_B T \approx 0.025$  eV) most of the donor and acceptor states are ionized. Material with more donor atoms than acceptor atoms is called n-material and the majority charge carriers are electrons according to the mass-action law. In p-type material the majority charge carriers are holes.

If p-doped and n-doped material forms a junction, free charge carriers will diffuse according to the concentration gradient of free electron and holes. An electrical field is generated by the diffusion and counter-acts the diffusion. A fraction of the free charge carriers drift back towards their majority carries side. In equilibrium, the counter-acting voltage, which causes the drift, is called built-in voltage  $V_{bi}$  and is in the order of 0.5 V. By applying a voltage (reverse bias), which has the same direction as  $V_{bi}$ , the recombination region can be extended even more. Around the junction, electrons and holes recombine. The recombination region is free of charge carriers and has a high resistivity. This region is called depletion zone (or space charge region). The width  $W$  of the depletion zone is given by following equation [8]:

$$W = \sqrt{\frac{2\epsilon_0\epsilon_{Si}}{e} \left( \frac{1}{N_A} + \frac{1}{N_D} \right) (V + V_{bi})}. \quad (3.5)$$

By assuming a p-n junction of a highly doped and lowly doped material (e.g. for an unirradiated ATLAS sensor is  $N_A \gg N_D$ ), and by neglecting the built-in voltage  $V_{bi}$  one can derive the following relationship:

$$W = \sqrt{\frac{2\epsilon_0\epsilon_{Si}}{eN_D} V}. \quad (3.6)$$

In this case the depletion zone extends widely into the lowly doped region (in our example the n-type bulk). The voltage needed for full depletion is called depletion voltage  $V_{\text{depl}}$ . Ideally, the depletion zone is extended over the complete thickness of the sensor. But this is not always possible due to limitations on the height of the supply voltage or early breakdown, to name a few. The size of the depleted volume, and the geometry and strength of the electric field within the depletion zone are important parameters which determines the efficiency of the detector. To receive maximum signal charge, a fully depleted sensor is essential.

Another important aspect is the detector capacitance which contributes to the pre-amplifier input capacitance. The capacitance of the signal source should be low in order to reduce the noise of the detector and to achieve a better overall S/N ratio [22, 18]. In case of planar sensor, the capacitance is influenced by the size of the depleted region whose capacitance  $C$  can be approximated by following formula [8]:

$$C(V) = \begin{cases} A \frac{\epsilon_0 \epsilon_{\text{Si}}}{W(V)} & V < V_{\text{depl}} \\ A \frac{\epsilon_0 \epsilon_{\text{Si}}}{d} & V > V_{\text{depl}} \end{cases}, \quad (3.7)$$

where  $A$  is the size of the p-n junction and  $d$  the thickness of the sensor. Increasing the reverse bias voltage  $V$  leads to a lower sensor capacitance but increases in revers the leakage current. The statistical fluctuations of the leakage current can be understood as noise current source feeding into the amplifier input (shot noise) [22]. However, for a pixel detector, the pixel to pixel capacitance dominates by far [18].

If an ionizing particle generates free charge carriers within the depletion zone, the charge carriers starts drifting along the electric field gradient to the corresponding electrodes. The movement of the free charge carriers induce a current at the collecting electrodes and hence in the input of the readout amplifier. The instantaneous current in the amplifier can be calculated by using Ramo's Theorem [23]:

$$i = e \mathbf{E}_W \mathbf{v}, \quad (3.8)$$

where  $\mathbf{v}$  denotes the drift velocity of the charge carriers and is equal to  $\mu \mathbf{E}$ .  $\mathbf{E}_W$  is the weighting field, which is given by  $-\nabla \phi_W$ , where  $\phi_W$  is the weighting potential. The weighting potential can be calculated by applying a unit potential ( $= 1$ ) to the readout electrode and a zero potential to all the others. The injected charge is given by integrating over time:

$$Q = \int_{t_1}^{t_2} i(t) dt. \quad (3.9)$$

In case of a pixel detector two conclusions can be drawn. They are denoted under small pixel effect [8]:

- Most of the signal charge is induced by the charge carrier drift close to the electrodes.

- Charge carriers drifting towards the backplane do not contribute significantly to the signal.

The first point particularly concerns irradiated sensors: the mobility  $\mu$  and the lifetime  $\tau^{11}$  of free charge carriers is reduced and the result is a smaller signal charge.

### 3.4.2 Radiation Damage in Silicon

High energy particles, which traverse the sensor material, not only transfer energy to the valence electrons crystal lattice atoms, but also to the crystal lattice itself. The impact can be severe, so that atoms are displaced from their lattice sites. The displacement leads to point defects such as interstitials (atoms in between lattice sites) or vacancies (empty lattice sites). If the impact is strong enough, defect clusters (conglomerates) may occur. Also possible are direct nuclear interactions, which lead to nuclear transmutation, and thus possibly to activation.

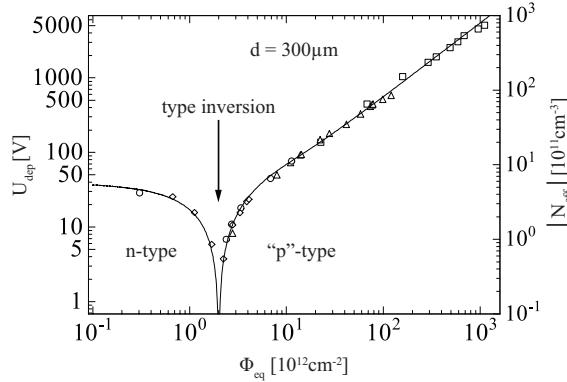

Such externally generated defects disturb the thermodynamic equilibrium. Most of these defects are mobile and attempt to attain thermodynamic equilibrium, e.g. point defects can annihilate or diffuse out of the surface. But it can be shown that also stable defects are formed: defects interact with each other and form new type of defects which can become immobile. Some of the defects are intentional such as dopants and oxygen but they can form a complex with unwanted defects, thereby losing their former functionality. This will result in a change of macroscopic (i.e. electrical) properties of the crystal. Especially the capturing dopants, e.g. phosphorus and boron for silicon, lead to the so-called effect of type inversion<sup>12</sup>: Initially n-typed silicon becomes effectively<sup>13</sup> intrinsic after a fluence of a few times<sup>14</sup>  $10^{12} n_{eq}/cm^2$  (NIEL<sup>15</sup>) [22]. Above this point, it becomes effectively p-type (see figure 3.13).

Many defects in the crystal, as stated above, diminish over time and hence all negative effects, which affects the sensor characteristics, will degrade in time. The speed of this process, which is called beneficial annealing, depends strongly on the temperature. In case of silicon, this process slows down in time. At some point it reverses and a increase of the effective doping change take place. The reason are former inactive defects which after a time become electrically active. This disadvantageous effect is called reverse annealing. The whole process can be slowed down by cooling down the sensor material.

The annealing and the following degradation of the detector can be controlled by the temperature at which the detector is kept during the maintenance periods.

Oxygen is used to radiation-harden silicon (oxygenated silicon). Oxygen has been found capturing silicon vacancies which leads to a decreased post-radiation depletion voltage [26].

To conclude, defects will have the following main consequences [22]:

---

<sup>11</sup>The charge collection distance (CCD) is the product of  $\mu$  and  $\tau$  and is commonly used to characterize detector materials.

<sup>12</sup>Applies to low-doped bulk silicon as the doping concentration is several orders of magnitude less than in the electrodes.

<sup>13</sup>The difference in the concentration of donors and acceptors determines the type.

<sup>14</sup>Depends on the doping concentration.

<sup>15</sup>NIEL stand for non-ionizing energy loss and is a quantity which describes the incident particle dependent rate of energy loss due to atomic displacements. The product of the NIEL and the particle fluence (time integrated flux) gives the displacement damage energy deposition per unit mass of material [24].

Figure 3.13: Absolute value of the effective doping concentration  $|N_{\text{eff}}|$  depending on the fluence  $\Phi_{\text{eq}}$  (neutrons, 1 MeV neutron equivalent) [25].

- They act as recombination-generation centers (recombination and generation of electron-hole pairs); in the depletion zone this leads to an increased reverse-bias (or leakage) current (shot noise, thermal runaway).

- They act as trapping centers; this leads to a reduced charge collection distance and hence smaller signal charge (loss of charge).

- They can change the charge density in the space-charge region; higher depletion (or bias) voltage is needed or under depletion may occur.

The first two points have consequences for the S/N ratio. The increase of the reverse-bias current is the most noticeable change. The volume-generated leakage current  $I_{\text{vol}}$  increases linearly<sup>16</sup> with the fluence  $\phi$  [22]:

$$\Delta I_{\text{vol}} = \alpha V \phi, \quad (3.10)$$

where  $V$  denotes the detector volume and  $\alpha$  has to be determined. If the fluence is scaled by the non-ionizing energy loss, then the increase of the leakage current is independent of the particle type.

### 3.4.3 Sensor Types and Technologies

For a detector, an efficient charge collection is necessary to meet the requirements of space, time and energy resolution and overall efficiency. All of these points depend largely on the properties of the sensor. In addition the sensor has to meet geometrical constraints on size and thickness while sustaining a massive amount of radiation damage. Concerning the IBL upgrade, there are three sensor technologies which may fulfill the requirements [27]: planar, 3D and diamond sensors. Each technology is demanding for different operating and environmental variables such as reverse-bias voltage and operating temperature. The first two sensor concepts (see figure 3.14) will be explained in the following.

---

<sup>16</sup>Above type inversion, the rise is stronger (see figure 3.13).

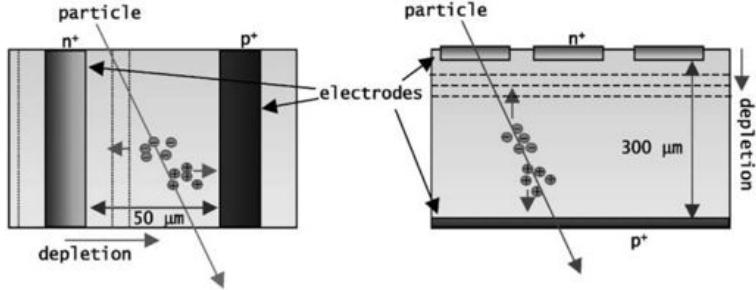

Figure 3.14: A 3D n-in-p sensor (left) in comparison to a planar n-on-n sensor (right) after type inversion. In case of a 3D sensor, the charge, which is generated by a traversing ionizing particle, is collected by a much shorter length. The result is a faster signals and a much lower depletion voltage. The dashed lines show how the depletion region grows from the  $n^+$ -implants, when a reverse bias voltage is applied [28].

**Planar Sensors** The planar technology is the most commonly used and preferred technology for vertex and tracking detectors. The electrical and mechanical properties of planar sensors are very well understood and the manufacturing is relatively low cost and has high yield. Compared to the other sensor technologies, planar sensors require the lowest operating temperature and a high bias voltage. This is because of its geometry: The electrodes are located on top and bottom of the bulk. For full charge collection, the depletion zone has to be extended throughout the whole bulk ( $\approx 250 \mu m$ ). According to formula 3.6 and Ramo's Theorem (formula 3.8) a high voltage has to be applied and charge carriers have to travel long distances to generate an adequate signal.

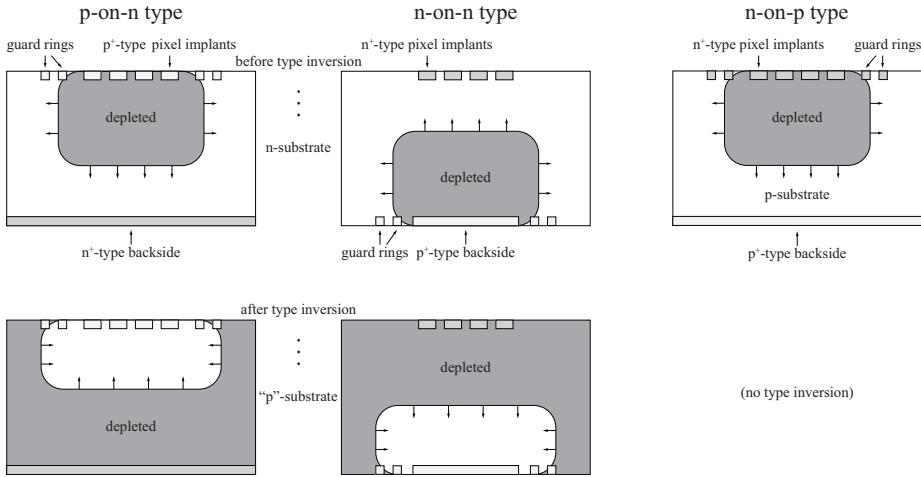

If one assumes negative charge collection at the readout electrode (due to limitations of the CSA), two different approaches for the sensor design are possible (see also figure 3.15):

**n-on-n** This type is used in the current Atlas pixel detector. Before type inversion the depletion region starts growing from the high voltage backside electrode ( $p^+$ -type) into the  $n$ -bulk. The potential drop towards the cutting edge is ensured by a multi guard ring<sup>17</sup> structure. For full charge collection, unirradiated n-on-n sensors have to be operated fully depleted or over-depleted. P-stop or p-spray implant are needed to isolate the  $n^+$ -pixel implants from each other due to electron accumulation beneath the Si-SiO<sub>2</sub> junction. After type inversion (now “p”-bulk) the depletion zone starts growing from the  $n$ -pixel implants. To be able to collect charge negative carriers the detector does not need to be operated fully depleted after type inversion.

**n-on-p** In contrast to the n-on-n type sensors, the p-bulk of the n-on-p type sensors does not change its type. Independent of the fluence, the depletion zone always starts to grow from the pixel side. Therefore n-on-p-type sensors suffice to having only a homogeneous  $p^+$ -implant on the high voltage

<sup>17</sup>Guard rings are biased by a punchthrough mechanism. A punchthrough current flows through the high field region at the cutting edge of the sensor, and creates a potential drop through the different guard rings [30].

Figure 3.15: Comparison between basic planar sensor concepts: p-on-n, n-on-n and n-on-p type from left to right, respectively. Both, the p-on-n and the n-on-n type, have initially an n-bulk. After a certain fluence (several times  $10^{12} \text{ n}_{\text{eq}}/\text{cm}^2$ ), the bulk becomes p-like. The p-on-n type sensor is the only sensor collecting holes at the pixel implants. It is mentioned for the sake of completeness and will not be addressed any further [29].

backside. Having structured implants (namely  $n^+$ -pixel and p-stop/spray implants) only on one side makes this sensor cost-effective [31]. In addition, the sensor can easily be thinned down. This reduces the material budget and improves tracking performance. A major drawback are possible discharges at the cutting edge of the sensor into the readout chip [32]. Although the sensor is biased from the back side the potential drop happens at the front side. A multi guard ring structure on the pixel side ensures the potential drop towards the pixel implants.

**3D Sensors** 3D sensors are the most advanced technology concerning radiation hard silicon detectors. It also requires most advanced process technology which is responsible for the higher costs compared to planar sensors. Cylindrical electrodes are implemented perpendicular to the sensor surface. Implanting the electrodes makes this sensor cost-intensive. 3D sensors require the lowest bias voltage by preserving the full bulk thickness and are operable at intermediate temperatures. This is because of the short distance between the electrodes ( $\leq 100 \mu\text{m}$ ). Due to the geometry of electrodes, the major drawback is the higher detector capacitance which leads to a higher noise and thus reduces S/N ratio. Another drawback is the reduced hit detection probability and charge collection efficiency for normal incidence. This only affects ionizing particles traversing the sensor electrodes. The detector recover full efficiency under a certain incident angle. Another possibility is the implementation of the electrodes under a certain angle into the bulk.

Two different design concepts are proposed for the IBL upgrade [27]: Single-sided (“full-3D”) with active edges and double-sided 3D sensors. The active edge technology allows a minimum of dead area at the edge of the sensor (a

few  $\mu\text{m}$  compared to a few 100  $\mu\text{m}$ ). Active edges becomes an important feature regarding IBL since overlapping (shingling) of modules in direction of the beam pipe is not possible.

## Chapter 4

# The USBpix Test System

### 4.1 Introduction

USBpix was developed as a small and light weighting test system for ATLAS FE-I3 pixel readout chips. As successor to TurboDAQ, which is rather big in size and consists of many expensive hardware components, it provides the functionality which is needed for a full characterization of pixel sensors attached to the FE-I3 pixel readout chip.

The development of the USBpix readout system started in the late 2008. The hardware design and basic software parts (USB driver, microcontroller code, hardware interface libraries, and basic FPGA code) were developed at SiLAB<sup>1</sup>[33, 34]. Other parts of the software (STcontrol and PixLib) were contributed by the ATLAS Pixel Collaboration and were adapted to the USBpix test system with support of University of Göttingen<sup>2</sup>.

A main part of this diploma thesis covers the code maintenance and further development of the USBpix test system for the FE-I3 readout chip. In the beginning of this work, source code refactoring was the main task to ensure extensibility and maintainability of the test system. During this work many parts of the source code were rewritten and new functionality was added. Changes were made to all system levels, i.e. driver, microcontroller code, libraries, user interface and in particular to the FPGA code. Continuous testing and the characterization of sensors (see section 6) during the development cycles helped to improve the overall quality of the software.

Furthermore, USBpix is capable to fulfill the needs for an ATLAS FE-I4 test system, of which development started in the late 2009. The FE-I3 test system's source code was ported to support the future ATLAS FE-I4 readout chip which is foreseen for a future IBL upgrade of the ATLAS pixel detector.

### 4.2 Requirements

The USBpix test system main purpose is the characterization of new generation of sensor material intended for being used for IBL and HL-LHC detector

---

<sup>1</sup>Silizium Labor der Universität Bonn, Nussallee 12, D-53115 Bonn, Germany.

<sup>2</sup>Georg-August-Universität Göttingen, II. Physikalisches Institut, Friedrich-Hund-Platz 1, D-37077 Göttingen, Germany.

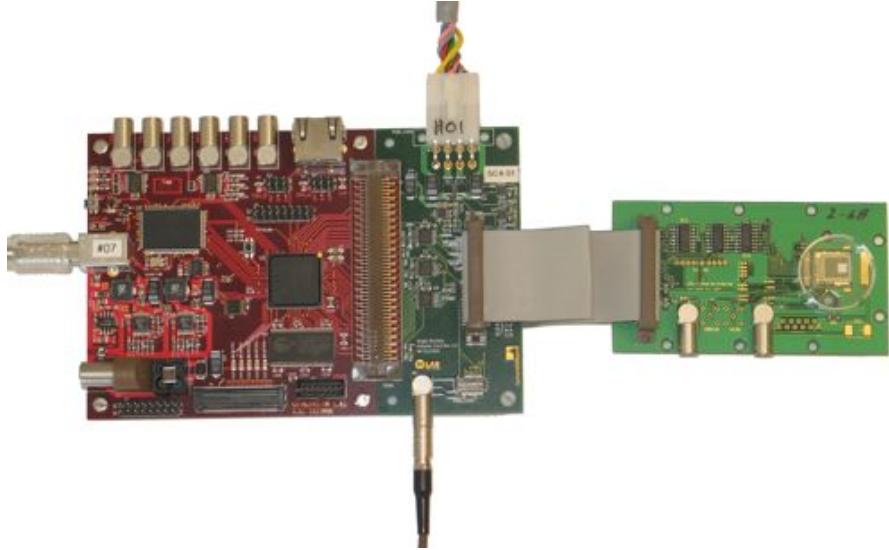

Figure 4.1: The USBpix test system (from left to right): the S3Multi-IO-Board, the Single Module Adapter Card (SMAC), and the Single Chip Card (SCC).

upgrades. Besides that, the USBpix test system has to provide most of the functionality as its predecessor TurboDAQ. The functionality of USBpix includes the following scan types (to name the most important ones):

**Analog Test** Test of the analog pixel block

**Crosstalk Scan** Measurement of the electronic crosstalk between adjacent pixels

**Digital Test** Test of the digital pixel block and digital readout chain

**Monleak Scan** Measurement of the leakage current

**Source Scan** Data taking with radioactive source and external trigger

**Threshold Scan** Measurement of the S-curve

**GDAC and TDAC Tuning** Coarse and fine tuning of the threshold

**FDAC Tuning** Tuning of the Time-over-Threshold (ToT)

**ToT Calibration** Measurement of the relationship between collected charge and ToT

Additionally, the integration of the USBpix test system into the framework of the EUDET beam telescope is one of the major tasks.

### 4.3 Hardware Parts of USBpix

The USBpix hardware is built up in a modular way (see figure 4.1). It consists of three different PCB boards which are connected over flat ribbon cable and

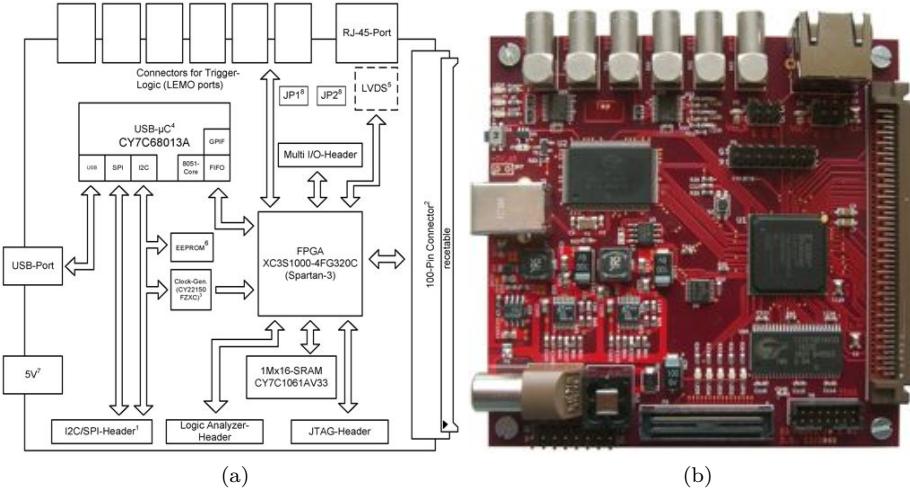

Figure 4.2: (a) Block diagram of the S3Multi-IO-Board. (b) Picture of the S3Multi-IO-Board [35].

on-board connectors. The entire hardware of the test system is connected via a USB 2.0 Hi-Speed interface (480 Mbps raw data speed) to a host computer (or DAQ computer) which is running the control software (STcontrol).

#### 4.3.1 S3Multi-IO-Board

The S3Multi-IO-Board is a multi-purpose I/O board (Rev. 1.03, see figure 4.2). It is the central control unit of the test system containing all of the programmable hardware parts. The communication between the host computer and the S3Multi-IO-Board is implemented in an 8051-based USB-capable microcontroller (Cypress CY7C68013A). The 8051-microcontroller steers the communication between hardware parts on the S3Multi-IO-Board (FPGA, EEPROM, programmable clock generator, ADC; for more details see following sections) and the software running on the host computer. To set the programmable clock generator (Cypress CY22150FZXI) or to read out the analog-to-digital converters (Maxim MAX1238, located on the Adapter Card) the microcontroller uses a 2-wire I<sup>2</sup>C serial interface. The EEPROM (Microchip 24LC128), which contains the firmware of the microcontroller, is serially connected to the 8051-microcontroller. Registers and Block RAM inside the FPGA (Xilinx Spartan-3 XC3S1000-FGG320) can be accessed by using the Slow Interface. The Slow Interface<sup>3</sup> is a 8-bit wide parallel data bus with a 48 MHz clock (UCLK, internal clock of the microcontroller). The address space is 16-bit wide. The microcontroller and the FPGA have access to 16 Mbit asynchronous SRAM. The SRAM (Cypress CY7C1061AV33) is connected to a 16-bit wide data bus<sup>4</sup>. The clock speed depends on whether the microcontroller or the FPGA is accessing the SRAM and is 48 MHz or 40 MHz, respectively. The memory can

<sup>3</sup>The name derives from the fact that the internal clock was initially running on 24 MHz. The speed of the internal clock was changed during this thesis.

<sup>4</sup>A 16-bit wide parallel interface is available in hardware but not implemented in software. Currently, only a 8-bit wide data bus is used.

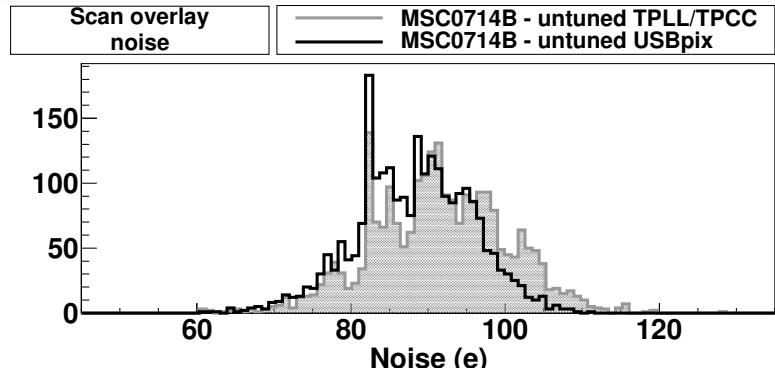

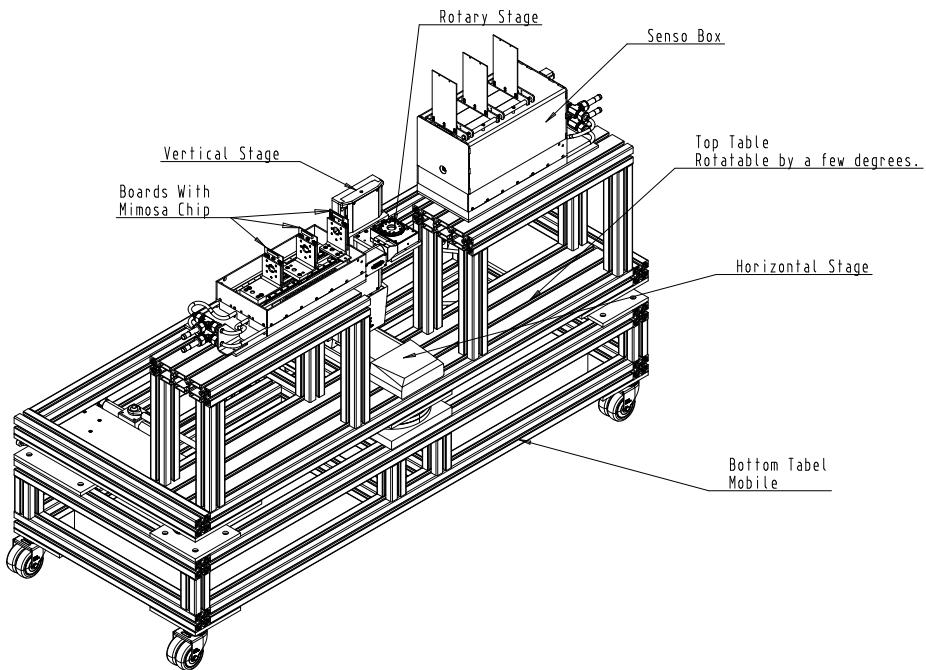

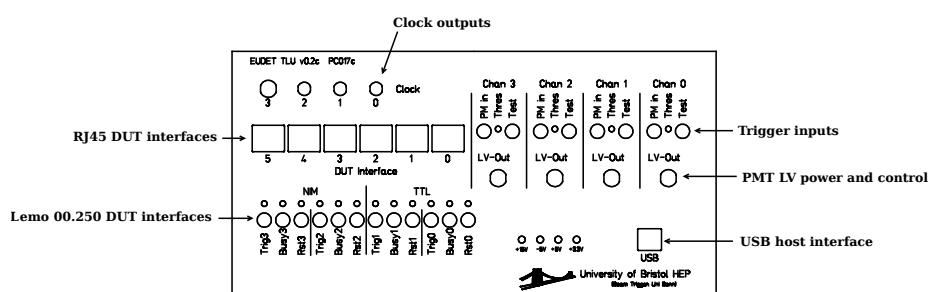

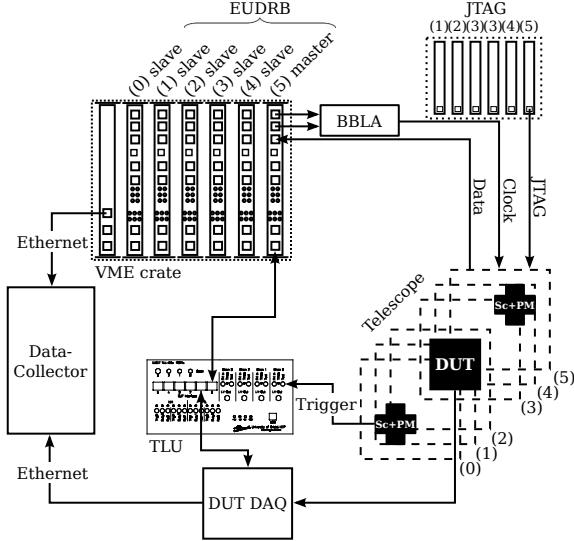

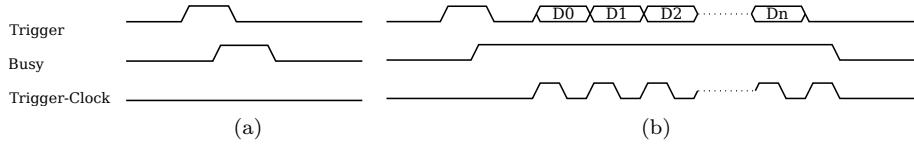

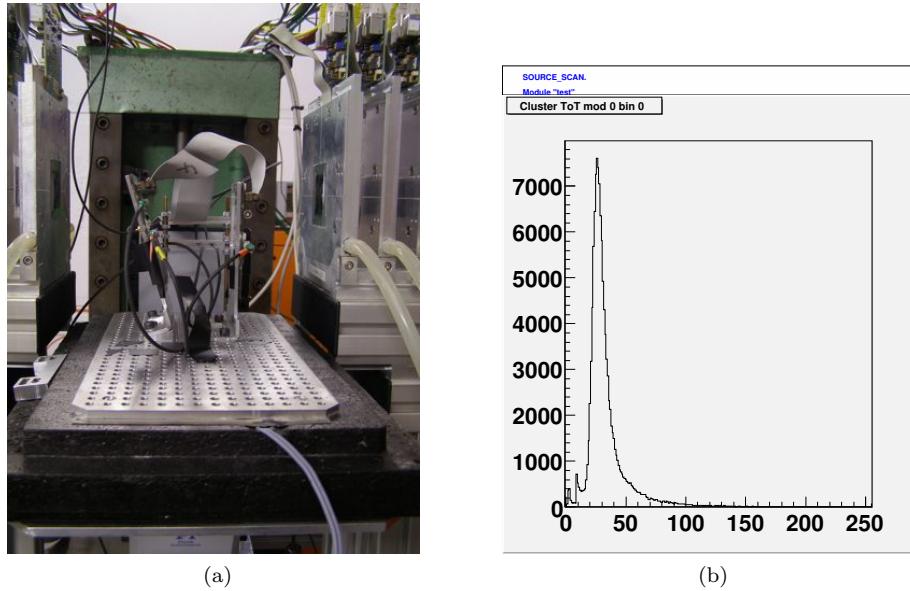

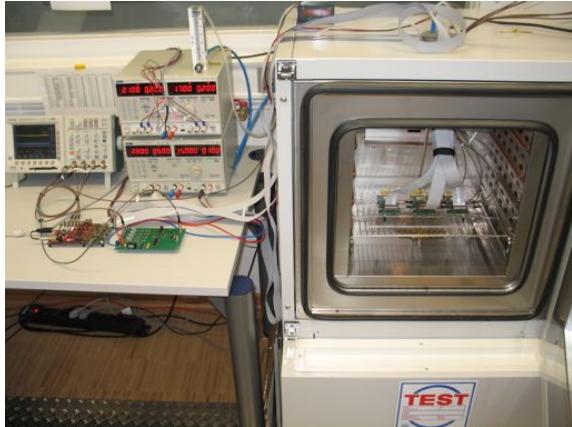

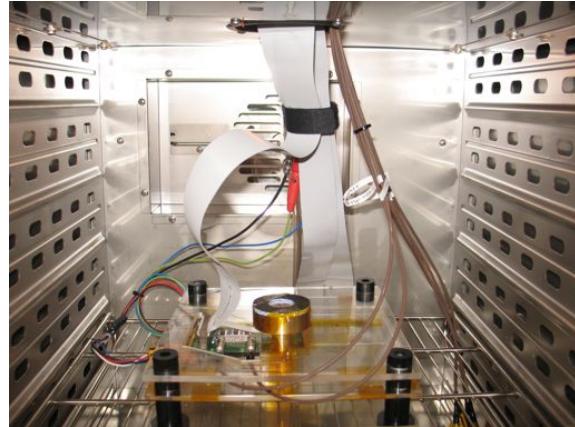

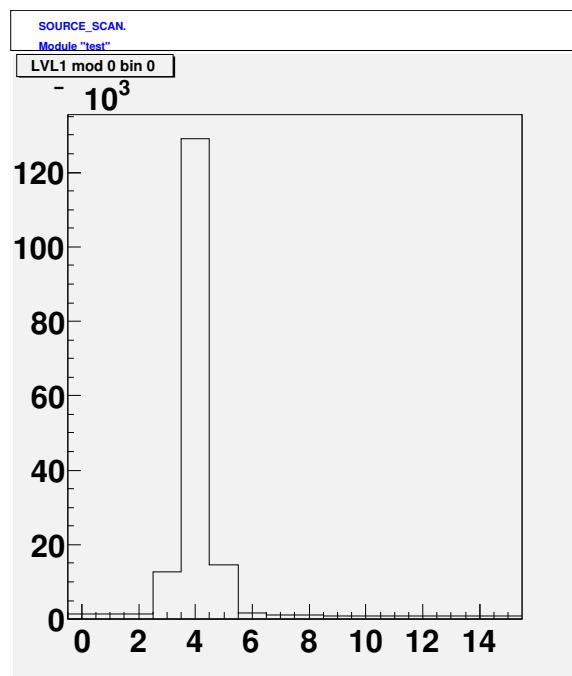

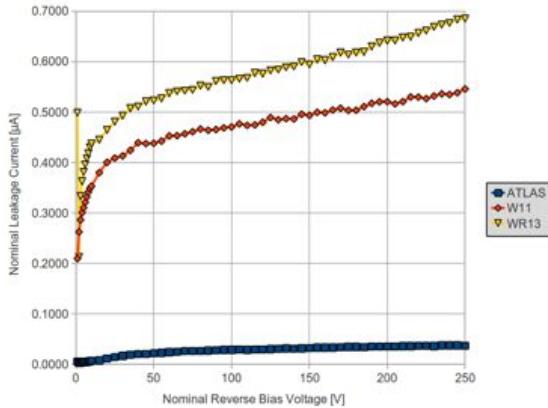

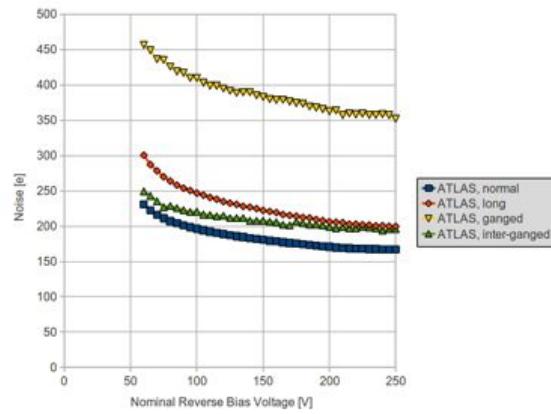

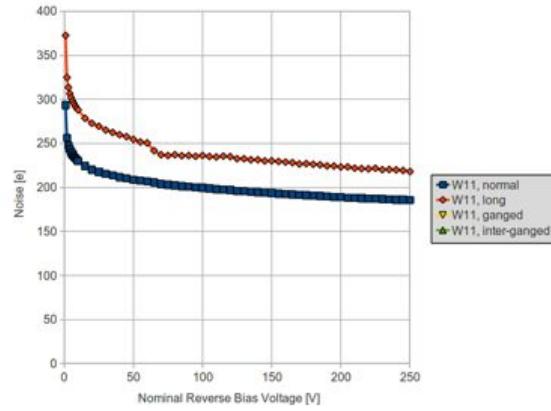

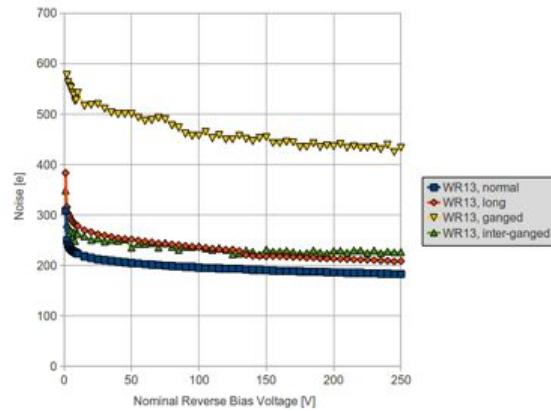

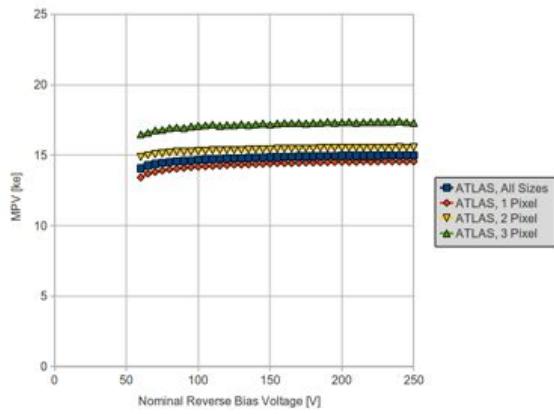

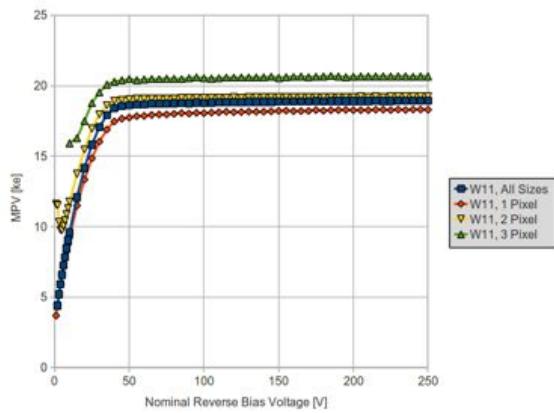

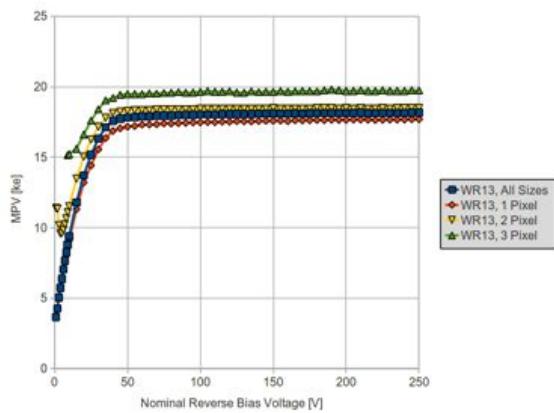

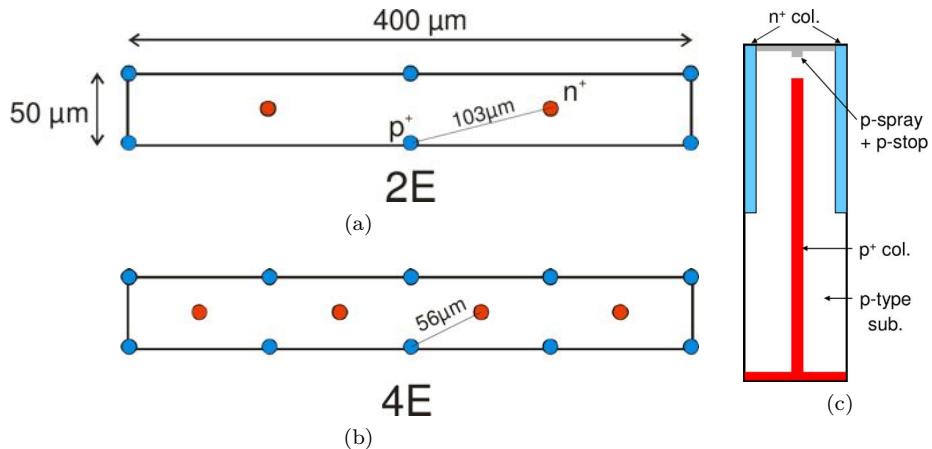

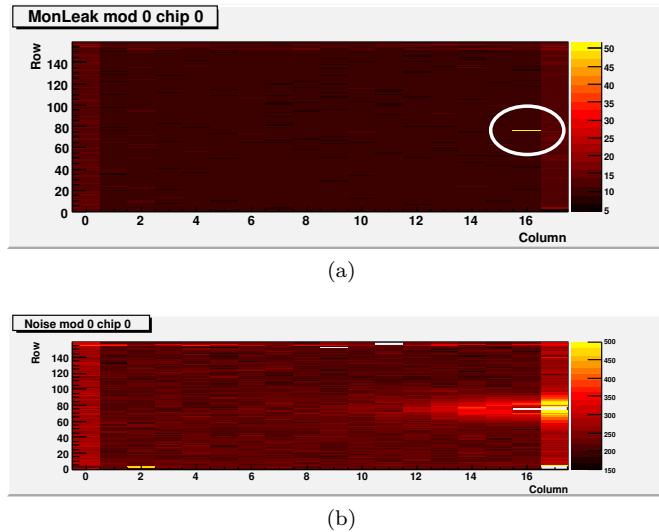

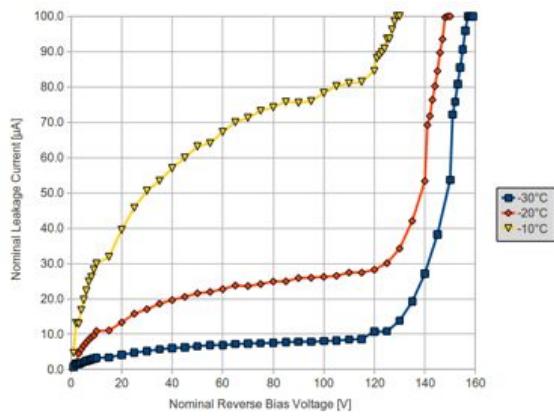

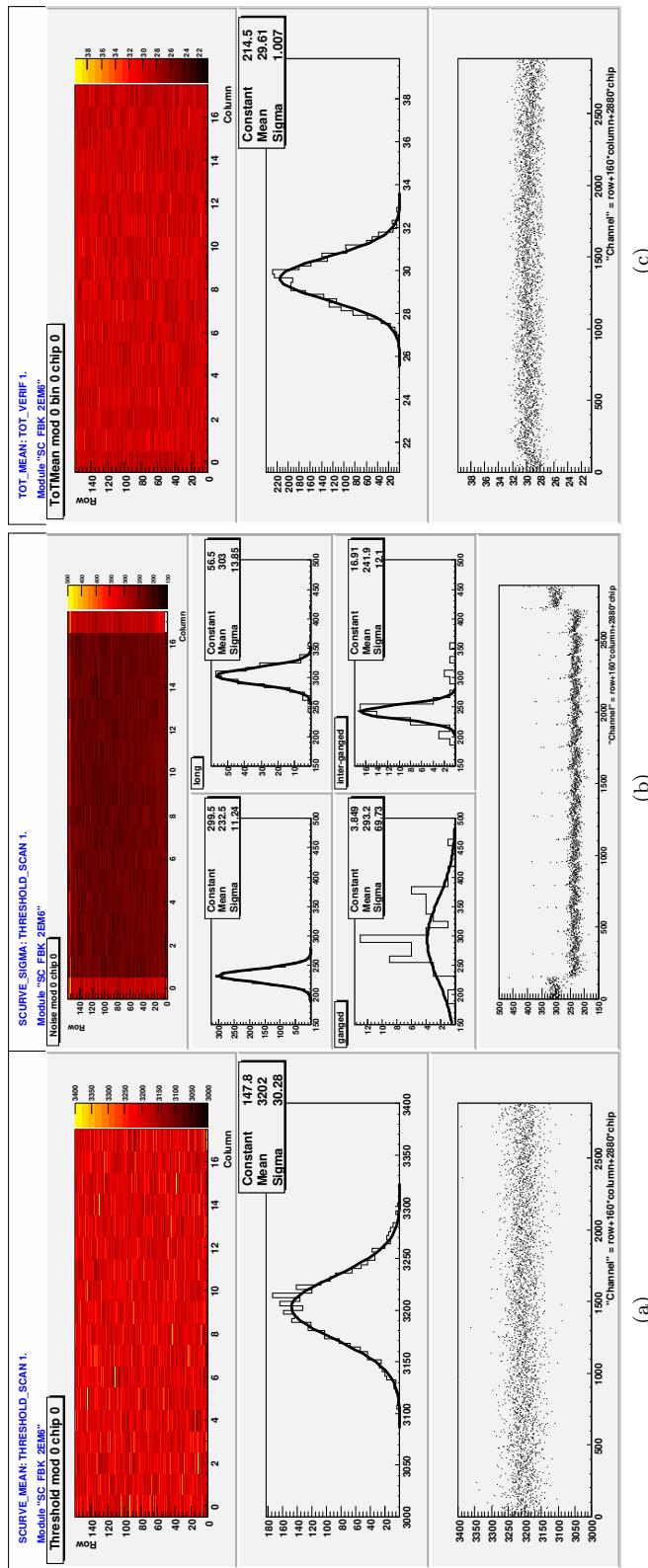

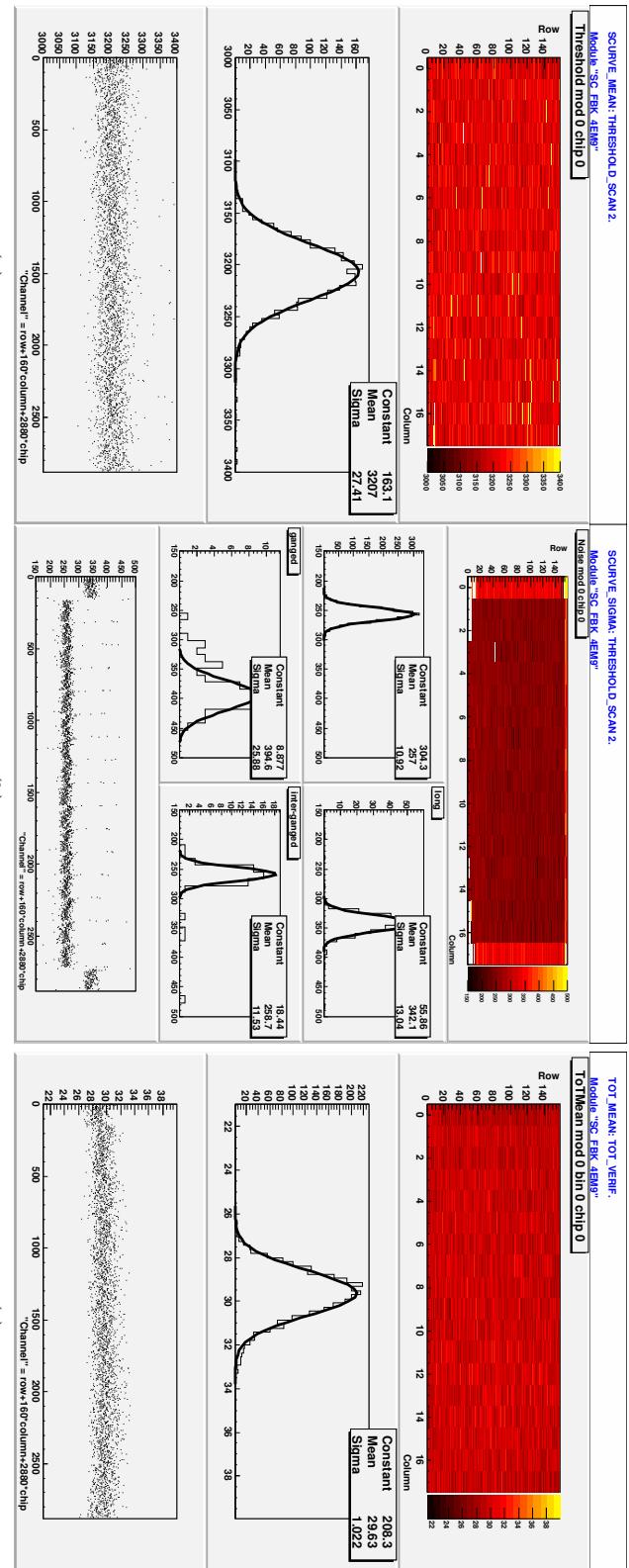

be accessed through a 20-bit wide address bus. The overall maximum read-out speed reaches  $1/4$  of the raw data speed of the USB 2.0 Hi-Speed interface (approximately 15 MB/s).