UNIVERSITÀ DEGLI STUDI DI BARI

XXXV Ciclo del Dottorato di Ricerca in Fisica

**Silicon pixel sensor characterization for

ultra-light tracking detector with

truly-cylindrical geometry.**

**Relatori:**

Prof. Giuseppe Bruno

Dott. Domenico Colella

**Dottoranda:**

Arianna Grisel Torres Ramos

Anno Accademico 2022/2023

# Abstract

ALICE (A Large Ion Collider Experiment) is the heavy-ion experiment at the Large Hadron Collider (LHC) at CERN; it is designed to address the physics of strongly interacting matter and in particular the properties of quark-gluon plasma. The experiment took data from 2009 to 2018 (LHC Run1 and Run 2) and went under a major upgrade during the LHC Long Shutdown 2 (2018-2021). Starting from 2022 detector is back in operation and it is foreseen to keep performing measurements up to 2032. A pillar of the ALICE future upgrade program is the improvement of the Inner Tracking System (ITS2) performance by the replacement of its three innermost layers (ITS3) during the LHC Long Shutdown 3, taking place between 2026 and 2028. The proposal is based on a vertex detector consisting of three cylindrical concentric layers composed by curved wafer-scale silicon sensors, built on CMOS Monolithic Active Pixel Sensors (MAPS) with the sensor matrix and readout integrated in a single chip. The first detector layer will be positioned at a radial distance from the interaction point of 18 mm. The new detector will present a significant reduction of the material budget, from  $0.36\% X_0$  (in ITS2) to  $0.05\% X_0$  per layer, thus improving the vertexing and tracking performance, especially for particles with low transverse momentum ( $p_T < 1$  GeV/c).

The main scope of this thesis is to report on the activities associated with the characterization of bent MAPS, fabricated with TowerJazz 180 nm CMOS Technology, as well as the development of tools and techniques dedicated to bend accurately such devices.

Extensive characterization of a single ALPIDE chip (used for the current ITS2), positioned flat and bent down to the intended radius for the innermost layer of the ITS3 (18 mm), was carried out in order to evaluate its performance under the mechanical stress involved in the bending process. The measurement of the main variables steering the chip functioning was performed by evaluating their behavior over the time and through the variation of different in-pixel circuit parameters. The results were compared for both geometries. These studies aimed to demonstrate that ALPIDE functionalities are preserved despite the curvature effects.

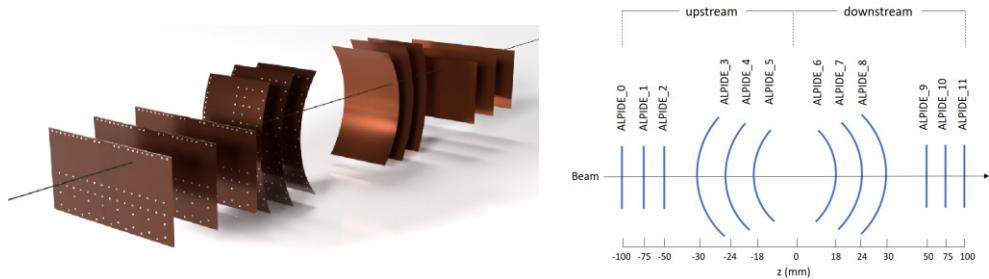

An important component in the investigation of a detector performance is the realization of a so-called test-beam experiment. The data acquired during the first ever in-beam characterization of a bent MAPS, performed in a test-beam campaign at the DESY II test-beam facility in June 2020, were analyzed

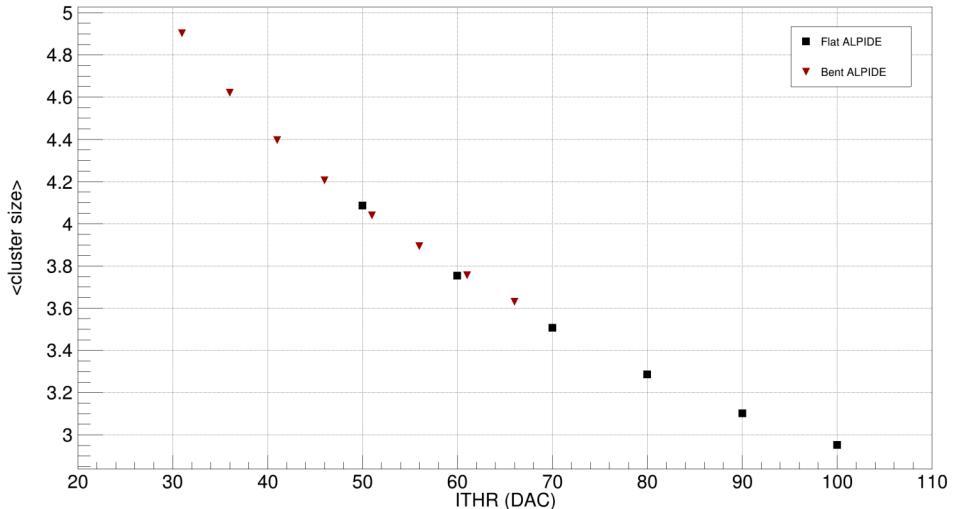

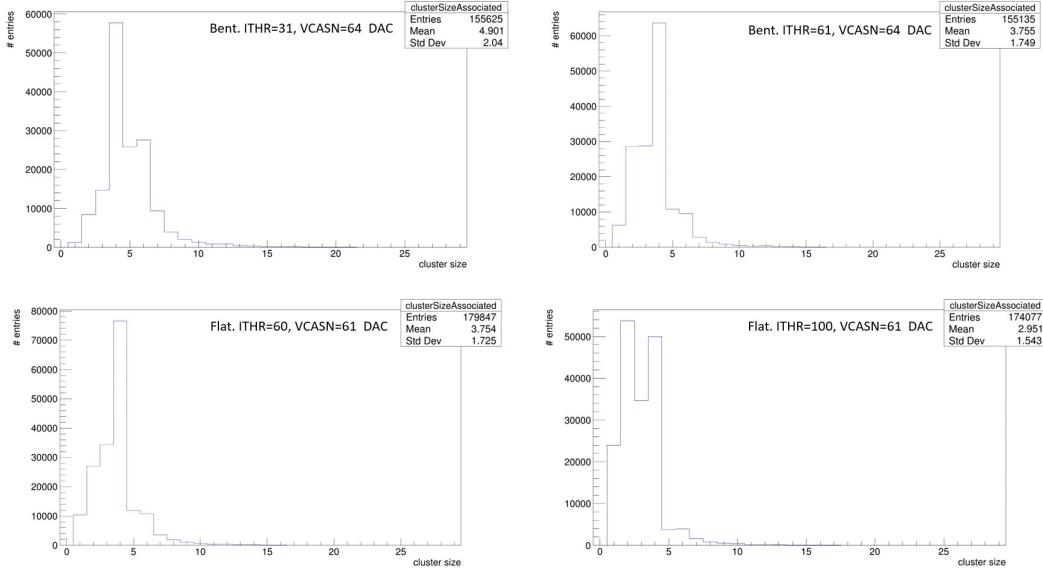

and systematically compared with data taken with a flat ALPIDE. The study had the main scope to evaluate the sensing performance of a bent chip through the variation of the working point defined by front-end parameters and contrast it with the results of an originally flat sensor.

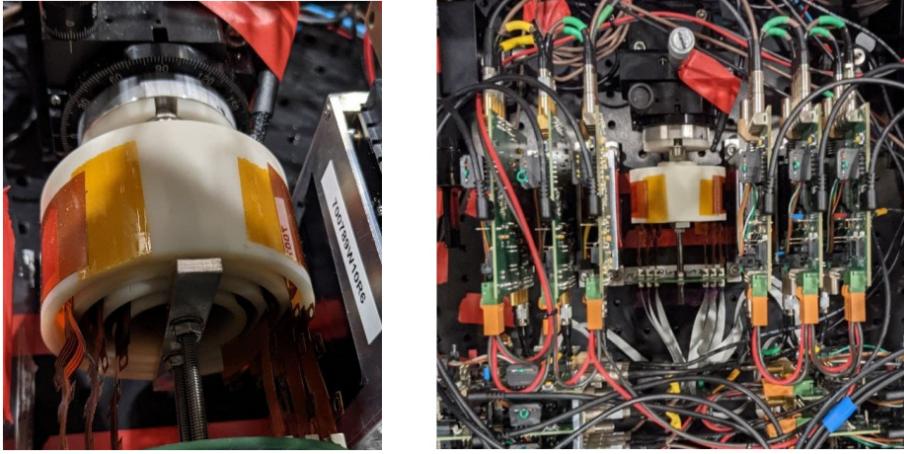

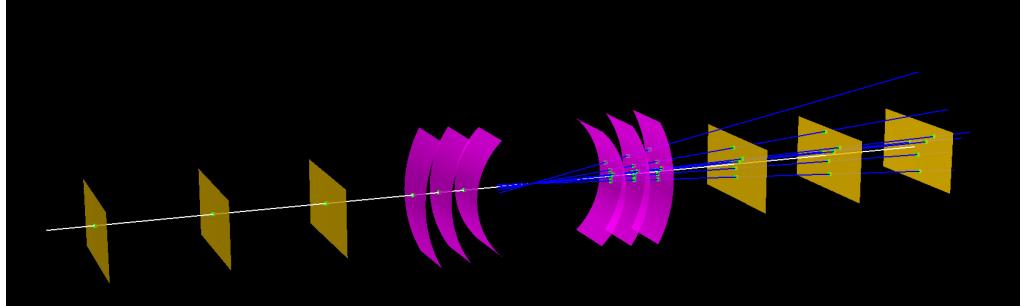

The analysis of efficiency, cluster size and preliminary position resolution was also performed for an experiment realized in July 2021 at CERN SPS facility, where a set of six ALPIDE chips were bent at the foreseen ITS3 layer radii, forming the so-called micro-ITS3. The objective was the simultaneous in-beam characterization of several concentrically arranged bent ALPIDE chips, thus modeling the tracking layers of the future ITS3.

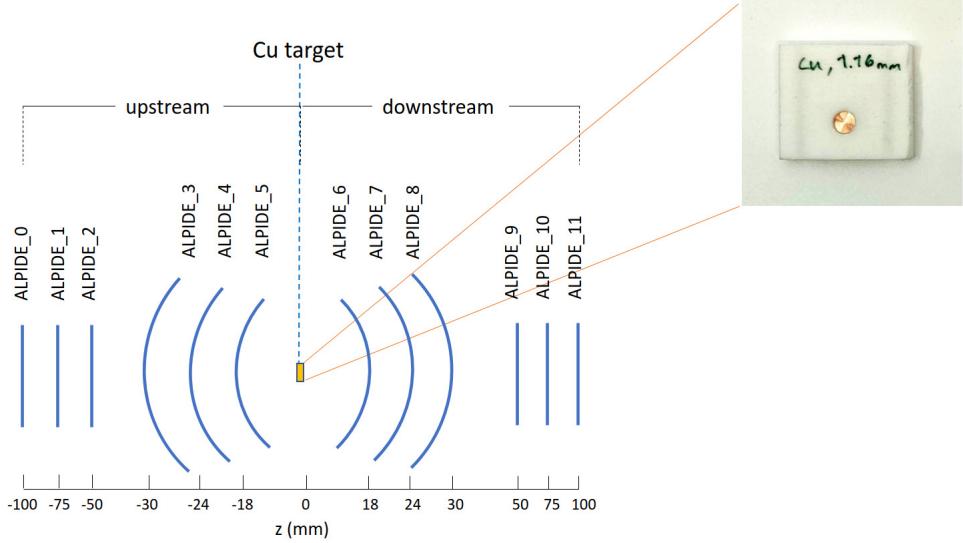

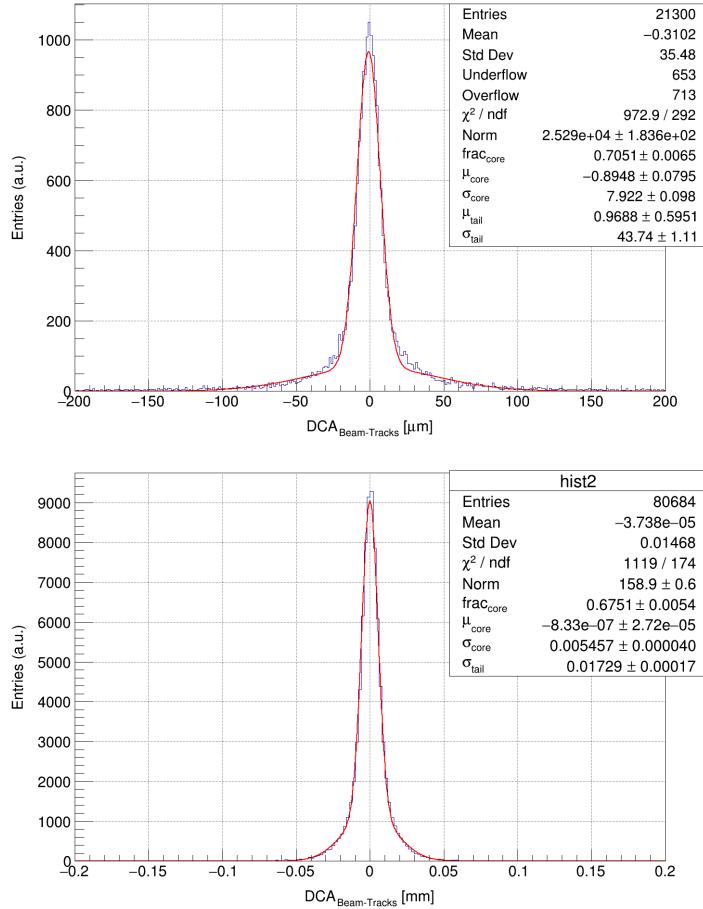

An additional study was done from measurements where a copper target was introduced in the center of the detector barrel of the micro-ITS3 in order to mimic particles emerging from a real collision. Through this activity the possibility to reconstruct tracks and vertices from hadronic interactions in a geometrical configuration very close to the next full ITS (including ITS3) has been explored and demonstrated.

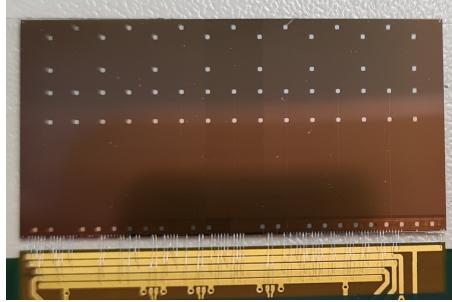

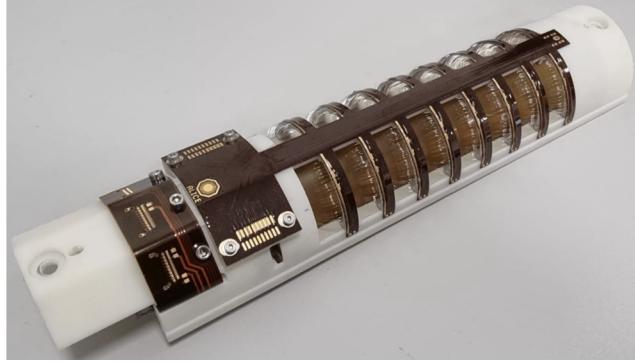

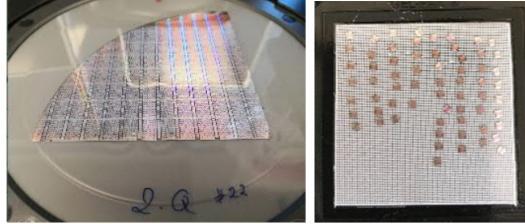

The tests on small sensors have opened the way to the investigation of a large scale sensor. The “super-ALPIDE” project has the goal to assemble a detector with geometry similar to one half-layer of the ITS3, using a working sensor with large dimensions made of a matrix of not diced ALPIDE chips. The concept of the super-ALPIDE design, including the components and mechanical structures implemented for readout and support, is presented in this thesis. Techniques and tools employed to perform sensor bending, parts assembly and wired interconnections are described in detail.

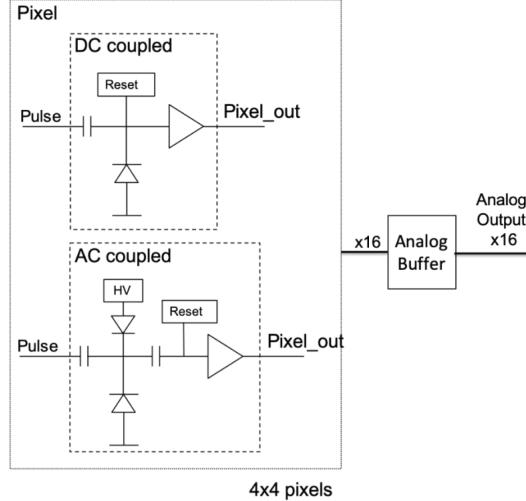

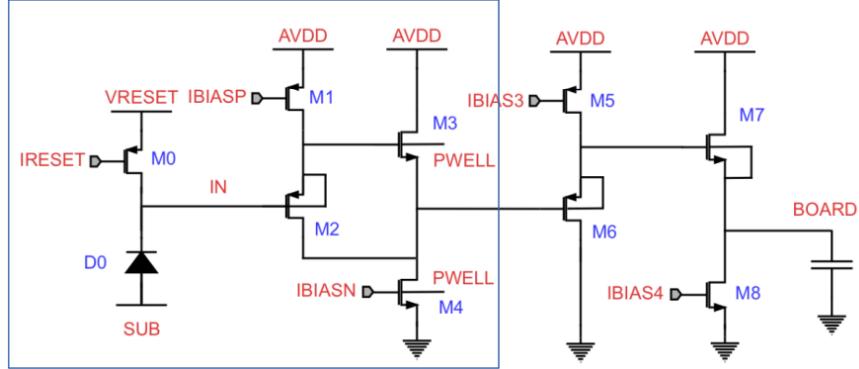

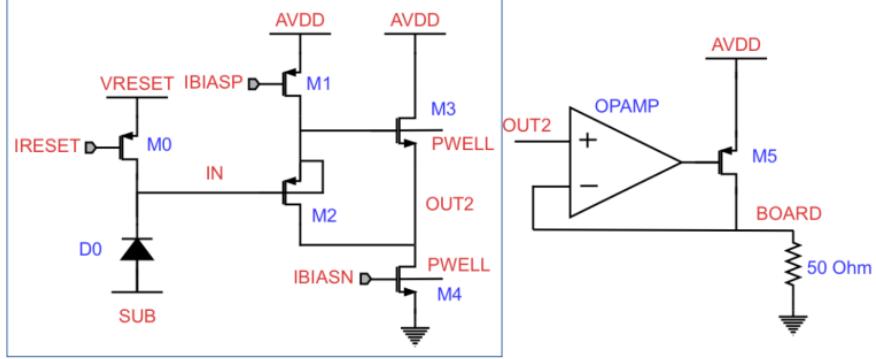

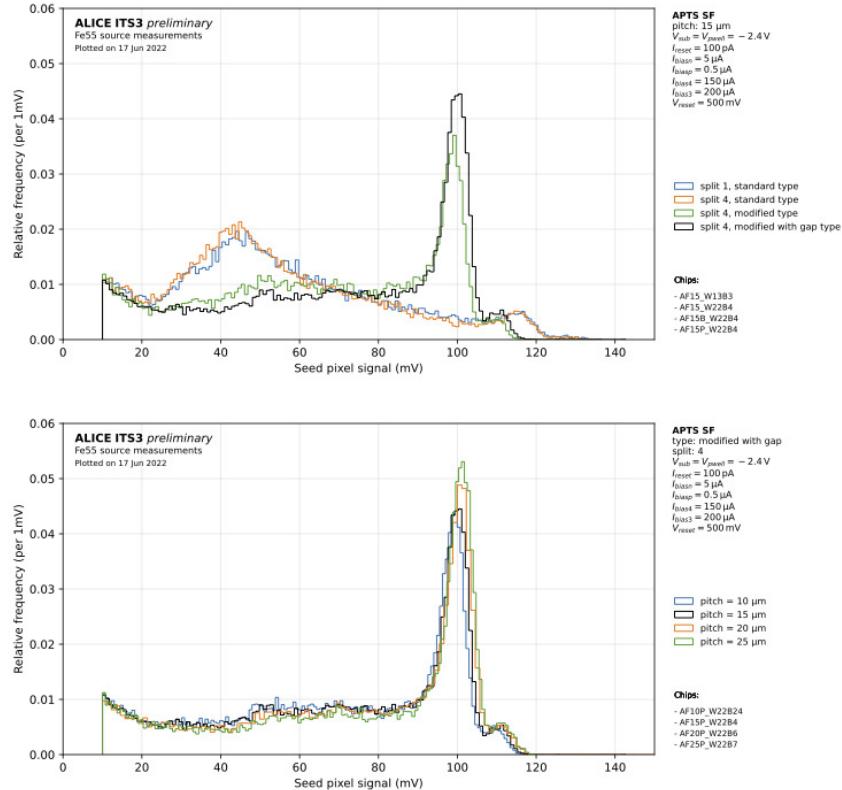

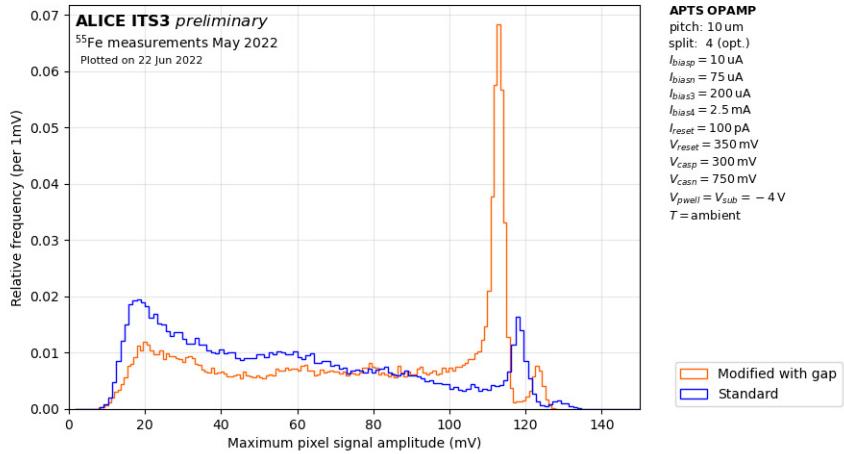

Another subject, within the context of the ITS upgrade R&D, is the preliminary study of new sensor prototypes based on TPSCo 65  $nm$  CMOS process, the first choice of the technology for the implementation of the wafer-scale sensor, which allows for more than four-fold increase of the number of transistors per pixel compared to the older 180  $nm$  and higher spatial resolution resulting from the possibility to fabricate smaller pixels. A first submission in TPSCo 65  $nm$  was done as a Multi Layer Reticle (MLR1). An overview of the three main prototype structures composing MLR1 (Digital Pixel Test Structure, CE65 and Analogue Pixel Test Structure) is given in the last chapter of this thesis. The APTS op-amp, modified with gap version with DC coupled in-pixel architecture and 10  $\mu m$  pitch, was tested in laboratory in order to characterize this chip flavor. The response of the pixels front-end was monitored by the measurement at different chip bias settings to evaluate the influence of the main parameters of the in-pixel circuit on the signal processing. The study of the device charge collection properties was performed through measurements with X-rays emitted by an  $^{55}Fe$  source.

# Contents

|          |                                                                  |           |

|----------|------------------------------------------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>                                              | <b>6</b>  |

| 1.1      | Ultra-relativistic heavy-ion collisions . . . . .                | 8         |

| 1.1.1    | The evolution of a heavy-ion collision . . . . .                 | 9         |

| 1.1.2    | Observables in heavy-ion collisions . . . . .                    | 11        |

| 1.2      | A Large Ion Collider Experiment . . . . .                        | 14        |

| 1.2.1    | Tracking detectors . . . . .                                     | 15        |

| 1.2.1.1  | Inner Tracking System (ITS) . . . . .                            | 16        |

| 1.2.1.2  | Time Projection Chamber (TPC) . . . . .                          | 17        |

| 1.2.2    | Particle identification detectors . . . . .                      | 17        |

| 1.2.2.1  | Transition Radiation Detector (TRD) . . . . .                    | 17        |

| 1.2.2.2  | Time of Flight (TOF) . . . . .                                   | 17        |

| 1.2.2.3  | High Momentum Particle Identification Detector (HMPID) . . . . . | 17        |

| 1.2.3    | Calorimeters . . . . .                                           | 18        |

| 1.2.4    | Muon detectors . . . . .                                         | 18        |

| 1.2.5    | Forward and trigger detectors . . . . .                          | 18        |

| 1.2.6    | ALICE upgrade prospect . . . . .                                 | 18        |

| 1.3      | Upgraded Inner Tracking System (ITS3) . . . . .                  | 20        |

| 1.3.1    | Physics performance . . . . .                                    | 20        |

| 1.3.2    | Tracking performance . . . . .                                   | 23        |

| 1.3.3    | Upgrade concept . . . . .                                        | 24        |

| 1.3.4    | Layout of the future ITS3 . . . . .                              | 30        |

| <b>2</b> | <b>Silicon Pixel Detectors in High Energy Physics</b>            | <b>33</b> |

| 2.1      | Silicon detectors . . . . .                                      | 33        |

| 2.1.1    | Signal formation in silicon sensors . . . . .                    | 34        |

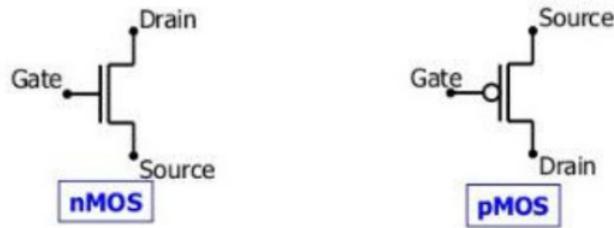

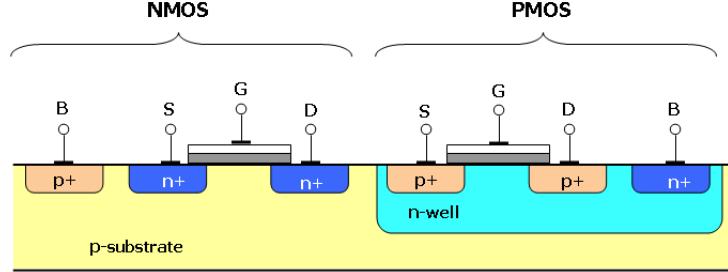

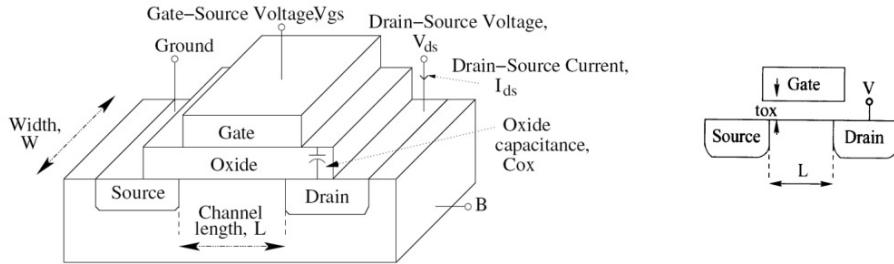

| 2.2      | CMOS technology . . . . .                                        | 35        |

| 2.2.1    | Field Effect Transistors (FETs) . . . . .                        | 35        |

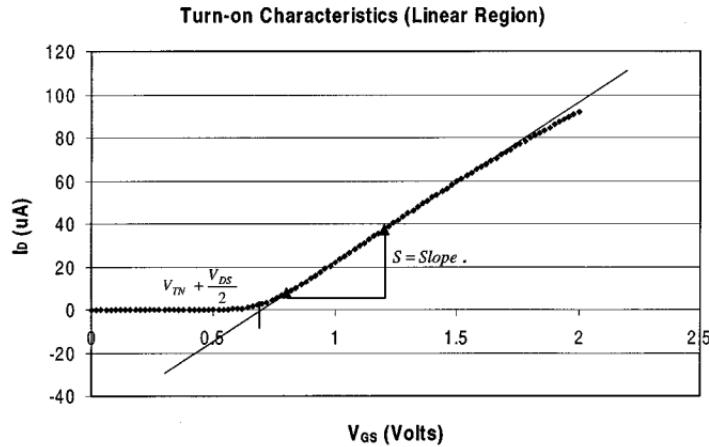

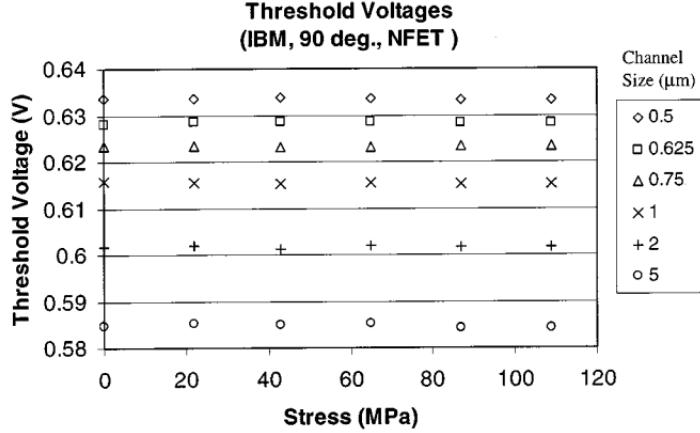

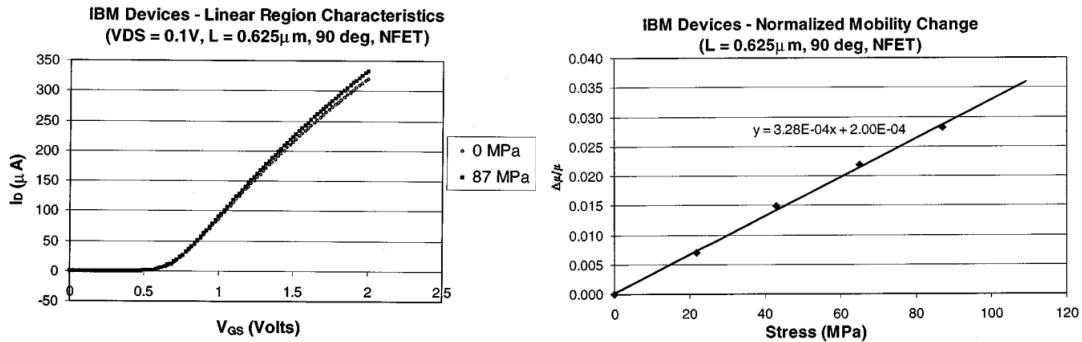

| 2.2.2    | Piezoresistance in MOSFETs . . . . .                             | 36        |

| 2.3      | Monolithic Active Pixel Sensors (MAPS) . . . . .                 | 41        |

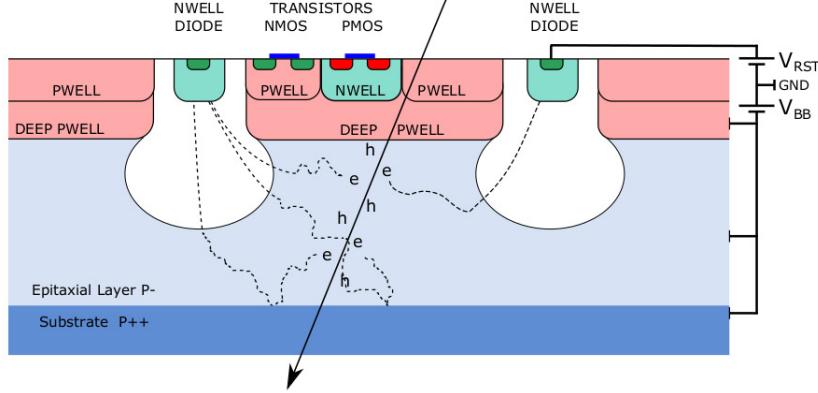

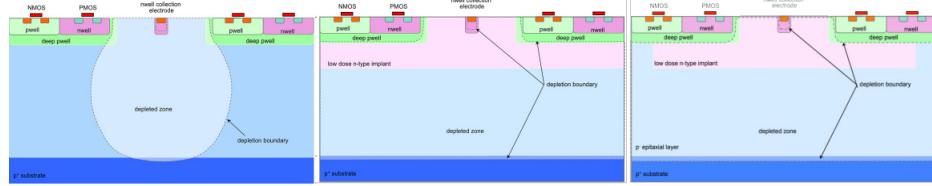

| 2.3.1    | MAPS process and principle operation . . . . .                   | 41        |

| 2.3.2    | Charge Generation and Collection in MAPS . . . . .               | 43        |

| 2.3.3    | Radiation effects . . . . .                                      | 45        |

|                                                                                   |            |

|-----------------------------------------------------------------------------------|------------|

| <b>3 The ALICE PIxel DEtector of the ITS</b>                                      | <b>48</b>  |

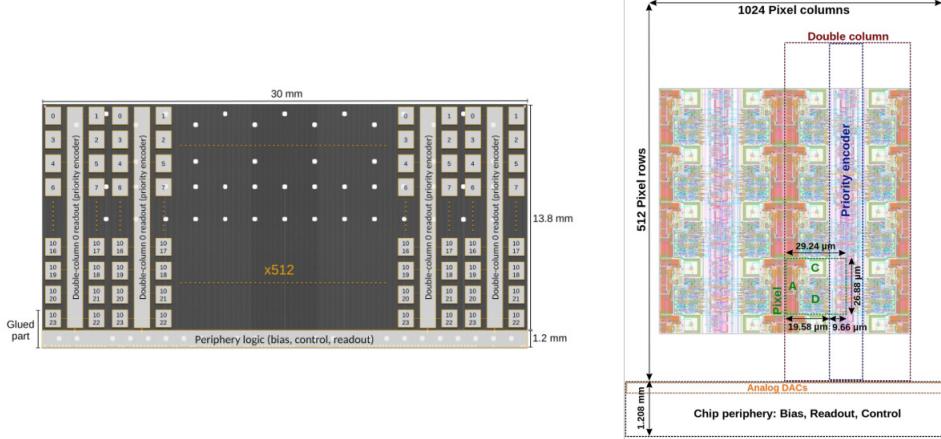

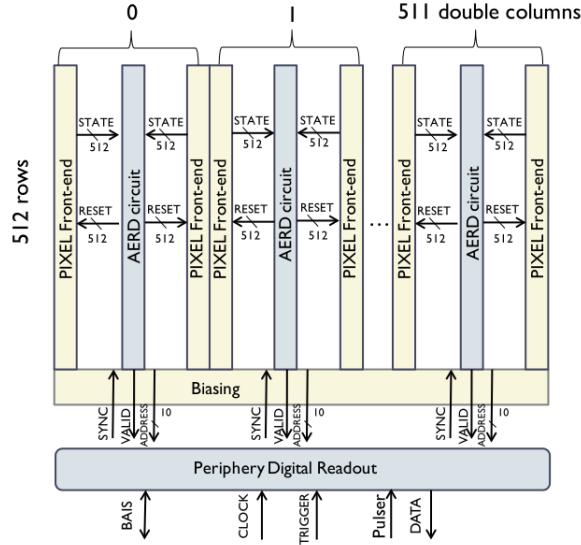

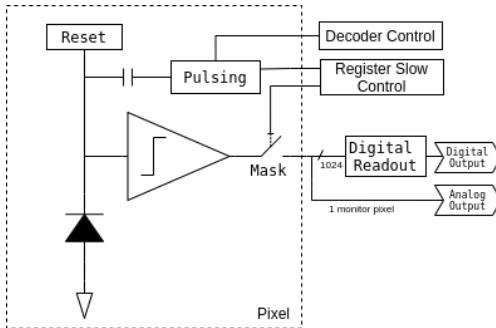

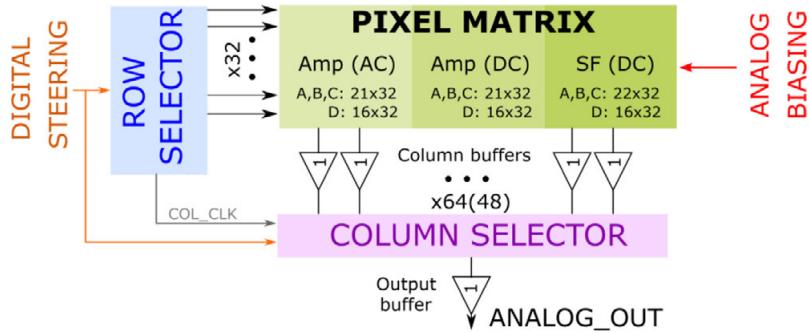

| 3.1 ALPIDE Pixel Matrix Architecture . . . . .                                    | 49         |

| 3.2 Principle of operation of in-pixel circuitry . . . . .                        | 49         |

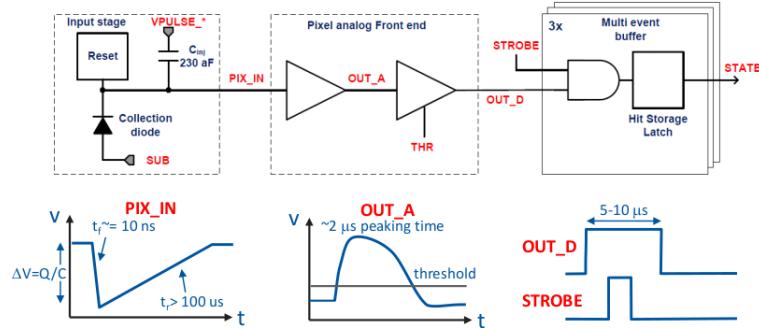

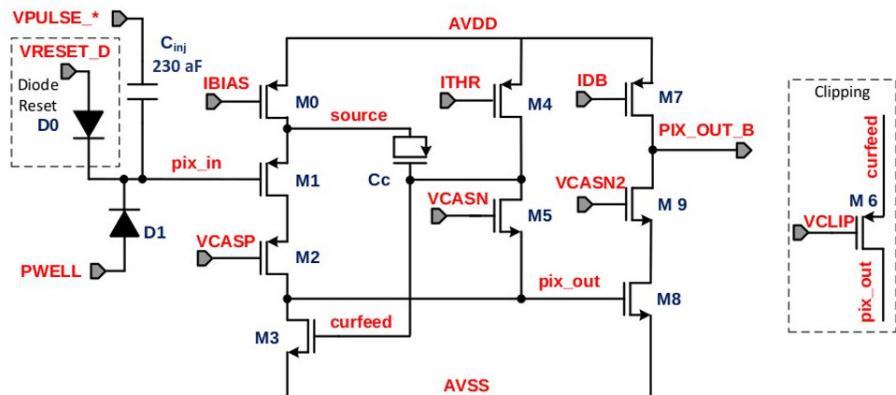

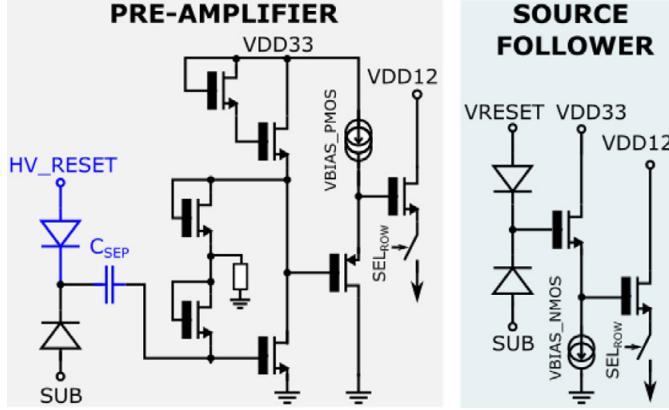

| 3.2.1 Pixel Analogue Front-End . . . . .                                          | 51         |

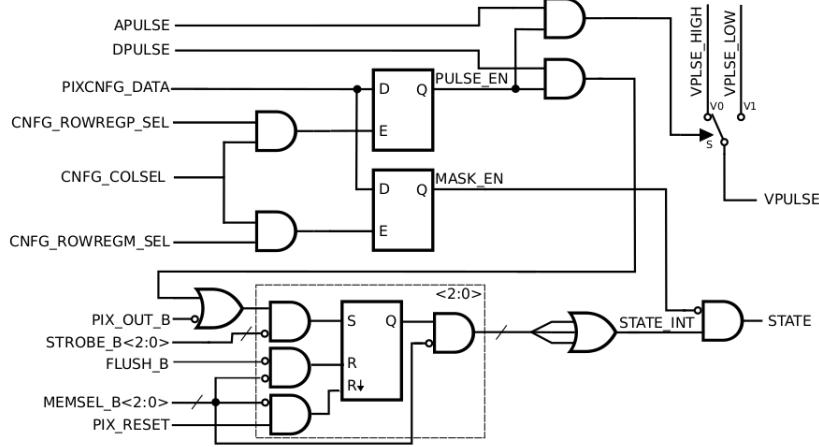

| 3.2.2 Pixel digital Front-End . . . . .                                           | 52         |

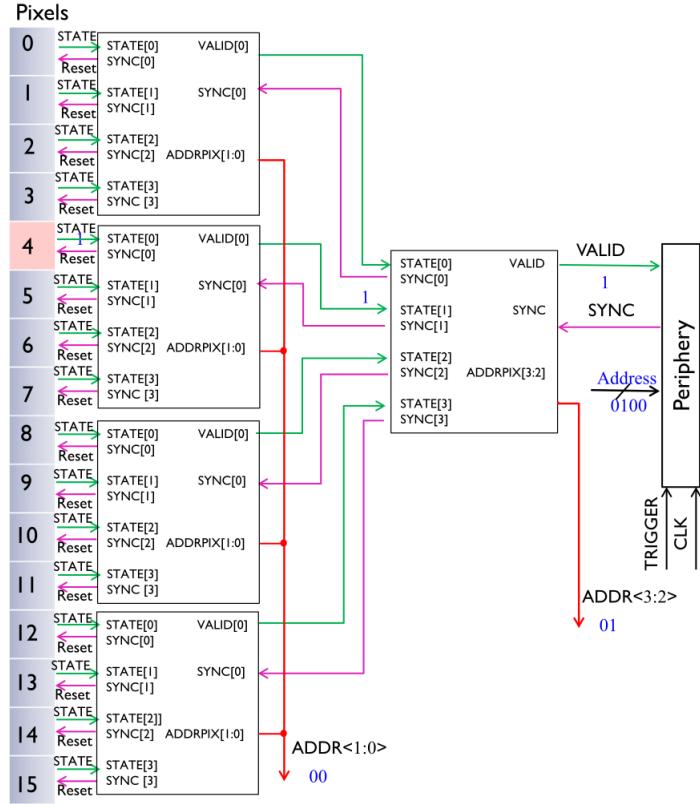

| 3.3 Address-Encoder and Reset-Decoder Circuit . . . . .                           | 52         |

| 3.4 Electrical characterization of an ALPIDE chip in laboratory . . . . .         | 54         |

| 3.4.1 Threshold and Noise . . . . .                                               | 56         |

| 3.4.2 Fake-hit Rate . . . . .                                                     | 58         |

| 3.4.3 Test results . . . . .                                                      | 59         |

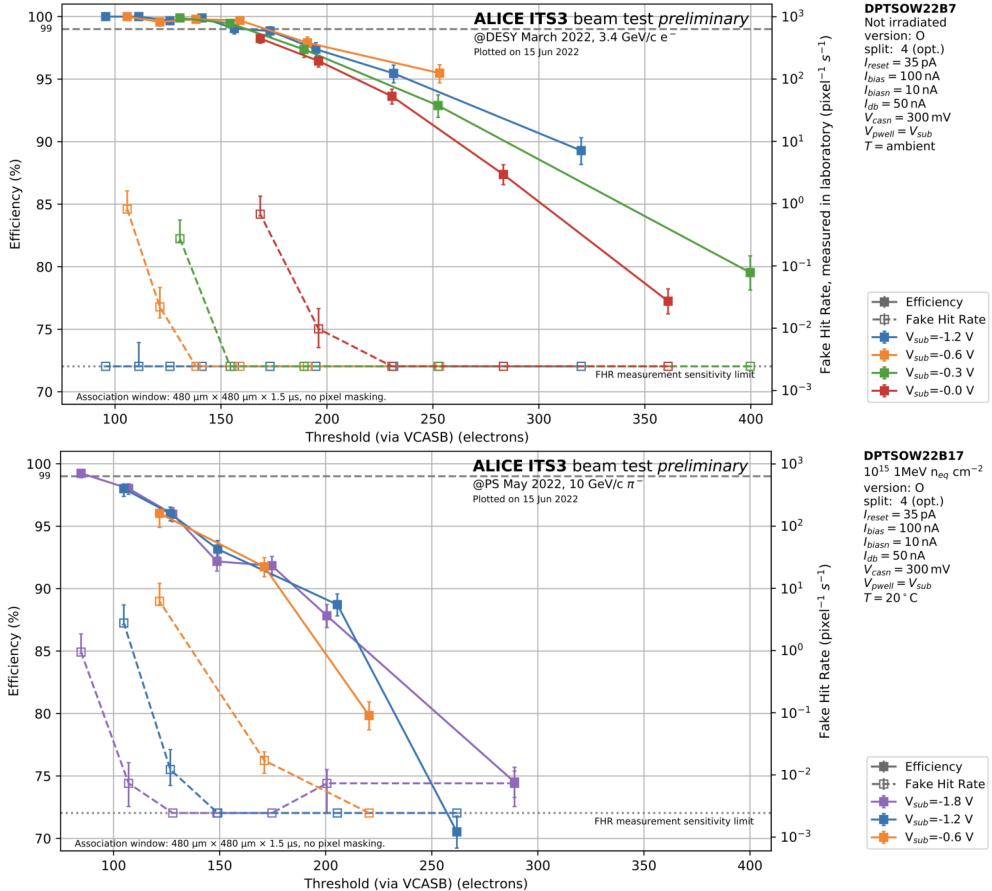

| 3.5 Study on the performance of bent ALPIDEs in test-beam environments . . . . .  | 65         |

| 3.5.1 Test-beam facilities . . . . .                                              | 66         |

| 3.5.2 Test-beam experiments . . . . .                                             | 67         |

| 3.5.2.1 Test-beam June 2020 . . . . .                                             | 68         |

| 3.5.2.2 Test-beam July 2021 . . . . .                                             | 69         |

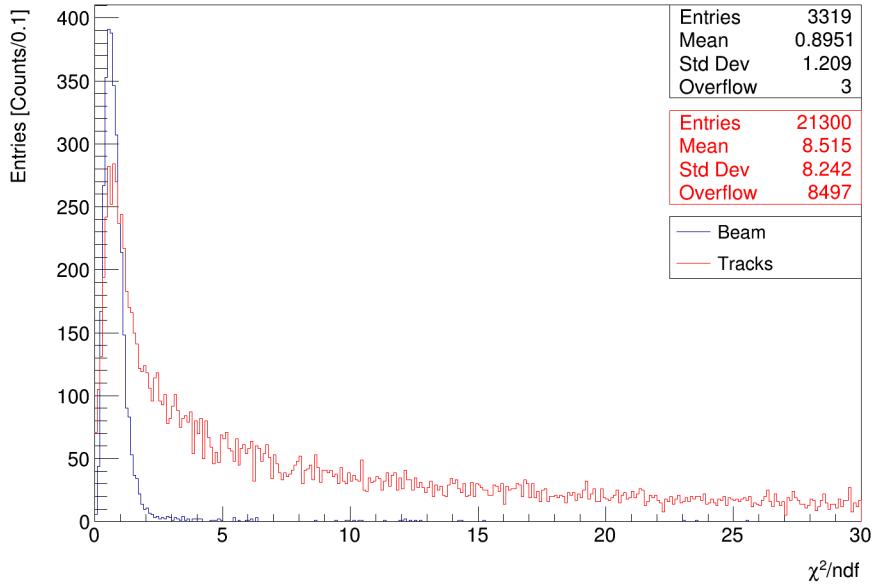

| 3.5.3 Test-beam reconstruction chain with Corryvreckan . . . . .                  | 72         |

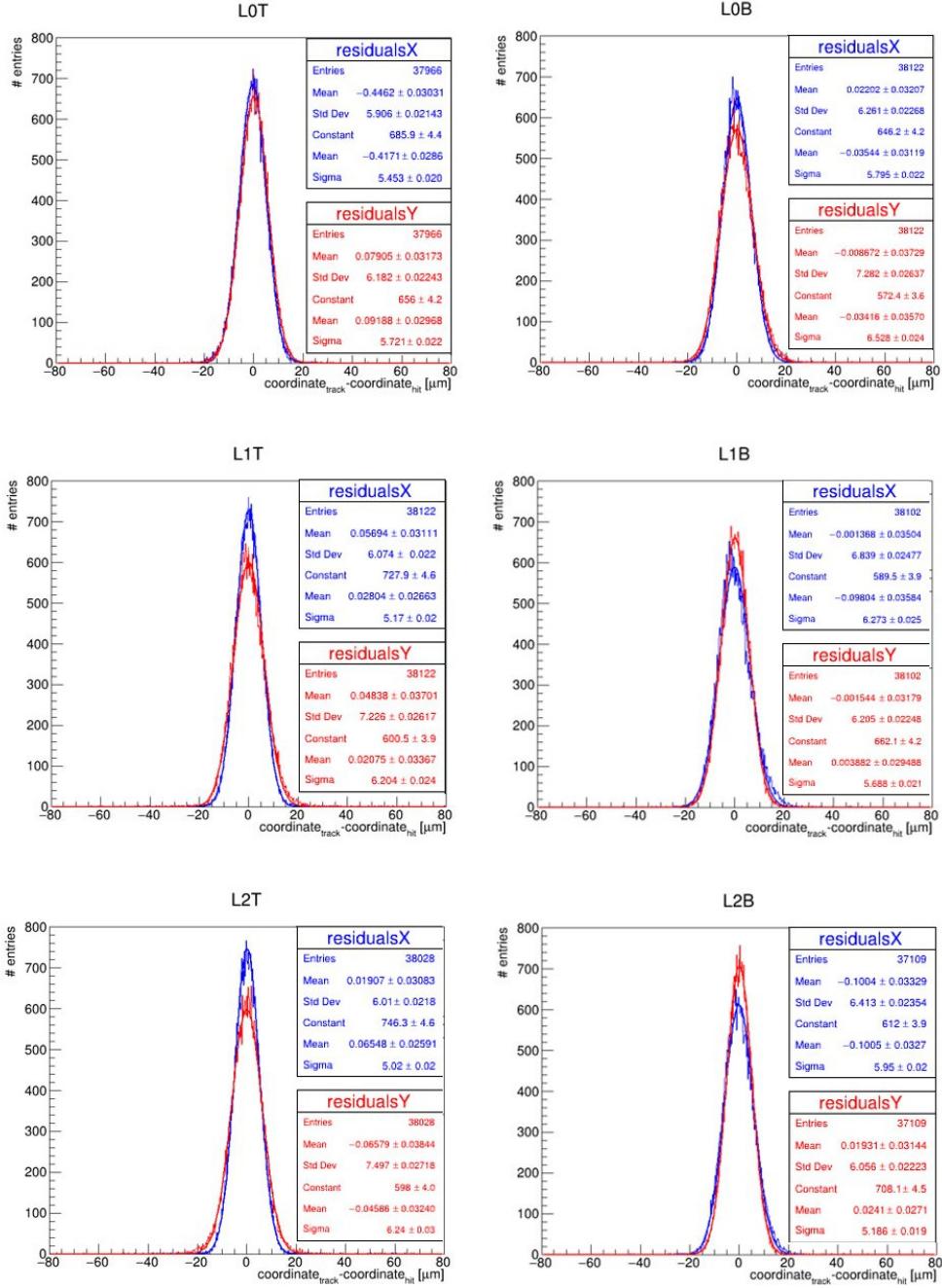

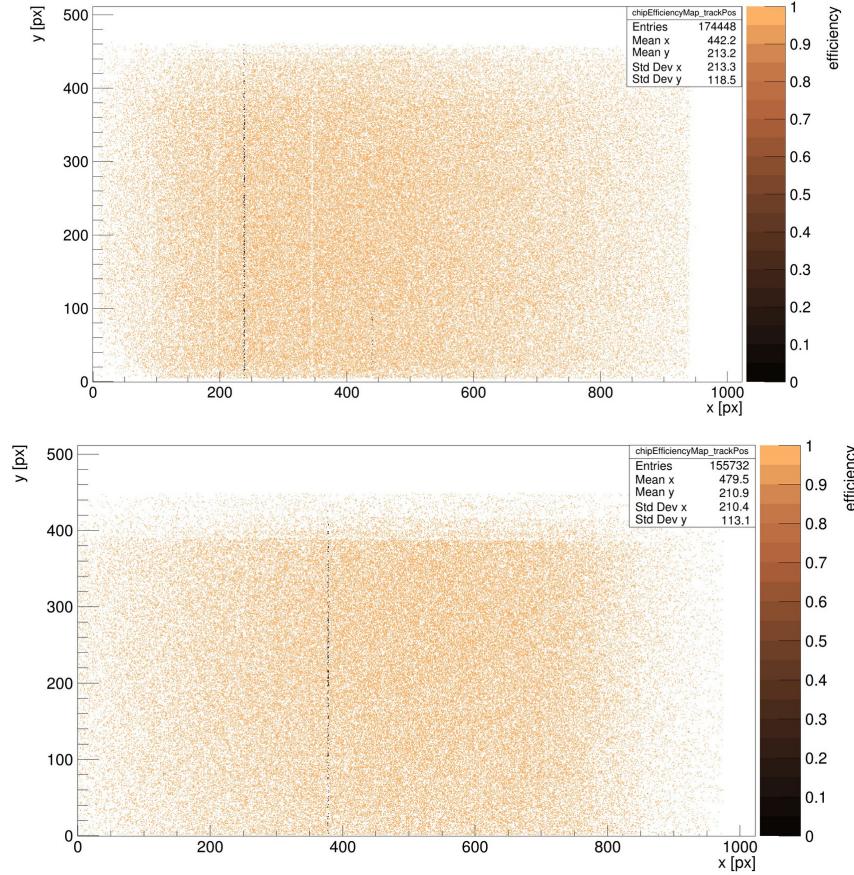

| 3.5.4 Analysis results . . . . .                                                  | 82         |

| 3.5.4.1 Test-beam June 2020 . . . . .                                             | 82         |

| 3.5.4.2 Test-beam July 2021 . . . . .                                             | 86         |

| <b>4 Wafer-scale sensor. The “super-ALPIDE” project</b>                           | <b>100</b> |

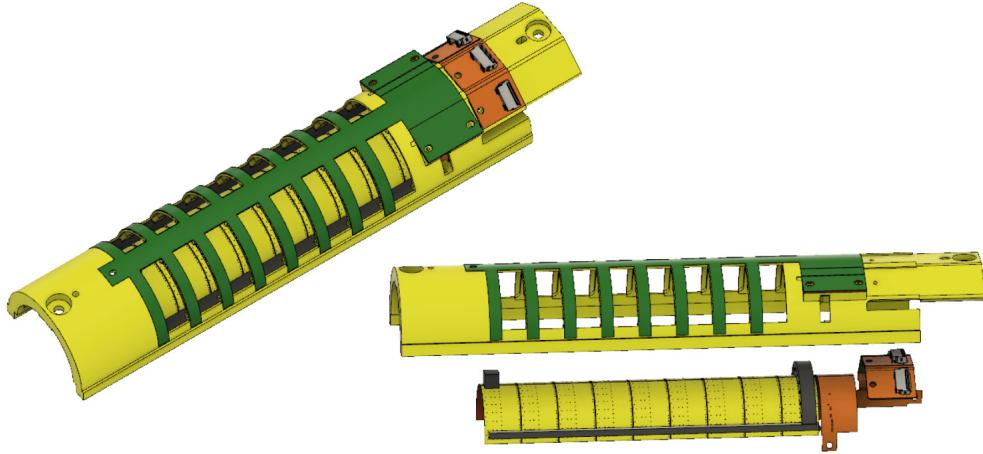

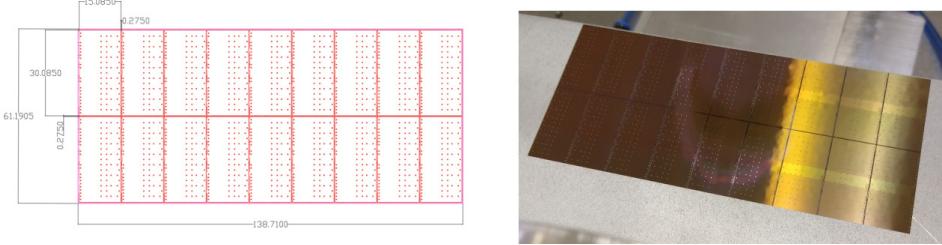

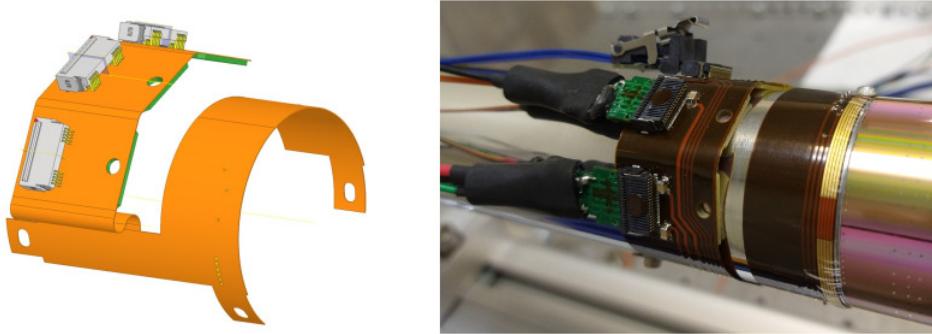

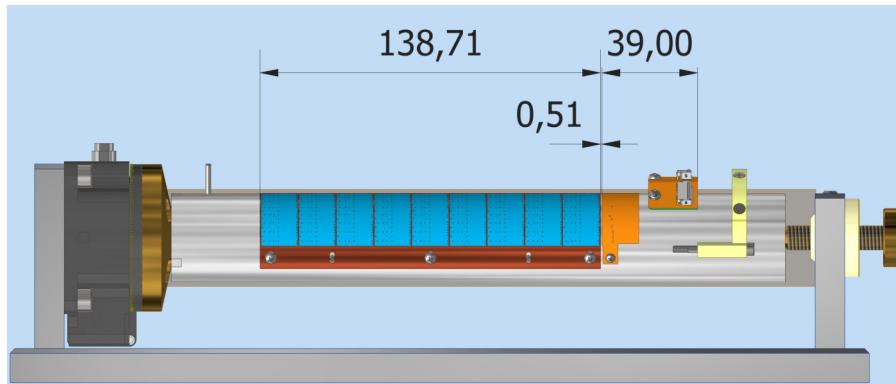

| 4.1 The super-ALPIDE design . . . . .                                             | 102        |

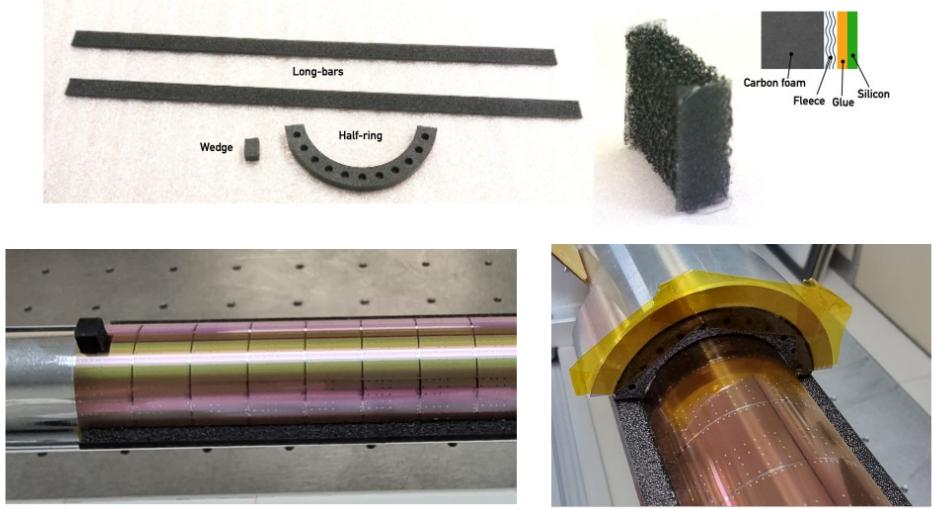

| 4.1.1 Support structures . . . . .                                                | 103        |

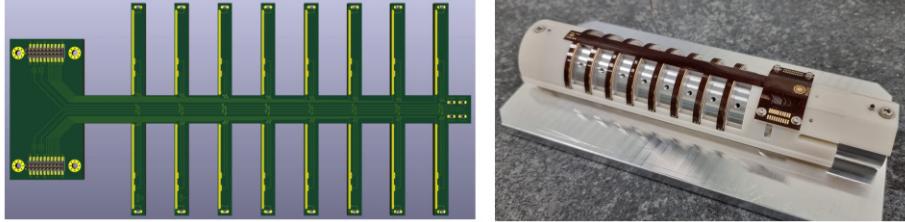

| 4.1.2 Flex Printed Circuits . . . . .                                             | 105        |

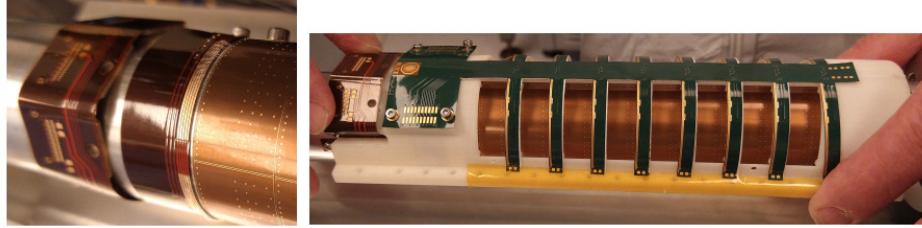

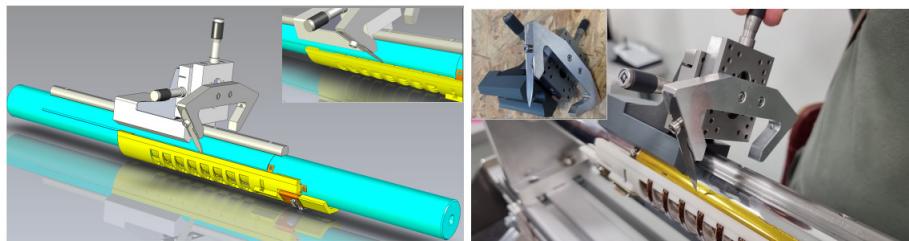

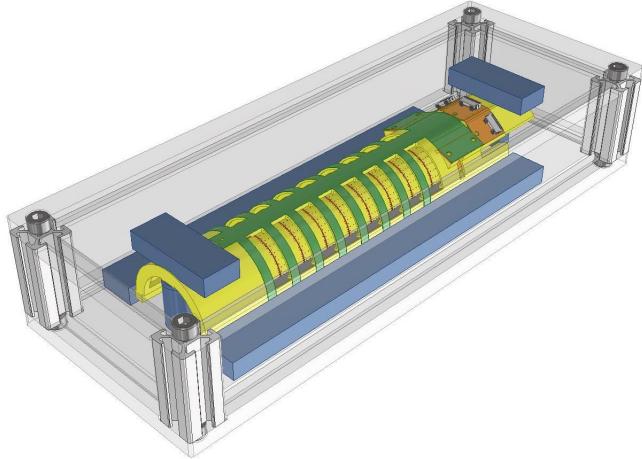

| 4.2 Detector assembly techniques . . . . .                                        | 107        |

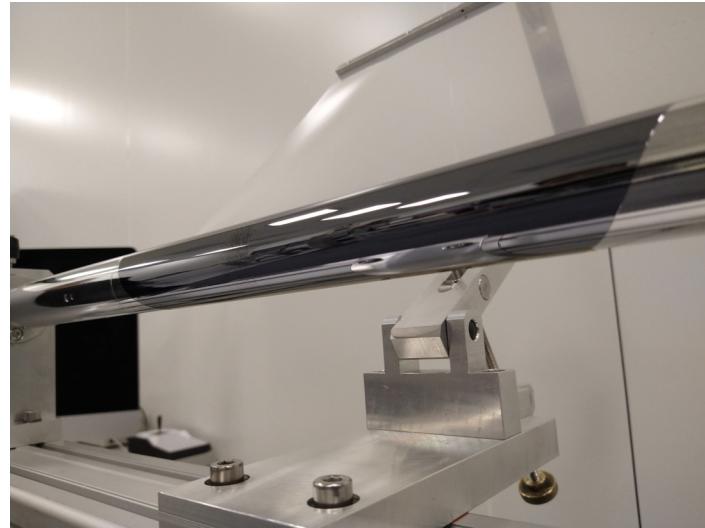

| 4.2.1 Silicon bending technique and tools . . . . .                               | 107        |

| 4.2.2 Edge-FPC to sensor interconnections . . . . .                               | 109        |

| 4.2.3 Support structures and exo-FPC gluing . . . . .                             | 110        |

| 4.2.4 Exo-FPC to sensor interconnections . . . . .                                | 112        |

| 4.2.5 Removal from the mandrel and transport box . . . . .                        | 114        |

| 4.3 Current status and plans . . . . .                                            | 115        |

| <b>5 Performance of first MAPS structures implemented in a 65 nm CMOS process</b> | <b>117</b> |

| 5.1 65 nm process technology . . . . .                                            | 118        |

| 5.1.1 General consequences of 65 nm CMOS at the circuit level                     | 119        |

| 5.1.2 Technology specifications . . . . .                                         | 121        |

| 5.2 Multi-Layer-Reticle 1 . . . . .                                               | 123        |

| 5.2.1 Test Structures of MLR1 . . . . .                                           | 124        |

| 5.3 Digital Pixel Test Structure (DPTS) . . . . .                                 | 125        |

| 5.4 CE-65 . . . . .                                                               | 127        |

| 5.5 Analogue pixel test structures (APTS) . . . . .                               | 130        |

| 5.5.1 Principle of operation . . . . .                                            | 130        |

| 5.5.2 Studies on the performance of APTS source follower version.135              |            |

|          |                                                                    |            |

|----------|--------------------------------------------------------------------|------------|

| 5.5.3    | Laboratory measurements of the APTS op-amp performance             | 136        |

| 5.5.3.1  | Test system                                                        | 136        |

| 5.5.3.2  | Chip response tests                                                | 138        |

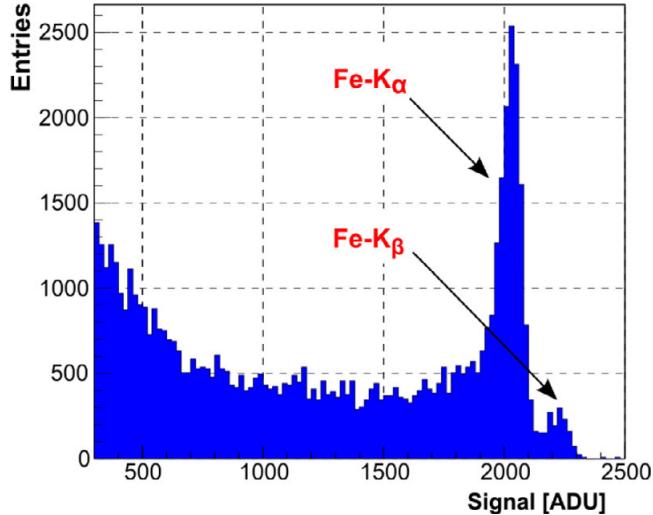

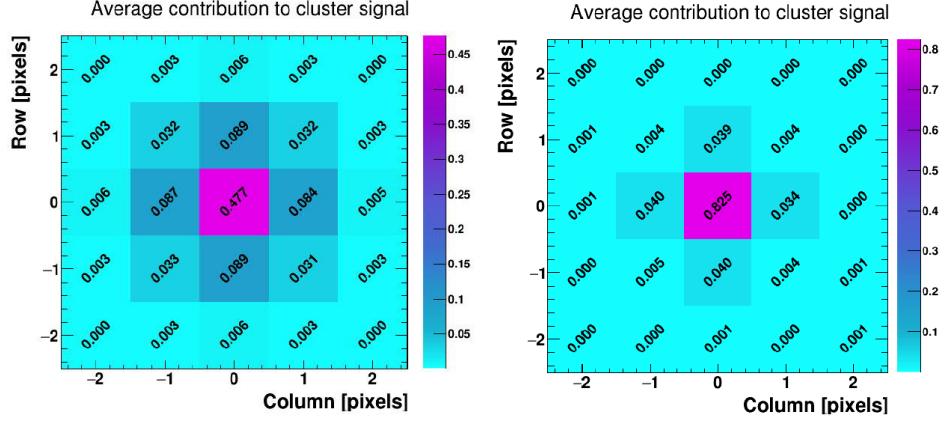

| 5.5.3.3  | Measurements with X-rays emitted by an $^{55}Fe$ source            | 146        |

| <b>A</b> | <b>Interaction of radiation with matter and Silicon properties</b> | <b>154</b> |

| A.1      | Energy loss for charged particles                                  | 154        |

| A.2      | Interaction of photons with matter                                 | 157        |

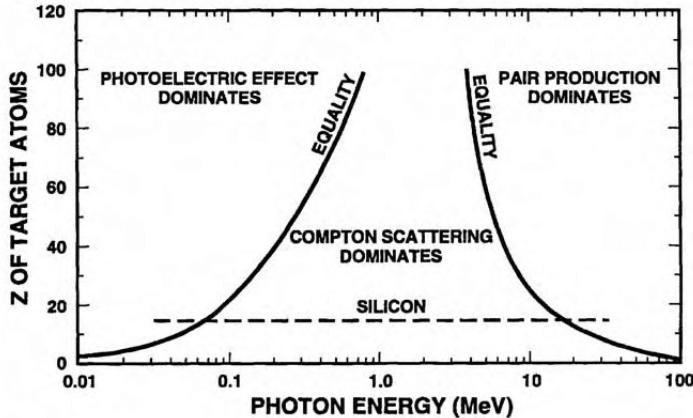

| A.2.1    | Photoelectric effect                                               | 158        |

| A.2.2    | Compton scattering                                                 | 158        |

| A.2.3    | Pair production                                                    | 159        |

| A.3      | Silicon properties                                                 | 159        |

| A.3.1    | Doping silicon                                                     | 160        |

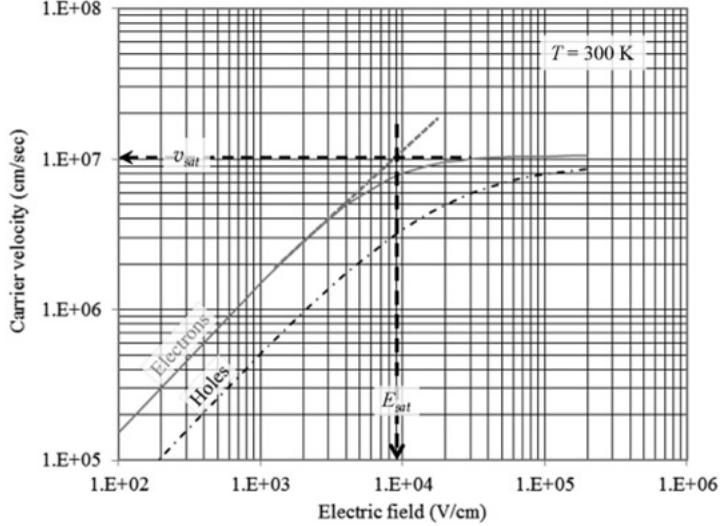

| A.3.2    | Drift                                                              | 161        |

| A.3.3    | Diffusion                                                          | 162        |

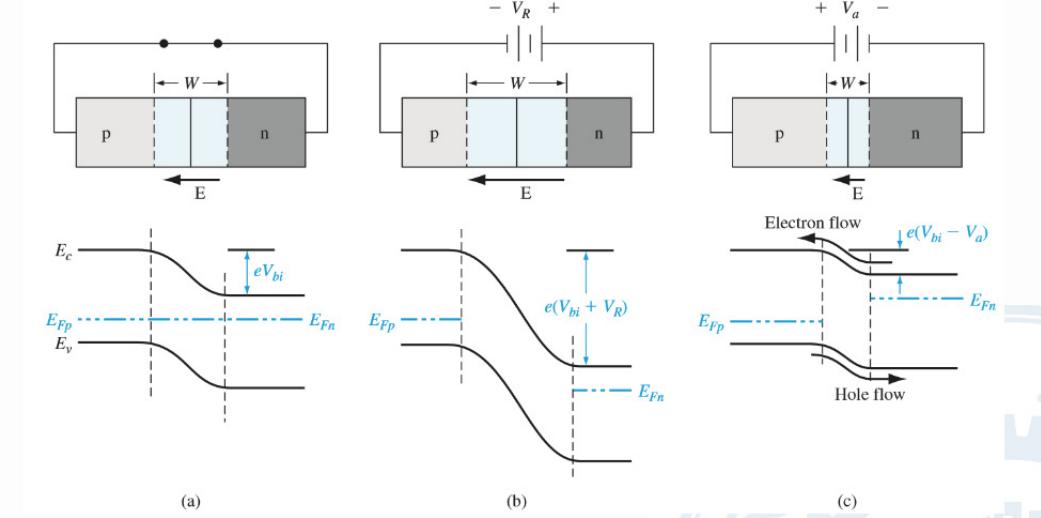

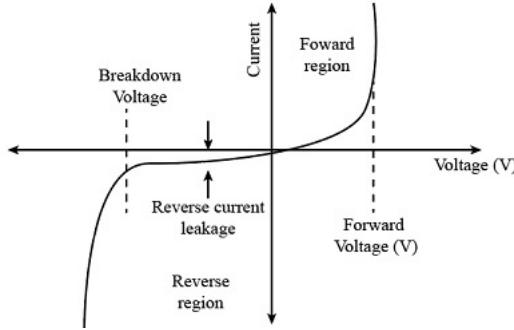

| A.3.4    | p-n junction                                                       | 163        |

| A.3.4.1  | Zero bias                                                          | 163        |

| A.3.4.2  | Forward bias                                                       | 163        |

| A.3.4.3  | Reverse bias                                                       | 164        |

| A.3.5    | Piezoresistivity                                                   | 165        |

# Chapter 1

## Introduction

ALICE (A large Ion Collider Experiment) at the Large Hadron Collider (LHC) at CERN [1], has been designed and optimized to address the physics of strongly interacting matter, in particular the properties of the quark-gluon plasma. It performs particle tracking and identification through several techniques and multiple detector technologies, allowing a comprehensive study of hadrons, electrons, muons and photons, produced in nucleus-nucleus collisions at high energies.

The innermost detector in the central barrel is the Inner Tracking System (ITS), which is placed around a beryllium beam pipe close to the Interaction Point (IP). The ITS has been replaced with an upgraded detector (ITS2) [2] during the second LHC Long Shutdown (LS2) in early 2021. The ITS2 consists of seven approximately-cylindrical detector layers based on CMOS Monolithic Active Pixel Sensors (MAPS) with the sensor matrix and readout integrated in a single chip, named ALPIDE (ALice PIxel DEtector), covering a  $10\ m^2$  area with about 12.5 billion pixels. The main objective was to increase the readout capabilities to allow the readout and recording of Pb–Pb minimum bias events at rates in excess of 50 kHz, the expected Pb–Pb interaction rate at the LHC after LS2.

The core of the detector is the ALPIDE chip, which is the result of an intensive R&D effort carried out in the last decade and has led to a quantum leap in the field of MAPS for single-particle detection, reaching unprecedented performance in terms of signal/noise ratio, spatial resolution, material budget and readout speed. There is still a lot that can be done to further improve MAPS for high-energy physics detectors by fully exploiting the rapid progress that this technology is making in the field of imaging for consumer applications. One of the features offered recently by CMOS imaging sensor technologies, called stitching, will allow developing a new generation of large size MAPS with an area of up to  $26\ cm \times 26\ cm$  using wafers that are  $300\ mm$  in diameter. Moreover, the reduction of the sensor thickness to values of about  $20\text{--}40\ \mu\text{m}$  will open the possibility of exploiting the flexible nature of silicon to implement large-area curved sensors. In this way, it will become possible to build a cylindrical

detector layer made only by silicon sensor, significantly reducing the material of the supporting structures.

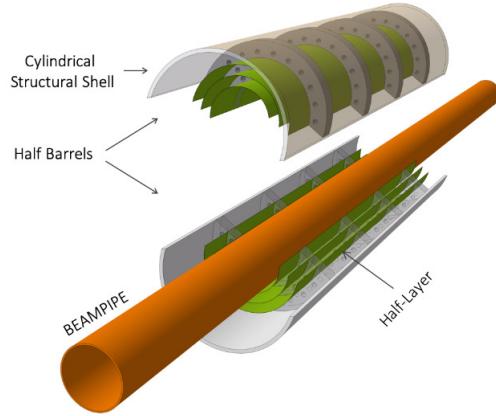

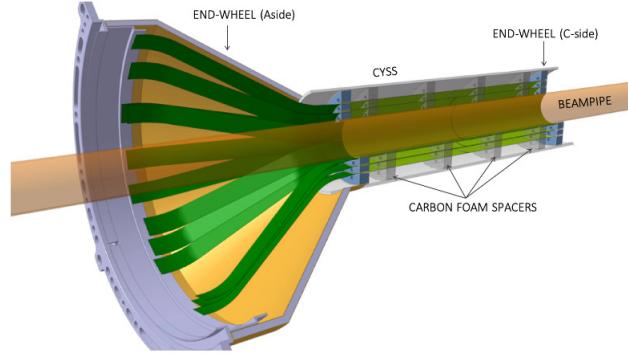

In that direction, an upgrade of the ITS2 is planned, aiming for a new detector installation during the third LHC Long Shutdown (LS3) between 2026 and 2028. The proposed upgrade, which is called ITS3, is based on a new vertex detector consisting of three truly-cylindrical layers composed by curved wafer-scale stitched silicon sensors, featuring a material budget of 0.05 %  $X_0$  per layer, with the first layer positioned at a radial distance from the interaction point of 18 mm. In the ongoing development of ITS3, the CMOS technology node was changed from 180 nm to 65 nm, which gives further advantages in integration density and power consumption. The new detector is intended to replace only the three innermost layers of the ITS2. With the first detection layer closer to the interaction point (from 23 mm to 18 mm) and a reduction of the material budget close to the interaction point by a factor of six, the new vertex detector will significantly improve the spatial precision and tracking efficiency at low  $p_T$ . The improvement of the vertexing performance and the reduction of material budget will have a dramatic impact on the measurement of charm and beauty hadrons at low transverse momentum as well as on the measurement of low-mass and low  $p_T$  dielectrons [3].

The content of this thesis is dedicated to: 1) the investigation of the ALPIDE features, specifically to verify that its performance does not change when it is positioned in flat and bent configuration; 2) the development of techniques dedicated to bend large size sensors and 3) the study on the feasibility of the newest MAPS prototypes fabricated in 65 nm CMOS process, to fulfill the mechanical and detection performance requirements for the future ITS3.

In this chapter an overview of the physics addressed by ALICE and a general description of the detector complex is given. The concept and improvement strategy for the next ALICE Inner Tracking System upgrade will be explained. In chapter 2, the properties of silicon detectors and the principles of operation of MAPS will be discussed. The ALPIDE chip used currently in the ALICE ITS2 is presented in chapter 3. The procedures developed to bend these devices down to the foreseen ITS3 layer radii will be reported and possible consequences of such bending will be investigated through the results of electrical tests in laboratory and studies on its performance in different test-beam experiments. In chapter 4, the “super-ALPIDE” project will be introduced by a description of the super-ALPIDE design, including the mechanical structures for readout and support. The techniques and tools employed to perform sensor bending, components assembly and wired interconnections will be depicted as well. Chapter 5 will be dedicated to give an overview of new sensor prototypes based on TPSCo 65 nm CMOS process, the first choice of the technology for the implementation of the wafer-scale sensor in the ITS3, focusing the attention on the results of an Analogue Pixel Test Structure characterization. Finally, the conclusions of the work presented in this thesis will be summarized in chapter 6.

## 1.1 Ultra-relativistic heavy-ion collisions

The collisions of ultra-relativistic heavy-ions allow us to study the strongly interacting matter under extreme conditions of high temperature and/or high nuclear matter density. The matter that fills the Universe today is done of hadrons, e.g. protons and neutrons that could further aggregate into nuclei, and the hadrons are made from quarks, the basic building blocks of matter, and held together by gluons, the carriers of the strong (nuclear) force. Under normal conditions, i.e. the ones of our Solar System in the Universe, the quarks are bound ('confined') into composite objects called baryons (bound states of three quarks, with the proton and the neutron being the most prominent examples) and mesons (bound states of a quark and anti-quark pair). Lattice computations of Quantum Chromodynamics (QCD), the theory of strong interactions, predict that at a sufficiently high energy density, there will be a transition from ordinary nuclear or hadronic matter to a plasma of free ('deconfined') quarks and gluons—a transition that took place in the early Universe a few microseconds ( $\sim 10 \mu\text{s}$ ) after the Big Bang and which might still play a role today in compact stellar objects. The characterization of this new high-temperature phase of matter, called the 'quark-gluon plasma' (QGP), requires a sufficiently large volume of hot matter and is therefore pursued in collisions of heavy nuclei at the highest possible energy. The coupling constant  $\alpha_S$  of the strong interaction depends on the momentum scale of the interaction. Processes corresponding to large momentum transfers between partons [4], where  $\alpha_S$  is small, can be investigated via a perturbative approach (pQCD). This involves an expansion to higher orders in  $\alpha_S$  [5], with only lower orders contributing significantly. For calculations concerning low-momentum transfer processes, the perturbative approach of QCD breaks down, as higher orders become dominant [6]. Such a non-perturbative regime, where the coupling constant becomes large, is of the utmost interest for the description of several essential features of the strong interaction. In particular, in this regime confinement<sup>1</sup> is observed [7]. This leads to the fact that quarks and gluons, the elementary particles carrying the "charge" of the strong interaction, known as colour, cannot be isolated, and therefore not directly observed. Only composite objects, hadrons, which do not possess a net colour charge, can be detected. Another key feature of strong interaction in the non-perturbative regime is the spontaneous breaking of chiral symmetry<sup>2</sup> [8, 9, 10].

The study of the QCD matter in its phase where quark and gluons are deconfined, i.e. not bound into hadrons, can be performed by producing a many body system of quarks and gluons, under the conditions of large energy density. Heating such a system, with zero (or very small) net baryon density, to a temperature exceeding 150–160 MeV (equivalent to more than  $10^{12}$  K), leads

---

<sup>1</sup>Quark confinement is the technical term describing the observation that quarks do not occur isolated in nature, but only in hadronic bound states as mesons and baryons.

<sup>2</sup>Chiral symmetry breaking expresses the fact that quarks confined in hadrons do not appear as nearly massless constituents but are endowed with a dynamically generated mass of several hundred MeV.

to the creation of the quark-gluon plasma (QGP). This is a state of matter where two of the basic features of low-temperature QCD, confinement and chiral symmetry breaking, are no longer present [11, 12, 13]. Below the ideal gas limit, the QGP manifests itself as a strongly interacting system of quarks and gluons. It behaves as an almost perfect liquid [14], with the possible presence during its evolution of bound states of quasi-particles (qq, gg, qg) [15].

### 1.1.1 The evolution of a heavy-ion collision

Collisions of heavy ions with ultra-relativistic energies are used to create the QGP in the laboratory. The evolution of a heavy-ion collision is commonly described in terms of a series of stages, which can in principle be factorised. They include: (i) an initial state, defined by the wave-functions of the projectiles, which are universal and independent of any specific scattering process; (ii) large- $Q^2$  interactions of partons drawn from the projectiles<sup>3</sup>; (iii) smaller- $Q^2$  interactions generating a pre-equilibrated parton gas; (iv) equilibration and expansion of the QGP; (v) hadron formation; (vi) chemical freeze-out of hadrons; (vii) hadronic interactions that subsequently freeze-out kinetically; (viii) free-streaming of stable particles to the detector.<sup>4</sup>

During a heavy ion collision the very large number of small- $Q^2$  interactions between the nucleons of the two colliding nuclei determine the overall energy density and entropy deposition in the initial state. Immediately after the collision, other smaller- $Q^2$  interactions occur in the context of a weakly coupled pre-equilibrium phase. This is followed by the creation of even softer partons in these processes, which enable the formation of a strongly coupled QGP phase. The hard processes from large- $Q^2$  interactions, which take place in the very early stage of the collisions, enable the creation of high momentum gluons and high momentum/mass quarks. As they have short wavelengths, they will interact with other quarks and gluons on a microscopic level, leading to energy loss effects (the energy being transferred to the medium), and therefore they offer information on the opaqueness of the QGP. The interactions of high-momentum partons with the QGP can be radiative as well as elastic. The amount of energy loss will depend on the colour charge, momentum, mass, type of process (inelastic or elastic), the distance traversed (path length) of the hard scattered parton, and is subject to stochastic processes. The heavy quarks produced via hard processes can also form quarkonia (bound heavy quark-antiquark states), with their production rate being suppressed with respect to scaled expectation from ordinary pp collisions, because the binding force between the quark and anti-quark is weakened (screened) by the presence of the colour charge of quarks and gluons. In addition, the parton fragmentation processes lead to jets, partonic showers that arise from these high energy partons, and that fragment into experimentally observable hadrons.

The evolution of the QGP for most processes involved in soft interactions after  $\sim 1 \text{ fm}/c$  can be depicted as follows. Since the mean free path of the

---

<sup>3</sup> $Q^2$  being the 4 momentum transfer squared

<sup>4</sup>For a more detailed conceptual description of heavy-ion collisions, see Ref.[16]

vast majority of the QGP constituents is expected to be much smaller than the size of the formed QGP (assuming these constituents are strongly coupled), multiple interactions drive the expansion. This expansion is highly influenced by the non-uniform energy distribution in the initial state as a function of space, which creates pressure gradients in the QGP stage. A radial flow occurs due to a greater pressure at the centre of the QGP compared to the outskirts, and this leads to a common velocity field outwards, which is superimposed to a thermal motion. The rate of the hydrodynamic expansion is influenced by the QGP's bulk viscosity, which is its resistance to volume growth. Anisotropic flow is the result of a directional dependence to these pressure gradients. This occurs due to spatial anisotropies in the initial state. These arise, e.g. if the collision zone is almond shaped ( $b^5 > 0$ , non central collisions). Such spatial anisotropies are converted to momentum anisotropies via the hydrodynamic response. This is influenced by the QGP's shear viscosity, which quantifies the resistance to fluid deformation.

Since the nuclei are charged, the movement of the incoming beams sets up a very large magnetic field (from the protons in the nuclei with relativistic energies), which can also have an influence on motion of quarks during the QGP stage. The Chiral Magnetic Effect (CME) leads to a splitting among positive and negative quarks in the QGP along the direction of the extremely large magnetic fields produced from the colliding ions. The decaying magnetic field will also induce an electric field, which can move the electrically charged quarks accordingly. The high-temperature QGP also produces thermal radiation, in the form of both photons and lepton-antilepton pairs. The electromagnetic radiation does not interact via the strong force in the QGP, and can therefore be used to gain information about the temperature from early to late times in the collision processes. In addition, strange quarks, which have masses below the deconfinement temperature (therefore the QGP temperature) can also be produced easily in the QGP stage, with the dominant mechanism coming from gluon interactions.

During the evolution, the parts of the QGP that cool below the transition temperature  $T_{pc}$  (“pseudocritical temperature”) will hadronise. The temperature and energy density of the medium will diminish with increasing distance from the collision centre and the transition to normal nuclear matter is a smooth cross-over. It is possible that hadronisation will happen at different times at different places in the phase-space.

The formation of hadrons from the QGP can proceed as follows. Hard partons in a jet will fragment and hadronise in the same manner as in elementary collisions. For partons at lower momenta, which are the majority, if they share a similar space and momenta as other partons, they can combine into hadrons via coalescence. Heavy (charm or beauty) quarks can also combine with heavy antiquarks, thus forming quarkonia and give rise to an additional production mechanism for closed heavy-flavour hadrons.

---

<sup>5</sup>Impact parameter: distance between the centers of two colliding nuclei at their closest approach during a collision.

After the hadrons materialise out of quarks and gluons, primarily pions ( $\pi$ ), kaons ( $K$ ) or protons ( $p$ ), the energy density may be large enough to allow for inelastic interactions, with a consequent evolution of their “chemical” composition, in terms of particle species. A loosely bound state such as the deuteron ( $d$ ) is particularly sensitive to such interactions, as it can be easily formed or destroyed. These interactions cease at the chemical freeze-out temperature  $T_{chem}$ , fixing the particle composition. Elastic interactions can still continue and halt at the kinetic freeze-out temperature  $T_{kin}$ , which is achieved at the time of  $\sim 15 \text{ fm}/c$ . At this point, the particle momenta are fixed. These particles travel towards the ALICE detector, where they will be measured  $\sim 10^{15} \text{ fm}/c$  after the initial collision.

### 1.1.2 Observables in heavy-ion collisions

There are various experimental probes used to investigate all phases of heavy-ion collisions: the initial state, the QGP phase, and the final hadronic phase. Each of these probes has varying sensitivity to each phase. To start, a fundamental quantity for many of these probes is the Lorentz-invariant differential yield of final state particles, given by:

$$E \frac{d^3N}{dp^3} = \frac{1}{2\pi p_T} \frac{d^2N}{dp_T dy} \quad (1.1)$$

which is the number density of the particle three-momentum scaled by the particle energy ( $E$ ). This will depend on the measured particle species in question, the transverse momentum,  $p_T$ , and rapidity,  $y$ . When the particle species is not known, pseudorapidity  $\eta$  is used instead<sup>6</sup>, and both are equivalent when the particle energy is much greater than its mass. Different  $p_T$  ranges will probe different physical processes, and for clarity in this review, one can define low- $p_T$  as  $p_T \lesssim 2 \text{ GeV}/c$ , intermediate- $p_T$  as  $2 \lesssim p_T \lesssim 8 \text{ GeV}/c$ , and high- $p_T$  as  $p_T \gtrsim 8 \text{ GeV}/c$ .

*Initial state:* For a given collision, the multiplicity can be determined, which is the number of charged hadrons produced in a broad momentum range. It plays a critical role in providing a selection on a range of impact parameters  $b$ . It will be large when  $b$  is small, which leads to large numbers of  $N_{part}$ <sup>7</sup> that will correspondingly produce large numbers of particles. Such small- $b$  collisions are referred to as central i.e. head-on, whereas collisions with large impact parameters and small numbers of  $N_{part}$  (and fewer produced particles) are referred to as peripheral. The multiplicity therefore provides an experimental handle on the centrality of a collision. Such a handle is extremely useful, as many of the system properties such as the energy density or lifetime depend upon the centrality. The multiplicity can also provide a measure of the initial state entropy.

---

<sup>6</sup>Defined as  $\eta = -\ln(\tan(\theta/2))$ ,  $\theta$  being the polar emission angle of the particle.

<sup>7</sup>Number of nucleons in the colliding nuclei that participate in an inelastic interaction (at least once)

Ultra peripheral collisions (UPCs) provide another handle on the initial state. These are heavy-ion collisions that typically have very large  $b$  values (greater than the nuclear diameter). The nuclei in these collisions are sufficiently separated such that short-range strong interactions are highly suppressed (and therefore no QGP formation). Measurements of the differential cross sections of light (e.g.  $\rho_0$ ) and heavy (e.g.  $J/\Psi$ ) vector mesons from these collisions are especially sensitive to the momentum distribution of partons (i.e. quarks and gluons) inside the nucleons. These distributions play a critical role for understanding the production rate of hard processes in the initial stages of heavy-ion collisions.

*QGP phase:* the amount of the hydrodynamic collective motion developed in the QGP phase can be explored using measurements sensitive to radial and anisotropic flow. Radial flow boosts higher mass produced hadrons to higher  $p_T$  in the low- $p_T$  region, and measurements of identified particle mean transverse momentum  $\langle p_T \rangle$  can therefore be used to extract information on the amount of radial flow that has developed. In order to investigate anisotropic flow, Eq. 1.1 can be expanded into the azimuthal angular dependence of the transverse momentum vector direction. The most widely used decomposition expresses the  $\varphi$  (the angular component of this vector) dependence of the produced particle density as a Fourier series as follows [17]:

$$\frac{dN}{d\varphi} \propto 1 + 2 \sum_{i=1}^{\infty} \nu_n \cos[n(\varphi - \Psi_n)] \quad (1.2)$$

The  $\nu_n$  terms, which can be determined experimentally, are referred to as anisotropic flow coefficients. They depend on the particle species,  $p_T$  and  $y$ . The term  $n$  corresponds to the order of anisotropic flow, and  $\Psi_n$  is the corresponding symmetry plane angle, which is the angular direction of anisotropic flow for the order  $n$  of interest. For the vast majority of produced hadrons, non-zero  $\nu_n$  coefficients arise mainly from the QGPs hydrodynamic response (with a relatively small contribution from the hadronic state).

Hard probes are produced in the earliest times of the collision. One of the ways they can be explored is by extracting their nuclear modification factor  $R_{AA}$ . This observable is constructed to be sensitive to changes of the dynamics of hard processes in heavy-ion collisions with respect to expectations from elementary pp collisions. Within a rapidity ( $y$ ) or pseudorapidity ( $\eta$ ) interval,  $R_{AA}$  as a function of transverse momentum is defined as follows:

$$R_{AA}(p_T) = \frac{1}{\langle T_{AA} \rangle} \frac{dN_{AA}(p_T)/dp_T}{d\sigma_{pp}(p_T)/dp_T} \quad (1.3)$$

The average nuclear overlap function  $\langle T_{AA} \rangle$  is obtained from the average number of  $N_{coll}$ <sup>8</sup> divided by the inelastic nucleon–nucleon cross section for the centrality range of interest. For hard processes, the yield  $N_{AA}$  in heavy-ion collisions is

---

<sup>8</sup>Total number of inelastic nucleon–nucleon collisions

expected to scale with the average nuclear overlap function  $\langle T_{AA} \rangle$  when compared to the production cross section  $\sigma_{pp}$  in pp collisions, in the absence of any QGP or initial state nuclear effects. That being the case, if  $R_{AA}(p_T) = 1$ , production from heavy-ion collisions can be considered as a superposition of nucleon–nucleon collisions, assuming the QGP is not formed in pp collisions. Any departure from unity reveals how these processes are modified in heavy-ion collisions. In particular,  $R_{AA}$  is expected to be below unity at high- $p_T$  for hadrons that originated from partons undergoing energy loss. Jet-finding algorithms can also be applied in heavy-ion collisions. The internal structure of jet showers is governed by quantum interference effects, resulting in the phenomenon of “angle-ordering”, whereby the highest  $p_T$  hadrons in the shower are on average most closely aligned with the nominal jet axis. A key parameter in jet measurements is the “jet radius” or “resolution parameter”  $R$ , which is effectively the size of the aperture through which the jet shower is viewed. The measured jet yields can be used to determine  $R_{AA}$ , while the jet radius dependence of the  $R_{AA}$  or jet substructure measurements provide information about the medium modifications of the quark and gluon radiation patterns. The heavy-ion jets can be compared to jets in pp collisions, where no such modifications are expected.

A specific class of hard probes, heavy quarks, gives access to several QGP features that can be accessed via differential measurements of  $R_{AA}$  and  $\nu_n$ . A key difference is that the corresponding hadrons are associated with early-stage probes across their entire  $p_T$  range.  $D$  mesons, which carry the vast majority of the charm quarks produced, can be investigated differentially as function of  $p_T$  via measurements of  $\nu_n$  and  $R_{AA}$ . Measurements of  $\nu_n$  at low- $p_T$  are sensitive to degree to which heavy quarks take part in the collective expansion of the QGP and approach thermalisation. Measurements of  $R_{AA}$  at high- $p_T$  provide insights on the energy loss processes of heavy quarks, which may be smaller than for light quarks or gluons, due to different Casimir coupling coefficient (with respect to gluons) and the dead cone effect (with respect to light partons) [18]. Measurements of quarkonia (e.g.  $J/\Psi$  or  $\Upsilon(1S)$ )  $R_{AA}$  and  $\nu_n$  are also carried out as a function of  $p_T$ . The  $R_{AA}$  studies allow the investigation of the aforementioned suppression and regeneration processes, with the latter expected to be dominant in the low- $p_T$  region due to larger heavy quark multiplicity in that kinematic range. Anisotropic flow measurements give complementary information to those from open heavy flavours, with the observed effect not involving the contribution of the flow of light quarks.

Electroweak probes e.g. photons, leptons or  $Z/W$  bosons provide another class of measurements. If they arise from hard processes in the initial stages, measurements of  $R_{AA}$  at high- $p_T$  are expected to be unity, and any deviations from this reveal the influences of non-QGP processes that affect this measurement (these can be studied using other means that will be described in the next section). On the other hand, measurements of direct photon (i.e. not from hadron decays) spectra at low- $p_T$  are expected to arise mainly from the softer processes in the QGP involving charged quarks, and their slope can be related to the temperature when they are created. Direct photons can also be produced from hadronic interactions, so that the observed yield is a convolution of their

emission along the whole collision history. Since photons are produced in an expanding QGP medium, they will be blue-shifted, which has to be taken into account regarding their connection to the temperature of the QGP.

*Hadronic phase:* a variety of methods are available to investigate the hadronic phase of the heavy-ion collisions. Measurements of identified hadron spectra and  $\nu_n$  at intermediate- $p_T$  are sensitive to the coalescence of quarks upon hadronisation from the QGP phase, which will compete with hadronisation from the well known fragmentation processes observed in QCD interactions. Such a coalescence mechanism enhances baryon production rates and  $\nu_n$  values compared to mesons in this  $p_T$  range. The chemical freeze-out temperature  $T_{chem}$  can be explored by measuring the total yields of specific particles ( $dN/dy$ ) via an integration over  $p_T$  in Eq. 1.1 for hadrons that do not decay quickly via the strong or electromagnetic interactions (e.g. protons, kaons, charged pions, hyperons etc.). Measurements of the production of strongly decaying resonances can offer insight into the duration of the hadronic phase. Their decay products for temperatures both above and below  $T_{chem}$  are subject to elastic scattering. If these effects are strong enough, they will lead to a depletion in the resonance yields, as the kinematics of the particles resulting from a resonance decay are altered in such a way that the resonance cannot be reconstructed anymore. On the other hand, regeneration processes from hadron–hadron interactions may form resonances during this phase. Final state hadron–hadron interactions can also be studied via the pair-wise femtoscopic correlation function, which can be extracted experimentally as:

$$C(k^*) = \frac{N_{pairs}(\text{same event})}{N_{pairs}(\text{background})} \quad (1.4)$$

where  $k^*$  is the invariant momentum difference between the pairs. The numerator is extracted from pairs produced in the same collision, and the denominator is obtained from a background hypothesis that assumes no correlated pairs, and is normalised such that  $C(k^*) = 1$  in the absence of same-event correlations. Femtoscopic correlations arise from quantum correlations which are sensitive to the size of the system at freeze-out, or final state hadron–hadron interactions, both of which predominately occur at low  $k^*$ .

## 1.2 A Large Ion Collider Experiment

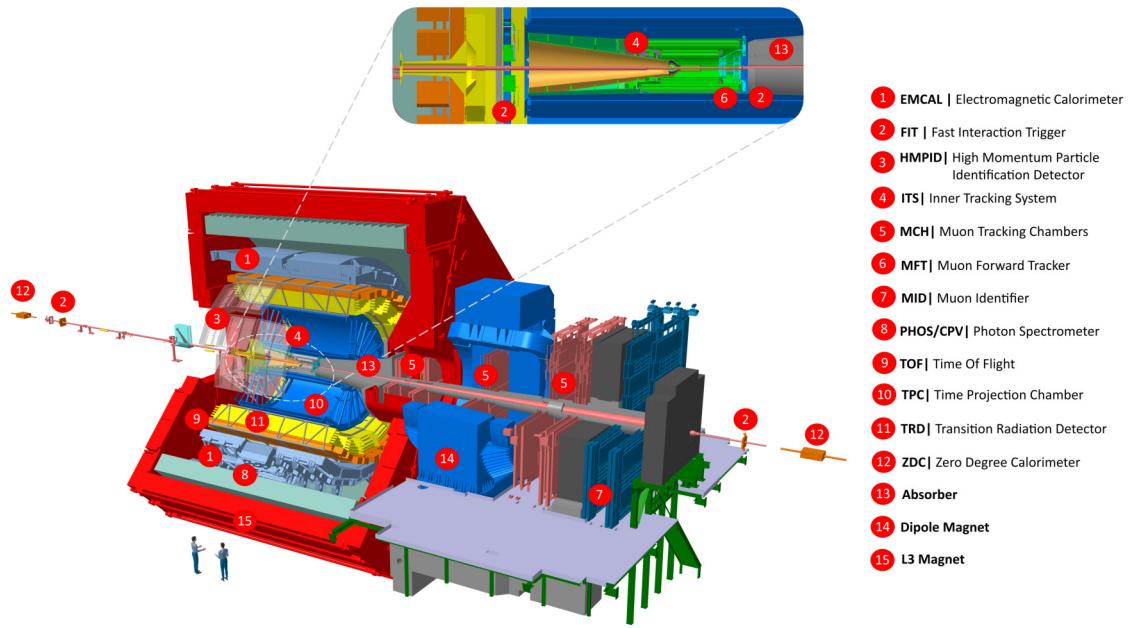

The ALICE detector stands 16  $m$  tall, 16  $m$  wide and 26  $m$  long, and weighs approximately 10 000 tonnes. It was designed and upgraded over almost three decades by a collaboration that currently includes over 2005 scientists and engineers from more than 171 institutes in 40 different countries. The experiment consists of 12 different detection systems, each with its own specific technology choice and design constraints. A schematic view of ALICE after the Long Shutdown 2 (2019 – 2021), is shown in figure 1.1.

Figure 1.1: ALICE 2 detector systems [19].

It consists of a central part, which measures hadrons, electrons and photons, and a forward single arm spectrometer that focuses on muon detection. The central ‘barrel’ part covers a region spanning from  $45^\circ$  to  $135^\circ$  (angle from the beam direction) and is located inside a huge solenoid magnet, which maximum field at the nominal power of 4 MW reaches 0.5 T. The central barrel contains a set of tracking detectors, which record the momentum of the charged particles by measuring their curved path inside the magnetic field. These particles are then identified according to mass and particle type by a set of PID detectors, followed by two types of electromagnetic calorimeters for photon and jet measurements. The forward muon arm ( $2^\circ$  –  $9^\circ$ ) consists of a complex arrangement of absorbers, a large dipole magnet and 14 planes of tracking and triggering chambers.

### 1.2.1 Tracking detectors

An ensemble of cylindrical detectors measures the passage of each particle carrying an electric charge at many points, so that its trajectory is precisely known.

The ALICE tracking detectors are embedded in a solenoidal magnetic field, produced by a huge red magnet, bending the trajectories of the particles; from the particles curvature we can find their momentum. The ITS provides the spatial precision in the tracking such that particles generated by the decay of other particles with a very short life time can be identified by seeing that they do not originate from the point where the interaction has taken place (the “primary vertex” of the event) but rather from a point at a distance of as small as a tenth of a millimeter.

### 1.2.1.1 Inner Tracking System (ITS)

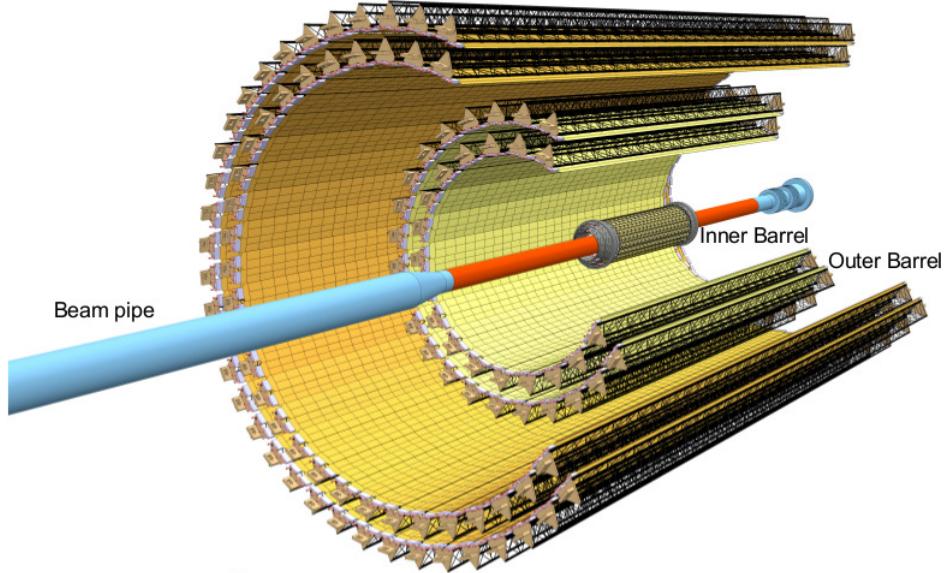

The current ITS2 consists of seven cylindrical, concentric detector layers (see figure 1.2) of  $50\text{-}\mu\text{m}$  thick CMOS monolithic active pixel sensors (MAPS), with a pixel pitch of about  $30 \times 30 \text{ }\mu\text{m}^2$  for a total of 12.5 Giga pixels covering an active surface of about  $10 \text{ m}^2$ . A key feature of the new ITS is the very low mass of the three innermost layers, which have a material budget of 0.3%  $X_0$  per layer. It is also able to handle the hit densities resulting from Pb–Pb collisions at 50 kHz interaction rate. The radii of the inner, middle and outer layers range from 2 to 43 cm and their lengths are 30 cm, 90 cm and 150 cm, respectively.

Figure 1.2: Layout of the current ALICE Inner Tracking System ITS2, showing seven cylindrical, concentric layers of monolithic active pixel sensors: the Inner Barrel, surrounded by the middle and outer layers of the Outer Barrel [2].

### 1.2.1.2 Time Projection Chamber (TPC)

In the radial direction, the ITS is followed by the Time Projection Chamber (TPC), the main tracking detector of the central barrel, extending from  $0.85\text{ m}$  to  $2.5\text{ m}$  in radius over a length of  $5\text{ m}$ . The ALICE TPC is a  $90\text{ m}^3$  cylinder filled with gas and divided in two drift regions by the central electrode located at its axial centre. The field cage secures a uniform electric field along the  $z$ -axis. Charged particles traversing the TPC volume ionise the gas along their path, liberating electrons that drift towards the end plates of the cylinder. The necessary signal amplification is provided by Gas Electron Multiplier (GEM) detectors. There is a particle identification capability in the TPC, obtained from the measurement of the specific energy loss in the TPC gas.

## 1.2.2 Particle identification detectors

### 1.2.2.1 Transition Radiation Detector (TRD)

The Transition Radiation Detector (TRD) extends from  $2.8\text{ m}$  to  $3.5\text{ m}$  in radius and provides additional space points for tracking, which are also used to determine the size of the distortions due to space charge effects in the TPC, as well as  $dE/dx$  measurements for particle identification, and the detection of transition radiation for electron identification at  $p_T > 3\text{ GeV}/c$ .

### 1.2.2.2 Time of Flight (TOF)

The subsequent Time-of-Flight detector (TOF) allows the identification of hadrons over a wide momentum range and electrons at low momentum. It measures the flight time of particles from the collision point out to the detector with precision of  $80\text{ ps}$ ; together with the momentum, this time determines the mass. It covers the central barrel over an area of  $140\text{ m}^2$  with 150 000 individual cells at a radius close to  $4\text{ m}$ .

### 1.2.2.3 High Momentum Particle Identification Detector (HMPID)

The High Momentum Particle Identification Detector (HMPID) is a ring-imaging Cherenkov detector that adds hadron (pions, kaons and protons) identification capabilities at large transverse momenta over a limited acceptance. It has two main parts: a radiator medium, where the Cherenkov light is produced and a photon detector used to generate images of the Cherenkov light (rings). It has a surface of about  $12\text{ m}^2$  and consists on 7 proximity focusing Ring Imaging Cherenkov (RICH) counters of  $1.4\text{ m} \times 1.3\text{ m}$  each. Cherenkov photons, emitted when a fast charged particle traverses the  $15\text{ mm}$  thick layer of liquid  $C_6F_{14}$  (perfluorohexane), are detected by a photon counter, which exploits the technology of a thin layer of CsI deposited onto the pad cathode of a multi-wire proportional chamber (MWPC).

### 1.2.3 Calorimeters

A large part of the acceptance in the central barrel is covered by electromagnetic calorimeters. The ElectroMagnetic Calorimeter (EMCal) is realised as Pb-scintillator sampling calorimeters with avalanche photon detector (APD) readout, whereas the PHoton Spectrometer (PHOS) uses  $PbWO_4$  crystals with APD readout.

### 1.2.4 Muon detectors

The muon detectors cover the forward pseudorapidity range  $-4.0 < \eta < -2.5$  and use a system of absorbers to remove hadrons and identify muons. The background of secondary muons from pion and kaon decays in the muon system is small at high  $p_T$ , thanks to the so-called ‘muon plug’ absorber, which is placed at  $z = 90\text{ cm}$  from the interaction point. The main muon detector stations use multiwire proportional chambers (muon tracking chambers, MCH), and resistive plate chambers (muon identifier, MID), both of which were equipped with new front-end electronics during the LHC LS2. The Muon Forward Tracker (MFT) has been added after the Run 2 and consists of tracking stations with the ALPIDE silicon pixel sensors that are installed in front of the muon plug to improve mass resolution and pointing resolution for the detection of secondary charmonia and muons from B-meson decays.

### 1.2.5 Forward and trigger detectors

A set of forward detectors form a Fast Interaction Trigger (FIT), which is used for triggering, event selection and determination of the collision time. The FIT system consists of two arrays of fast Cherenkov radiators placed on both sides of the interaction point (FT0), complemented with 3 sets of scintillator detectors. The interaction trigger is provided by the FT0 together with a large azimuthally segmented scintillator detector placed on the opposite side of the muon detectors, which is also used to determine the reaction-plane orientation in Pb–Pb collisions. Two additional scintillator detectors, FDD, are placed on opposite sides of the interaction point at large distances to cover  $4.7 < \eta < 6.3$  and  $-6.9 < \eta < -4.9$  to select diffractive and ultra-peripheral collisions with rapidity gaps. The Zero-Degree Calorimeters (ZDC) are installed at  $\approx 100\text{ m}$  on either side of the interaction point to help determine the centrality and event plane orientation. The readout electronics of the ZDC were upgraded to increase the readout rate to match the rest of the system.

### 1.2.6 ALICE upgrade prospect

In spite of the huge progress made so far by ALICE in the last years (for a detailed assessment of the main findings of the ALICE experiment in Run 1 and Run 2 see [20] and [21]), several fundamental questions still remain open and need to be addressed experimentally. For instance, low- $p_T$  collective flow measurements are modeled successfully in terms of QCD hydrodynamics operating

at sub-fermi time scales, and the generic suppression of high- $p_T$  hadron yields can be accounted for by jet quenching models in terms of medium-modified parton showers. However, the microscopic dynamics that gives rise to the fast hydrodynamisation is untested experimentally, and so is the question of how efficiently partons lose momentum, hydrodynamise, and thermalise in dense QCD matter. Also, the dynamical mechanisms that lead to a characteristic, event-multiplicity dependent hadrochemical composition remain unknown, and our understanding of heavy-flavour hadronisation, in particular in the baryon sector, is still incomplete.

ALICE in particular, aims, in Runs 3 and 4, to improve substantially the precision of heavy flavour production measurements and to measure for the first time the thermal emission of dileptons in heavy ion collisions at the LHC, both to determine the temperature in the early phase of the collisions and to study the mechanisms for chiral symmetry restoration in the regime of vanishing baryon density. Improved precision at high mass as well as larger statistics are also required to perform differential measurements of dielectron production and elliptic flow to trace the evolution of the emission of electromagnetic radiation with the temperature and to disentangle emission from the QGP and from the hadronic phase.

Existing measurements at the LHC have already shown that charm quarks lose energy as they propagate through the QGP and that charm baryon production is enhanced in central Pb-Pb collisions, suggesting that new hadronisation mechanisms, for example via combination of independently produced quarks, are at work, and that charm quarks may largely equilibrate in the plasma. The improved track impact-parameter resolution and readout rate of the upgraded apparatus will allow one to measure baryon to meson ratios in the charm sector, as well as dual flavour mesons, like the  $D_s$ , with sufficient precision to disentangle charm transport and hadronisation effects and to constrain the transport coefficients of charm quarks in the QGP.

With the next Inner Tracking System upgrade, referred to as ITS3, ALICE will perform first measurements of fully reconstructed beauty hadron decays. Beauty quarks are not expected to reach full thermal equilibrium, thus providing not only an important qualitative test of heavy quark transport, but also of hadronisation away from equilibrium. The study of QGP hadronisation via the combination of uncorrelated quarks is key to understand the dynamics connecting hadronisation and collective flow.

An important upgrade to ALICE to be realized during LS3 for data-taking in 2026–2028 at the LHC, is the installation of the forward electromagnetic and hadronic calorimeter (FoCal). The FoCal is a highly granular Si+W electromagnetic calorimeter combined with a conventional sampling hadronic calorimeter covering pseudorapidities of  $3.4 < \eta < 5.8$ . It will significantly enhance the scope of ALICE for inclusive and correlation measurements with mesons, photons, and jets to explore the dynamics of hadronic matter at small  $x$  (momentum fraction) down to about  $10^{-6}$ .

The ALICE target integrated luminosities for the future physics program are listed in the following. For Pb–Pb collisions at  $\sqrt{s_{NN}} = 5.3 \text{ TeV}$ :  $L_{int} =$

$13 \text{ nb}^{-1}$ ; p-Pb collisions at  $\sqrt{s_{NN}} = 8.5 \text{ TeV}$ :  $L_{int} \approx 0.5 \text{ pb}^{-1}$ ; pp reference samples at the same centre-of-mass energies as the Pb-Pb and p-Pb samples:  $L_{int} \approx 6 \text{ pb}^{-1}$  for each energy; pp collisions at top LHC energy  $\sqrt{s} = 13.6 \text{ TeV}$ :  $L_{int} = 200 \text{ pb}^{-1}$ ;  $^{16}\text{O} - {^{16}\text{O}}$  collisions at  $\sqrt{s_{NN}} = 6.8 \text{ TeV}$  (few days in Run 3 with  $L_{int} \approx 0.5 - 1 \text{ nb}^{-1}$ ).

The detector design was guided considering a series of test-bench observables to be measured in order to address the physics goals. These required charged particle tracking providing a transverse momentum resolution in the order of 1 – 2 % with excellent efficiency over a large pseudorapidity range. Besides the gain in the size of the statistical sample, an extended rapidity coverage is crucial for the low  $p_T$  reach as well as studies of long-range correlations and for studies of the rapidity dependence of the yields. In addition, ultimate track impact-parameter resolution is required ( $\sim 2 \mu\text{m}$  at  $p_T = 1 \text{ GeV}/c$ ). This is essentially for an effective reconstruction of secondary vertices and decay chains, e.g. of heavy-flavoured hadrons. It is also a key ingredient for the rejection of heavy-flavour background for the dielectron measurements.

For what concerns the particle identification, electrons must be identified in a  $p_T$  range from  $\sim 50 \text{ MeV}/c$  up to about  $\sim 2 \text{ GeV}/c$ . For muons the challenge is to achieve an efficient identification starting from  $p_T \sim 1.5 \text{ GeV}/c$  at  $\eta = 0$ . The combination of electrons and muons at low and high transverse momenta, respectively, ensures access to leptonic channels over a wide  $p_T$  range. Hadron identification must span the range up to a few  $\text{GeV}/c$  to identify the products of heavy flavour decays, while retaining high efficiency. For the detection of photons, the requirements are different for different measurements. While the measurement of photon-jet correlations calls for a large acceptance, the reconstruction of states such as the  $\chi_c$  relies in addition on the measurement of photons at low energies. The detection and energy determination of very low- $p_T$  ( $\geq 1 \text{ MeV}/c$ ) photons calls for a specially optimised detector in the forward direction to exploit the longitudinal boost.

## 1.3 Upgraded Inner Tracking System (ITS3)

### 1.3.1 Physics performance

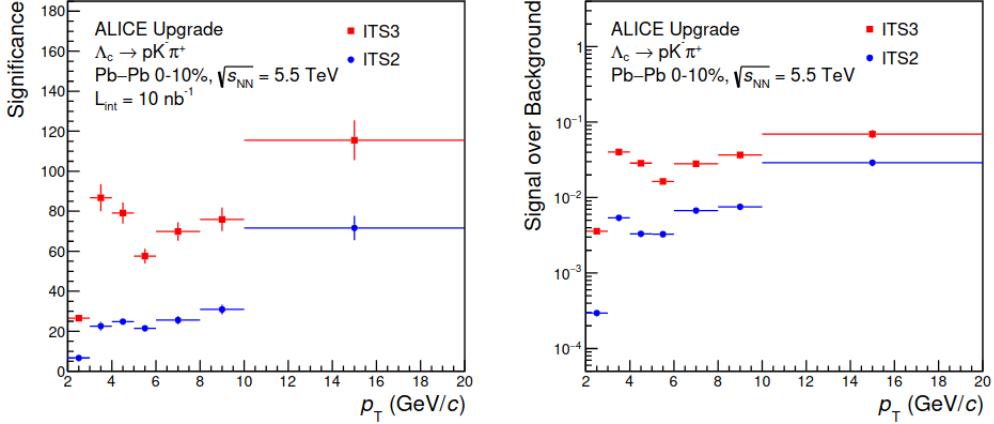

As stated in the previous section, an improved vertex resolution will be beneficial for the measurement at low transverse momentum of key observables studied by ALICE. A refined impact parameter resolution and a reduced material budget of the ITS layout will significantly extend the physics capability for the study of heavy-flavour production, notably in the baryon sector, and for the study of low-mass dielectrons, two of the main objectives of the ALICE physics programme in the next decade. In this section the expected improvements of the performance will be outlined considering the case of  $\Lambda_c$  and thermal dielectrons production.

## Measurement of $\Lambda_c$ production

The measurement of the production yields and flow of charm and beauty baryons is of particular interest to study the thermalization and the mechanism of hadronization of c and b quarks in the QCD medium. In particular, if in Pb–Pb collisions heavy quarks can thermalize and hadronize via recombination with light-flavour quarks present inside the quark-gluon plasma (QGP) or at the QGP phase boundary, the production of charm and beauty baryons is expected to be significantly enhanced (compared to measurements in pp collisions) in the low and intermediate momentum region, say below  $10 \text{ GeV}/c$ . An enhancement of the baryon-to-meson ratio was measured in the light-flavour sector ( $p/\pi$  [22] and  $\Lambda/K_S^0$  [23]) for  $1 < p_T < 6 \text{ GeV}/c$  and can be described in terms of light-quark recombination and hadron-mass-dependent radial collective flow [22, 23].

A precise measurement in the charm sector would provide crucial information on the charm quark thermalisation and hadronisation in the Quark-Gluon Plasma, as well as on the roles of recombination and radial flow. In addition, such measurements can provide further evidence for the deconfinement of charm quarks in the fireball, see, e.g., [24, 25, 26]. First measurements in Pb–Pb collisions at  $\sqrt{s_{NN}} = 5.02 \text{ TeV}$  [27, 28] and preliminary measurements in Au–Au collisions at  $\sqrt{s_{NN}} = 200 \text{ GeV}$  [29] indicate a possible enhancement of the ratio  $\Lambda_c/D_0$  for  $p_T < 10 \text{ GeV}/c$  and no significant modification for higher  $p_T$ . These measurements have limited statistical precision and prevent a clear conclusion.

From the experimental point of view, the main issue for the measurement of charmed baryons is their rather short lifetime: the  $c\tau$  of the  $\Lambda_c$  is about  $59 \mu\text{m}$ , a factor of 2 smaller than that of the  $D_0$  meson. In addition, unlike the  $D_0$ , the  $\Lambda_c$  does not have two-prong decays into charged hadrons. The most convenient decay channels are  $\Lambda_c^+ \rightarrow pK^-\pi^+$ , which has a large three-prong combinatorial background, and  $\Lambda_c^+ \rightarrow pK_s^0$ , for which a precise determination of the decay vertex is not possible because of the long decay length of the neutral kaon. The former is the benchmark channel considered for the ITS3 upgrade. The measurement requires very precise tracking and impact parameter resolution, because the decay tracks are typically displaced from the main interaction vertex by only a few hundreds of microns. This makes the measurement of the  $\Lambda_c$  a powerful benchmark to generally assess the improvement provided by the ITS3 in terms of physics performance for heavy-flavour physics.

A comparison of the performance between ITS2 and ITS3 is shown in figure 1.3 for the statistical significance  $S/\sqrt{S+B}$  (left) and signal-to-background  $S/B$  ratio (right).  $S$  and  $B$  are the signal and background yields in an invariant-mass range of  $\pm 3\sigma$  around the  $\Lambda_c$  nominal rest mass, where  $\sigma$  is the invariant-mass resolution (about 5 to  $15 \text{ MeV}/c^2$  depending on  $p_T$ ). The statistical significance is given for 8 billion events in the 0 – 10 % centrality class, corresponding to  $L_{\text{int}} = 10 \text{ nb}^{-1}$ . An improvement is found with ITS3 of a factor about four for the significance and ten for the  $S/B$  ratio, because the better track impact-parameter resolutions allows for a larger rejection of the combinatorial background and a larger efficiency for the signal selection.

Figure 1.3:  $\Lambda_c^+ \rightarrow pK^-\pi^+$  in central Pb–Pb collisions at  $\sqrt{s_{NN}} = 5.5$  TeV ( $L_{int} = 10\text{nb}^{-1}$ ): statistical significance (left) and  $S/B$  ratio (right) as a function of  $p_T$  [3].

### Measurement of Thermal Dielectrons

Electromagnetic radiation produced by the high-temperature system formed in heavy-ion collisions can be detected using real direct photons with very low momentum or virtual photons yielding low invariant-mass dilepton pairs ( $M_{ee}$ ). In this section we discuss the measurement using dielectron pairs in the ALICE central barrel, which requires acceptance for  $e^+e^-$  pairs at invariant masses and transverse momenta as low as possible. This implies electron detection down to  $p_T < 100$  MeV/c. Since the production rate of thermal dileptons is low, very good electron identification is mandatory to suppress the combinatorial background arising when one of the particles of the pair is a hadron misidentified as an electron. Moreover, electrons from  $\pi^0$  Dalitz decays and photon conversions (mainly from  $\pi^0 \rightarrow \gamma\gamma$ ) produce a large combinatorial background. This calls for low material budget specially of the innermost detection layer and for the capability to reconstruct  $e^+e^-$  pairs from photon conversions and Dalitz decays for rejection before the definition of dielectron candidates.

The proposed ITS3 upgrade will enhance the performance of the thermal dielectrons measurement with respect to the ITS2 because:

- The reduction of the material budget of the beampipe by 30% and of the first detection layer by a factor of about six determines a reduction by a factor of about three of the number of electrons from photon conversions before the first track measurement point.

- The enhanced low- $p_T$  tracking capability of the ITS3 substantially improves the reconstruction efficiency of photon conversions in which one of

the particles of the dielectron pair often has very low momentum. This reduces the combinatorial background.

- The improved track impact-parameter resolution of the ITS3 enables efficient tagging of electrons from semi-leptonic charm decays, which form a substantial physical background to the pair-yield and dominate the invariant-mass spectrum for  $M_{ee} > 1.1 \text{ GeV}/c^2$ .

### 1.3.2 Tracking performance

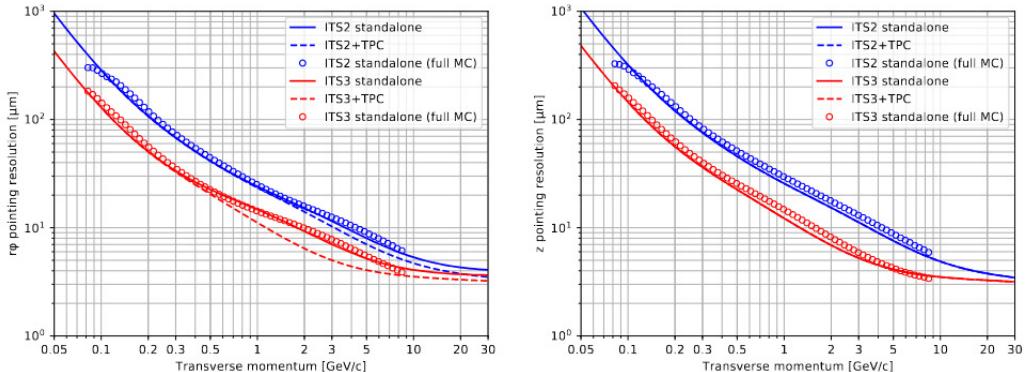

An important measure of the achieved tracking precision is the track impact-parameter resolution, defined as the dispersion of the distribution of the Distance of Closest Approach (DCA) of the reconstructed (primary) tracks to the interaction vertex. It is the parameter that defines the capability of a vertex detector to separate secondary vertices of heavy-flavour decays from the interaction vertex. A comparison of the impact-parameter resolution of ITS2 and ITS3 is shown in figure 1.4 for pions at typical pseudorapidity  $\eta = 0.5$ . The solid lines show the resolution for tracks fitted in the seven ITS layers only, while the dashed lines show the resolution for tracks fitted in both the TPC and the ITS. For  $p_T \sim 1 \text{ GeV}/c$ , the impact parameter resolution of ITS3 plus TPC is a factor of about two better than that of ITS2 plus TPC.

Figure 1.4: Impact parameter resolution for primary charged pions as function of the transverse momentum for the ITS2 upgrade (blue) and the ITS3 upgrade (red) in the transverse plane (left panel) and in the longitudinal direction (right panel). All solid lines show the results with FMCT and ITS only, all dashed lines show the results with FMCT and ITS+TPC, all open circles show the results with full MC and ITS only. [3].

A Fast Monte Carlo Tool (FMCT) was used in detector design phase to optimize the number of layers, their radial position, the material budget and the detector resolutions. The latter, for the ITS-only case, were also estimated with

a full MC simulation, where pions were transported through the detector material using the GEANT3 package [30] and their trajectories were reconstructed using the Cellular Automaton ITS tracker [2]. The Full MC resolutions are shown by the circles for both ITS2 and ITS3 in figure 1.4, while FMCT results are shown as solid or full lines. The two results are found to be very similar, validating the conclusions drawn from the fast simulation tool.

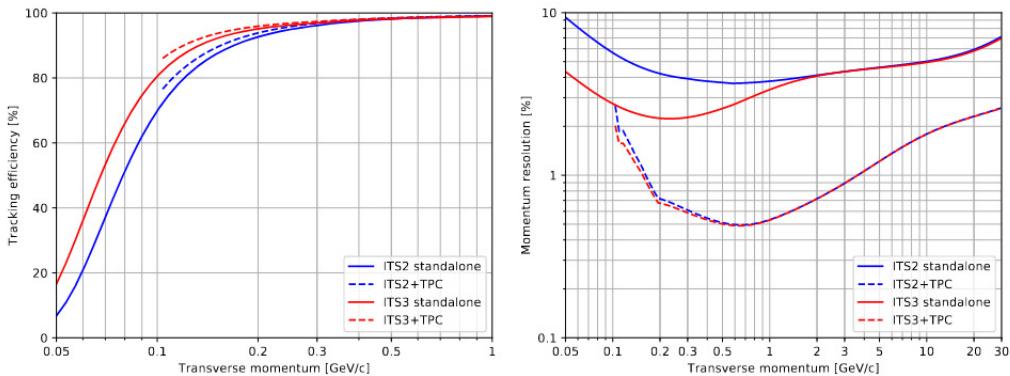

The left panel of figure 1.5 shows the track-finding efficiency in the environment of a single central Pb–Pb collision. The plot shows the efficiency only for "correct tracks", i.e. tracks that contain all clusters produced by the same particle, while at low  $p_T$  there will be a significant contribution from tracks with one or more clusters from other particles. The  $p_T$  resolution of the ITS3, shown on the right panel of figure 1.5, benefits significantly from the lower material budget of the Inner Barrel in the ITS-only mode. In the ITS–TPC combined tracking mode, at  $p_T$  below 0.5  $GeV/c$ , the ITS3 configuration essentially gives the same  $p_T$  resolution as ITS2.

Figure 1.5: Track finding efficiency in central Pb–Pb collisions (left panel) and transverse momentum relative resolution (right panel) in the ITS-only (solid lines) and ITS–TPC combined (dashed) reconstruction modes as function of transverse momentum for the ITS2 and two different ITS3 detector configurations. All solid lines show the results with FMCT and ITS only, all dashed lines show the results with FMCT and ITS+TPC. [3].

### 1.3.3 Upgrade concept

#### The ITS2

The current ITS2 is formed by seven layers, grouped into two separate barrels. The Inner Barrel (IB) consists of the three innermost layers (Layers 0 to 2), while the Outer Barrel (OB) contains the two middle and two outer layers (Layers 3 to 6) (See figure 1.2). The three Layers of the IB are also referred to as the Inner Layers, while, for the OB, Layers 3 and 4 are referred to as Middle Layers

and Layers 5 and 6 as Outer Layers. In the azimuthal direction, each Layer is segmented in elements called Staves. The Stave, which extends over the whole length of the respective Layer, is the basic building block of the detector. The Stave contains all structural and functional components, thus making it the smallest operable part of the detector.

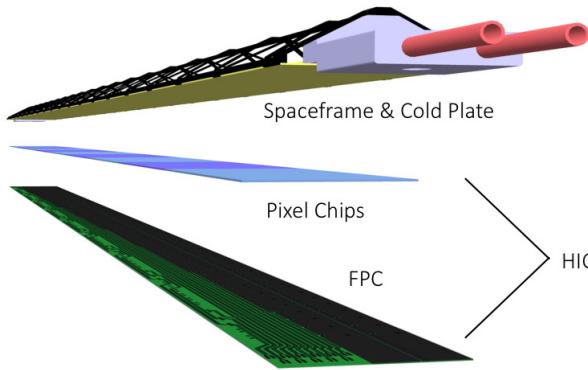

The three Inner Layers are built with identical Staves, which are based on the following elements:

- Space Frame: a carbon fibre support structure providing the mechanical support and the necessary stiffness.

- Cold Plate: a sheet of high thermal-conductivity carbon fibre with embedded polyimide cooling pipes, which is integrated into the Space Frame. The Cold Plate is in thermal contact with the Pixel Chips to remove the generated heat.

- Hybrid Integrated Circuit (HIC): an assembly consisting of a polyimide Flexible Printed Circuit (FPC) onto which the Pixel Chips and some passive components are bonded.

Each IB Stave is instrumented with one HIC, which consists of nine ALPIDE chips in a row connected to the FPC, covering an area of  $15 \text{ mm} \times 271.2 \text{ mm}$  including  $100 \mu\text{m}$  gaps between adjacent chips along the longitudinal direction ( $z$ ). The interconnection between Pixel Chips and FPC is implemented via conventional aluminum wedge wire bonding. The HIC is glued to the Cold Plate with the Pixel Chips facing it in order to maximize the cooling efficiency. A schematic drawing of the IB Stave is shown in figure 1.6. An extension of the FPC, like shown in figure 1.7, connects the Stave to a patch panel that is served by the electrical services entering the detector only from one side.

Figure 1.6: Schematic layout of the ITS2 Inner Barrel Stave. Nine pixel sensors are mounted on a flexible printed circuit (FPC) to form a hybrid integrated circuit (HIC). The HIC is glued on a carbon fibre support structure (Space Frame), which integrates a water cooling circuit (Cold Plate) [3].

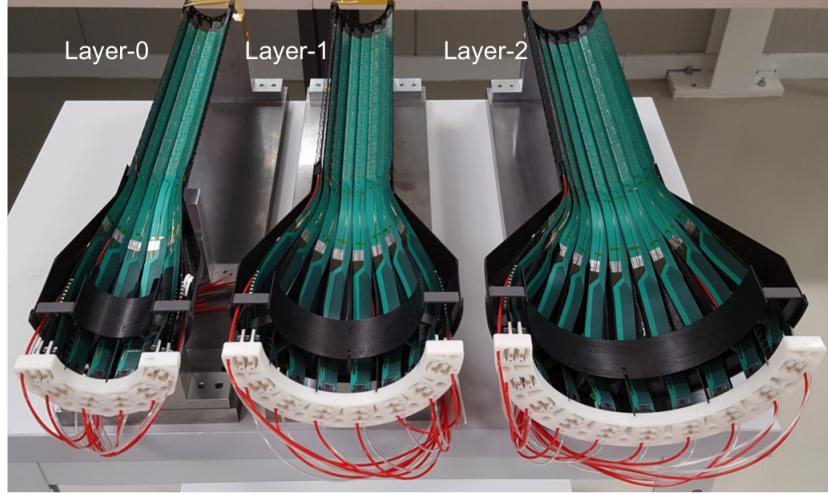

Figure 1.7: Photograph of the ITS2 IB half-layers (Layer-0, Layer-1 and Layer-2). [3].

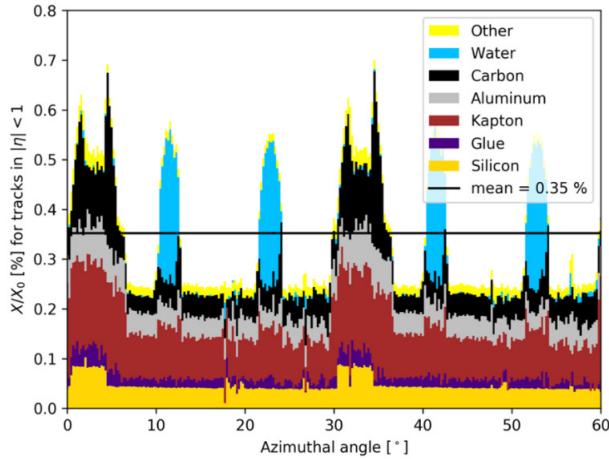

Figure 1.8 shows the azimuthal distribution of the material of Layer 0 traversed by particles with  $|\eta| < 1$ . Adjacent Staves are partially overlapping to ensure detector hermeticity. The highest peaks correspond to the overlap of the reinforced structures along the edges of the Space Frame, which guarantee the required stiffness, while the narrow spikes correspond to the reinforcement of the upper central vertex. The peaks at a value of about 0.5%  $X_0$  are due to the polyimide cooling pipes embedded in the Cold Plate, which have an inner diameter of 1.024 mm and a wall thickness of 25  $\mu\text{m}$  and are fully filled with water during the operation of the detector. The average value (0.35%  $X_0$ ) is unprecedentedly low, which is of crucial importance to achieve high impact parameter resolution at low transverse momentum.

The table 1.1 summarizes the layout parameters of the ITS2.

Table 1.1: Layout parameters of the ITS2. [31]

|                      | Inner Barrel |         |         |         | Outer Barrel |         |         |

|----------------------|--------------|---------|---------|---------|--------------|---------|---------|

|                      | Layer 0      | Layer 1 | Layer 2 | Layer 3 | Layer 4      | Layer 5 | Layer 6 |

| Length [cm]          |              | 27.1    |         | 84.3    |              | 147.5   |         |

| Radial position [cm] | 2.3          | 3.1     | 3.9     | 19.4    | 24.7         | 35.3    | 40.5    |

| N. staves            | 12           | 16      | 20      | 24      | 30           | 42      | 48      |

| N. HICs              | 12           | 16      | 20      | 384     | 480          | 1176    | 1344    |

| N. pixel chips       | 108          | 114     | 180     | 2688    | 3360         | 8232    | 9408    |

Figure 1.8: Azimuthal distribution (averaged over  $|\eta| < 1$ ) of the material budget of ITS2 Layer 0. The angular interval in the figure corresponds to two staves, with  $\varphi = 0$  on the horizontal plane, where two staves from the upper and lower half barrels partly overlap. [3].

### Improvement strategies

As shown in the material breakdown of the ITS2, the silicon sensor, which has a thickness of  $50 \mu\text{m}$  and ideally is the only component that would be needed in the detector acceptance, contributes only 15 % to the total. The rest is due to the material of the electrical substrate (Flexible Printed Circuit, FPC), which represents the main contribution (50 %) including the passive components and the glue, of the cooling circuit (20 %) and of the carbon spaceframe (15 %). In order to significantly reduce the material budget, the electrical, mechanical and cooling material have to be reduced. The electrical substrate is the flexible printed circuit that distributes the supply and bias voltages as well as the data and control signals to the pixel sensors. In standard CMOS circuit manufacturing, the maximum size of a chip is limited to the reticle area defined by the field of view of the photolithographic process, which is typically a few centimeters in both directions. For this reason, the Stave surface is covered by tiling several sensors. The reticle is just stepped and repeated across the wafers to create multiple identical images of the same circuit or group of circuits. Stitching is a technology that allows the fabrication of an image sensor that is larger than the field of view of the lithographic equipment [32]. In this technology, the reticles which fit into the field of view of that equipment are placed on the wafer with high precision, achieving a tiny but well defined overlap. In this way, wafer-scale sensors can be manufactured, allowing the fabrication of sensors of arbitrary dimensions, the only limit being the size of the wafer. This opens the possibility of fabricating a pixel sensor with the dimension of an entire stave. The distribu-

tion of power and electrical signals could then be done entirely inside the silicon chip and the electrical substrate would terminate close to the chip edge, where the interconnections to the chip would be realized.

Concerning the elimination of the material associated with the cooling circuit, the possibility of using a low-speed ( $< 2 \text{ ms}^{-1}$ ) air flow to remove the heat produced by the ITS Inner Layers, in combination with peripheral liquid cooling, was experimentally demonstrated as a viable option for sensors with a power density below  $20 \text{ mWcm}^{-2}$  [3]. It should be noticed that the higher the air flow, the stiffer the mechanical support structure has to be, in order to keep the vibrations of the sensor, caused by the air flow, smaller than the intrinsic spatial resolution.

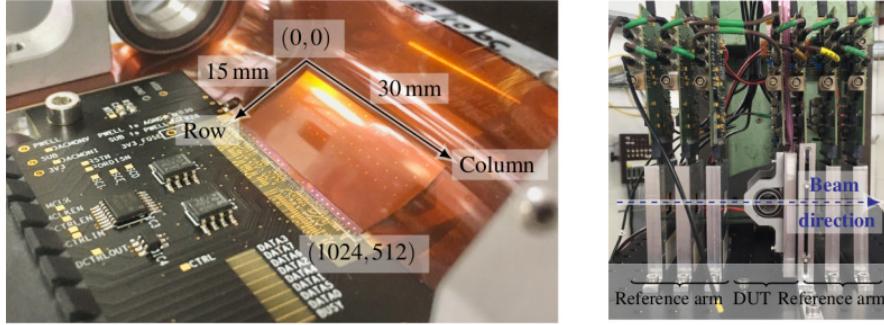

Each ALPIDE chip contains approximately  $5 \times 10^5$  pixels, each measuring about  $27 \mu\text{m} \times 29 \mu\text{m}$ , arranged in 512 rows and 1024 columns, for a total active area of  $30 \text{ mm} \times 15 \text{ mm}$ . The total power consumption is  $180 \text{ mW}$ , which corresponds to a power density of about  $40 \text{ mWcm}^{-2}$ . However, most of this power (about  $150 \text{ mW}$ ) is dissipated by the digital interface circuitry and the high-speed output data links, which are located in a small area of about  $30 \text{ mm} \times 1.5 \text{ mm}$  close to one edge of the chip. Only about a sixth of the total power is dissipated in the pixel matrix, which corresponds to a power density of about  $7 \text{ mWcm}^{-2}$ . This would be well within the range for which air cooling represents a viable and effective solution. On the other hand, to place the pixel sensor digital periphery at the end of the sensor would be possible if the sensor had the dimensions of a stave.

As mentioned before, at present small sensors are mounted edge-to-edge on top of an FPC module that provides the power distribution and data bus. The key new idea is to make use of the stitching technology avoiding the need of an FPC and realizing a single large sensor, where power distribution is managed internally, confining the interconnections to the outside world to the sensor edge.

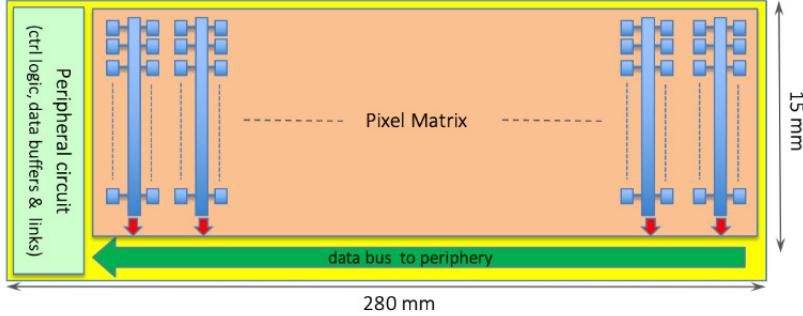

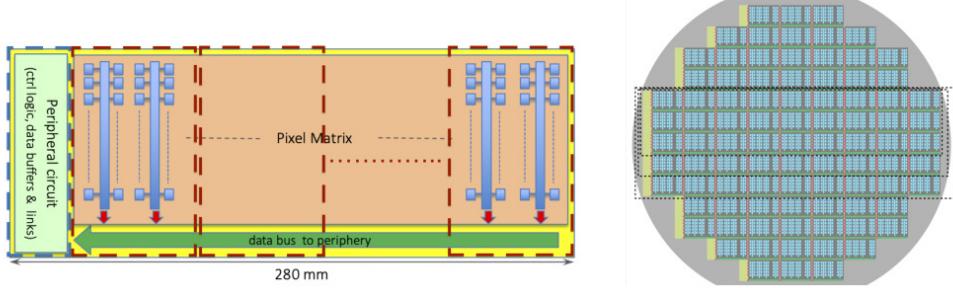

A first step in these directions would be to develop a chip with stitching in 1 dimension according to the scheme outlined in figure 1.9 of size  $15 \text{ mm} \times 280 \text{ mm}$ , which corresponds to the full length of a stave. The columns run along the short side of the sensor, and have the same length as in the current ALPIDE sensor. Data are extracted from the matrix as in the ALPIDE chip with hit-driven circuitry based on a priority-encoder addressing scheme [33]. Groups of 16 double columns are read out sequentially, but in principle all of them could be read out in parallel<sup>9</sup>. Data are transmitted from the bottom of the columns along one long side of the sensor to the periphery, as indicated by the green arrow at the bottom of figure 1.9.

The periphery, shown on the left part of the sensor in figure 1.9, contains the control logic to steer the priority encoders, the interface for the configuration of the chip and the serial data transmitters. Since the chip periphery is outside the detector acceptance, there is no particular constraint on the size of the periphery that will be adjusted on the basis of the requirements.

The data bus is conservatively estimated to take an area of up to  $50 \mu\text{m}$

---

<sup>9</sup>A more detailed description of the ALPIDE chip readout will be given in a next chapter.

Figure 1.9: Diagram of stitched sensor in one direction (horizontal and vertical dimensions not to scale). Stitching in the vertical direction is also possible. [3].

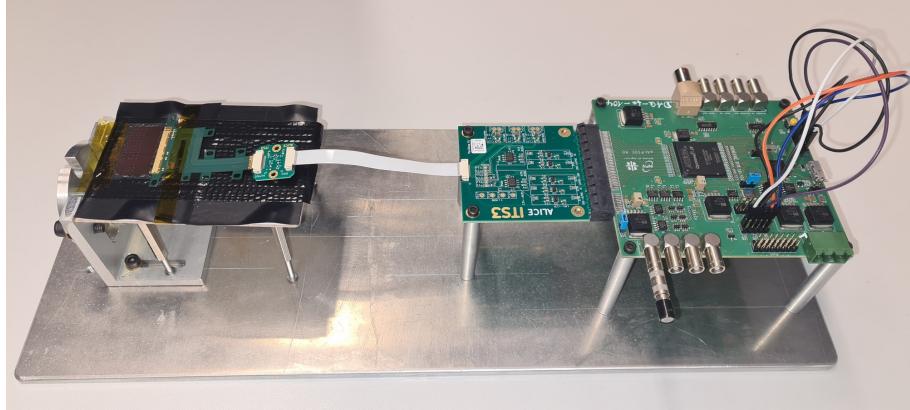

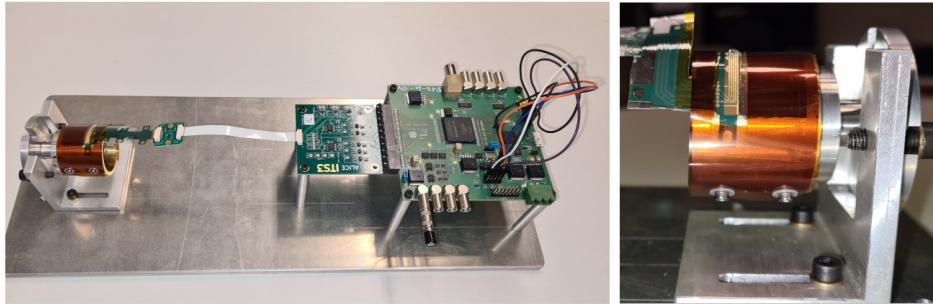

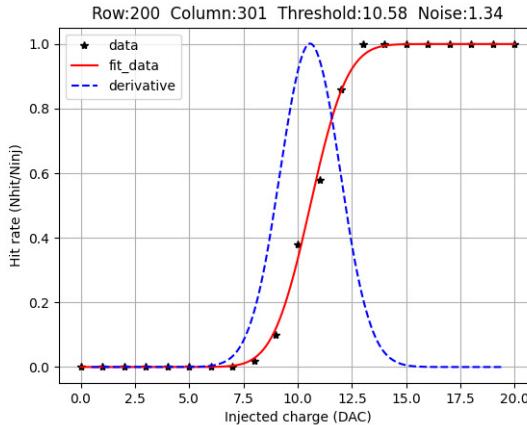

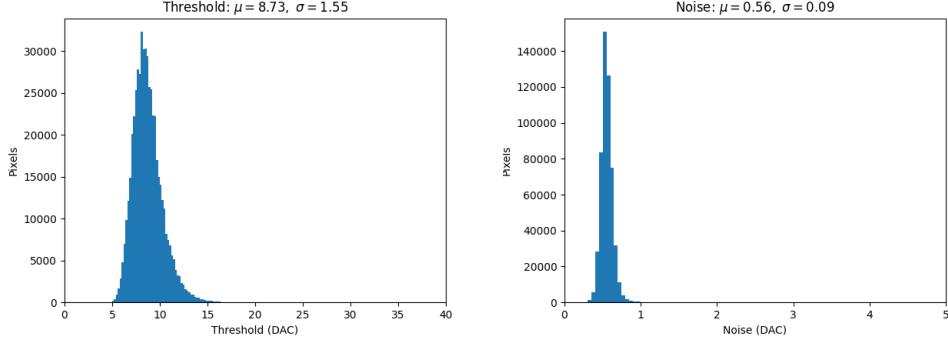

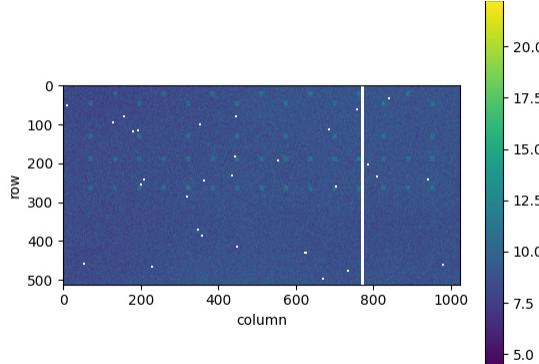

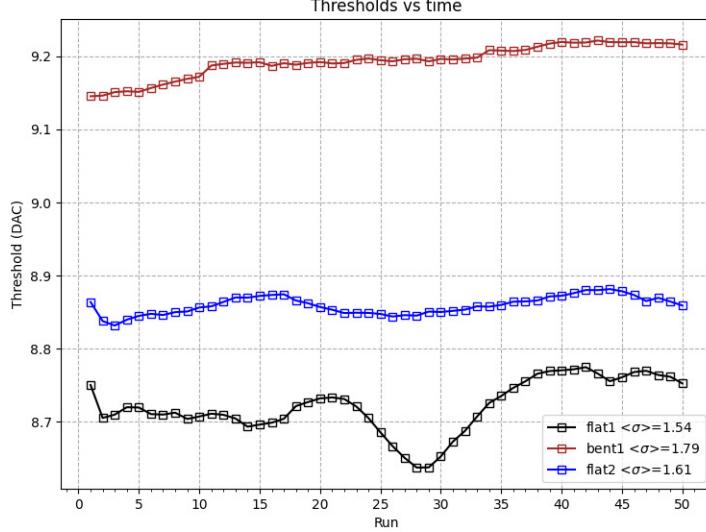

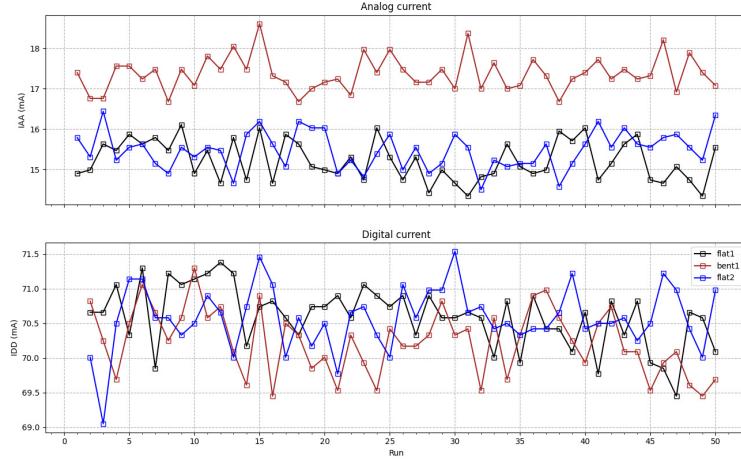

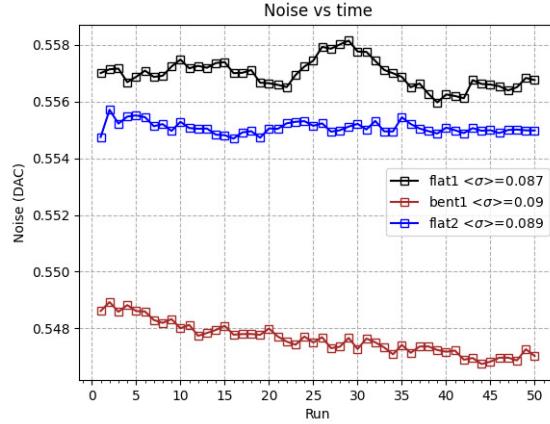

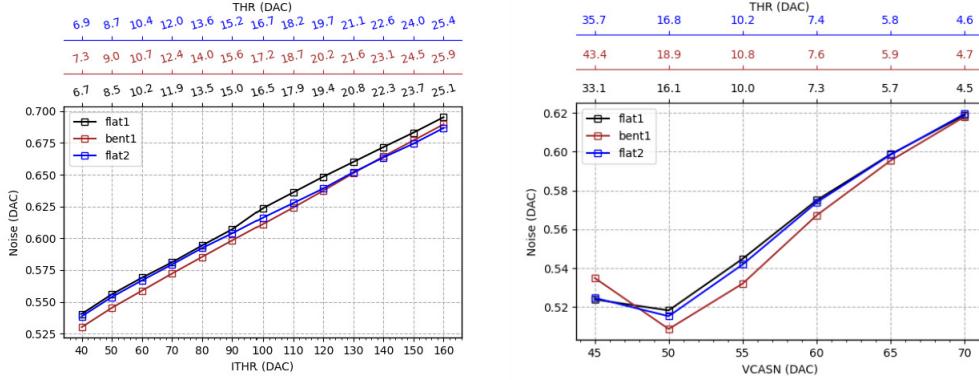

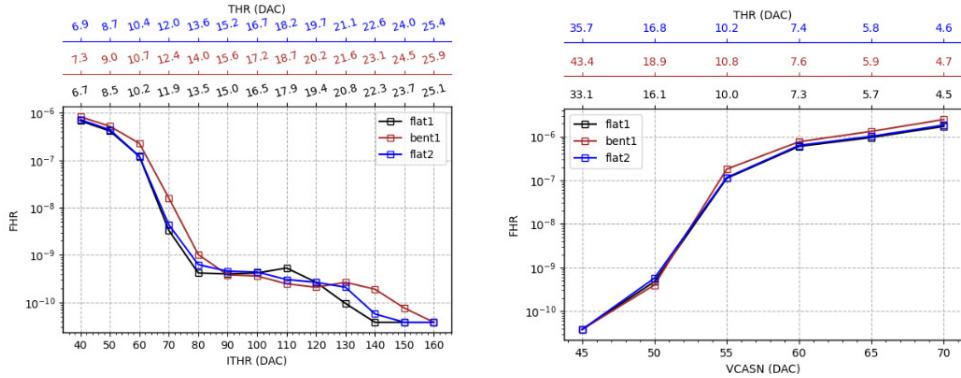

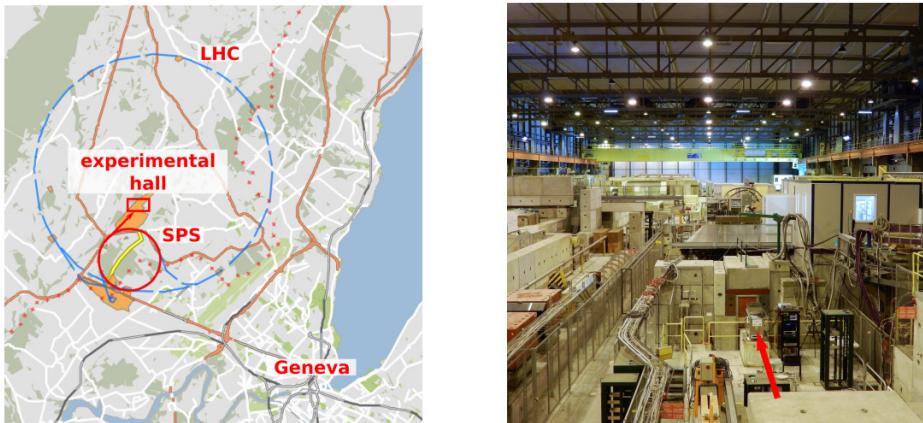

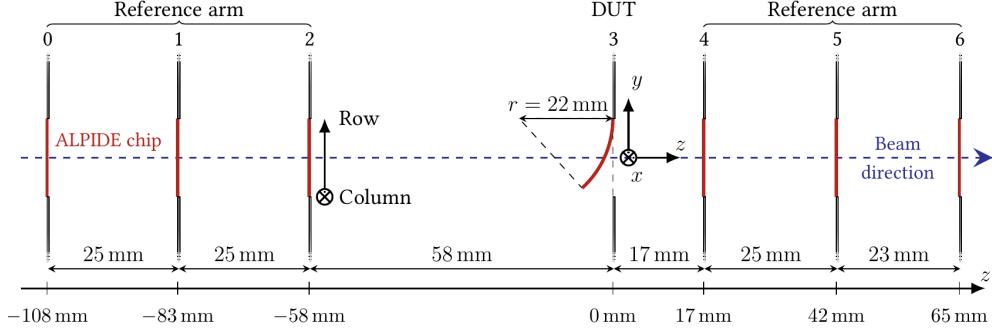

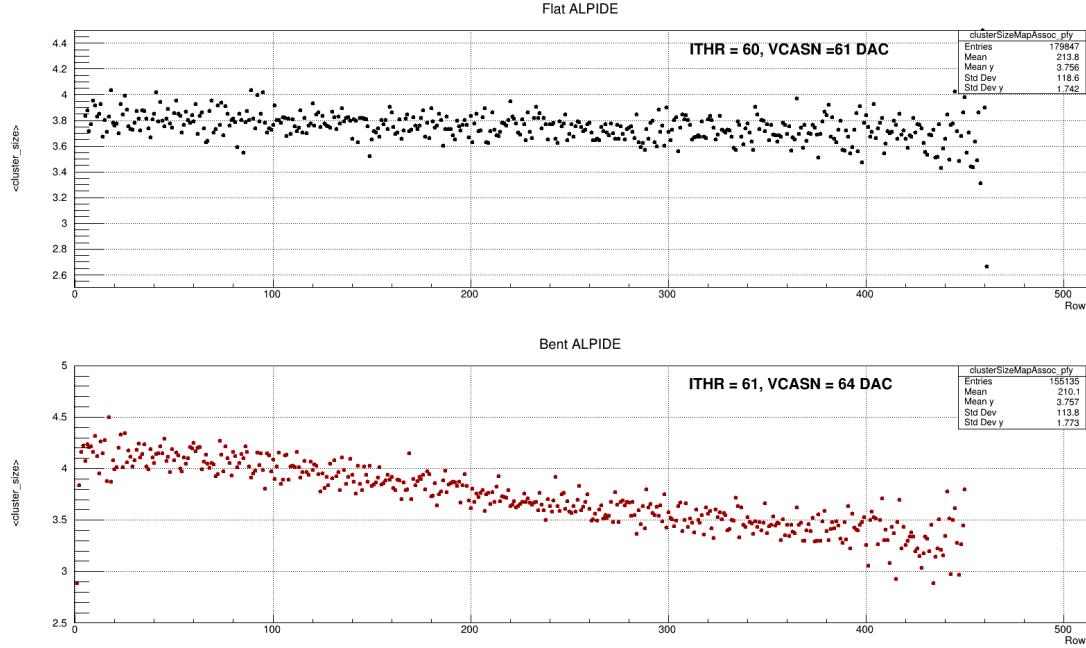

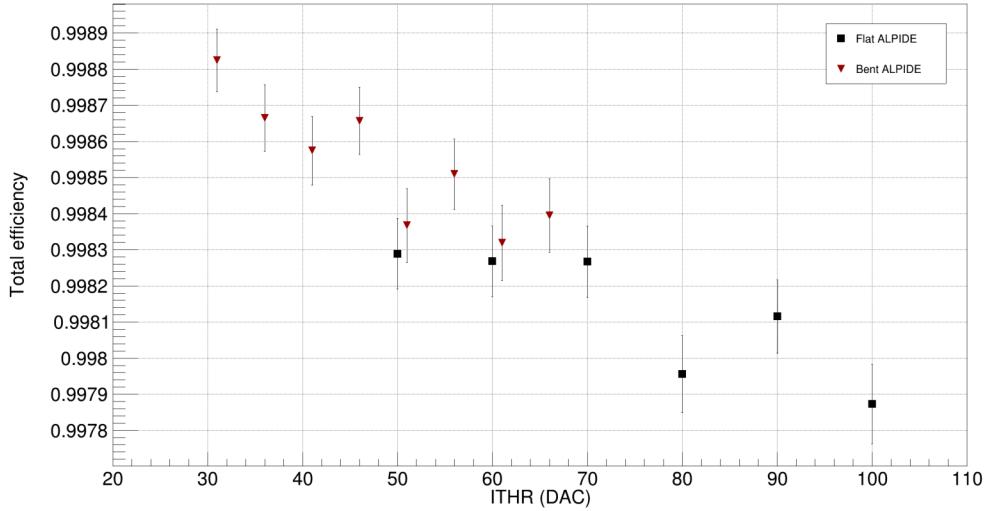

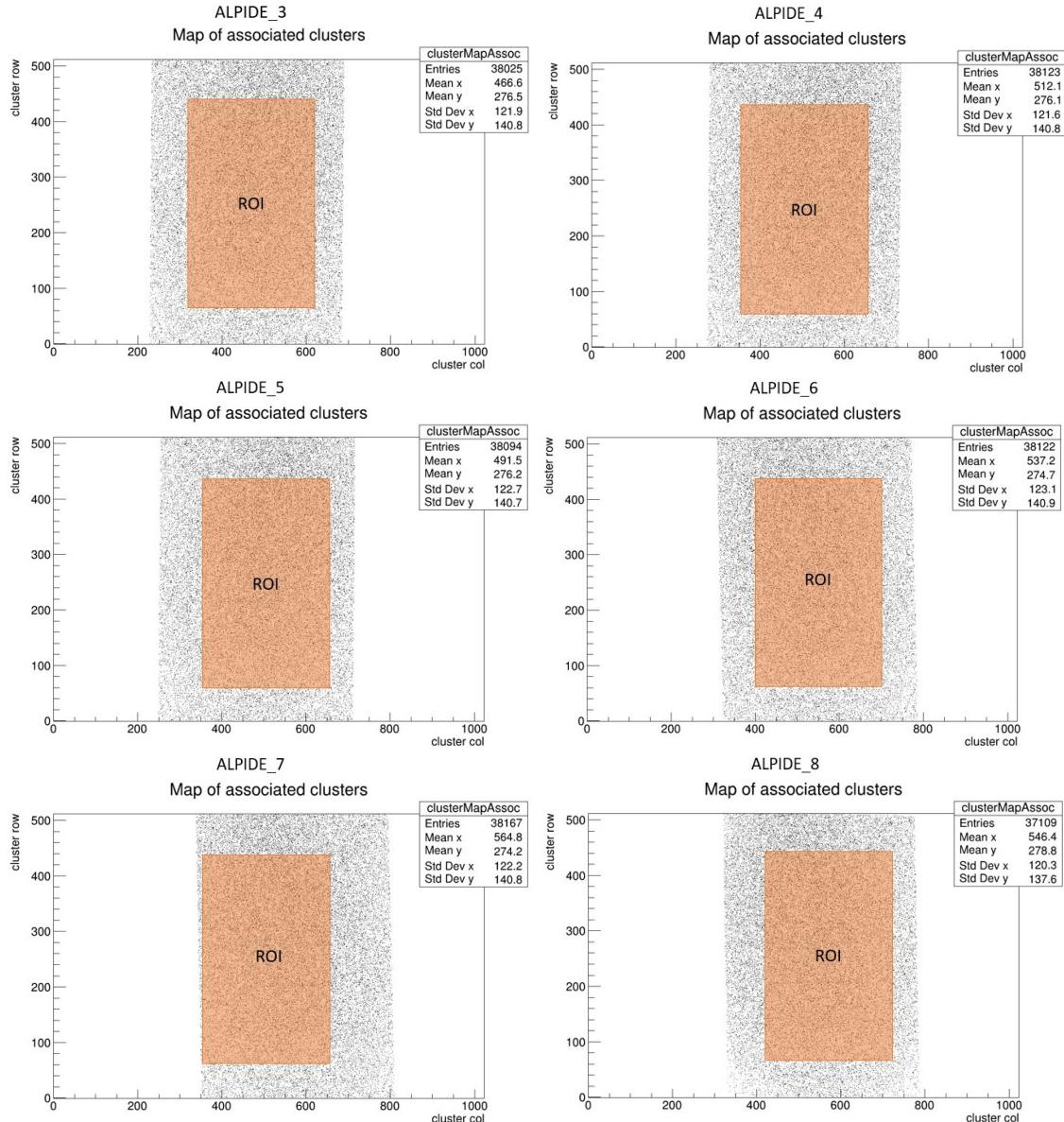

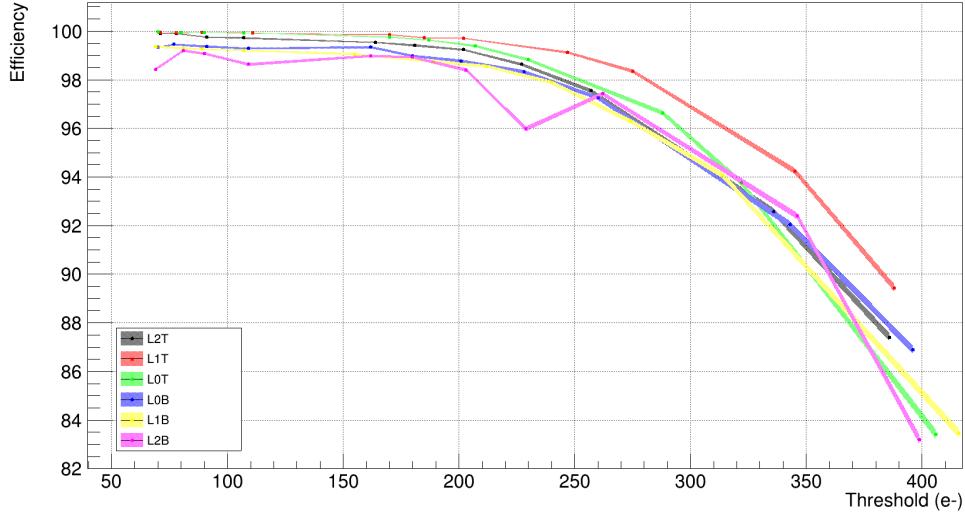

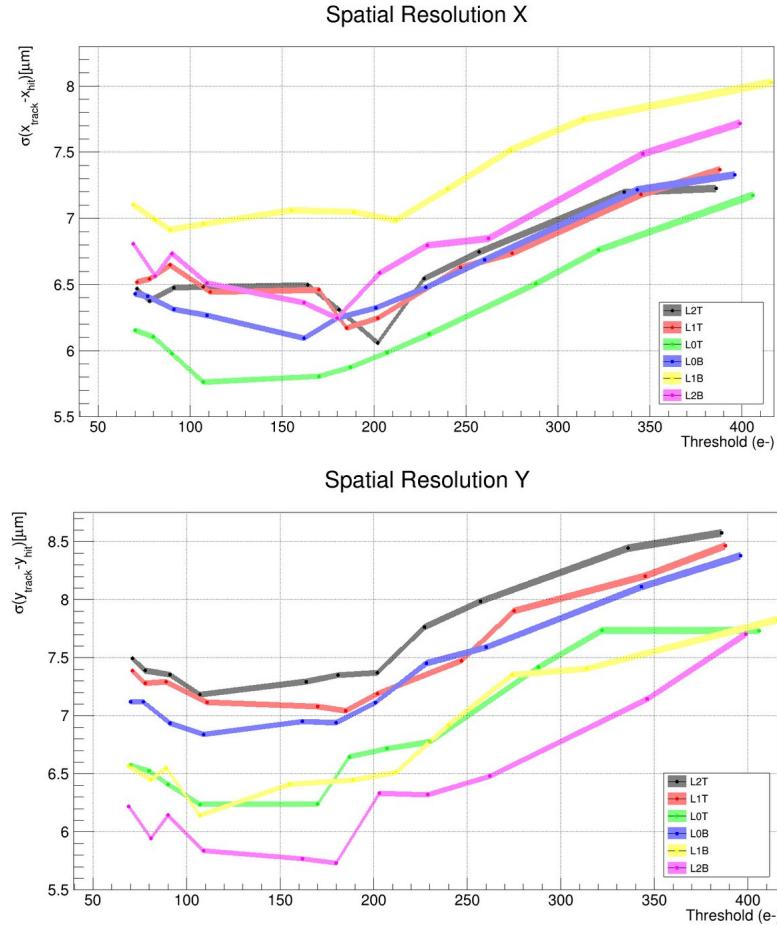

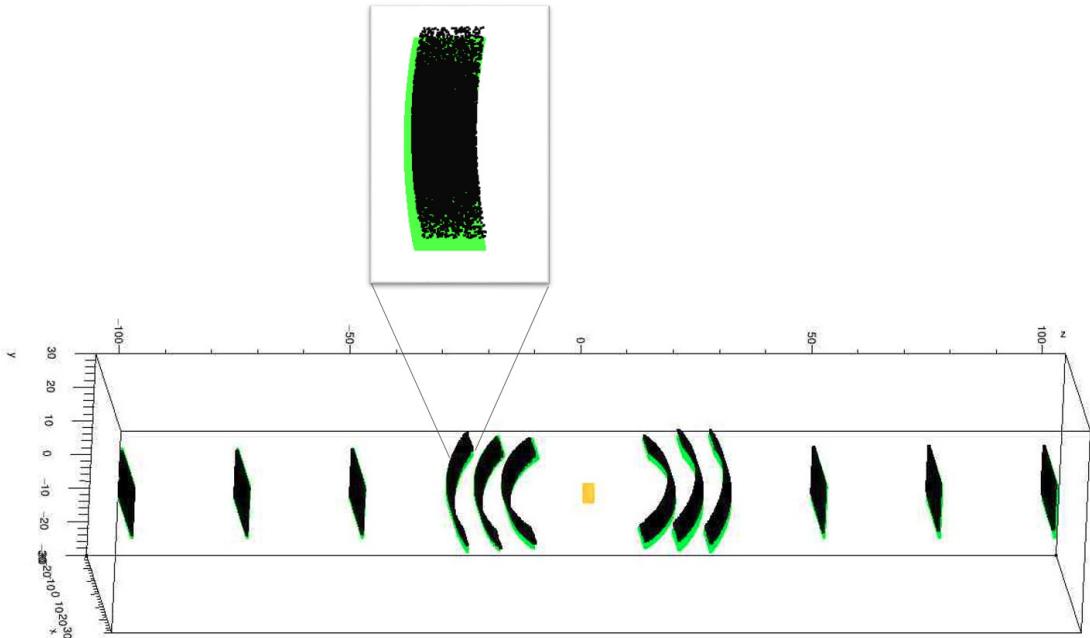

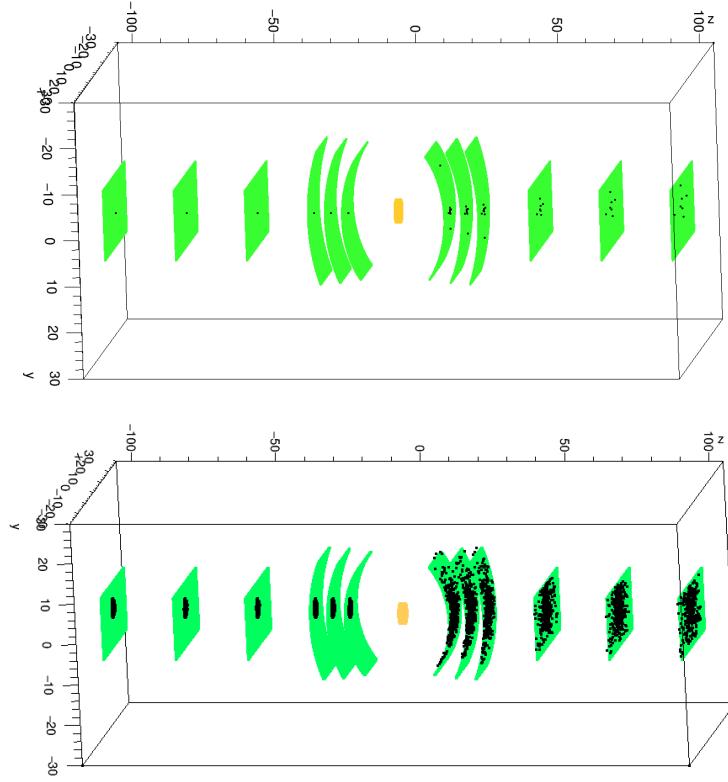

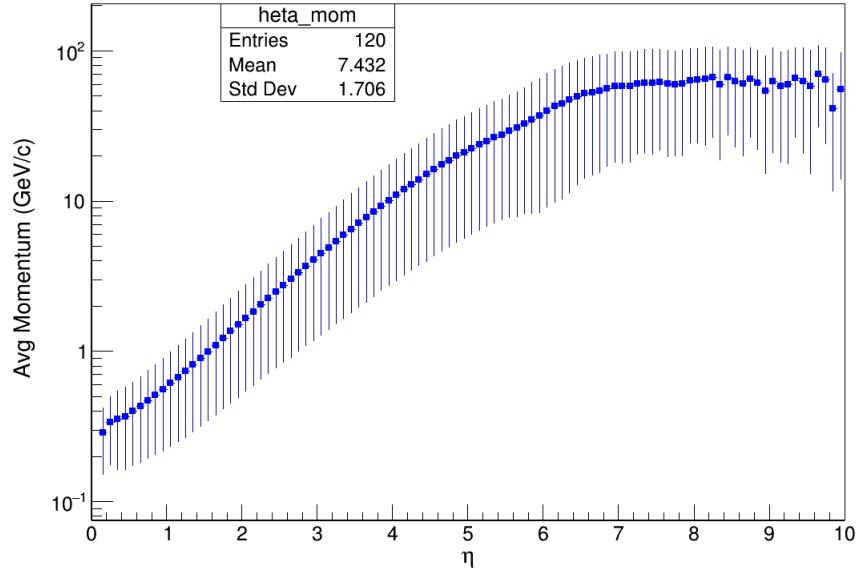

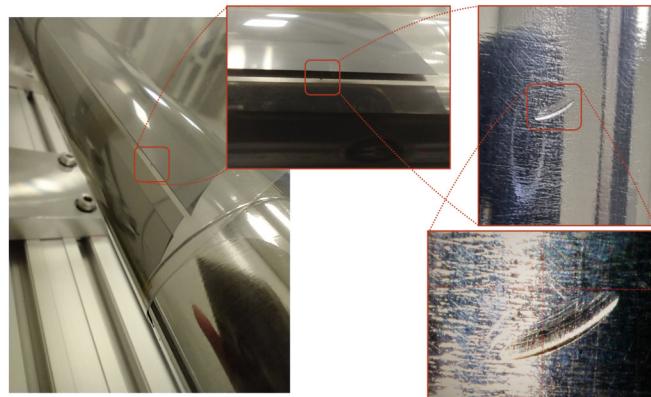

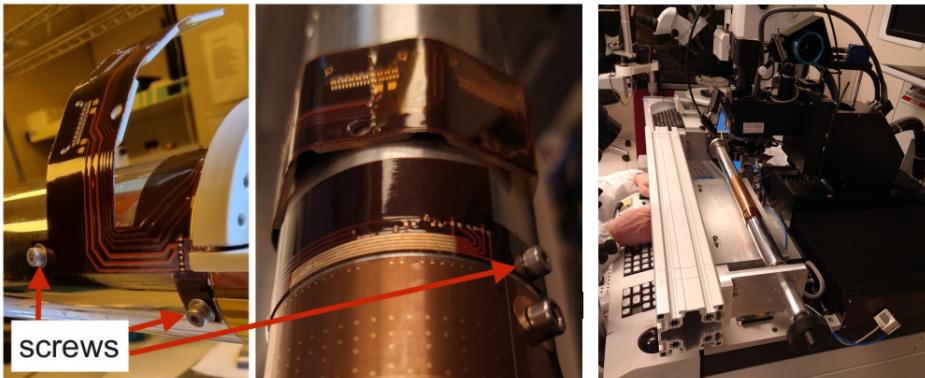

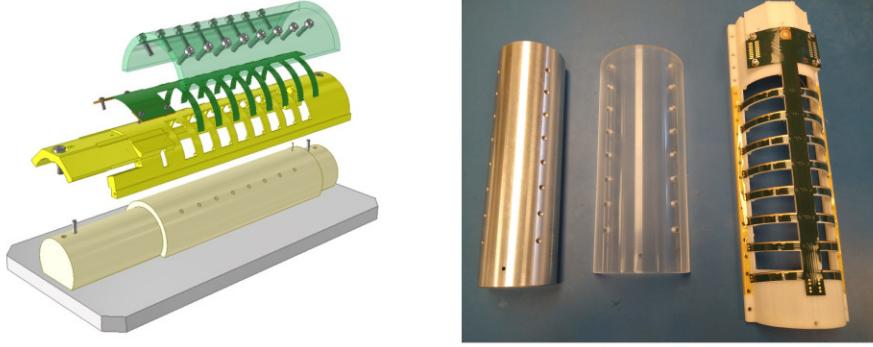

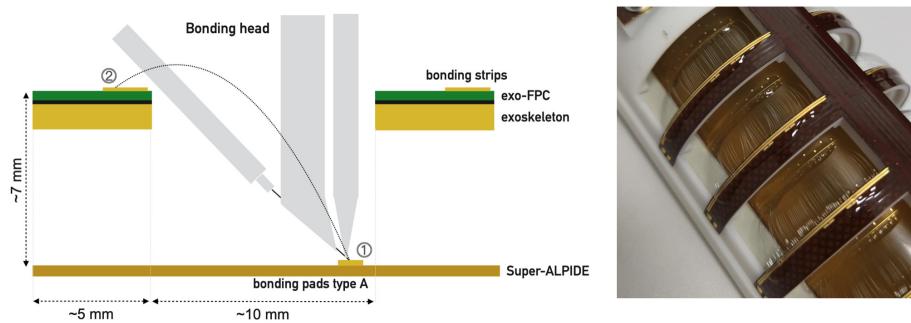

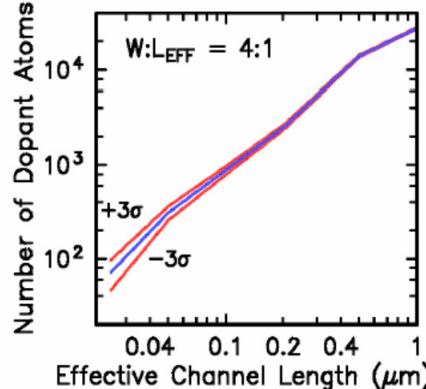

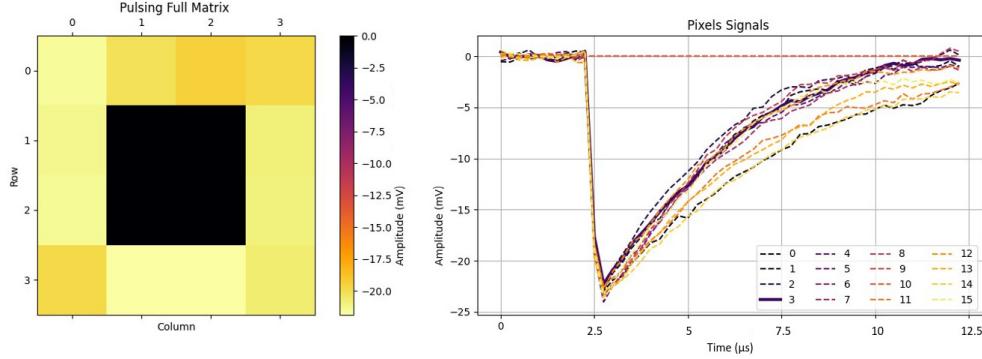

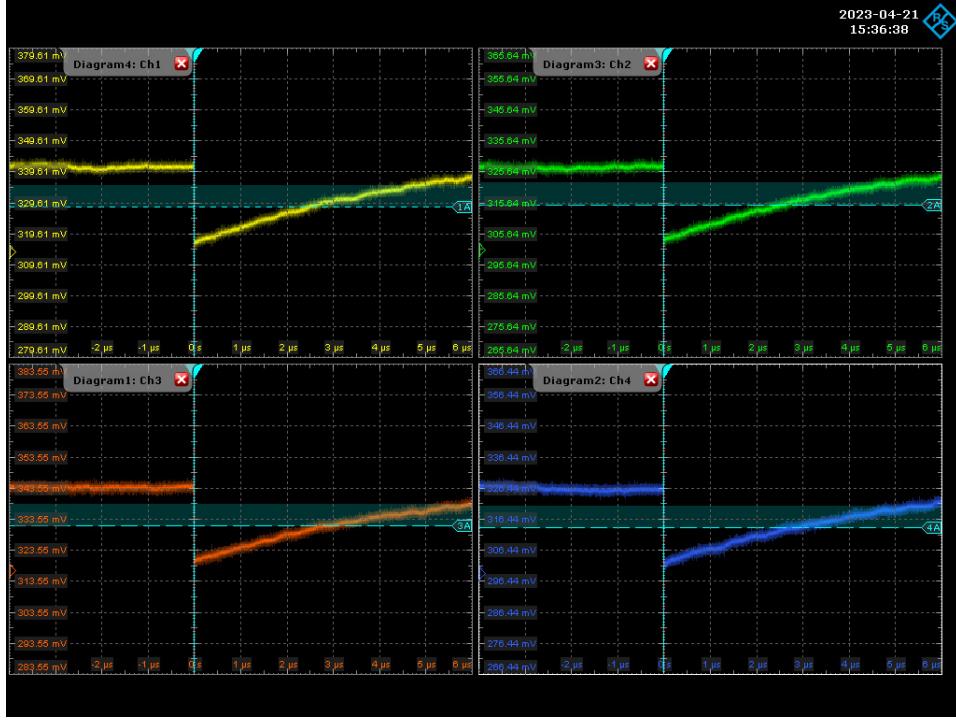

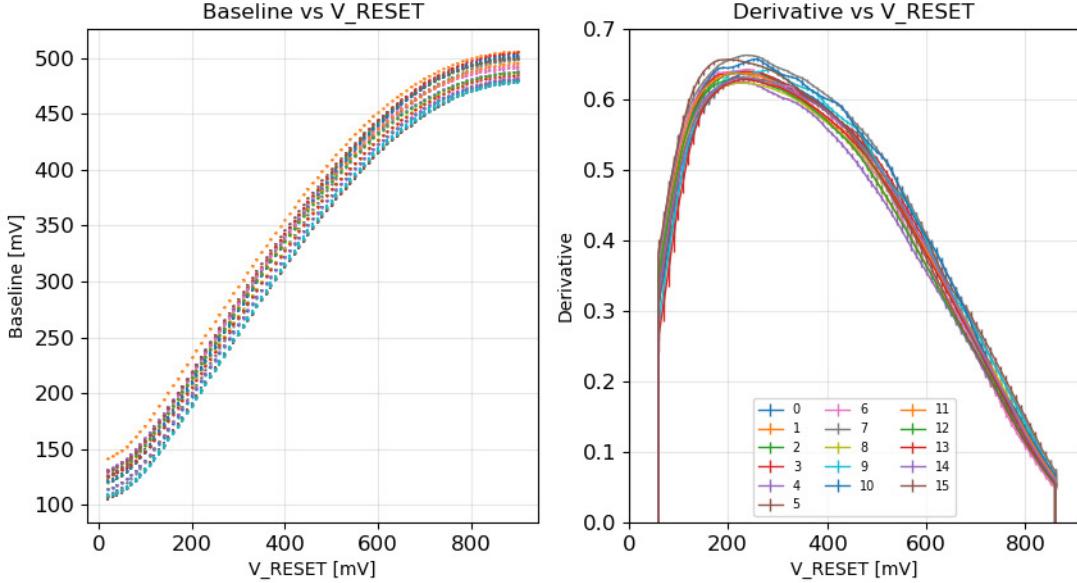

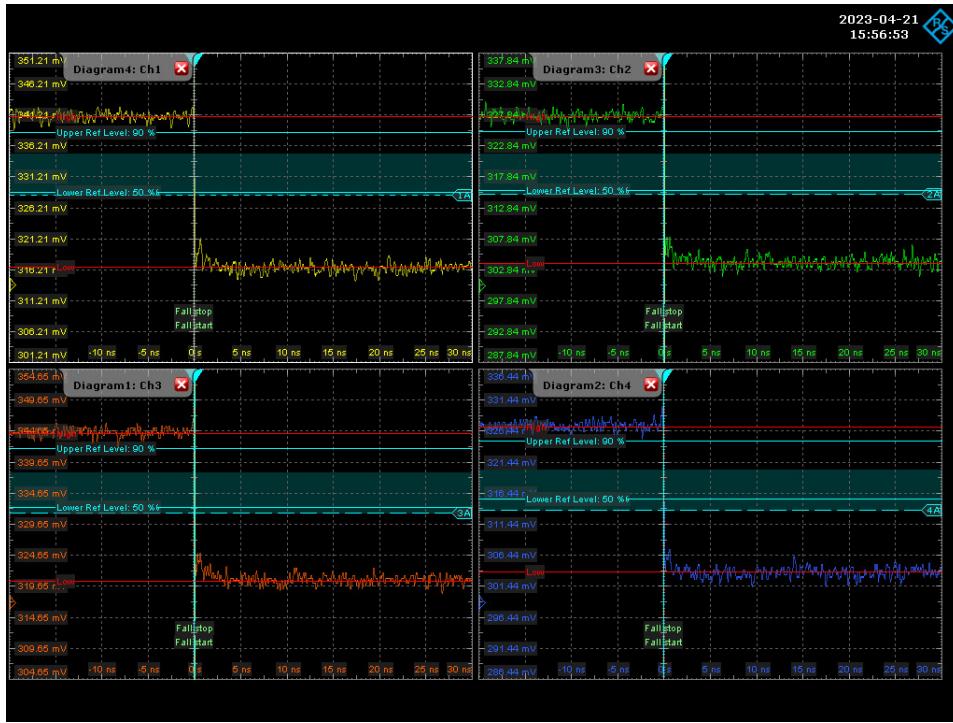

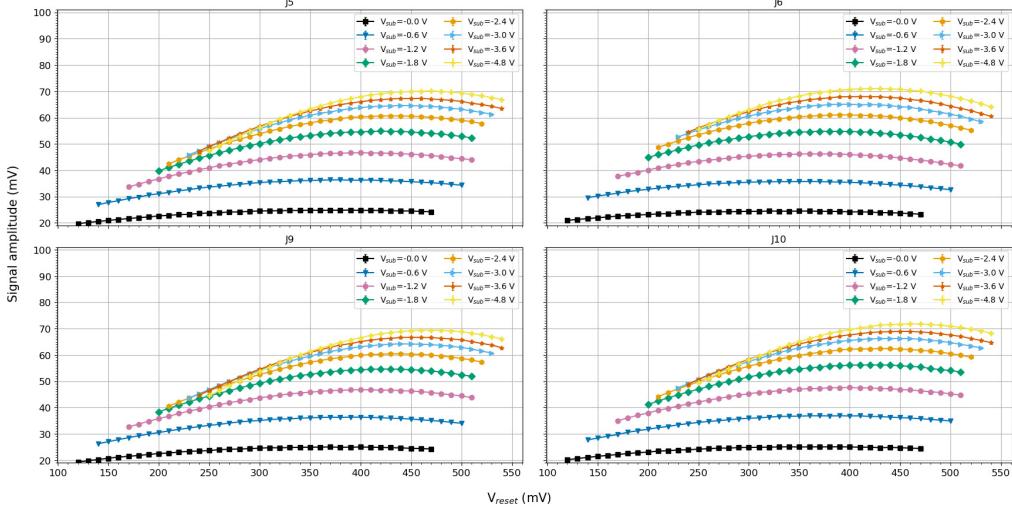

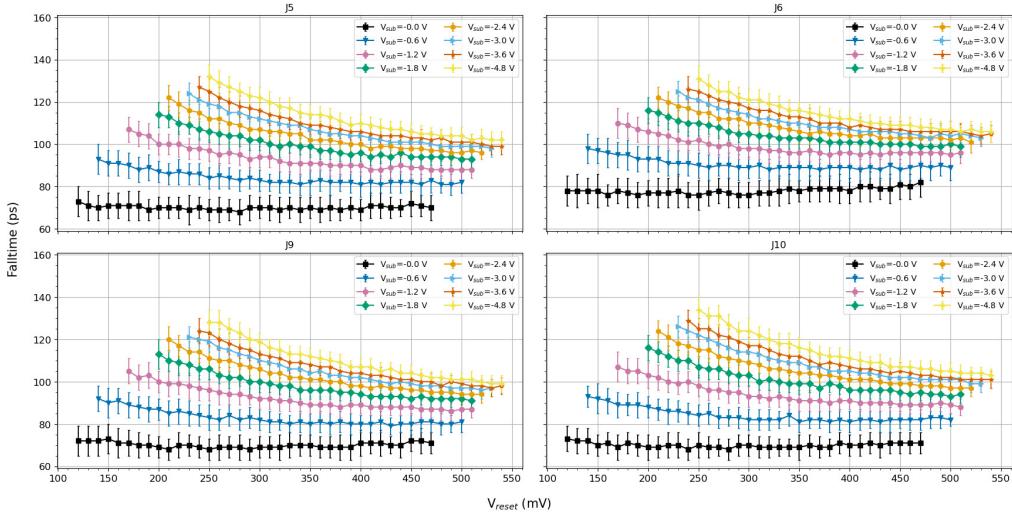

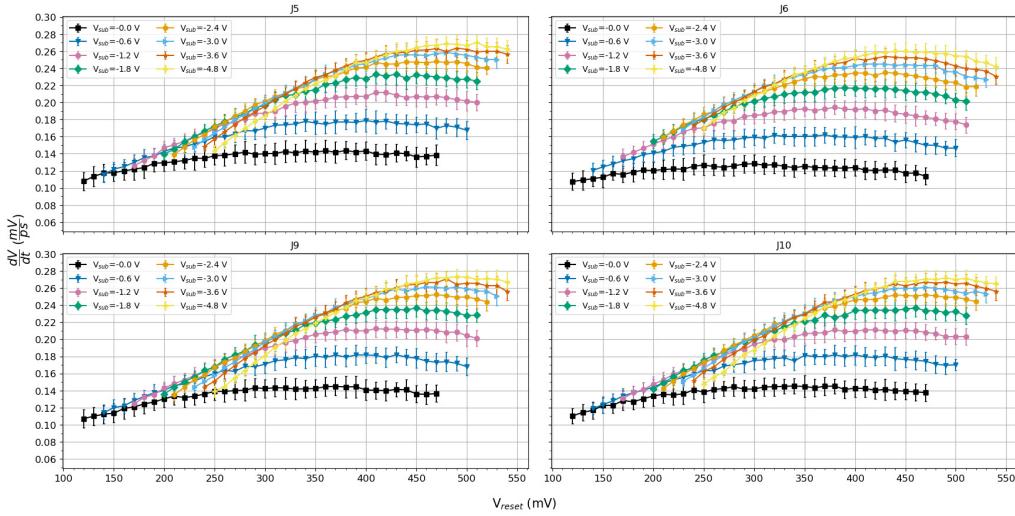

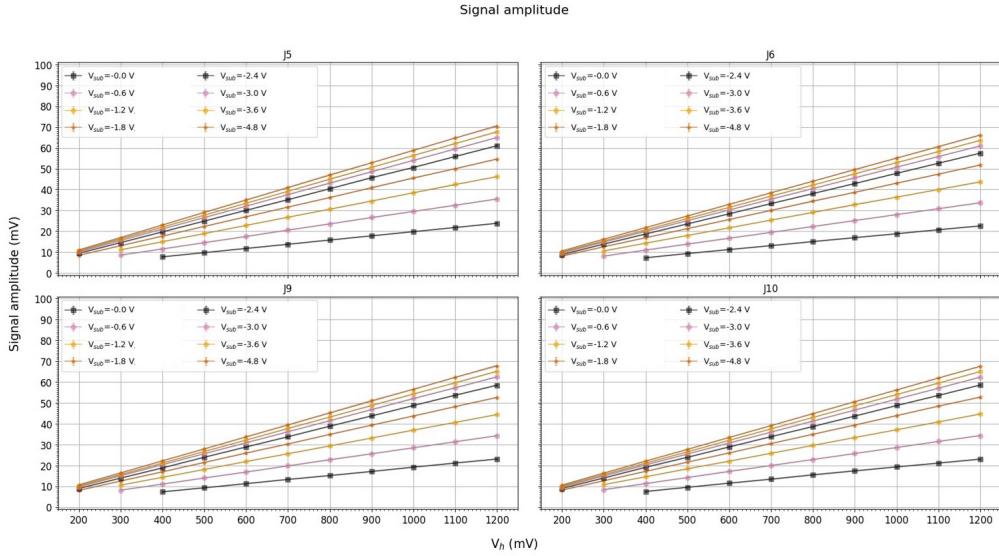

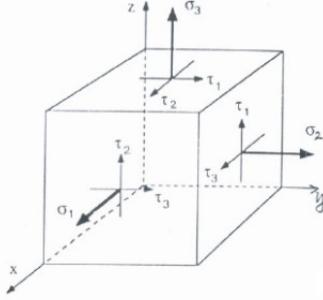

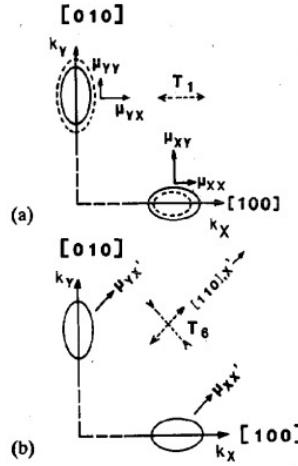

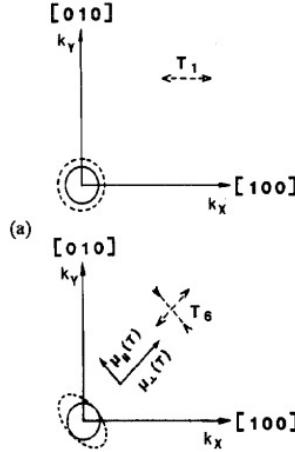

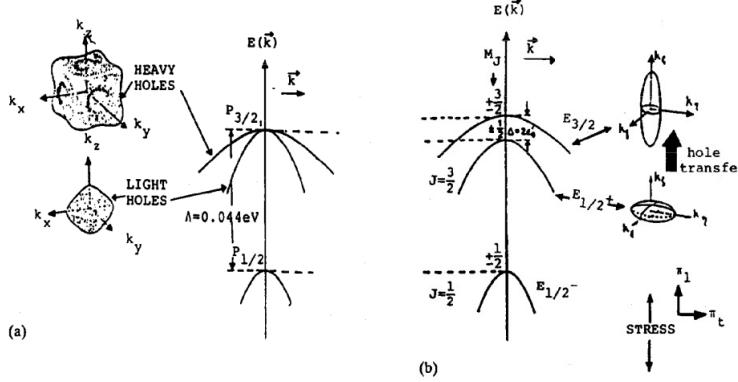

$\times 280\text{ mm}$ , which amounts to a dead area that corresponds to about 0.3 % of the detector acceptance. As a comparison, the ITS2 has gaps in the  $z$ -direction between adjacent chips (matrix to matrix) of  $100\text{ }\mu\text{m}$ , which result in a total dead area of 0.5 %.